# Specification and Verification of Real-Time Constraints in Coarse-Grain Dataflow

Dana S. Henry

MIT / LCS / TR-487 May 1991

### © Dana S. Henry 1991

The author hereby grants to MIT permission to reproduce and to distribute copies of this technical report in whole or in part.

This report describes research done at Schlumberger Corporation and written at the Laboratory of Computer Science of the Massachusetts Institute of Technology. Funding for the Laboratory is provided in part by the Advanced Research Projects Agency of the Department of Defense under Office of Naval Research contract N00014-89-J-1988.

This report was originally published as the author's Master's thesis.

### Specification and Verification of Real-Time Constraints in Coarse-Grain Dataflow

Dana S. Henry

Technical Report MIT / LCS / TR-487 May 1991

MIT Laboratory for Computer Science 545 Technology Square Cambridge MA 02139

### Abstract

We present a method for verifying real-time constraints in a distributed, coarse-grain dataflow environment starting with a program which has already been allocated onto a machine. The user specifies the timing of each module together with real-time constraints; and we verify the constraints. To deduce program's timing, the user specifies all possible behaviors of each dataflow module and assigns timing costs to each module's behavior. We use the behavior and timing of individual modules to derive a data independent timing model for the entire program. User specifiable constraints include conditional constraints and constraints through non-deterministic paths. An event-driven verification verifies constraints. We justify the need for an event-driven verification, describe design issues, and offer a tagging scheme for sharing state among multiple verifications.

Key Words and Phrases: hard real-time, deadline, specification, verification.

# Acknowledgements

Many thanks to every one who has helped in the preparation of this thesis. Special thanks to Professor Arvind, my MIT advisor, for his genuine interest, invaluable support, and precious advise which guided the structure and emphasis of this work. Special thanks also to Dr. David Barstow, my Schlumberger advisor, for his continuing encouragement, his invaluable trust, and the wonderful research environment he has provided. Thanks to Schlumberger-Doll Lab for Computer Science and its members for providing a conducive environment during the time I spent working there on this thesis. Thanks to members of the MIT LCS Computation Structures Group for providing a friendly atmosphere at all other times. And, finally, endless thanks and gratitude to my mother and my grandmother for their unconditional love and support always.

# Contents

| 1 | Intr | oductio  | on                                     | 8    |

|---|------|----------|----------------------------------------|------|

|   | 1.1  | Real-T   | ime Software                           | . 8  |

|   | 1.2  | Distrib  | outed Real-Time Software               | . 10 |

|   | 1.3  | Resour   | ce Allocation                          | . 10 |

|   | 1.4  | Synops   | sis                                    | . 11 |

| 2 | Pro  | ject's E | Background                             | 12   |

|   | 2.1  | •        | ation                                  | . 12 |

|   | 2.2  | The Pr   | roblem                                 | . 13 |

|   |      | 2.2.1    | Feedback                               | . 13 |

|   |      | 2.2.2    | Real-Time                              | . 14 |

|   | 2.3  | Goals    |                                        | 15   |

| 3 | Pro  | iect's I | Environment                            | 16   |

|   | 3.1  | •        | n Machine (SM)                         |      |

|   |      | 3.1.1    | Program                                |      |

|   |      |          | Assumptions                            | . 18 |

|   |      | 3.1.2    | Machine                                | . 19 |

|   |      | 3.1.3    | Allocation                             | . 20 |

|   |      |          | Allocation Constraints                 | . 21 |

|   |      |          | Program Topology Constraints           | . 21 |

|   |      |          | Machine Capacity Constraints           | . 22 |

|   |      |          | Dedicated Resource Constraints         | . 22 |

|   |      |          | Real-Time Constraints                  | . 22 |

|   | 3.2  | Examp    | oles                                   | . 22 |

|   |      | 3.2.1    | Tool Arm Attachment                    | 23   |

|   |      | 3.2.2    | SLT-L Measurement                      | 25   |

|   |      | 3.2.3    | Sample Program                         | . 28 |

|   |      | 3.2.4    | Program and Constraint Characteristics |      |

|   |      | 3.2.5    | Sample Machine                         |      |

|   |      | 3.2.6    | Sample Allocation                      |      |

|   | 3.3  | Summa    | ary                                    | 35   |

| 4 | Tim  |          | ecification                            | 37   |

|   | 4.1  | Abstra   | acting Behavior of a Module            | . 39 |

|   |      |          | Simple Modules                         |      |

|   |      |          | Selector Modules                       | . 40 |

|   |      |          | Merge Modules                          | 41   |

|   |                     | Deterministic Merge Modules              | 1  |

|---|---------------------|------------------------------------------|----|

|   |                     | Speculative                              | 2  |

|   |                     | Acknowledged                             | 2  |

|   |                     | Tagged                                   | 3  |

|   |                     | Deterministic Merge Modules Summary 4    |    |

|   |                     | State Dependent Modules                  |    |

|   |                     | Generalization of Merge Modules          |    |

|   |                     | Module's Abstract Behavior Summary       |    |

|   | 4.2                 | Module's Timing Specification            |    |

|   |                     | 4.2.1 Simple Timing                      |    |

|   |                     | 4.2.2 Data Dependent Timing              |    |

|   |                     | 4.2.3 General Timing                     |    |

|   |                     | 4.2.4 Module's Timing Summary            |    |

|   | 4.3                 | Program's Execution Model                |    |

|   | т.о                 | 4.3.1 Static Description                 |    |

|   |                     | 4.3.2 Runtime State                      |    |

|   |                     | Token                                    |    |

|   |                     | Module                                   |    |

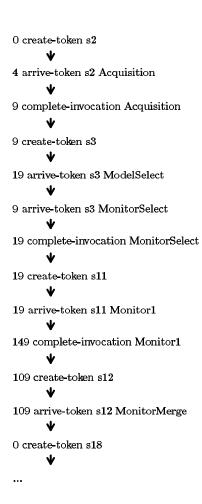

|   |                     | 4.3.3 Event-Driven Simulation            |    |

|   |                     |                                          |    |

|   |                     | Token Creation                           |    |

|   |                     | Token Arrival                            |    |

|   |                     | Invocation Completion                    |    |

|   |                     | 4.3.4 Program's Execution Model Summary  |    |

|   | 4.4                 | Summary                                  | 2  |

| 5 | Con                 | nstraint Specification 64                | 4  |

| Ü | 5.1                 | Simple Constraints                       |    |

|   | $5.1 \\ 5.2$        | Conditional Constraints                  |    |

|   | 5.2 $5.3$           | Nondeterministically Merging Constraints |    |

|   | 5.3                 | Summary                                  |    |

|   | 9.4                 | Summary                                  | o  |

| 6 | $\overline{ m Ver}$ | ification 75                             | 5  |

| Ū | 6.1                 | Verification                             |    |

|   | 0.1                 | 6.1.1 Static Description                 |    |

|   |                     | 6.1.2 Runtime State                      |    |

|   |                     | 6.1.3 Verification                       |    |

|   |                     | Initialization                           |    |

|   |                     | Constraint Testing                       |    |

|   |                     | 6.1.4 Implementation Summary             |    |

|   | 6.2                 | Extensions and Issues                    |    |

|   | 0.2                 | 6.2.1 Contention                         |    |

|   |                     | 6.2.2 Initial Tokens                     |    |

|   |                     |                                          |    |

|   |                     |                                          |    |

|   |                     | 6.2.4 Constant Latency                   |    |

|   | $c \circ$           | Alternative to Event Driven Verification | 11 |

|   | 6.3                 | Alternative to Event-Driven Verification |    |

|   | 6.3                 | 6.3.1 Nondeterminism                     | 3  |

|   | 6.3                 |                                          | 3  |

|   |     |         | Tagging                                             |

|---|-----|---------|-----------------------------------------------------|

|   |     |         | Invocation Times                                    |

|   |     |         | Overlapping Input Streams                           |

|   |     |         | Summary of Nondeterminism in Unordered Verification |

|   |     | 6.3.2   | Contention                                          |

|   |     |         | Module Contention                                   |

|   |     |         | Resource Contention                                 |

|   |     |         | Summary of Contention in Unordered Verification     |

|   |     | 6.3.3   | Alternative Summary                                 |

|   | 6.4 | Tagge   | d Verification to Avoid Duplication of Verification |

|   |     | 6.4.1   | Tagged Verifier                                     |

|   |     |         | Tagged State                                        |

|   |     |         | Event Handling                                      |

|   |     |         | Simple Events                                       |

|   |     |         | Multiple Forks                                      |

|   |     | 6.4.2   | Modified Tagged Verifier                            |

|   |     | 6.4.3   | Tagged Verification Summary                         |

| 7 | Cor | ıclusio | n 98                                                |

|   | 7.1 | Impro   | vements                                             |

|   |     | 7.1.1   | Linking Behavior of Modules                         |

|   |     | 7.1.2   | Specification of Periodic Input                     |

|   | 7.2 | Future  | Directions 90                                       |

### Chapter 1

### Introduction

Many computerized systems are subject to strict time constraints. Control systems in the oil logging industry, automated manufacture, space exploration, as well as defense, call for fast, time-bound response. If a delay in response beyond the specified time-bound would lead to a system failure (with often dire consequences), the system is classified as a hard real time system.

### 1.1 Real-Time Software

The needs of these hard real-time systems differ from the common needs addressed by the standard computing environments. Most programming languages abstract functional behavior from timing considerations. Most operating systems and network protocols offer a few time bound services.

This lack of high-level support has lead to many ad hoc approaches. Many time-critical systems have been implemented at assembly level. Higher level implementations have been tested on specific prototypes with common input cases. Others have been subjected to stochastic simulations insensitive to small populations and unstable operating conditions – the essentials of worst case verification. Not surprisingly, such solutions have led to high development costs and unexpected failures.

In contrast, an optimal real-time system should provide a user with programming ease and predictability. The system should accept a high-level specification of real time requirements and verify their feasibility.

Investigated specification approaches vary from integrated program specifications as in realtime languages, to isolated timing specifications. Of the programming languages, the best known is Ada which allows specification of relative constraints. More thorough treatment of real time concepts can be found in research languages such as LUSTRE [12], a synchronous, real time dataflow language. Other approaches range from use of static typing to specify relative and absolute time predicates [13] to the extension of temporal logic to model states and events through clock ticks [14].

Verification efforts vary with the nature of timing constraints. Relative timing constraints enforce sequencing of events within an execution and can be verified without knowledge of machine speeds. Absolute timing constraints place absolute bounds on execution latencies and require knowledge of hardware timing. They are typical of hard real time systems.

Research in verification of relative time constraints has met with much success. Formal specifications such as those based in temporal logic can be used to prove liveness and precedence relations.

Verification of absolute constraints has generated attention at two different levels, at the low machine level and at the high specification level. At machine level, commercial projects have successfully bound system latencies. Masscomp's Real Time Unix [23], for instance, binds system response times through fixed priority scheduling for predictable schedules, through memory locking for processing free of paging and swapping, and through kernel preemption for bound delay of real time processes due to outside system requests.

At higher level, few of the formal specification methods have succeeded in providing a clean interface to the low machine level verification. One of the more successful approaches in this respect has been Jahanian and Mok's real time logic (RTL) [11]. Their logic relies on safety assertions, maximum delays along each module, for deadline specification. As long as all assertions are met by the underlying machine, an absolute constraint is feasible. Such assertions hide synchronization and contention costs and correspond to worst case analysis of individual latencies as explored by Leinbaugh and Yamini [5].

More accurate latency bounds can be achieved through direct simulation. However, as Stankovic [1] points out, this approach must tackle the complexity barrier. For all but the simplest programs, accuracy must be sacrificed to lower the cost of computing the simulation.

### 1.2 Distributed Real-Time Software

The design of a real-time system is further complicated by the frequent use of multiple processors, which may be necessary for several reasons. First, the computing power of a single processor may not be enough to meet hard real time constraints. Second, an application may require different processor types. And third, acquired data may need to be processed at different locations.

As a result, an optimal real time system should provide specification and verification methods within a distributed, heterogeneous environment. This requirement heightens the need for modular timing specifications. It further introduces the need for verifiable real-time communication and its specifications.

### 1.3 Resource Allocation

A further complication in the design of a hard real time system is the need for an optimized, predictable resource allocation method. A predictable allocation schedule is essential to absolute constraint verification. While easy to achieve, predictability has not been required of many existing schedulers [23].

A reasonably optimized allocation method is essential to meeting absolute constraints. In an optimal real-time system, one would like an automated allocator to arrive at an optimal allocation schedule. Such an allocator would be NP complete even for the much simpler case of two identical processors executing independent tasks with no communication overhead [9]. As a result, all practical scheduling algorithms within a multiple processor environment rely on heuristics. The most common approach is a back-tracking branch and bound search within a simulation. Simplified versions include heuristic transformation of a program graph onto a multiple processor graph, and an independent allocation of computation paths beginning with the most critical path. Several conflicting goals in these approaches are the minimization of complexity, the preservation of a global program view, and the consideration of all relevant time costs.

### 1.4 Synopsis

In this thesis, we attempt to develop a technique for dealing with real time constraints in the context of a device control and data acquisition system for oil well logging. We narrow our attention to periodic programs and start with an existing software architecture, the Stream Machine [17]. We augment and simplify the computational model to achieve a simple timing specification. We analyze constraints and check feasibility within an allocation scheme.

The content of this thesis tracks the progress of its project. Chapter one introduces the issues and complexity in real time systems and points out related work. Chapter two presents initial thoughts and goals behind this project. Chapter three describes the targeted applications and the inherited programming environment, the Stream Machine. Chapter four presents a specification method for the envisioned real-time costs in our computational model. It outlines our approach towards real-time specification and implements this approach. Chapter five presents a specification method for the envisioned real-time constraints. Chapter six offers a verification method for the developed constraint specifications. It outlines the initial assumptions, and describes and optimizes our verifier. Finally, Chapter seven of the thesis, draws results and lessons from the project and suggests areas of further work.

### Chapter 2

# Project's Background

### 2.1 Motivation

The motivation for this work came from the increasing need for feedback control in acquisition of oil well data. On site acquisition and interpretation of oil well data is the main service of the Schlumberger Wireline Testing and Service Companies. Schlumberger acquires and interprets data for clients throughout the world. All acquisition is done with tools and computational resources contained within a highly customized vehicle, the Schlumberger truck. Upon request, the regional Schlumberger branch dispatches a truck to a well site, lowers appropriate sensory tools into the well and acquires data through attached on board computers.

It is essential that well data acquisition be fast and reliable. The acquisition of data halts the production of oil within a well. As a result, the acquisition must be fast in order to minimize the lost revenue and operational expense of an idle well. The malfunction of the sensory tools lowered into the well or of the computational environment can cause delay and loss or damage of expensive tools. As a result, the acquisition must be highly reliable. Finally, the acquired data must be accurate and relevant to further interpretation.

The relevance, accuracy, and reliability of the acquisition process can be enhanced through real-time feedback to the sensory tools. Real-time feedback can increase the accuracy of acquired data as the tool adjusts its speed, resolution, and other parameters based on feedback data. Similarly, real-time feedback can improve relevance of acquired data as the tool zooms in on critical regions of the well and reacts quickly to any aberrations. Finally, real-time feedback can improve reliability through real time monitoring of tool conditions and prompt recovery of an endangered tool.

### 2.2 The Problem

### 2.2.1 Feedback

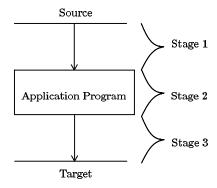

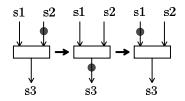

Our process of generating feedback consists of three stages. In stage one, we acquire data from a periodic source. In stage two, we feed the acquired data to an application program and compute feedback data. Finally in stage three, we forward feedback data to its target. Figure 2.1 illustrates the feedback process.

Figure 2.1: The Three Stages of a Feedback Process.

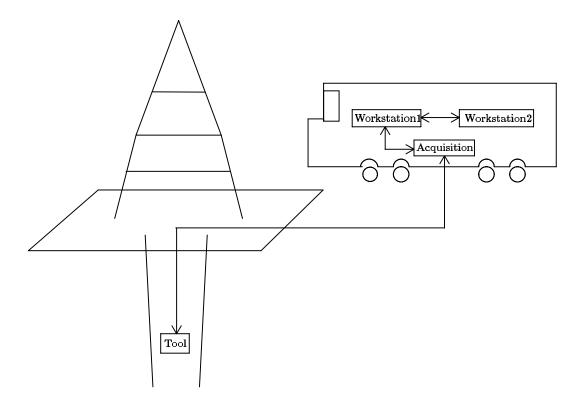

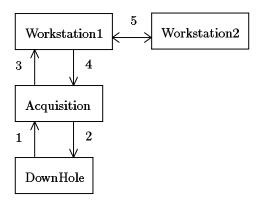

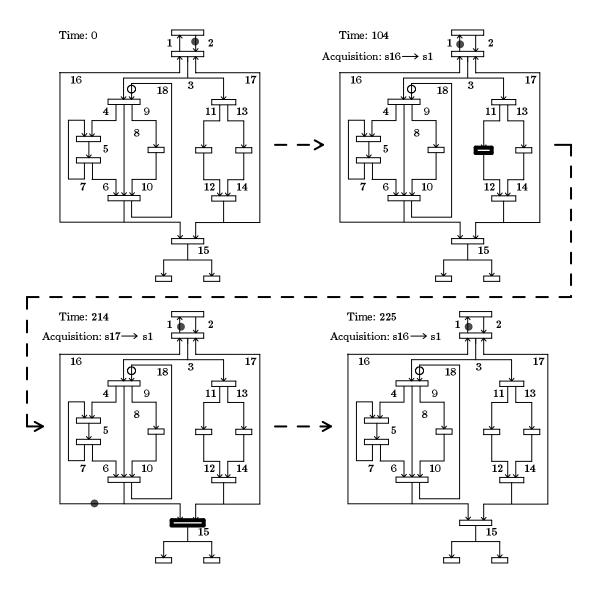

Figure 2.2 illustrates the feedback process within our present domain. In our present domain, the periodic source of data is a sensory tool lowered into an oil well. Data acquired by the tool's downhole processor propagates up the well hole into the Schlumberger truck. On board the truck, the data is accepted by a dedicated acquisition processor. The acquisition processor communicates with an on board workstation via shared memory. Two on board workstations may cooperate in computing feedback data. The target of feedback data is, again, a sensory tool within the well.

We expect our domain to evolve as feedback requirements increase with new sensory tools and as technology progresses. Specifically, we expect to see more computing power on the Schlumberger truck. Multiple and specialized processors and coprocessors will absorb the increased computational load. As the temperature and pressure resistance of VLSI circuits increases, we also expect to see part of the computing stage shifting from the truck into the well. A processor within the sensory tool will reduce the data bandwidth between the tool and the truck and shift low-computation feedback control into the tool.

Figure 2.2: Resources Utilized by a Feedback Process within our Domain.

### 2.2.2 Real-Time

The relevance of feedback information varies with time. For example, a feedback directive to recover a tool becomes irrelevant once the tool has been lost. Similarly, a feedback adjustment of a measurement technique becomes irrelevant once the measurement conditions have changed. To achieve our aims, we must

- 1. constrain the latency of each feedback process, and

- 2. guarantee to meet imposed constraints.

To guarantee imposed constraints, we must implement each feedback process and verify that our implementation meets the imposed constraints. To implement a feedback process, we must assign resources to each of the three stages of a feedback process and write the application program of stage 2.

One way to verify a feedback latency constraint is to run and time our feedback process implementation. If the process completes within the constrained time, the constraint has been met. However, this meeting of a constraint does not reflect on future invocations of this implementation. For one, the latency of each invocation may be data dependent. Different input

data may require different computation and propagate through the feedback process at different speed. To guarantee a constraint, we would need to run and time our implementation for all possible input values - an unlikely prospect.

Moreover, the individual latencies within an implementation may vary. The latency through a communication channel, for instance, may depend on the instantaneous contention for that channel. The latency of code execution may depend on the momentary number of system call interrupts. While all individual latencies within a feedback process must have a finite upper bound to guarantee a real-time constraint, a single run of the feedback process is unlikely to capture the worst case scenario.

### 2.3 Goals

The goal of this project is to design a prototype verification system for real-time feedback processes in the Schlumberger oil well logging context. We start with the present feedback process model - the Stream Machine. The goal of our system is to integrate into this model

- 1. specification of implementation's timing,

- 2. specification or implementation's real-time constraints, and

- 3. verification of implementation's constraints.

### Chapter 3

# Project's Environment

This project builds on top of an existing application domain and an existing feedback process model. The following chapter describes both the application, the Schlumberger well acquisition software, and the model, the Stream Machine. Moreover, the chapter gives examples, extracts their characteristics, and formulates a representative problem used through the remainder of this thesis.

### 3.1 Stream Machine (SM)

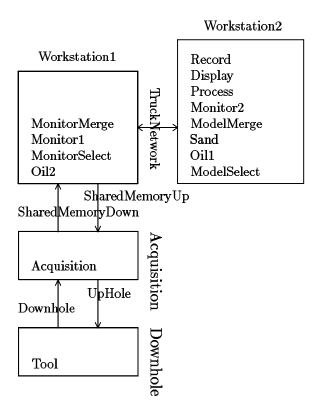

The computational model employed on the Schlumberger trucks is the Stream Machine (SM). The SM imlements a computational model on top of a distributed computer network. An instance of an SM implementation consists of a program description, a machine description, and an allocation description. An SM program consists of buffered communicating sequential processes. A machine consists of distributed hardware resources such as those on the Schlumberger truck. And an allocation maps program components - processes and streams, onto the machine resources - the hardware.

### 3.1.1 Program

A program consists of a set of processes, or modules, and a set of streams. Modules communicate via tokens along streams. Each module interleaves a finite number of suspending and executing states. Suspended, a module awaits a token along a given input stream. Alternately, a module may await a token along one of several input streams, thus introducing nondeterminism. On the token's arrival, a module consumes the arrived token, and executes. While executing, a module may produce token(s) along any of its output streams. Each stream accepts tokens from exactly

one producer module and forwards these tokens to one or more consumer modules. Tokens are guaranteed to reach consumer modules in the order in which they were generated.

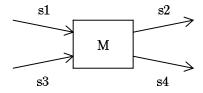

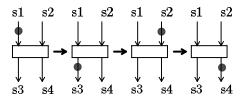

Figure 3.1 shows a high-level representation of a module. This module has two input streams, 1 and 3, and two output streams, 2 and 4.

Figure 3.1: A Box and Arrow Representation of an SM Module, M.

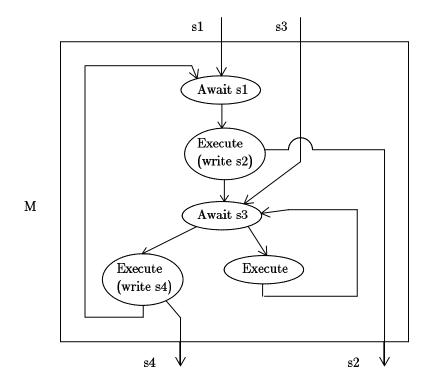

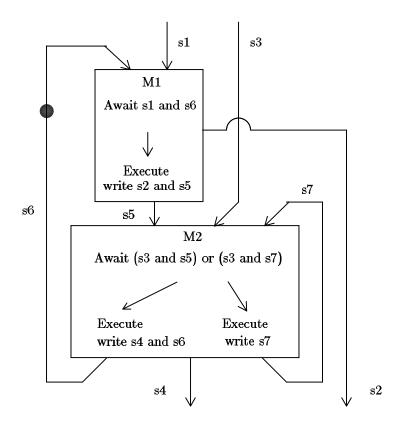

Figure 3.2: A Finite State Representation of an SM Module, M.

Figure 3.2 gives a more detailed view of this module. It shows its internal finite state behavior. In its initial state, this module awaits a token along stream s1. It consumes the arrived token along stream s1 and executes producing one token along stream s2. When done executing, the module awaits a token along stream s3. It consumes the arrived token along stream s3 and executes. During this execution, the module may produce a token along stream s4 and, eventually, return to its initial state. Alternately, the module may produce no tokens and return to its third state, awaiting a token along stream s3.

Through the rest of this thesis, we will represent program modules either with finite state diagrams such as that of Figure 3.2, or, more abstractly, with box and arrow diagrams such as that of Figure 3.1.

### Assumptions

In order to simplify our specification, we restrict the original Stream Machine model. The Stream Machine model, as described in [17], is a model of buffered communicating sequential processes (CSP). Stream reads and writes are interspersed throughout each module leading to many module states. In each state, a module is either executing with interspersed stream writes or waiting to read from one of its input streams. Figure 3.2 showed an example of possible module states.

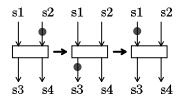

We narrow this model by constraining each program module to have only two states - one await state and one execute state. This constraint takes us from a CSP model to a coarse-grain dataflow model. Here each module waits to read from all of its input streams at once. It then executes with interspersed stream writes.

Figure 3.3 reformulates the module of Figure 3.2 into two coarse-grain dataflow modules. This conversion splits the original CSP module along each await state. Note that arrows indicating control flow in Figure 3.2 have now turned into streams. They have become streams 5, 6, and 7. These new streams enforce the original flow of control between what have now become two modules.

We retain a nondeterministic merge module present in the original CSP model as our means of introducing nondeterminism.

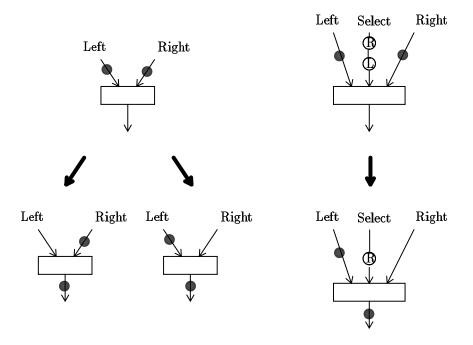

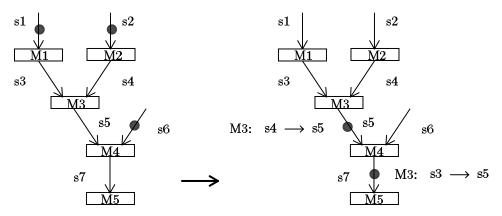

Unlike in the original CSP model, in the dataflow model, a module cannot merge tokens from several input streams onto a single output stream in a deterministic order. A standard mechanism for merging tokens in a given order is to specify the desired order along a special input stream, the *Select* stream. The merge module awaits a token along the Select stream and then, based on the token's value, awaits a token along one of its input streams. A dataflow module with a single await state cannot achieve this behavior. It cannot decide which input stream to read next based on the value read along another input stream. We complete our coarse-grain dataflow model by adding a special module which allows this behavior - the deterministic merge module.

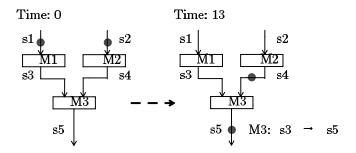

The deterministic merge module determines the order in which tokens merge onto an

Figure 3.3: A CSP Module, M, Converted into Two Dataflow Modules, M1 and M2.

output stream based on values along the Select stream. Compare the simplest merge module with the simplest deterministic merge module (Figure 3.4). Say one token arrives along each input stream sometimes during the program. In case of the merge module, the order in which the two input tokens will merge onto the output stream is not known. It depends on the relative arrival time of the two input tokens. Whichever input token arrives first will merge first. In case of the deterministic merge module the order is known regardless of tokens' arrival time. The order is determined by tokens along a third input stream, the Select stream. Tokens along this stream identify the input stream from which to merge next.

### 3.1.2 Machine

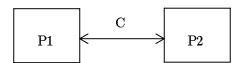

A machine consists of a set of processors and a set of channels. Both, the processors and the channels are heterogeneous. Processor performance is described by the processor's rate of instruction execution, and by the processor's contention protocol. Channel performance is described by the channel's rate of packet propagation, it's latency of propagating a packet, the size(s) of a packet, and the channel's contention protocol. Again, we represent processors and

Figure 3.4: Comparison of a Merge Module and a Deterministic Merge Module.

channels with box and arrow diagrams such as that of Figure 3.5. The machine in Figure 3.5 consists of two processors, P1 and P2, communicating via a bidirectional channel, C. Each box is a processor; each multi-directional arrow is a channel.

Figure 3.5: A box and arrow representation of a simple SM machine.

### 3.1.3 Allocation

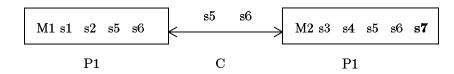

Figure 3.6: A Box and Arrow Representation of an SM Allocation.

An allocation allocates machine resources to program components. We limit our attention to static allocations. Each module is assigned to one processor. Each stream is assigned to a set of processors and channels. We represent allocations with labeled box and arrow diagrams such as that of Figure 3.6. In Figure 3.6, the modules and streams of Figure 3.3 have been allocated

onto the machine of Figure 3.5.

Since machine resources are heterogeneous, the performance of each program component depends on its allocation. For modules, the latency of each execution state depends on the processor allocation of that module. Moreover, since specialized processors optimize certain computations, module's execution latencies do not scale with processor's rate of instruction execution. Consider a vector processor, for instance; although its optimal rate of instruction execution may be ten times that of a general processor, a module of scalar code will not execute ten times faster. As a result, the number of high level instructions within a module is insufficient to predict module performance under different allocations.

For streams, the propagation latency of each token along a stream depends on the channel and processor allocations of that stream. Each channel and processor may accept packets of limited length. The latency of a token thus becomes the latency of its packets. Moreover, the time to propagate a token along a channel may vary with each channel. The time to dispatch an arrived or departing packet may vary with each processor. For simplicity's sake, we will assume in all further discussion that each token maps onto exactly one packet. This assumption simply removes a multiplication factor from our discussion.

Aside from individual components' performance, the performance of the entire program also depends on an allocation. It depends on the specific allocations to each resource and on the scheduling method along each resource. Multiple allocations to a resource may cause contention, degrading the program's performance. The resource's scheduling method can moderate this performance degradation by favoring time-critical tasks.

#### Allocation Constraints

The process of allocating a program onto a machine is limited by three types of constraints: program topology constraints, machine capacity constraints, and dedicated resource constraints. All three types of constraints must be satisfied in order for a program to execute to completion and produced desired results.

**Program Topology Constraints** These constraints insure that communicating processes will be able to communicate. To achieve this, any two modules which communicate via a stream must be allocated onto a single processor or onto two processors connected by a sequence of channels and intermediate processors.

Machine Capacity Constraints These constraints insure that the limits of each machine component are not exceeded. To achieve this, the load on each processor must not exceed the capacity of that processor. The load on each channel must not exceed the capacity of that channel.

The load on a processor can be determined by scaling all module execution latencies and all packet forwarding latencies along the processor by their frequencies. Similarly, the load on a channel can be determined by scaling all packet propagation latencies along the channel by their frequencies. Finding these frequencies is part of an implementation specification, one of the major goals of our project.

**Dedicated Resource Constraints** These constraints limit the set of available mappings. They limit the allocation of a given module to certain processors. This limitation is necessary for modules which explicitly make use of certain resources. For instance, a module which displays data on the user's screen must have access to that screen. A module which retrieves data from a sensory tool must have access to that tool.

#### Real-Time Constraints

The above three constraints guarantee that an allocated program will run to completion and produce desired results. They do not, however, address the real-time behavior of produced results. To address timing properties, we must further constrain an allocation. We place a time limit on the propagation of certain tokens from the creation of token(s) by the source module(s) to the arrival of the **corresponding** feedback token(s) to the target module(s). A data independent specification of this propagation process is the major component of a real-time constraint specification, another major goal of our project.

### 3.2 Examples

Many programs with real-time constraints are currently in use or under consideration by Schlumberger, with many more anticipated in the future. We give two realistic examples. For future reference, we further develop a sample example encompassing the characteristics of the previous two.

### 3.2.1 Tool Arm Attachment

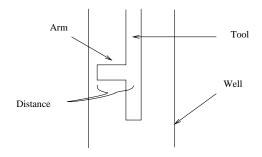

The first example is that of anchoring the arm of a tool, the SAT<sup>1</sup> tool, to the wall of a well. This example has been extensively analyzed in [18]. The tool consists of a tester with geophones for measuring seismic vibration and an arm for locking the tool into the borehole. There is a pressure sensor on the arm for detecting when the arm is pressing against the borehole well (Figure 3.7).

The movement from the center of the well towards a wall of the well is controlled by feedback from an application program outside the well. The program responds to two streams of data from the tool:

**Distance Stream** The distance stream sends up tokens describing the distance of the arm tip from the center of the well.

**Pressure Stream** The pressure stream sends up tokens describing the pressure on the tip of the arm.

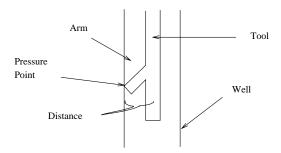

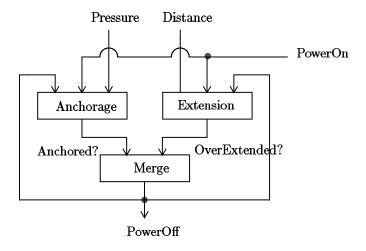

Figure 3.8 shows our implementation diagram for the SAT program. Here, the Extension module accepts a token from the Distance stream and decides whether the arm has overextended. If so, the module forwards a token to the Merge module. Another module, the Anchorage module, accepts a token from the Pressure stream and decides whether the arm has anchored to a wall. If so, the module forwards a token to the Merge module.

A Merge module awaits a value along either one of its two input streams. When the Merge module receives a token along the Anchored? stream, it turns off power to the anchored tool and informs the Extension and Anchorage modules. When the Merge module receives a token along the OverExtended? stream, it turns off power to the overextended tool and informs the Extension and Anchorage modules.

Notice that, in its await state, the Merge module awaits a token along any one of multiple streams. As a result, the Merge module introduces nondeterminism into our program. It is a nondeterministic merge module.

There are two timing constraints on this program:

Given a token on the Pressure stream, the corresponding token on the PowerOff, if any, must arrive back within a time limit sufficient to prevent damage to the arm from pressing against the wall.

<sup>&</sup>lt;sup>1</sup>Mark of Schlumberger

Figure 3.7: An Overextended Arm and an Anchored Arm.

Figure 3.8: SAT Program Diagram.

Given a token on the Distance stream, the corresponding token on the PowerOff stream,

if any, must arrive back within a time limit sufficient to prevent damage to the arm from

overextension.

### 3.2.2 SLT-L Measurement

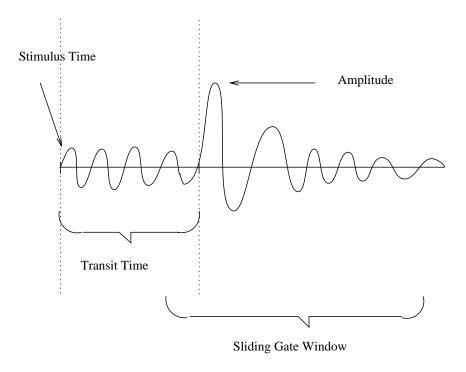

A second example of a real-time program is that of acquiring data with the SLT-L<sup>2</sup> tool. This tool, again, consists of a tester lowered into the well. The tester measures the time required for a sound wave to move a certain distance through the rock formation. The measurement is made by using a transmitter to generate a brief sound and a receiver to detect the arrival of sound as it propagates through the formation. The receiver measures the signal's amplitude within a time window that begins after the sound is generated.

Figure 3.9 shows a sound wave in response to sound impulse at stimulus time. The sound wave propagates to the receiver transit time after its generation by the transmitter. The sound wave is measured within a sliding gate time window. The sliding gate window is offset from the stimulus time by a variable time offset.

The quality of the measurement is, again, maintained by feedback from an application program outside the well. The software modules respond to two streams of data from the tool:

Maximum Response Amplitude Stream The amplitude stream sends up tokens describing the maximum amplitude of the response signal.

Signal Transit Time Stream The transit time stream sends up tokens describing the offset of the maximum amplitude response from the stimulus.

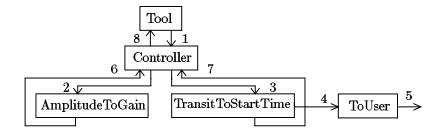

Figure 3.10 gives an implementation of the SLT-L program. The Tool module in this program is allocated onto the tool processor of Figure 2.2. It provides a periodic source of input data and is the target of feedback data. The Controller module is allocated onto the acquisition processor of Figure 2.2. It accepts a packet of data from the tool, separates it into the maximum signal amplitude and the signal transit time, and forwards these to stream 2 and stream 3 respectively. The Controller module also accepts feedback data from streams 6 and 7 and forwards these to the tool.

The remaining three modules of Figure 3.10 implement the feedback computation process. The AmplitudeToGain module adjusts receiving filter's gain based on the maximum detected

<sup>&</sup>lt;sup>2</sup>Mark of Schlumberger.

Figure 3.9: SLT-L Sound Wave.

Figure 3.10: SLT-L Program Diagram.

amplitude of the signal. The TransitToStartTime module adjust the starting time of the sliding gate window based on the transit time of the previous signal. In addition, the ToUser module processes four consecutive transit time measurements and outputs the result to the user.

Figure 3.11: Diagram of an Optimized SLT-L Program.

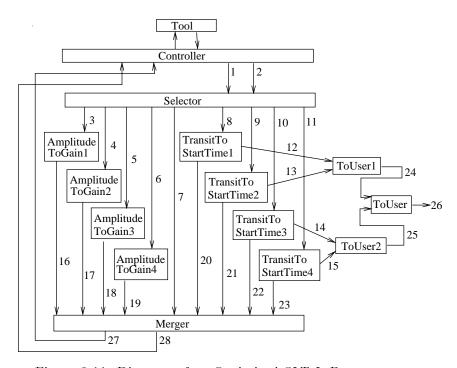

In order to relax the real time constraint on feedback propagation, we present an optimized implementation of the SLT-L program (Figure 3.11). In this implementation, The feedback data is computed in one of four ways corresponding to different transmitter/receiver pairs. The Selector module interleaves between the four different ways to compute feedback. In any one cycle, it forwards the maximum signal amplitude to the next AmplitudeToGain module. It also forwards the signal transit time to the corresponding TransitToStartTime module. In addition, all TransitToStartTime modules forward the computed start time to the ToUser modules. The ToUser modules process four consecutive measurements and forward the result to the user.

This implementation is identical to that of Barstow in [16]. The implementation overlaps the computation of four feedback values. The four-way interleaving of feedback computation

lessens the real time feedback constraint. Each amplitude and transit time measurement can be used to adjust the gain and start time of the fourth next measurement instead of the very next one. There are two resulting timing constraints on the optimized SLT-L program:

- Given a token on the maximum response amplitude stream, stream 1, the corresponding token on the filter gain stream, stream 27, must arrive back in time to adjust the gain of the collecting filter for the fourth next measurement.

- Given a token on the transit time stream, stream 2, the corresponding token on the sliding gate start time stream, stream 28, must arrive back in time to adjust the start time for the fourth next measurement.

### 3.2.3 Sample Program

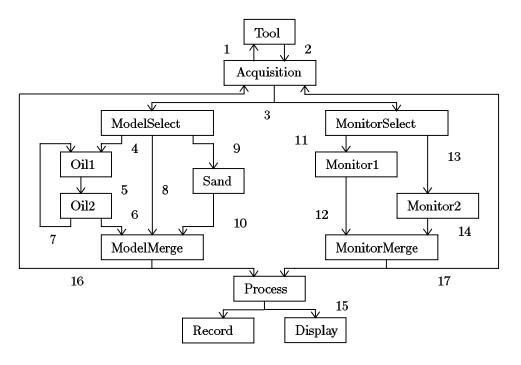

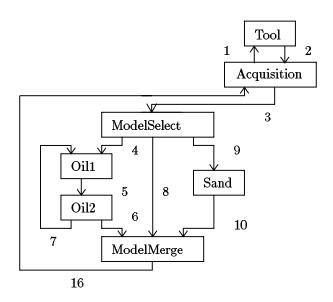

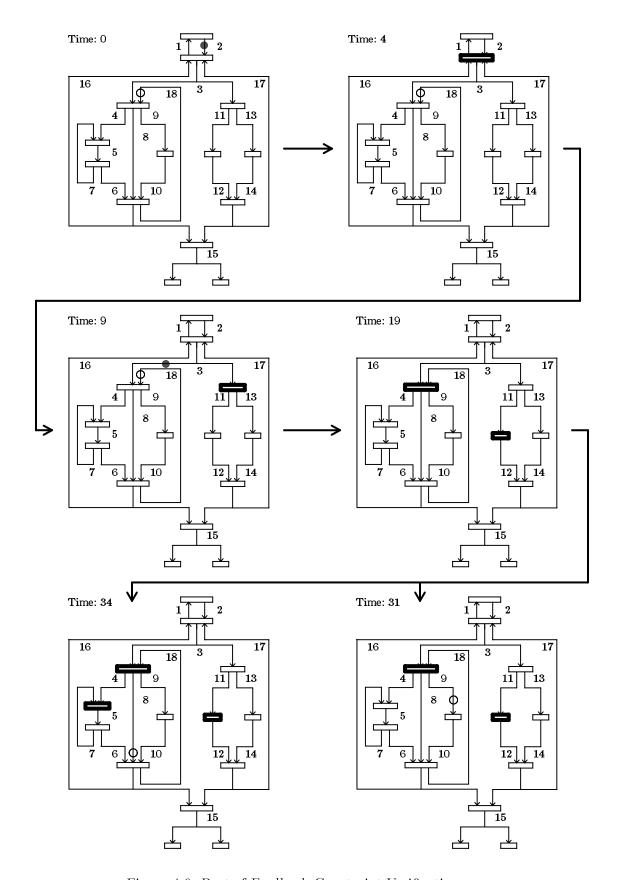

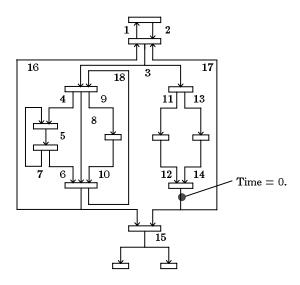

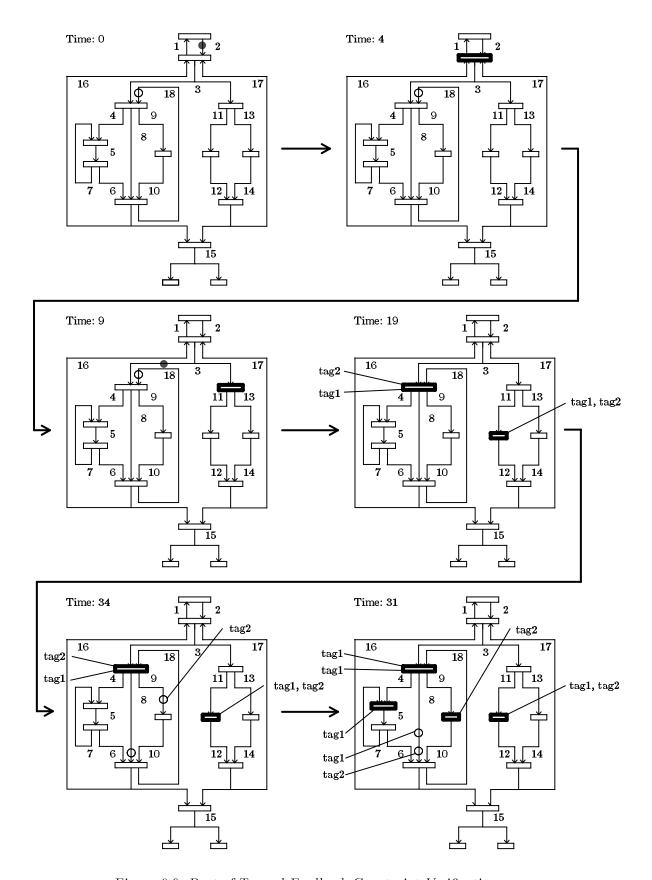

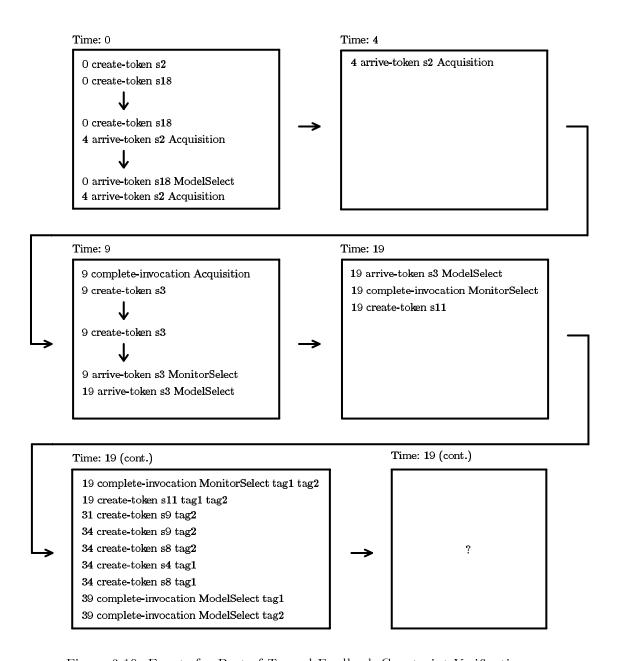

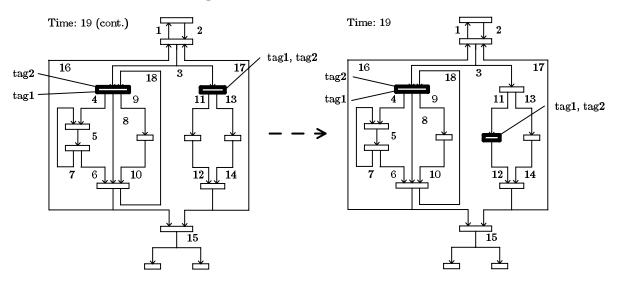

Figure 3.12: SAMPLE Program.

Finally we present an artificial example program, SAMPLE, that is characteristic of our domain and will be used throughout this thesis. Figure 3.12 shows the program diagram of SAMPLE. In this section, we give an informal description of SAMPLE's behavior. A detailed description will follow in Table 4.3.

SAMPLE acquires data with a hypothetical tool. As before, the tool is a tester lowered into a well. SAMPLE monitors the performance of the tool, initiating tool recovery if necessary. At

the same time, SAMPLE analyses acquired data. Similarly to the SLT-L program, SAMPLE adjusts tool's measurement parameters based on analyzed data. Moreover, SAMPLE forwards analyzed data for further analysis, storage, and immediate display.

More specifically, SAMPLE provides two types of feedback to the tool through the Acquisition module. A periodic feedback signal from the parameter adjusting segment of SAMPLE controls the tool behavior. An emergency feedback signal from the performance monitoring segment of SAMPLE recovers the tool in case of abnormality.

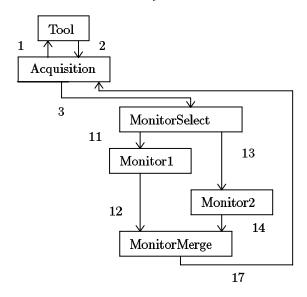

Figure 3.13: The Segment of SAMPLE Program Responsible for Performance Monitoring and Possible Tool Recovery.

Figure 3.13 shows the segment of SAMPLE program responsible for performance monitoring and possible tool recovery. Two modules, Monitor1 and Monitor2, monitor two separate aspects of the tool's performance. Each of these modules evaluates acquired data for certain abnormal conditions and notifies the MonitorMerge module of detected abnormalities. Based on input from both modules, the MonitorMerge module decides whether to generate an emergency tool recovery signal. Because of Monitor1's long latency, each Monitor module only evaluates every other data. The MonitorSelect module intermittently forwards data to the Monitor1 module and to the Monitor2 module. Correspondingly, the MonitorMerge module intermittently merges data from the Monitor1 module or from the Monitor2 module.

To illustrate the content of a module, Figure 3.14 shows a possible code routine which comprises the body of the Monitor1 module. We will return to this routine in the next chapter.

Figure 3.15 shows the segment of SAMPLE program responsible for adjustment of tool's

```

data = read(#11);

if (data <= 42)

write(#12, ''OK'');

else

i = 0;

while (data > 42) and (i < 100)

data = data + old-data[i];

i = i + 1;

write(#12, data/i);

update-old-data(data, old-data);</pre>

```

Figure 3.14: Source Code for SAMPLE's Monitor1 Module.

Figure 3.15: The Segment of SAMPLE Program Responsible for Adjustment of Tool's Measurement Parameters.

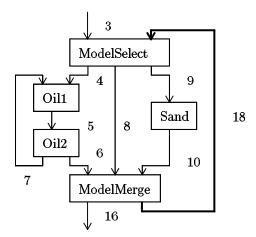

measurement parameters. The ModelSelect module evaluates incoming data. Depending on data value, the ModelSelect module forwards either one token to the oil model or two tokens to the sand model for further evaluation. Simultaneously, the ModelSelect module informs the ModelMerge module of its model choice along stream 8. Within the oil model, data flows from the Oil1 module to the Oil2 module. The Oil2 module sends evaluated data to the ModelMerge module and update information to the preceding Oil1 module. Within the sand model, two tokens invoke the Sand module. After each invocation, the Sand module forwards a token to the ModelMerge module. The ModelMerge module merges incoming tokens from the two models in the order specified by the ModelSelect module's directives.

Figure 3.15 illustrates a common use of deterministic merge modules. The ModelMerge module - a deterministic merge module, acts together with the ModelSelect module to preserve FIFO (first-in-first-out) ordering of tokens through the subgraph. The two modules preserve the FIFO ordering of multiple tokens entering two different paths, the oil model path and the sand model path. The ModelSelect module informs the ModelMerge module of the order in which it injects tokens into the subgraph. The ModelMerge module merges the outgoing tokens in the order specified by the ModelSelect module.

Stream Machine code for the ModelSelect and the ModelMerge modules (Figure 3.2.3) illustrates this behavior. The code shows that the choice of the second input stream to the ModelMerge module is dependent on the value along the first input stream, the select stream. It illustrates that, while other modules consume a static set of input tokens, a deterministic merge module selects the remainder of its input set based on the value of the token along its select stream.

In addition, both the ModelMerge module and the MonitorMerge module forward all output to the Process module for further processing. The Process module sends data to the Display module for immediate display and to the Record module for long term storage.

We constrain both types of feedback in SAMPLE - tool recovery feedback and parameter adjusting feedback. Here, we offer an informal description of these constraints. A formal specification will follow in Figures 5.5 and 5.6.

First, we constrain tool recovery feedback - the time it takes the monitoring segment of SAMPLE to generate a recovery signal. This constraint is conditional on SAMPLE's detection of abnormal conditions. Under normal tool conditions, a recovery signal will, of course, not be generated. Since each of the two performance monitoring modules receives only every other

Figure 3.16: Sample Code for the ModelSelect and ModelMerge Modules.

data, they will both detect abnormal conditions after two cycles. As a result, we constrain the time it takes to generate a recovery signal to be no more than two cycles. Say, for instance, that the tool's sampling cycle takes 150 time units. Then the time it takes two successive tokens along stream 2 to propagate through the performance monitoring segment of SAMPLE (Figure 3.13) and generate a recovery signal along stream 1 must be less than 300 time units.

Second, we constrain parameter adjusting feedback - the time it takes the parameter adjusting segment of SAMPLE to adjust tool's parameters. This time varies depending on detected formation. An oil rich formation requires different adjustments then a sandy formation. In either case, we constrain SAMPLE to generate adjustment parameters before the tool's next cycle. We assume the tool's sampling cycle to be, again, 150 time units. Then the time before one initial token along stream 2 propagates through the oil or the sand model (Figure 3.15.) and produces one token along stream 1 must be no more than 150 time units.

### 3.2.4 Program and Constraint Characteristics

We have looked at three different programs in this section: the SAT, the SLT-L, and SAMPLE. From these, we can draw several conclusions about the programs in our domain. First, all three programs contained cyclic paths. These paths were used to provide feedback. Second, all three programs received periodic data from a tool. Finally, the behavior and timing of all three programs depended heavily on input data.

Yet another characteristic of our programs was balanced flow of data. Because of limited buffer sizes, tokens could not accumulate indefinitely along any one arc. Moreover, because of our FIFO model, tokens could not be discarded upon buffer overflow. As a result, the arrival of tokens along the input arcs of a module had to be balanced and consumed steadily. The MonitorMerge module of Figure 3.12 illustrated. The module awaited one token along stream 12 for every one token along stream 14.

For each of the three programs we have discussed, we have described real-time constraints which bind the program. Real-time constraints in all three programs also shared several major characteristics. First, constraints were absolute, numeric limits, as opposed to relative, precedence limits. They were often dictated by feedback control rates. In general, constraints specified propagation delay from an initial point to a final point through many possible computation paths.

In addition, the constraints we saw ranged from hard to very soft. A signal to retrieve a malfunctioned multi-million dollar tool was an example of a hard signal. Any chance of missing the constraint limit was a clear failure. In contrast, a high rate signal to adjust tool speed was an example of a soft signal. An unlikely, random chance of missing the constraint limit was acceptable.

Also, constraints could be conditional on branching decisions within the computation. For instance, in our SAT example, the user constrained a critical path of unguaranteed existence, the path from the Pressure stream to the PowerOff stream. Given a token on the Pressure stream, a corresponding token on the PowerOff stream is conditional on the PowerOff branch of the Merge module.

### 3.2.5 Sample Machine

Having looked at several programs, we next look at a sample machine. Figure 3.17 shows the diagram of a sample machine. Tables 3.2 and 3.1 give the machine's heterogeneous channel and processor parameters. This machine is similar to the wireline acquisition machine of Figure 2.2. It, too, has

- two workstations, Workstation1 and Workstation2, (of uneven capacity)

- an uphole tool processor, the Acquisition processor, connected to one of the two workstations, and

• a downhole processor, the DownHole processor, connected to the uphole processor.

This sample machine is typical in its lack of homogeneity. It is composed of diverse processors with varying hardware (speed) and system level parameters (multitasking, interprocess communication, scheduling method ...). Channels connecting individual processors are equally diverse. Channel hardware (speed, latency) and system level parameters (broadcast, one way communication, ...) vary.

Figure 3.17: Sample Machine.

| Processor Parameters |              |           |  |

|----------------------|--------------|-----------|--|

|                      |              | Available |  |

| #                    | Name         | Capacity  |  |

| 1                    | DownHole     | 100%      |  |

| 2                    | Acquisition  | 100%      |  |

| 3                    | Workstation1 | 80%       |  |

| 4                    | Workstation2 | 100%      |  |

Table 3.1: Parameters for Sample Machine Processors.

### 3.2.6 Sample Allocation

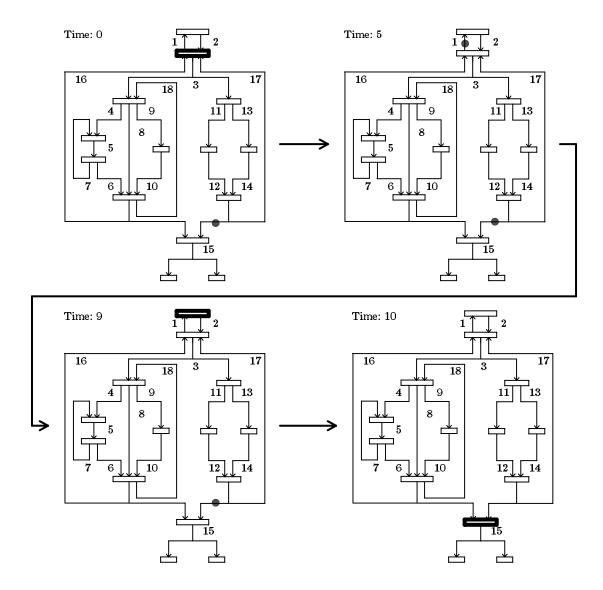

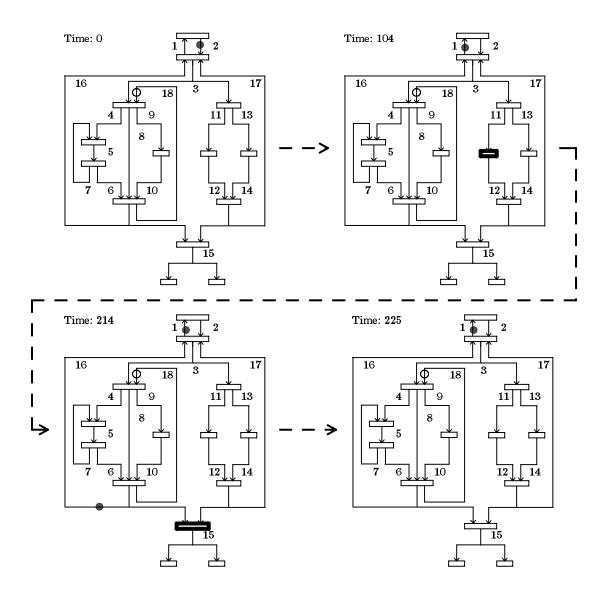

We conclude our examples with a sample allocation of our sample program onto our sample machine. Figure 3.18 illustrates. It shows the allocation of individual program modules to processors. Program's streams have been allocated so as to connect each producer module with all of its consumer modules. As we see from the figure, the number of processes and streams greatly exceeds the number of processors and channels, leading to resource contention.

Any allocation of the sample program onto the sample machine is constrained by three

|   | Channel Parameters |                  |           |  |  |  |

|---|--------------------|------------------|-----------|--|--|--|

|   |                    | Packet Propagate | Direction |  |  |  |

| # | Name               | Latency          | From To   |  |  |  |

| 1 | SignalUp           | 4                | 1-2       |  |  |  |

| 2 | SignalDown         | 4                | 2-1       |  |  |  |

| 3 | SharedMemoryUp     | 0                | 2-3       |  |  |  |

| 4 | SharedMemoryDown   | 0                | 3-2       |  |  |  |

| 5 | TruckNetwork       | 10               | 5,6-5,6   |  |  |  |

Table 3.2: Parameters for Sample Machine Channels.

dedicated resource constraints. First, the Tool module must be allocated to the Downhole processor. (Conversely, no module other than the Tool module may be allocated to the Downhole processor.) Second, the Acquisition module must be allocated to the Acquisition processor. And third, the Display module must be allocated onto the Workstation2 processor.

It is easy to see that our sample allocation satisfies dedicated resource constraints. The Tool and the Acquisition modules are the sole occupants of their dedicated resources, the Downhole and the Acquisition processors. And the Display module has been correctly allocated to Workstation2. The allocation also satisfies topology constraints. All communicating modules are able to communicate via connecting channels and processors. To satisfy machine capacity constraints, we need to determine the maximum load on each processor and channel. This information will easily follow from our verification of real-time constraints in chapter 6. In the remainder of this thesis, we will consider whether this allocation satisfies sample program's real-time constraints.

### 3.3 Summary

Before attempting a specification of timing costs and constraints, we must gain a practical understanding of our domain. This chapter attempted just that. In doing so, it hinted at several problematic areas.

First, this chapter illustrated the degree to which program's timing depends on input values. In the SAMPLE program, for example, the time to update tool's parameters depended on the formation surrounding the tool. Different calculations were called for in an oily or sandy formation. Even the existence of timing constraints was conditional on input. SAMPLE's

Figure 3.18: Sample Allocation of Program onto Machine.

recovery signal would not be generated without an abnormal status data from the tool.

In addition, allocation affected program's timing. First, the speed of program's modules and streams depended on their assigned processors and channels. Some modules, such as the Tool module in SAMPLE, would not run at all under some assignments. Thankfully, we do not attempt to allocate program's resources in this work. However, our timing verifications will have to be allocation dependent.

More seriously, allocation onto limited number of resources indicated timing costs due to contention. In our sample allocation, for instance, eight different modules competed for one processor. With several modules activated concurrently, the contention time could easily exceed the execution time of a module.

# Chapter 4

# Timing Specification

Having described our domain, we proceed to address the first goal of this project as outlined in Chapter 2 (page 15) - a timing specification of a feedback process. Our goal is to to specify enough timing information in order to verify real-time constraints.

At present, our description of a feedback process consists of program's instructions and its allocation. Take our SAMPLE program. We are given a number of modules and streams (Figure 3.12), together with the source code of each module and with SAMPLE's processor and channel mappings (Figure 3.18).

We are asked to verify whether a constraint is met. Take the simplest constraint through a single module such as SAMPLE's Monitor1 module. Figure 3.14 showed the source code for this module. Say we constrain the time from the arrival of a token along stream 11 to the creation of one token along stream 12 to be less than x time units. How do we verify this constraint?

Excluding all other costs, the simple time to execute Monitor1's instructions up to and including the generation of a token along stream 12 is not constant. The time varies with the input value read on stream 11. But our imposed constraint must be met for any input value.

Fortunately, we can derive an upper bound. We can derive the maximum possible time to execute instructions up to and including the generation of a token along stream 12. It is the time to execute Monitor1's most time demanding instruction trace on Workstation1 up to and including a "write(#12,...)" instruction. This is the instruction trace resulting from 100 iterations of Monitor1's while loop.

In order to verify the feasibility of generating one token along stream 12 within x time units of an arrived token along stream 11, we have specified the longest execution time separating the

two events. The specification amounted to listing the maximum time for the Monitor1 module to generate a token. In order to verify the feasibility of a constraint through multiple modules, we will need to specify execution times, independent of data values, along all intermediate modules and streams.

We will not tackle timing costs caused by contention in this chapter. Since other timing costs are unaffected by contention, we will postpone discussion of contention until the following chapter. Our aim, by the end of this chapter, will be to specify enough information in order to verify real-time constraints in a contention free program.

We approach our specification design with several goals.

- 1. Data Independence: Most importantly, we wish to avoid data dependent specification. To draw on data values of tokens would be to return to the code-level description of each module and to verification through repeated program execution. Instead, our goal is to statically isolate all possible time events and associated timing costs.

- 2. **Separation of Program and Machine:** We wish to preserve the Stream Machine's clean separation of program and machine description. Program behavior specification should draw purely on a program; the associated timing specification should draw on an allocated program.

- 3. **Modularity:** We wish to preserve the modularity of the Stream Machine description. Our program specification should specify behavior and associated timing at component level.

Our first goal is to describe the behavior of a feedback process. We would like to isolate all actions which take time. In case of a stream, the action is clear: it is the propagation of a token along that stream. In case of a module, time consuming actions become less obvious. At each invocation, a module may output tokens along different streams at different times. Its output may depend on its input values as well as on its periodicity. In case of the deterministic merge module, even the invocation time is conditional on which streams the selector stream selects for input. Somehow, we must abstract module's behavior to capture all possible timing costs. Having described all actions which take time, we will then move on to assign timing costs to each action and, finally, to simulate timing and behavior of the entire program.

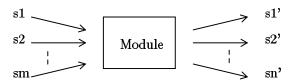

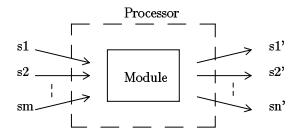

## 4.1 Abstracting Behavior of a Module

In each module's invocation, several actions characterize the advancement of time. Take the general module of Figure 4.1. The module is invoked at the moment it accumulates all awaited tokens along streams  $s_1$  though  $s_m$ . It consumes its input tokens and executes for some time. At certain times past its invocation, the module outputs tokens along streams  $s'_1$  through  $s'_n$ .

Figure 4.1: Sample Module.

#### Simple Modules

We start our exploration of behavior with the simplest possible module. This module awaits one token along one input stream and executes outputting one token along one output stream. SAMPLE's Monitor1 module is an example. Monitor1 consumes one token along stream 11 and then executes outputting one token along stream 12. Referring to the general module of Figure 4.1, our description simply lists the one input and the one output stream, indicating execution by an arrow (" $\rightarrow$ "):

$$s_1 \rightarrow s_1'. \tag{4.1}$$

In case of the Monitor1 module:

$$s_{11} \rightarrow s_{12}$$

.

A simple extension of our description allows for one token along each of multiple input streams and each of multiple output streams. An example of this timing behavior is SAMPLE's Dil2 module. Dil2 consumes one token along stream 5 and then executes outputting one token along stream 6 and one token along stream 7. Our extended description simply list all input streams and all output streams, again indicating execution by an arrow ("\rightarrow"):

$$s_1 \wedge s_2 \wedge \dots s_m \rightarrow s_1' \wedge s_2' \wedge \dots s_n'.$$

(4.2)

In case of the Oil2 module:

$$s_5 \rightarrow s_6 \wedge s_7$$

.

Finally, a module may await multiple tokens along any one input stream and produce multiple tokens along any one output stream. An example is SAMPLE's Sand module which consumes two tokens along stream 9. In our description, we include multiple tokens along a stream by adding an optional coefficient, c, in front of that stream:

$$c_1 s_1 \wedge c_2 s_2 \wedge \dots c_m s_m \quad \to \quad c_1' s_1' \wedge c_2' s_2' \wedge \dots c_n' s_n'. \tag{4.3}$$

In case of the Sand module:

$$2s_9 \rightarrow s_{10}$$

.

#### Selector Modules

The first difficulty arises with data dependent modules. These modules behave differently depending on values of input tokens. They *select* their behavior based on values. Take the MonitorMerge module which consumes one token along stream 12 and another one along stream 14. Depending on the values of these tokens, MonitorMerge does or does not generate a token along stream 17. As our ultimate goal is a data independent verification, we cannot incorporate token's values into our description. Instead, we describe all possible behaviors, making no choice among them:

$$c_{1}s_{1} \wedge c_{2}s_{2} \wedge \dots c_{m}s_{m} \rightarrow c'_{1,1}s'_{1} \wedge c'_{1,2}s'_{2} \wedge \dots c'_{1,n}s'_{n}$$

$$\rightarrow c'_{2,1}s'_{1} \wedge c'_{2,2}s'_{2} \wedge \dots c'_{2,n}s'_{n}$$

$$\rightarrow \dots$$

$$(4.4)$$

In case of the MonitorMerge module:

$$s_{12} \land s_{14} \rightarrow s_{17}$$

$\rightarrow .$

We will refer to the description of Equation 4.4 as a behavior statement. A behavior statement states how a module will behave for a given input set of tokens.

#### Merge Modules

Yet another variation on Equation 4.2 captures the behavior of merge modules. In its simplest form, merge modules merge the values along two input streams onto a single output stream. SAMPLE's Process module is an example. Process awaits one token along stream 16 or one token along stream 17. Whenever a token along either stream arrives, Process consumes the token and executes, generating one token along stream 15. The behavior of the Process module can be described by two statements:

$$\begin{array}{ccc} s_{16} & \rightarrow & s_{15} \\ \\ s_{17} & \rightarrow & s_{15}. \end{array}$$

In general, the behavior of a merge module can be described by multiple statements which share the same output sets:

$$c_{1,1}s_{1} \wedge c_{1,2}s_{2} \wedge \dots c_{1,m}s_{m} \rightarrow c'_{1,1}s'_{1} \wedge c'_{1,2}s'_{2} \wedge \dots c'_{1,n}s'_{n}$$

$$\rightarrow c'_{2,1}s'_{1} \wedge c'_{2,2}s'_{2} \wedge \dots c'_{2,n}s'_{n}$$

$$\rightarrow \dots$$

$$c_{2,1}s_{1} \wedge c_{2,2}s_{2} \wedge \dots c_{2,m}s_{m} \rightarrow c'_{1,1}s'_{1} \wedge c'_{1,2}s'_{2} \wedge \dots c'_{1,n}s'_{n}$$

$$\rightarrow c'_{2,1}s'_{1} \wedge c'_{2,2}s'_{2} \wedge \dots c'_{2,n}s'_{n}$$

$$\rightarrow \dots$$

$$\dots \rightarrow \dots$$

$$(4.5)$$

#### Deterministic Merge Modules

We next consider several ways to model the behavior of a deterministic merge module. We have already seen the deterministic merge module's role in preserving FIFO ordering in Section 3.2.3. In the model subgraph in Figure 3.15, the selector module ModelSelect together with the deterministic merge module ModelMerge maintained the FIFO ordering of tokens entering and exiting the subgraph. To correctly model the behavior of the sample program, we too must preserve this ordering in our specification of modules' behavior.

We start our specification of the deterministic merge module ModelMerge from our specification of a simple merge module (Equation 4.5):

$$s_6 \wedge s_8 \rightarrow s_{16}$$

$$s_{10} \wedge s_8 \rightarrow s_{16}$$

.

Here, an input token on stream 8 matches either an input token on stream 6 or an input token on stream 10, depending on which of the two arrives first. The select/merge pair's FIFO synchronization is simply ignored.

**Speculative** A slight improvement lets us specify every possible synchronization along our select/merge pair. Since we do not know which set of input tokens a selector token will name, we specify all possibilities. We separate different possibilities with a "|":

$$statement_1$$

|  $statement_2$

| ... (4.6)

Within this notation, specification of the ModelMerge module becomes:

$$s_6 \land s_8 \rightarrow s_{16}$$

$$s_{10} \land s_8 \rightarrow s_{16}$$

The arrival of one token along stream 6 and one token along stream 8 does or does not fire an invocation of the module depending on which of the possible statements we consider.

An obvious disadvantage of this approach is that the behavior of all but one statement is unrealistic. Take the case where the ModelSelect module has generated one token each along streams 4 and 8. Choosing ModelMerge module's first statement,  $s_6 \land s_8 \rightarrow s_{16}$ , correctly portrays the module's behavior and preserves the select/merge pair's FIFO synchronization. However, choosing ModelMerge module's second statement,  $s_{10} \land s_8 \rightarrow s_{16}$  leads to infeasible behavior. The choice leaves two unconsumed tokens, one along stream 6 and one along stream 8, forever.

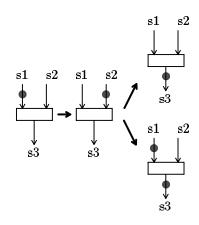

**Acknowledged** We can assert FIFO ordering through an explicit addition of acknowledgment streams to select/merge pairs. Figure 4.2 illustrates on our oil model example. With an added acknowledgment stream, stream 18, the specification of ModelSelect's actions becomes:

$$s_3 \land s_{18} \rightarrow s_4 \land s_8$$

$$\rightarrow 2s_9 \land s_8$$

Figure 4.2: The Model Segment of SAMPLE with an Explicit Acknowledgment Stream.

Specification of ModelMerge's actions becomes:

$$s_6 \land s_8 \rightarrow s_{16} \land s_{18}$$

$s_{10} \land s_8 \rightarrow s_{16} \land s_{18}$

This solution is not optimal. It limits parallelism and lowers execution speed by sequentializing entry into each select/merge pair.

However, in feedback control programs, such as SLT-L (Section 3.2.2), select/merge pairs are commonly used for generality rather than synchronization. In fact, this is the case in our sample program. Here the tool cycle time exceeds the propagation time along either branch of the model segment<sup>1</sup>. As a result, FIFO ordering through this select/merge pair is guaranteed and no acknowledgment is necessary. Because within our application domain explicit FIFO enforcement is often unnecessary, we leave implementation of the alternative tagged approach below for further work.

Tagged A more satisfying approach is the explicit treatment of select/merge pairs. Here we capture the alignment of the select module's and the deterministic merge module's actions. On each invocation of the select module, we tag the generated selector stream token with its output set selection. The corresponding merge module checks the tag of its input token along the selector stream in order to select the remainder of its input set.

We describe the select module as:

$$c_1s_1 \wedge c_2s_2 \wedge \dots c_ms_m \rightarrow s'_1 \wedge c'_{1,2}s'_2 \wedge \dots c'_{1,n}s'_n, \ s'_1 = \operatorname{Tag}_1$$

<sup>&</sup>lt;sup>1</sup>It must in order for feedback to affect the next measurement - a constraint imposed in section 3.2.3

$$\rightarrow s_1' \wedge c_{2,2}' s_2' \wedge \dots c_{2,n}' s_n', \ s_1' = \operatorname{Tag}_2$$

$$\rightarrow \dots \tag{4.7}$$

Here, tokens along selector stream,  $s'_1$ , are assigned a tag designating the select module's choice. Correspondingly, the merge module selects its input set according to the supplied tag:

If

$$s_1 == \operatorname{Tag}_1, \quad s_1 \wedge c_2 s_2 \wedge \dots c_m s_m \quad \rightarrow \quad c'_{1,1} s'_1 \wedge c'_{1,2} s'_2 \wedge \dots c'_{1,n} s'_n$$

$$\qquad \qquad \rightarrow \qquad c'_{2,1} s'_1 \wedge c'_{2,2} s'_2 \wedge \dots c'_{2,n} s'_n$$

$$\qquad \qquad \rightarrow \qquad \dots$$

If  $s_1 == \operatorname{Tag}_2, \quad \dots \quad \rightarrow \quad \dots$  (4.8)

Like the speculative approach, this solution does not modify the original program. In addition, it is always correct, preserving the intended FIFO synchronization. Table 4.2 shows the tagged behavior specification of our ModelSelect and ModelMerge pair.

However, the introduction of tags into our description is worrisome. At first glance, it seems that we have violated our main goal - a data independent specification. Tokens along the selector stream clearly carry values from the select module to the merge module. The timing behavior of the merge module depends on the tag value along its selector stream. Are we back to verification through repeated execution for each possible input value? Not quite. Unlike data values, tags do not directly affect evaluation, instead, they align. They align actions of the merge module with those of the select module. Through a finite number of choices, tags describe all valid alignments of those two modules' actions.

**Deterministic Merge Modules Summary** We have seen two satisfactory ways to express the behavior of deterministic merge modules - through the addition of acknowledgment streams and through tagging. Tables 4.1 and 4.2 show SAMPLE modules' behavior specifications under the two schemes.

#### State Dependent Modules

In our assumption, we have restricted the Stream Machine modules to two states; each module is either reading its input streams or executing, irrespective of the module's history. This restriction simplified our specification at the cost of lowered performance and expressiveness.

Execution that might have preceded otherwise is postponed until all input streams have been read. And, more importantly, information regarding periodic behavior of a module is lost.

Periodicity played a role in the timing of two of our three illustrative programs. Successive cycles of the SAMPLE program invoked one of two monitoring calculations. In the SLT-L program, successive cycles interleaved among four computations adjusting the tool's parameters.

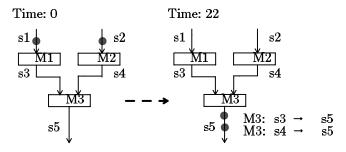

We illustrate consequences of neglected periodic behavior on SAMPLE's monitor subprogram (Figure 3.13). At this point our best approximation of the MonitorSelect module's behavior is:

$$s_3 \rightarrow s_{11}$$

$$\rightarrow s_{13}.$$

This specification states that on each invocation, the MonitorSelect module generates either one token along stream 11 or one token along stream 13. The specification does not capture the periodic interleaving of output to streams 11 and 13.

As a result, the subsequent input set specification of module MonitorMerge,  $s_{12} \wedge s_{14}$ , is unrealistic. The specification of the MonitorSelect module does not guarantee a balanced arrival of tokens at streams 12 and 14. The MonitorMerge module may produce no output and accumulate an overflow of tokens along one of its two input streams. Clearly, this is not the behavior we wished to specify.

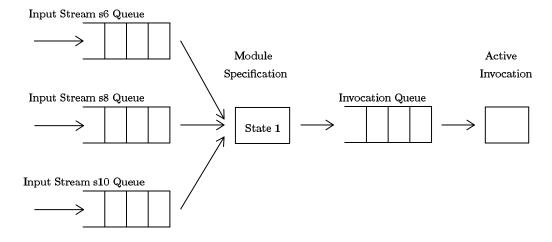

To recapture the periodic behavior of modules, we can relax the "statelessness" assumption and allow multiple module states. By convention, we use state 1 as the initial state:

state x:

$$statement_x$$

next state: state y.  $(4.9)$

For instance, the timing actions of the MonitorSelect module become:

state 1:

$$s_3 \rightarrow s_{11}$$

next state: state 2

state 2:  $s_3 \rightarrow s_{13}$

next state: state 1

It is interesting to note that we have not reverted to a CSP model. Our deterministic finite automata of module specifications allow for periodic states. They do not allow for data dependent states. By attaching next state to individual output sets, rather than sets of statements, we could easily reclaim a CSP model. However, none of the sample programs of Chapter 3 indicate a need for this additional source of nondeterminism - a nondeterministic finite automaton.

| SAMPLE Modules' Time Critical Actions |       |                                                    |            |  |  |  |

|---------------------------------------|-------|----------------------------------------------------|------------|--|--|--|

| Module                                | State | Statement                                          | Next State |  |  |  |

| Tool                                  | -     | $s_1 \rightarrow$                                  | -          |  |  |  |

| Acquisition                           |       | $s_2 \rightarrow s_3$                              |            |  |  |  |

|                                       | -     | $s_{16} \rightarrow s_1$                           | -          |  |  |  |

|                                       |       | $s_{17} \rightarrow s_1$                           |            |  |  |  |

| ModelSelect                           | -     | $s_3 \land s_{18} \rightarrow s_4 \land s_8$       | -          |  |  |  |

|                                       |       | $\rightarrow 2s_9 \land s_8$                       |            |  |  |  |

| Oil1                                  | =     | $s_4 \rightarrow s_5$                              | =          |  |  |  |

|                                       |       | $s_7 \rightarrow$                                  |            |  |  |  |

| Oil2                                  | -     | $s_5 \rightarrow s_6 \land s_7$                    | -          |  |  |  |

| Sand                                  | -     | $2s_9 \rightarrow s_{10}$                          | -          |  |  |  |

| ModelMerge                            | ı     | $s_6 \land s_8 \rightarrow s_{16} \land s_{18}$    | -          |  |  |  |

|                                       |       | $s_{10} \land s_8 \rightarrow s_{16} \land s_{18}$ |            |  |  |  |

| MonitorSelect                         | 1     | $s_3 \rightarrow s_{11}$                           | 2          |  |  |  |

|                                       | 2     | $s_3 \rightarrow s_{13}$                           | 1          |  |  |  |

| Monitor1                              | İ     | $s_{11} \rightarrow s_{12}$                        | -          |  |  |  |

| Monitor2                              | -     | $s_{13} \rightarrow s_{14}$                        | -          |  |  |  |

| MonitorMerge                          | -     | $s_{12} \land s_{14} \rightarrow s_{17}$           | -          |  |  |  |

|                                       |       | $\rightarrow$                                      |            |  |  |  |

| Process                               | -     | $s_{16} \rightarrow s_{15}$                        | -          |  |  |  |

|                                       |       | $s_{17} \rightarrow s_{15}$                        |            |  |  |  |

| Record                                | -     | $s_{15} \rightarrow$                               | -          |  |  |  |

| Display                               | -     | $s_{15} \rightarrow$                               | -          |  |  |  |

Table 4.1: Specification of SAMPLE Modules' Behavior Using Acknowledgment Streams for Deterministic Merge Modules.

#### Generalization of Merge Modules

Finally, we can expand the specification of merge modules to allow different behavior for different input sets:

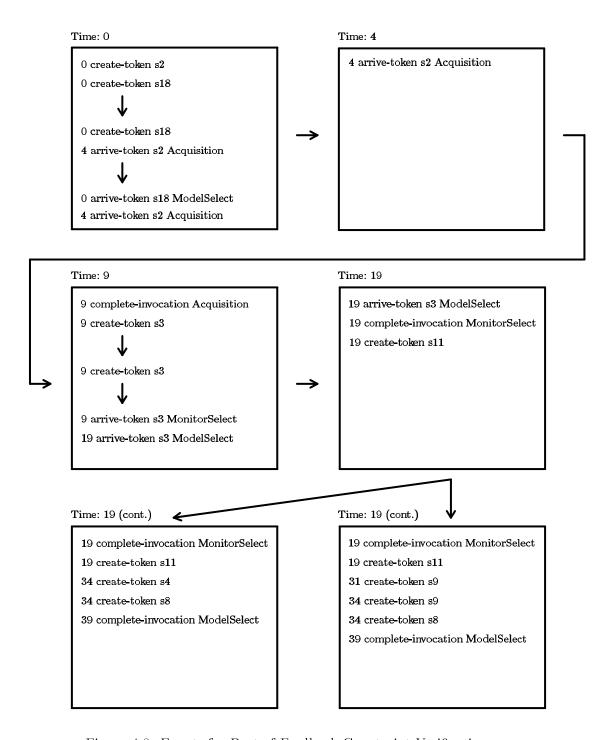

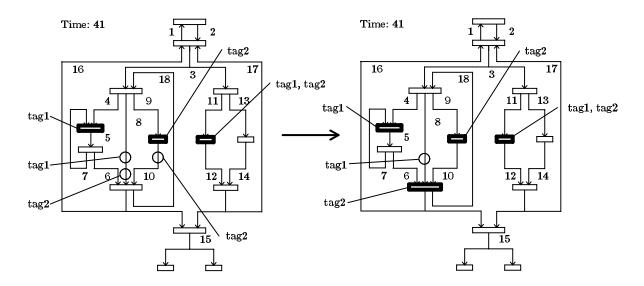

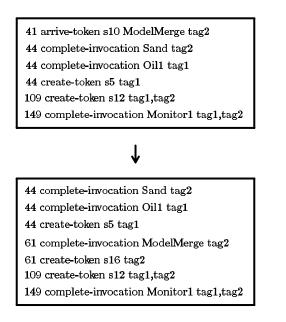

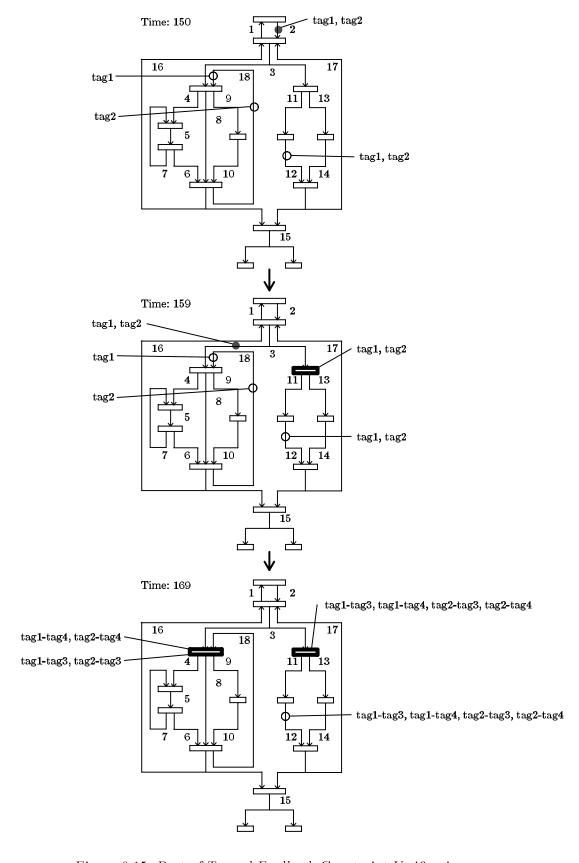

$$c_{1,1}s_{1} \wedge c_{1,2}s_{2} \wedge \dots c_{1,m}s_{m} \rightarrow c'_{1,1,1}s'_{1} \wedge c'_{1,1,2}s'_{2} \wedge \dots c'_{1,1,n}s'_{n}$$