# Aurora at MIT

Final Report on MIT's Participation in the Aurora Gigabit Testbed\*

David D. Clark, Henry Houh, and David L. Tennenhouse, editors<sup>†</sup>

Laboratory for Computer Science Massachusetts Institute of Technology

The Aurora Gigabit Testbed linked researchers at MIT, the University of Pennsylvania, the University of Arizona, Bellcore and IBM. The Aurora partnership included Nynex, Bell Atlantic and MCI, who investigated issues related to the gigabit transmission facilities which they provided to the research teams.

Aurora activities at MIT were undertaken by two groups: the Telemedia, Networks and Systems (TNS) Group and the Advanced Network Architecture (ANA) Group. Section 1 of this report describes the work performed by the MIT/TNS group, under the direction of David Tennenhouse; Section 2 describes the work of the MIT/ANA Group, under the direction of David Clark; the Appendixes list the publications and students supported by the project.

<sup>\*</sup>This research was supported by the Corporation for National Research Initiatives.

<sup>&</sup>lt;sup>†</sup>The authors can be reached at: MIT Lab for Computer Science, 545 Technology Square, Cambridge, MA 02139; Tel: (617) 253-6005; Email: {ddc,hhh,dlt}@lcs.mit.edu

# Section 1: TNS Group Activities

### 1 Introduction

The TNS group's testbed activities included: the development of the VuNet, an ATM-framed local distribution system; research on the design of host/network adapters; and the demonstration of network-based multimedia applications.

Some of our achievements in the testbed program include: the deployment of the VuNet infrastructure (encompassing 8 switches, 11 network-based video appliances, 11 host workstations and a suite of multimedia applications); demonstration of seamless DAN/LAN/WAN internetworking; the development of a number of different host/network adapters; and the investigation of ATM end-working and signaling issues.

Along the way we learned a number of lessons concerning: the distinction between cell switching and ATM layer functions; the role of memory in the design of host interfaces and end-working software; the striping of ATM transmission facilities; and the traffic implications of computation-intensive multimedia applications.

In the following subsections we describe the research objectives, approach, experimental results and lessons learned by members of the TNS group.

### 2 Research Objectives

The TNS group's activities focused on the following subset of Aurora's research objectives [5]:

- The design and evaluation of ATM-framed local distributions systems

- The design, development and evaluation of alternative host interfaces

- The integration of gigabit switching, transmission and multiplexing systems

- The demonstration and evaluation of new paradigms for distributed applications

In accordance with MIT's portion of the Aurora Statement of Work, we also worked with other interested groups to:

• Develop specifications for the ATM layer and to investigate ATM adaptation

The following paragraphs describe the relationship between these goals and the approach taken in our research.

#### ATM-framed local distribution

Our work on local distribution focussed on the VuNet, an ATM-based Desk Area Network. The **VuNet**, which was developed as part of the testbed, was deployed in individual offices and laboratories at MIT and a VuNet node was established at U. Penn. To facilitate VuNet / Sunshine integration, a VuNet node was located at Bellcore for a brief period.

#### Host Interfaces

Within the testbed as a whole, several areas of host interface research were investigated by the Aurora partners and taken together these provide a fairly good map of the *design space*. The MIT/TNS group investigated a portion of this design space, with particular emphasis on the adapter's point of

attachment, cost, and use of memory. We developed programmed I/O, DMA-based, and coprocessorbased adapters and collaborated with Bellcore on the design of the Osiris host interface. We also developed the Vidboard, an ATM-based camera that is directly attached to the VuNet.

#### Gigabit switching, transmission and multiplexing

The MIT/TNS group investigated a number of internetworking and systems integration issues and demonstrated the seamless ATM-based internetworking of: the VuNet DAN, the AN2 LAN, and the Sunshine WAN. We also collaborated with Bellcore on the design of an ATM-based cell processor for use in the port controllers of the Sunshine switch.

#### Distributed Applications

**The VuSystem**, a separately funded project, is a programming system for the software-based processing of audio and video data. Within the context of Aurora, we demonstrated the operation of VuSystem applications over the VuNet / Aurora infrastructures.

#### ATM and Adaptation Layer Issues

MIT researchers helped initiate the development of SEAL/AAL5, which has been adopted for a wide range of packet-oriented services (frame relay, IP, etc.). During the course of our research we investigated a number of issues related to **ATM end-working** and an **application-oriented approach to signaling**.

### 3 Approach

The following sections provide details concerning the approach, design and implementation of key technologies developed within the project.

### 3.1 Local Distribution Systems - the VuNet

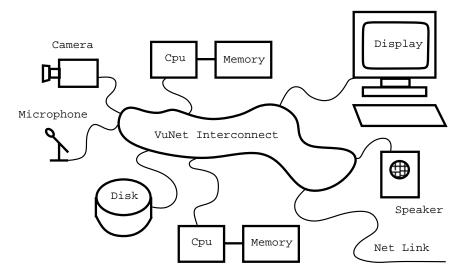

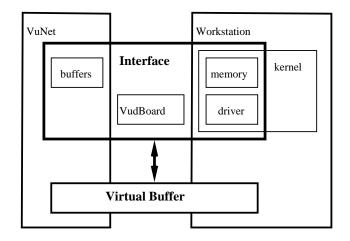

A Desk-Area Network (DAN), as illustrated in Figure 1, is a small local system in which peripherals, such as multimedia devices, are taken out of the workstation and connected directly to the network. Workstations access these devices over the network and coordinate the movement of information streams among the different parts of the system. Aurora's DAN implementation is known as the **VuNet** and the Vidboard, described in section 3.3, is an example of a DAN-enabled peripheral.

The VuNet is a gigabit-per-second desk/local-area ATM network which interconnects general-purpose workstations, network-based multimedia devices and bridges to other networks. The DAN Approach replaces the workstation's haphazard collection of peripheral interfaces and connectors (e.g. SCSI, VGA, EISA) with a generic ATM-based connector that supports a heterogeneous range of peripherals including cameras, displays, disks, etc. We envisage a vigorous market for such peripherals which would be able to operate with any manufacturer's platform. VuNet peripherals are highly programmable and are connected directly to the VuNet, allowing them to be shared among all hosts, including hosts not local to the peripheral's desk area.

With small networks, it is possible to rethink the ways certain network design issues are addressed. Many of these issues also arise in the design of Local-Area Networks (LANs), Metropolitan-Area Networks (MANs), and Wide-Area Networks (WANs), however their characterization within the DAN environment is different than in the LAN or WAN. For example, small desk area networks need not be designed for high utilization as traffic aggregation is not a principal design objective.

Figure 1: A Desk Area Network where devices are taken out of the workstation and attached directly to the network. The workstations coordinate the flow of data from various devices on the network to other devices.

Larger networks can provide efficient communications because large numbers of hosts share the communications medium. In a small working area environment, there is a smaller number of hosts, making it more difficult to depend on statistics in sharing the aggregate bandwidth necessary for efficient operation. The fact that bandwidth is less expensive over the short distances involved suggests a VuNet design regime that leverages inexpensive, lightly utilized bandwidth.

Similarly, shared wide area components, such as the line card serving a heavily multiplexed link, can be relatively expensive. However, in a small desk area network, careful attention must be paid to the cost per end node. Hence it becomes attractive to trade off functionality for cost in the non-multiplexed components such as the end system switch ports and interfaces. Simple, inexpensive interfaces become an important design objective.

Within Aurora, both regions were explored. Bellcore's Sunshine effort explored the wide area, and the VuNet explored the desk area.

A key goal motivating the design of the VuNet hardware was simplicity. Sophisticated network functions (e.g. multi-cast, back-pressure, support for ATM adaptation layers, service classes) were pushed to the edge of the network and became the responsibility of the clients. We believe that a local environment such as the VuNet can be effectively served by a simple switch fabric having a limited number of access ports and an internal speed that is greater than that of the clients.

The remainder of this section describes the VuNet design and the hardware that was built. The considerations that drove the design were:

- Software intensive philosophy: Wherever possible, the VuNet design favors software-based solutions that reduce the complexity of network hardware by moving functionality into the software of the end nodes. An important benefit of this software-intensive approach is the ability to port the system to higher-performance workstations easily. Over the span of the Aurora project, four different hardware platforms were used with two varieties of host interfaces, for a factor of ten difference in performance.

- **Bursty traffic:** Since host processes running within an operating system generate network traffic during their time slices, their generation of data is inherently bursty. Similarly, they consume data in bursts that are not synchronized to the incoming traffic. Accordingly, sources and sinks of video and audio information must be able to handle data in bursts and the DAN and

its hosts and peripherals must support bursty traffic.

- **Asynchronous client interface:** Clients should not be slaved to the network clock. Instead, the network ports should support various input and output rates. ATM, with its small cell size and variable cell rates, can accommodate this requirement.

- Simple client interface: Fast and slow clients alike should see the network as a place to easily write and read ATM cells. The VuNet uses a modified cell format in which the cell length is increased from 53 to 56 bytes in order to make cells quadword-aligned.

- **Data transparency:** All classes of traffic (video, audio, file transfer, etc.) are treated in a similar manner until they reach the target application, and multiple video streams are easily supported since hardware limitations are not placed on their number.

- **Interoperability and modularity:** Multimedia peripherals such as a video capture board were designed to interface directly to the VuNet rather than to a workstation I/O bus. This allows the peripherals to be shared among all the hosts connected to the VuNet. It also avoids redesigning a peripheral for each vendor's computer platform.

These principles were applied to all aspects of the design of the local ATM distribution system.

#### 3.1.1 The VuNet Cell Switch

In the development of the VuNet we separated the switching of cells (between switch ports) from ATM level functions such as VCI mapping. We started with a simple model of the "ideal" exchange of cells between two hosts that are directly connected to each other over a communications channel of zero length and infinite speed. An important observation is that even this channel requires a memory-based buffer or FIFO of some sort, if only to decouple the clock rates, and ultimately the application burst rates, of the communicating processes.

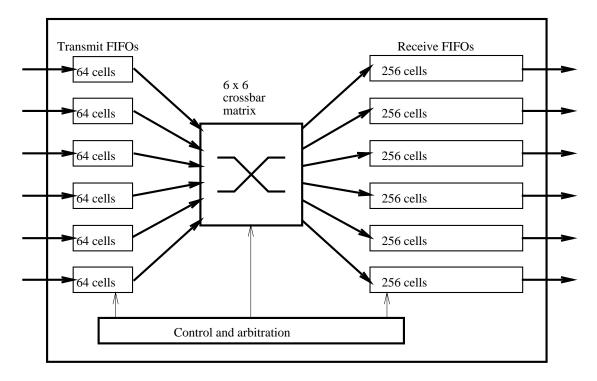

To satisfy our "ideal" model of cell transfer, the switch fabric, which consisted of bidirectional ports with first-in first-out (FIFO) buffers which fed a crossbar matrix, allowed each host to accept cells at a rate that exceeds the aggregate rate at which cells are presented by all of the attached hosts. Current versions of the VuNet switch have either four or six ports and we clock the crossbar matrix at a rate of 700 Mbps per port. Given the small number of ports and the rate at which our present hosts are able to generate traffic, this provides a close approximation to the model.

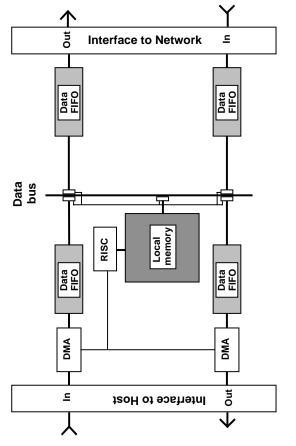

The switch provides a straightforward interface that simplifies the design of client hardware. Since the timing of the client side of the port FIFOs is decoupled from the internal timing of the switch matrix, there is no need for clients to synchronize their operation with the internal switch clock, as is often the case with traditional switch designs. Furthermore, both the transmit and receive blocks can be operated concurrently. The FIFOs also serve to buffer cell bursts, an important factor in our simplified network. Finally, the data bus width to the port is selectable, either 32 or 64 bits, allowing a simple mapping to workstation and processor buses. All these factors make it easy to design devices which connect directly to the switch, satisfying the "simple client interface" objective.

The VuNet was designed around a non-standard 56-byte ATM cell, as the switches had 64-bit interfaces. While this presented new issues when bridging to other networks (as discussed in Section 3.4), it greatly simplified the design and complexity of switch and the network-based devices.

#### 3.1.2 Cell Relaying

The preceding section described cell switching among devices that are attached to a single switch. Inter-switch communication can be modeled by a device (or set of devices) that is connected to ports on two different switches. This cell relaying host performs two functions: it copies cells between

Figure 2: The six port VuNet switch.

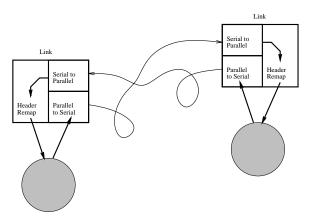

Figure 3: The links in VuNet perform header remapping and next output port lookup for hop-by-hop cell routing.

the switches and it re-maps VCIs. The relay serves as an intermediary with knowledge of the VCI address spaces associated with the switch ports.

The VuNet link implements a minimal set of relaying functions, cell copying and VCI mapping. To support the inter-office separation of switches, it is constructed in two parts that are inter-connected by high speed channels as illustrated in Figure 3. The channels use single mode optics and serial coding based on the HP G-Link chipset and the links presently operate at 500 Mbps. Link processing is table driven, and the management of the link tables is left to the communicating end systems. This will be discussed in further detail in Section 3.5.

The link tables are large enough to remap the entire 64K (16-bit) VCI space to 64K new VCIs and four bits of switch port information. All other bits in the ATM header remain untouched.

The VuNet does not support the Header Error Check (HEC) function on a hop-by-hop basis as we do not believe that HEC is an essential function for desk area or even local area operation. For compatibility purposes a cell source can pre-compute the HEC that is expected by the destination.

Management of the link tables is performed using control cells sent with a reserved ATM VCI. Cells received by the link on these special VCIs cause the link to re-write entries in its header lookup table. They can also cause the link to emit a cell containing table entries, so link tables can be read back.

# 3.2 Host Interfaces

Many researchers believe that host interface performance can be improved through the off-loading of network protocol processing, i.e., moving functionality from the host to the interface. Within Aurora, several different types of host interfaces were developed to explore this hypothesis. For the VuNet, several types of interfaces were designed. MIT also participated with Bellcore in the design of their Osiris host interface.

Using these various interfaces, different methods of segmentation and reassembly were investigated; this spanned the gamut from specialized on-board host interface hardware to extremely simple host interface hardware combined with software segmentation and reassembly. Different methods of host-interface synchronization were used including interrupt driven handling and device polling. The various interfaces also explored different network points of attachment.

The simplest VuNet interface was a programmed I/O interface in which the processor was responsible for writing data to the interface. Another version supported DMA with variable burst sizes from one ATM cell size and up. In both cases, the segmentation and reassembly was performed by the host processor. An ATM-based coprocessor interface was also designed and fabricated. This interface, which resembled a floating point unit, connected directly to the coprocessor port of the CPU.

Finally, MIT participated in the design of the Bellcore Osiris interface, a custom segmentation/reassembly hardware engine attached via the processor I/O bus. In the Osiris design large packets are transferred to the interface, which segments the packets before transmission into the ATM network.

The following subsections describe the design of these host interfaces.

### 3.2.1 VuNet Programmed I/O Interfaces

All of the VuNet host interfaces rely on the CPU to perform the ATM segmentation and reassembly (SAR) tasks. Although this approach was computationally intensive, it provided a flexible environment for the study of many host interface issues. Other Aurora partners, working in parallel, investigated other aspects of the design space, especially hardware-based SAR.

The first of VuNet interfaces designed was the VuNet Programmed I/O interface, known as the VupBoard. This host interface served only as a memory-mapped extension of the read port of the switch output FIFOs. Cells were read into memory through 14 reads of the memory address corresponding to the FIFO. Other addresses corresponded to control and status indicators such as the state of the FIFOs.

Similarly, sending cells into the network required making 14 writes to memory, interleaved with writes to the address corresponding to the FIFO write control signals.

While better methods of utilizing the processor were later investigated, this initial interface provided an early development platform that allowed us to explore software segmentation and reassembly of ATM cells and interrupt-driven packet processing. Using the VupBoard we were able to develop and debug device driver software that made the VuNet accessible to applications via the standard UNIX socket services. The driver also made the VuNet accessible via standard IP services, including NFS,

Figure 4: A block diagram of the VudBoard, which consists of 11 chips.

Telnet, FTP, etc. Finally, since the programming model for the VupBoard was similar to (though an order of magnitude slower) that of the cell coprocessor, it provided a vehicle through which we could benchmark software and project the expected performance of a system with a coprocessor interface.

#### 3.2.2 VuNet DMA Interfaces

The next VuNet-specific interface focused on improving the bandwidth and relaxing the temporal coupling between the host CPU and the interface – building interfaces, that are faster, rather than smarter.

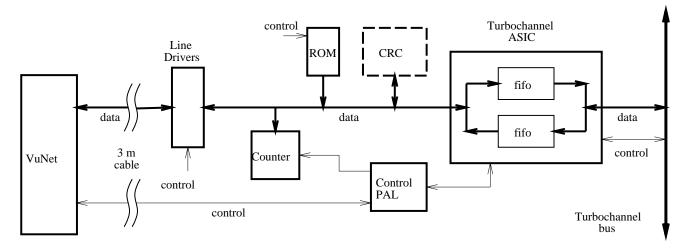

Although the design does not use any custom ATM circuitry, it does utilize the TURBOchannel Interface ASIC  $(TcIA)^1$  for the DEC TURBOchannel bus. This bus is used in the DEC 3000 line of Alpha workstations, as well as in the DEC 5000 line of MIPS-based systems. The TcIA performs the DMA request and arbitration, and contains two 60-byte FIFOs for receive and transmit.

As shown in Figure 4, the single chip PAL controls all data movement between the ATM network and TURBOchannel ASIC. Since the data bus from the VudBoard to the VuNet switch is shared by the receive and transmit paths, it arbitrates between reading cells from the switch and writing cells to the switch, with reception given priority over transmission.

The counter is used to implement an optional transmission timer that controls the pace of cells injected into the network.<sup>2</sup> Finally, the ROM provides device identification information. Although it is superfluous to our design, it is included on the interface in order to conform to the TURBOchannel specification.

Various hardware and software configurations allowed experimentation with interrupt-driven versus polled packet-processing. This allowed measurements of packet delivery latency and packet processing/context switching overhead.

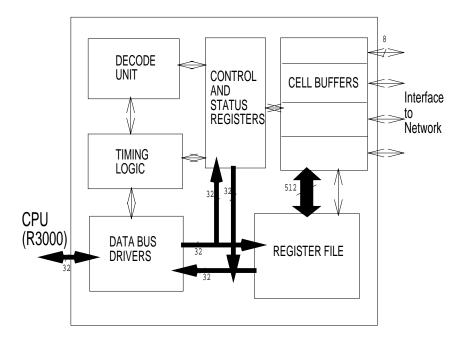

#### 3.2.3 Cell Coprocessor Interface

A cell-based coprocessor chip was designed to provide a direct interface between an ATM network and the coprocessor interface of a conventional RISC processor. The combined RISC processor/cell

$<sup>^1\,{\</sup>rm The}\,\,{\rm TcIA}$  chip has been discontinued and is no longer available.

$<sup>^{2}</sup>$  This could be used as an experimental way for implementing flow control, and is currently used for implementing pacing should a target host not have the ability to receive bursts of data at the full rate which can be transmitted.

Figure 5: Cell-Based Coprocessor Design

coprocessor complex could form the core of an ATM-compatible workstation or could be used as a stand-alone cell processor, similar in function to Bellcore's cell processing engine. To perform network operations, such as reading and writing cells, the RISC processor executes coprocessor instructions, much the way it performs floating point operations.

¿From a software perspective, this interface was quite similar to our programmed I/O interfaces. However, from simulations, a considerable performance improvement was to be realized – by completely bypassing the memory subsystem and permitting the direct transfer of cell data to/from the CPU's registers.

Figure 5 is a block diagram of the prototype coprocessor which is designed to operate with the 40 Mhz versions of the MIPS R3000 processor. This work was closely aligned with Bellcore's work on a standalone cell processing engine. The bus interface, timing logic, instruction decoder, and control/status registers have been substituted for Bellcore's on-chip RISC engine and memory interface. The instruction decoder includes a pipeline follower that tracks the MIPS instruction stream, decoding and sequencing any instructions that pertain to the coprocessor. A large fraction of the design, including the network interface, cell buffers and register file has been directly copied from the Bellcore chip. The savings resulting from the substantial re-use of chip design and layout is a clear demonstration of the benefits of the close collaborative links established within Aurora.

#### 3.2.4 High Performance Host Interface

One of the other interfaces designed within Aurora was the Bellcore Osiris board [7], designed with the assistance of MIT. This was a hybrid system with the ability to scatter ATM cell payloads into host buffers corresponding to VCIs. Though some overhead processing is needed to maintain and set up areas of memory for different packets that come in, no more processing is required than in transferring fully assembled packets from the host interface.

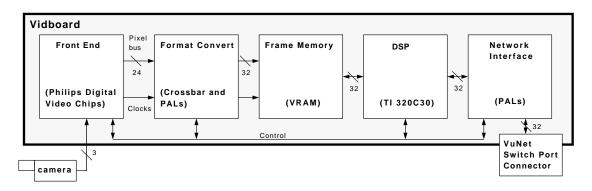

Figure 6: Block diagram of the Vidboard

### 3.2.5 Summary

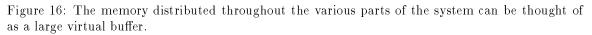

Host interface functionality can be categorized into three primary functions: data movement, data processing, and data delivery. Data movement functions include reading data from processor memory and writing the data to the network, and vice versa, while data processing functions include demultiplexing data, performing checksums, packet reassembly, and packet segmentation. Data delivery to the application level often entails working withing the methods used in the operating system, which may necessitate copying from operating system memory space to application memory space.

Functions such as packet segmentation and reassembly (SAR) are some of the more complex functions. The *complex interface* approach would be to perform this processing on the interface itself through the use of customized hardware and/or a dedicated CPU. In a *reduced complexity interface* (RCI) these functions are performed by the host CPU itself, i.e., on the shared and general purpose processing engine of the workstation.<sup>3</sup>

Scattering individual cell payloads into different areas of host memory is an attractive mix between hardware and software SAR. Scatter reassembly is a function that does not require a complex design, yet may save some per packet assembly costs. Essentially the only difference between this hybrid method and outboard packet reassembly is that the bus transfers occur in ATM-sized chunks in the former, and packet-sized chunks in the latter. The trade-off involves a reduction in memory requirements and latency in exchange for an increase in bus arbitration overhead.

# 3.3 Information Appliances - the Vidboard

Multimedia systems typically consist of workstations that contain a number of multimedia addin boards for functions such as video and audio capture and playback. Our DAN equivalent, an ATM-based video capture board, known as the Vidboard, was use to explore the properties of a network-based video source.

The Vidboard is based on a front-end frame-memory processor architecture that is capable of generating full-motion video streams having a range of presentation (picture size, color space, etc.) and network (traffic, transport, etc.) characteristics. The architecture is novel in that it also permits the decoupling of video from the real-time constraints of the television world. Through a closed-loop control mechanism, a destination device can dynamically vary the frame rate of a video stream during the course of a session, which allows easier integration of video into the software environment of computer systems.

<sup>&</sup>lt;sup>3</sup> These concepts are developed further in [10]

Figure 7: Block diagram of the AVlink

### 3.4 Seamless ATM – DAN/LAN/WAN Internetworking

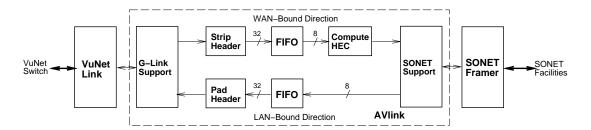

One of the important ideas of ATM is that of "seamless" interconnection; that is, the concept of a uniform network service that transcends local and wide areas. Although standardized SONET/ATM represents one approach, ATM-based networks which do not adhere fully to the SONET standards and conventions can still be incorporated into the "seamless" network. The use of the ATM protocol reference model identifies differences between two ATM networks which can then be converged through relatively simple hardware. To investigate these issues we developed two specialized VuNet links, the AVlink and the Zebra.

#### 3.4.1 AVlink

The AVlink is an ATM bridge interconnecting the VuNet and the Aurora testbed wide-area facilities. Differing design considerations for each network have caused a number of architectural differences between them. The AVlink overcomes these differences and provides low latency interconnection between the two networks. Performance numbers and several configurations in which the AVlink has been used are described in a Section 4.1.2.

On the VuNet side, the AVlink is similar to other inter-switch links. On the Aurora side, the AVlink attaches to one of the four available OC-3c channels via Bellcore's STS-3/OC-12 multiplexor. The use of multiple channels in parallel, a technique known as striping, is complicated by the presence of varying end-to-end delays between the channels. This effect, sometimes known as skew, was also investigated in the development of the Bellcore Osiris board.

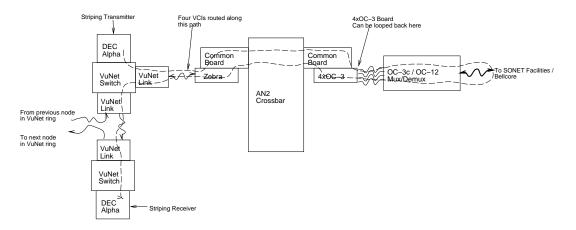

#### 3.4.2 Zebra – Striping

The Zebra is an ATM bridge interconnecting the VuNet to the AN2 switch, an industrial strength ATM LAN developed by Digital. The AN2 can, in turn, be connected to the Aurora facilities via a four channel OC-3 card and an OC-3/OC-12 multiplexor developed by Bellcore.

In order to formalize the issues associated with network striping, we developed a reference model that distinguishes four degrees of freedom of relevance to striping implementations. These are:

- Striping Topology: How and where the path between two hosts is split into stripes. Possible cases are end-to-end splitting, internal splitting, or some combination of these two.

- Participation of Hosts and Networks: The degree to which the hosts and networks support a striping implementation.

- Striping Layer: The network layer at which the striping occurs. This can range from the physical layer all the way up to the application layer, and determines the size of the striping unit, which is the largest unit of data which is transported intact on a single stripe.

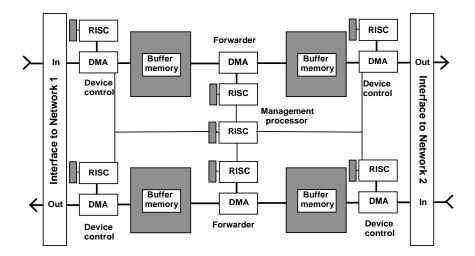

Figure 8: Environment developed for striping experiments.

• Implementation Issues: There are two main problems to overcome when implementing network striping; these are balancing the loads on the stripes, and maintaining synchronization across the stripes so that higher layer data may be correctly reassembled. The implementation issues relate to the various options available for solving these problems and the means by which the characteristics of the striped facilities are made visible to the layer at which striping is being performed.

An environment that interconnected the VuNet DAN, the AN2 LAN, and the Sunshine WAN using the Aurora facilities, was developed (Figure 8) to explore and experiment with the functional space mapped out by the model. As part of this environment, a bridge between the VuNet and AN2 was developed. Known as the Zebra, this board converges the differences between the two networks. The configuration linking these three networks, as well as some lessons learned about network striping, will be presented in a later section.

# 3.5 ATM End Working

Using the VuNet as a research platform, several aspects of service integration were investigated. First, VuNet network communications were fully integrated into the system, directly via ATM-supported UNIX sockets, and indirectly, via IP-supported interfaces (including UDP and TCP sockets). This allowed all the usual Internet services, e.g., FTP, Telnet, NFS, etc. to be offered over the VuNet.

Also, the Vidboard network based video capture device was used as a platform for real-time traffic generation within the network. Source traffic shaping allowed investigation into real-time traffic interaction with the host device drivers. A closed-loop control mechanism was developed for graceful degradation of real-time traffic bursts.

Investigations into the jitter arising from the middle and upper layers within the end systems of multi-service networks were also conducted.

#### 3.5.1 A UNIX Device Driver with Software SAR

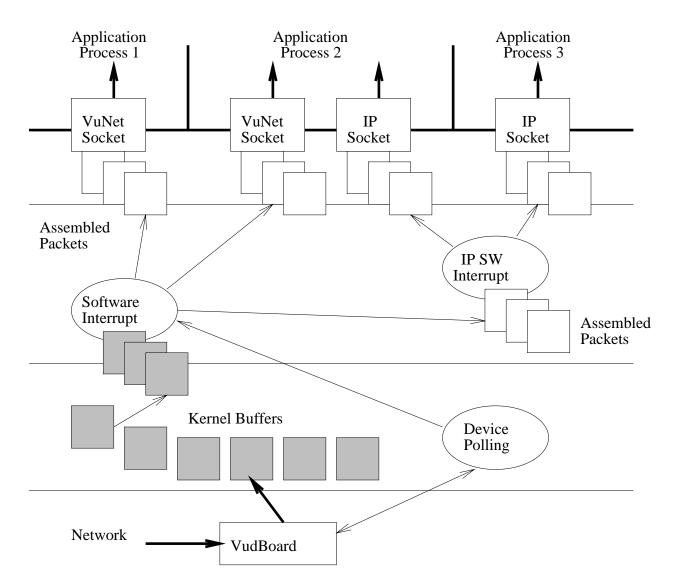

Our initial requirements of data transparency, interoperability and modularity dictated the structure of our network device driver. The driver, as shown in Figure 9, was designed to be organized into several major levels. At the highest level are the application processes, which receive data over the UNIX socket interface. Below this are the kernel side of the socket interface level, the reassembly and protocol processing level, and the buffer and device management level.

Figure 9: Cells are read from the network at and passed to the software reassembly process at regular polled intervals. These assembled packets are then passed to the IP handler or directly to a VuNet socket.

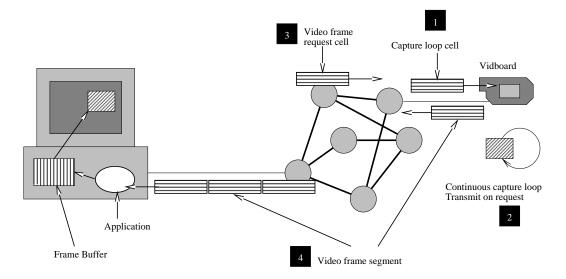

Figure 10: Video source control model: 1) A command cell is sent to the Vidboard, starting it in a 2) continuous video capture loop, where, upon 3) receipt of a frame request cell from workstation, a 4) video frame is delivered.

If cells have been received on the network, the driver temporarily halts the VudBoard in order to point it to a new kernel buffer, freeing up the other buffer to be queued for reassembly. Buffers were allocated and quickly swapped in order to minimize the time the host interface is "deaf." Because of the size of the output buffers on the switch, the driver had to be designed so that cells were not lost while this was occurring. Thus, the VudBoard was restarted before the buffers which contained network data were processed.

The buffers that are queued by the previous level may contain interleaved ATM cells over many difference VCIs. The reassembly process must look up the VCI to determine the type of connection, and reassemble the cell payloads into packets, stripping out the ATM header information and other related information. This is done by copying the data into different buffers reserved for reassembled packets.

Depending on the kind of packet reassembled, packets are passed directly to the VuNet application socket, or may be passed to the IP Packet Handler for additional protocol processing and further demultiplexing. The UNIX socket mechanism is used as the data delivery mechanism for the applications that use our network data. Once the data is delivered to the socket level, it can be copied out to user space on user reads, completing the delivery of data to the application. Integrating UNIX sockets allowed the seamless integration of the network to the application level.

Clearly, our software-based SAR approach involves considerable copying of network data, and this is an issues which we will return to in the *lessons* section of this report.

#### 3.5.2 Vidboard Network Protocols

Hosts in the VuNet are not dedicated to processing and forwarding network data - they are user machines under varying loads. In order to prevent the backlog and loss of cells while hosts are busy with user tasks, a protocol was developed for the use of network based peripherals, such as the Vidboard.

The command cell protocol is used in making the Vidboard execute a particular task. The protocol consists of using a single ATM cell, which is formatted into a number of fields, to carry command

information to the Vidboard. The command code field indicates the task to be executed. Additional information about the task is carried in the command parameters field.

As shown in Figure 10, cells are usually generated in response to a command cell. Other examples of responses are status information in response to a diagnostic command and a video stream in response to a video data request. The response to a video request has two types of characteristics: video *adaptation layer* and video *traffic shaping*.

For sending video data from the Vidboard to a workstation, we adopted an *adaptation layer* similar to that specified by the ATM Adaptation Layer 5 (AAL5) standard, except that the cyclical redundancy check (CRC) value for error-detection has been replaced by a more easily computed checksum value. In this protocol, scan lines are grouped into packets which are then fragmented into ATM cells. The size of the packet is user-programmable.

The Vidboard is capable of generating video faster than some workstations can process it. In order to avoid overwhelming the workstation network interface with video data, the Vidboard implements *traffic shaping*. Video is sent in small bursts separated by delays, during which the burst is processed by the workstation. The workstation requesting the video sets four parameters in the video request command cell to tune the video stream's traffic characteristics to its needs.

As part of the protocols for controlling the Vidboard from across a network, a scheme was developed which dynamically varied the Vidboard's frame rate during a video session. The Vidboard is placed in a constant video capture loop and is sent requests for frames as they are needed. The application can vary the rate of requests to match its ability to process video. As an example, a video-in-awindow application gracefully halves its rate of requests as a second video-in-a-window is started and the two applications have to share the available machine cycles.

# 3.6 Application-oriented Signaling

Each application in the VuNet is responsible for opening, maintaining, and closing its own connections. This is done in a "wormhole" fashion by way of ATM control cells embedded in the cell data stream. Applications use library functions that access a shared file and execute an allocation algorithm that prevent nodes from stealing other nodes' VCIs. Background processes can be used to verify link tables and refresh connections when necessary, such as in the case where a link card has been power cycled. In order to maintain table consistency when the network is reconfigured, it is possible to run topology daemons that allow each host to discover the network topology.

# 3.7 The VuSystem

The VuSystem[14, 15] is a programming system for the software-based processing of audio and video data. The VuSystem was designed to run on ordinary Unix workstations which have no specific support for the manipulation of multimedia data. Because the VuSystem includes an easy to program and extensible in-band processing component, it is uniquely suited to the development of applications that perform intelligent processing of live media.

VuSystem applications [13] combine intelligent media processing with traditional capture and display. Some process live video for more responsive human-computer interaction. Others digest television broadcasts in support of content-based retrieval. Both classes demonstrate the utility of networkbased multimedia systems that deliver audio and video data all the way to the application.

Examples of some VuSystem applications include:

**The Room Monitor** processes video data from a stationary camera in a room. It processes the live video to determine if the room is occupied or empty, and records video frames only when activity is detected above some threshold. It produces a file containing a series of video clips that summarize the activity in the room. A video browser is used to view the segments.

| Vabrowser                                                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Deap Thoughts<br>to me, boxing is<br>litu ballet except<br>that there's no<br>music or choreography of<br>and the danars hit<br>each other | 12011 (12012)<br>12011 |

| Pathname<br>Mb,6,AAV<br>Setail Divege Beliete<br>Control<br>IKK K DI (2000)<br>Centrol Famel Program Search                                | ud.,6<br>Hey 13 1993                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

Figure 11: The whiteboard program.

| - Vs8portaltrowser                                                                                                                                                        | 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| reloading index file, please asit,                                                                                                                                        | Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughilighte<br>Aughi                                                                                                                                                                                                                                                                                                                                                                             |

| Pathnami<br>//side/pinento/Neus/CM/SportsCenter/CM/SportsCenter<br>Detail Charge Belate<br>Control<br>IOC C I 2 2011<br>Ecentral Panel Program<br>Rout the Sports Browser | Polyres at<br>Dopol<br>Roy EL 400/78<br>Roy EL 400/78<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Robustor<br>Rob |

Figure 12: The sports browser.

- **The Whiteboard Recorder** keeps a history of changes to an office whiteboard. It works by taking video from a stationary camera aimed at the whiteboard and filtering it. By following a simple set of rules, the filtering distills the video into a minimum set of images. A browser (Figure 11) can be used to view the saved images.

- **The News Browser** provides interactive access to television news articles. CNN Headline News is automatically partitioned into segments and saved on disk at regular intervals. The stories are viewed with a video browser program. News stories that are closed-captioned can be retrieved based on their content.

- **The Joke Browser** records late-night talk show monologues, and segments them into jokes by processing the closed-captioned text. It extracts information from a recorded monologue through the analysis of closed-captions. In addition to the text of the jokes, the captions contain hints to the presence of audience laughter and applause. A joke parsing module groups captions into jokes.

- **The Sports Highlight Browser** records and segments a nightly sporting news telecast into a set of video clips. Each clip represents highlights of a particular sporting event, and the clips can be browsed as shown in Figure 12. This application generates its annotations through the template matching of scoreboard graphics.

While many VuSystem applications do not require a high speed ATM network in order to function, they were easily layered on top of the VuNet. Performance of the applications using VuNet based devices equaled or exceeded performance using specialized video and audio capture devices.

### 4 Experiments and Results

### 4.1 The VuNet

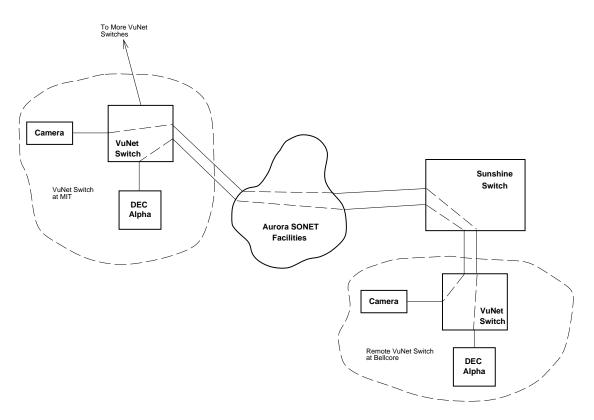

Eight VuNet nodes were deployed at MIT, Bellcore and the University of Pennsylvania over a period of three years. Each VuNet node consisted of a four or six port switch equipped with a link (or AVlink), one to three Vidboards, and one or two host interfaces. The nodes at MIT were typically connected in a ring, with a stub protruding from the ring which connected, through Aurora and two AVlinks, to a similarly-outfitted VuNet node located at Bellcore in Morristown, NJ, then at University of Pennsylvania, as shown if Figure 13. ViewStation applications required no modification to operate over Aurora.

In total, 8 switches, 11 network-based video appliances, 11 host workstations and a suite of multimedia applications were deployed to demonstrate seamless DAN/LAN/WAN internetworking.

The following subsections describe some results achieved with the VuNet hardware, using as the primary example, the Vidboard client connected to the VuNet running the VuSystem software.

#### 4.1.1 Local VuNet Performance

Each switch functioned at a speed of 700 Mbps per port, per direction, for an aggregate capacity of 2.8 Gbps for the four ports switches and 4.2 Gbps for the six port switches. Individual switches were run at over 1.5 Gbps per port, for an aggregate capacity of 9.0 Gbps, though this speed was not used in deployed switches. Within the local ATM ring, the inter-switch links operated at 500 Mbps.

#### 4.1.2 AVlink/Zebra Performance

Seamless interconnection really works. Despite the lack of a common physical layer standard, the integration of the different ATM networks was performed quite easily; cells from the VuNet were

Figure 13: Wide-area configuration.

routed via the Sunshine switch and accepted by the VuNet node on the other end. The only issues then become connection management in the separate conjoined networks. The VuNet used cell-based signaling whereas the Sunshine switch used out-of-band connection management. However, this was bridged by allowing Sunshine to switch the VuNet connection management cells.

In a separate experiment, the AN2 switch was attached to the VuNet as a stub off the main ring. On another port of the AN2 switch was a connection to the Aurora/SONET facilities, using an AN2 line card which generated 4 OC-3c channels and a Bellcore multiplexor board which generated an OC-12 channel from four OC-3c channels and vice-versa. Since only one AN2 switch was available, two hosts on the local VuNet ring were connected using a loopback topology. Software was written for the line card processor which allowed it to support the in-band connection management used by the VuNet. Using this configuration, VuNet hosts were able to set up connections through each of the OC-3c channels, which they could use as stripes. Code could then be written to implement various striping schemes outlined by our reference model.

### 4.2 Host/Network Adapters

The work on the host adapters spanned four generations of host workstations. Initially, the VuNet hosts were DEC 5000/200 (25 Mhz) and later 5000/240 (40 Mhz) workstations based on the MIPS R3000 processors. During the middle of the project, all the workstations were upgraded to 133 MHz DEC 3000/400 Alpha workstations. At the end of the project, one 200 MHz DEC 3000/800 Alpha workstation was acquired and connected to the VuNet.

#### 4.2.1 VupBoard

Using the VuSystem software, the performance of the VupBoard was measuring using video generated by a Vidboard. The VupBoard driver was a very processor-intensive process as it required making TURBOchannel bus reads for getting data from the network.

While this contributed to the processor load, hence slow interface speed, while reading and writing to the network, the primary limitation of the VupBoard was due not to this, but to the interruptdriven nature of the board. Interrupt service latencies were not guaranteed in any way, causing data to be potentially lost in the buffers of the switch when the device was not able to be serviced while large amounts of data arrived.

Initially, with the DEC 5000, 10 Mbps of data was delivered to the application level. Upon upgrading to the DEC 3000/400, 15 Mbps of data was delivered to the application. As the VupBoard was phased out soon after introduction of the VudBoard, no numbers are available for the DEC 3000/800.

#### 4.2.2 VudBoard

Using an application which reads and writes data to VuNet sockets along with the standard VuSystem applications, we tested the performance of the current VudBoard.

When a packet is queued for transmission, the packet segmentation occurs before the resulting page can be moved cell-by-cell over the TURBOchannel to the VudBoard. The peak data transmission of a single page occurs at 232 Mbps. However, since we can only DMA one page at a time (due to a bug in the DEC ASIC used), we must process an interrupt for each page to be transmitted. The performance achieved for transmitting many pages is 67 Mbps. On the receive side, 512 Kbit bursts at 232 Mbps can easily by processed by the VudBoard. The bottleneck on the receive side, however, is the host processing.

When data arrives at the host interface, it must contend for the TURBOchannel bus to transfer its data into host memory. Due to bus arbitration, grant latency, and a wait period between successive transfers, the host interface is unable to write to memory at a rate greater than 232 Mb/sec. However, since the host cannot process data at this rate, it cannot be sustained indefinitely. The maximum sustained rate at which data could be transferred across the bus was 131 Mb/sec.

When host processing is factored in and the data is reassembled and delivered to the application level, we find that we can indefinitely sustain a data rate of 100.7 Mb/sec of assembled data packets delivered to the application memory space. The device driver must process and reassemble raw ATM data at 111 Mb/sec in order to sustain this packet data rate to the application level. The actual data transfer rate over the TURBOchannel bus is actually 134 Mb/sec, but this reflects transfer of 64 bytes per ATM cell.

Performance of the VudBoard is summarized in Table 1, along with VupBoard performance numbers. Throughput measurements are made while running the full suite of ViewStation software within the UNIX operating system.

|                                  | Data delivered to the application level<br>(Megabits per second) |      |       |  |

|----------------------------------|------------------------------------------------------------------|------|-------|--|

| Interface                        | PIO DMA DMA/Improved Driver                                      |      |       |  |

| DEC 5000/200                     | 10.4                                                             | 15.4 |       |  |

| DEC 3000/400 (133 MHz)           | 14.7                                                             | 34.4 | 66    |  |

| DEC $3000/800 (200 \text{ MHz})$ |                                                                  |      | 100.7 |  |

Table 1: VudBoard performance measured by data delivered to application level.

#### 4.2.3 Coprocessor Simulations

A coprocessor chip for the VuNet was designed and fabricated. Though it was not integrated into a MIPS-based workstation, it was partially debugged to the extent that cell registers could be read and write data using our logic analyzer/signal generator. A full suite of simulations were performed, and the following describes our experiments and results.

To measure the throughput attainable by the coprocessor host interface, we performed timing experiments on a floating point coprocessor. The processes' view of the coprocessor interface essentially consists of coprocessor general purpose registers and coprocessor control registers. These are available on a floating point coprocessor as well, and since the timing of all coprocessors (whether floating point or network interface) with respect to the main processor in the R3000 architecture is the same, the results we obtained can be expected with the network interface cell coprocessor also.

The workstation configurations evaluated were a DECstation 5000/200 and a DECstation 5000/240. We ran a series of experiments in which the **Interface Model**, **Transfer Direction**, **Cell Operations**, and **Processor Speed** were independently varied. The results are summarized in Tables 3 and 4. Some of the simulations present optimistic results that provide an upper boundary on the burst performance that could be achieved by the traditional interfaces. For example, our DMA values capture the data transfer rate between memory and the registers. Thus, we assumed that the DMA transfer has occurred at little interference to the processor, and the rate of this DMA transfer is much higher than the rate at which data can be accessed by the processor.

| 3.7         |                                                                                                                                                                                                                                                                              |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name        | Function                                                                                                                                                                                                                                                                     |

| Vup         | Programmed I/O VupBoard interface. For receive routines, this consists of loads from TURBOchannel to processor registers, followed by stores into memory. For transmit, it consists of loads from memory to the processor registers, followed by stores to the TURBOchannel. |

| Vup1        | Same as Vup, except with no header byte swap.                                                                                                                                                                                                                                |

| Cop1        | Similar to VUP, using the coprocessor approach.                                                                                                                                                                                                                              |

| Cop2        | For receive, move header from coprocessor to processor registers.<br>Then store body directly from coprocessor register file to mem-<br>ory. For transmit, load header into CPU registers, and load body<br>directly from memory to coprocessor registers.                   |

| Cop3        | In the receive direction, store entire cell directly into memory. For<br>transmit, load entire cell directly from main memory to coprocessor<br>registers.                                                                                                                   |

| Cop4        | Same as Cop1, except with no header byte swap.                                                                                                                                                                                                                               |

| Cop5        | Same as Cop2, except with no header byte swap.                                                                                                                                                                                                                               |

| Cop6        | Same as Cop3, except with no header byte swap.                                                                                                                                                                                                                               |

| DMA<br>DMA1 | In the receive mode, load data that has already been stored into<br>main memory by DMA. In the transmit mode, store data into main<br>memory to be read by the network through DMA.                                                                                          |

| DMAI        | Same as DMA, except with no header byte swap.                                                                                                                                                                                                                                |

#### Table 2: Interface models

• As expected, the simulated numbers predicted a throughput higher than observed. In the programmed I/O path, the receive and transmit throughput suggested by the index numbers are 89 Mbps and 166 Mbps. This can largely be accounted for by the fact that we assumed that TURBOchannel writes and reads took 3 and 8 cycles respectively. Some logic analyzer experiments conducted by Chris Lindblad and Dave Tennenhouse indicate that the read performance on the TURBOchannel is 14 Turbo-cycles. This changes our predicted value in the

| Direction | Vup                           | Cop1  | Cop2  | Cop3  | DMA   |  |  |

|-----------|-------------------------------|-------|-------|-------|-------|--|--|

| D         | DECstation 5000/200 (in Mbps) |       |       |       |       |  |  |

| Receive   | 57.2                          | 210.3 | 292.4 | 304.4 | 176.2 |  |  |

| Transmit  | 79.7                          | 104.6 | 120.7 | 124.9 | 96.3  |  |  |

| D         | DECstation 5000/240 (in Mbps) |       |       |       |       |  |  |

| Receive   | 39.1                          | 250.5 | 314.6 | 368.2 | 201.8 |  |  |

| Transmit  | 100.4                         | 187.9 | 226.1 | 247.2 | 151.4 |  |  |

Table 3: Peak Throughput (with header byte swap)

| Direction                | Vup1                          | Cop4  | Cop5  | Cop6  | DMA1  |  |  |

|--------------------------|-------------------------------|-------|-------|-------|-------|--|--|

| D                        | DECstation 5000/200 (in Mbps) |       |       |       |       |  |  |

| $\operatorname{Receive}$ | 63.1                          | 337.1 | 512.6 | 535.8 | 239.3 |  |  |

| Transmit                 | 91.4                          | 127.6 | 150.3 | 152.3 | 116.0 |  |  |

| D                        | DECstation 5000/240 (in Mbps) |       |       |       |       |  |  |

| Receive                  | 40.5                          | 373.6 | 529.5 | 559.4 | 287.4 |  |  |

| Transmit                 | 105.2                         | 243.6 | 299.8 | 302.5 | 180.3 |  |  |

Table 4: Peak Throughput (without header byte swap)

receive direction to 48 Mbps, which is much closer to the observed value. Unfortunately, no experimental values are available for TURBOchannel write direction.

• The observed throughput in the *DMA1* case are 290 Mbps and 196 Mbps, in the receive and transmit directions, respectively. These values take into account the *entire* path of data, all the way from the network DMA device, to the correct location in memory. The Bellcore Osiris board [7] runs at 480 Mbps and 384 Mbps. However, these figures are for the direct path between the DMA device and memory, and do not take into account the copying of this data into some final location in memory. Our predicted throughput figures (294 Mbps and 268 Mbps), are limited by the memory subsystem, rather than the throughput between the memory and DMA device. Thus these provide an upper bound on the overall performance achievable, if a DMA board, such as the Bellcore board, were used. Even if the DMA board could transfer at higher rates into memory, the total throughput would be bound by the performance of the memory system.

| Direction                | Predicted |      | Obsei | rved  |

|--------------------------|-----------|------|-------|-------|

|                          | Path      | Rate | Model | Rate  |

| $\operatorname{Receive}$ | IO1       | 89   | Vup1  | 40.9  |

|                          | IO3       | 294  | DMA1  | 290.7 |

|                          | REG1      | 486  | Cop4  | 379.7 |

| Transmit                 | IO1       | 166  | Vup1  | 111.9 |

|                          | IO3       | 268  | DMA1  | 196.0 |

|                          | REG1      | 358  | Cop4  | 259.7 |

Table 5: Predicted vs. Observed Throughput (in Mbps)

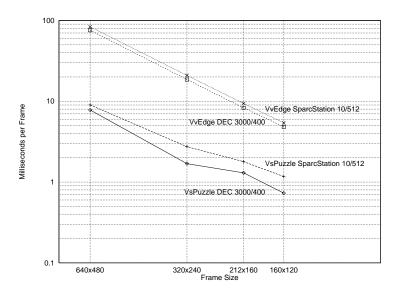

### 4.3 Vidboard Performance

The high speed of the VuNet and the properties of its client interface make it so that the traffic characteristics of a data stream injected at one point in the network are preserved as the stream arrives at its destination. This property was exploited to tailor the traffic characteristics of a video stream generated by the Vidboard to the needs of the workstation receiving it.

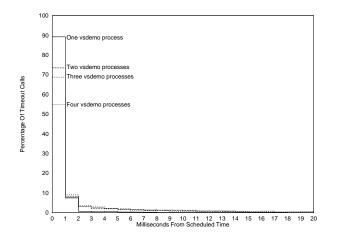

Our software environment processes multimedia information in small bursts. Video frames are segmented into transmission frames (t-frames) which are transmitted in bursts separated by delays. A pseudo-AAL5 segmentation protocol [16] is used to ship the t-frames. The stream is shaped using the following parameters: number of scan lines per t-frame (LT), number of cells per burst (CB), interburst delay and interframe delay. These parameters are used to shape the video stream to match the burst absorption timing properties of the workstation. These properties are related to the latencies of the interrupts and routines involved in processing a burst of data.

|                                                                                                   | $\begin{array}{l} \text{scan lines per t-frame} \\ (480 \text{ scan lines} = 1 \text{ frame}) \end{array}$ |                                        |                     | interburst<br>delay |                   |

|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------------|---------------------|-------------------|

| $\begin{array}{l} \text{cells per burst} \\ (14 \text{ cells} = 1 \text{ scan line}) \end{array}$ | 4 16 120 480                                                                                               |                                        |                     |                     |                   |

| (14  cens = 1  scan me)                                                                           | (frames/s)                                                                                                 |                                        |                     | (us)                |                   |

| 14                                                                                                | 7.7 8.7 9.1 9.5                                                                                            |                                        |                     | 150                 |                   |

| 28                                                                                                | 9.1                                                                                                        | 10.0                                   | 10.5                | 11.7                | 240               |

| 42<br>56                                                                                          | $9.0 \\ 9.5$                                                                                               | $\begin{array}{c}9.5\\10.0\end{array}$ | $\frac{10.5}{10.5}$ | 11.1<br>11.1        | $\frac{390}{510}$ |

Table 6: Effects of traffic shaping on frame rate

|              | Video type         |                    |  |  |

|--------------|--------------------|--------------------|--|--|

| Picture size | Black and white    | Dithered Color     |  |  |

|              | frames/s (Mbits/s) | frames/s (Mbits/s) |  |  |

| 640x480      | 15.0(37)           | 4.3(10.5)          |  |  |