# Message-Driven Dynamics

by

Richard Anton Lethin

M.S., Massachusetts Institute of Technology (1991) B.S., Yale College (1985)

# SUBMITTED TO THE DEPARTMENT IN PARTIAL FULFILLMENT OF THE REQUIREMENTS OF THE DEGREE OF

# DOCTOR OF PHILOSOPHY IN ELECTRICAL ENGINEERING AND COMPUTER SCIENCE

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY MARCH 1997

©1997 Richard A. Lethin. All rights reserved.

The author hereby grants MIT permission to reproduce and distribute publicly paper and electronic copies of this thesis document in whole or in part.

| Signature of Author |                                          |                                                           |

|---------------------|------------------------------------------|-----------------------------------------------------------|

|                     | Department of Electrical Engineering and | Computer Science<br>March 18, 1997                        |

| Certified by        |                                          |                                                           |

|                     | Professor of Electrical Engineering and  | William J. Dally<br>Computer Science<br>Thesis Supervisor |

| Accepted by         |                                          |                                                           |

Dr. Arthur C. Smith Chairman, Departmental Committee on Graduate Students

# Thesis Committee

William J. Dally Professor of Electrical Engineering and Computer Science

> Thomas F. Knight, Jr. Senior Research Scientist

F. Thomson Leighton Professor of Mathematics

The research in this thesis was supported in part by a fellowship from the John and Fannie Hertz Foundation

# Message-Driven Dynamics

by

Richard Anton Lethin

Submitted to the Department of Electrical Engineering and Computer Science at MIT on March 18, 1997 in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy in Electrical Engineering and Computer Science

#### Abstract

Fine-grained message-driven parallel computers offer the promise of massive computational power with relatively low costs of logic and memory. The first such computer, the J-Machine, was constructed at MIT. This research critically examines this machine and finds that global flow control and load balancing were neglected in the J-Machine design and that these features must be considered for successor designs.

The fact that the J-Machine is unable to run effectively a heavy fine-grained synthetic work-load demonstrates the importance of this issue. Queues overflow and divert the processors from performing useful computation. Instead, the processors spend most of their time servicing costly overflow traps.

This thesis analyzes the queueing dynamics of large heavy closed message-driven workloads and derives expressions for overflow rate as a function of the number of processors, the number of messages, and queue size. A threshold of tolerable imbalance is derived, beyond which no queue size will suffice. To model the J-Machine's routers, a mean value model is constructed and it shows that the router arbitration logic chosen for the J-Machine shapes the qualitative observed overflow behavior. Simply making the J-Machine queues larger is not a useful solution to preventing overflows: at saturation, the network imparts sufficient imbalance so that even balanced applied workloads exceed the tolerable threshold.

Active global flow control and load balancing mechanisms are needed. Using simulation, the thesis compares one mechanism that returns overflowed messages to the sending processor to a mechanism using a high-water-mark and a priority alternate network. The conclusion is that the high-water-mark based scheme is more effective in preventing overflows.

**Keywords:** J-Machine, message-driven, message passing, closed queuing networks, fine grain, heavy load, mean value analysis, wormhole networks, buffer sizing, queue overflow.

Thesis Supervisor: William J. Dally

Title: Professor of Electrical Engineering and Computer Science

#### Acknowledgements

Computer architecture research is a long process, particularly when it involves building hardware, and particularly in graduate school. The pure labor of forging specifications into silicon can approach being overwhelming. Stuart Fiske, John Keen, Peter Nuth, and I devoted large portions of our graduate careers to building the Message-Driven Processor for the J-Machine. As a member of the research staff, Mike Noakes designed logic, diagnostics, packaging, interfaces, and device drivers; Andrew Chang has maintained the J-machine since Mike left. We became and have remained friends.<sup>1</sup>

At Intel Corporation, Greg Fyler marshalled resources and made sure that the MDP passed through corporation and fabrication hurdles. Roy Davison's VLSI layout consulting services were invaluable. Duke Xanthopoulos, Eric McDonald and John Cha designed peripherals for the J-Machine.

Software for the J-machine came from brilliant and effusive code production by the CVA software team: Waldemar Horwat wrote the prototype CST Compiler, COSMOS, and the MDP simulator; Scott Furman, Mike Noakes, Debbie Wallach, Shaun Kaneshiro and Ellen Spertus made it work on the hardware. Todd Dampier wrote the first queue overflow handler routines. Our collaborators at Caltech, notably Daniel Maskit, ported the GNU C compiler to the J-machine.

Andrew Chien and Scott Wills provided early architectural vision for the J-Machine and CST. Soha Hassoun and Jerry Larivee designed early versions of the MDP. Martin Szummer's UROP work sparked my interest in queueing problems in the J-Machine.

I would like to thank Bill Dally for being an inspiring and devoted graduate advisor for me. Bill correctly positions his research projects aggressively beyond the mainstream; the J-machine is one of the most creative hardware projects in academia, and remains one of the largest academic parallel computers ever successfully completed (is there a larger one?). Bill's creativity, stamina, and high result yield became for me the benchmarks that drove me to improve my research. On the occasions when entrepreneurship and consulting threatened to divert me from graduate school, Bill has gone beyond the call of duty to keep me excited about MIT.

My graduate career has benefited substantially from associations with other MIT faculty members. Conversions with Tom Knight and course work with David Gifford and Ron Rivest provided inspiration for educational and enjoyable research distractions. Tom Leighton's mathematical skills helped me attempt more careful queueing analysis. I am also grateful to have had the opportunity to teach VLSI for Chris Terman, and thank him for his career assistance and advice. I would also like to acknowledge the rich experience that came from studying with Robert Goldberg when he visited to lecture at the MIT Sloan School.

<sup>&</sup>lt;sup>1</sup>As to the J-Machine itself, the one in our lab still runs the diagnostic suite perfectly after more than two years since the last time Andrew and I reassembled it.

I've enjoyed working Steve Keckler, arguing about compilers and processor architecture, ducking under the boom (most of the time), deploying the spinnaker, and jaunting off to Japan. However, rebuilding Etchells 105 was NOT fun.

Kathy Knobe patiently helped organize and encouraged my ideas, diluted my trace-scheduling chauvinism with her *real* compiler knowledge, and provided thesis-related commiseration.

Jim O'Toole has been a great graduate school friend by pushing me to strive in many areas: among them skiing the Sunrise trail at Norsk, cranking out thesis text, and looking for business strategy angles.

I will miss lunchtime conversations with the CAG folks; a political conversation including David Shoemaker, David Kranz, and Larry Dennison smothers the spectrum, and one can't match a real computer architecture conversation with John Kubiatowicz, Kirk Johnson, Don Yeung, or David Chaiken. Any meal with with Nate Osgood epitomizes brainstorming: ideas and enthusiasm like mad. What great fun!

My appreciation for computer architecture (and juicy hardware bugs) grew from designing the world's first VLIW with the Multiflow team. Josh Fisher taught my first computer architecture course at Yale and in doing so determined my career. John O'Donnell assigned me the task of designing the TRACE 28/200 floating point unit on my first day of work, and to date has not stopped sending neat projects my way. David Papworth and Paul Rodman taught me how to design supercomputers and how to debug them with a logic probe. Bob Colwell introduced me to computer architecture research and encouraged my decision to go to graduate school. Since Multiflow, it's been a pleasure working on additional VLIW projects with my friends including Cindy Collins and Ben Cutler at Equator.

I am grateful to Stuart Fiske, Kathy Knobe, Mike Noakes, Jim O'Toole, Teri Mendelsohn and Robert Parker for careful and constructive readings of this thesis text.

For their good friendship and support of my studies, I thank Stuart Fiske, Julia and Peter Nuth, Elliza McGrand, Dan Slavin, Cindy Collins, Michelle Nicholasen, Kathy Knobe, John Redford, Marco Fillo, Jane Murray, Peter Kindlmann, Jodeane Pringle, Stefan Freudenberger, Amy Bruckman, Trevor Darrell, Kathleen Smith, Nathaniel Kahn, Christine Langer, and Dan Simon. I also thank my siblings Carol, Peter and Douglas.

Teri Mendelsohn, of course, deserves special mention as my strongest inspiration and love. We can go to Paris, now.

Finally, as thanks for all that they are and all that have done for me, I would like to dedicate this thesis to my parents, Maria and Jay.

# Contents

| 1 Introduction |     |                        | on                                                          | 13 |  |  |

|----------------|-----|------------------------|-------------------------------------------------------------|----|--|--|

|                | 1.1 | 1.1 Overview           |                                                             |    |  |  |

|                | 1.2 | Backgr                 | round                                                       | 16 |  |  |

|                |     | 1.2.1                  | Philosophy                                                  | 17 |  |  |

|                |     | 1.2.2                  | Hardware                                                    | 19 |  |  |

|                |     | 1.2.3                  | Anomaly                                                     | 22 |  |  |

|                |     | 1.2.4                  | Analysis                                                    | 29 |  |  |

|                |     | 1.2.5                  | J-Machine Improvements                                      | 30 |  |  |

|                | 1.3 | Relate                 | d Research                                                  | 32 |  |  |

|                |     | 1.3.1                  | Other Architectures                                         | 32 |  |  |

|                |     | 1.3.2                  | Queueing Models                                             | 36 |  |  |

|                |     | 1.3.3                  | Summary                                                     | 41 |  |  |

|                | 1.4 | Thesis                 | Outline                                                     | 42 |  |  |

| 2              | J-M | J-Machine Architecture |                                                             |    |  |  |

|                | 2.1 | MDP a                  | and Communication Implementation                            | 48 |  |  |

|                |     | 2.1.1                  | CPU                                                         | 48 |  |  |

|                |     | 2.1.2                  | Network                                                     | 51 |  |  |

|                |     | 2.1.3                  | Processor-Network Interfaces                                | 58 |  |  |

|                | 2.2 | Deadle                 | ock Possibility                                             | 61 |  |  |

|                |     | 2.2.1                  | The Consumption Assumption                                  | 61 |  |  |

|                |     | 2.2.2                  | Processor's Message Queues Help with Consumption Assumption | 62 |  |  |

|   |     | 2.2.3   | Processor Progress Determines Message Queue Progress | 62  |

|---|-----|---------|------------------------------------------------------|-----|

|   |     | 2.2.4   | A Cyclic Blocking Dependency?                        | 63  |

|   | 2.3 | Queue   | e Overflow Handler                                   | 64  |

|   | 2.4 | Concl   | usion                                                | 70  |

| 3 | Que | euing I | Model                                                | 72  |

|   | 3.1 | Basic   | Closed Queuing Model                                 | 74  |

|   | 3.2 | Queue   | e Overflow                                           | 76  |

|   | 3.3 | Balan   | ced Workload                                         | 78  |

|   |     | 3.3.1   | All States Equiprobable at Equilibrium               | 78  |

|   |     | 3.3.2   | Counting States                                      | 79  |

|   |     | 3.3.3   | Balanced Workload Overflow Residency                 | 83  |

|   |     | 3.3.4   | Leighton's Method                                    | 84  |

|   |     | 3.3.5   | Balanced Workload Overflow Rate Estimation           | 88  |

|   |     | 3.3.6   | Balanced Workload: Conclusion                        | 92  |

|   | 3.4 | Imbal   | anced Workload                                       | 92  |

|   |     | 3.4.1   | Simple Examples                                      | 93  |

|   |     | 3.4.2   | Allowed Degree of Imbalance                          | 94  |

|   |     | 3.4.3   | Allowed Degree of Imbalance (Careful Analysis)       | 96  |

|   |     | 3.4.4   | Multiple Bottleneck Servers                          | 99  |

|   |     | 3.4.5   | Imbalanced Overflow Residency and Rate               | 100 |

|   |     | 3.4.6   | Imbalanced Workload: Conclusion                      | 104 |

|   | 3.5 | Discus  | ssion                                                | 104 |

|   |     | 3.5.1   | Open Queuing Networks                                | 104 |

|   |     | 3.5.2   | Exponential vs. Deterministic Service Distribution   | 107 |

|   |     | 3.5.3   | Analysis of Request/Reply Variation                  | 109 |

|   |     | 3.5.4   | Other Dynamic Questions                              | 112 |

|   | 3.6 | Concl   | usion                                                | 113 |

| 4 | J- $M$                            | achine Experiments 1                               | 15  |  |  |

|---|-----------------------------------|----------------------------------------------------|-----|--|--|

|   | 4.1                               | Snakes                                             | 116 |  |  |

|   |                                   | 4.1.1 Workload Parameters                          | 118 |  |  |

|   |                                   | 4.1.2 Metrics                                      | 120 |  |  |

|   |                                   | 4.1.3 Derived Parameters and Metrics               | 120 |  |  |

|   |                                   | 4.1.4 Some Software Details                        | 122 |  |  |

|   | 4.2                               | Typical J-Machine Snakes Performance Measurement   | 126 |  |  |

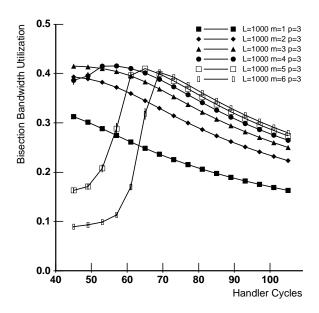

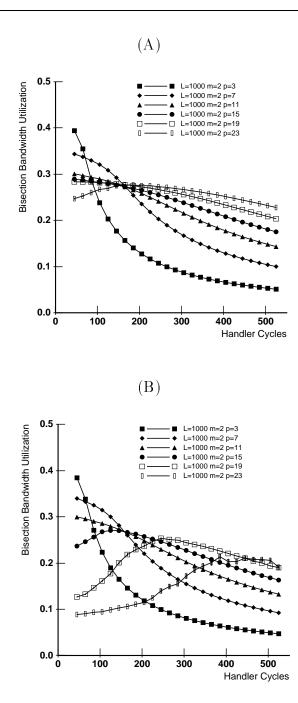

|   |                                   | 4.2.1 Typical Measurement as Bisection Utilization | 127 |  |  |

|   | 4.3                               | Lower Performance is Due to Queue Overflows        | 127 |  |  |

|   | 4.4                               | No Avalanches                                      | 129 |  |  |

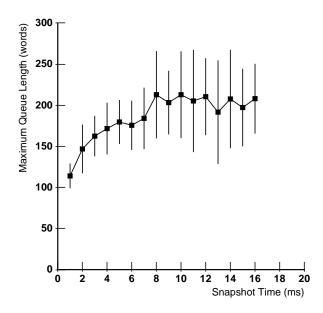

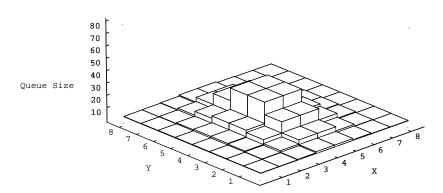

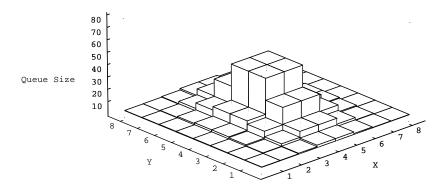

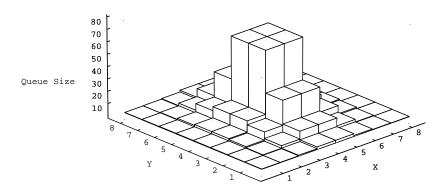

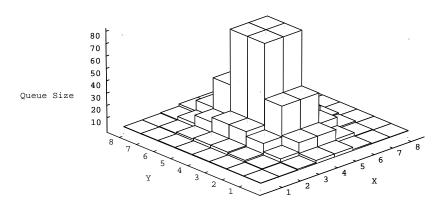

|   | 4.5                               | Queue Size Snapshots                               | 132 |  |  |

|   |                                   | 4.5.1 Comparison to Model                          | 134 |  |  |

|   |                                   | 4.5.2 Sticky Overflows                             | 138 |  |  |

|   | 4.6                               | Adjusting Queue Size                               | 141 |  |  |

|   | 4.7                               | Overflows Occur at the Center of the Machine       | 143 |  |  |

|   | 4.8                               | Effect of Message Length                           | 143 |  |  |

|   | 4.9                               | Effect of the Number of Messages                   | 145 |  |  |

|   | 4.10                              | Request/Reply                                      | 147 |  |  |

|   | 4.11                              | Discussion                                         | 149 |  |  |

| 5 | Mean Value Model of the J-Machine |                                                    |     |  |  |

|   | 5.1                               | Mean Value Analysis Review                         | 156 |  |  |

|   |                                   | 5.1.1 Arrival Theorem                              | 156 |  |  |

|   |                                   | 5.1.2 Exact MVA                                    | 157 |  |  |

|   |                                   | 5.1.3 Multi-Class MVA                              | 159 |  |  |

|   |                                   | 5.1.4 Approximate Mean Value Analysis              | 161 |  |  |

|   |                                   | 5.1.5 Blocking                                     | 162 |  |  |

|   |                                   | 5.1.6 Summary                                      | 165 |  |  |

|   |                         | 5.1.7  | Heads Up 16                                          |  |  |  |

|---|-------------------------|--------|------------------------------------------------------|--|--|--|

|   | 5.2                     | AV M   | odel Results: Fair Router                            |  |  |  |

|   |                         | 5.2.1  | AV Result                                            |  |  |  |

|   |                         | 5.2.2  | Simulation with Unfair Routers                       |  |  |  |

|   |                         | 5.2.3  | Simulation with Fair Routers                         |  |  |  |

|   | 5.3                     | Unfair | Router Model                                         |  |  |  |

|   |                         | 5.3.1  | Queue Size for 16-processor Linear Array             |  |  |  |

|   |                         | 5.3.2  | Unfair Queue Size Predictions for 512-node J-Machine |  |  |  |

|   | 5.4                     | Modifi | cations to AV for Snakes Workload                    |  |  |  |

|   |                         | 5.4.1  | Changes to the AV model for Snakes                   |  |  |  |

|   |                         | 5.4.2  | Snakes Model Predictions                             |  |  |  |

|   | 5.5                     | Discus | sion                                                 |  |  |  |

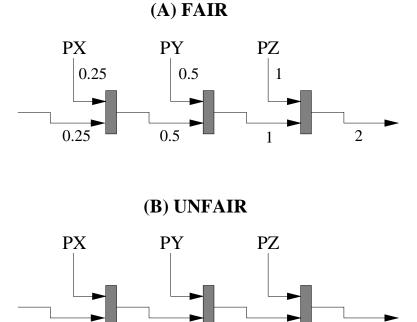

|   |                         | 5.5.1  | Why are the J-Machine's Routers Unfair?              |  |  |  |

|   |                         | 5.5.2  | Architectural Implications                           |  |  |  |

|   |                         | 5.5.3  | More Extensive Validation Needed                     |  |  |  |

|   |                         | 5.5.4  | Explore More of the Parameter Space                  |  |  |  |

|   |                         | 5.5.5  | Larger Machines                                      |  |  |  |

|   |                         | 5.5.6  | Final Challenge                                      |  |  |  |

|   |                         | 5.5.7  | Summary                                              |  |  |  |

| 6 | Architecture Variations |        |                                                      |  |  |  |

|   | 6.1                     | The P  | roblem                                               |  |  |  |

|   |                         | 6.1.1  | Metric                                               |  |  |  |

|   |                         | 6.1.2  | Workload                                             |  |  |  |

|   |                         | 6.1.3  | Machine                                              |  |  |  |

|   | 6.2                     | Descri | ption of Variations                                  |  |  |  |

|   |                         | 6.2.1  | Reference                                            |  |  |  |

|   |                         | 6.2.2  | Request/Reply                                        |  |  |  |

|   |                                    | 6.2.3  | Return to Sender                             | 203 |  |  |

|---|------------------------------------|--------|----------------------------------------------|-----|--|--|

|   |                                    | 6.2.4  | Virtual Channel Flow Control                 | 20  |  |  |

|   |                                    | 6.2.5  | High Water Mark, Alternate Output Priorities | 207 |  |  |

|   |                                    | 6.2.6  | Discussion                                   | 208 |  |  |

|   | 6.3                                | Measu  | rements                                      | 208 |  |  |

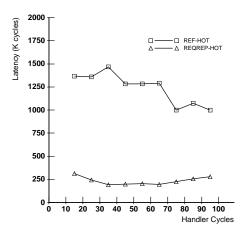

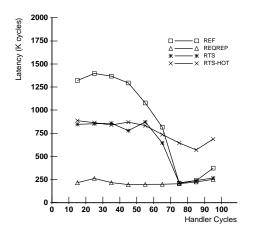

|   |                                    | 6.3.1  | Measurements for REF and REQREP              | 209 |  |  |

|   |                                    | 6.3.2  | Measurements for RTS                         | 210 |  |  |

|   |                                    | 6.3.3  | Virtual Channel Flow Control                 | 214 |  |  |

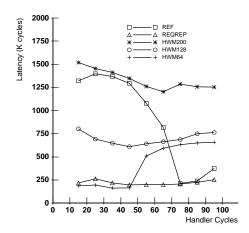

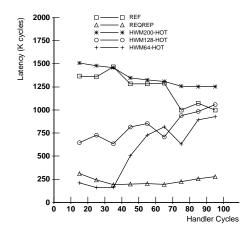

|   |                                    | 6.3.4  | Measurements for HWM                         | 214 |  |  |

|   | 6.4                                | Discus | sion                                         | 216 |  |  |

|   |                                    | 6.4.1  | What's Wrong with HWM?                       | 216 |  |  |

|   |                                    | 6.4.2  | Is RTS that bad?                             | 217 |  |  |

|   |                                    | 6.4.3  | What Other Variations Are There?             | 217 |  |  |

|   | 6.5                                | Conclu | ısion                                        | 218 |  |  |

| 7 | Con                                | clusio | as                                           | 219 |  |  |

|   | 7.1                                | Summ   | ary                                          | 219 |  |  |

|   | 7.2                                | Contri | butions                                      | 223 |  |  |

|   | 7.3                                | Future | e Work                                       | 224 |  |  |

| A | Adve and Vernon Wormhole Model 220 |        |                                              |     |  |  |

|   | A.1                                | Model  | Overview                                     | 22  |  |  |

|   | A.2                                | Chann  | nels                                         | 229 |  |  |

|   | A.3                                | Workl  | oad                                          | 231 |  |  |

|   | A.4                                | System | n                                            | 233 |  |  |

|   | A.5                                | Netwo  | rk                                           | 233 |  |  |

|   |                                    | A.5.1  | Rigid Messages                               | 233 |  |  |

|   |                                    | A.5.2  | Catchup Time                                 | 237 |  |  |

|     | A.5.3                    | Channel Waiting Time | 237 |

|-----|--------------------------|----------------------|-----|

|     | A.5.4                    | Channel Residency    | 240 |

|     | A.5.5                    | Channel Utilization  | 240 |

|     | A.5.6                    | Physical Link        | 241 |

|     | A.5.7                    | Node Queue           | 242 |

| A.6 | Proces                   | sor                  | 243 |

| A.7 | Independence Assumptions |                      |     |

| A.8 | Modeli                   | ing Issues           | 247 |

| Δ 9 | Closin                   |                      | 240 |

# Chapter 1

# Introduction

"Fine-grained message-passing applications running on fine-grained hardware" is the computer architecture philosophy that rallied the construction of the J-Machine at the Massachusetts Institute of Technology (MIT) from 1986 to 1993. The goal of this research effort was to demonstrate that a machine designed to be consistent with this philosophy would lead to greater computer processing throughput for lower cost by using an array of small "Jellybean" chips aggregated into a parallel computer.

When physicists invest years in the design and construction of a synchrotron, they do so with the expectation that the product of the effort will confirm or disprove some theory, uncover some previously unknown anomaly requiring a theoretical revision, or perhaps give evidence for the existence of a new fundamental particle. The investment in the J-Machine was fraction of the magnitude of the investment in a synchrotron, yet the same question forms in both cases: what was *learned* after building the machine?

This thesis provides one answer: despite the attraction of fine-grained message-passing parallel computing, and some attention to architecting a machine for a fine-grained workload, the J-Machine does not run fine-grained message-passing parallel programs well. This is not merely a problem where the design has some performance bug, or is uncompetitive with industry because of more constrained academic budgets and staffing. Instead, the problem is that the most important challenges to the design of such a machine – the scheduling, flow control, and load balancing of fine-grained computations – remain unsolved. This thesis explains why the simple load balancing and flow control methods used in the J-Machine do not suffice. Someone designing another fine-grained parallel computer may wish to read this thesis, to avoid some of the mistakes made in the J-machine's architecture, and overall to

better understand the inherent problems with fine-grained architecture.

## 1.1 Overview

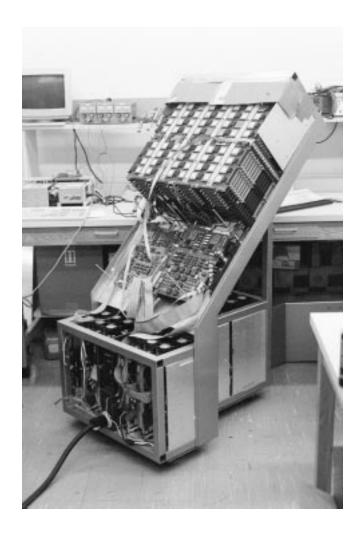

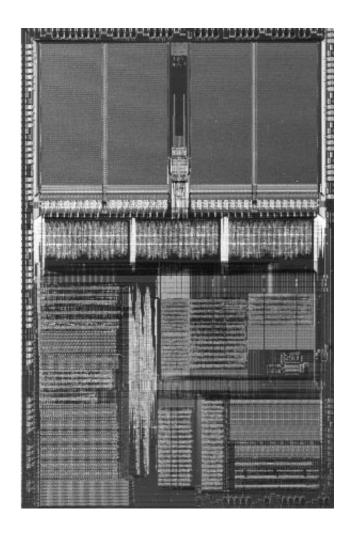

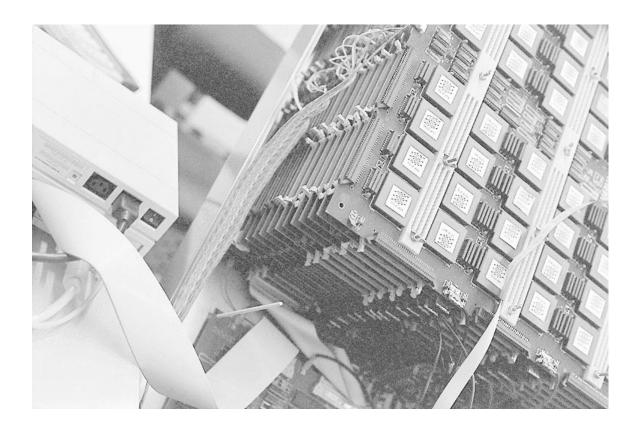

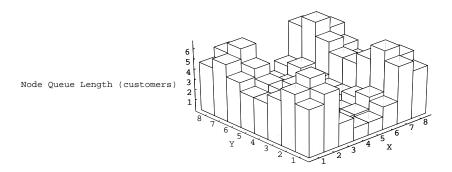

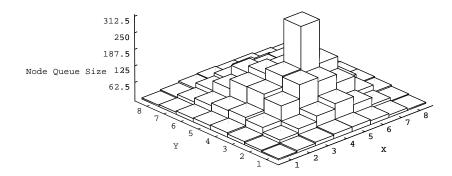

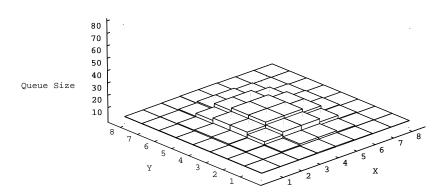

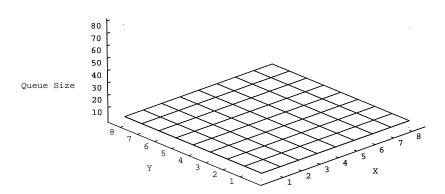

The J-Machine (Figure 1-1) is an experimental fine-grained parallel computer prototype that the Current VLSI Architecture Group built at MIT during the years 1986-1993. This thesis examines the performance of the J-Machine running synthetic workloads and finds that overflows in the processors' message buffers can severely limit the J-Machine's performance. With heavy fine-grained loads, the message buffers overflow on the processors in the center of the J-Machine's mesh.

To analyze the observed behavior, this thesis constructs models of the machine and solves them using queueing theory: one idealized model using classic product-form-solution closed networks, and another incorporating more realistic architecture features with mean-value solutions. The analysis finds that simply using queues to load balance the machine and avoid flow control requires queue sizes larger than those that the J-Machine provides, and that larger queues are insufficient with even a slight amount of imbalance.

Finally, the thesis presents the simulated behavior of some simple hardware load balancing mechanisms that are designed to avoid queue overflows. This work finds that one simple improvement in the J-Machine architecture can help avoid overflows when running workloads that are problematic for the current machine.

The following are among the contributions of this research.

- Methods for estimating and calculating the overflow rates and residencies for closed queueing networks for balanced (Section 3.3) and imbalanced (Section 3.4) random workloads.

- Methods for determining the required hardware buffer size as a function of the number of processors and the number of tasks for closed uniform random queueing workloads (Section 3.3.4).

- A formula for the degree of load imbalance that a closed queueing network can tolerate as a function of the number of processors and tasks (Section 3.4.2).

Figure 1-1: Photograph of the MIT J-Machine with the cover removed. The processor are arranged on a stack of 16 printed circuit boards, with each board holding an 8 by 8 array of Message-Driven Processors. You can see this stack in the upper portion of the pictured machine.

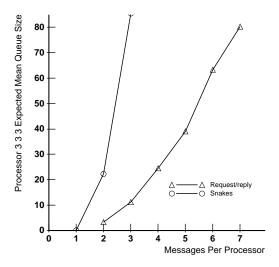

- The observation that a shared-memory workload where every random task request is answered with a task reply is substantially more stable than a workload where the tasks are walking the machine randomly (Sections 3.5.3, 4.10, 5.4.1, and 6.3.1).

- Measurements of the performance of the J-Machine running synthetic models of its intended fine-grained random workloads, and determination of the load parameters where the machine performs predictably and well. In general, best performance is achieved only when the network is lightly loaded (Chapter 4).

- The determination that the workload parameter region where the J-Machine is unable to perform well is coincident with the workload parameter regions where processor message buffers overflow (Chapter 4). In other words, message-queue overflows cause poor J-Machine performance.

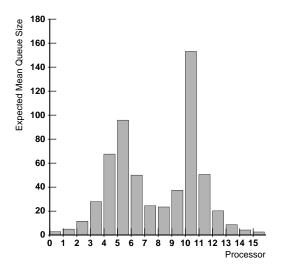

- The observation that the location of the queue overflows within the J-Machine is in the center processors (Section 4.7).

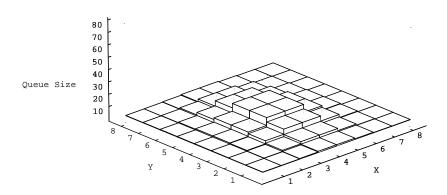

- Modifications for a published mean value queueing model for heavy load traffic (Appendix A) and results from this model, showing that the particular choice of unfair arbitration within the J-Machine routers is responsible for the queues overflowing in the center of the machine (Chapter 5).

- Presentation of the simulated behavior of simple hardware load balancing modifications for the J-Machine. These simulations demonstrate that a high-water-mark based traffic escape for the J-Machine processors performs much better than other load balancing mechanisms which are used in existing parallel computers (Chapter 6).

# 1.2 Background

The following section is an overview to the context, goals, and rationale for this research. It begins with a description of the philosophical context that drove the J-Machine architecture: the notions of fine-grained hardware and fine-grained software, and then describes some of the architectural features of the machine which are important and novel. Then the section describes some of the observations that drove this thesis research: anomalous

and unanticipated behavior when the machine runs heavy fine-grained workloads. Next, the section describes the queueing models that the thesis deploys to explain the observations. Finally, the section describes the evaluation of some of the load balancing attempts to solve the observed problems.

#### 1.2.1 Philosophy

#### Fine Grained Hardware

The J-Machine [DFK<sup>+</sup>92, DCF<sup>+</sup>89, Dal90a, DKN93, Dal90b, DK85, NWD93, ND90, ND92, Cha87] is a fine-grained parallel computer, meaning that the amount of memory on each of its processors is small. In fact, the name "J-Machine" is an abbreviation for the full name of the computer: "Jellybean Machine." On a system with a small amount of memory per processor, the processors can be small, cheap, and plentiful, like jellybean candies. Consequentially, a parallel computer built from these "jellybeans" should be cheap and therefore more likely to be cost-effective [Dal90a].

#### Fine Grained Software

The intended software model for the J-Machine is also fine-grained. Tasks running on the machine would be quickly handled and quickly retired, perhaps taking as few as 10-100 cycles [Dal87, p.135]. The logic behind this short task model is that dividing an application into many small tasks exposes as much parallelism as possible. Furthermore, many algorithms can easily be structured into these small tasks. The J-Machine, being a massively parallel computer, would have the computational power and memory bandwidth required to execute those tasks in parallel.

#### Wire Efficiency

Another component of the J-Machine's philosophy is wire efficiency. Some interconnection networks scale the amount of wire faster than the number of processors (e.g. hypercube); a goal of the J-Machine architecture was to avoid this. This drove the decision to use a

3D topology for the network: one indicative characteristic of this network is the fact that messages traveling from one place in the machine to another never need to "double-back" in space: they can travel by the shortest distance to their destination [Dal87]. However, to allow unstructured workloads (see below) it was decided to provide the abstraction at the lowest levels that the machine is fully-connected.<sup>1</sup>

#### Unstructured Workload

From the moment of their genesis, some parallel computing architecture and programming model design choices are extremely centered on the topology of the interprocessor communication network and on mapping the structured and regular data flow of some applications directly onto the regular network topology. A systolic array is an example of such an architecture. One strength of this topology-centered approach is the mathematical certainty of the associated algorithm analysis. A weakness is that it is limited to specific data flows which are known before runtime.

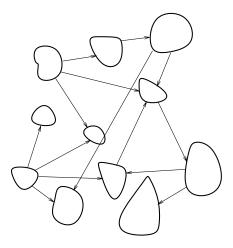

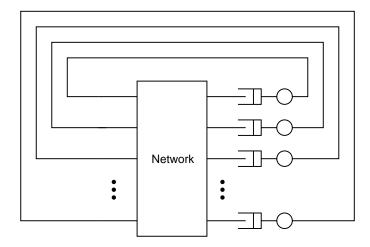

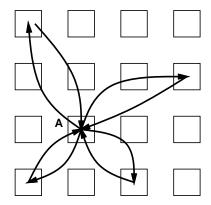

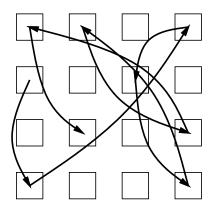

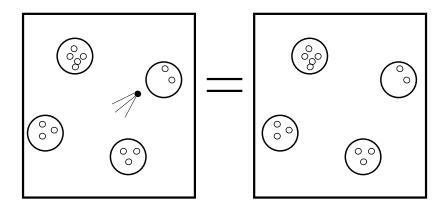

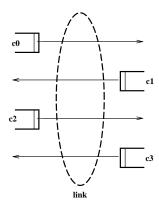

The J-Machine was architected to try to address this weakness. Rather than constrain traffic to a particular structured flow, the primitive operation on the J-Machine is the object-oriented method invocation. The intended workload is a distributed object-oriented program. To initiate remote methods quickly and efficiently, this operation is mapped directly to a hardware primitive: sending an interprocessor message (Figure 1-2). The J-Machine hardware was designed to send messages quickly with high throughput and thereby effectively run parallel objected oriented workloads of unstructured and arbitrary traffic.

Target applications for this sort of machine might be an AI application of agents or actors [Dal92] communicating among themselves, or a virtual reality model with concurrent world modeling and rendering, or a speculative concurrent distributed discrete event simulation. For these applications, asking the programmer to map their applications all as systolic

<sup>&</sup>lt;sup>1</sup>This doesn't seem controversial today: most parallel computer networks provide the same abstraction, that is, the network inputs accept messages from any input for delivery to any output. But there's a tension here: another desirable property of the abstraction is equality (or isomorphism) between all network inputs. The J-Machine's 3D network provides a connectivity equivalence. However, it does not provide equivalence in performance, and this stems from the fact that the mesh, as the only topology that does not require doubling back is also inherently non-isomorphic. Note that there are other networks with provably efficient space-mapping (but don't have the no-doubling-back property) but can provide isomorphic interfaces (e.g., Leiserson's Fat Tree [Lei85, L<sup>+</sup>92]).

Figure 1-2: Programming model for the J-Machine: a cloud of distributed objects, communicating via message passing.

flows would be too burdensome. As a consequence, we tried to build a machine that would be able to run an unstructured workload well.

#### 1.2.2 Hardware

#### Wormhole Network

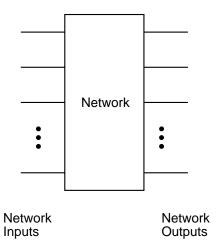

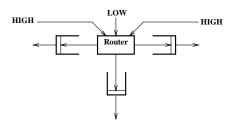

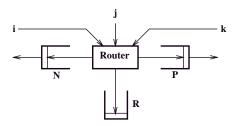

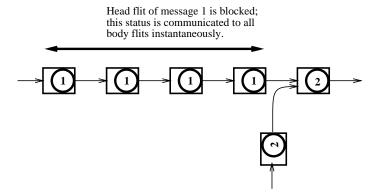

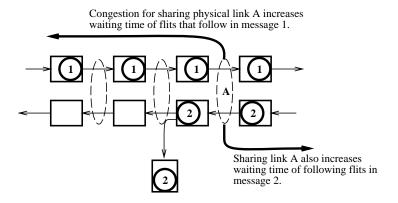

The network of the J-Machine was designed to support the philosophical goals. It is a wormhole network with excellent load vs. latency characteristics, as demonstrated analytically and with simulation, running various random and other traffic flows [Dal90c]. The routers are simple with little multiplexing and buffering. This makes them fast and cheap. Dally showed that wormhole routers guarantee progress (freedom from deadlock and live-lock) because the link-level blocking within the network cannot form cycles. As long as the destination processors obey the *consumption assumption*, that is, the processors guarantee that they will remove any arriving message from the network, the acyclic blocking dependencies can not form deadlock (Figure 1-3).

Figure 1-3: The wormhole network presents an abstraction of progress-guaranteed messagedelivery from inputs to outputs, as long as the outputs obey the consumption assumption.

#### Message-Driven Processor

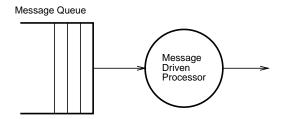

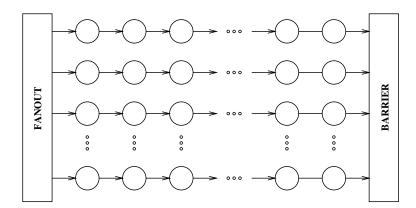

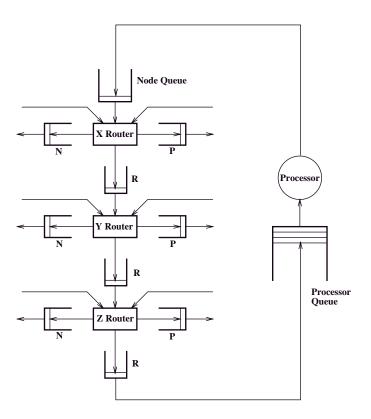

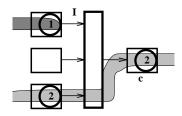

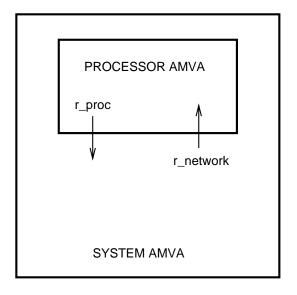

The processors in the J-Machine were also designed to support the goal of running unstructured fine-grained software well. The processors are different from conventional processors: they are Message-Driven Processors (MDPs) [Dal87, p.183]. The difference is in the way that tasks are initiated. While most current parallel computers are fast conventional commodity CPUs that are connected with some communication network (in many cases, mesh-based networks which are siblings to the J-Machine's network), the MDP is a hardwired custom processor, dedicated to its tasks. With the conventional processors in most parallel computers, the initiation and management of tasks is mostly under program control; occasionally, it is interrupt-driven. In the MDP, the management of tasks is hardwired as First-In-First-Out (FIFO) service of the message queue (Figure 1-4). The MDP is designed to repeat the sequence of initiating, executing, and suspending tasks, and it is only this task handling scheme which works well on the MDP. Fixing this task loop into hardware shaves a couple of instructions off the initiation and suspension of tasks – which is important if tasks are themselves only tens of cycles long.

In addition to being designed to run fine-grained software well, the MDPs are themselves

Figure 1-4: In the MDP, there is a direct correspondence between tasks and messages. The MDP hardware implements FIFO service of an incoming message queue. It is overflows of this pictured message queue, upstream of the processor, which are the subject of scrutiny in this thesis. These queues are fixed size and 512 words long.

fine-grained: they are fine-grained processors.<sup>2</sup> A fine-grained processor is one with a small amount of local memory; each MDP has about 10 KByte of memory on-chip and 1 MByte of slow off-chip DRAM. The rationale behind making a fine-grained machine is that the marginal cost of additional processors is low, so they should be scattered liberally around the machine. Note, though, that this fine-grained architectural choice comes at a cost; it implies<sup>3</sup> that memory-implemented hardware features and particularly the message queues will be small. This results in another burden or constraint for flow control, load balancing and task scheduling. This thesis will show that in the J-Machine, this additional burden becomes the most critical performance issue.

#### J-Machine

The J-Machine was built by a team of MIT graduate students and staff working with Intel Corporation engineers to produce the MDP chip [DFK<sup>+</sup>92]. This team completed a 1024-node machine at MIT in 1992 and brought up the system's micro-kernel, called COS-

<sup>&</sup>lt;sup>2</sup>Fine-grained software by our definition involves applications made up of short (10-100 cycles) tasks. A fine-grained parallel computer is one where the processors each have a small amount of memory; or in other words, where the memory is divided finely over the processors.

<sup>&</sup>lt;sup>3</sup> "Implies" is perhaps too strong a word: rather it strongly biases (if one isn't awake at the wheel) the design choices in a way that makes memory implemented hardware features small. In the case of message queues, one could (really, should) design them so that their overflows smoothly flow into other nearby processors, so that capacity constraints do not impose such stark performance penalties.

MOS [HTD], and created the compiler for Concurrent Smalltalk (CST) [CD88a, CD88b, Hor89, HCD89], the system's programming language. Consistent with the philosophy of the machine, CST offered a programming abstraction far from the details of the machine, focused principally on letting the programmer express fine-grained object oriented programs.

The effort was extremely successful. With 1024 nodes, the J-Machine is one of the largest academic parallel computers ever built. The machine actually runs applications and is extremely reliable.<sup>5</sup> With the success of the first prototype, two additional J-Machines were built: one for Steve Taylor's parallel programming research group at Caltech, and another for Argonne National Laboratories. Although some aspects of the machine, such as the clock speed, were not competitive with other commercial processors of its time, other aspects of the machine, such as the network, were competitive.

## 1.2.3 Anomaly

#### J-Machine Evaluation

Various applications were written for the J-machine. A number of synthetic benchmarks tested the throughput of the network, the agility of message passing, the ability to perform sorting, and the speed of barrier synchronization [NWD93]. For the most part, these synthetic benchmarks were hand-written, occasionally the result of the programmer working strenuously to overcome the MDP's hard FIFO coding model.

Two applications were written in CST: a ray tracer [Fat92], and a traveling-salesman-problem search [Kan93]. The Caltech research group produced a C compiler for the J-machine that includes message-driven language extensions, called Message-Driven C (MDC) [Mas94, MZT93, MT93] and ported a number of applications to the machine.

All these applications were coarse-grained, in contrast with the initial goals of the project to build a machine for fine-grained software. That is, the number of cycles that tasks in

<sup>&</sup>lt;sup>4</sup>Later, the compiler team add programming primitives to allow the programmer control over the location of objects and method invocations.

<sup>&</sup>lt;sup>5</sup>At the time of this writing, the current J-Machine at MIT, which consists of 512 processors, has been running without any hardware failures for over 2 years. This is great, because replacing a processor in the center of the J-Machine is as tedious (and unpleasant) as simultaneously replacing the head gaskets of eight automobiles [ND90].

the applications took to execute might be measured in the hundreds, rather than tens. The applications tended to use the network lightly. For the CST applications, it was surprising that the programmers chose to try to make the applications as MIMD-like as possible, trying to minimize communication.

For the MDC applications, Maskit observed that using the J-Machine, the overhead for communication in the network was an insignificant component of application run time [MT93]. Partly, this was because the MDC tasks were so heavy-weight that it was impossible to use the network heavily. But also, this was because the overhead for injecting and receiving a message on the MDP actually was low, as the J-Machine designers had intended.

#### Fine Grained Workloads

Still, though, with these application programs being coarse grained, the performance of the J-machine running fine-grained applications was not being studied.

One of the goals of this research has been to begin to study the ability of the J-Machine to run its intended fine-grained workload.

#### Network Saturation

Waldemar Horwat, the author of the CST compiler, empirically determined a communication-to-computation ratio for some small microbenchmarks written in CST. This ratio is the average amount of network traffic produced for a unit amount of computation. Based on this ratio, he concluded that when the size of the J-Machine exceeded 300 processors (the "Horwat Limit" for the J-Machine), the amount of communication traffic produced by the machine would exceed the capacity of the J-Machine's bisection [Hor89, p.110]. That such a limit exists makes sense because with the parallel computer being cube-shaped, the bisection of the machine grows only as  $N^{\frac{2}{3}}$ , slower than the number of processors N. Horwat concluded that in order to use machines larger than 300 processors, the programmer or some system process would need to map the application to the machine in a way that exploited locality and reduced the bisection bandwidth requirements of applications.

However, this thesis takes the position that if the programmer does not explicitly reduce

Figure 1-5: When the MDP's are combined with the network, the resulting system appears to have cyclic dependencies.

bisection pressure, the application should still be able to run well, albeit at the network-limited rate.

Our J-Machine laboratory prototype consisted of 1024 nodes, and the MDP has network addressing bits that would enable the hardware to scale to as many as 32K nodes. These machine sizes are larger than the Horwat Limit.

Another goal of this research has been to study how the machine responds to the situation when the network is saturated by the application, in the region beyond the Horwat Limit.

#### Is the System Flow Dependency Graph Acyclic?

The wormhole network guarantees that messages make progress to their destination because of the lack of cyclic constraints in the link-level flow control dependence graphs and because of the consumption assumption. However, when one looks at the whole J-Machine system (including the MDPs) the consumption assumption appears to be violated. If the message queues filled, the processor would not be able to take in any new messages from the network

(Figure 1-5). Another way of looking at this is to note that the flow-dependence graph for the whole J-Machine (not the network in isolation) appears to include cycles of dependent and finite message buffering with non-adaptive routing. These dependency cycles run through the processors, into the network, and back into the processors.

Another goal of this research has been to investigate the consequences of this apparent violation of the basic network-progress assumptions.

#### Processor Message Buffers

The designers of the MDP recognized the potential violation of the consumption assumption, and they tried to avoid it by making the message buffer on the MDP relatively large (512 words). Our expectation was that by making this queue large, it would almost always be empty. By being empty, the processor would implicitly obey the consumption assumption. But, while the buffer is large, it is still finite-sized. So, there is some chance that it can fill.

#### Processor Queue Overflows

If the message buffer fills, the consumption assumption is violated, and the machine can deadlock. To provide freedom from deadlock, the designers of the MDP added a message-buffer-overflow-trap feature for the MDP. The trap handler for message overflow empties the buffer to some alternate storage, to make room for more messages - so that the processor can comply with the consumption assumption. During the trap, the incoming network queue is temporarily blocked, so that the system does not lose any messages.

However, it turns out that the trap handlers for message buffer overflows is very slow, so much so that the performance penalty that an overflow trap exacts on the system is costly. With some design attention, the trap handler could have been much faster. However, the designers expected queue overflows to occur rarely, and so spent little attention on making the overflow handler fast.

Implicit in the inattention that this aspect of the architecture received—basically, making it possible for a processor with a full-queue to self-rescue itself, while not making it fast—is an assumption that overflows of these queues would be rare.

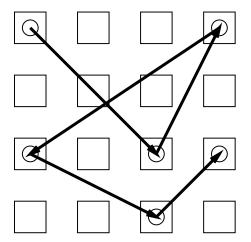

Figure 1-6: A task makes random jumps around the machine. A large number of these tasks are created in our simple workload.

But how rare is rare?

The final goal of this thesis research is to provide a method for predicting the frequency of queue overflows in the J-Machine and in similar systems.

#### A Simple Experiment

I decided to try a simple experiment: measuring the performance of the J-Machine running a heavy-load, synthetic, fine-grained workload. This synthetic workload is simple: a number of tasks are created on the machine and distributed over the processors. Each task demands a small amount of computation from the processors (40 cycles or more, controlled by a spin-loop), picks another processor on the machine uniformly at random, sends a message to create a similar task on that random processor, and then suspends (Figure 1-6). In effect, the workload consists of a large fixed number of tasks making random hops over the processors in the machine.

One might reasonable intuit that this workload should perform well on the J-Machine: it is uniform and simple; the number of tasks in existence at any moment is constrained (there

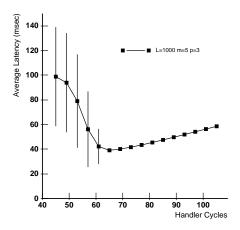

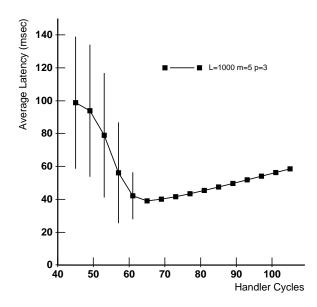

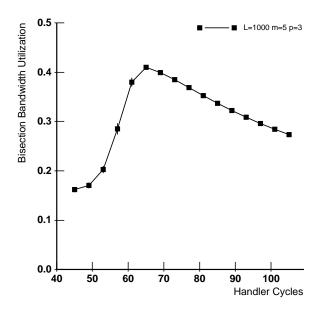

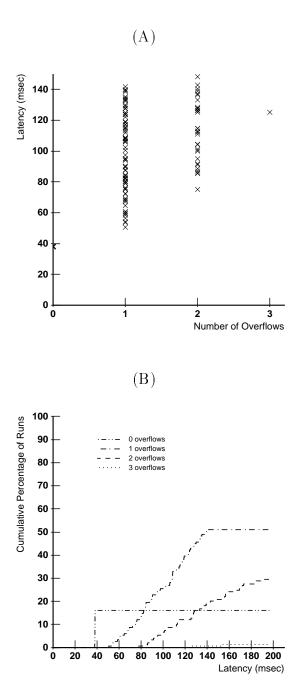

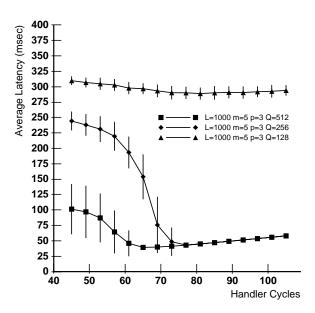

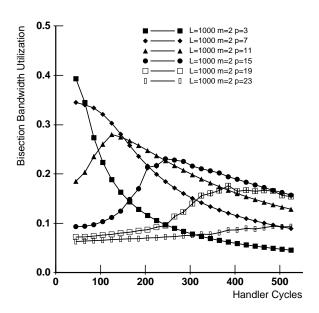

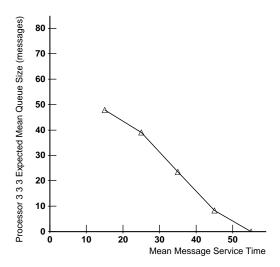

Figure 1-7: Moving into the fine grained domain (shorter task handlers), the average latency and variance of the simple benchmark increases sharply.

is no explosion of parallelism<sup>6</sup>), so it is a sort of best-case model of the type of oblivious parallel program for which the machine was designed. It this intuition correct?

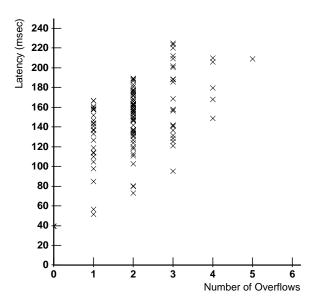

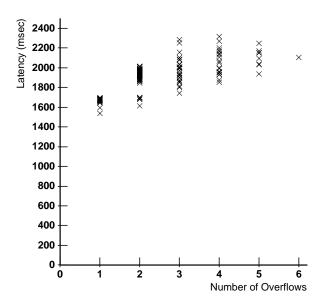

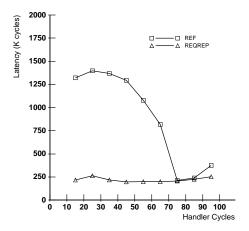

#### Sharp Drop In Performance

The measured performance of this workload (see Figure 1-7 and Chapter 4) exhibited surprising results. Each point on the graph shows the measured latency of the workload averaged over several independent runs. As the message handler time is reduced (moving to the left along the curve) the workload is becoming more fine grained. And as the workload is becoming more fine-grained – the intended workload for the J-Machine – the latency increases sharply, with high variance in the measurements. This sharp increase in latency occurs at the point when the network saturates. Ideally, the performance would level off as the machine approached saturation. But this is not the case on the J-Machine. Why is this sharp performance loss occurring?

<sup>&</sup>lt;sup>6</sup>See Blumofe and Leiserson [BL93] for more about the size problem.

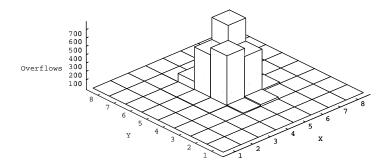

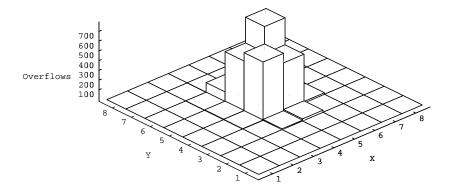

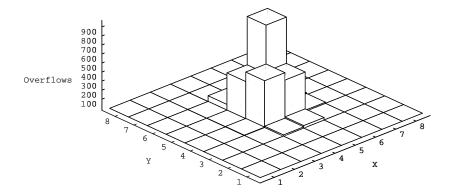

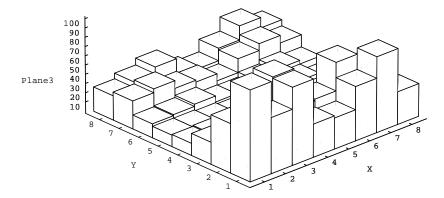

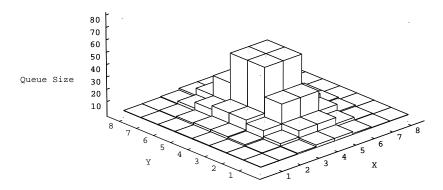

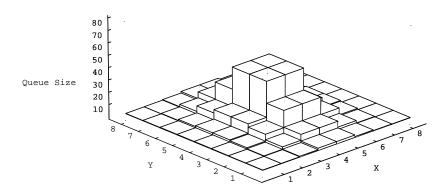

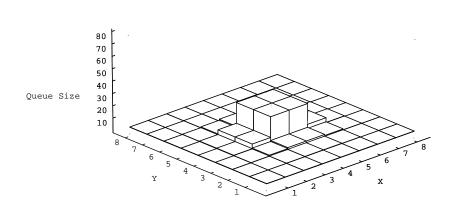

Figure 1-8: The cumulative number of overflows vs. processor X-Y position for the 4th processor board in the J-Machine after many runs of the synthetic workload. All of the overflows occur in the center processors.

#### Drop In Performance Due Queue Overflows

Further observation of the J-Machine showed that the reason for the drop in performance was due to the onset of processor message queue overflows.

In this heavy load region and running this simple synthetic workload, the implicit architectural assumptions that this queue would rarely overflow proves to be false.

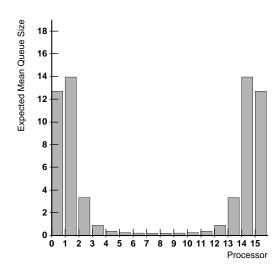

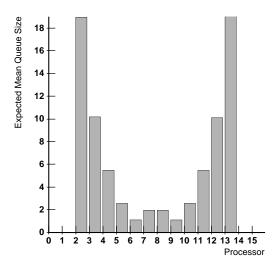

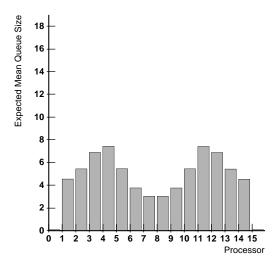

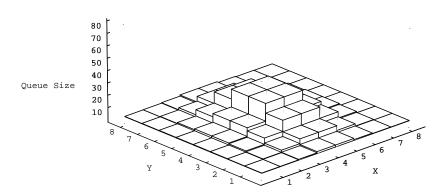

Another surprising observation is that for this workload, overflows occurred in the processors near the center of the machine (Figure 1-8). Overflows never occurred on the edge processors.

This thesis uses a mean value model to demonstrate that the overflows are occurring in the center of the machine because of unfairness in the machine's routers.

## 1.2.4 Analysis

Observing the actual behavior of the J-machine raises some questions. How well does the J-Machine run its intended fine-grained workload? What happens when the network on the J-Machine becomes saturated? Is the implicit violation of the consumption assumption important? Why do queue overflows occur, and why do they occur in the center of the machine?

How can these questions be answered?

#### Using Queueing Theory

Classic queueing theory comes to mind immediately. This theory is "classic" because the body of this research is several decades old, well-established, and thoroughly deployed. The mathematical techniques of classic queueing theory rely largely on ergodic properties of continuous-time, discrete-state Markov models. The theory includes a number of results for queueing networks, which are systems of servers traversed by customers. By restricting the server and routing behaviors to particular mathematical ideals, e.g. FIFO non-preemptive exponential service disciplines, the queueing networks yield elegant solutions for the equilibrium probability distribution of the configurations of customers on servers. These probability distributions allow one to solve for throughputs, queue size processes, and so on.

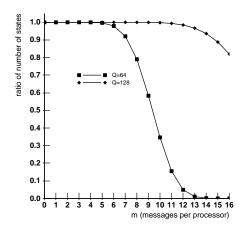

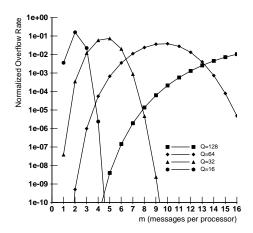

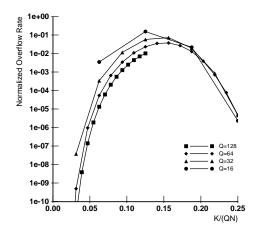

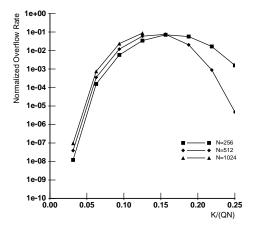

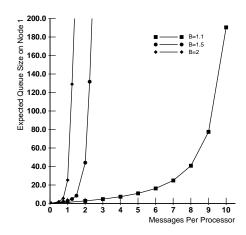

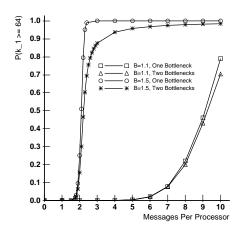

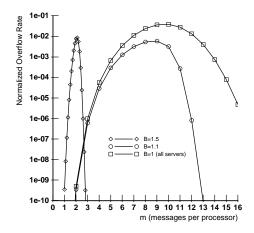

One drawback of classic queueing theory is that it does not allow for blocking behaviors in the queueing networks. Because blocking turns out to be such an important effect in the J-Machine (and in any parallel computer), the applicability this theory is limited. Still, one can assume that network effects are unimportant, and study the dynamics of message traffic on large machines like the J-Machine. This is done in Chapter 3, constructing a model of this synthetic workload on the J-Machine as a classic closed queueing network, and generate techniques for determining the expected rate of overflows for this workload for both balanced and imbalanced workloads. Chapter 3 also derives relations for the required queue size as a function of the number of processors, the number of tasks, and the degree of imbalance. Based on these results, The chapter finds that when the workload is balanced and uniform, the size of the MDP's buffers is barely adequate for short messages (which consume buffer space more quickly).

In addition, the chapter shows that for imbalanced workloads, well-known queueing dynamics lead to massive task accumulations at slow processors when relationships among the number of processors, the number of tasks, and the degree of imbalance exceed certain thresholds.

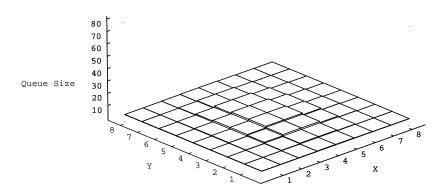

#### Mean Value Models

Unfortunately, because the classic queueing models do not account for network blocking, they cannot explain why overflows occur in the center processors of the machine. Fortunately, approximation techniques exist for modeling closed systems of processors connected by a deterministically routed wormhole network. These techniques are based upon mean value models, which are numerical methods which ignore the higher moments (e.g., variance) and solve for the mean (average) values of traffic rates, accumulations, and waiting times in queueing networks. Inexact approximations exist for adding blocking, and particularly wormhole routing, to mean value models. In Chapter 5 and in Appendix A, I use these approximations, implementing a solver and improving it for the particulars of heavy load traffic on the J-Machine. These techniques yield a model which is only qualitatively correct; the accumulation of errors from the many approximations and the particular choice of studying the heavy load domain make it difficult to get quantitatively correct traffic models.

The mean value model shows initially that overflows should occur on the edges of the machine. With some thought, it becomes apparent that this is due to a discrepancy between the fairness of the routers in the first version of the model vs. those in the J-Machine. A modification to the mean value model is developed for the J-Machine's unfair routers. This new model shows that queues overflow in the center of the machine.

# 1.2.5 J-Machine Improvements

One might question whether the J-Machine has fundamental design problems. It is incorrect to argue that the J-Machine is severely flawed: the fact that it runs applications and various small benchmarks counters such an argument. However, there clearly is room for improving the J-Machine, particularly for this heavy-load, fine-grained workload, to prevent the dramatic performance loss due to queue overflows. The "obvious" solution – simply increasing queue sizes – is not the best solution: this adds to the cost of the machine because the

increased memory on each processor for the larger queue is multiplied by the large number of processors in the parallel computer. Furthermore, it does not help with the case of the imbalanced workload, with its large accumulation of traffic. So although adding memory might help, it does not completely address the problem.

Because queue overflows are not infrequent, it might help performance if queue overflow handlers were faster. However, any slowdown at all for overflow runs the risk of creating a local hot spot in the machine, triggering the bottleneck dynamics which lead to further massive traffic accumulations at that hot spot.

#### Request/Reply

If the traffic pattern for tasks is modified from a basic random walk to one following a requestand-reply pattern (similar to the traffic one might find in a shared memory machine), the queueing behavior of the workload is extremely stable. Each of the four core research chapters briefly discuss this, looking at this phenomenon using classic queuing models, J-Machine measurements, mean value analysis, and simulations. All find that request-and-reply is more stable than the random walk.

Since the request-and-reply routing is a characteristic of shared-memory machines, and since the J-Machine does not require messages to follow the request-and-reply pattern, in some sense the instability of the J-Machine workload stems from it not being a shared-memory machine.

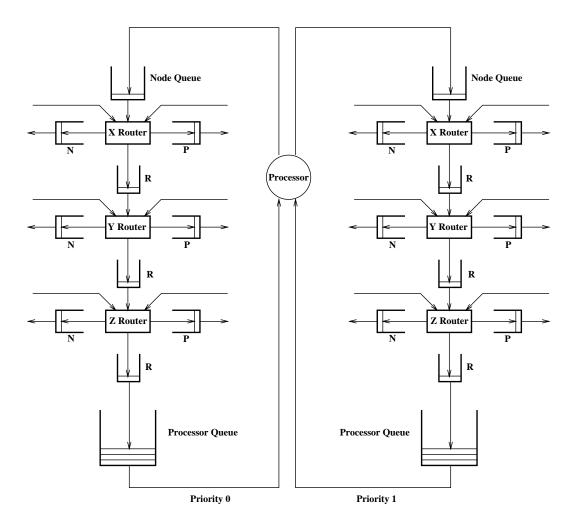

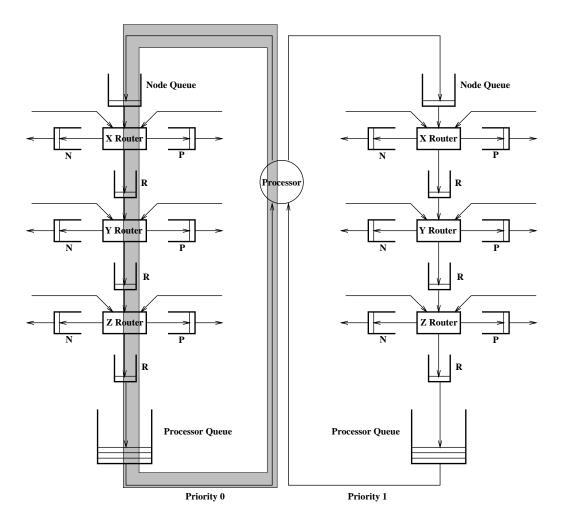

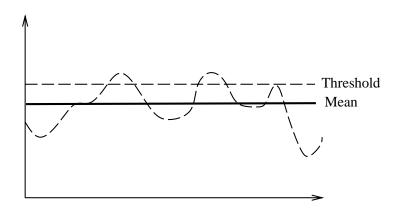

#### High Water Mark, Alternate Output Priority

As an alternative to these solutions (increasing queue size, speeding the overflow handler, or changing to a shared-memory message pattern), Chapter 6 investigates methods in which the hardware performs some primitive heuristics to attempt to balance the load. One heuristic involves designating a high-water mark threshold in the message queue, and automatically switching the processor to send output traffic on a high-priority network when the quantity of accumulated traffic crosses that threshold. In this way, the hardware automatically responds to the danger of a buffer overflow by giving the processors output channel a boost in priority

and potentially throughput, allowing the processor to reduce the size of its input queue by serving traffic faster.

In the heavy-load traffic domain, simulation shows that this technique is sometimes effective in preventing queue overflows.

## 1.3 Related Research

#### 1.3.1 Other Architectures

#### Alewife

Alewife uses a single network and faces the possibility of deadlock due to the protocol's backward-coupling of blocking from the network inputs to the network outputs [KJA<sup>+</sup>93]. Alewife prevents deadlock by using a countdown timer on each processor that resets any time the network output at a processor makes progress. If the counter reaches zero, the processor takes an interrupt and manually drains all arriving network traffic into memory, breaking deadlock. This timer-based solution is a different way of detecting deadlock than the J-Machine's queue overflow trap. Neither the J-Machine nor Alewife's solution actually detect the deadlock – instead, they both detect supersets of the deadlock condition. A solution with more detection precision might be a timer that resets any time the input or the output makes progress. Kubiatowicz has reported that the Alewife team did not find these deadman timeouts to be problematic [Kub95]. This is probably a result of a combination of factors. First, the Alewife machines that have been actually constructed have been small – 32 to 128 nodes; in contrast, the J-Machine prototype has 512 to 1024 nodes. This means Alewife is unlikely to saturate its network. Second, the Alewife group has concentrated on actual application benchmarks, while in this thesis the focus has been on synthetic benchmarks that try to characterize the J-Machine's overflow problem. Third, the Alewife machine mostly runs shared memory types of applications (though there are some exceptions, notably Chong's work [CA96] that contrast shared memory and message passing implementations of applications); as I report in Sections 3.5.3, 4.10, and 5.4.1, the request/reply sort of traffic is substantially more stable with respect to queue sizes than is the synthetic message passing workload (which I call "Snakes"). Despite this, for shared

memory machines this thesis work is relevant (and the equations in Section 3.5.3 should be considered), particularly if they are large in size and definitely if they also support message-passing.

#### **DASH**

The architects of the DASH machine [LLJ<sup>+</sup>92] also recognized the potential for deadlock, and so partitioned their protocol into requests and replies, onto two decoupled virtual networks – a solution also used by von Eicken et. al. in Active Messages on the CM-5 [vECGS92]. In DASH, the protocol does allow for "request" messages to spawn other "request" messages - which then creates the possibility of deadlock. However, if the shared-memory protocol engines detect that they cannot make progress on their network inputs, they start to send negative acknowledgments back to the requesters, forcing those requesters to perform their traffic in a deadlock-free strict request/reply fashion. This thesis applies in the sense that for larger DASH-style machines which might saturate the bisection and have heavier and larger network traffic loads, one might ask how the queue sizes and possibilities of deadlock arise. The thesis provides some answers.

#### Cilk (CM-5)

Blumofe et. al.'s Cilk programming system [BJK<sup>+</sup>95] is more aggressive about using the two virtual networks that the CM-5 provides. This stems from a sophisticated approach to scheduling; see Blumofe's work [BL93] on scheduling multithreaded computations. Brewer and Kuszmaul also show [BK94] how to improve Cilk's substrate Strata, observing the formation of bad patterns of traffic and showing how to get good throughput on high-volume all-to-all types of communication patterns.

#### Cray T3D

Kessler and Schwarzmeier report [KS93] that the Cray T3D (and T3E) uses wormhole routing. The design is based upon the routing used in the J-Machine [Dal90a]; however, the T3D network has a torus topology so that it requires the extra deadlock-breaking virtual

channels that Dally invented [DS87]. To fight the isomorphism-loss (noted by Adve and Vernon [AV91, AV94]) that the deadlock-breaking virtual channels cause, Scott and Thorson [ST94] demonstrate using simulated annealing to optimize the virtual channel routing assignments to balance channel traffic. The lack of isomorphism in the J-Machine's mesh topology is one of the causes of traffic imbalance; even Scott and Thorson's solution retains some nonisomorphism, however, it is so slight and the T3D network is so fast that it's hard to see the traffic imbalance being problematic.

With the T3D being a coarse-grained hardware implementation (in contrast to the J-Machine, which is fine-grained) the network queues are more than 10 times larger than on the J-Machine; the methods in Chapter 3 show that this is sufficient to prevent overflows in balanced loads. With imbalanced loads, however, this may not be sufficient.

Dally reports [Dal93] that the T3D network implements the return-to-sender algorithm (RTS) that Chapter 6 finds to be ineffective in balancing the load. RTS may be effective for load-imbalance due to burstier traffic. Demonstrating this would be an interesting result. Chapter 6 suggests that the RTS algorithm needs to be combined with some sort of backoff and flow control, but leaves the design of such a backoff scheme as further work.

#### Chaos Router

Konstantinidou and Snyder's Chaos Router [KS91] uses adaptive routing with random misroutes that is provably free of livelock and deadlock. Note, though, that their network analysis, like the ones for the J-Machine's network, is for an *open* network; that is, they study the network in a context where the consumption assumption is made. It is not immediately apparent how their network behaves in the closed (e.g., including processors in the system) context. Probably, with only a small modification, this can work as a seamless solution to dealing with queue overflows: a true fine-grained approach. Study of this network is likely to be fruitful, and the analytical modeling process aesthetically rewarding. As Karamcheti and Chien point out [KC94], one downside of the Chaos approach (and any adaptive network solution) is the loss of guarantees of message order arrival, but asking for this if the primary metric of quality is seamless overflow handling may be asking too much.

#### EM-X

Kodama et. al. report [KSS+95] that the EM-X parallel computer has transparent concurrent spilling and restoring of the network output buffer to and from an off-chip message buffer. This too is an elegant and seamless way to increase effective queue size; and its inclusion shows that the architects of the EM-X recognize the problem of queue capacity constraints. The size of the EM-X queues are not reported; the methods in Chapter 3 may add some insight into proper sizing of these queues.

#### Chien's CONCERT

Chien, one of the early J-Machine team members, has published a number of excellent papers closely examining interaction of network design and programming. This work comes from his implementation, with Karamcheti and Plevyak, of the Concert programming system [CKP93]. With Karamcheti, he highlights [KC94] the effect of network design decisions on end-to-end properties that programmers find valuable: flow control, in-order delivery, and reliable transmission. The J-Machine network provides in-order delivery and reliable transmission (though not fault-tolerant). However, it does not provide adequate flow control mechanisms. Karamcheti and Chien report [KC94] that providing these properties in software (rather than in the network) can be expensive. Aoyama and Chien [AC94] report the cost of implementing these features in hardware.

Kim, Liu and Chien propose [KLC94] that a good solution to this problem is "Compression-less Routing" - a way to speculatively inject wormhole messages, but with clean flow control feedback from the network and still allowing adaptivity. One nice observation is that the network can provide selectable in-order guarantees (by restricting the route) to allow the programming system to make the tradeoff between adaptivity and in-order delivery. Note that this study is with the network in an open context (in contrast to the research in this thesis). Within this context, the problem of deadlock formation is strictly within the network (rather than involving the processors or the application). They report that deadlocks actually occur infrequently. Developing an analytical reasoning behind this observation would be interesting.

#### Others

Brewer et. al. propose [BCL+95] moving the management of the queueing to the application, proposing an application-network interface called RQ for "Remote Queues." This is in contrast to the J-Machine, which fixes queue and communication policy in hardware. Given that general universal flow control solutions are elusive, allowing the application more control with clean interfaces is a good approach. Wallach et. al. [WHJ+95] propose another clean interface to the network called Optimistic Active Messages (OAM). In their scheme, the processor optimistically tries to send messages, but if network backpressure is encountered, the message is sent to memory. This differs from the J-Machine, where the processor gets caught by network backpressure, and is forced to do nothing but take SEND faults and spin until the backpressure is resolved. Wallach et. al.'s scheme has the desirable property of breaking the progress deadlock, and is probably the right model for designing a network interface (simply designing the network interface to allow the programmer to *choose* to use OAM is a giant-step from the J-Machine.)

The work in this thesis is less normative than the research in Brewer et. al. and Wallach et. al.; rather than proposing new solutions (other than the load balancing proposal in Chapter 6) this research reflects a preference and, with us having spent the time and money to build the machine, an *obligation* to analytically study of the existing J-Machine. Furthermore, the J-Machine architecture, by hard-wiring queueing and interface policy, is resistant to being used as a platform for normative research (Though Spertus [SD, S<sup>+</sup>93, SD95] obtained some results). But the exclusion from the ability to do normative research is not just a question of hardwired policy, this is also a general downside of doing computer architecture research by building hardware.<sup>7</sup> Sigh. One can't be all things.

# 1.3.2 Queueing Models

Most queueing theory is based upon continuous time, discrete state Markov models; Klein-rock provides [Kle75] the classic introductory text. The tools for queueing networks is based up early work by Jackson and Gordon and Newell [Kle75] who gave now well-known product form solutions to equilibrium probability distributions for expected latency, queue size, and

<sup>&</sup>lt;sup>7</sup>Things can get pretty bad: suppose the chip doesn't work!

throughput at the nodes of a network given exponential random service time distributions and random routing decisions. Basket et. al. [BCMP75] extended this work to a general solution for a more (though not fully) general set of service distributions. Chapter 3 primarily requires only the simpler Gordon and Newell solution for the closed queueing network and give ways, based upon that solution, to estimate overflow rates as functions of the number of customers and queue size. The challenge is in overcoming an intractably-large state-space distribution; Buzen [Buz72, Buz73] provided some recurrences which help in this problem.

Section 3.5.3 does use Basket et. al.'s solution (called BCMP) to attempt to study why the Request/Reply pattern of communication is so much more stable than the unconstrained "Snakes" traffic. Unfortunately, the formulation in terms of BCMP for Request/Reply does not have the simple solution as does the formulation in terms of the Gordon and Newell network for Snakes; and for this reason the analysis of Request/Reply remains for future work.

Determining the rate of queue overflow is essentially one of determining higher moments of the queue size random variable. McKenna and Mitra introduced [MM84] a method involving an integral representation of the BCMP solution that yields estimates of the higher moments. This method is not considered in this thesis; one possible limitation is that the method applies only to moderate-utilization domains and only in the case where each class of traffic includes one "think" node – perhaps implicitly making the network an open network. However, the very simple traffic patterns in this thesis might allow simple solutions using McKenna and Mitra, and shed some light on the Request/Reply vs. Snakes question. This remains for future work.

#### Stability

Note that the term "stability" in the context of this research is describing the volatility of the queue size process with respect to the buffer size, examining the implicit load balancing that comes with randomly selecting the destination node of communication patterns. In the context of open networks, stability refers to the long-term behavior of the queue size process, whether the achieved average service rate of all nodes is higher than the rate of incident traffic. Stability of this sort is trivial to determine in a classic exponential server

network [Kle75] but in the context of routing and blocking decision processes is a subject of active research; see, for example Bertsekas et. al. [BGT95] or Dai and Weiss [DW94]. Coffman et. al. study [JGG+95] the asymptotic stability of first and higher moments for a rotating ring in an open-network context; the effort required for this result is impressive.

#### Queueing Networks with Blocking

Classic queueing networks (those solved by Jackson, Gordon and Newell or BCMP) do not allow for blocking effects. When these classic networks are applied to study the J-Machine in Chapter 3, the blocking and routing effects are being ignored. Others make similar assumptions; see, for example, Harchol and Black's application of queueing theory to study routing on square arrays [HB93].

There is a moderate sized literature on the incorporation of blocking models into queueing networks. Perros [Per94] provides a text for this topic, and Onvural provides a survey [Onv90] for closed networks. One of the items of note in Onvural's survey is a taxonomy of blocking mechanisms; the behavior of a queueing network varies a great deal with the mechanism. The J-Machine's link-level blocking is a simple Blocked-after-Service (BAS) mechanism; Onvural shows this mechanism is strictly free from deadlock if the total number of customers in the network is less than the smallest blocking cycle. On the J-Machine, a large parallel computer, the number of customers (which correspond to messages or tasks) far exceeds the size of the smallest cycle. This is why the J-Machine has mechanisms to detect potential deadlock situations and respond to them (in effect, this detection changes one of the servers in each cycle to be non-BAS and breaks the deadlock).

The techniques for analyzing blocking networks did not prove to be as useful for this thesis as did the Adve and Vernon analysis [AV91]; much of the technique in the literature appears to provide only small equivalences or solutions for small networks. This is not a condemnation of the skill of the researchers producing this literature, more an acknowledgment of the difficulty of the problem and idealism of the goal.

In one paper of note: Akyildiz [Aky88] considers BAS networks which meet the deadlock-freedom criterion (fewer customers than the capacity of the smallest blocking cycle) and notes that the throughput can be estimated for solving specially constructed smaller nonblocking

networks which have comparable state spaces (though different structure). This resembles Chapter 3 analysis because both it and the chapter are concerned with state space sizes. However, Akyildiz is concerned with estimating throughput and considers blocking (i.e., queue-filling events) effects only for their brief effect on throughput. In contrast, Chapter 3 is solving for the rate of queue filling events, and is motivated by the extreme cost of these events on the J-Machine.

The result noted in Chapter 3 that all states have equivalent probabilities with a balanced workload resembles one of the working axioms of thermodynamics: that in a physical process all states that are accessible have equal probabilities [Rei65]. Furthermore, the reasoning that the chapter uses to conclude that overflows will be rare – comparing the relative size of state spaces – resembles reasoning in thermodynamics. This connection with thermodynamics breaks down with imbalanced or request/reply workloads because the state probabilities are no longer all equal. Still, the connection with physical reasoning is attractive, if for nothing other than aesthetics. Some literature analyzing blocking networks also uses thermodynamic analogies, for example, the entropy-maximization techniques proposed by Kouvatsos and Denazis [KD93]; also, Harrison and Nguyen [HN93] review Brownian approximations for heavy-load queueing networks. Perhaps some of these methods may apply to the characterization of parallel computers – this is left for others to pursue as future work.

#### Mean Value Analysis

Adve and Vernon's model of a shared-memory parallel computer with a wormhole-routed mesh network forms the basis of Chapter 5 and Appendix A. Their model differs from the J-Machine because it is for a shared memory architecture, and because their routers are different in structure. Furthermore, the fact that the J-Machine's routers are unfair substantially changes the results. The chapter and appendix largely consist of reimplementation of the model with these changes and then computation of the results; this was a nontrivial task, given the size and intricacy of the equations; it was necessary to examine Adve and Vernon's solver at length to determine the meaning behind their concise published explanation.

Adve and Vernon's model uses a technique called Mean Value Analysis (MVA) (which was invented by Reiser and Lavenberg [RL80]) to solve for the first moments (i.e., mean or av-

erage) of queue length, throughput, and waiting time within the network. The beginning of Chapter 5 reviews the fundamental equations within MVA. The classic Reiser and Lavenberg MVA also does not admit blocking; so Adve and Vernon's model incorporate many assumptions about independence to approximate the blocking behavior. With the many assumptions and with the large size of the J-Machine and the very heavy load points chosen, the model does not closely validate with simulated values; it only matches simulation and hardware measurements in a qualitative sense. Investigating the sources of the validation problems and incorporating fixes is likely to be a time consuming task.

#### Flow and Congestion Control

The challenges of flow and congestion control have been recognized for decades. Flow control refers to control of a source to match (and especially not exceed) the rate of the receiver. Link-level flow control, for example, is flow control over a single link where the receiver indicates when it is ready to accept more data. End-to-end flow control matches a source to a receiver which is several links away.

Congestion control refers to controlling several traffic sources to avoid loss of throughput, latency, and deadlock due to congestion (accumulations of traffic) within a network.