# An Efficient Virtual Network Interface in the FUGU Scalable Workstation

by

#### Kenneth Martin Mackenzie

S.B., Massachusetts Institute of Technology (1990) S.M., Massachusetts Institute of Technology (1990)

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

#### February 1998

© Massachusetts Institute of Technology 1998. All rights reserved.

| Author       |                                                                                               |

|--------------|-----------------------------------------------------------------------------------------------|

| D            | Department of Electrical Engineering and Computer Science<br>22 December 1997                 |

| Certified by |                                                                                               |

| ·            | Anant Agarwal<br>Associate Professor of Computer Science and Engineering<br>Thesis Supervisor |

| Certified by |                                                                                               |

| ,            | M. Frans Kaashoek                                                                             |

|              | Associate Professor of Computer Science and Engineering Thesis Supervisor                     |

| Accepted by  |                                                                                               |

|              | Arthur C. Smith                                                                               |

|              | Chairman, Departmental Committee on Graduate Students                                         |

## An Efficient Virtual Network Interface in the FUGU Scalable Workstation

by Kenneth Martin Mackenzie

Submitted to the Department of Electrical Engineering and Computer Science on 22 December 1997 in partial fulfillment of the requirements for the degree of DOCTOR OF PHILOSOPHY

#### **Abstract**

A scalable workstation is one vision of a mainstream parallel computer: a machine that combines scalable, fine-grain communication facilities for parallel applications with virtual memory and preemptive multiprogramming to support general-purpose workloads. A key challenge in a scalable workstation is the Virtual Network Interface (VNI) problem. The problem is that high performance communication for parallel programming depends on a tight coupling between the application and the network while multiprogramming and virtual memory effects disrupt such coupling.

This thesis introduces and evaluates the "direct" virtual network interface: a solution to the VNI problem for fine-grain messages in a scalable workstation. The direct VNI employs two complementary architectural techniques to reconcile speed and protection. First, two-case delivery optimistically provides direct, user-level access to network interface hardware but also transparently backs the direct system with a robust, software-buffered system. Two-case delivery allows the scalable workstation to support both good parallel application performance through the fast hardware interface and good global system performance by permitting buffering when required for multiprogramming. Second, the software-buffered mode uses virtual buffering to provide effectively unlimited buffer capacity by storing messages in dynamically managed virtual memory. Virtual buffering gives the user the convenient illusion of a very large buffer while giving the operating system the means to minimize actual, physical memory consumption.

The direct VNI ideas are implemented in an experimental scalable workstation, FUGU, consisting of emulated hardware, a matching simulator and a custom operating system. Results from workloads of real and synthetic applications show that the direct VNI provides high performance because the direct case is both fast and common. Microbenchmarks show the protected direct delivery case costs only 60% (10s of cycles per message) more than unprotected messages on the same hardware. Further, in a mixed workload experiment, we observe that our parallel applications see only 14-33% of messages buffered when 10% of the CPU time is devoted to unrelated, high-priority, interactive tasks. Finally, results show that physical buffering requirements remain naturally low in real applications despite the combination of unacknowledged messages and unlimited buffering.

Thesis Supervisor: Anant Agarwal

Title: Associate Professor of Computer Science and Engineering

Thesis Supervisor: M. Frans Kaashoek

Title: Associate Professor of Computer Science and Engineering

## Acknowledgments

This research was supported in part by NSF grant # MIP-9012773, in part by ARPA contract # N00014-94-1-0985, in part by a NSF Presidential Young Investigator Award to Anant Agarwal and in part by a NSF National Young Investigator Award to M. Frans Kaashoek.

## **Contents**

| 1 | A So | calable Workstation 1                          | 13         |

|---|------|------------------------------------------------|------------|

|   | 1.1  | Challenges in a Scalable Workstation           | 15         |

|   | 1.2  | An Efficient Virtual Network Interface         | 17         |

|   | 1.3  | Contributions                                  | 18         |

|   | 1.4  | Roadmap                                        | 18         |

| 2 | The  | Virtual Network Interface Problem              | 19         |

|   | 2.1  | Programmability                                | 19         |

|   | 2.2  | Protection                                     | 22         |

|   | 2.3  | Performance                                    | 25         |

|   | 2.4  | Problem Statement                              | 29         |

| 3 | A D  | irect Virtual Network Interface                | 31         |

|   | 3.1  | Programmability                                | 32         |

|   | 3.2  | Protection                                     | 37         |

|   | 3.3  | Performance                                    | 38         |

|   |      | 3.3.1 Two-Case Delivery                        | 4(         |

|   |      | 3.3.2 Virtual Buffering                        | 41         |

|   |      | 3.3.3 Programmer-Visible Performance Tradeoffs | 42         |

|   | 3.4  | Discussion                                     | 43         |

| 4 | Two  | -Case Delivery Technique                       | 15         |

|   | 4.1  | Direct Access Path                             | 47         |

|   | 4.2  | Buffered Path                                  | 53         |

|   | 4.3  | Transparent Access                             | 56         |

|   | 4.4  | Discussion                                     | 57         |

| 5 | Virt | ual Buffering Technique                        | 59         |

|   | 5.1  | Unlimited Buffering                            | 52         |

|   | 5.2  | User Flow Control                              | 55         |

|   | 5.3  | Resource Management                            | 58         |

|   | 5.4  | Discussion                                     | 59         |

| 6 | Exp  | erimental System 7                             | <b>7</b> ] |

|   | 6.1  | Hardware                                       | 72         |

|   |      | 6.1.1 Emulated Hardware                        | 72         |

|   |      | 6.1.2 Fast Simulator                           | 74         |

|   | 6.2  | System Software                             | 76        |

|---|------|---------------------------------------------|-----------|

|   |      | 6.2.1 Operating System                      | 76        |

|   |      | 6.2.2 Scheduler                             |           |

|   | 6.3  | Libraries                                   | 19        |

| 7 | Resu | ults                                        | <b>31</b> |

|   | 7.1  | Applications and Standalone Performance     | 33        |

|   | 7.2  | Mixed Workload Performance                  | 37        |

|   |      | 7.2.1 A Mixed Workload Experiment           | 38        |

|   |      | 7.2.2 Mixed Workload with Real Applications | 92        |

|   | 7.3  | Mixed Workload Analysis                     | 95        |

|   | 7.4  | Buffer Consumption                          | )2        |

|   |      | 7.4.1 Artificially Induced Buffering        | )2        |

|   |      | 7.4.2 Limits to Buffering Behavior          | )5        |

|   | 7.5  | Overflow Control                            | )8        |

| 8 | Rela | ated Work                                   | 1         |

|   | 8.1  | Messaging Models                            | 1         |

|   | 8.2  | Network Interfaces                          | 2         |

|   | 8.3  | Miscellaneous                               | 4         |

| 9 | Con  | nclusion 11                                 | 17        |

| A | Bulk | k Transfer 11                               | 19        |

# **List of Figures**

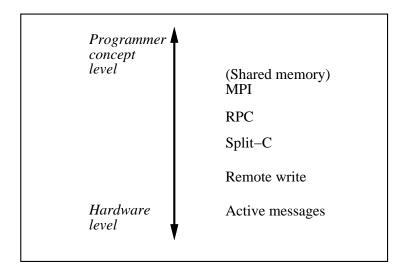

| 2-1 | Communication model abstraction levels                  |

|-----|---------------------------------------------------------|

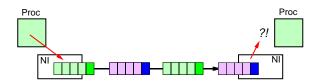

| 2-2 | Undeliverable messages                                  |

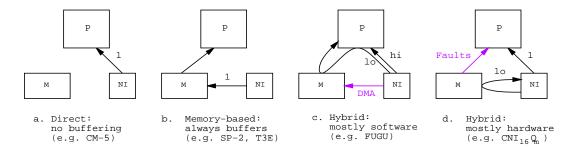

| 2-3 | Approaches to buffering                                 |

| 3-1 | Names of FUGU components                                |

| 3-2 | Message timeline for the fast path                      |

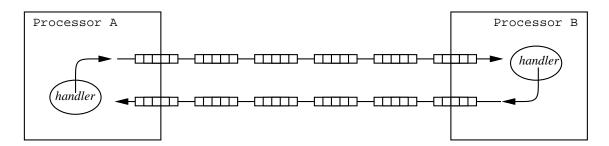

| 3-3 | Protocol deadlock situation                             |

| 3-4 | Simple protection based on Group Identifiers (GIDs)     |

| 3-5 | Direct virtual network interface operating modes        |

| 4-1 | Message timeline for the fast path                      |

| 4-2 | Message timeline for the buffered path                  |

| 4-3 | Direct virtual network interface registers              |

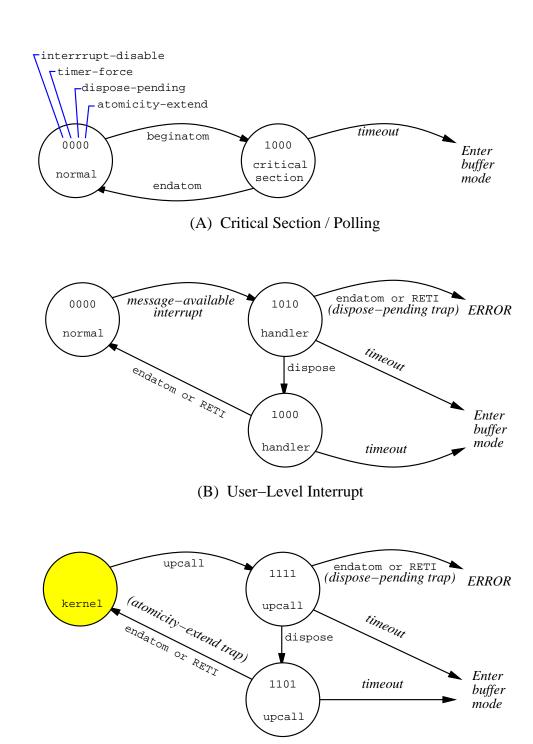

| 4-4 | Three revocable interrupt disable examples              |

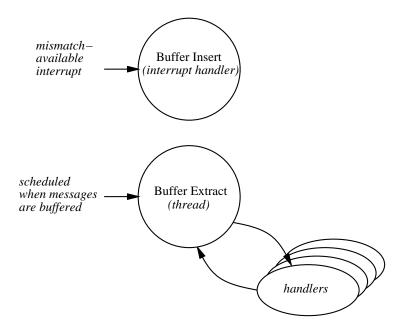

| 4-5 | Software buffering components                           |

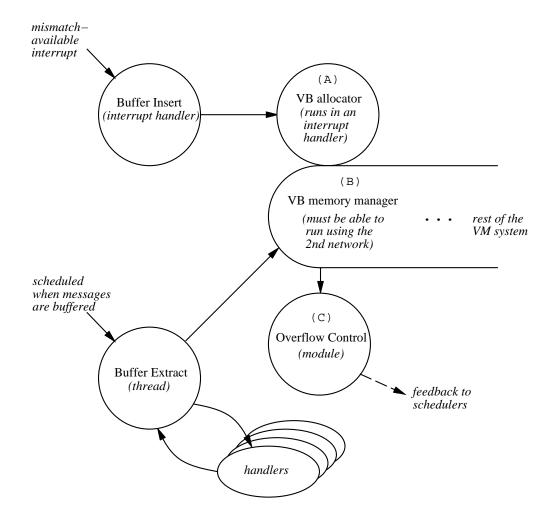

| 5-1 | Virtual buffering components                            |

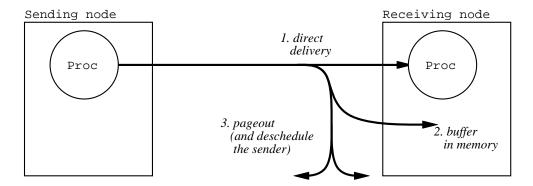

| 5-2 | Message reception cases                                 |

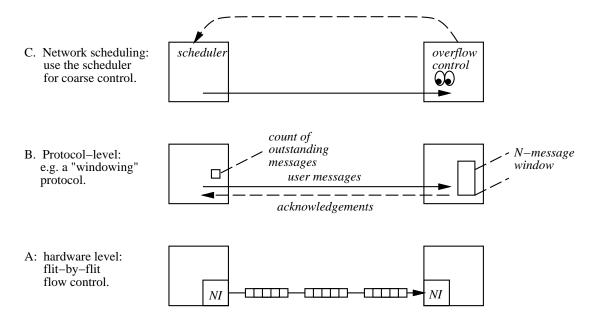

| 5-3 | Levels of flow control in a message system              |

| 5-4 | Virtual buffering system operating modes                |

| 5-5 | Overflow control mechanics                              |

| 5-6 | Conventional paging system mechanics                    |

| 5-7 | Virtual buffer queue length threshold                   |

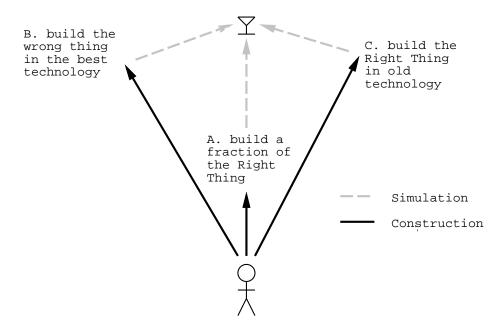

| 6-1 | Approaches to mixed hardware-software system evaluation |

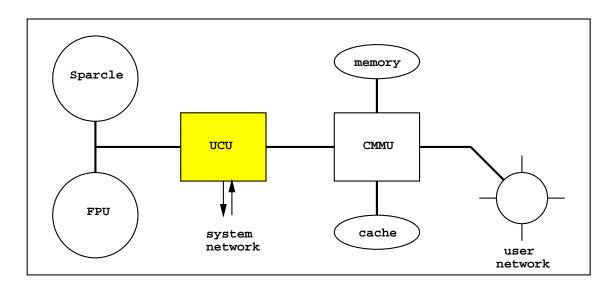

| 6-2 | Block diagram of a single FUGU node                     |

| 6-3 | Photograph of a single FUGU node                        |

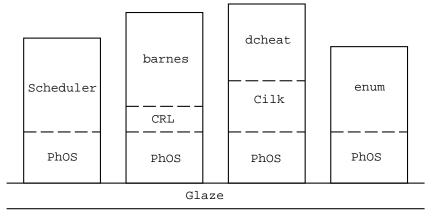

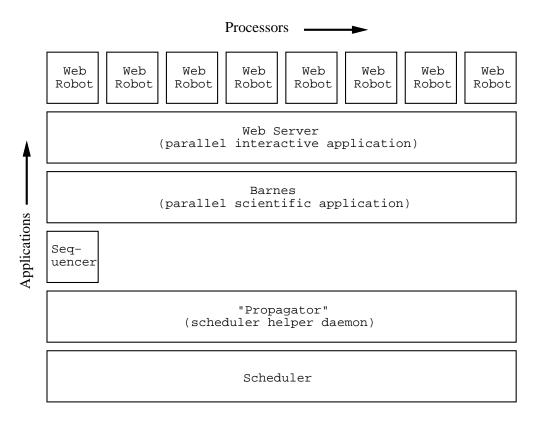

| 6-4 | Software structure of a single FUGU node                |

| 6-5 | Typical FUGU workload                                   |

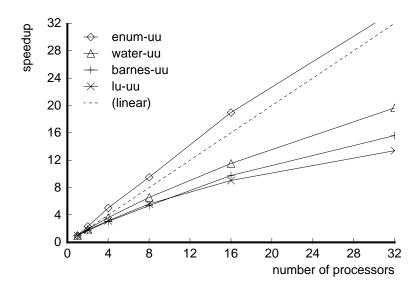

| 7-1 | Application speedup standalone                          |

| 7-2 | Impact of increased message overhead                    |

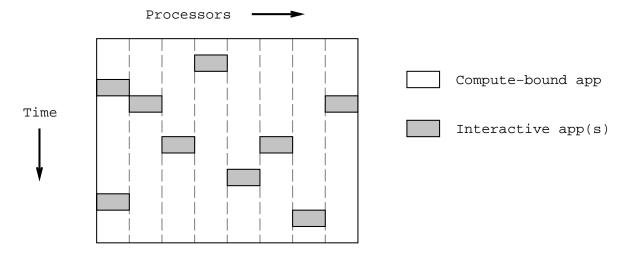

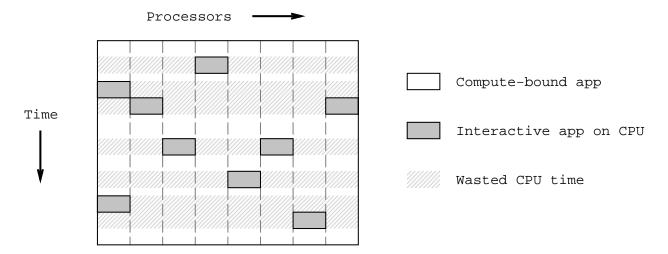

| 7-3 | Ideal mixed workload with independent scheduling        |

| 7-4 | Actual mixed workload with independent scheduling       |

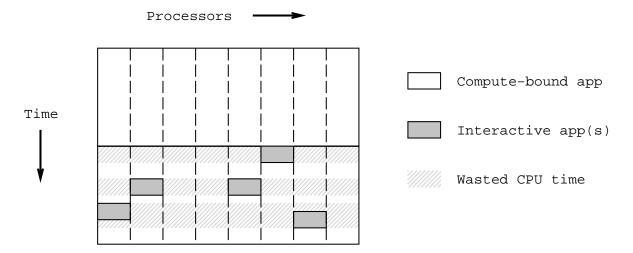

| 7-5 | Mixed workload with co-scheduling                       |

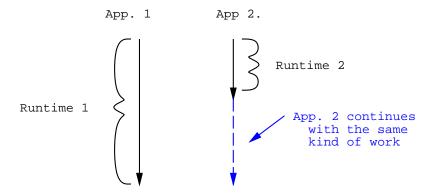

| 7-6 | Mixed workload timeline                                 |

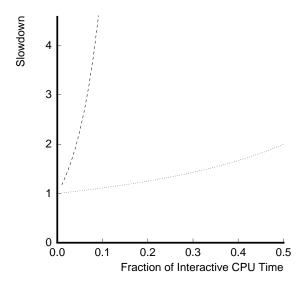

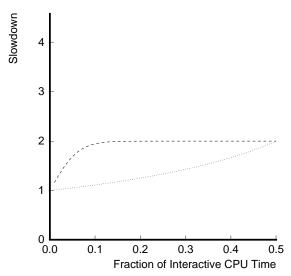

| 7-7 | Expected slowdowns under interactive scheduling         |

| 7-8 | Expected slowdown under gang scheduling                 |

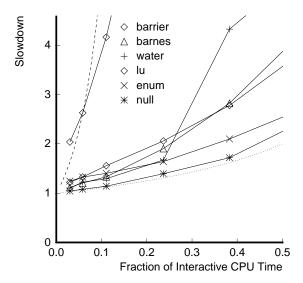

| 7-9  | Performance of a mixed workload with interactive scheduling      |

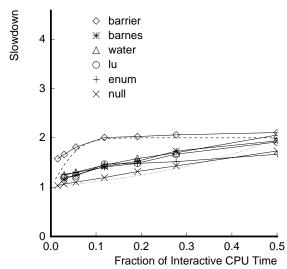

|------|------------------------------------------------------------------|

| 7-10 | Performance of a mixed workload with coscheduling                |

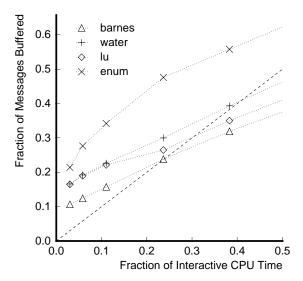

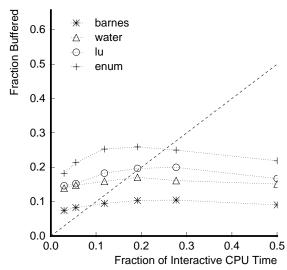

| 7-11 | Fraction of messages buffered with interactive scheduling        |

| 7-12 | Fraction of messages buffered with coscheduling                  |

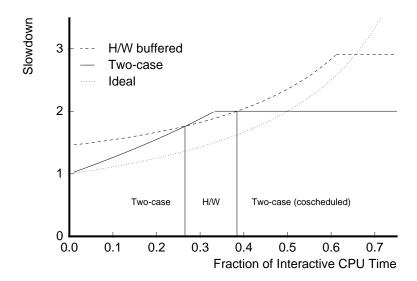

| 7-13 | Hardware buffering versus two-case delivery                      |

| 7-14 | Direct VNI versus hardware-buffering                             |

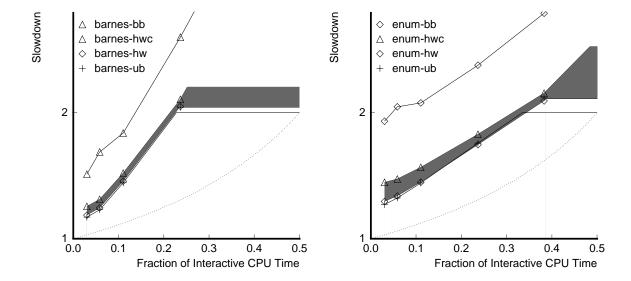

| 7-15 | Performance tradeoff for the barnes application                  |

| 7-16 | Performance tradeoff for the enum application                    |

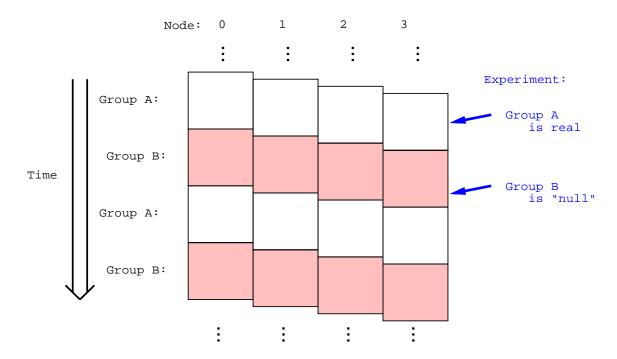

| 7-17 | Gang scheduling with artificial skew                             |

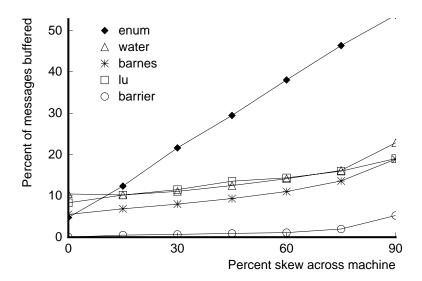

| 7-18 | Fraction of messages buffered versus decreasing schedule quality |

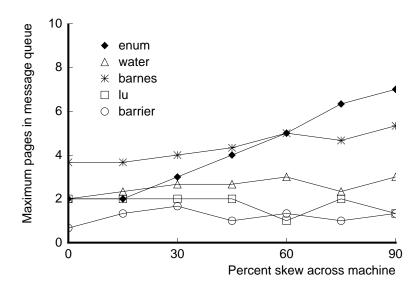

| 7-19 | Maximum pages of buffer space per processor                      |

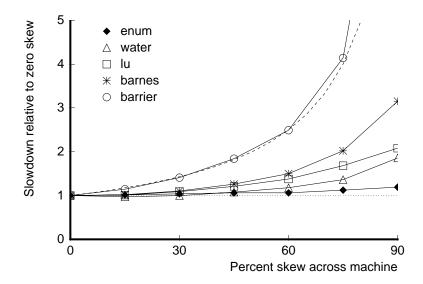

| 7-20 | Relative runtimes versus decreasing schedule quality             |

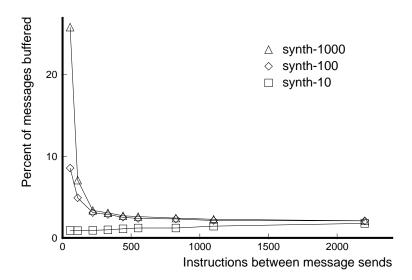

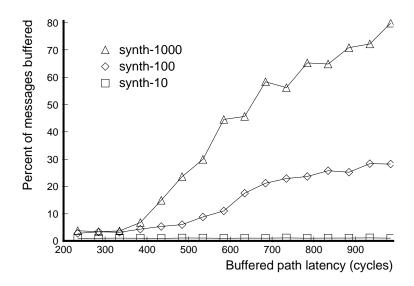

| 7-21 | Fraction of messages buffered, $f_{buf}$ versus send interval    |

| 7-22 | Fraction of messages buffered versus cost of the buffered path   |

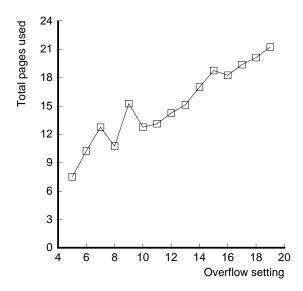

| 7-23 | Overflow control experiment                                      |

| 7-24 | Maximum pages used versus overflow control threshold             |

| 8-1  | Approaches to buffering                                          |

## **List of Tables**

| 1-1 | Comparison of machine qualities                                | 1.  |

|-----|----------------------------------------------------------------|-----|

| 1-2 | Challenges in scalable workstations                            | 1.  |

| 2-1 | Direct and memory-based delivery modes                         | 28  |

| 3-1 | Direct, hardware-buffered and software-buffered delivery modes | 39  |

| 3-2 | Buffering options.                                             | 4   |

| 4-1 | Direct virtual network interface operations.                   | 48  |

| 4-2 | Direct virtual network interface Interrupts and traps          | 48  |

| 4-3 | Flags in the User Atomicity Control ( <i>UAC</i> ) register    | 50  |

| 4-4 | Cycle counts to send and receive a null message                | 52  |

| 4-5 | Cycle counts for buffered path overheads                       | 55  |

| 7-1 | Application descriptions                                       | 83  |

| 7-2 | Application base measurements                                  | 83  |

| 7-3 | Application run times over a range of machine sizes.           | 84  |

| 7-4 | Mixed workload analysis model parameters                       | 98  |

| 7-5 | Maximum pages used versus overflow control threshold           | 109 |

## Chapter 1

## A Scalable Workstation

Parallel processors have become commonplace as high-end workstations, in the form of clusters and as large, dedicated machines. Small-scale symmetric multiprocessors (SMPs) are used as high-end workstations or as servers. Such machines are expected to run a mixed workload of interactive, workstation-like applications as well as parallel applications. Work on larger parallel applications is increasingly focussed on making use of clusters of workstation-class uni- or SMP-based multiprocessors. Clusters are again expected to support a mixed workload of parallel, interactive applications, such as world-wide web search services or data mining services, as well as parallel, compute-intensive applications such as scientific and engineering simulation models. A few commercial, massively-parallel processors (MPPs) exist running primarily parallel, scientific codes.

An ideal, general-purpose multiprocessor would give high performance over a range of machine sizes while running a mixed workload. Existing SMPs, clusters and MPPs each fall short of some aspect of this goal. Table 1-1 summarizes the characteristics of each type in the space of communication efficiency (parallel performance), scalability (efficiency over a wide range of machine sizes) and support for standard multiuser operating system features. Each of the existing machine types exhibits some but not all of the desired qualities of a general-purpose multiprocessor. We discuss each of the rows in Table 1-1 below.

Current SMPs work well as small multiprocessors but are limited by the use of a broadcast bus as the interprocessor interconnect. The bus structure makes communication efficient and, in

| Approach              | Efficient     | Scalable     | Multiuser |

|-----------------------|---------------|--------------|-----------|

|                       | Communication | Interconnect | Features  |

| SMPs                  | ×             |              | ×         |

| Clusters              |               | ×            | ×         |

| MPPs                  | ×             | ×            |           |

| Scalable Workstations | ×             | ×            | ×         |

**Table 1-1.** Qualitative comparison of machines in terms of support for efficient communication, support for scalable communication and support for multiuser operation. SMPs, clusters and MPPs each exhibit some of the desired qualities.

particular, makes cache-coherent shared memory easy to support. However, the bus forms a global bottleneck that limits the scale of SMP machine sizes to a few nodes. The solution is to replace the bus with a point-to-point network and to synthesize shared memory communication by using hardware or software to communicate via messages over this network. Hardware solutions using directory-based cache coherence have been demonstrated in research prototypes [45, 1, 40] and high-end commercial machines [35, 41, 48, 78]. Software solutions have been demonstrated in research prototypes [47, 10, 34, 29, 64, 66, 36, 20] using a variety of techniques. Future solutions are likely to make use of judicious combinations of hardware and software support in hybrid machines that support both shared memory and message passing communication [61, 1].

Clusters typically support only message-passing for inter-node communication in hardware and synthesize shared memory (if desired) in software. The bottleneck in clusters is the interface to the interconnection network and sometimes the network itself. Network interfaces (NIs) for cluster nodes have evolved according to the demands of Local Area Networks (LANs), *i.e.*, using heavyweight protocols that tolerate uncertain network characteristics and the view that the network is a peripheral device. Current work in cluster NIs seeks to reduce protocol overhead, to tighten the integration of the NI with the processors and to take advantage of the characteristics of the so-called System Area Network (SAN) environment [76, 63, 80, 6, 18, 16, 28, 13].

Higher performance network interfaces suitable for significantly finer-grain parallel problems have been demonstrated in massively-parallel processors as research prototypes [69, 7, 15, 1, 60, 2, 55] and as commercial machines [44, 68, 71]. However, MPP work has largely ignored issues of mixed workloads that require multiprogramming, demand paging and interactive scheduling.

A *Scalable Workstation* represents one vision of the convergence of SMP, cluster and MPP goals and technologies that combines efficient communication, a scalable interconnect and multiuser support. Specifically, a scalable workstation has the following characteristics:

- It will run a mixed workload, consisting of both interactive, response-time sensitive jobs and compute- and communication-intensive parallel jobs.

- It will support efficient communication including both explicit communication through message passing and implicit communication through shared memory.

- It will use a scalable, point-to-point interconnect with the characteristics of a SAN, *e.g.*, high reliability, effective hardware flow control and low latency.

Scalable workstations are expected to run a mix of the workloads that desktop workstations and SMP servers run now and to enable the use of parallel programs for more applications. Scalable workstations fit naturally into either a "workstation" or a "network computer" model of organization. In a workstation model, scalable workstations serve as desktop computers tailored in size to the needs of the user. In a network-computer model, desktop machines are minimally functional and are backed by group-level or departmental-level scalable workstations as servers tailored in size to the needs of the group. Despite partial centralization, the network-computer model remains workstation-like if each desktop head is guaranteed the resources of some number of processors in the backing server.

A scalable workstation supports a full set of communication primitives. Shared memory is widely considered more easily programmable than message passing. Message passing remains desirable as well for several reasons. First, the strengths of message-passing for bulk transfer

|         | Multiprogramming    | Virtual Memory          |

|---------|---------------------|-------------------------|

| Message | Isolation           | Page faults in handlers |

| Passing | Parallel scheduling | DMA coherence           |

|         |                     | Translation for DMA     |

| Shared  | (Isolate using VM)  |                         |

| Memory  | Parallel scheduling | Translation Coherence   |

|         |                     |                         |

**Table 1-2.** Challenges arising from the integration of four features desired in a scalable workstation. Message passing and shared memory are features desired for high performance parallel processing while multiprogramming and virtual memory are features desired for general-purpose, multiuser operation.

and explicit synchronization are complementary to the strengths of shared memory for automatic communication [37], making a mixed model attractive. Second, raw message-passing can have performance benefits over shared memory in reduced interconnect traffic and more robust latency tolerance [12]. In particular, even if written assuming a shared-memory programming model, a program in which communication patterns are amenable to compile-time analysis might make better use of compiler-generated message passing communication than of even hardware-supported shared memory. Third, distributed shared memory and message passing implementations are naturally similar at a low level, so if an implementation provides shared memory in hardware the additional cost of exposing message passing is low [39]. Finally, one reading of technology trends is that shared memory systems increasingly will be implemented in software using messages to minimize hardware [1, 30] and/or to take advantage of application-specific knowledge [61].

Finally, a scalable workstation is made "scalable" by its point-to-point interconnect. Scalability has two meanings. First, the bandwidth of the network potentially scales up as processors are added. The benefit is that increasing the number of processors can lead to increased application performance for a larger class of applications. Second, the cost of the interconnect scales with the number of processors. The benefit is that a single machine design can exhibit good cost/performance for a wide range of machine sizes including small sizes.

A scalable workstation is an attractive vision. However, the combination of mixed workloads, mixed communication models and the distributed nature of the system leads to a number of challenges, described next.

### 1.1 Challenges in a Scalable Workstation

The primary challenges in a scalable workstation arise from the integration of communication features with multiuser features. Message passing and shared memory are the two communication models. Multiprogramming and virtual memory are features arising from the goal of supporting a mixed, multiuser workload. Table 1-2 enumerates the challenges that arise from integrating these features by considering the intersection of each of the communication models with each of the multiuser features.

There are a number of important challenges, only the first of which is pursued in detail this thesis. The discussion below explains each challenge listed in the table and regroups them into four named problems.

- First is the "Virtual Network Interface" (VNI) problem which encompasses the top row of items in Table 1-2. Messages in a multiuser system must be isolated from one another and resilient to disruptions such as page faults in virtual memory. At the same time, the interface must allow for efficient communication. Research on communication mechanisms supports that view that efficiency comes from tight coupling of the network with the application. The demands of isolation tend to interfere with tight coupling from both directions. For protection reasons, the network may not be able to deliver a message immediately. Similarly, due to multiprogramming, an application may not be able to receive a message immediately. Demandpaged virtual memory causes a similar effects: a page fault (or a remote shared memory miss) in message handling code introduces a delay in message reception that may be intolerable to the network. We proposed a solution to the VNI problem in [49] and partly evaluated it in [50]. This VNI solution is implemented in FUGU and is the focus of this thesis. Other recent network interface work addresses the VNI problem with similar goals, notably CNI [57], the \*T family [60, 2] and the M-machine [24]. These projects are described as related work in Chapter 8.

- Second is the DMA problem. Efficient bulk transfer through messages requires the support of Direct Memory Access (DMA) hardware or equivalent functionality provided by a coprocessor. Using DMA with virtual memory requires virtual address translation for the DMA engine. Either the DMA engine itself must be capable of performing such translations or there must be a secure means for the DMA engine to receive physical addresses from the processor. Further, combining DMA with virtual memory (or with shared memory) introduces a data coherence problem because the DMA engine becomes an additional source of memory operations. We proposed a solution to the DMA problem in [49] and some elements of that solution are implemented in FUGU (Appendix A). Others have addressed DMA with virtual memory in network interfaces as well [79, 67].

- Third is the translation coherence problem. Virtual memory combined with shared memory introduces coherence problem with cached translations because virtual-to-physical mappings are conventionally cached at the processors. A solution to translation coherence needn't be as efficient as data cache coherence but must be scalable. We proposed a scalable solution to translation coherence in [49]. Teller examined a number of solutions to translation coherence [74].

- Finally, there is the scheduling problem. Parallel schedulers for mixed workloads are not yet fully understood. It appears important to be able to schedule some applications with traditional, per-processor, priority-based scheduling and others with coordinated scheduling ("coscheduling"). Network scheduling in Table 1-2 refers to the problem of controlling the impact of one application's network traffic on another. Traffic effects can be ameliorated by communication models that minimize blocking such as sender-based messages. Ultimately,

<sup>&</sup>lt;sup>1</sup>The integration of shared memory with message passing presents problems that are similar to those presented by virtual memory. For instance, a cache miss to a remote shared memory location is similar to a page fault and could be handled in the same way.

however, network effects must be considered by a parallel scheduler. A "flexible coscheduling" parallel scheduler was proposed in [43] and is partly implemented in FUGU. Others are working on the same problem [21, 72].

While DMA, translation coherence and scheduling have each been studied to some extent in the FUGU system, the focus of this document is on the solution to the VNI problem.

#### 1.2 An Efficient Virtual Network Interface

Existing solutions to the VNI problem compromise in one of three ways: in *performance*, by reducing the performance of the implementation, in *protection*, by limiting the support for multiprogramming, or in *programmability*, by limiting the flexibility of the communication model and therefore limiting its efficiency as a programming target.

This thesis presents the "direct" virtual network interface as a solution to the VNI problem that meets all three parts of the challenge. The direct VNI supports an aggressive, low-level message model, User Direct Messages (UDM), in which user messages logically correspond one-to-one with one-way, unacknowledged messages sent through the network. Messages are isolated for protection by tagging each message with a global identifier corresponding to the communicating application and by interpreting the tags appropriately.

The direct VNI architecture reconciles efficiency with protection by recognizing that protection failures are uncommon. The thesis introduces two complementary techniques as part of the architecture. First, the direct VNI uses *two-case delivery* to optimistically provide direct, user-level access to network interface hardware with a transparent, software-buffered fallback delivery system. The result is a system that simultaneously supports both good parallel application performance through an efficient, low-level interface and enables good global system performance through flexible multiprogramming. Second, the software-buffered mode uses *virtual buffering* to provide effectively guaranteed message delivery while giving the operating system the freedom to automatically manage physical buffering resources.

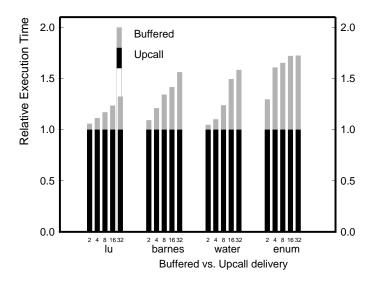

The two-case delivery and virtual buffering ideas are evaluated using workloads of real and synthetic applications running on a simulator and partly on emulated hardware. The results answer two main questions. First, results show the direct path is also the common path under most conditions, justifying the use of software buffering. Experiments show that only 14-33% of messages in our sample parallel applications take the buffered path when 10% of CPU time is devoted to uncorrelated interactive tasks on 16 processors. Second, further results show that physical buffering requirements remain low (a few pages) for our sample applications despite the combination of unacknowledged messages and unlimited buffering.

The combination of UDM with an implementation based on two-case delivery and virtual buffering makes for a network interface that is both efficient and virtualized and that is particularly appropriate for the environment of a scalable workstation. The ideas are usable separately.

#### 1.3 Contributions

The FUGU project has been a cooperative effort involving a number of people making overlapping contributions. The particular contributions of this thesis are fourfold:

- 1. We identify the virtual network interface problem and enumerate its major issues.

- 2. We present the direct virtual network interface, which applies the architectural techniques of two-case delivery and virtual buffering with overflow control to the virtual network interface problem. The thesis includes a detailed description of the two techniques. The essence of the UDM programming model and the specific hardware used to virtualize user interrupts have also been described by Kubiatowicz in the context of the Alewife machine [39].

- 3. We report on the implementation of a scalable workstation, FUGU, that uses direct virtual network interface. FUGU consists of emulation-based hardware, a companion instruction-level simulator and a custom operating system. Features of the hardware have been previously described by Michelson [54] and by Lee [42].

- 4. We present an evaluation of the direct virtual network interface based on simulation and emulated hardware. The evaluation shows that the direct VNI in FUGU has best-case receive-side overhead within 60% (10s of cycles) of an unvirtualized interface built on the same hardware, that the sustained performance is good for several real applications given scheduling support when appropriate and that memory consumption remains low in reasonable applications for a broad definition of reasonable.

## 1.4 Roadmap

The rest of the document is organized as follows. Chapter 2 describes the aspects of the VNI problem. Chapter 3 presents our direct VNI solution, including the programmer-visible model and an overview of the architectural approach. Chapters 4 and 5 describe and discusses the details of the two-case delivery and virtual buffering architectural techniques, respectively. Chapter 6 introduces the experimental FUGU system used to evaluate the direct VNI ideas. Chapter 7 describes the experimental evaluation and presents the results from application workloads run on the FUGU system. Chapter 8 summarizes related work and Chapter 9 concludes.

## Chapter 2

## The Virtual Network Interface Problem

A key issue in a scalable workstation is the problem of reconciling efficient communication with standard support for multiprogramming. Efficient communication implies a tight coupling between application code and the communication system: the processes running an application can rely on timely action by the communication system and vice versa. Multiprogramming and related support, notably demand-paged virtual memory, prevent a process in an application from being able to guarantee its own timely behavior. We call the problem of reconciling communication efficiency with multiuser support the *virtual network interface* problem.

A full solution to the problem must address three major issues:

- Programmability: the interface to the communication system must serve as an efficient target for a programmer, a compiler or a runtime system. Assuming a good implementation, an interface model is good when it expresses naturally what the user needs to do and when it exposes the fundamental underlying costs of communication.

- Protection: the communication system must provide protection for multiprogramming and must be compatible with virtual memory and scheduling for mixed workloads.

- Performance: the communication system must transport data with low latency and high bandwidth. Ideally, given a particular programming model, the protected communication system will perform as well as raw, unprotected hardware.

Each of these three issues in isolation is not difficult. Supporting a programmable, protected interface while providing high performance is the real challenge. This chapter discusses each of the three issues and attempts to define an "ideal" for each against which any system should be compared. We will refer back to these points in the rest of the thesis when discussing the solutions in the direct VNI and in related work.

## 2.1 Programmability

The first issue is that the communication model must be both general and efficient. In the realm of fine-grain message passing models, low-level models that expose fundamental costs are attractive

**Figure 2-1.** Existing communication models take a variety of approaches to bridging the programmer's notion of communication with the capabilities of the hardware. Here, an arbitrarily chosen set of models are arrayed on the right along an axis of "close to the program" at the top to "close to the hardware" at the bottom.

because they give the programmer the means to minimize those costs. We describe the desired functionality of a low-level model and enumerate the sources of costs.

The communication model of most interest in this thesis is the model for fine-grain messages. As described in the introduction, a scalable workstation is expected to support both shared memory and message passing communication models. Shared memory integrates naturally with virtual memory and multiprogramming so we consider only message-passing issues here. Further, message passing has two main purposes with different requirements: small, synchronizing messages and large, bulk transfer messages [37]. Fine-grain messages for combined data transfer and synchronization require low overhead and latency for maximum utility. Messages for bulk transfer demand chiefly high bandwidth because latency and per-message overhead are amortized over the time of the transfer. Thus, while low-overhead bulk transfer extends the usefulness of a bulk transfer mechanism, overhead is a secondary issue. We consider only small messages as the focus of this thesis and assume that bulk transfer messages are supported separately. Low-overhead bulk transfer support in FUGU is implemented as an extension of the direct VNI mechanism and is described in Appendix A.

Message-passing models for small messages are varied and controversial because, like an instruction set, a message model must balance naturalness as a programmer's abstraction with implementability in hardware. The model must serve as an efficient target for the application programmer, compiler or library writer. Simultaneously, the model must be implementable with high speed and using acceptable amounts of hardware. The tension between expressiveness and implementability leads to a tradeoff. Figure 2-1 sketches the tradeoff and loosely places some existing models in the space of the tradeoff. For instance, MPI [53] is a relatively high-level model. MPI defines synchronous send/receive operations and multicast/reduction operations as primitives. These primitives correspond to multiple messages in the network hardware. Close to the other extreme, Active Messages [77] is a low-level model with primitives that correspond closely to fundamental hardware operations. Each user message in Active Messages corresponds to a single hardware message

through the network which invokes a user handler at the destination.

While a final conclusion awaits further research, we believe that the most successful interfaces in the long run are likely to be low-level ones that expose the fundamental costs of communication. In analogy to RISC instruction sets, a low-level abstraction both allows the hardware to be focused on support for a few, simple, fast primitives and gives software the opportunity to synthesize compound operations in an application-specific manner. At a minimum, a low-level model such as Active Messages can efficiently emulate a higher-level model such as MPI given a sufficiently low-overhead implementation. Efficiency in this context means that the emulation overhead of an Active Message implementation of, for instance, send/receive in MPI over a native implementation is negligible compared to fundamental costs such as data transfer time. More important than emulation, a low-level model offers the promise that network traffic and protocol overhead may be reduced over that required by a higher-level model by programmer specialization [77] or through automatic, compile-time analysis and specialization [22, 33].

An ideal low-level model provides a complete set of communication operations and exposes fundamental costs. The programmer is thus given the ability to craft communication protocols tailored to the application and to minimize communication costs using application-specific knowledge. The fundamental communication operations for fine-grain messages passing are data transfer and control transfer:

- Ideal data transfer moves data words from the right place to the right place, *i.e.*, from register/cache/memory of the source process to the register/cache/memory of the destination process, depending on the needs of the source and the destination. Small messages are likely to be transferred from register to register on the assumption that they are intended to be sent as soon as they are generated and to be consumed as soon as they are received.

- Ideal control transfer allows the sender and receiver to synchronize in the most convenient way; by having the receiver poll for a message, receive an interrupt when a message arrives, or with no synchronization at all. Both polling and interrupts have advantages and disadvantages in performance and in programmability. In terms of performance, interrupts work well for moderately frequent but latency-critical messages. Polling works well for predictable, high-volume message patterns or for latency-tolerant applications. In terms of programmability, interrupts give predictable performance without tuning. This is an advantage because periodic polling is often difficult to synthesize accurately. With polling, the atomicity model is clearer and less error-prone: a faulty polling-based application tends to deadlock, which is much easier to debug than a synchronization failure. [8].

The fundamental costs of communication arise from the operations of data and control transfer. Costs per message are due to latency and resource consumption in the network, in the endpoint (the network interface and/or the processor) and in any memory used if messages are buffering:

- Messages consume network bandwidth and suffer latency due to the network. Network resource consumption is a per-message cost.

- Message handling at the sending and receiving endpoints consumes computation bandwidth in the processor or network interface. Such computation also adds latency to the message.

Endpoint resource consumption is a per-message cost in a low-level model like Active Messages. A more complex model may use hardware or a coprocessor to reduce the endpoint cost for messages that are part of the complex model's protocol.

Messages that are buffered in memory at some point consume memory storage space and consume message system bandwidth. Memory consumption is a per-message cost when buffering is used.

#### In addition:

• A message system incurs additional, possibly substantial, costs in the network, the endpoints and memory if a layer of protocol is required to synthesize message reliability, ordering, flow control, etc. [32], needed by the application.

The ideal communication model is both natural to program and is effective at minimizing the costs of communication. Low-level models work by exposing the fundamental operations and the fundamental costs based on the assumption that a compiler, a library implementation or the application programmer can best minimize the costs. In a lightweight, asynchronous model, each logical message specified by the programmer corresponds one-to-one with a message through the physical interconnect. This correspondence give the programmer maximum control over the traffic generated by the application and thus control over the per-message costs. Having each message invoke a handler on the processor gives the programmer the "glue" to build arbitrary protocols that minimize the required messages.

We have presented desirable programmability features and enumerated costs for fine-grain message-passing. The fine-grain messages mechanism is assumed to be complemented by support for bulk-transfer messages and for shared memory. The programmability of the virtual network interface in a scalable workstation is tempered by the need to support protection, described next.

#### 2.2 Protection

The second issue in a virtual network interface is that the architecture must be compatible with multiuser operation in a scalable workstation. Multiuser operation requires protection between applications in all elements of the system: in the processors, in memory and in the network. A virtual network interface architecture must provide the protection for the network and must tolerate the *effects* of protection in the other elements of the system. The primary effect of protection from the point of view of the message system is that protection mechanisms can render network messages *undeliverable*, temporarily or permanently. This section discusses the undeliverability problem, protection for the network in particular and then protection for memory and the processor in a general way.

**Undeliverable Messages.** The primary consequence of the various aspects of protection from the point of view of the message system is that a message is not always deliverable to the destination process at the time a sender wishes to send. A message may be undeliverable due to application choice if the programmer's model allows a receiver to refuse messages. Multiuser protection features exacerbate the problem by introducing new reasons for messages to be undeliverable, *i.e.*, because

**Figure 2-2.** Protection requirements can make messages undeliverable. Here an incoming message from a different application has been mixed in with a parallel application's messages. The currently running (light colored) application cannot receive the (dark colored) message at the head of the queue for protection reasons. If the architecture permits potentially undeliverable messages to be launched into the network, the receiver must buffer, NACK or drop such messages.

the wrong process is scheduled at the receiver or because the receiving process takes a page fault. Figure 2-2 illustrates a situation in which a message has been launched from the sender on the left but the receiver is not ready to receive. How the receiver responds is a major architectural issue in a virtual network interface.

The focus of the discussion here is on protection rather than virtualization (naming) because it is protection that ultimately causes the undeliverability effect. Virtualization features, such as a mechanism to translate a virtual processor number in a message headers into a physical processor number, are useful, but protection is fundamental.

**Network Protection.** In the abstract, protection means preventing one application from discovering the results of another application or altering the execution of another application. Applied to the message system, protection means preventing an application from reading, forging or destroying another application's messages. More subtly, an application also must be prevented from unduly *delaying* messages belonging to another application. The effect of protection in the network is that messages may be made undeliverable at times due to protection conflicts.

Rigid scheduling strategies in a multiprocessor, *i.e.*, space partitioning or strict gang scheduling, can effectively solve the network protection problem by permitting only one application's messages in a portion of the network at a time. Rigid scheduling solves both the problems of isolation of data and of delay effects between individual messages. The CM-5 [44], for instance, provides protected multiprogramming by strict gang scheduling. Application messages are isolated because only one application is active in a partition at a time. The CM-5 network interface allows an application process to block the network, but the CM-5 limits the delay effect of such blocking to other applications by saving and restoring network state at application switch times. However, requiring rigid scheduling at all times is undesirable for interactive performance reasons.

Flexible scheduling implies that the messages of multiple applications may be active in the network at the same time. The network architecture must solve the two problems of isolating messages of multiple applications and of controlling the delay of one application on another application. Both problems lead to undeliverable messages.

The first part of network protection is isolating network data. With multiple applications sending messages simultaneously, isolation of network data requires tagging each message indelibly with information that allows it to be identified to a protection system which can in turn determine which process or processes may have access to the message. Tagging requires three mechanisms: the sending network interface must include a mechanism to apply the tag in a trusted way, the message

in transit must encode the tag indelibly and the receiving network interface must include a mechanism to interpret the tag in a trusted way. The flexibility and expressiveness of the protection mechanisms may be arbitrarily elaborate, but at the bottom level the consequences are simple: messages must be identifiable while in transit and certain messages may be undeliverable due to protection conflict.

The second part of network protection is minimizing the delay effect of one application on another. Some amount of interaction between applications is inevitable since the applications share resources. However, for instance, if one application refuses to receive its own messages, perhaps because it polls only infrequently, the result can be a network blockage. The network interface must receive messages and keep network traffic moving whether the application is ready to receive messages or not. This problem is another instance of undeliverability.

Memory and Processor Protection. Memory and processor protection are conventional in uniprocessor workstations and largely extend naturally into scalable workstations. From the point of view of the network interface, memory and processor protection are simply other potential sources of undeliverability: a message can become undeliverable because it requires a memory or processor resource that is temporarily or permanently unavailable. For instance, a message handler that takes a page fault on its first instruction renders that message undeliverable for the (presumably intolerable) period required to service the fault. Parallel scheduling is a whole topic unto itself. We discuss it here in the context of message passing because scheduling has an impact on what the message system can expect.

A scalable workstation requires a system scheduler that caters to needs of both interactive, response-time-sensitive applications and parallel, synchronization-intensive applications. A system with an interactive workload needs a scheduler that provides good response time to interactive events. Standard, priority-based scheduling addresses this requirement well [73]. The natural extension of a priority-based scheduler to a multiprocessor is to schedule processes independently on each processor of the multiprocessor. However, parallel jobs, particularly ones that perform inter-process synchronization frequently, often require some form of coscheduling for best performance [59]. The conflict in scheduler requirements is stark in a scalable workstation where we want to run mixed workloads. A standard solution does not yet exist although a number of researchers are working on the problem [21, 72, 43]. Essentially what is required is a scheduler that works well in both interactive- and coscheduled modes.

Beyond the scheduler, the virtual network interface itself needs to operate efficiently in both modes. Coscheduled applications can easily make use of the low latency of a direct interface since coscheduling means that the sender and receiver of a message tend to be scheduled simultaneously. Applications running under standard, priority-based scheduling may be able to make use of a direct interface sometimes or "optimistically" but in general will require buffering of messages that arrive when the wrong process is scheduled.

The ideal support for protection in a virtual network interface provides isolation between individual messages so that multiple applications may be scheduled independently on each processor if application characteristics do not demand coscheduling. Ideally, the message system isolates the virtual networks of applications both in terms of correctness and in terms of performance and imposes no additional overhead in either the independently-scheduled or coscheduled scenarios.

#### 2.3 Performance

Finally, a virtual network interface architecture must address the issue of performance given the demands of programmability and protection. The challenge of programmability with a low-level model is to provide full functionality with overheads near hardware limits. The complication introduced by protection is the problem of undeliverable messages. This section discusses the challenges of a low-level model and of undeliverability from the perspective of performance, then concludes by comparing the characteristics of two means of building a network interface in hardware: direct and buffered. A direct interface which brings network queues all the way to the processor offers low overhead for the operations in a low-level model. A buffered interface which queues messages in memory can solve the undeliverability problem. We conclude that a successful approach will combine the characteristics of each.

**Programmability.** A low-level model, as described in Section 2.1, demands full functionality and addresses communication costs by relying on the compiler, library or programmer to minimize messages. The performance challenge in the architecture and implementation is minimizing the per-message costs.

A particularly difficult case is the situation of message delivery via interrupt. There are two overheads associated with delivery via interrupt: the cost of having the processor take the interrupt and the delay of transporting the first word of data from the network interface to the processor.

A low-level model is most useful if the network provides reliable, exactly-once message transport semantics and flow control so that low-level operations can be used without an additional layer of protocol-level fault tolerance. A point-to-point network in one cabinet (a System Area Network or SAN) may be made to be sufficiently reliable that protocol-level fault tolerance becomes unattractive compared to a combination of link-level fault tolerance (*e.g.*, via ECC) and simple end-to-end fault detection. Other researchers take the same view [9, 24]. MPP manufacturers have found it feasible to build reliable networks for machines with several hundreds of nodes [68]. Placing the network in one cabinet avoids most of the practical causes of failures, *e.g.*, those due to unpluggings, independent power supply failures, cable damage and electromagnetic interference.

**Protection.** As discussed above, a consequence of the various aspects of protection is that messages are not always deliverable to the destination at the time a sender wishes to send. Messages may be undeliverable even in a single-user system due to application choice if the programmer's model allows a receiver to refuse messages. Multiuser protection features exacerbate the problem by introducing new reasons for messages to be undeliverable, *e.g.*, because the wrong process is scheduled at the receiver. There are a small number of possible solutions to undeliverability. Of these, buffering is attractive because, in the spirit of a low-level model, it works without adding the requirement of additional protocol messages.

There are four options for dealing with undeliverable messages, one sender-side and three receiver-side. The first option is to rule out undeliverable messages by prenegotiating all resources needed for a message transfer before a message is launched. The second, third and fourth options are to drop, to negatively acknowledge (NACK) or to buffer such messages.

Prenegotiation is widely used. For instance, with a remote-write model, the system can require that the sender can only name locations at the destination that are known to physically exist. As another instance, with a synchronous send/receive model, the receive statement can be used to trigger

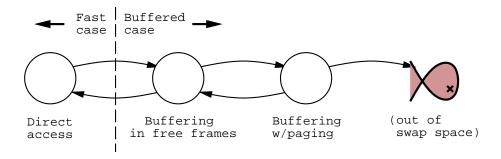

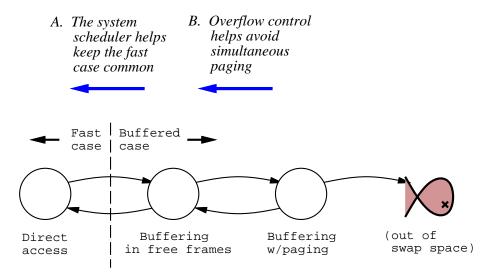

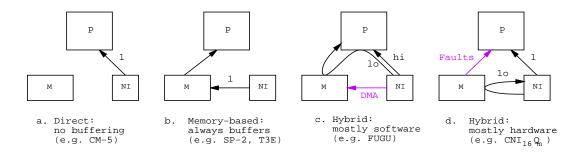

**Figure 2-3.** A network interface my delivery messages directly, may buffer all messages in memory or may take a hybrid approach. The annotations on the arcs represent relative frequencies along each path.

the send. Prenegotiation has costs in extra protocol overhead and potentially in delay. Prenegotiation is most useful when its costs are amortized over a bulk transfer or when the idea of prenegotiation is propagated all the way back to the model, *e.g.*, a shared memory or remote memory model, so that the programmer can work around its costs.

Of the three receiver-side options, dropping is the least desirable because it introduces unreliability into a system that may otherwise have adequately reliable hardware. Dealing with unreliability adds the extra costs of buffering copies at the sender and of extra traffic to manage the copies.

NACKs introduce complexity into the network interface, add traffic and overhead for buffer management and require a reserved back-path. The "return-to-sender" strategy, used in the T3E [68] and the M-machine [24] is a form of NACK that avoids much of the common-case buffer overhead. Return-to-sender assumes a reliable network. Both dropping and NACKing have the effect of increasing network demand under load. Further, dropping and NACKing are subject to livelock unless additional steps are taken to prevent it.

Finally, buffering has the advantage of letting messages always make forward progress, at least with respect to traversing the network. However, buffering only postpones the undeliverability problem unless the buffer is effectively infinite in size or the total buffer space required by the workload is provably limited by some means. The SP-2 takes the "effectively infinite" approach by providing a very large (8MB) physical buffer [71]. Infinite buffering offers the lowest overhead provided the real costs of buffering can be kept low. The next section talks about the performance cost of providing support for buffering in hardware.

Undeliverability is described here in terms of protection for correctness but there is also a related performance issue. If the message system does not demand prenegotiation of all resources, then undeliverability in terms of correctness becomes a receiver-side protection issue. However, there is also a similar performance issue: it might be beneficial to remove messages from the network (or, symmetrically, not to inject them) just to improve traffic flow within the network. Mukherjee, *et al* [57], found it beneficial to buffer messages at the receiver automatically in some applications.

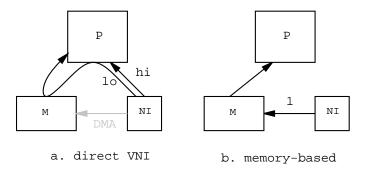

**Direct vs. Buffered Interfaces.** Message passing network interfaces developed for high-performance parallel machines have taken two general approaches: direct and memory-based. Direct interfaces allow the processor to handle messages directly out of the network. Memory-based interfaces provide special hardware to extract messages out of the network and buffer them in memory; the processor then accesses the message buffers in memory. Although a definitive conclusion awaits further

research, past research indicates that direct interfaces tend to be more efficient than memory-based interfaces. Direct interfaces that can be accessed at cache speeds offer even better performance [27]. For example, the CNI paper [55] showed that a direct, cache-level interface exhibited 50% higher bandwidth than their best interface placed on the memory bus. Direct interfaces are challenging to protect without sacrificing efficiency or seriously impairing the multiprogramming model. Therefore, one appeal of memory-based interfaces is that they may be protected through standard memory mapping mechanisms.

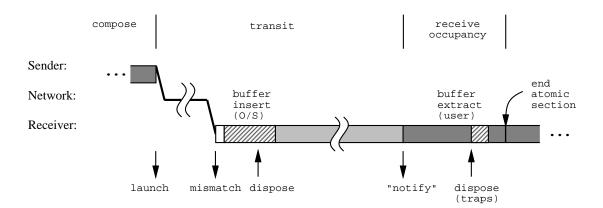

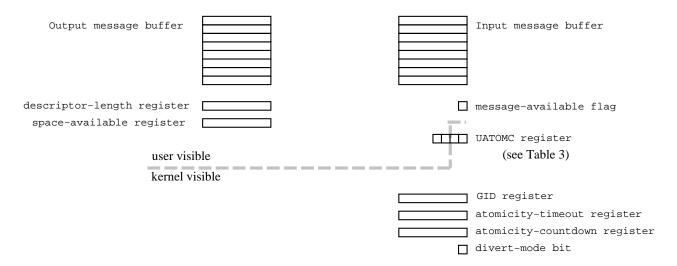

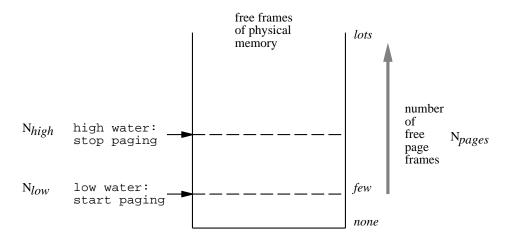

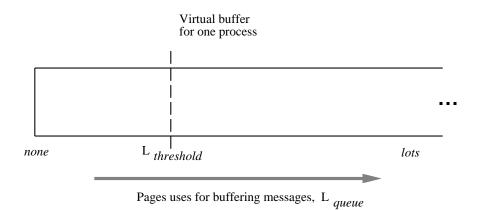

Figure 8-1 gives schematic views of the different approaches to message delivery. Figure 8-1a shows a direct interface with no buffering and Figure 8-1b shows a memory-based interface. Hybrid schemes are also possible. The two-case delivery system to be described in this thesis uses hardware for direct delivery and software for buffering as in Figure 8-1c. A two-case delivery system using all- or mostly-hardware by having the network interface manage memory itself is shown in Figure 8-1d. For instance, Mukherjee, *et al*'s  $CNI_{16}Q_m$  [55, 56] interface provides both a fast path and a (potentially virtual) buffered path by using the network interface to buffer messages. Hybrid solutions will be discussed in more detail in Chapter 8.

Direct network interfaces, Figure 8-1a have been used in research machines [15, 7, 60, 1, 55] and one commercial machine, the CM-5 [44]. These interfaces feature low latency by allowing the processor direct access to the network queue. Direct NIs can be inefficient unless placed close to the processor. Anticipating continued system integration, we place our NI on the processor-cache bus. The CNI paper showed how to partly compensate for a more distant NI by exploiting standard cache-coherence support [55].

Memory-based interfaces, Figure 8-1b in multicomputers [6, 9, 65, 68, 71] and workstations [16, 18, 75, 76] provide easy protection for multiprogramming if the NI also demultiplexes messages into per-process buffers. Automatic hardware buffering also deals well with sinking bursts of messages and provides the lowest overhead (by avoiding the processors) when messages are not handled immediately.

Memory-based application interfaces provide low overhead when access to the network hardware is relatively expensive (true for most current systems), when latency is not an issue so that messages can be handled in batches, or when buffering is actually required. Increased integration of computer systems and the mainstreaming of parallel processing challenges these assumptions. On-chip network interfaces can have low overhead. Further, parallel programs frequently require low latency; so much so that they may require coordinated scheduling to keep latencies low and predictable. Coordinated scheduling has the effect of reducing the need for buffering. Buffering may still be required occasionally for protection reasons but the occasions are rare.

Direct interfaces tend to provide the best performance while buffering provides a means of solving the undeliverability problem. Table 2-1 summarizes the tradeoff between direct and memory-based interfaces by listing the operations required to receive messages using each of the control transfer mechanisms described in Section 2.1. For instance, messages received via interrupt using a direct interface (Figure 2-1, middle left) suffer the overhead of a user interrupt and the (minimal) overhead of reading the message payload from the tightly-coupled network interface. The direct interface is assumed to be accessed via load/store instructions that proceed at the speed of the level 1 cache. In contrast, the buffered interface suffers two extra overheads for reception via interrupt (Figure 2-1, middle right): the cost of reading data from memory and the cost of buffer management.

There are three other observations to make about this table. First, interrupts are demanding: it

| Delivery          | Delivery of data                  |                                         |  |

|-------------------|-----------------------------------|-----------------------------------------|--|

| of control Direct |                                   | H/W Buffered                            |  |

| Polling:          | <inter-poll time=""></inter-poll> | <data in="" memory="" placed=""></data> |  |

|                   | Poll on network                   | <inter-poll time=""></inter-poll>       |  |

|                   | Read data from network            | Poll on memory                          |  |

|                   | Run handler                       | Read data from memory                   |  |

|                   |                                   | Run handler                             |  |

|                   |                                   | Buffer management                       |  |

| Interrupt         | Interrupt                         | <data in="" memory="" placed=""></data> |  |

| w/upcall:         | Read data from network            | Interrupt                               |  |

|                   | Run handler                       | Read data from memory                   |  |

|                   |                                   | Run handler                             |  |

|                   |                                   | Buffer management                       |  |

| Interrupt         |                                   | <data in="" memory="" placed=""></data> |  |

| w/thread:         |                                   | OS: Interrupt                           |  |

|                   |                                   | OS: Schedule thread                     |  |

|                   |                                   | OS: Run handler thread                  |  |

|                   |                                   | Read data from memory                   |  |

|                   |                                   | Run handler                             |  |

|                   |                                   | Buffer management                       |  |

|                   |                                   | OS: Reschedule thread                   |  |

**Table 2-1.** The sequence of operations used to receive a message for direct and memory-based data access modes using polling, upcall-based user interrupts and a thread signaled by an interrupt. Buffered operations differs from direct in the addition of overhead to store and fetch message data from memory and of buffer management overhead. Polling differs from interrupts by avoiding interrupt overhead, but adds the overhead of failed polls and the latency due inter-poll time. Thread-based interrupt handling differs from upcalls in the addition of scheduling overhead.

is easy for the overhead and latency of interrupts to become high, especially if a full thread model (Figure 2-1, lower right) is used. Second, polling can be either faster or slower than interrupts. The overhead of a successful poll is almost certainly lower than the overhead of an interrupt, but not all polls are successful and a polling application suffers additional latency due to the time between poll points. Third, most of the costs of control transfer and of memory access can be made to disappear if the application can be written so that messages are handled in *batches*. A memory-based interface then amortizes memory access costs over cache lines or could even apply prefetching. However, depending on a batching effect in a design reduces the usability of an interface. In other words, it is easy to provide communication for embarrassingly parallel applications using any technique; the challenge is to support the widest range of applications.

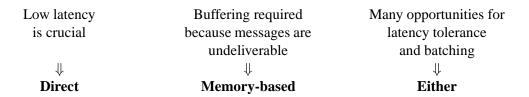

Between the demands of programmability and the consequences of protection, the best interface then depends on the situation:

Summarizing this section, the ideal VNI architecture and implementation in terms of performance would suffer the minimum amount of extra cost in all situations over what is absolutely required to support the communication model and protection. Since direct and buffered interfaces have different strengths, the ultimate solution is likely to be a hybrid. The solution described in this thesis is one such hybrid. Other hybrid approaches are discussed in the related work presented in Chapter 8.

#### 2.4 Problem Statement

The problem is to build a virtual network interface that addresses the three issues described in this chapter:

- 1. Programmability: The programming model must be an efficient target for the application programmer, a library developer or the compiler.

- 2. Protection: The system must coexist with flexible multiprogramming and the usual features of a multiuser machine (virtual memory) in order to support mixed workloads.

- 3. Performance: The implementation must be fast despite multiuser effects. Ideally the implementation is as fast as an implementation that is not burdened with multiuser features.

The design space is large and there is interesting work to be done in approaches that compromise one or more of the three points above. The goal of this work (and others), however, is to preserve all three points. The next chapter describes our solution.

## Chapter 3

## **A Direct Virtual Network Interface**

A virtual network interface must address the issues of programmability, protection and performance. This chapter introduces the heart of the thesis: a "direct" virtual network interface that achieves the three virtual network interface goals for message-passing communication with short messages. This chapter defines the programming and protection models and then overviews the architecture of the direct VNI that gives performance given the models. In other words, for the purposes of the thesis, the programmability and protection features are taken as design choices while the focus is providing good performance given these choices.

The direct VNI takes a novel approach to the VNI problem: the direct VNI provides a very low-level message model that optimistically maps to direct, user-level access to physical network hardware and then virtualizes that access through transparent emulation only when required for protection. The result is a solution that achieves performance near that of a single-user, all-hardware system with the flexible protection of a much more elaborate, software-based system.

The direct VNI achieves the goals of programmability, protection and performance:

- The direct VNI achieves the goal of programmability through its low-level model. The low-level model used is User Direct Messages (UDM), described here as well as by Kubiatowicz [39]. The particular model is arguably desirable, as we will show, but amounts to a design choice.

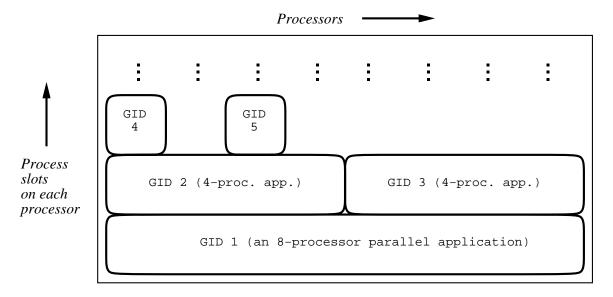

- The direct VNI provides protection that is compatible with multiprogramming, virtual memory and arbitrary scheduling policies, with some caveats. Isolation is based on labeling all the processes in an application with a single Group Identifier (GID) and permitting communication only between processes with the same GID. This protection mechanism is simplistic, but, combined with virtual memory and scheduling, produces the full set of undeliverability problems discussed in Section 2.2. The direct VNI architecture is thus applicable to systems with more general protection mechanisms.

- The direct VNI architecture achieves good performance because most messages proceed at hardware speeds, allowing performance approaching that of a dedicated, single-user machine without protection. The architecture achieves this goal via two techniques, two-case delivery and virtual buffering.

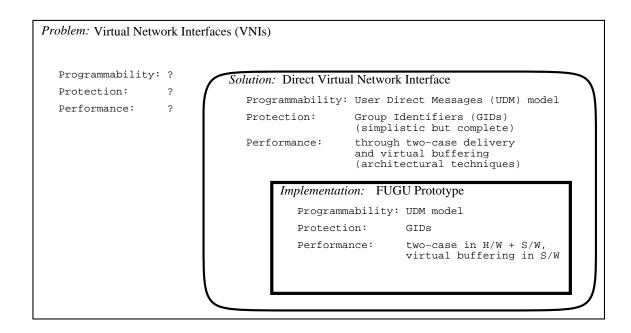

**Figure 3-1.** Summary of the problem, the solution to the problem at the architecture level, and the implementation of the architecture in FUGU.

Figure 3-1 depicts the relationship between the problem described in the last chapter, the solution architecture overviewed in this chapter and the architecture and implementation details to be described in subsequent chapters. Virtual Network Interfaces are network interfaces for multiuser machines. Any multiuser multiprocessor needs to address the VNI problem. The direct virtual network interface is the solution explored in this thesis. The focus of the thesis is on providing good performance given an aggressive, low-level communication model, represented by UDM, and a full set of protection features. The implementation applies the complementary architectural techniques of two-case delivery and virtual buffering in the FUGU prototype.

The remainder of this chapter is organized as a description of how the direct VNI addresses the issues of programmability, protection and performance as introduced in the previous chapter. Section 3.1 describes the UDM model which gives the direct VNI programmability. Section 3.2 describes the model of protection. The protection model used for this thesis is simplistic, but gives rise to the full set of protection-induced complications described in the previous chapter. Section 3.3 overviews the architecture of the direct VNI solution including the two-case delivery and virtual buffering techniques and describes how the solution achieves good performance. Section 3.4 concludes with a discussion of alternate design choices that arise at this point.

### 3.1 Programmability

The direct VNI addresses programmability by providing a low-level model, User Direct Messages or UDM. UDM is an abstract model for message-passing communication intended to represent a minimal but complete representation of the capabilities of a raw hardware interface. The UDM model is "programmable" in two senses. First, it is programmable in the sense that it is a natural, low-level

target for a programmer, for a compiler or as a building block for other protocols (*e.g.*, send/receive, RPC) in a library. Second, although it could be implemented in terms of other primitives, UDM is sufficiently low-level to be implemented efficiently as a direct interface in hardware. UDM primitives correspond one-to-one with network hardware primitives and UDM is thus "programmable" in that it exposes the fundamental costs of the hardware.

The novelty of UDM with respect to other low-level models (such as Active Messages [77]) is that UDM defines the *control* transfer mechanisms along with the data transfer mechanisms as part of the model. UDM includes both polling and a user-level interrupt for message delivery notification. The key feature is a set of *atomicity* (interrupt disable) operations that allow an application using UDM to construct message receive code with the same flexibility and efficiency as an in-kernel device driver.

UDM provides all of the facilities commonly desired from fast message interfaces within a multiprocessor: low-overhead message construction and launch, as well as low-overhead reception via interrupts or polling. UDM allows the programmer to view the network hardware as a dedicated, user-level resource with effectively unlimited buffering. The buffering serves as an aide to deadlock avoidance in user protocols. The network is virtualized in the same sense that the CPU and memory are virtualized in a virtual machine. It is up to the hardware and runtime system to maintain these illusion.

As mentioned above, UDM has two major components, corresponding to data and control. First, the UDM model has a notion of *messages*, which are the unit of communication, along with operations to *inject* messages into the network at the source and *extract* them from the network at the destination. Second, and uniquely, UDM provides an explicit *atomicity* mechanism, which is a low-overhead, virtualized interrupt disable. The atomicity mechanism grants user code explicit control over the arrival of message interrupts, allowing a smooth integration of both polling and interrupts as mechanisms for notification of message arrival. The data and control parts of the model are discussed below, followed by a discussion of unlimited buffering used for deadlock avoidance.

**Data Transfer Model.** Data are transferred as the payload of a *message*. A message is a variable-length sequence of words. Two of these words are specialized: the first is an implementation-dependent routing header which specifies the destination of the message. The second specifies a handler to be run at the destination to receive the message, as in Active Messages. Remaining words represent the data payload and are unconstrained.<sup>1</sup>

The semantics of messaging are *asynchronous* and *unacknowledged*. At the source, messages are injected into the network at any rate up to and including the rate at which the network will accept them. The injection operation is *atomic* in that messages are committed to the network in their entirety; no "partial packets" are ever seen by the communication substrate [38]. This atomicity property is useful for multiprogramming because it allows the output interface to be multiplexed preemptively easily. Message injection can be viewed in the following fashion:

<sup>&</sup>lt;sup>1</sup>The details of the data message constraints and layout are outside the scope of the UDM model. For concreteness, the following details are actually implemented in FUGU's direct VNI. First, the "destination" is a integer between 0 to P-1 corresponding to one of the P virtual processors in the current parallel application. Second, since the protection model (described in Section 3.2) limits messages to within a single application, the message "handler" is specified as the raw virtual address of the handler code. Third, the FUGU hardware supports messages of up to 16 words without the use of DMA.

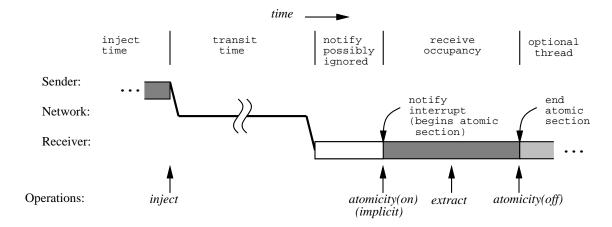

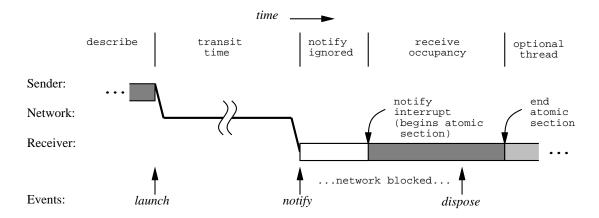

**Figure 3-2.** Message timeline for interrupt-based delivery on the fast path. The action at the sending node is at the top, at the network in the middle and at the receiving node at the bottom. The message is launched by an inject operation from a thread at the sender. After traversing the network, and after a possible delay due to interrupts disabled at the receiver, the arrival of the message invokes an interrupt handler at the receiver. The interrupt handler executes with interrupts disabled by default.

```

inject (header, handler, word0, word1, ...)

```

The inject operation may block temporarily if the message system is unable to proceed for any reason (e.g., resource contention in the network), but will eventually succeed. For performance reasons, blocking can be avoided by using a conditional, non-blocking version of inject, called injectc. Once a message has been injected into the network, the UDM model guarantees that it will eventually be delivered to the destination specified in its routing header.

At a destination, messages are presented sequentially for extraction.<sup>2</sup> A message is extracted from the network with an atomic operation that reads the contents of the message and frees it from the network:

```

extract() \Rightarrow (header, handler, word0, word1, ...)

```

Implicit in this syntax is that the message contents are placed directly in user variables without a redundant copy operation. The network provides a message available flag which can be examined to see if an extract operation will succeed. It is an error to attempt an extract operation when no message is available. Note that, in addition to the extract operation stated above, UDM provides a similar operation called peek which permits examination of the next message without dequeuing it.

By wrapping user-level network operations in inject and extract abstractions, UDM virtualizes these operations, permitting the underlying system to switch transparently between physical and virtual network access as needed. This is one of the central features of UDM, which we exploit for two-case delivery in later sections.

<sup>&</sup>lt;sup>2</sup>Message ordering is implementation-dependent. FUGU preserves FIFO ordering between pairs of virtual processors.