# PROJECT WHIRLWIND

Contract N5ori60

R-1777

A METHOD OF TEST CHECKING

AN ELECTRONIC DIGITAL COMPUTER

MARCH 15, 1950

SERVOMECHANISMS LABORATORY

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

**Copy** 37

Report R-177

A METHOD OF TEST CHECKING AN ELECTRONIC DIGITAL COMPUTER

Submitted to the OFFICE OF NAVAL RESEARCH Under Contract N50r160 Project NR-048-097

Report by Gerald Cooper

SERVOMECHANISMS LABORATORY

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

Cambridge 39, Massachusetts

Project DIC 6345

March 15, 1950 (Thesis Date: January 14, 1950)

#### FOREWORD

Because it presents information of lasting value, this thesis report, which has had only very limited distribution, is being issued as a Project Whirlwind R-series report.

Reliability of operation is one of the most important goals of the research being done on the large-scale electronic digital computer. Part of this general problem is the development of methods of error detection and trouble location. A very useful technique adopted by Project Whirlwind is the provision of facilities for the variation of d-c supply voltages to various parts of the computer. By this means, dynamic and incipient failures can be converted into steady-state failures, and deteriorating components removed before they cause errors.

This so-called marginal checking makes use of specially designed check problems. A method of designing such problems for use with the Whirlwind I computer is developed in this thesis.

# TABLE OF CONTENTS

| FORE  | NORD  |        |           |       |        |       |     |      |     |     |     |    |   |   |   |   | 2   |

|-------|-------|--------|-----------|-------|--------|-------|-----|------|-----|-----|-----|----|---|---|---|---|-----|

| ABSTI | RACT  |        | G & 4 & 2 |       |        |       |     |      |     | u   |     |    |   |   |   | ٠ | 7   |

| ACKNO | OMIED | GMENT  |           |       |        |       | •   |      |     |     |     |    |   |   | v |   | 8   |

| ORGAI | NIZAT | ion .  |           |       |        |       |     |      |     |     |     | ·  |   | 6 |   | 0 | 9   |

| 1     | INTR  | ODUCTI | ON        |       |        |       | ٠   |      |     |     |     |    | , |   |   |   | 10  |

|       | 1.1   | The A  | utomatic  | Die   | gital  | Comp  | ite | r.   |     |     | 0   | 0  |   |   |   |   | 10  |

|       | 1.2   | Relia  | bility    | 5 4   |        |       |     | a a  |     | •   |     |    |   | • |   |   | 11  |

|       | 1.3   | Princ  | iples of  | Che   | ecking | : .   |     |      |     |     |     |    |   | A |   |   | 15  |

|       |       | 1.31   | Built-    | în Cl | neckin | g.    | •   |      |     |     |     | o  | 4 |   |   |   | 16  |

|       |       | 1.32   | Program   | nmed. | Check  | ing   | ٥   | 0 0  | o   | •   | ,   |    | • | 8 | , | , | 17  |

|       | 1.4   | Scope  | of this   | The   | esis . |       |     |      | .0  |     |     |    | 6 |   | 0 |   | 50  |

| 2     | DESCI | RIPTIO | n of whi  | (RLW) | IND I  | •     |     |      |     |     |     |    | 3 |   |   | • | 21  |

|       | 2.1   | Machin | ae Unite  |       |        |       |     |      | d   |     |     | D  | , | D |   |   | 21  |

|       |       | 2.11   | The Bas   | ic I  | eatur  | 88 .  | •   |      |     | ۰   |     |    | 3 |   |   |   | 22  |

|       |       |        | 2.111     | The   | Flip-  | Flop  |     |      |     |     |     |    |   |   |   | ٥ | 22  |

|       |       |        | 2.112     | The   | Gate ! | Tube  |     |      |     |     |     |    |   |   |   |   | 23  |

|       |       |        | 2.113     | Resi  | torati | on.   |     |      |     |     | 4   |    | 0 | ٠ |   |   | 24. |

|       |       |        | 2.114     | The   | Elect  | ronic | S   | wit  | ch  |     |     |    | ٥ |   |   | 0 | 25  |

|       |       | 2.12   | Simple    | Comi  | oinati | ons o | of  | Bas  | ic  | St  | ae  | 99 | 1 |   |   |   | 25  |

|       |       |        | 2.121     | The   | Binar  | y Fl  | lp- | Flo  | p I | leg | gis | te | r | 0 |   |   | 25  |

|       |       |        | 2.122     | The   | Shift  | ing 1 | Reg | ist  | er  |     |     |    | a |   |   |   | 26  |

|       |       |        | 2.123     | The   | Binar  | y Add | ler |      |     |     |     |    |   | 0 |   | 0 | 27  |

|       |       |        | 2.124     | The   | Binar  | y Cou | ınt | er   |     |     |     |    |   | D |   |   | 28  |

|       |       |        | 2.125     | The   | Time-  | Pulse | e D | ist: | rib | ut  | or  |    |   | 0 |   |   | 29  |

|   |      | 2.13   | The Sys  | ten . |        | 0 0   | 0    |     | 9 6   |    | •   |   |   | ٥ | 0  | ,  | ٠ | . 29 |

|---|------|--------|----------|-------|--------|-------|------|-----|-------|----|-----|---|---|---|----|----|---|------|

|   |      |        | 2.131    | Centr | al Co  | ntr   | 1    | 0   |       |    |     | a |   | 0 | •  |    | 0 | . 30 |

|   |      |        | 2.132    | Test  | Stor   | ::-0. | •    | •   | • •   |    |     | c |   |   | 0  | 13 | • | . 31 |

|   |      |        | 2.133    | Arith | me tic | E1    | am € | nt  | 0 (   |    | a   |   | • |   | ۰  |    |   | .32  |

|   |      |        | 2.134    | In-ut | -Cut-  | ut I  | C1.e | me  | nt    |    |     | 0 | • | • | 9  | 9  | • | .33  |

|   |      |        | 2.135    | Pu118 | -In (  | Check | cin  | g   |       |    | •   |   | 9 |   | 0  | 5  |   | . 34 |

|   |      |        | 2.136    | Test  | Conts  | rol   | 6    |     | 9 (   |    |     |   |   |   |    |    |   | . 34 |

|   |      |        | 2.137    | Plect | rosts  | atic  | 98   | or  | a-ere |    |     | 0 |   |   | ٥  |    | 0 | . 35 |

|   | 5.5  | Machi  | ne Cycle |       | 4 9.   |       |      | •   |       |    |     |   | 0 | 0 | •  | 6  |   | .35  |

|   |      | 2.21   | Frogram  | Timi  | ng .   | . :   | 9    |     |       |    |     |   | • | • |    | •  | 9 | .36  |

|   |      | 2.22   | Cpereti  | on Ti | ring   | 0 6   | 0    |     | 0 6   |    | 6   | 0 |   |   |    |    | ٥ | .37  |

| \ | 2.3  | Progr  | emring a | nd Co | ding   |       |      |     | 0 4   |    |     | ٥ |   | • |    |    |   | .38  |

|   |      | 2.31   | Nomencl  | ature |        |       |      |     |       |    | •   |   |   | 0 |    |    | ۰ | .38  |

|   |      | 2.32   | The Ope  | ratio | ns .   |       | •    |     | ٥ .   | ۰  |     | 0 |   |   | .0 | •  |   | . 39 |

| 3 | DISC | recton | OF FAIL  | HDFC. |        |       |      |     |       |    |     |   |   |   |    |    |   | lin  |

|   |      |        | ificatio |       |        |       |      |     |       |    |     |   |   |   |    |    |   |      |

|   | 202  |        | Steady-S |       |        |       |      |     |       |    |     |   |   |   |    |    |   |      |

|   |      |        | Dynamic  |       |        |       |      |     |       |    |     |   |   |   |    |    |   |      |

|   |      |        | Incipie  |       |        |       |      |     |       |    |     |   |   |   |    |    |   |      |

|   |      |        |          |       |        |       |      |     |       |    |     |   |   |   |    |    |   |      |

|   |      |        | Intermi  |       |        |       |      |     |       |    |     |   |   |   |    |    |   | 17   |

|   |      |        | Febrodu  |       |        |       |      |     |       |    |     |   |   |   |    |    |   |      |

|   |      |        | Random   |       |        |       |      |     |       |    |     |   |   |   |    |    |   |      |

|   | 3.2  |        | ing Cons |       |        |       |      |     |       |    |     |   |   |   |    |    |   |      |

|   |      |        | Influen  |       |        |       |      |     |       |    |     |   |   |   |    |    |   |      |

|   |      | 3.55   | Operat1  | onal  | rifed  | ta c  | 2    | Fa. | ilu   | TO | B . | 0 | 0 |   |    |    |   | .45  |

|   |      |        | 3.22  | 21   | Ampl        | 111      | ere          |       |     | 9     |              | et i |       | 4   | 9            |      | 0   | 0   | 60 |   |   | .46  |

|---|------|--------|-------|------|-------------|----------|--------------|-------|-----|-------|--------------|------|-------|-----|--------------|------|-----|-----|----|---|---|------|

|   |      |        | 3.22  | 303  | Gate        | Tul      | be .         |       |     |       |              |      |       |     | ò            |      | 6   | ý   |    | 3 |   | .47  |

|   |      |        | 3.20  | 23   | Fisp        | -F10     | age          |       | •   |       |              |      | p 18  |     | a            |      | 0   |     |    | 9 |   | . 48 |

|   |      |        | 3.22  | oli  | Port        | ore:     | r Pu         | 180   | 8   |       |              | а    |       |     | 3            |      | ۰   | ,   | 9  |   | • | . 49 |

|   | 3.3  | Margi  | nal ( | Chec | king        | n<br>1 0 |              | 0     |     |       |              | 6    |       |     | 9            | •    |     | à   |    |   | a | . 50 |

|   | 3.4  | Sura   | ry .  |      |             |          |              |       | •   |       |              |      |       |     |              |      |     | 0   | 9  | • |   | . 53 |

| ħ | Pulk | CTPL S | OF T  | resi | <b>9</b> 50 | UER      | מ אם         | esi   | GN  |       |              |      |       |     | 4            |      | 0   | 6   | ٠  |   |   | . 54 |

| * | 4.1  | Object |       |      |             |          |              |       |     |       |              |      |       |     |              |      |     |     |    |   |   |      |

|   | 4.2  | Histor |       |      |             |          |              |       |     |       |              |      |       |     |              |      |     |     |    |   |   |      |

|   | 4.3  | Propo  | sed I | roc  | edur        | · •      |              | ٠,    |     |       |              |      |       |     |              | ø    |     |     | •  |   |   | .56  |

|   |      | 4.31   | Subo  | 1171 | sion        | of       | the          | Co    | m i | uŧ    | er           | •    | . 0   | ۰   |              |      | •   | 9   | •  |   | ۰ | . 56 |

|   |      | 4.32   | The   | Che  | r.e1        | Con      | ocep         | 8     |     |       |              |      |       |     | •            |      | ,   | ٥   |    |   |   | . 57 |

|   |      | 4.33   | Use   | 02   | the         | Chai     | nnel         | Co    | nc  | ep    | *            | 0    |       |     |              | 0    | •   | 8   |    |   | • | .58  |

|   |      | 4.34   | Mult  | tipl | e Fa        | ult      |              |       |     |       |              |      |       |     |              | 0    |     | 9   |    |   |   | . 59 |

|   |      | 4.35   | Troi  | ible | Loc         | atio     | on .         |       |     |       | •            |      |       |     | •            |      | •   | •   |    | • |   | . 61 |

| 5 | EXAM | PLES O | F DE  | SION | FFO         | 0700     | JRE          |       |     |       |              |      |       |     |              |      |     | 6   |    |   |   | . 63 |

|   | 5.1  | Single | e Far | 11.6 | Sequ        | enc      | 88.          | ۵     |     |       |              |      | b 0   | ٥   | 0            |      | •   | ٥   |    |   |   | . 63 |

|   |      | 5.11   | Arit  | time | tic         | Conf     | trol         | Fl    | ip  | an E. | 1.0          | ps   |       |     | 0            | 9    | ę   | a   |    |   |   | . 63 |

|   |      |        | 5.11  | 11   | Chan        | nel      | Seg          | men   | 8   | 1     | -            | 31,  | m     | Co  | n <b>t</b> 1 | rol  |     | 0   |    |   |   | . 64 |

|   |      |        | 5.11  | rs   | Chan        | nel      | Seg          | men   | \$  | 2     | 400          | Mu   | 1 1 1 | rl; | y            | 0    | •   |     |    |   |   | . 65 |

|   |      |        | 5.11  | 13   | Chan        | mel      | 50g          | De n  | ts  | 3     | A            | an   | 1 3   | B.  |              | 51-4 | 121 | 2 . |    |   | ٥ | . 67 |

|   |      |        | 5.11  | 14   | Chan        | nel      | Seg          | men   | t   | 4     | -            | D4.  | rić   | le  |              | •    |     | •   |    |   |   | . 68 |

|   |      |        | 5.13  | 15   | Chan        | nel      | Seg          | man   | \$  | 5     | <b>(80</b> ) | Sp   | ec 1  | al  | -A           | h    |     |     |    |   |   | . 73 |

|   |      |        | 5.12  | 16   | Chan        | nel      | Seg          | m r m | ŧ   | 6     | 40           | Po   | int   | -0  | r            |      |     | 0   | 9  |   |   | .72  |

|   |      |        | 5.13  | 17   | The         |          | plet<br>trol |       |     |       |              |      |       |     |              |      |     |     |    |   | • | .72  |

|   |      | 5.12   | Inpu  | 15-( | ut u        | e E      | l em e       | nt    |     |       | •            |      |       |     |              |      |     | ٠   | 6  |   |   | . 72 |

| 5.121 In-Out Register                             | 74   |

|---------------------------------------------------|------|

| 5.122 In-Cut Control Flip-Flops                   | 77   |

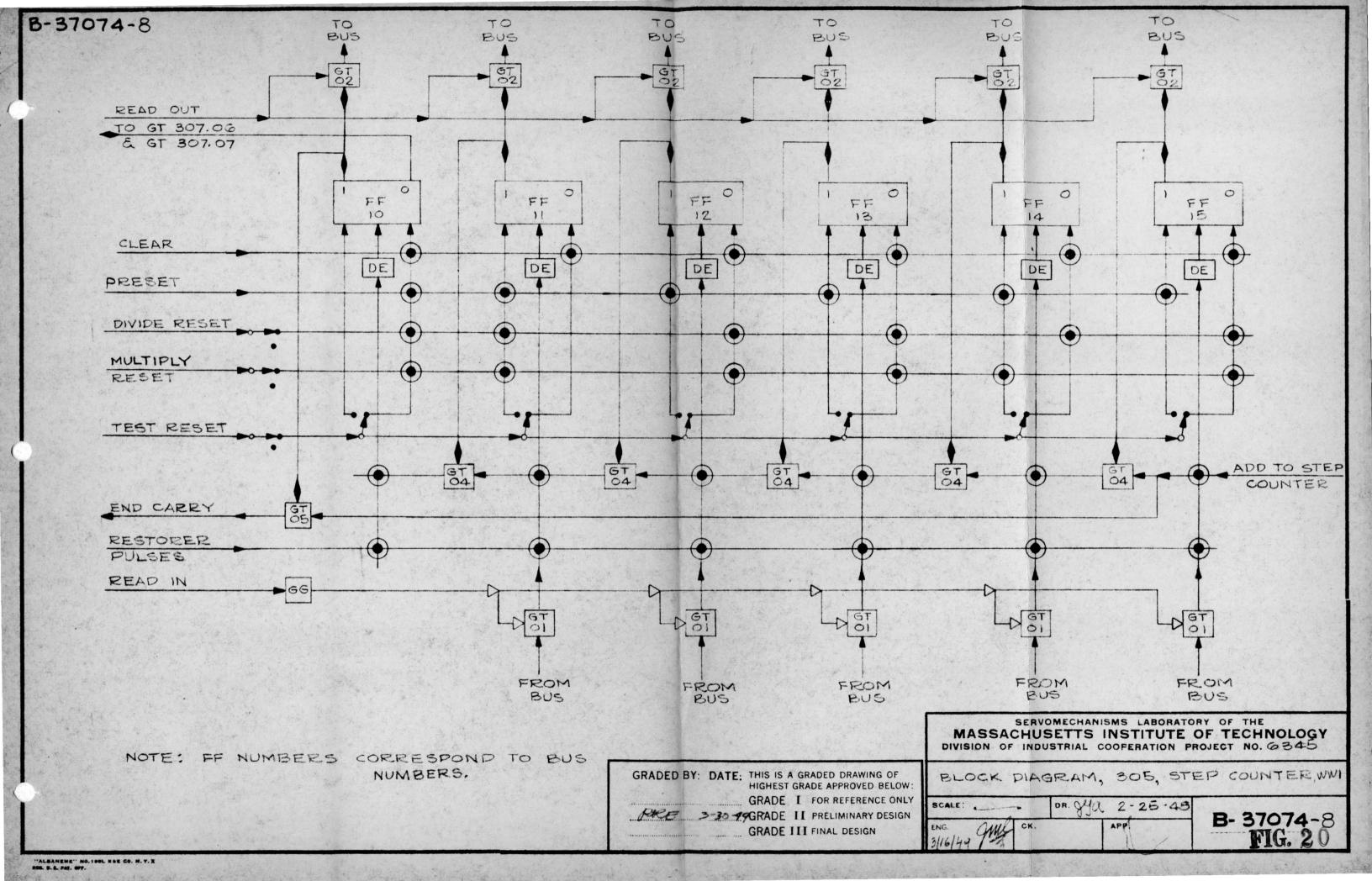

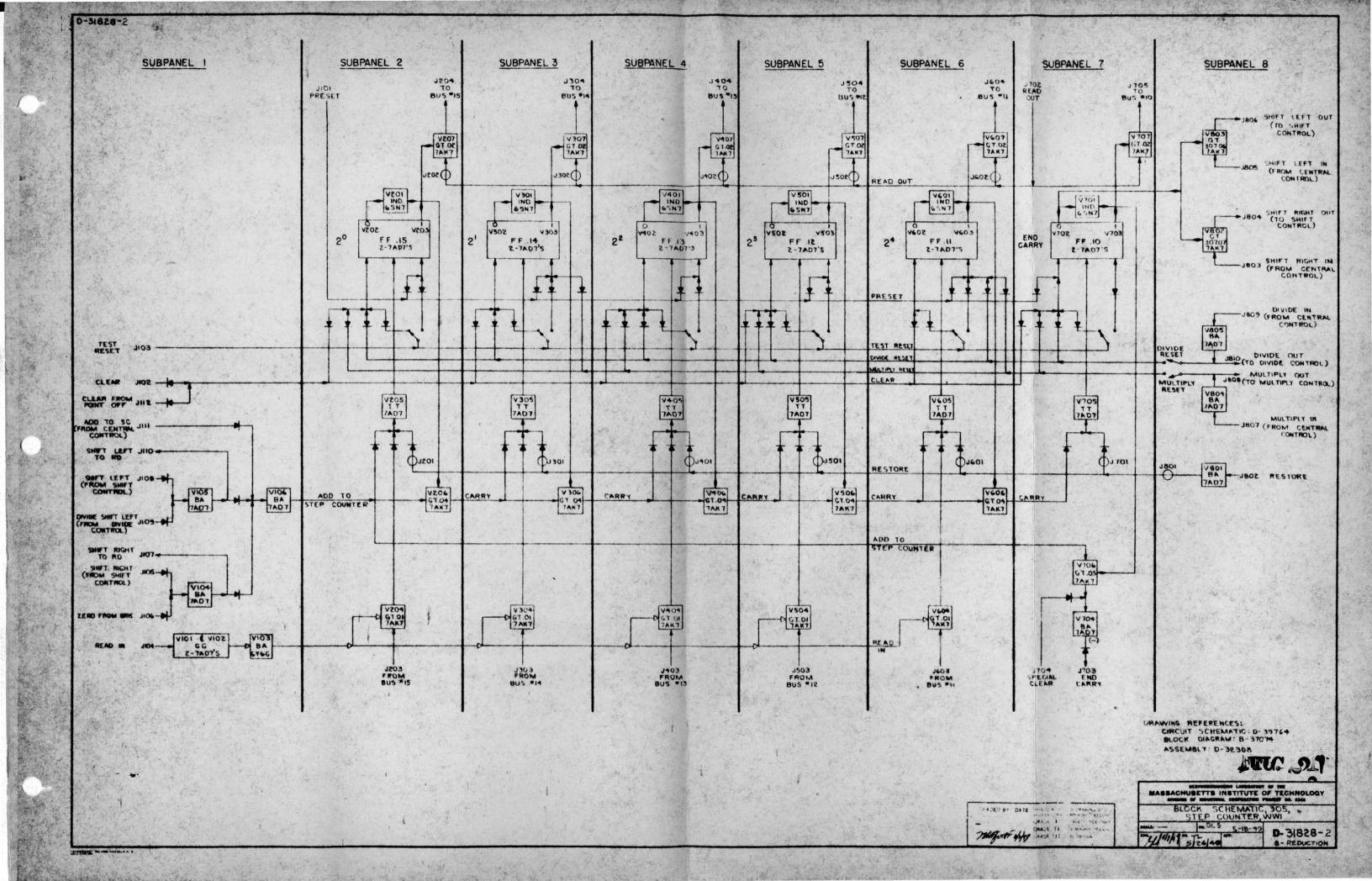

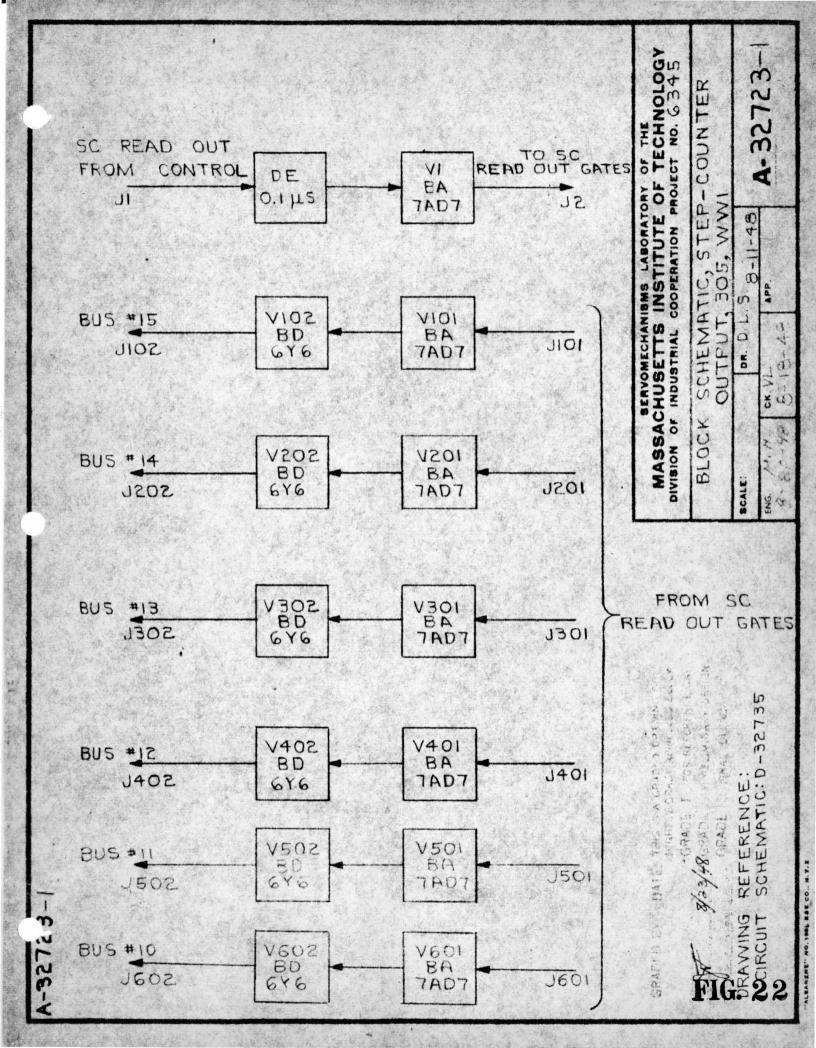

| 5.13 Step Counter                                 | 79   |

| 5.131 Step Counter Flip-Flops                     | 81   |

| 5.132 Step Counter Cate-Tubes                     | 8H   |

| 5.2 Fultiple Faults - The Program Counter         | 85   |

| 5.3 Trouble Location - Control-Pulse Out-ut Units | 91   |

| 6 RESULTS AND CONCLUSIONS                         | 95   |

| 6.1 Experimental Results                          | 95   |

| 6.11 Discussion of Low Margin on Line 113         | 97   |

| 6.12 Discussion of Low Fargin on Line 79          | 98   |

| 6.2 Evaluation of the Design Procedure            | 99   |

| 6.3 Surgestions for Further Work                  | 101  |

| AFFENDIX I - A Short Guide to Coding              | 102  |

| AI SEDIX II - Details of Goded Programs           | 105  |

| ATTENDIX III - Glorsery                           | 110  |

| SIFLIOCRAPHY                                      | 111  |

| LIST OF ILLUSTRATIONS                             | .113 |

| ILLUSTRATIONS                                     | 114  |

#### ABSTRACT

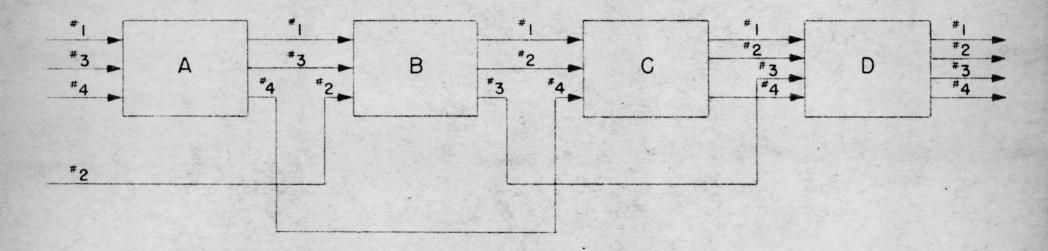

This thesis study describes a method of designing check problems to be used in detecting errors and locating trouble in a large-scale digital computer. The computer is systematically subdivided into small sections. A study is made to determine the paths (channel segments) in these sections along which information is routed, as well as the sources, destinations, and methods of transmission of the information.

One of these methods is selected for the routing of each type of information from one of the sources to one of the destinations of each channel segment. The destination is then examined to see whether it received the proper information.

This process, used in conjunction with the Project Whirlwind method of marginal checking, permits a sequence of instructions

to the computer to be specified. Limited tests in the Whirlwind I

computer indicate that test sequences designed by this method will

be quite useful.

#### ACKNOWLEDGEMENT

The author wishes to express his sincere thanks to Mr. N. H.

Taylor for supervising this thesis and making many helpful suggestions for the conduct of the work and the preparation of this report. He is also indebted to Mr. J. W. Forrester for making available the facilities of Project Whirlwind for the treparation of this thesis. Thanks are also due to the personnel of Project Whirlwind with whom the author had several stimulating and helpful discussions, particularly to Mr.

R. R. Werett, Mr. C. W. Adams, Mr. J. M. Salzer, and Mr. R. P. Mayer.

#### ORGANIZATION

This thesis deals with a very specialized to ild which requires considerable background material for its complete treatment. The first three chapters provide most of this material while develoring some of the bases for the method presented. In detail, the material is arranged as follows:

Chapter 1 presents the problem of checking digital commute a and indicates some possible solutions.

Chapter 2 is a fairly detailed description of the operation of Wil.

Charter 3 discusses the nature of failures and their influence on checking procedures.

Chapter 4 presents a systematic approach to designing special problems to check the operation of the computer.

Chapter 5 gives a number of examiles of the applications of the approach to checking WVI.

Chapter 6 discusses and evaluates the results of the thesis.

Appendix I is a short guide to coding prepared by the Electronic Commuter Division of the Servomechanisms Laboratory, N.I.T.

Appendix II contains the coded programs which have been developed by the method described in this thesis.

Appendix III contains a glossory of special terms used in this thesis.

#### 1 - INTRODUCTION

### 1.1 The Automatic Digital Computer

numerical problems. It is capable of performing entirely automatically any desired sequence of arithmetic operations on given data. This is in distinction to analogue commutation where the data is handled as physical quantities in a system obeying rhysical laws having the same form as the operations involved (see Fig. 1). It also has the ability to choose among several alternate computing routines on the basis of its own calculations. A wide variety of problems can be solved through the use of the automatic di ital corruter because of the great flexibility implied in these properties. The high calculating speed which is characteristic of the automatic digital consuter, makes it varticularly valuable because of the great number of problems whose solution by more customery means, though possible in principle, is impossible in a practical sense because of the prohibitive amount of time and labor involved.

As one might suspect, a rather complicated device is required to accomplish these results. For example, Whirlwind I (WWI), the electronic digital computer under development at the F.I.T. Servomechanisms Laboratory, consists of approximately 4500 vacuum tubes plus associated components such as resistors, capacitors, inductors, and crystal rectifier diodes. Good computer design requires that each individual component be operated under conditions that ensure as long a life as possible. Nevertheless, each

Superscripts refer to the numbered bibliography.

component will eventually fail to operate satisfactorily. When such a failure occurs, it is quite likely, though by no means certain, that an error will appear in the computed results. Such errors, if they remain undetected, may cause considerable damage. There is no longer any doubt that computers can be made to work; the tables of functions calculated at the Harvard Computation Laboratory have amply demonstrated this fact. The ouestion is: how consistently will they provide correct results? Reliable results must be obtained if the latent value of the automatic digital conputer is to be realized in practice.

#### 1.2 Peliability

but they are also inevitable. This is not just a reculiarity arising from the use of the autoratic digital computer; other methods of problem solution are also subject to error. What level of error occurrence can be telerated? Pefore this question can be answered quantitatively, a considerable amount of statistical data must be accumulated. It will be difficult to interpret such data on a comparative basis because of the speed differences among various methods. The amount of computation which can be done during the periodetween errors must be taken into consideration in some suitable manner. Thus far, only qualitative reasoning has been applied to this problem. Rowever, one error per week has been suggested by a leading authority as a reasonable goal for a computer of the same nature as Whirlwind I.

This statement was rade by J. W. Forrester during a discussion of his talk -t the Harvard Symposium on Large-Scale Digital Calculating Machinery on September 13, 1949. The proceedings of this symposium have not yet been published.

The fact that errors will occur does not mean that we must be resigned to accept erroneous results. There are many methods for checking on the validity of calculated results (see section 1.3 and references 6 and 9). Then it is known that a particular result is in error, it is usually possible to remove the source of the error and then proceed to calculate the correct value. Thus, by using these methods, the effective reliability of the computer can be increased tremendously, although the speed is reduced somewhat. Of course, there are a number of applications in which time is an important factor so that there is no time available for a second calculation under error-free conditions. Such applications will require very special techniques to achieve satisfactory reliability, but error detection is essential even then.

errors, for it is certainly conceivable that two failures can occur simultaneously in such a way as to multify the method being used. This is not to say that there is no method for detecting errors caused by two compensating, simultaneous failures. It is always possible, at least in principle, to devise a scheme which will detect any specified combination of faults, but in the most general case, additional equipment would be required.

This additional equipment would give rise to new combinations of faults which could not be detected without further resort to extra equipment.

For a given computer, there will always be some combinations of faults which cannot be detected without changing the computer. It becomes necessary to decide upon an adequate degree of error detection. Here the economics of the situation is an important factor. Since any desired level

of checking can be provided at the cost of either soney or time, some balance must be achieved between conflicting interests. It seems to be quite generally agreed that the probability of an undetected error cocurring in a machine which is checked in all cases of single failures is sufficiently low. However, any method which provides a check in many cases of multiple faults at little extra cost should be carefully considered.

As mentioned previously the time required to detect an error by a given method is frequently of vital importance in applications where time. is a factor. These may be exemplified by the problem of directing the flow of air traffic in accordance with the specified schedules and the actual positions and velocities of the aircraft involved. 13 The computer is used. to correlate this data and surrly the appropriate instructions to the pilots of the sircraft regarding the flight pattern to be maintained. When these instructions are in error, the pilots and the operator of the control tower should be informed immediately so that arroppriate emergency measures may be taken. The importance of instantaneous error detection is quite evident in this cass. Indeed we may even look askance at the fact that it is possible for some errors to go undetected. However, we must remember that it is quite possible for the sircraft itself to fail. This is a very special case and the accuracy requirements imposed are far greater than would be encountered in rost ordinary arclications. Even where the danger to human life is not so immediate, speed in error detection is quite important. A considerable amount of erroneous commutation might be accumulated before an error is detected. This will be wasteful, but it is again difficult to pass other than a qualitative judgment on the value of speed in error detection. In general, speed is actieved at the cost of equipment

and additional equipment is another source of trouble, aside from the monetary aspects involved. It may be said, with little fear of contradiction, that it is preferable to save equipment at the cost of time, all other factors being equal.

Once a failure is known to exist, the next step is to repair it. Pefore any repairs can be carried out, the faulty component must be located. Conventional methods of trouble location in small pieces of equipment are completely inadequate for a job of this ramnitude. Special autoratic methods must be devised to isolate the faulty component. It is not accesary to locate the specific component by these automatic means, but the fault should be isolated to a unit in which conventional techniques may be employed in a reasonably short time. A computer which makes one arror a week cannot be said to be very reliable if it takes a week to locate its source. In that time, another error may have occurred and another week of troable location is in prospect. Under such conditions, all of the operating time of the computer would be taken up in trouble location. The useful outrut would be practically mil. It does not seem unreasonable to expect that the computer perform useful work during at least half the time it is operating. Indeed, this would be a rather poor corputer. On the other hand, it takes a finite arount of time to make the actual repairs. Experience with Whirlwind I indicates that this time is of the order of magnitude of 15 or 20 minutes, on the average. It is pointless to go to great lengths to develor an automatic trouble location scheme which isolates the fault within a few seconds. 20 A rerfectly satisfactory method would be one which located the faulty component in less than 10 minutes. This would mean that approximately an hour would be required

Less than 1% of the operating time of the computer (assuming one error per week) would be lost for this reason.

the detection of errors in the operation of the entire computer. When an error is detected by such a method, the faulty component is known to be somewhere in the computer. Thus a measure of trouble location has been achieved, even though it is of dubious value. When an error is indicated by a method devised to check a relatively small unit, the faulty component is known to exist in that unit. A large measure of trouble loc: tion has been achieved. There is no difference between checking and trouble loc: tion. The distinction is one of degree rather than kind.

## 1.3 Principles of Checking

methods is that of providing a suitable standard to compare with the results obtained from the unit being checked. The choice of the size of the unit to be checked depends on the degree of trouble location that is desired. It is clear that if no fault exists in any of the small units which comprise the computer, then no fault exists in the entire computer. Thus, if a scheme is devised to check every small unit of the computer, including all their interconnections, then this cheme checks the entire computer. The various methods which have been suggested thus far differ in the flexibility with which they may be applied units of varying size.

There are essentially two different amroaches to the roblem of generating a commercian standard: built-in checking and programmed

checking schemes. In programmed checking, the computer treats the calculation of this standard as another problem which it can solve. Built-in checking permits higher computing speeds but requires more equipment than program ed checking. More than one type of checking is frequently used in a computer. The amount of each type is dictated by economic considerations.

## 1.31 Built-In Checking

an identical one to duplicate its function. The results obtained by the duplicate unit are a standard with which to compare those of the original unit. A special unit is provided to make this comparison. If an error is detected, it may have been caused by a failure in either unit. It is also possible (though improbable) for the same failure to occur in both units simultaneously, giving a correct check in the presence of an error. This has been discussed in section 1.2 and is not a serious objection. It is, of course, possible to provide three or more identical units to guard against such double failures. However, none of the existing or projected computers has incorporated more than two sets of identical equipment because of the cost involved. Checks of this type are known as multiple checks. Sultiple checks are generally used for large units; the number of comparison units required when small units are involved is felt to be excessive.

A more efficient use of checking equipment is achieved by a comvarison of some identifying characteristic (or tag) of the actual and

expected results rather than the results themselves. Such checks are called tag checks; "casting out nines" is a tag check used in decimal multiplication. In some very special cases, certain characteristics of the result of an operation may be independent of the numbers involved. It is frequently advantageous to provide a check which takes cognizance of the situation. An example of such a predetermined check is given in section 5.12.

A more detailed discussion of built-in checking may be found in reference 6.

#### 1.32 Program ed Checking

The process by which a problem is stated in a form suitable for solution by a computer is called programing. Thus, those checking methods which treat the generation of a comparison standard as a problem to be solved by the computer are referred to as programmed checking. There are two approaches possible to programmed checking: mathematical checks and test checking.

results of a calculation. Checking procedures based on these identities are applicable to all corruters for they are essentially another group of problems which are within the problem-solving capabilities of digital computers. There are certain types of identities which are encountered so freque thy that names have been assigned to the checking procedures which are based upon their use. However, there is undoubtedly a group of miscellaneous relationships which hold in special cases that cannot be fitted into such a classification. These miscellaneous techniques:

depend largely on the alertness and in-equity of the programmer and cannot be discussed here.

the solution of a problem is repeated a specified number of times and both (or more) sets of results are corpared. In identity checking, two (or more) equivalent mathematical procedures are used to obtain two (or more) sets of results for comparison. With some problems, a rather good check may be obtained by reversing the process of problem solution and finding the given initial data from the alleged solution, yielding what is known as inverse checking. In sample checking, the solution to a general class of problems is obtained for a special case in which the answer is known; the correct solution indicates that the computer is probably capable of solving this general class of problems. It is possible to examine the solutions of problems which are known to lead to continuous functions for continuity, thus giving rise to smoothness checking.

on the whole, mathematical checks are applicable to large groups of units and hence are not particularly useful in trouble location. They wary in effectiveness with the tyres of failures that exist, but they are quite useful for an overall check on a specific problem. It is not necessary to know that the whole comuter is working to be reasonably sure that the results are correct. Mathematical checks are discussed more fully in reference 6.

In test checking, the results obtained from the solution of specially designed problems are corpored with the known answers. Techniques for designing such problems have not yet been fully developed.

Most of the work in this field has been of an exploratory nature. 2,3,4,5,5,2,21.

The several amproaches which have been suggested are applicable only under very restricted conditions. The most severe shortcoming of some of these is that they make use of single functions in sequences which cannot be performed by the commuter. Each operation that the commuter performs consists of a predetermined sequence of such functions; the programmer may choose the sequence of operations arbitrarily, but he cannot do so with the functions. Some of the amproaches which do not suffer from this chortcoming may be quite useful in specific cases, but they lack generality. This thesis represents an attempt to develor a systematic amproach (for use with WWI) which is generally applicable to the design of such problems. The resulting problems will be referred to as test sequences.

endingenuity are valuable assets. Systematic ar reaches to programming have been proposed which are quite good, but a completely satisfactory method has not yet been found. 14,16,22,23 In many cases, much more efficient programs may be obtained more easily by rethods other than a literal application of the general method. This would seem to imply that a systematic method of test checking is not necessarily the best method in a specific case. Indeed, this thesis contains examples in which departures from the general method have been made in the interests of simplicity and efficiency. In short, the proposed method is only to be used where simpler methods are not immediately obvious.

## 1.4 Organization of This Thesis

is required to thoroughly exclain many of the examples of this thesis.

The paper would become quite unwieldy if all this detail were included.

Much of the information found in some of the references has therefore been omitted. 12,16,19 However, in order to make this paper reasonably self-contained, a considerable amount of material has been included. The procedure followed in this respect has been to give fairly detailed explanations of the basic elements, followed by examples to illustrate the manner in which more complex details can be explained in terms of the basic elements. The same procedure has been followed in explaining the examples of that sequence design.

Froject Whirlwind are defined in reference 15. Every effort has been made to define such terms when they are first used. As a matter of convenience, additional special terms have been adopted for some of the concepts arising in checking. These are defined when they are introduced and have been collected for easy reference in Arpendix III. Some, but not all, of these terms have come into standard usage at Project Whirlwind and elsewhere.

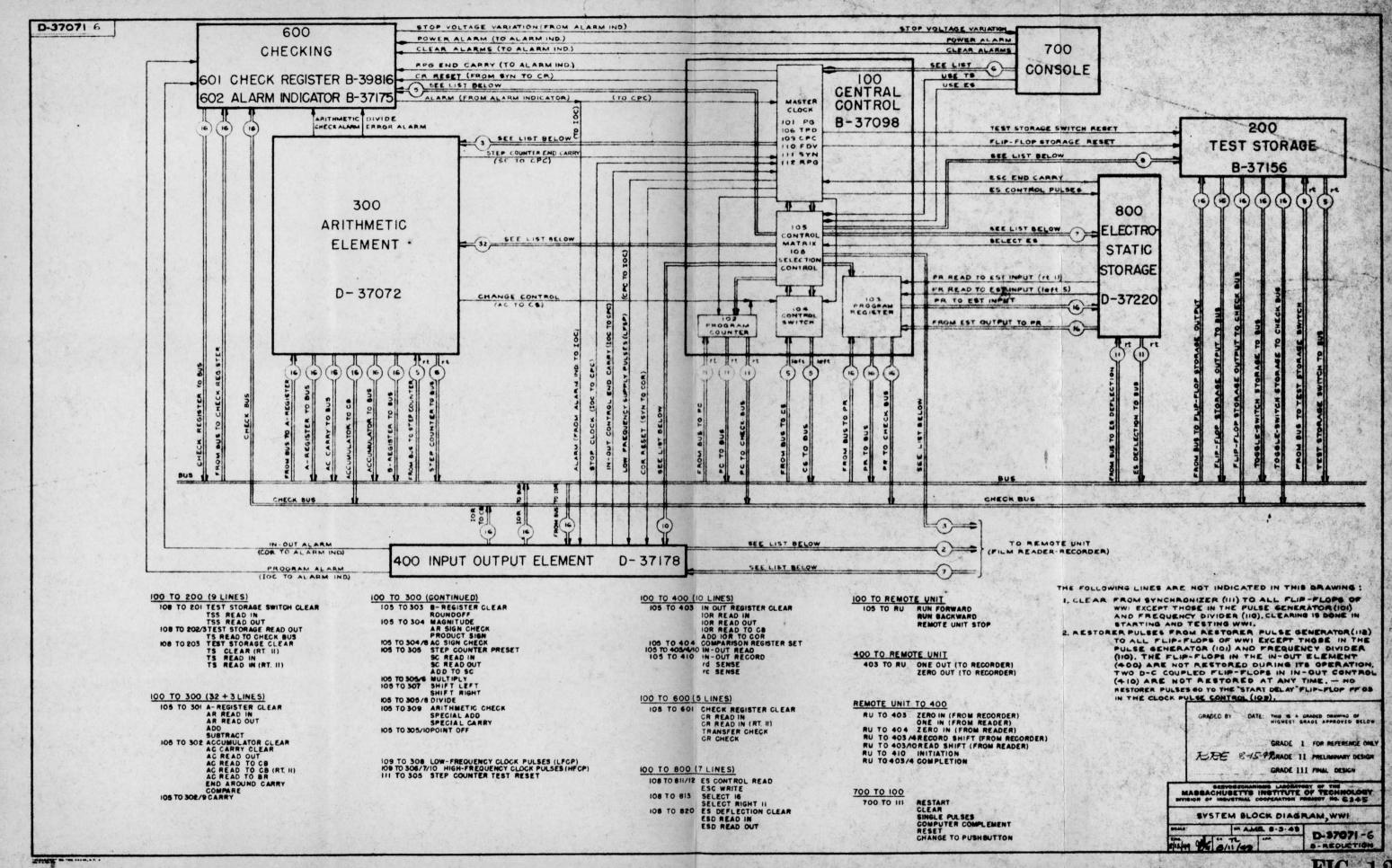

#### 2.1 Machine Units

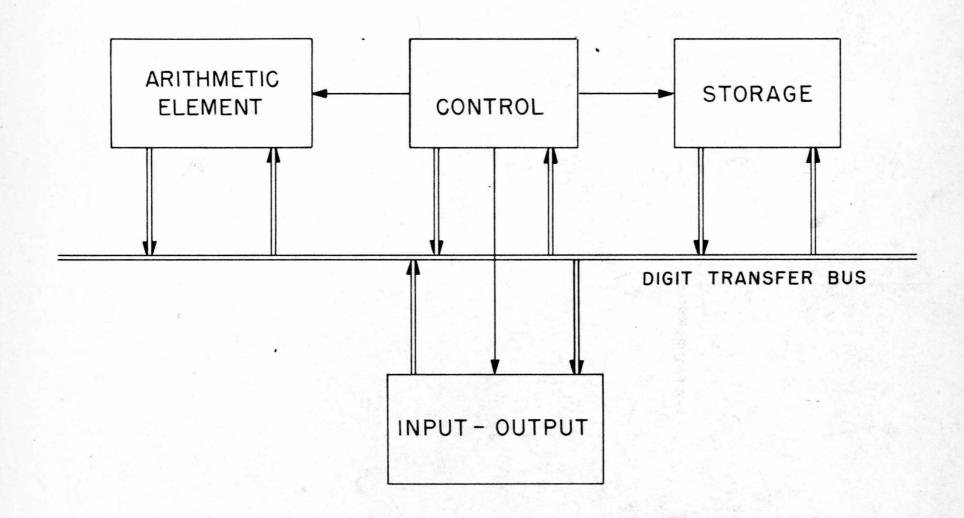

Whirlwind I (and, indeed, every computer) may be thought of as being divided into four main functional units: the memory (or storage), the control, the arithmetic element, and the input-output device (see Fig. 2). The memory stores the numerical data required for the solution of problems, as well as the instructions (coded into numerical form) which govern the actual steps of problem solution. The control interprets the instructions and provides the machine with the signals needed to perform them. The arithmetic element actually performs certain elementary arithmetic operations (addition, subtraction, shifting, multiplication, and division) whenever the control supplies the appropriate command signals. The input-output device is the link between the machine and the outside world; it provides the machine with raw data and receives the computed results. It is frequently used to supplement the remory by connecting a large-capacity external memory (having a slower operating speed) to the machine.

Two different devices are used for the internal memory of WWI.

These are the flip-flop and the electrostatic storage tube. The flipflop is discussed in section 2.111. The dectrostatic storage tube is

a cathode-ray type tube in which the numbers are stored as charged spots

on a dielectric surface. The final model of this tube is expected to

have a capacity equivalent to 1024 flip-flops, thus saving a considerable

amount of space. Its speed of operation is somewhat slower than that of

the flip-flop, but it is faster than magnetic tape or drum memories. The

control contrins a source of pulses which are routed to the rest of the computer in accordance with the settings of electronic switches. Flip-flops are used to manipulate the numbers in the arithmetic element. A great diversity of external equivment may be connected to the computer by means of the input-output element. Photographic film is expected to be the main external storage medium, but it will be possible to use provided so that analogue information may also be headled.

#### 2.11 The Pasic Features

With few exceptions, three basic stages are used throughout the con uter; the flip-flop, the gate tube, and the electronic switch. Of course, amplifiers are provided where needed to obtain appropriate signal or impedance levels. The flip-flop is essentially a memory device. The gate tube is a sensing device, usually employed to sense the contents of a flip-flop. The electronic switch is what its name implies a multiposition switch which operates at high speeds.

#### 2.111 The Flir-Flop

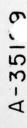

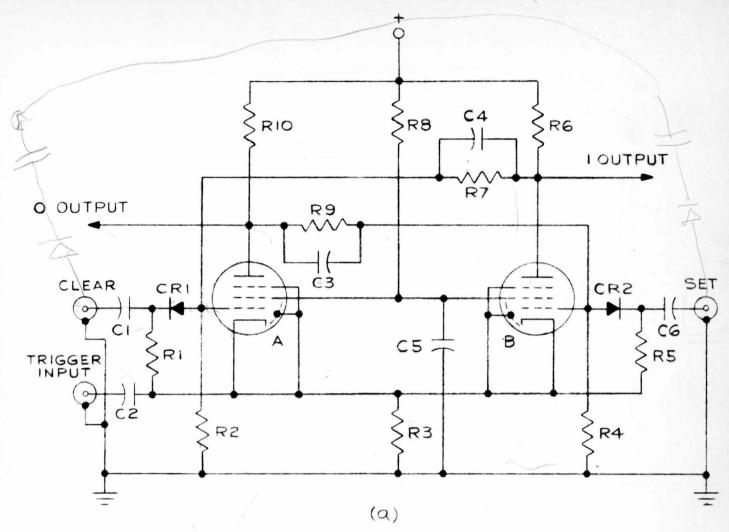

tubes so interconnected that, at any time, one is fully conducting and the other is completely cut off (see Fig. 3). The plate potential of the cut off tube is "high" (nearly equal to the plate supply voltage), while that of the conducting tube is "low" (considerably less than the plate supply voltage, the difference being the drop in the plate load resistor). If tube A (see Fig. 3) is cut off, the potential at the O output is high, that at the loutrut is low, and we say that the flip-flop contains O,

or is chared. If tube I is out off, the O outcut is low, the 1 output is high, and we say that the flip-flop contains 1, or is set. By applying a positive palse at an appropriate point in the circuit (the trigger in ut), the flip-flop may be nade to switch its state, i.e., if it formerly contained 0, it will now centain 1, or if it formerly contained 1, it will now contain 0. This action is referred to as triggering or complementing. There are two additional inputs which require negative rulses. On is the clear input, which puts the flip-flor in the clear condition regardless of its condition before the pulse was applied. The other is the set input, which outs the flip-flop in the set condition regardless of its previous centent. The flip-flop is eften represented symbolically by a rectangle having three input lines and two output lines, as is also shown in Fig. 3, and is abbreviated FF. Sach TF in WWI is designated by a system number.

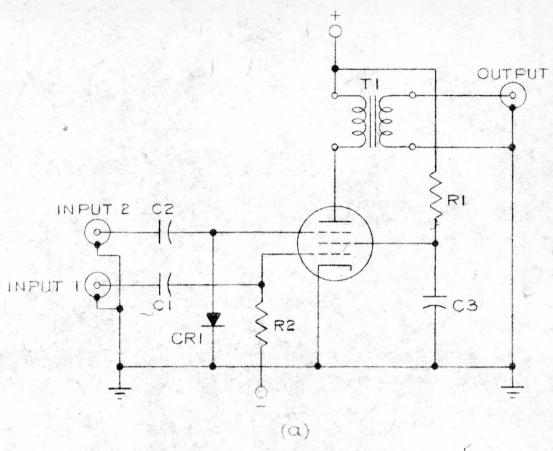

## 2.112 The Gate Tube

The gate tube is a coincidence device: it provides an output

if, and only if, two signals occur simultaneously. Its basic element

is usually a pentode, with one signal being applied to the control grid,

the other, to the suppressor grid (see Fig. 4). These two grids are biased

sufficiently to maintain the tube cut off even when full signal is applied

to one (but only one) of them. As mentioned above, its principal use is

in sensing the content of a flir-flop. If it is desired to know if the

flir-flor contains 1, we marely connect the 1 output to the suppressor

of the gate tube through a suitable coupling circuit. This coupling circuit must change the d-c level of the output but must preserve the distinction between the two possible voltage levels (see section 2.113). If the

I side is high, the super soor potential will be brought above cut-off, and there will be an out-ut rulse when the control grid is pulsed. The cute issaid to be open. If the I side is low, the superessor will remain below cut-off, and no output is obtained when the control grid is pulsed. The gate is said to be closed. Thus, the presence of a pulse on the output line at the time of sensing indicates that the flip-flop contains 1, while the absence of a rulse at t is time indicates that it contains 0. The gate tube is represented symbolically by a square having two in ut lines and one output line, as shown in Fig. 4, and is abbreviated as GT. Each CT in Wall is designated by a system number.

#### 2.113 Restoration

its output takes on the characteristics of a d-c signal. Bather than use d-c courling circuits, the scheme of peridocially complementing and recommending the flip-flops was adopted to permit the use of n-c courling circuits. This scheme is called restoration and the pulses which are used to complement and recomplement the flip-flops are called restorate pulses. The restorer-pulses occur in pairs with an interval of 1 usec. between them. These restorer-pulse pairs are repeated at a fixed interval (except during the operation of electrostatic storage) of 16 usec. between the first pulses of successive pairs (the restorer interval). The surply of pulses to the computer is suppressed during the in erval occupied by the restorer-pulse pairs, so that operations are not carried out while the flip-flows contain the complements of the numbers they are supposed to hold.

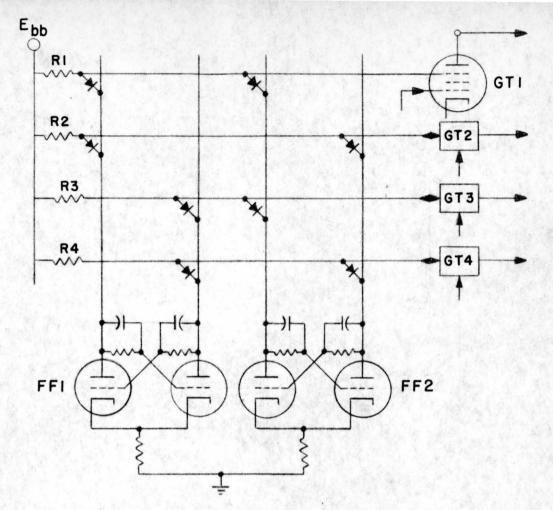

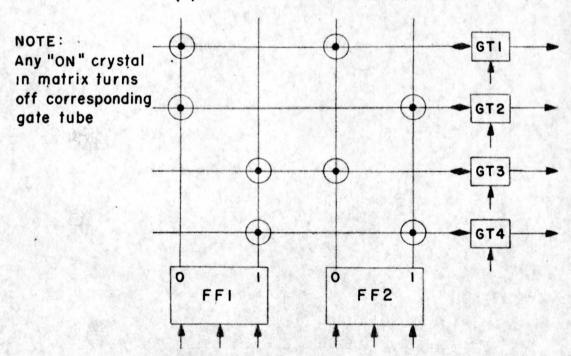

## 2.114 The Electronic Switch

open, depending on the contents of a flip-flows (see Fig. 5, drawn for a = 2). Plate current for the flip-flop tubes sust pass through the diods matrix and all but one of the resistors (R1,R2,R3, and R4). If, for example, the right hand tubes of both flir-flops should be conducting, current will be drawn through R2, R3, and R4. No current will flow through F1 because it is con exted only to the left-hand tubes. Thus the upper line will be at a positive potential with respect to the others and the gate tule connected to it will be placed at a positive potential with respect to the others and the respect to the others and the case to the others for each different combination of flip-flo contents. An altern to form of electronic switch, using give tules rather than a diode matrix, is frequently used.

# 2.12 Simple Combinations of Paste Stages

There are many possible ways of combining the basic stages to obtain devices capable of performing the functions required in a computing machine. To illustrate these possibilities, some of the rore company encountered combinations will be discussed below. The symbols used in the various diagrams are explained in Fig. 6.

# 2.121 The Binary Flip-Flop Pegister

A collection of n flip-flors is essentially a memory device capable of storing an n-digit binary number. By permanently assigning each flip-flop to a particular digit column of the number, the so-called binary flip-flop register is obtained. Three digit columns of a typical

register, the A-register (AR), are shown in Fig. 7. Three sets of gats tubes are provided so that the number in the register may be examined, two sets on the 1 side, one set on the 0 side. A pulse applied to one of the cets on the 1 side will cause the number contained in the A-register to amear on the out ut lines of that set. One set is used to transfer the number in the A-register to the Accumulator (CTO5, when the add line is rulsed), while the other set transfers this number to the "bus" (CTO2, when the read-out line is pulsed). The bus may be connected to any of several units. The set on the 0 side is used to obtain the "nines-complements" of the number (obtained by replacing each 0 by 1 and each 1 by 0, see A rendix I) for use in subtraction (CTO4, when the subtract line is pulsed). The read-in gate tubes (CTO1) serve as switches through which the bus may be connected to the in ut of the A-register when a gating signal is applied. It might be remarked that the flip-flows associated with the electronic switch in reality form a binary register.

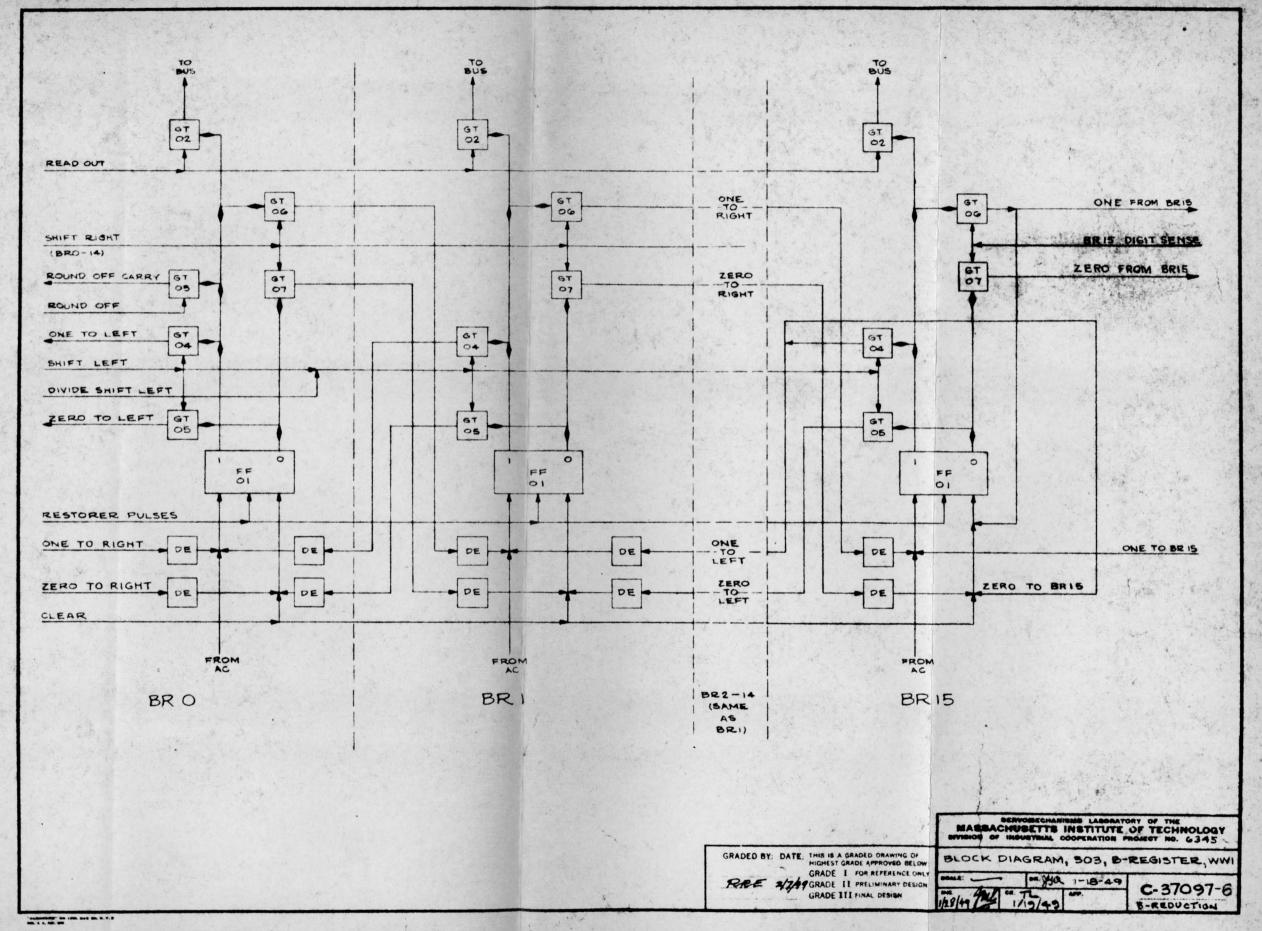

## 2.122 The Stifting Perister

A register in which provision has been rade to shift its contents either to the left or to the right is called a shifting register. Three digit columns of a typical shifting register, the B-register (BR), are shown in Fig. 8. The facility to shift the content of each digit column one digit column to the left is provided by GTO4 and GTO5. The facility for shifting right is provided by GTO6 and GTO7. The mechanism of shifting is quite simple. Consider shift left. If a particular digit column contains 1, a pulse will agreen on the output of GTO4 when the shift left line is pulsed. After a slight delay, the flip-flop of the

digit column to the left will be set by this pulse. If the digit column had contained 0, a pulse would have been obtained on the output of 6505 (instead of 6504) which would clear the flip-flow to the left. Hence, the content of the criginal digit column would agreer in the next digit column on the left. This process is carried on simultaneously for all digit columns, with some special conventions adopted to handle the columns at each end of the register.

## 2.123 The Binary Adder.

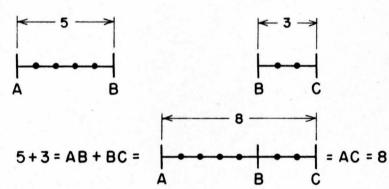

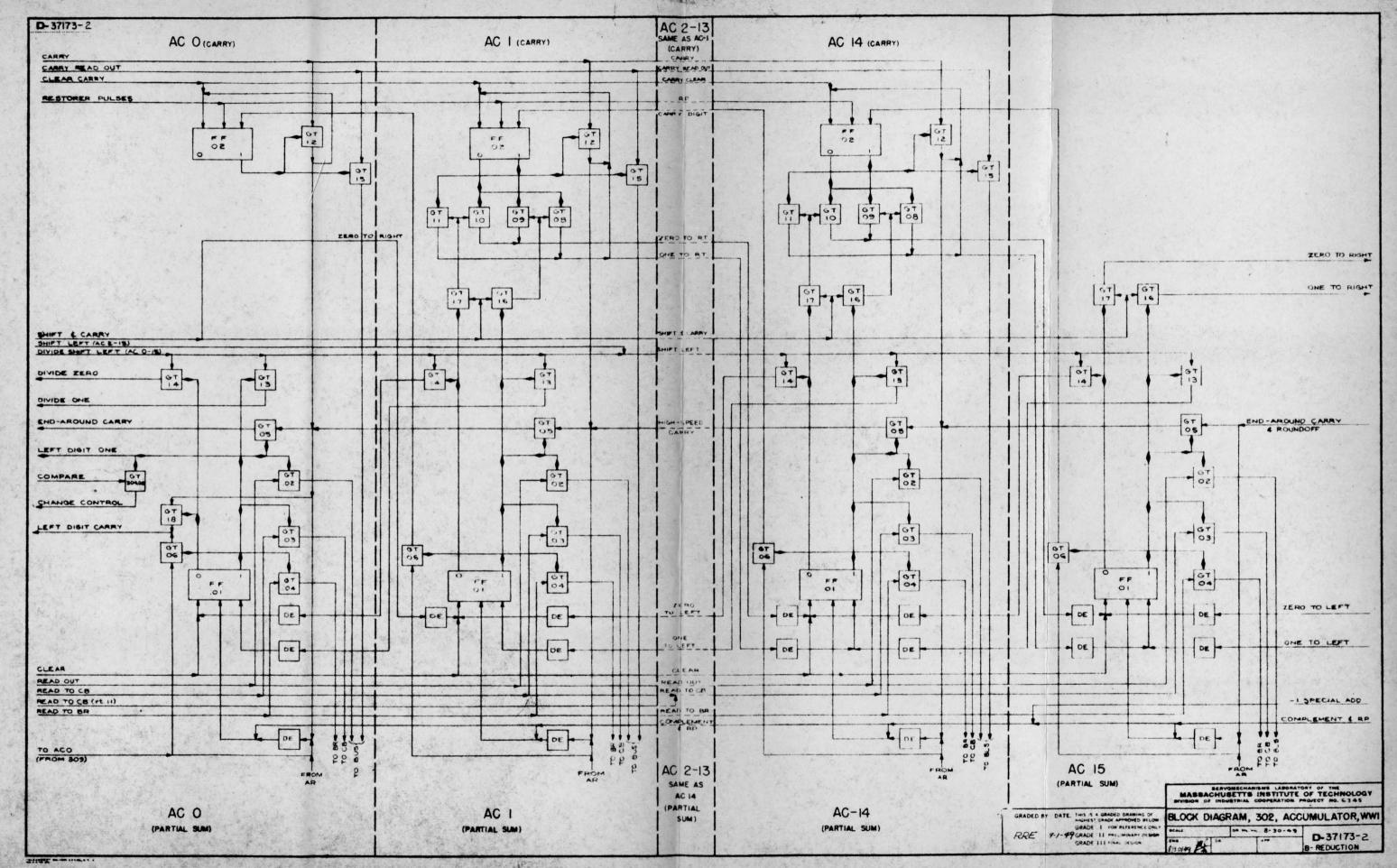

All arithmetic processes in WWI are performed as a combination of additions and shifts. The device which performs the additions in WWI is called the Accumulator (see Fig.9). The Accumulator (AC) is capable of a number of operations other than addition, but we will only discuss it as a b nary adder. Consider only FFOl in the column labeled .Cl5 (partial sum) and FFO2 in the column labeled ACI4 (carry). Only CTO6 of ACI5 (partial sum) and CT12 of ACI4 (carry) are of interest. First let us examine the binary addition table:

Assume that a number is already in AC and that the number contained in AR is to be added to it. Only one digit column will be discussed (AC15); the same process takes place simultaneously in each digit column. When the aid gate tubes of AR are pulsed, the number will are error the lines labeled "from AR". Assume AC15 (FFO1) contains O initially. If the number being added in is O, no pulse will appear at the input ("from AR") no change occurs and FFO1 continues to contain O, as it sould. If the number being added was 1, a pulse appearing at the input will be applied

to GTOS, but it will find GTOS closed. After a slight delay, the pulse will be applied to the trigger input of FFOI causing it to chance its content to 1. Thus the correct result is also obtained for this case.

Now assume that AGIS (FFOI) contained 1 initially. If the number being added in is 0, no chance occurs; FFOI containes to contain 1, as it should. If the number being added in is 1, the pulse will find GTOS open and will proceed to set FFO2 of AGI4. After a slight delay, the pulse will trigger FFOI of GI5 to 0. This, again is the correct result, i.e., the sum is 0, with 1 to carry. The carry is subsequently added in to the next digit column by applying a pulse to the carry line. This uses GT12 to sense the carry flip-flop (FFO2). This second addition ray also result in a carry, which would require another carry pulse, and so on. However, a storter method has been devised which requires only one carry pulse. The method tutilizes GTO5 and is called the high-speed carry. It will not be discussed further.

# 2.124 The B nary Counter

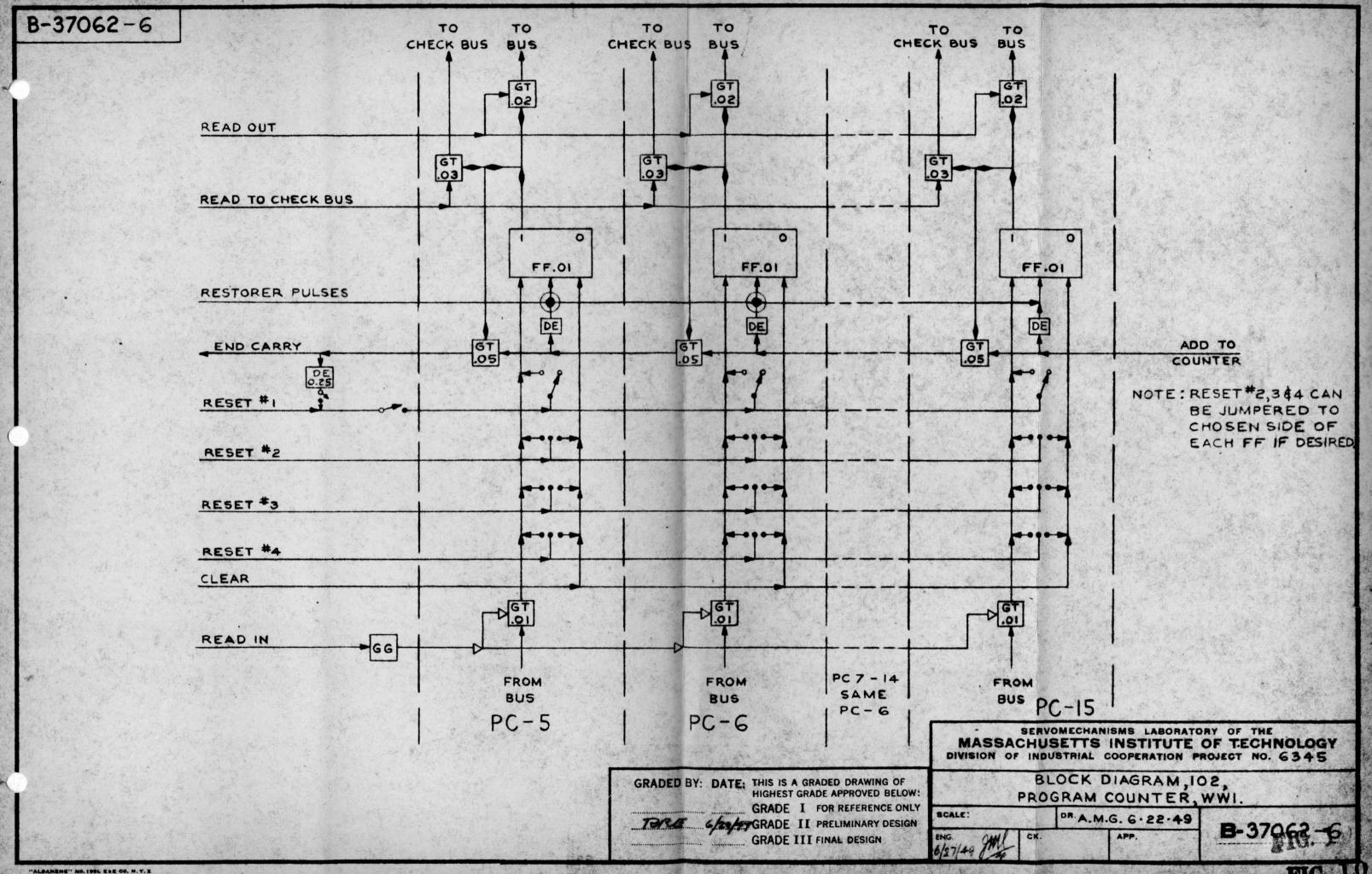

The binary counter is just what its name implies: it counts the number of pulses applied to its input, indicates this number in the binary system and supplies, if desired, an outsut pulse when its capacity is exceeded, the counter being returned to 0 when this occurs. A typical binary counter, the Program Counter (PC), having a maximum capacity of 2048, is shown in Fig. 10. Assuming each filt-flop is initially clear, two input pulses must be applied to any flip-flop in order to obtain an output pulse from the associated 6705. Thus, two outsut pulses are required from PC6 in order to obtain an output pulse from PC6. This, in turn, requires four pulses from PC7, which in turn, requires eight

pulses from PCE, etc. The capacity of the counter is increased by a factor of two for each flip-flop stage. The number of pulses the counter has received is indicated at any time by the contents of the flip-flops, FC15 giving the 2° digit, FC14, the 2¹ digit, etc., with PC5 giving the 2¹0 digit. It is possible to preset this counter so that the overflow pulse is obtained after any predetermined number of pulses (less than 2045, of course).

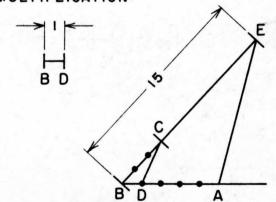

## 2.125 The Time-Pulse Distributor

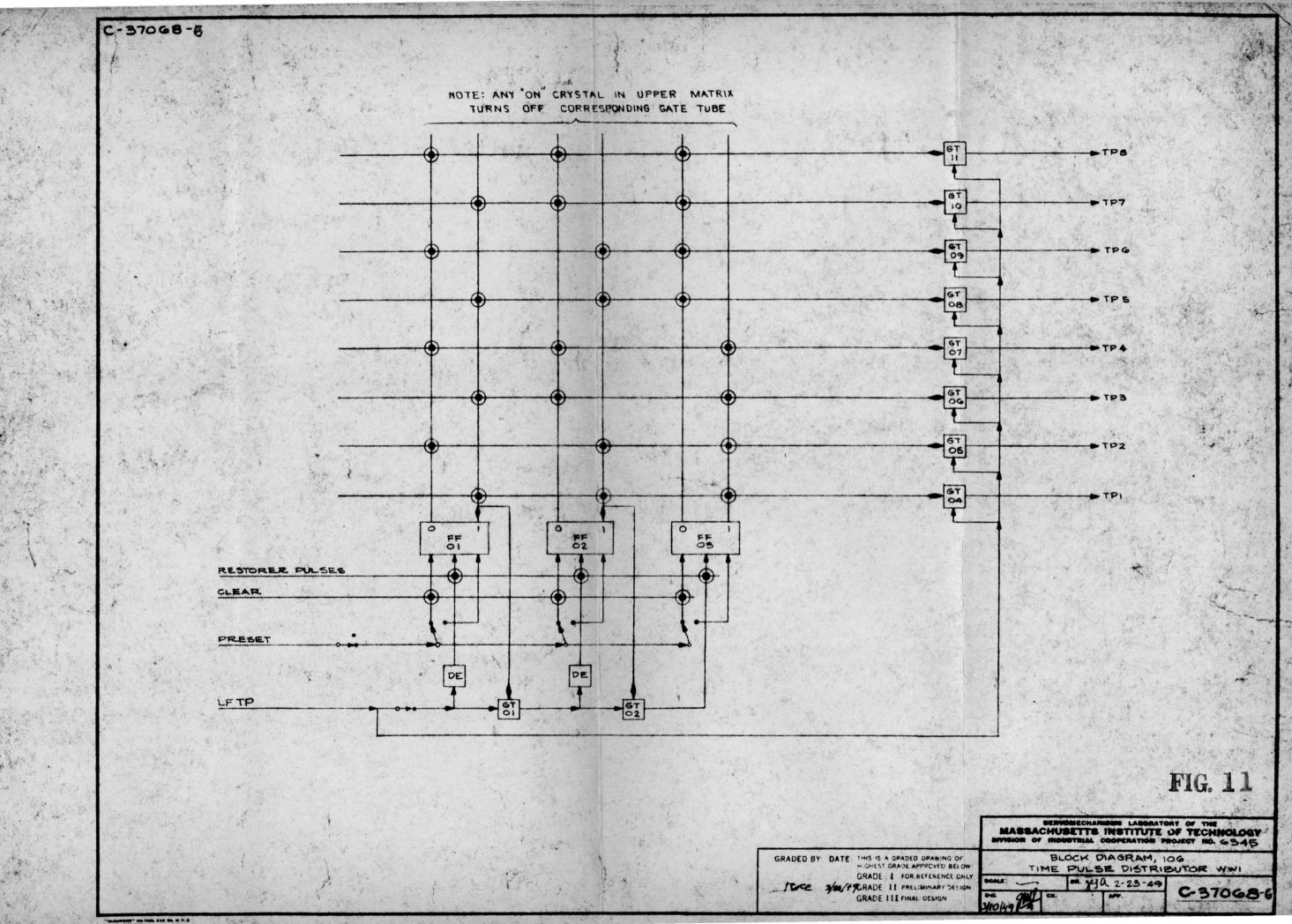

tary steps in proper time sequence in order to build up a more complex operation. Thus, if we have a supply of timing pulses, we want the first one to go to one part of the computer, the second one to another part, the third one to still another, etc. The time-pulse distributor accomplishes this conversion from a time distribution to a time end space distribution. It is a combination of a binary counter and an electronic switch (see Fig. 11). The out ut lines are selected in accordance with the contents of the counter. The input rules, in addition to performing the counting, emerges on the selected line. There is no need for the overflow pulse in t is type of operation so that no provision has been made for it.

# 2.13 The System

The interconnections among the various units are shown in detail. A 16-digit binary number will be referred to as a word. A word may represent an instruction or an actual numerical value. Words are transferred from one part of the system to another via a set of 16 dables which are

connected to the unite via gate tubes. All digits are transferred simultaneously (parallel digit transmission) with a separate cable being recuired for each. A word is transmitted to the bus from a particular unit by pulsing its read-out gate tubes. A word which is on the bus will be transmitted to any unit whose read-in gate tubes are open. Another set of 16 cables (the "check bus") is provided as a multiple check on the bus. By a suitable arrangement of the timing, it is possible to check corei erably more than the condition of the bus. The other connections, which transmit pulses that control the performance of the various steps of the overations, are made directly. Such pulses are called commands.

## 2.131 Central Control

It also contains a source of pulses which eventually become commands.

It also contains a source of pulses which eventually become commands.

The master clock supplies these rulees in various forms. The basic rulee source is the pulse generator which supplies high-frequency clock rulees (HFCP) at a 2 mc. rate and low-frequency clock pulses (LFCF) at a 1 mc. rate. The frequency divider is used in conjunction with the restorer—pulse generator (RFC) to generate the restorer pulses. Clock-pulse control (CFC) determines which pulses will be supplied to the remainder of the computer during such times as restoration and the operation of an auxiliary control. The synchronizer provides single pulses at the control of a rush button. The bulk of the operations are carried out by the time-pulses which appear on successive lines at intervals of 1 usec.

(the interval is longer during restoration and the operation of an auxiliary control). There pulses are provided by the time-pulse distributor (TFD)

(see section 2.125). The program counter (FC) is the device which contains the location of the next instruction to be performed. The control switch (CS) determines which operation is to be performed by energizing the appropriate line of the control matrix (CK). Each line of the control matrix opens certain gate tubes (control pulse output units). Nach of there gate tubes is sensed on a certain time pulse (in some cases, on two time pulses). The pulses which emerge from these gate tubes are the commands. Thus by setting the control switch to a given position, the sequence of commands required to perform the operation determined by that position is obtained. A different sequence of commands is obtained by changing the centents of the control switch. The program register (F) is a fuffer resister which serves two different purposes, to be duscussed in sections 2.137 and 2.21. Storage selection control will be discussed in section 2.137.

## 2.132 Test Storage

Fart of the memory of WWI consist of 5 flip-flor registers and 27 togrie-switch registers (each capable of holding a word). These registers are known as test storage (TS). The 5 flir-flop registers may receive and transmit words, but the 27 toggle-switch registers can only transmit words. A switch must be manually operated in order to change the contents of a toggle-switch register. The registers of test storage are numbered from 0 to 31; the number assigned to a particular register is called the address of the register. The flip-flop registers may be assigned to any desired address by changing see cables. A 32-position switch called the test storage switch (TSS) determines the register to which the machine has access. If the commend storage read-out is given,

to the number contained in the storage register whose address corresponds to the number contained in the storage switch. The command storage read-in will read a word into the register whose address is in the storage switch (if it hap one to be a togele-switch register, the re-d-in process connot take place).

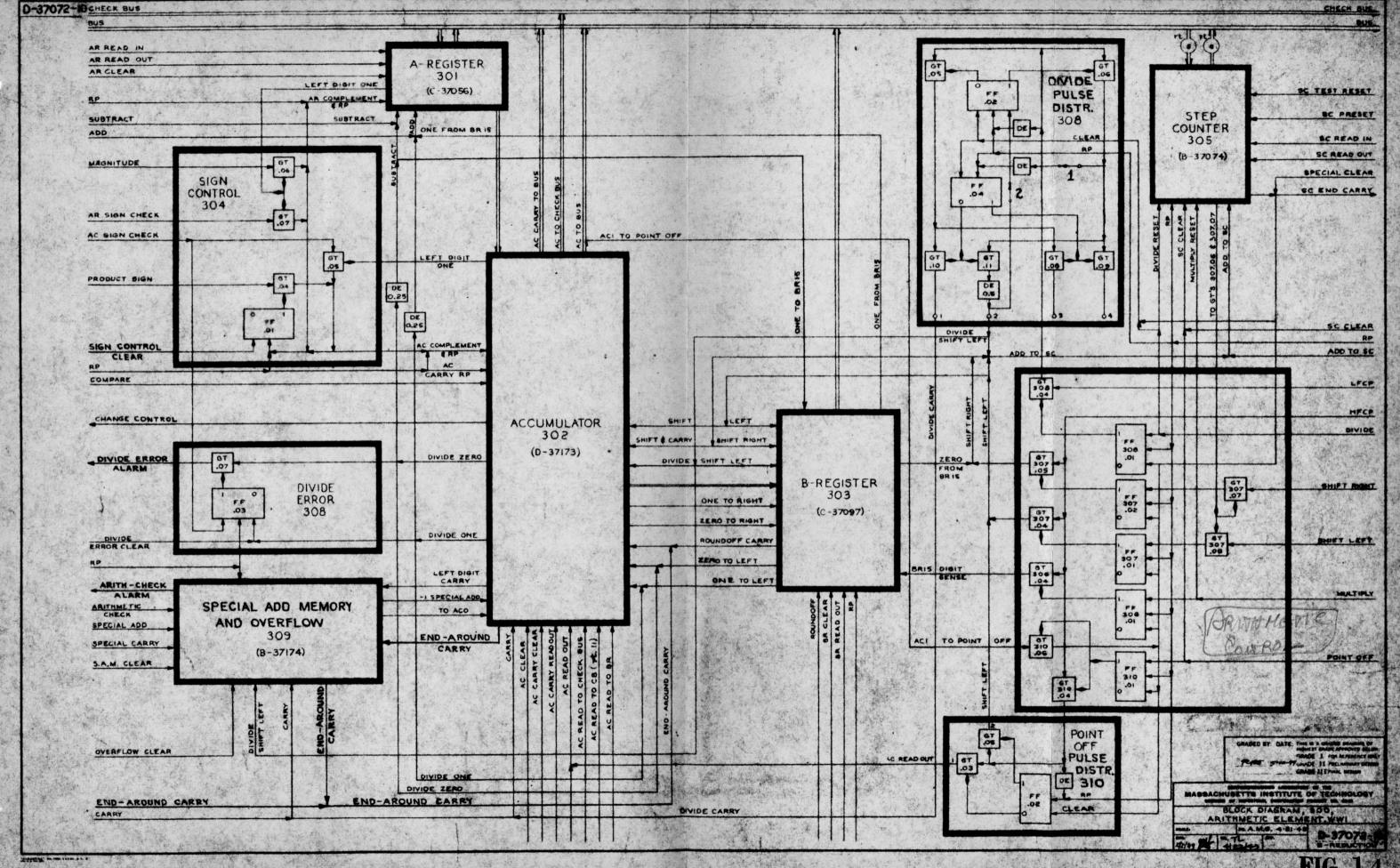

#### 2.133 Arithmetic Element

The arithmetic element (AE) is shown in Fig. 14. The numbers are manipulated in the A-register, the B-register, and the accumulator, which have been discussed in sections 2.121, 2.122, and 2.123, respectively. Fany of the arithmetic operations require a longer sequence of commands than c:n be provided with the eight time-pulses available from central control. The remainder of the arithmetic element (with the exception of erecial-add memory and overflow, sign control, and divide error) is used as an sarilinry control to provide these corrands. One of the commands provided by the control matrix on such operations is stop clock, which is sent to clock-pulse control and stops the supply of pulses to the time-pulse distributor. At the same time a command is sant to arithmetic control which posmits it to commonce operation. Wither LECF of HFCP (depending on the operation) are used to carry out these arithmetic operations. When the operation is complete, an end-carry bulse which permits the time-pulses to resume is sent to clock-pulse control by rithretic control.

Certain conventions have been adopted regarding number representation. These are explained in Arpendix I. The use of the "ninescomplement" to represent a negative number means that the negative -y

of a positive number y is actually represented by 2-y-2-15 in this machine.

This is perfectly all right for addition and subtraction as long as endround carry is provided. Shifting multiplication, and division are

quite complicated for negative numbers if the "nines-complement" is

used. The sign control has been provided so that these operations can

be carried out for the positive magnitudes of the numbers involved

and the proper sich affixed to the result by complementing each digit.

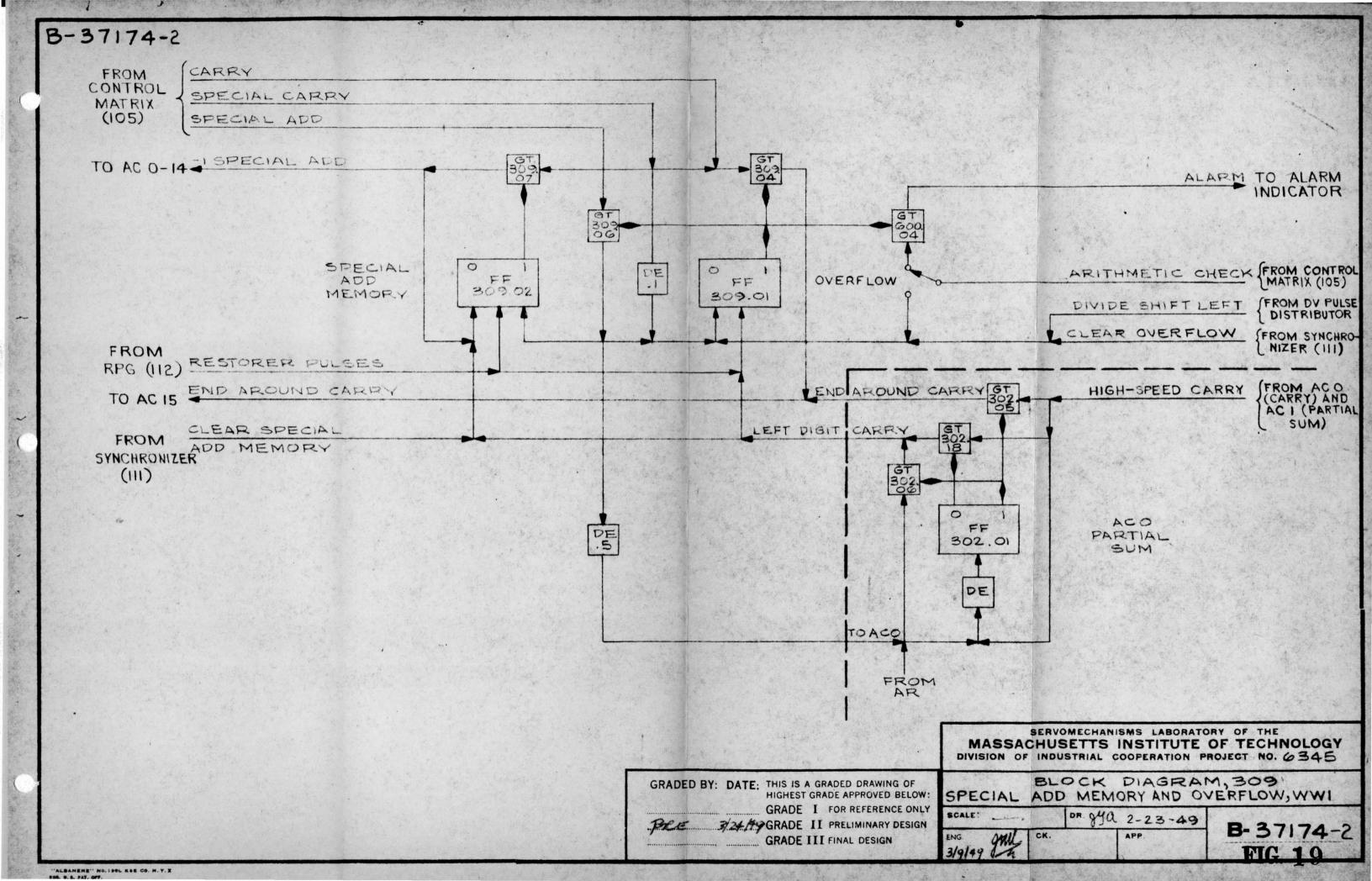

Special-add memory and overflow is necessary if the computer is to have the facility of using two words to represent a double-length number. The addition of the less significant halves of two numbers represented in this fashion may produce a carry into the least significant digit of the other half of the sum. The special-add memory and overflow is used to remember such a carry. An addition of two single-length numbers which results in such a carry means that the capacity of the corruter has been exceeded. When such a situation occurs, the special-add remory and overflow will surply an clarm signal which can be used to stor the corrutation at that point and provide some indication to the overator. A similar situation can occur in the divide operation if the dividend is greater than the divisor. The divide error is used to provide an indication of this situation.

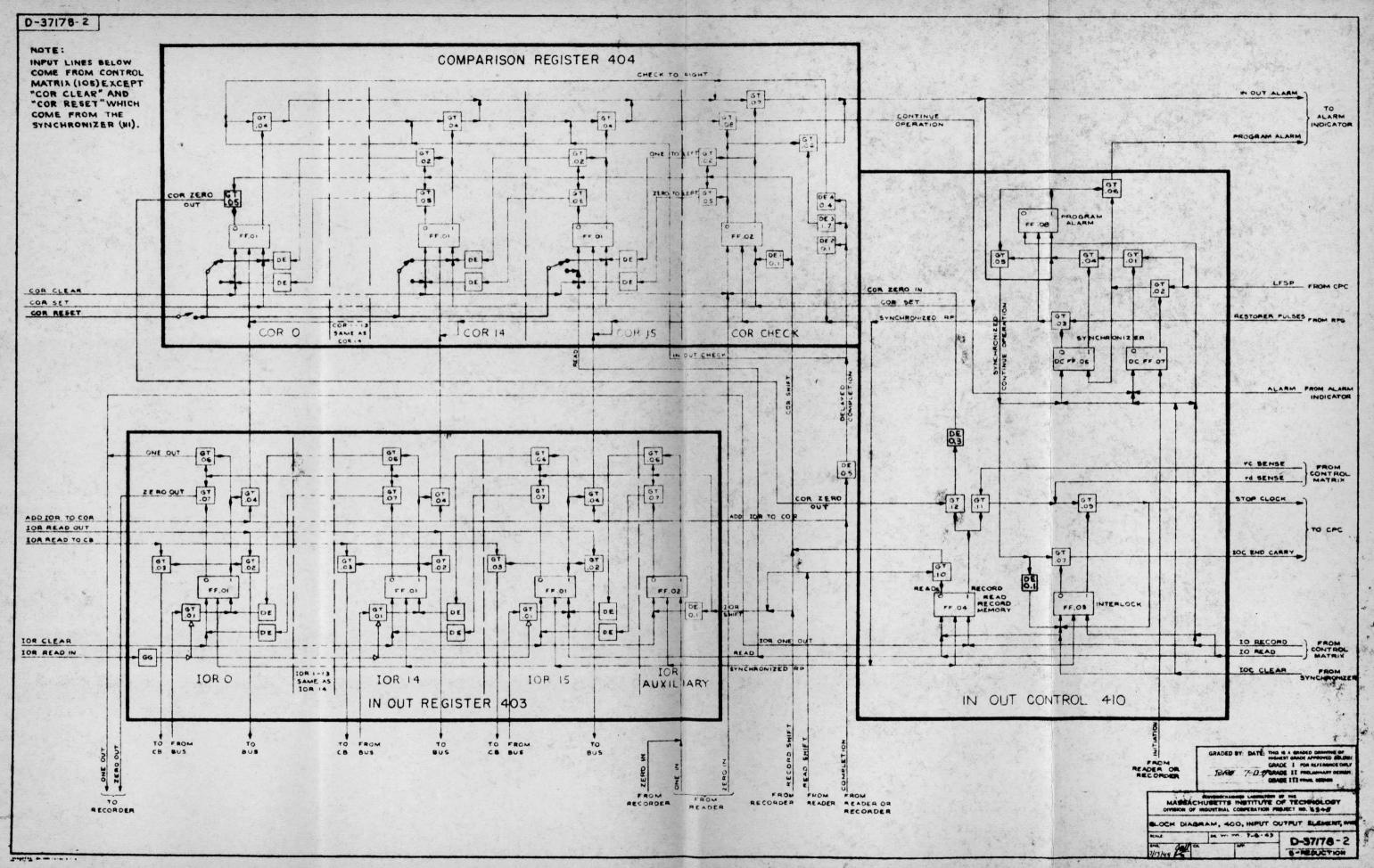

# 2.134 In ut-Cutrut Element

A block diagram of the input-out ut element is shown in Fig. 15. Words are transferred between the in-out register and the external equipment on commands supplied by the external equipment. When such a transfer is to take pl ce, the command stop clock is sent to clock-pulse control. Then the transfer is completed, an in-out control end-carry rules is sent

to clock-pulse control to permit the time-pulses to resume. A rather complicated system is provided to permit the computer to operate at the same time as the external equipment. The comparison register is used as a built-in check on the operation of the in-out register. Its overation will be described in section 5.12.

## 2.135 Built-In Checking

It was mentioned in section 2.13 that the check bus has been rrowided to check on the transfer of words via the bus. The check register is used to compare the words transmitted by both buses. When a word is transferred from unit A to unit B via the bus, it is also transferred from unit a to the tripper invute of the check register via the check bus. If the check register was originally clear, it will receive the word that was transferred. Some time later, the word received by unit D is transferred to the trigger inputs of the check register via the bus. No provision is rade for carries. If the two words are the same, the check register will contain 0. The gate tubes on the 1 stdes of the flip-:lops are sensed. If any of the flip-flors contains la an out ut calse is obtained. This output palse is sent to the alarm indicator and is also used to stop the supply of pulses to the computer (with the exception of restorer-pulses and the pulses required for electrostatic storage). The alarm indicator provides visual and sural indication of the discrepancy. Alarm pulses may also be obtained from other parts of the corruter, such us the divide error, the in-out element, and the special-add nemory and overflow.

# 2.136 Test Control

The operation of the comuter is controlled by a number of push buttons located in test control. With these push buttons and some

may be required to operate the computer. A single step of the problem can be performed using another rush button. Test equipment is provided to set up some special operating conditions that have been found useful for testing purposes.

#### 2.137 Electrostatic Storige

The bulk of the memory of WWI will be provided by electrostatic storage tubes (SST). It is ultimately expected to have a capacity of 2048 words. It is convenient to think of electrostatic storage (ES) as being made up of registers having addresses ranging from 0 to 2047. Storing selection control determines whether ES or TS is to be used. If both are used simultaneously, the addresses from 0 to 31 must te assigned to TS while the addresses from 32 to 2047 must be assigned to ES. The program register is used as a buffer between ES and the rest of the computer. When a word is transferred to 35 it is actually transferred to the program register. A subsequent command IS write will stop the suprly of time-pulses and restorer-pulses and will start electrostatic stor ge control (ESC). The word in FR will be transferred to the position in 'S corresponding to the address contained in the ES decoder (ESD) (it is similar in function to TSS, but it is not a switch) under the control of ESC. After this transfer has been completed on ESC endcarry is sent to CFC which will permit the supply of time-rulees and restorer-rulses to be resumed.

## 2.2 Machine Cycle

The period of time required to fill the counter of the TPD

when starting from the clear condition will be referred to as the machine cycle. During this period, the computer performs one operation and prespares to perform the next operation.

### 2.21 Frogram Timing

The series of cormands necessary to enable the comuter to proceed from one operation to the next is known as program timing (see Fig. 16).

For convenience, a separate line of the control matrix is used to gate open the proper commands. Nearly all of the overation lines are connected to the program timing line. Those which are not connected to this line, are nevertheless connected to those gate tubes which provide the commands essential to sequencing. Program timing provides some additional commands which are cormon to nearly all operations (these additional commands do not interfere with any of the operations which do not require them). We will discuss only that portion of program timing which is essential to sequencing. Some of the cormands are concerned with checking the transfers by use of the check register.

on time-pulse? (TP?), the convends PC read out and SS read in are given. Both TSS and ESD will receive the address contained in FC, but SSC will determine whether TS or ES is used. In order for the read in to give the convect result, both TSS and ESD must be clear. This will have been accomplished by the convend SS clear on TP1. On TP4, the word contained at the address specified by PC is transferred to FR. This transfer is direct if ES is used, but requires the command PP read in if TS is used. TP4 also clears CS after a 1/2 usec. delay. This energizes the line with controls the ri operation. This operation does not have

program timing, but the commands which occur on TP5 of the ri operation are an essential part of program timing. The commands PR read out,

GS read in, and SS read in are given on TP5 of ri. This results in GS

being set up to perform the overation specified at the address which was

contained in PC at TP2. At the same time, SS is set up so that the correct

operand will be available from stora e. The commands necessary to perform

the particular operation are obtained starting with TP6. Inasmuch as GS

will not be changed until TP42 of the next machine cycle, it is possible

to use TP1 to TF4 for obtaining these corrects. On TP7 of program timing,

the address contained in PG is increased by 1 by the command add to FC.

Thus, on the next machine cycle, the instruction contained at this new

address will be performed.

Flexibility in the choice of addresses for successive orders is provided by a special operation, subprogram (sp). The sp operation chan es the contents of PC to the number specified in its address section. An additional operation, conditional program (cp) which makes such a change conditional upon the sign of the number contained in AC (if the number is negative, the change is made; if positive, it is not changed), permits the michine to choose its own computing routine on the basis of the results of some computation.

# 2.22 Operation Timing

The series of commands which are concerned with actually carrying out the overation specified by the particular setting of CS is called operation timing. As an example, operation timing for an will be discussed. The address contained in PC at TP7, indicating the register containing

the instruction which would ordinarily follow, is transferred to AR, where it is available for further use, if desired. Thus, AR is cleared on TP6. On TP8, the commands PC read out and AB read in transfer this address to AB. On TP8 1/2 (TPE delayed by 1/2 psec.), PC is cleared. The address specified in the sp instruction is still contained in FR (it was there at TP4 of program timing). Hence, on TP1, the commands PR read out and PC read in transfer the desired address to PC. This address will be read out of PC to SS on TP2, thus the next instruction will be obtained from the address specified in the sp instruction.

### 2.3 Programming and Coding

The term programming is used in a general sense to indicate the process by which a problem is prepared for solution by the computer. Coding is a much more specific term referring to the step in which the problem is stated in terms of operations which the computer performs. Then a problem has been put in this form, it is referred to as a coded program. We shall be mainly concerned with coding in this themis. A more detailed discussion of coding for WWI may be found in reference 16. A compact summary of the basic information has been included in this thesis as Appendix I.

# 2.31 Nomenclature

we have previously defined the term word as a 16-digit binary number. If the word is interpreted as an instruction, the first (left-hand) 5 digits are the coded representation of the operation to be performed. There are 32 operations possible with this convention. In

when TS is used, only the last 5 digits specify the address. When the operation code specifies a shift, the last 5 digit indicates its extent. For convenience in writing codes, two-letter abbreviations have been adopted for each operation (e.g., sp. cp. ri. ca. etc.). Another convenient notation is FC(x), which indicates the address of the resister containing x. The symbol CR (y) indicates the contents of the register whose address is y. Thus, the combination of symbols on FC(x) represents an instruction which will transfer the contents of the storage register containing x to the accumulator. Of course, it is necessary to assign a specific address to the register containing x before the instruction can be used in the computer. If x were put in register 31, this instruction would be written on 31. In the machine, this would a peer as 10000000000011111 (10000 is the code for ca).

The computer distinguishes between a word used as an instruction and a word used as a number on the basis of the time in the michine

cycle at which this number is transferred from stories. If it is transferred on TP4 and TP5 (via the program register), it will be treated as

an instruction. At any other time, it will be treated as a number. Thus,

it is possible to manipulate an instruction as though it were a number.

Indeed, it is a very common practice to do just that in programming (see,

for example, reference 3).

### 2.32 The Operations

The operations which have been accepted for permanent use in WWI are listed in Ampendix I. A brief description of each is included

there. In addition, there are a number of operations which have been temporarily wired into the control matrix. These operations are distinguished by a two-letter code in which the first letter is q. One of these, gc (check), will be used very frequently in this thesis. It corpores the contents of the storage register indicated in its address with the contents of the accumulator. The corporison is carried out in the check register in a manner very similar to checking of the bus transfers (see section 2.135). An alarm is obtained if the words do not agree. Though gc is only a temporary operation at present, it seems very likely that it will be made a permanent operation.

### 3 - DISCUSSION OF FAILUPES

#### 3.1 Classification of Failures

functions. Its ability to perform these functions devends on many factors. These factors generally vary with time in an irregular fashion.

The status of all these factors at a particular instant will determine whether the stage can perform one of its functions at that instant. A failure need not be precent at all times. However, if it is not present during a checking process it will not be detected. Thus, the nature of the factors causing failures and the degree to which they can be controlled exert an important influence on the process of error detection. It is helpful to classify failures according to a scheme which indicates this influence.

# 3.11 Steady-State Failures

an irreversible change in one or more factors which renders a state permanently incapable of performing a function is colled a steady-state failure. The stage will consistently yield the same incorrect response at every application of the signal. A typical example is an open cable; it can never transmit a pulse. However, it must not be concluded that a permanent failure of a component is necessarily a steady-state failure of the stage. If a resistor used to terminate a cable should become open, a distorted pulse waveform would result. Whether this will cause a failure depends on several other factors which need not always be unfavorable.

### 3.12 Dynamic Failures

Closely akin to the steady-state failure, though somewhat more subtle in its effect, is the dynamic failure. 21 The distinguishing factor is that it appears only on certain applications of the signal. It may be that a coupling condenser will charge slightly every time it passes a rulee. If there is not sufficient time for it to discharge between successive pulses, the charge will continue to build ap. The amplitude of the outrut pulses will decrease as the charge on the contensor increases. Sventually the outcut pulse will be too small to drive the next stage. This offect is referred to as FRF-sensitivity (pulse-repetition frequency) and is an example of a dynamic failure. The open terminating resistor referred to in section 7.11 might be a dynamic failure or it might not be a failure at all. Another interesting example of a dynamic failure found in the overetion of WWI (after considerable effort) was the result of "ringing" on a d-c power surely line. The various supply lines have been provided with IC-filters to prevent the coupling of pulses between circlits. The current surges which accompany the switching of vacuum tubes cause the filter circuits to oscillate or "ring" with a fairly small amplitude. It so happened that the timing of a problem was such that the fourth time a particular pulse occurred coincided with the peak of this oscillation. This was barely sufficient to interfere with correct operation; indeed an error did not always occur on this pulse. This failure was not due to a defective component; it was a design weakness which, in all fairness. the designer could not have been expected to anticipate.

#### 3.13 Incipient Pailures

Some factors change in a continuous fashion. For example, the cathods emission of a tube tends to decrease gradually as it ages. Eventually, the change will have progressed to a point where correct operation is no longer possible and a steady-state failure will evist. Pefore this point is reached, the operation of the stage becomes more sensitive to other factors. An incipient failure is said to exist. Slight we reations in some factors would not cause any failures in a stage without an incipient failure, but these variations would cause failures when an incipient failure is present. Aging effects are found in all components, but are more pronounced in tubes and crystal rectifiers.

### 3.14 Intermittent Failures

Frequently a stars will be abnormally sensitive to a factor which fluctuates in a random fashion. This sensitivity is not the result of a progressive deterioration as is the sensitivity exhibited by an incident failure, but is more or less constantly present. The high contact resistance present in a poorly soldered joint might be a cause of such sensitivity. The failure will appear at irregularly spaced intervals. Such a failure is called an intermittent failure. It is quite similar to the incipient failure in arrearance, but not in cause.

#### 3.15 Reproducible Failures

Another tyre of failure which is manifested at irregularly spaced intervals is the reproducible failure. Its im-ediate cause is an external disturbance of some sort: mechanical vibrations, presence

of r-f radiation, and the like. Of course, there must be some other factor with makes the stage sensitive to these disturbances, but it may operate very satisfactorily as long as the disturbance, is not present.

Py artificially causing such disturbances, reproducible failures may be made to occur whenever desired, and hence take on the characteristics of steady-state failures.

### 3.16 Random Failures

is the random failure. It does not require an abnormally sensitive stage for its occurrence. It generally results from an unusual combination of unfavorable conditions among the factors which are subject to veriation. It may be due to an exceptionally large variation of one such factor, e.g., a power line transient far exceeding the normal lim ts. Although there is always a cause for such a failure, it remains unknown to the overator.

### 3.2 Checking Considerations

### 3.21 Influence of Various Tyres of Failures

determining the ability of the commuter to function properly. If the ability should change during the course of the experiment, it becomes difficult, if not impossible, to interpret the results in terms of the condition of the commuter. It is quite possible to obtain the correct solution to a problem even though dynamic, incipient, intermittent, reproducible, and rendom failures are present. In short, test checking is applicable to only steady-state failures. In designing test sequences,

no consideration need be given to any failures which are not essentially steady-state failures. However, it has been noted that dynamic, incipient, and reproducible failures are very closely related to steady-state failures. If supplementary means can be found to convert these types of failures into steady-state failures during the performance of the test sequences, test checking may be used for their detection. Of course, if an intermittent or random failure should occur at an optortune time, it, too, would be discovered by test checking. However, mathematical checks are much more effective in dealing with irregularly spaced failures.

### 3.22 Operational Effects of Failures

ability to perform a certain function. The problem of designing a checking sequence may be stated in terms of these functions; the checking sequence must require each stage to perform all such functions. One of the first tasks, therefore, is to determine these functions for each of the elementary stages. It is not necessary to consider each component failure for this purpose, as will become arrarent when it is done in sections 3.221 to 3.224.

When it is desired to use a problem for trouble location, a more detailed knowledge of the operational effects of the failures is required. The actual response of the faulty state rust be known. This is an important practical distinction between checking and trouble location. It would perhaps be well to restate this in the form of the questions which the designer must ask in each case:

Checking: What must the stage do?

Trouble Location: What will the stage do?

Some of the answers in typical cases are given below.

### 3.221 Amplifiers

amplitude to drive the succeeding stages when the appropriate input signal is applied. The output amplitude may lie among a wide range of values when a faulty component is present. The particular amplitude level which is obtained will either be capable of driving a succeeding bi-stable stage or it will not be capable of driving it. Since the output will ultimately be applied to a bi-stable stage, it may be said that the amplifier will not supply any output pulse if a failure exists. This does not mean that the actual amplitude is zero, but that it might just as well be zero as far as its effect on the operation of the computer is concerned. If the output is capable of driving the succeeding stage, no failure exists.

It is, of course, possible to obtain an out ut when no input signal is applied. However, there is no way of predicting the relation of the times of occurrence of such spurious pulses to the timing of computer operations. Thus, failures of this type are essentially intermittent and need not be considered. As additional justification for disregarding them, it should be noted that such failures are extremely rare in well-designed amplifiers.

To summarize this discussion, the two questions of 3.22 will be enswered. An amplifier stage must provide an outrut whenever the appropriate signal is applied to the input. If a failure exists, no output

will be obtained when a signal is applied to the invut. The extreme simplicity of these conclusions tends to belittle their importance. Geretainly they are intuitively obvious, but they must be clearly realized in designing test sequences. Note that the failure of the amplifier may be due a large number of causes (open filament, open plate load resistor, grid-to-cathode short, etc.), all of which exhibit the same symptom.

### 3.222 Gate Tubes

The gate tube can fail in three ways:

- 1. An output pulse is obtained without coincident invuts.

- 2. No outrut rulee is obtained for coincident invuts.

- 3. An outrut pulce is coupled back to an in ut line.

Case 3 is extremely rare if care has been given to the layout. Furtherrore, it is correctly termless if the input line is driven by an amplifier, as is often true. This case will therefore not be considered in

this thesis. Case 2 is quite possible and fortunately, is amenable to

easy analysis. Two possibilities must be considered under case 1: the

output pulse is obtained without any input or it is obtained with only

one input. The former possibility represents an oscillatory condition

which is extremely unlikely. If it should exist, it would be extremely

difficult to determine the times when a spurious pulse would occur. It

would take on the characteristics of an intermittent failure, so that it

need not be considered. The latter possibility also may result in spurious

pulses at indeterminate times, which, again, need not be considered.

However, in the usual amplication of the gate tube, a signal is amplied to

one input to determine whether the other input is energized at that time.

ever this sensing signal is applied, even though the other input is not energized. This is a straightforward manifestation and will be considered. To surrarize, it will be assumed that to the failure of a gate tube can exhibit only two possible effects:

- 1. It will never provide an output when a sensing signal is applied.

- It will always provide an output when a sensing signal is applied.

### 3.223 Flip-Flops

of three inputs and to retain such information indefinitely. A faulty component may cause it to develop a preferred position, i.e., it will not remain in the other position indefinitely, though it will remain in the preferred position for any desired period of time. Once again an indeterminate time factor appears in the consideration of the effects of failures: the veriod of time a flip-flop can hold the non-preferred information before reverting to its preferred state. If this period is longer than the time it is required to hold the non-preferred information, this weakness will not have an adverse effect on its operation. The longest interval between restorer-pulse pairs is the maximum amount of time that a flip-flop would be required to hold one state. However, for reasons which are not fully understood, flir-flops have been observed to revert to the preferred position even though restorer pulses are used. Some