#### Report R-220

ANALYSIS AND DESIGN

OF A

DIGITAL-TO-ANALOG DECODER

by Robert Louis Walquist

DIGITAL COMPUTER LABORATORY

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

Cambridge 39, Massachusetts

December 1, 1952 (Thesis date: May 28, 1951)

#### FOREWORD

Because it treats a subject of widespread current interest, this thesis report, which has had only limited distribution, is being published as a Digital Computer Laboratory R-series report. Digital computers are finding rapidly increasing applications to the control of physical systems of many kinds. The input to such systems must be in analog form such as an electrical voltage or a shaft position. The unmodified output of the digital computer is a set of numerical digits. Before this digital information can be fed into the control system, it must be translated into analog form. One device for this conversion is the digital-to-analog decoder described in this report.

Signed Robert L. Walquist

Robert L. Walquist

#### ABSTRACT

"Analysis and Design of a Digital-to-Analog Decoder"

by

Robert Louis Walquist

Submitted for the degree of Master of Science

in the

Department of Electrical Engineering

on May 23, 1951

The purpose of this thesis is to study the general problems associated with the various types of digital-analog conversion equipment and, by means of this study, to design a high-accuracy digital-to-analog decoder without sacrificing speed of response.

In choosing a particular form of conversion device for use in a system, the following characteristics must be considered:

- 1. The general applicability of the input to or output from the conversion device;

- 2. The accuracy of the conversion;

- The sensitivity of the conversion;

- 4. The freedom from drift of the conversion device;

- 5. The time taken for a single conversion;

- 6. The amount of equipment necessary for single and multiple conversion channels.

The <u>internal</u> operation of the conversion device may be characterized by only two of these quantities:

- 1. The number of quantizing levels (the static conversion accuracy);

- 2. The conversion time.

Comparison of these two characteristics of digital-analog conversion devices to the characteristics of analog systems indicated that quantization error is similar to noise, while conversion time is similar to bandwidth.

The problem of conversion is one of comparison or matching of the input and output signals of the conversion device. The three fundamental ways in which this comparison may be accomplished are:

- 1. Serial matching of each quantizing increment;

- 2. Serial matching of each binary digit;

- 3. Parallel matching of all digits (simultaneous comparison).

These three methods of comparison are completely analogous to the three ways in which digital information may be transmitted.

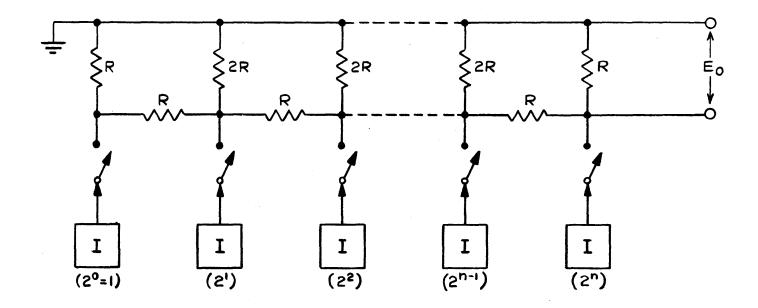

Study of the various conversion methods indicates that a binary-weighted decoder which uses equal-valued current sources connected to a binary-weighted ladder network is one of the best solutions to the digital-to-analog decoder problem. Experimental design and testing of 2 stages of a proposed 10 stage decoder of this type gave the following results:

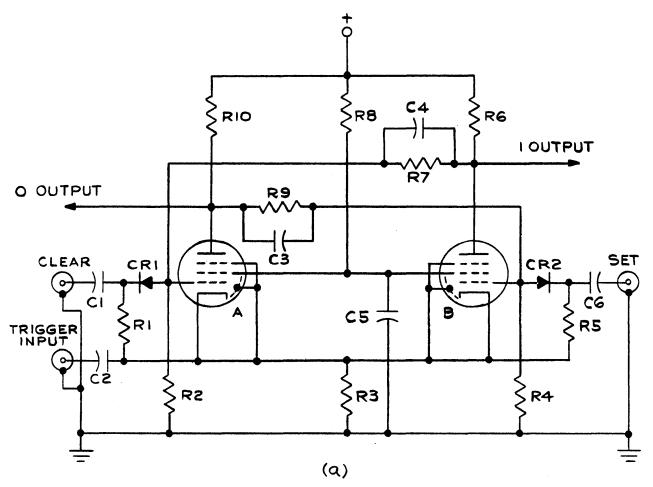

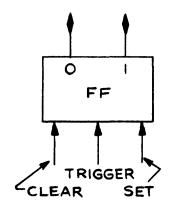

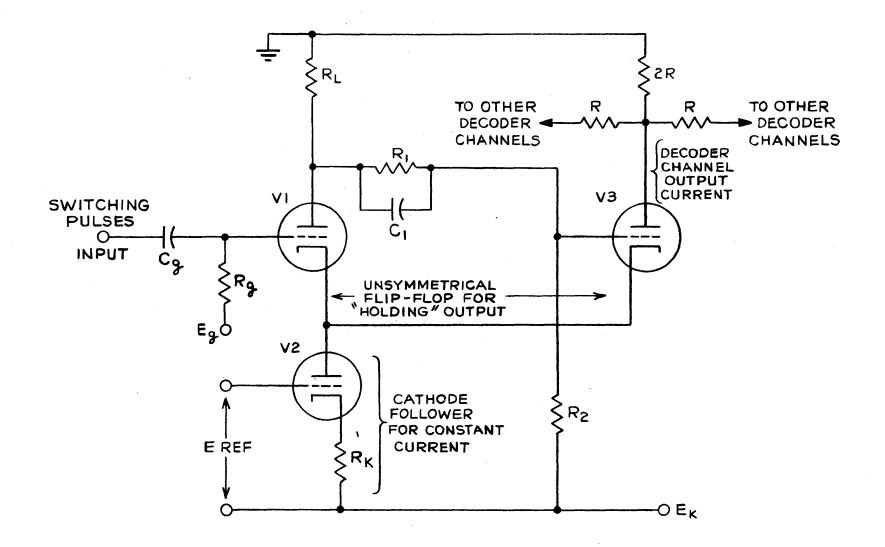

- 1. With only 1 ½ twin-triodes used for each stage, accurate current sources were built, each of thich includes a storage medium (an unsymmetrical flip-flop) for holding digital information.

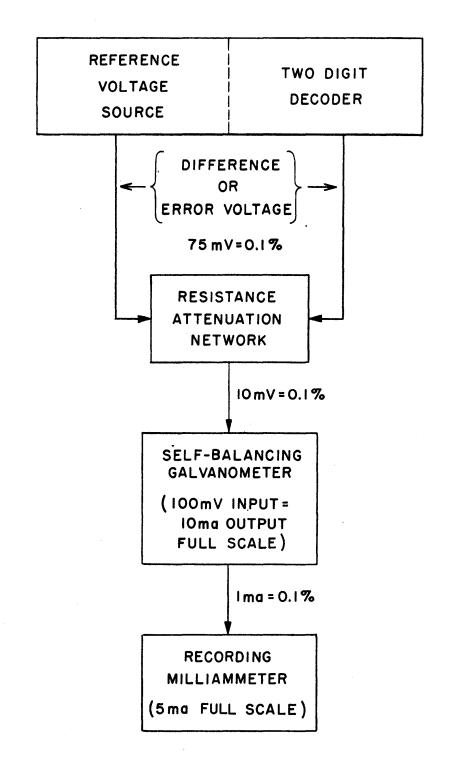

- 2. A maximum output voltage of 100 volts, without the use of amplifiers, may be obtained from the decoder with an accuracy of 0.1 percent (10 binary digits). Recalibration need be carried out no oftener than every few days.

- 3. The time taken by the decoder to set up this accuracy of output voltage, with only a small load applied, is less than 1.5 microsecond.

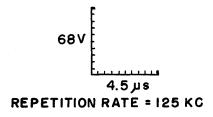

- 4. Repeated operation of the decoder may be obtained at frequencies up to 125 kilocycles.

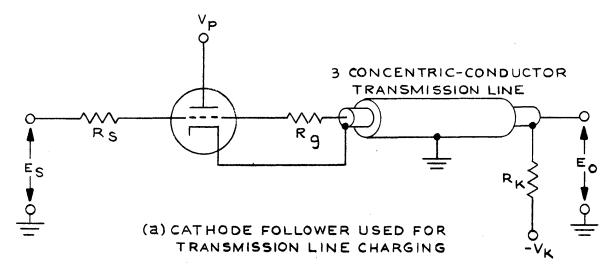

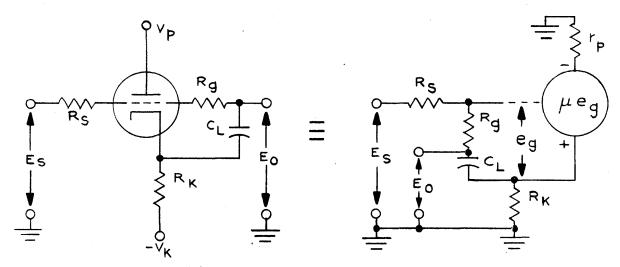

Transmission of the output voltage of a decoder becomes an important problem whenever many paralleled devices are to receive this voltage. Special transmission schemes, such as three-conductor transmission lines, may be used to retain the rapid response and accuracy of the decoder output voltage but only at the expense of increased complexity of equipment and greater power loss.

## Report R-220

## TABLE OF CONTENTS

|      |              |                                         |                                                        | Page |

|------|--------------|-----------------------------------------|--------------------------------------------------------|------|

| FORE | WORD         | • • • • •                               | •••••                                                  | ii   |

| ABST | RACT         | • • • • •                               |                                                        | iii  |

| TABL | E OF         | FIGURE                                  | S AND GRAPHS                                           | xi   |

| 1.0  | INTE         | ODUCTI                                  | ON                                                     | 2    |

|      | 1.1          | Uses                                    | of Digital-Analog Conversion Devices                   | 3    |

|      |              | 1.11                                    | Digital Computer Control Systems                       | 3    |

|      |              | 1.12                                    | Telemetering and Servomechanism Control Systems        | 5    |

|      |              | 1.13                                    | Information Storage                                    | 7    |

|      | 1.2          |                                         | nalysis of Conversion Devices as Presented is Paper    | 9    |

| 2.0  | IMPC<br>ANAI | RTANT<br>OG CON                         | ENGINEERING REQUIREMENTS OF DIGITAL  VERSION EQUIPMENT | 12   |

|      | 2.1          |                                         | nput and Output of the Conversion                      | 13   |

|      |              | 2.11                                    | Digital Information Represented as a Binary Number     | 13   |

|      |              | 2.12                                    | Analog Information Represented as Voltage Amplitude    | 14   |

|      |              | 2.13                                    | "Holding" of the Analog Output of a Decoder            | 16   |

|      | 2.2          | Accur                                   | acy of Conversion                                      | 17   |

|      | 2.3          | Sensi                                   | tivity of Conversion                                   | 18   |

|      | 2.4          | Freed                                   | om from Drift                                          | 19   |

|      | 2.5          | Conve                                   | rsion Time                                             | 19   |

|      | 2.6          | Amoun                                   | t of Equipment Needed                                  | 20   |

|      | 2.7          | *************************************** | Historical Summary of Digital-Analog                   | 21   |

|      |              | 2.71                                    | Table of Previous Coders                               | 22   |

|      |              | 2.72                                    | Table of Previous Decoders                             | 23   |

# $\frac{\texttt{TABLE OF CONTENTS}}{\texttt{(continued)}}$

|     |      |                |                                                                              | Page |

|-----|------|----------------|------------------------------------------------------------------------------|------|

| 3.0 | ANAI | YSIS O         | F DIGITAL-ANALOG CONVERSION DEVICES                                          | 25   |

|     | 3.1  | The P<br>Compa | roblem of Conversion is One of rison or Matching                             | 26   |

|     |      | 3.11           | Serial Matching of Each Quantizing Increment                                 | 27   |

|     |      | 3,12           | Serial Matching of Each Binary Digit                                         | 31   |

|     |      | 3.13           | Parallel Matching of All Digits (Simulatione taneous Comparison)             | 32   |

|     | 3.2  |                | rison of Digital-Analog Conversion es to Analog Systems                      | 34   |

|     |      | 3,21           | Methods for Comparing Analog Devices                                         | 35   |

|     |      | 3.22           | Quantization Error Compared to Noise                                         | 37   |

|     |      | -              | Conversion Time Compared to Bandwidth                                        | 38   |

|     | 3.3  |                | ing the Conversion Device to the External                                    | 38   |

|     | 3.4  |                | usions and Evaluation of the Various                                         | 41   |

| 4.0 |      |                | F THE DECODER PROBLEM BY BINARY-WEIGHTING                                    | 7474 |

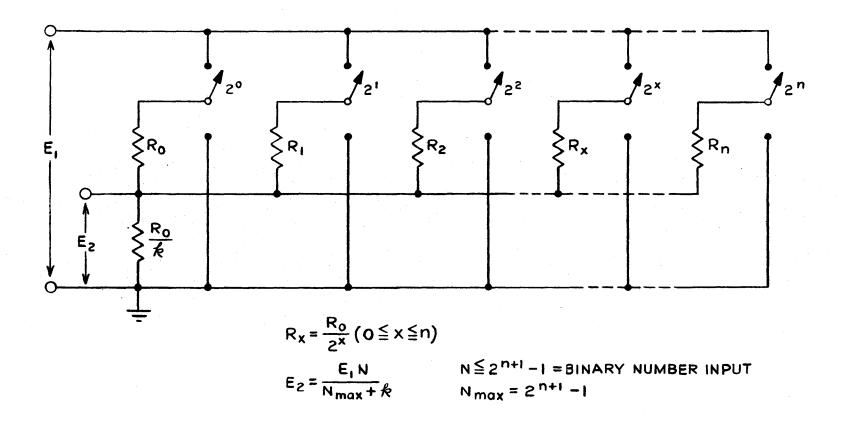

|     | 4.1  | Basic          | Binary-Weighted Decoder Circuit                                              | 44   |

|     |      |                | Accuracy Limitations of This Decoder                                         | 46   |

|     |      | 4.12           | An Accuracy Problem Common to All<br>Numerically-Weighted Conversion Devices | 47   |

|     |      | 4.13           | Possible Ways of Improving this Decoder Circuit                              | 48   |

|     | 4.2  | An Im          | proved Voltage Source Decoding Circuit                                       | 50   |

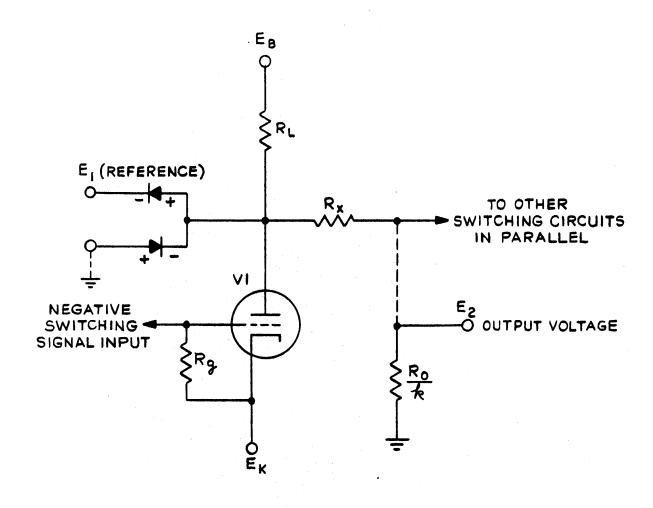

|     |      | 4.21           | A Possible Voltage Source Switching Circuit                                  | 53   |

## Report R-220

## $\frac{\texttt{TABLE OF CONTENTS}}{(\texttt{continued})}$

|     |      |                  |                                                                      | Page |

|-----|------|------------------|----------------------------------------------------------------------|------|

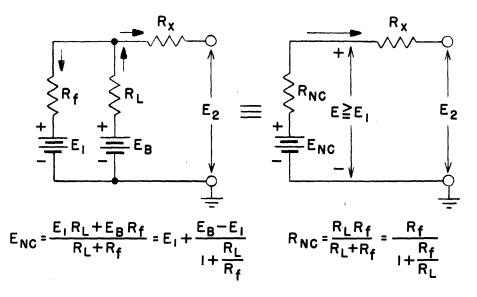

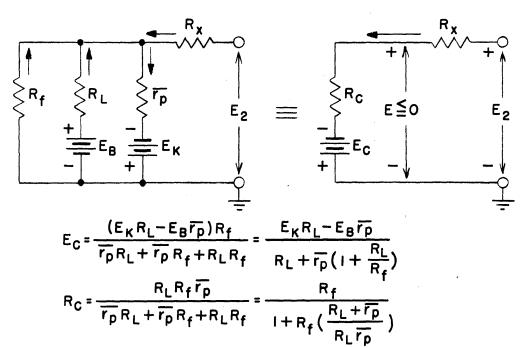

|     |      | 4.22             | Analysis of the Switching Circuit of Figure 7                        | 55   |

|     |      | 4.23             | Summary of the Method of Using Binary Weighted Voltage Sources       | 59   |

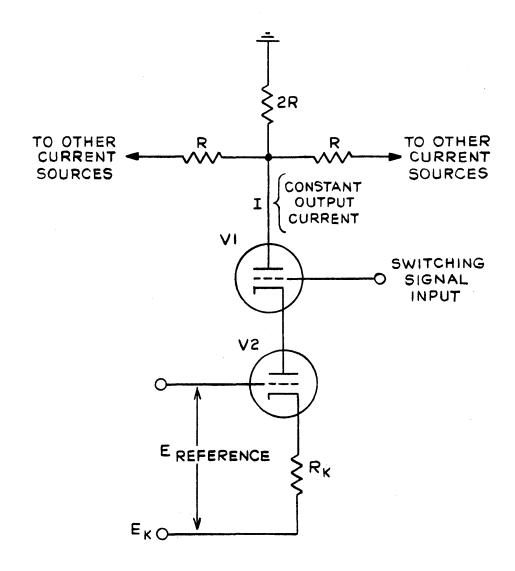

|     | 4.3  |                  | ary-Weighted Decoding Circuit Using ant-Current Sources              | 61   |

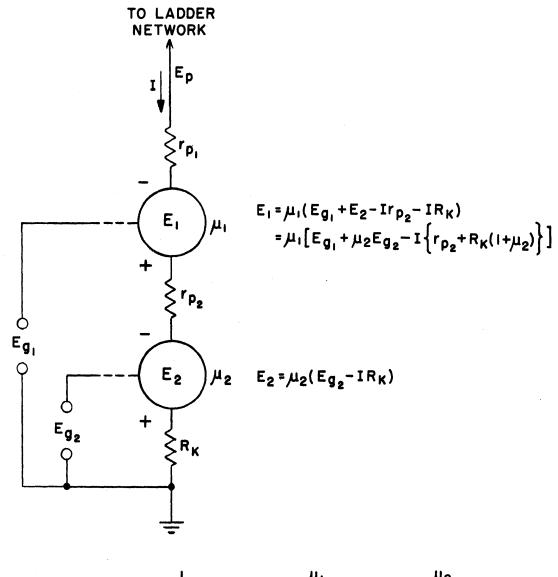

|     |      | 4.31             | Analysis of a Constant-Current Source                                | 64   |

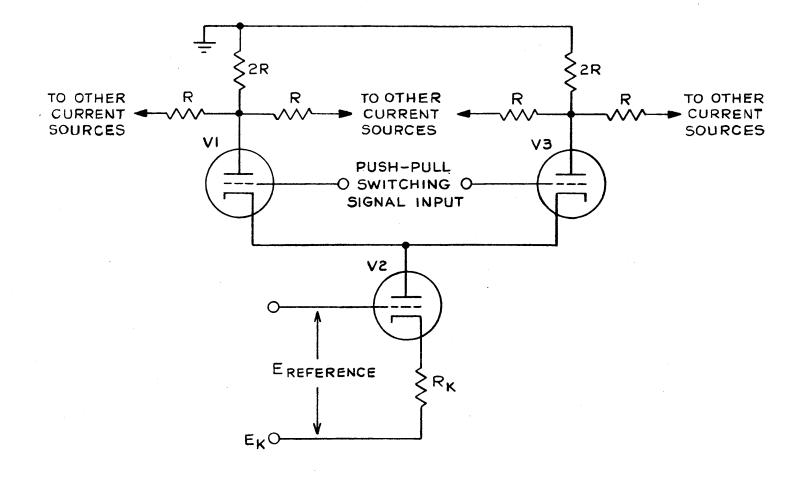

| ,   |      | 4.32             | Ways of Improving the Switching of the Cascaded Cathode-Follower     | 70   |

|     |      | 4.33             | Analysis of the Unsymmetrical Flip-Flop Used as a Storage Medium     | · 77 |

|     |      |                  | 4.331 Switching the Current Source "On"                              | 78   |

|     |      |                  | 4.332 Switching the Current Source "Off".                            | 80   |

|     | 4.4  |                  | ation of Binary-Weighted Decoding Methods Voltage or Current Sources | 82   |

| 5.0 | EXPE | RIMENT<br>CE DEC | AL STUDY OF A BINARY-WEIGHTED CURRENT-                               | 85   |

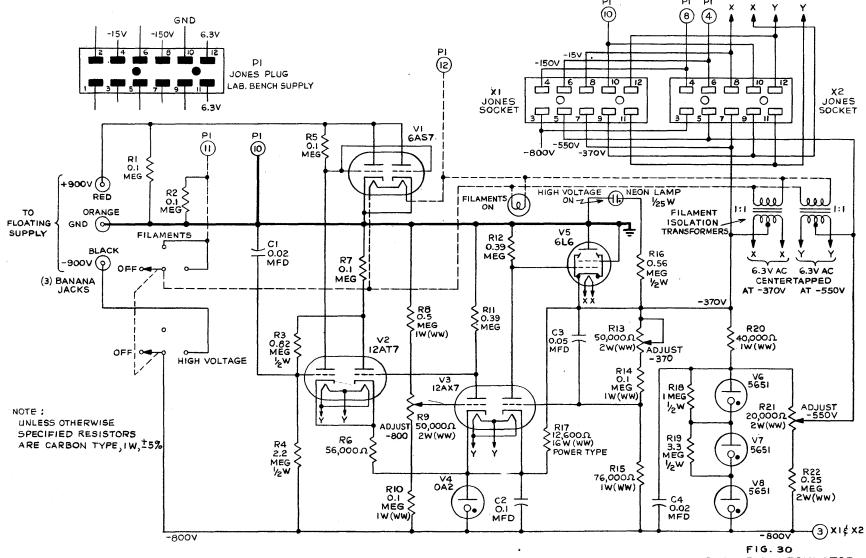

|     | 5.1  |                  | ge Reference Element and Power Supply xperimental Decoder            | 85   |

|     | e e  | 5.11             | Possible Voltage Reference Elements                                  | 86   |

|     |      |                  | 5.111 Standard Cells as Reference Elements                           | 86   |

|     |      |                  | 5.112 Dry Cells (Batteries) as Reference Elements                    | 87   |

|     |      |                  | 5.113 Standard Voltage-Regulator (V-R) Tubes                         | 87   |

|     |      |                  | 5.114 The 5651 Voltage-Reference Tube                                | 87   |

|     |      | •                | 5.115 The New Corona Discharge Tubes                                 | 88   |

|     | •    | 5.12             | Power Supply Regulator Design                                        | 88   |

|     | 5.2  | Final            | Binary-Weighted Decoder Design                                       | 91   |

|     |      | 5.21             | The Choice of Tube Type for the Decoder                              | 91   |

## $\frac{\texttt{TABLE OF CONTENTS}}{(\texttt{continued})}$

|              |       |          |                                                             | Page |

|--------------|-------|----------|-------------------------------------------------------------|------|

|              | 5.22  |          | Adopted for Switching the Current                           | 92   |

|              | 5.23  |          | of Ladder Network and Cathode-<br>er Resistors              | 93   |

|              | 5.24  | The Che  | ecking Circuit                                              | 95   |

|              | 5.25  | Other 1  | Details of the Final Decoder Design                         | 96   |

| 5.3          | Stati | c Testi  | ng of Experimental Decoder                                  | 98   |

|              | 5.31  |          | of Power Supply and Filament e Fluctuations                 | 98   |

|              | 5.32  |          | of Grid Current on Output Current                           | 101  |

|              | 5.33  | Output   | Current for Current Source "Off"                            | 102  |

|              | 5.34  |          | of Ladder Network Voltage on Current                        | 103  |

|              | 5.35  | Drift '  | Tests of Experimental Decoder                               | 104  |

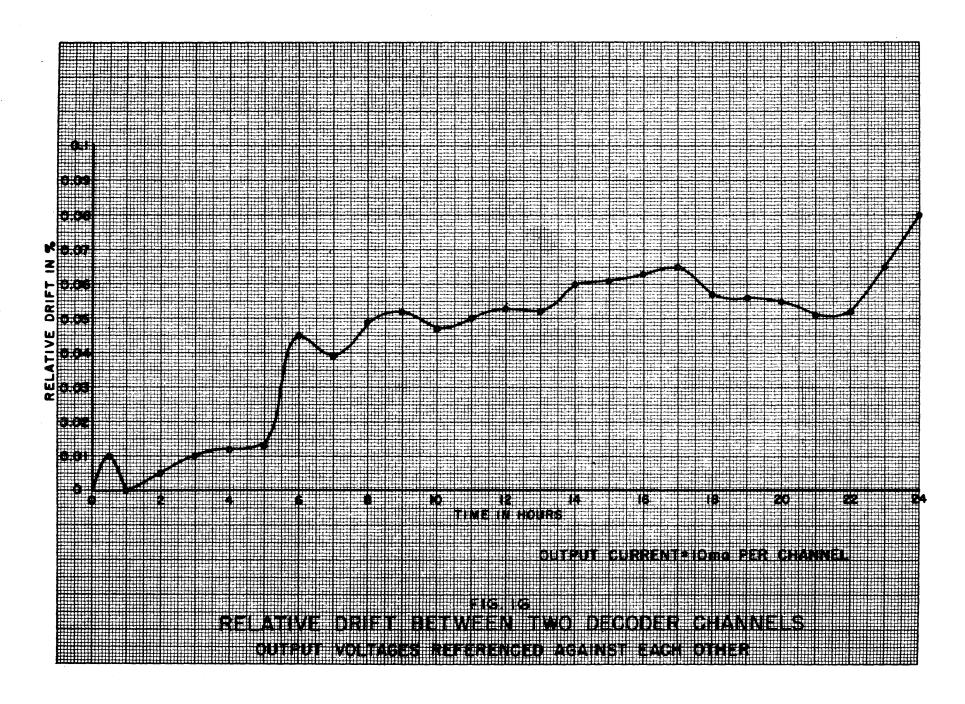

|              |       | 5.351    | Relative Drift Between Two Decoder Channels                 | 105  |

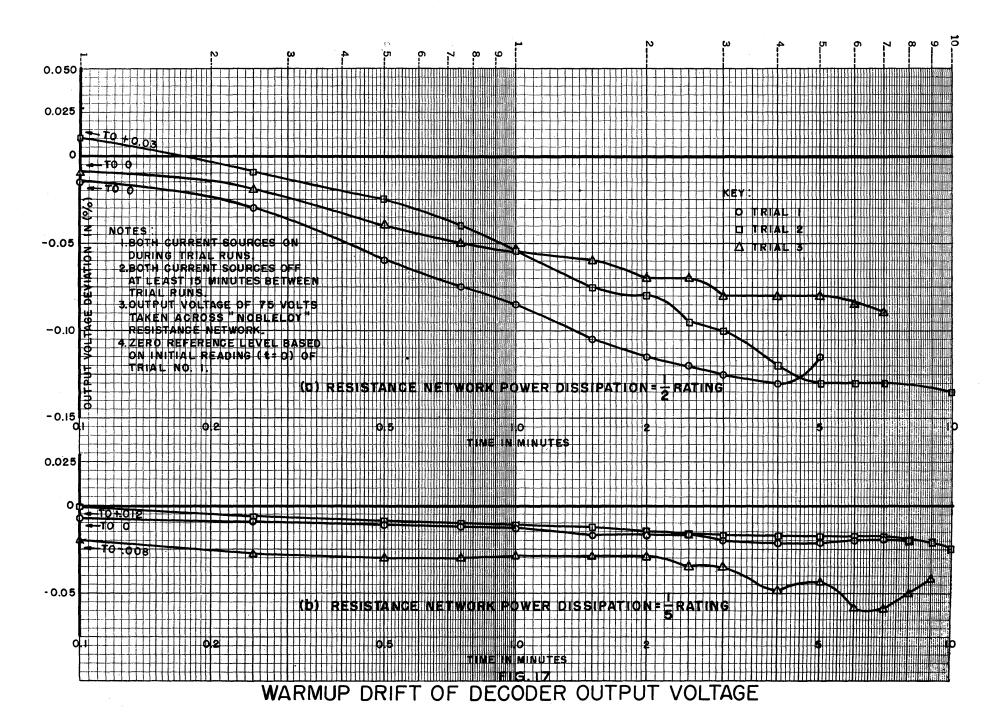

|              |       | 5.352    | Warmup Drift of Decoder Output Voltage                      | 107  |

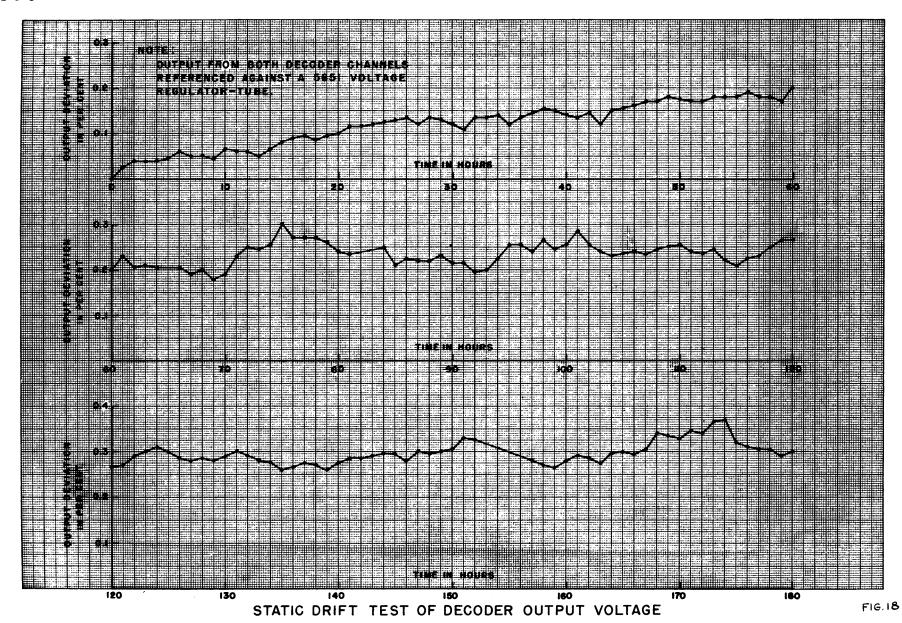

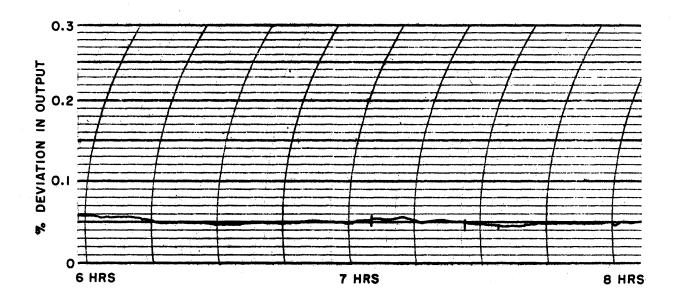

|              |       | 5.353    | Extended Drift Test of Decoder Output Voltage,              | 109  |

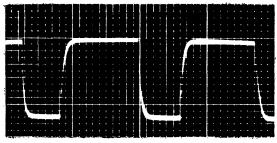

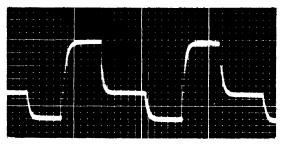

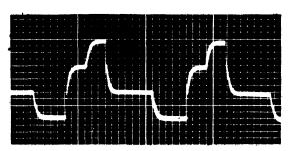

| 5.4          | Dynam | ic Test  | ing of Experimental Decoder                                 | 115  |

|              | 5.41  | Input 8  | Switching Pulse Discrimination                              | 115  |

|              | 5.42  | Single   | Decoder Channel Response                                    | 119  |

|              |       | 5.421    | Output Circuit Time Constant                                | 119  |

|              |       | 5.422    | Current Source Waveforms and Time Delays                    | 121  |

|              |       | 5.423    | Maximum Repetition Frequencies for Switching Current Source | 123  |

|              | 5.43  |          | ction Tests of Two Current-Source                           | 124  |

| 5 <b>.</b> 5 | Summa | ry and ( | Conclusions of Decoder Testing                              | 124  |

|              |       |          |                                                             |      |

## Report R-220

# $\frac{\texttt{TABLE OF CONTENTS}}{\texttt{(continued)}}$

|       |        |          |                                                                                           | Page |

|-------|--------|----------|-------------------------------------------------------------------------------------------|------|

| 6.0   |        |          | PROBLEMS IN THE USE OF BINARY-WEIGHTED                                                    | 7.00 |

|       | DECO   | DEKS     |                                                                                           | 128  |

|       | 6.1    |          | f a Binary-Weighted Decoder for ing                                                       | 128  |

|       |        | 6.11     | The Pulse Distributor                                                                     | 129  |

|       |        | 6.12     | The Amplitude Comparator                                                                  | 133  |

|       |        | 6.13     | Multiple Input Channels                                                                   | 134  |

|       | 6.2    | Trans    | mission of the Decoder Output Voltage                                                     | 135  |

|       |        | 6.21     | Use of D-C Amplifiers at the Output of the Transmission Line                              | 136  |

|       |        | 6.22     | Use of Cathode-Followers at the Output of the Decoder                                     | 138  |

|       |        | 6.23     | Use of a Three-Conductor Transmission Line                                                | 139  |

|       |        | 6.24     | Conclusions Regarding the Various Transmission Schemes                                    | 142  |

|       | 6.3    | Gener    | al Summary                                                                                | 143  |

|       | 6.4    | Sugge    | stions for Further Study                                                                  | 147  |

| APPE  | NDICE  | <u>S</u> |                                                                                           |      |

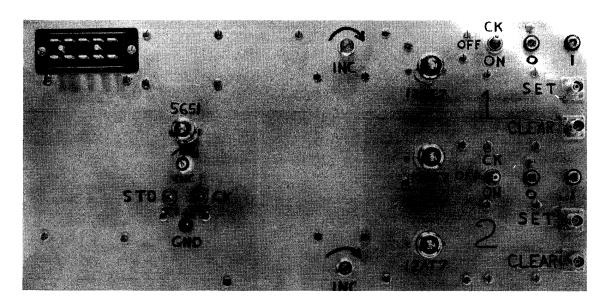

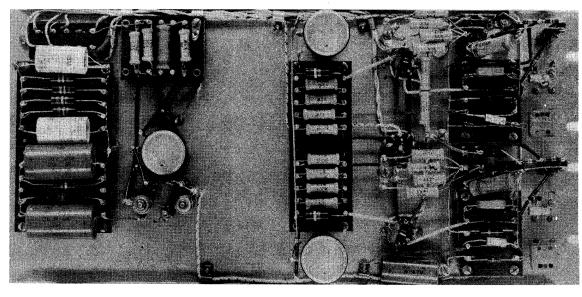

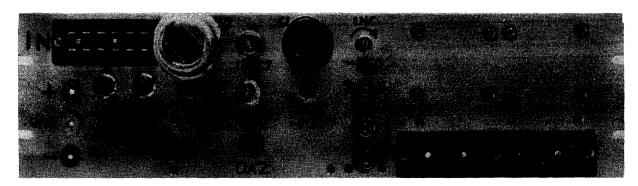

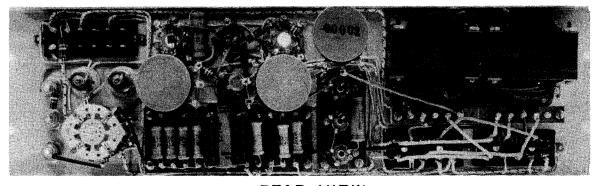

|       | Α.     | Two-D    | graphs and Circuit Diagrams of Experimental igit Decoder and Associated Power-Supply ator | `148 |

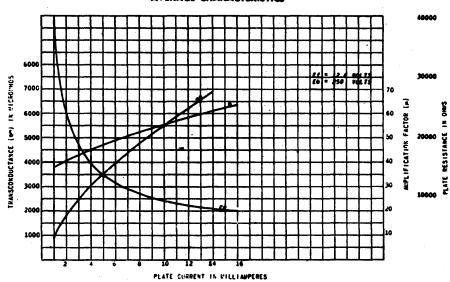

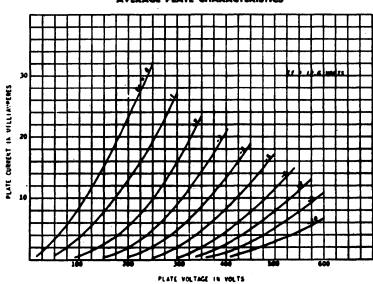

|       | В.     |          | cteristics of Decoder Vacuum Tubes and eloy" Resistors                                    | 153  |

|       | C.     | Charg    | ation of Equations for Cathode Follower ing of Three Concentric-Conductor mission Line    | 159  |

| TOT   | TOODAT |          |                                                                                           |      |

| DADI. | TOQUAL | HIL      | *************                                                                             | 165  |

## LIST OF ILLUSTRATIONS

| Figure Number | Drawing Number  | Page Number |

|---------------|-----------------|-------------|

| 1             | A-45252         | 4           |

| 2             | A-45253         | 6           |

| 3             | B-45254         | 8           |

| 4             | A-45288         | 30          |

| 5             | A-45259         | 45          |

| 6             | A-45261         | 51          |

| 7             | A-45258         | 54          |

| 8             | A-45272         | 56          |

| 9             | A-45260         | 62          |

| 10            | A-45255         | 65          |

| 11            | A-45271         | 67          |

| 12            | A-45257         | 72          |

| 13            | A-35129         | 74          |

| 14            | A-45256         | 76          |

| 15            | <b>A-</b> 45262 | 106         |

| 16            | A-45276         | 108         |

| 17            | A-45273         | 110         |

| 18            | B-45275-G       | 112         |

| 19            | A-45274         | 113         |

| 20            | A-45263         | 116         |

| 21            | A-45269         | 118         |

| 22            | A-45266         | 120         |

| 23            | A-45268         | 121         |

| 24            | A-45267         | 125         |

| 25            | A-31051         | 130         |

| 26            | A-45278         | 1717        |

| 27            | A-45287         | 149         |

| 28            | B-45270         | 150         |

| 29            | A-45286         | 151         |

| 30            | B-45264         | 152         |

| 31            | A-40481         | 158         |

## ANALYSIS AND DESIGN

OF A

DIGITAL-TO-ANALOG

DECODER

#### 1.0 INTRODUCTION

A digital-to-analog decoder is a device which converts or changes a quantity represented by a set of numerical digits into an analog quantity such as an electrical voltage or shaft position. The digital-to-analog decoder is one of two general classifications of digital-analog conversion equipment, the other classification being the inverse or encoding equipment. Digital-analog conversion may be thought of as an extension of the field of analog-analog conversion which deals with the problem of changing a quantity, such as light intensity, into an analogous quantity, such as a shaft position. A fundamental difference, however, is introduced because of the fact that the digital representation of a quantity, by its very nature, can only assume discrete values. That is, if the quantity to be represented digitally falls between two numerical values, it must be represented by one or the other of these two values and not by some intermediate value. Analog quantities, on the other hand, may assume an infinite number of values inside of the finite range through which they vary. It thus becomes the problem of the digital-analog conversion equipment to interconnect an analog system which has the possibility of conveying an infinite amount of information to a digital system which can convey only a limited amount of information, this amount being directly dependent upon the range of numbers handled by the digital system.

#### 1.1 Uses of Digital-Analog Conversion Devices

Devices which convert one analog quantity into another analog quantity have been widely used where one form of analog information

is more easily measured and controlled than others. One might well ask: why the need of converting between analog and <u>digital</u> information? The following three examples should help to answer this question.

#### 1.11 Digital Computer Control Systems

Before the advent of high-speed digital computers into the fields of electronic control and simulation, analog computers were used for performing complex and varied operations upon the information being handled by such control and simulation systems. Since these systems operate on analog information, as do the analog computers, the need for conversion equipment is only that of converting one analog quantity into another. However, analog computers are limited in their accuracy, cannot deal with complex problems involving several independent variables, and are restricted to performing a given set of operations upon the information received by them. In order to overcome these limitations and especially to allow the computer to make decisions as to what it will do with the information it receives, digital computers have been introduced into these fields.

With the introduction of digital computers into control and simulation systems, a new problem arises. Digital computers perform operations upon discrete values of input information (as represented by a sequence of numbers), whereas the control or simulation system external to the computer uses continuous information such as voltages or shaft positions. In order, therefore, for the digital computer to be connected into these systems, it is necessary to

USES OF DIGITAL-ANALOG CONVERSION DEVICES

(1) DIGITAL COMPUTER CONTROL SYSTEMS

introduce devices which will convert continuous analog information into digital information and vice versa. The replacing of analog equipment by a digital computer thus requires not only a knowledge of the computer characteristics but also a knowledge of the digital-analog conversion devices through which the computer is connected to the rest of the system.

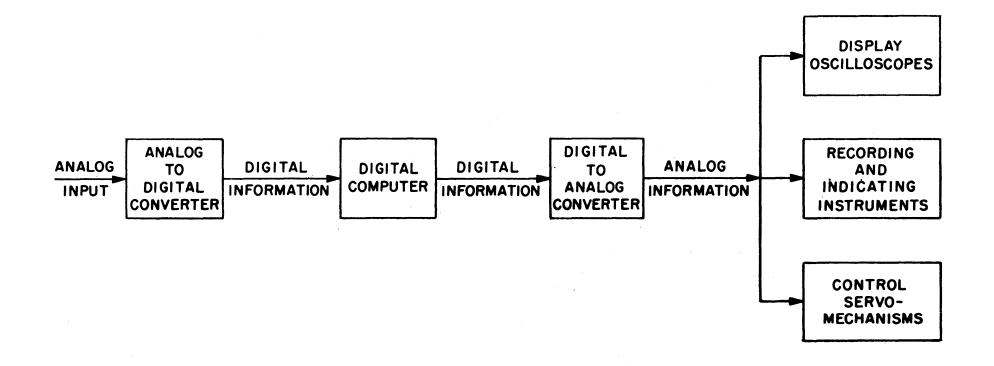

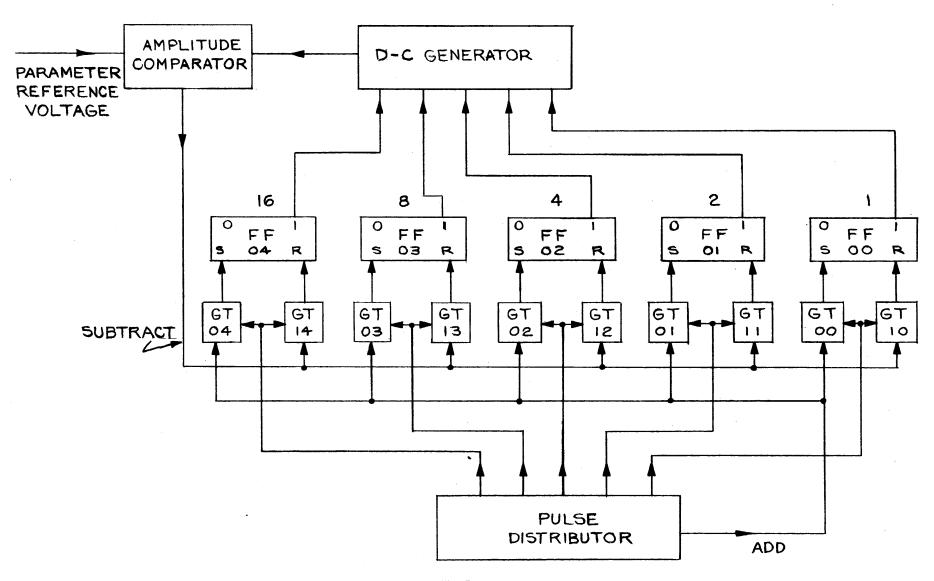

A control or simulation system utilizing a digital computer is shown in Figure 1. Analog information is received by a conversion device which changes this analog information into a form of digital information usable by the digital computer. The digital computer then processes this information, yielding the digital results of this processing at its output. These digital results are then changed into analog information by a second conversion device, the output of which is connected to the desired analog equipment.

#### 1.12 Telemetering and Servomechanism Control Systems

In some telemetering problems, the accuracy of the quantity being telemetered is often of great importance. Noise, occurring during the transmission of the information as a continuously variable quantity, reduces the accuracy obtainable at the receiving device to a value which may be considerably less than the accuracy of the transmitted information. However, it is possible to convert the continuous information into discrete or digital information at the transmitting end and send this digital information in the form of

USES OF DIGITAL-ANALOG CONVERSION DEVICES

(2) SERVOMECHANISM CONTROL SYSTEMS

time sequences of pulses, multiplexed frequencies, pulse positionings, or by some other method. Such transmission schemes can reduce transmission noise to a relatively insignificant level.

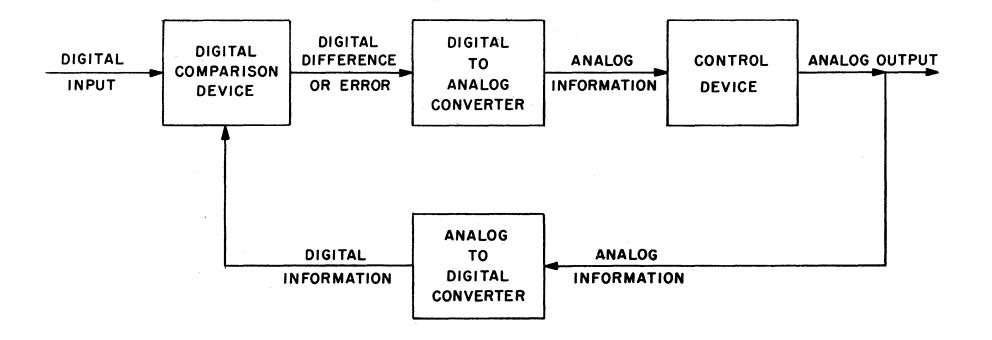

A receiving device for handling telemetered digital information might appear in the form shown in Figure 2. Here a servomechanism or control device is operated by comparing the input digital information with digital information proportional to the analog output of the device. Comparison might be made of digital quantities rather than analog quantities in order to achieve a higher degree of accuracy.

### 1.13 <u>Information Storage</u>

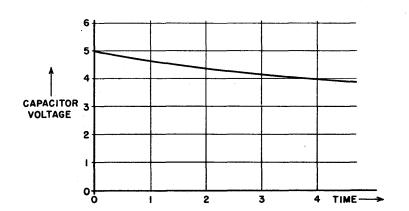

In systems where it is desirable to store information for some arbitrary length of time, storage of continuous-valued quantities becomes quite difficult due to drift or decay of the stored quantity. An example of the decay of a voltage stored on a capacitor is shown in Figure 3-A. Due to leakage resistances both in the capacitor and the associated circuitry, the capacitor voltage will decay in an exponential manner. Such a method of storage is adequate only if the discharge time constant of the circuitry is considerably greater than the time interval over which the voltage is to be stored.

The same capacitor can be made to store information indefinitely if, in some manner, the decaying voltage can be returned to its original level after it has drifted from this value. However, in order to do this, it is necessary to quantize the original voltage (change it from a continuous quantity to a discrete quantity) so

(A) INFORMATION STORED AS A CONTINUOS ANALOG QUANTITY

(B) INFORMATION STORED AS A DISCRETE OR QUANTIZED ANALOG QUANTITY

(C) INFORMATION STORED AS A DIGITAL QUANTITY

USES OF DIGITAL-ANALOG

CONVERSION DEVICES

(3) STORAGE OF INFORMATION

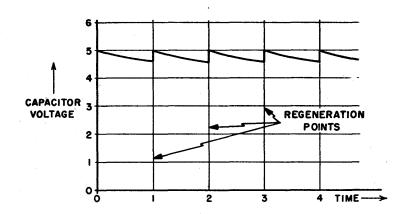

that any drift can be recognized and corrected. Such a scheme is shown in Figure 3-B where the magnitude of the decayed voltage is sensed and is increased (as indicated by the regeneration points) until it equals the next larger quantizing unit.

The information may also be stored as a digital quantity as shown in Figure 3-C. Here, the storage medium is assumed to be drift free, such as a rotary switch, so that regeneration is not necessary and the information may be stored indefinitely. Two different methods of storing this digital information are given: one of these requires the use of a group of storage units, each having 10 discrete and stable storage positions; the other requires the use of a larger group of storage units but with each having only 2 discrete and stable positions.

#### 1.2 The Analysis of Conversion Devices as Presented in This Paper

The examples given in the previous section show three of the various ways in which digital-analog conversion devices may be employed. In each of these usages it becomes important to know the characteristics of the conversion device, including a knowledge of the analog and digital input-output information. The various sections of this paper attempt an analysis of the field of digital-analog conversion equipment, with emphasis placed upon the problem of designing a binary-weighted decoder.

Section 2 of this paper discusses in a general way the various characteristics of conversion devices including the analog input to or output from the conversion device. This discussion is

presented from an engineering point of view, stressing the requirements which are important when one is designing conversion equipment. It also gives a common background upon which a rough comparison can be made between different types of conversion devices.

analog conversion equipment may operate in order to match or compare the input and output signals. It is also pointed out that these three methods are identical to the three ways in which digital information may be transmitted. The number of quantizing levels (static conversion accuracy) and the conversion time are shown to be the important parameters for discussing the internal operation of the conversion device. It is pointed out that these quantities are comparable to the signal-to-noise ratio and bandwidth of analog systems. Two brief examples are given in order to show the extreme cases which may arise when a digital-analog conversion device is to be matched to the remainder of a system.

With the information presented in Sections 2 and 3 as a foundation upon which to build, and for the reasons given therein, Section 4 approaches the problem of designing a suitable decoder by the use of parallel-channel, binary-weighting methods as distinguished from incremental methods. Two methods of binary weighting are analyzed: the use of voltage sources as the weighting elements, and the use of current sources as the weighting elements. The engineering difficulties encountered with each of these methods are discussed and an evaluation is made of their relative merits.

Section 5 discusses the final design and testing of 2 stages of a proposed 10 stage binary-weighted decoder. For reasons given in Section 4, current sources incorporating a "holding" or storage medium are used for each decoder channel (each binary digit). The results achieved with this decoder are evaluated in terms of the principles stressed in Section 2, with special emphasis being placed on accuracy, drift, speed of response, and ease of calibration.

Section 6 discusses briefly some of the engineering problems which would be encountered if a binary weighted decoder is used as an encoding device to change analog voltages into an equivalent binary number. The problem associated with the accurate and rapid transmission of the output voltage of a decoder is also considered along with some of the possible means for solving the problem. The section ends by summarizing the material covered in this report, pointing out some of the limitations, and suggesting possible directions for further study.

## 2.0 IMPORTANT ENGINEERING REQUIREMENTS OF DIGITAL-ANALOG CONVERSION EQUIPMENT

type of equipment is a difficult one, since the factor which ultimately determines a selection is the cost. If several pieces of equipment will all adequately do a specified task, then that piece of equipment which is the least expensive is chosen. However, the principal difficulty here is in the meaning of adequate.

Different applications must meet different requirements; and even for the same application, what seems adequate for one user may not be adequate for another. Unless the exact usage to which a piece of equipment is to be put is known beforehand, cost is an inadequate means of comparison. For this reason, this chapter discusses several of the important design considerations for digital-analog encoding and decoding devices.

The design of any system that is to either code or decode digital information must consider the following:

- The general applicability of the input to or output from the conversion devices;

- 2. The accuracy of the conversion:

- 3. The sensitivity of the conversion;

- 4. The freedom from drift of the conversion device;

- 5. The time taken for a single conversion:

- 6. The amount of equipment necessary for single and multiple conversion channels.

The following sections of this chapter consider each of these items briefly. Wherever possible, reference is made to the achievements and limitations of already existing conversion equipment.

#### 2.1 The Input and Output of the Conversion Device

Since a digital-analog conversion device must deal with both analog and digital representations of information, it is important to determine which of the many possible forms these representations should take. Analog information may assume a multiplicity of forms, including such things as position, velocity, pressure, voltage, current, etc. Digital information may likewise be expressed in several ways, two of which were shown in Figure 3. Two of the most useful forms (one digital and one analog) are discussed below.

#### 2.11 Digital Information Represented as a Binary Number

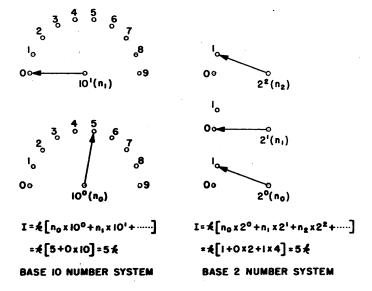

The almost universal way to represent digital information is by means of a decimal number (base 10 system) which uses the digit values 0 through 9. The position of a digit in the number determines the power of 10 by which that digit is to be multiplied. As an example, consider the number 54; the decimal representation of this number is:

$$N_{10} = n_1 \times 10^1 + n_0 \times 10^0 = 5 \times 10^1 + 4 \times 10^0 = 54$$

However, it is possible to use other forms of representing digital information by adopting a new number base. Consider, for example, the

use of a binary (base 2) form of number representation. Here, instead of the 10 distinct digital values of the decimal system, we have only 2 distinct values -- 0 and 1. The same decimal number 54 would be written in the binary system as follows:

$$N_2 = n_5 \times 2^5 + n_4 \times 2^4 + n_3 \times 2^3 + n_2 \times 2^2 + n_1 \times 2^1 + n_0 \times 2^0$$

$$N_2 = 1 \times 2^5 + 1 \times 2^4 + 0 \times 2^3 + 1 \times 2^2 + 1 \times 2^1 + 0 \times 2^0 = 110110$$

Two conclusions can be drawn from the above comparisons:

- The smaller the number base, the larger the number of digits needed to specify a given number;

- 2. The smaller the number base, the fewer the number of values each digit must assume.

This latter consideration is a very important one when high speed and high reliability are desired. Since electronic equipment is almost always used in high speed devices, and since this equipment works most reliably in an off-on (0-1) fashion, it is customary to use the base 2 system for the representation of digital information in conversion equipment.

#### 2.12 Analog Information Represented as a Voltage Amplitude

Considering only the general applicability of the input to or output from a conversion device, the advantage of using voltage as the analog parameter is immediately apparent. Electrical transducers which convert pressure, strain, temperature, light intensity,

color, sound intensity, pitch, pH (hydrogen ion) content, and an almost endless variety of other quantities into analog voltages are quite common. Also, a voltage output can be used for deflecting an oscilloscope beam, for operating a recording galvanometer or visual indicating instrument, or, in conjunction with a servomechanism, for positioning a shaft.

Several schemes have already been devised and tested for changing a set of binary digits into an analog voltage. 1,4,5,6,12, 17, 20, 24.\* Similar work has been done on the converse problem of changing an analog voltage into a set of binary digits. 6, 12, 18, 19, 21, 24. Besides the use of voltage as the analog parameter, systems have been considered and designed wherein a shaft position 20, 22, 23, 24 is used as an indication of the analog parameter. One of the disadvantages of this latter technique is the difficulty of obtaining the analog input quantities in the form of shaft positions (unless they already occur as such) without first having to convert to an analog voltage. A system which eliminates the intermediate step of conversion from an analog voltage to a shaft position and then to a set of binary digits should be more advantageous, since the introduction of each conversion step in the process introduces another source of error and the possibility of an increased complexity of the conversion equipment.

<sup>\*</sup> Superscripts refer to items in the Bibliography.

#### 2.13 "Holding" of the Analog Output of a Decoder

An important consideration in any digital-to-analog conversion is the "holding" or "non-holding" property of the output. If the output of the conversion device is "holding" from one digital input to another, a steady value of output is obtained for each digital conversion and this value of output is maintained constant, regardless of the time elapsed before the next digital input.

In systems where the digital input to the conversion device is uniformly spaced in time, and adjacent pieces of digital information are sufficiently close together, the consideration of a "holding" or "non-holding" output is not as important, since the average value of the output quantity can be directly related to the digital input. Even here, however, the "non-holding" character of the output will be important if the digital input changes rapidly, for an averaging device is effectively a low pass filter and must necessarily have a time delay over which it averages a reading.

The problem is even more acute when the digital input to the conversion device is randomly spaced in time. Either the conversion device must maintain constant the magnitude of the analog output, or else the analog receiving device must be able to store information. In either case, storage of some form must be utilized. Since most analog devices do not have the requisite storage medium, it is desirable to place this burden upon the conversion device.

#### 2.2 Accuracy of Conversion

A second important consideration in the design of a conversion device is the accuracy of the conversion. Methods have been suggested for obtaining a high degree of accuracy in both the analog-to-digital conversion 22 and in the digital-to-analog conversion 17. Such methods rely on the use of a fine and coarse analog evaluating device. As outlined, these methods give a theoretical accuracy of 0.01 percent or better, but the difficulties of building and stabilizing such devices have not been thoroughly studied. Methods which have actually been tried, and which do not use a coarse and fine level of evaluation of the analog quantity, more generally have accuracies of around 1 or 2 percent. 5, 12, 17 However, transducers, output meters, and recorders have an accuracy of about this same order of magnitude -- generally around 1/2 to 1 percent. (Bridge balancing schemes will give a much higher sensitivity to parameter changes, but the reference level of the variable parameter usually has an accuracy of only 1/2 to 1 percent.) Thus, an accuracy of conversion of around 1 to 2 percent rather than the accuracy of the analog device would be the limiting factor. It is desirable to have the overall accuracy of conversion approach the accuracy of the transducers or output devices, rather than have the accuracy limited by the conversion device.

#### 2.3 Sensitivity of Conversion

Besides the accuracy, the sensitivity of the conversion device is important -- by sensitivity is meant the ability of the conversion device to reproduce small changes in the digital or analog input quantity. It is quite often desirable to have a sensitivity which is considerably greater than the accuracy of the conversion device. Sensitivities as high as 1 part in 1,000 have been obtained 20, but a more usual figure is somewhere around 1 part in 200 or 300. 6, 12, 17, 23

High sensitivity may be obtained from an analog voltage to digital conversion device by utilizing two input channels from each transducer. One input channel is used to establish the reference level of the input quantity, while the other input channel is connected in a sensitive bridge circuit such that the input to the conversion device gives only the deviation of the parameter from a fixed reference level. This second input channel could then give a very high sensitivity; but such a scheme would not increase the overall accuracy of the conversion since this accuracy would be set by the input channel establishing the reference level. Since the input channel establishing the reference level must yield a coarse bridge adjustment and since the sensitivity of the bridge should not vary with the reference level, difficulties would be encountered in such a system if the reference level is forced to vary over wide limits.

#### 2.4 Freedom from Drift

The drift of most of the high-sensitivity systems so far developed has not been checked closely enough to determine to what extent this drift will affect the results. If a conversion system has to be frequently adjusted and recalibrated due to such things as zero drift, sensitivity to power supply voltage fluctuations, and aging components, the usefulness of the device is critically handicapped. Ideally, the system should not have to be checked after it is once installed; however, such stability of operation is generally not forthcoming, especially where high accuracy is desired.

This need for calibration, especially in the more accurate systems, often requires an increased system complexity in order that a simple checking and recalibrating scheme may be incorporated.

This checking feature has often been neglected in the past, with the result that the utility of the devices has been seriously handicapped.

#### 2.5 Conversion Time

For a computer operating with analog inputs and outputs, the time of conversion of these quantities becomes another important parameter in determining the utility of the conversion device. Analog-to-digital conversion times as short as 10 microseconds have been obtained in a Pulse Code Modulation system by the use of a special beam deflection coding tube. 12, 18, 19 The receiving end of

the system converts a time sequence of pulses to analog voltages in the same length of time. Digital-to-analog conversion times of around 3 microseconds have been obtained with the system used at Project Whirlwind for deflecting the electron beams in the electrostatic storage tubes. Conversion times, however, generally run around 150 to 250 microseconds. 17, 20

The higher the rate at which the computer can sample the several analog inputs and adjust the several analog outputs, the more versatile the computer will be. Certainly the coding and decoding times will determine the total number of analog signal inputs and outputs that can be obtained during a given time interval. This in turn limits the product of the number of channels of information and the sampling rate per channel. High conversion speed is an important quantity when designing any conversion device; however, as will be pointed out in the next section, accuracy of conversion and conversion time are interrelated and may require that a compromise be made in the one or the other.

#### 2.6 Amount of Equipment Needed

If a system is to be practicable, both the amount of equipment necessary for a single conversion channel and the additive equipment necessary for handling several conversion channels must be considered. Quite often, the additive equipment per added channel can be reduced by increasing the amount of equipment needed for a single conversion channel. Such matters must be evaluated in terms

of the probable number of conversion channels to be used, with the idea in mind of reducing the net amount of equipment and thus the net cost.

One additional factor must be considered when multiple conversion channels are used — this is the difficulty of switching analog quantities which are amplitude sensitive. Several schemes have been devised for getting around this difficulty. The amplitude sensitive analog quantity often is used to phase modulate <sup>20</sup> or frequency modulate <sup>22</sup> an alternating voltage waveform. The switching is then done on this modulated voltage, the switching device being insensitive to phase and frequency variations. Other methods involve the utilization of time positioned pulses to represent the analog magnitude, all switching operations being done on these pulses. <sup>17</sup>, <sup>20</sup>

The methods mentioned above have one inherent disadvantage -they must perform an additional conversion with the possibility of

introducing additional errors. Up to the present, a satisfactory

solution to this problem has not been obtained.

## 2.7 <u>Brief Historical Summary of Digital-Analog Conversion</u> Equipment

With the various engineering requirements for digital-analog conversion equipment firmly in mind, it is worthwhile to compare several of the devices which have been designed in this field. The following tables list the basic principles of operation, and a few other important

| Developed by                               | Type of<br>Input          | Principle of Operation                                                                                                                                                                                                                           | Accuracy | Time of Con-<br>version in<br>microseconds | Amount of Equipment<br>Duplicated for Mul-<br>tiple Inputs* |

|--------------------------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------|-------------------------------------------------------------|

| Goodall Ref. 6                             | Voltage<br>Magni-<br>tude | An amount of charge is removed from capacitor corresponding to largest binary digit contained in analog input. Process is continued for all smaller binary digits. Time-positioned pulses occur as the output.                                   | 1/32     | 10                                         | all                                                         |

| Bell<br>Labora-<br>tories<br>Ref. 12,18,19 | Voltage<br>Magni-<br>tude | Vertical position of electron beam in "coding tube" is determined by the magnitude of analog input. Horizontal deflection of electron beam gives time-positioned pulse output corresponding to magnitude of analog input.                        | 1/128    | 10                                         | almost all                                                  |

| Stabler Ref. 23                            | Shaft<br>Position         | Number in binary counter is changed each time shaft is moved. Counter is reversible in operation and direction of shaft rotation is sensed by means of photo cells.                                                                              | 1/180    | Continuous<br>Conversion of<br>Position.   | all                                                         |

| Sisson<br>Ref. 20                          | Shaft<br>Position         | Shaft position is converted to phase-modulated signal; phase-modulated signal is converted to pulse-position modulated signal; latter signal is converted to binary number by means of binary counter.                                           | 1/360    | 250                                        | approx. 1/5                                                 |

| Smith Ref. 21                              | Voltage<br>Magni-<br>tude | Output of binary weighted voltage generator is compared with analog input voltage, and resulting error signal is used to set the voltage generator. Comparison is continued until error is less than the smallest unit of the voltage generator. | 1/32     | 100                                        | approx. 1/5                                                 |

<sup>\*</sup> It is assumed here that analog voltages cannot be switched without introducing error, and hence voltage switching is not considered when evaluating the amount of duplication necessary.

| Developed by                   | Principle of Operation                                                                                                                                                                                                                                 | Is Output "Holding" in Nature? | Accuracy         | Time of Con-<br>version in<br>microseconds | Amount of Equipment<br>Duplicated for Mul-<br>tiple Outputs* |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------------------|--------------------------------------------|--------------------------------------------------------------|

| Goodall Ref. 6                 | Time-positioned input pulses discharge a capacitor in binary weighted time sequence. Output is proportional to decrease of voltage across capacitor.                                                                                                   | NO                             | 1/32             | 10                                         | almost all                                                   |

| Shannon-<br>Rack<br>Ref. 1, 12 | Time-positioned input pulses cause equal current pulses to flow in a capacitor circuit. Binary weighting is accomplished by allowing capacitor to discharge to 1/2 its value between input pulses. Output is proportional to voltage across capacitor. | NO                             | 1/128            | 10                                         | all                                                          |

| Sard<br>Ref. 17                | Binary number is converted into a pair of time-positioned pulses by means of binary counter. Time between pulses is integrated to obtain output voltage.                                                                                               | NO                             | Approx.<br>1/50  | Approx.<br>150                             | 1/3                                                          |

| Susskind<br>Ref. 20            | Same principle as used by Sard above, except that time-positioned pulses are held in delay and regeneration network.                                                                                                                                   | ¥ES                            | Approx.<br>1/200 | Approx.<br>150                             | 1/2                                                          |

| Ely<br>Ref. 4,5                | Binary weighted current sources are summed in load resistance which converts sum of currents into analog voltage. This voltage is amplified to obtain usable output.                                                                                   | YES                            | 1/32             | 3                                          | all                                                          |

<sup>\*</sup> It is assumed here that analog voltages cannot be switched without introducing error, and hence voltage switching is not considered when evaluating the amount of duplication necessary.

### 2.72 Table of Previous Decoders

quantities, for 5 decoding and 5 coding devices. The Bibliography in the Appendices of this report gives a fairly complete listing of the references dealing with these devices for those who desire a more detailed study.

Several conclusions as to the desirability of a particular conversion method may be drawn from the information presented in these tables. However, the tables do not indicate if a particular method has been exploited up to its theoretical limits. It appears as if certain of the devices could be improved in accuracy without sacrificing other factors such as time of conversion. It might be, however, that some of the methods have already been pushed to the extreme with respect to these factors. In order to obtain a better insight into the problem, the following section is devoted to an analysis of digital-analog conversion devices from the point of view of accuracy and conversion time.

#### 3.0 ANALYSIS OF DIGITAL-ANALOG CONVERSION DEVICES

As was pointed out in Section 2, there are several important quantities to consider in connection with conversion devices. When the conversion device is viewed only from the outside and one is interested in the relationship between input and output, this is certainly true. However, if one is to describe the internal operation of the conversion device, it is sufficient to consider only the following:

- The number of quantizing levels (the static conversion accuracy)

- 2. The conversion time.

As was explained in Section 1, one of the inherent characteristics of any conversion device which involves digital quantities is quantization. Quantization is introduced because of the finite range of numbers which can be handled by the digital portion of the conversion device. The second item given above, the conversion time, is introduced because there is always a certain delay between the time when an input signal is applied to the conversion device and the time when the correct output signal has been established. In analog or continuous data systems, this is generally characterized by a phase lag or time delay; in digital-analog conversion devices it is more useful to speak of this as the conversion time.

Since the above two quantities determine how fast and how accurately the components of the conversion device must operate, it is possible to derive relationships between the conversion time, the quantization accuracy, and the operating frequency for the various conversion devices. The following section gives examples of several forms of digital-analog conversion devices and shows that certain conversion methods are more restrictive in their accuracy-conversion-time relationships than others.

#### 3.1 The Problem of Conversion is One of Comparison or Matching

The problem which any conversion device must solve is:

given an input signal, determine and produce the corresponding

output signal. In order to accomplish this, it is necessary for

the conversion device to compare and match its output signal with

the input signal. Since some of the conversion devices are forced

to make more than a single comparison during this conversion

process, the number of comparisons necessary will, to a large extent,

influence the operating speed of the various components of the

conversion device.

There are three fundamental ways in which the requisite comparison process can be carried out in the digital-analog conversion device; these are:

- 1. Serial matching of each quantizing increment;

- 2. Serial matching of each binary digit;

- 3. Parallel matching of all digits (simultaneous comparison).

It should be emphasized that this classification of conversion methods is not restricted to either encoding or decoding devices alone, but is equally applicable to both. The following sections briefly discuss and exemplify each of these methods.

#### 3.11 Serial Matching of Each Quantizing Increment

The method of increment matching is accomplished by making a comparison between the input and output signals of the conversion device. If the two do not agree, the output signal is changed by one quantizing unit. A new comparison is then made, and the process is continued until an agreement is established. There are two fundamental ways in which this method of increment matching may be accomplished:

- 1. The last tested value of the output is stored, and a new output is established by changing the preceding output a sufficient number of quantizing increments so that it agrees with the new value of the input;

- 2. The output is cleared to zero, and a new output is established by comparing the input and output at each quantizing level until the correct output level is reached.

The first method given above corresponds to the operation of the continuous coding device which was given in the table in Section 2.71 for the continuous conversion of a shaft position into a binary number. <sup>23</sup> This conversion device remembers the last position of

the shaft and changes its binary number output only if the shaft moves to a new position. Such an operating method requires, of course, that the conversion device realize in which direction the shaft has turned in order that it can correctly change the output quantity. With this type of operation, there is an obvious relationship between the frequency at which comparisons must be made (the frequency of operation of the equipment in the conversion device) and the conversion time:

$$\mathbf{f_c} = \frac{1}{2} \tag{3-1}$$

where  $f_c$  is the frequency of making comparisons, and  $\gamma$  is the conversion time.

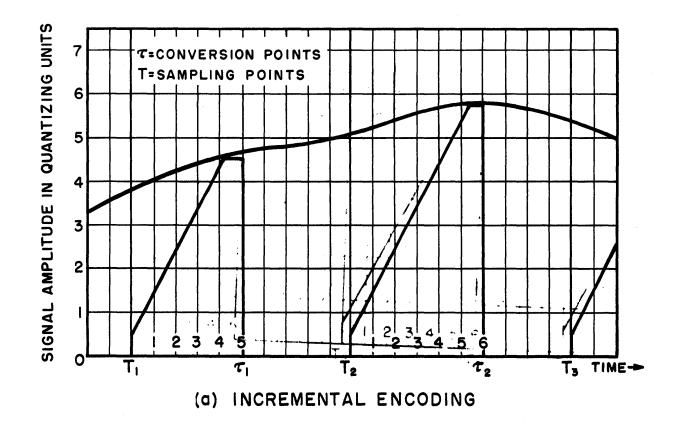

The second method given above has been used in the following form as an encoding device: 22,24 An integrating circuit generates a voltage amplitude which is proportional to the time interval being measured (counted) by a binary counter; a continuous amplitude comparison is made between this generated voltage and the voltage which is to be converted; when the output voltage of the integrator is equal in magnitude to the analog input voltage, the counter is stopped and now contains the binary number representation of the input voltage. Figure 4-a shows this form of incremental encoding.

This same conversion scheme is also used to convert binary numbers to analog voltages. The number is put into a counter, and as the integrator linearly increases the output voltage of the conversion device, pulses are sent to the counter, each pulse

subtracting one unit from the counter. When the contents of the counter equals zero, the integrator is stopped and the amplitude of the output voltage is linearly related to the input number.

In both of the methods just presented, a comparison is made between the input and output of the conversion device for each quantizing level. It is immediately obvious, therefore, that the frequency of comparison for the conversion device will depend upon the number of quantizing levels. In terms of the notation used for the continuous conversion device, we have:

$$f_{c(max)} = \frac{1}{2} \times N \tag{3-2}$$

Equation 3-2 shows that we have paid rather dearly for the privilege of each time initiating the comparison from a zero reference level. The only benefits which have resulted are:

- The conversion device no longer has to store or remember the last value of the output;

- 2. The conversion equipment need not sense the direction of change of the input signal, since the zero reference is generally made equal to the minimum (or maximum) value of the input signal.

(b) BINARY-WEIGHTED ENCODING

FIG. 4

EXAMPLES OF SAMPLING CONVERSION DEVICES

#### 3.12 Serial Matching of Each Binary Digit

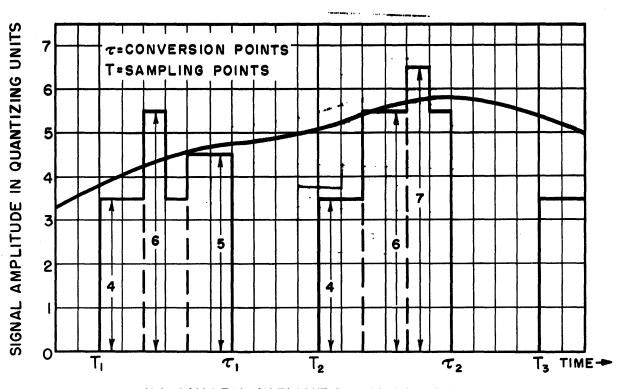

Instead of making a comparison of each quantizing increment as was done in Section 3.11 above, it is possible to make these comparisons on a digital basis. One possible way of doing this for encoding is shown in Figure 4-b. <sup>21</sup> In this method, a comparison voltage is generated by the conversion device, the amplitude of which is proportional to the largest binary digit of the output number. This magnitude is then compared with the input voltage amplitude:

- (a) If the comparison voltage amplitude is less than the input voltage, the conversion device leaves this binary digit in the one

(1) position, which at the same time leaves the corresponding comparison voltage set up;

- (b) If this voltage magnitude is greater than the input voltage, the binary digit is cleared to the zero (0) position, at the same time reducing the comparison voltage by an equivalent amount (if no other binary digit is in the 1 position, the comparison voltage is reduced to zero).

This process is continued for each smaller binary digit until every digit has been checked. At the end of the conversion process, the comparison voltage is equal in magnitude (within one quantization unit) to the input voltage, and the conversion device now has the correct binary number representation of the input signal.

There are several other conversion devices which operate in this same manner. One of these is the Bell Laboratories' Coding Tube which is used for converting a voltage amplitude into a binary number. 12, 18, 19 Here, each binary digit is checked as the deflected electron beam is swept horizontally across the tube. Another example would be the Shannon-Rack decoder which receives its digital information serially, and thus sets up each digit in time sequence. 1, 12

All of the above-mentioned devices follow the same general rule for establishing a relationship between the input and output signals of the conversion device: a comparison is made for each binary digit. As a result, the following relationship must hold:

$$f_{c(max)} = \frac{1}{2} \times \log_2 N \tag{3-3}$$

where  $f_{c(max)}$  is the maximum frequency of making comparisons,  $\mathcal{T}$  is the conversion time, and  $log_2N$  equals the number of binary digits in the digital part of the conversion device.

# 3.13 Parallel Matching of All Digits (Simultaneous Comparison)

Two methods have already been given by which a conversion between the digital and analog realms can be carried out. Both of these methods have operated with only a single comparison channel, requiring the comparisons to be made in a serial fashion. It is

possible, however, to parallel the conversion equipment so that all comparisons can be made simultaneously. There are two fundamental ways of doing this:

- Parallel all of the quantizing increments and interrogate the number of increments corresponding to the input signal;

- 2. Parallel the binary digits and interrogate the digits such that a correspondence is obtained with the input signal.

Obviously, it is the second method which would be used, since the first method requires N information-carrying channels, while the second method requires only  $\log_2$ N information-carrying channels. An example of the latter method is included in the table of decoders in Section 2.72 where an output voltage is established by simultaneously setting up all digits of a binary number. For this device we again arrive at a relationship of:

$$f_{c} = \frac{1}{C} \tag{3-4}$$

It is worthwhile to compare the conversion method which led to equation 3-1, with the method which led to equation 3-1, since they yield identical equations, and remembering that the methods are equally applicable to both coders and decoders. The continuous conversion device established the relationship of equation 3-1 by keeping in constant communication with the input signal. By this constant communication, the last value of the input signal was always available;

Thus, a change in this value could be sensed and the output signal correspondingly corrected. The parallel conversion method which led to equation 3-4, however, did not need to remember the last value of the input in order to establish a new value of the output. Each time a conversion is made, the total value of the input is sent to the conversion equipment over parallel channels. This latter method allows the output of the conversion device to be kept independent of the input signal fluctuations at all times except when an actual conversion is taking place; but more will be said of this later.

### 3.2 <u>Comparison of Digital-Analog Conversion Devices to</u> Analog Systems

The preceding section has established relationships between the number of quantizing levels, the conversion time, and the frequency of comparison for the various conversion devices. However, no restrictions have as yet been placed upon the number of quantizing units or upon the length of time allowable for the conversion process. The specification of these values can be accomplished only if one has a knowledge of the overall system in which the conversion device is to be used.

In order to consider the effect which the conversion device will have upon the external system and thus to determine such factors as the requisite number of quantizing units and the conversion time,

it is very helpful to have a single method of evaluation for the entire system. Since the digital-analog conversion equipment interconnects the digital and analog fields, it is possible to consider the entire system from either of these two points of view. However, because the analysis and synthesis of analog devices has been carried the further, it appears logical to choose this field. The following sections first discuss the important characteristics used to describe analog devices and then compare these characteristics and the ones established above for digital-analog conversion devices.

#### 3.21 Methods for Comparing Analog Devices

Analog equipment, especially electrical equipment, has been rather thoroughly analyzed and several methods of evaluating the various pieces of analog equipment have been developed. An electrical signal can be described in terms of its frequency components, the phase and magnitude of these components, and some sort of description of the noise, such as the mean square signal-to-noise amplitude ratio or power density spectrum. If one wishes to perform some sort of complex operation on the electrical signal, it is possible to apply the methods of filter theory and network synthesis in order to determine how well one can perform this operation. The determination of how well the operation is performed may take several forms, but probably the one most used is that of the mean square error between the desired result and the obtained result.

In analog conversion devices, generally the only desired form of operation on the input signal is that of converting it from one analog variable into another. In this case, the dynamic and steady-state accuracy and the time delay with which the conversion is achieved are the important quantities. Various analog conversion devices may thus be compared by means of the mean square error criteria, where the desired output of the conversion device is an exact replica of the input except for the form of the analog variable, i.e., related directly by means of a scale factor. If a constant time lag between the input to and the output from the conversion device is not important, then the mean square error may be evaluated by assuming the desired output of the conversion device to be delayed with respect to the input signal by a fixed time delay.

In order to obtain a value for the mean square error, it is necessary to be able to describe completely the input signal to the conversion device. Even though this description can be made and the mean square error determined, this particular error criteria may not always be the best one to use. It is possible, however, to obtain a <u>crude</u> and <u>relative</u> evaluation without using this criteria and hence without requiring a complete description of the input signal. The properties of the conversion device (which itself may be thought of as being similar to an amplifier for which the

desired output is a scale factored replica of the input) can be described in much the same fashion as one describes an amplifier — the bandwidth, the linearity or accuracy, and the noise level of the device. All three of these can produce a distortion of the input signal. When several frequency components are present in the input signal, bandwidth distortion attenuates and phase shifts some of these frequencies with respect to the others. When a single frequency component is applied to the input, linearity distortion (an amplitude-sensitive distortion) will introduce new frequency components. Noise level is usually independent of the input signal, being dependent upon the equipment in the system.

With this section as a background, it is possible to relate the conversion time and the size of the quantizing units of the digital-analog conversion device to certain of the parameters used to describe analog systems.

#### 3.22 Quantization Error Compared to Noise

In the terms of numerical analysis, quantization error is equivalent to a round-off error. This round-off error is produced because of the limited number capacity of the digital part of the conversion system. In this respect it is similar to noise, since any variation of the <u>input</u> signal within a single quantization unit does not change the <u>output</u> signal. If one were then to express the output of a quantizing device in terms of the input signal and a quantizing error, the result would be:

$$g(t) = f(t) - E[Q, f(t)]$$

(3-5)

where  $0 \le E[Q, f(t)] \le Q$  is the instantaneous deviation of the output signal, and Q is the magnitude of a quantization interval. Quantization can thus be looked upon as an additional noise or corruption of the input signal, the frequencies of this noise being dependent upon and higher than the frequencies of the input signal to the quantizing device. With quantization similar to noise, the maximum amplitude of which is equal to one quantizing unit, the necessity of keeping the quantizing units small for high accuracy systems is immediately obvious.

#### 3.23 Conversion Time Compared to Bandwidth

The conversion time has been defined as the interval between the time when an input signal is applied to be converted and the time when the output has been established to within the desired accuracy. The frequency of conversion (the reciprocal of the conversion time) thus roughly corresponds to the bandwidth of an analog system. This is readily seen by noting that as the frequency of the input signal to the conversion device increases, the accuracy of the output decreases, if the conversion frequency is maintained constant. The conversion frequency itself is related to the time constants of the conversion device in much the same way that the bandwidth of an analog system is related to the various system time constants.

#### 3.3 Matching the Conversion Device to the External System

With quantization and conversion time related to accuracy and bandwidth, it is now possible to see what relationships must exist between the conversion device and the rest of the system.

If a signal with a certain noise level is applied to the input of a conversion device, it is obviously desirable that the conversion device introduce little additional error into this signal. In order to accomplish this, it is necessary that the size of the quantization unit and the amplitude of the noise signal should be of similar magnitude. However, an additional factor which has not been considered so far is the interrelationship between the quantizing unit, the conversion time, and the characteristics of the input signal. The examples which follow should help in this respect.

One possible signal which we might specify as an input to a digital-analog conversion device is a signal for which the peak amplitude and maximum frequency are all that are specified. Inside of these boundary values, it is possible for the signal to vary in any and all fashions. If the output from the conversion device is at all times to be accurate to within one quantization unit, it is necessary to establish a new value of the output each time the input signal changes from one quantization level to another. The rate at which the input changes levels is dependent upon the slope of the input waveform and the size of the quantization units of the conversion device. The relationship which results is:

$$\frac{dE}{dt} \times C \cong Q \tag{3-6}$$

where  $\frac{dE}{dt}$  is the slope of the input waveform during the conversion,  $\gamma$  is the conversion time, and Q is the size of a single quantization unit.

The above relationship is a very pessimistic one, since it requires in the extreme that the maximum conversion frequency equal the product of the number of quantizing levels times the angular frequency of the highest frequency component of the input signal. The reason for this result is that so little was assumed to be known about the input signal to the conversion device. It might also be noted that this same relationship occurs if a simple R-C filter is used to pass such a signal, where conversion frequency is related to the filter's upper half-power frequency, and the number of quantizing levels is inversely related to the desired instantaneous accuracy of the signal at the output of the filter.

Instead of the almost completely arbitrary input signal given in the last example, let us assume a signal having a constant slope (a ramp input). If we make the slope of this ramp equal to the slope used in equation 3-6, the apparent result is that 7 must be the same as before in order to have the converted signal accurate to within one quantization unit. This is certainly true, if we proceed with the conversion as previously; but we must also recognize that a total of two readings will completely specify the ramp input signal. In this case, then, we may introduce a device which will sample the ramp at a particular point and then hold this sample for as long as is necessary to complete the conversion. By repeating this process a second value is obtained, and if the times at which the samples are obtained are known, the ramp can be completely specified.

It must be realized from these two examples that there is no unique way in which one can specify a relationship between the conversion time, the size of the quantizing units, and the characteristics of the input signal. The process of sampling and holding the input signal, as was done in the second example, need not introduce large errors if enough is known about the characteristics of this input signal. However, this knowledge of the input signal required that one know ahead of time the system in which the conversion device is to be used, and also that some suitable criteria for evaluation, such as mean square error, can be applied. If this is not the case, the two examples given, plus the fact that it is desirable to have the quantizing error and the signal noise-level of about the same magnitude, allow one to bracket the necessary requirements.

#### 3.4 Conclusions and Evaluation of the Various Conversion Methods

This section is not intended as an exhaustive discussion of all the possible types of equipment and the associated problems which one might run into in the field of digital-analog conversion devices. However, it has been possible to obtain some idea of the problems associated with conversion equipment. Certain relationships have been derived which are useful in comparing the various conversion methods and which allow a relative evaluation of such devices. The following paragraphs summarize the conclusions which can be drawn from the discussion in this section.

Quantization may be considered as a noise introduced into the input signal by the conversion device; it may also be considered

as a round-off error, if one wishes to describe it in the terms of numerical analysis. Conversion frequency is directly related to the bandwidth of an analog system: as the bandwidth of an analog system is increased in order to pass higher frequency signals, the conversion frequency of a conversion device should also be increased, if an increase in error is to be avoided.

Exact relationships cannot be obtained between the input signal to a conversion device and the conversion time unless the input signal is completely described and suitable evaluation criteria are known. However, if this evaluation can be made, it is possible, by means of sampling and holding of the input function over the conversion interval, to increase the conversion time over the limiting value obtained in equation 3-6. The type of system to which the output of the conversion device is connected is also important, since this system can help to eliminate the corruption introduced by the sampling process. 10

Three fundamental techniques have been presented in this section for the conversion between digital and analog quantities.

Each of these conversion methods has a direct correspondence to the three basic methods of transmitting digital information:

1. Transmission in series of all the increments which correspond to the present value of the signal;

- Transmission in series of each binary digit which corresponds to the present value of the signal;

- 3. Transmission in parallel of all the digital information corresponding to the present value of the signal.

Speed of conversion is achieved in the third method given above at the sacrifice of increasing the number of conversion channels. However, the method also allows a time multiplexing of the conversion equipment thus allowing for the handling of several conversion channels. Because of this speed and the possibility of multiplexing, the parallel-channel, binary-weighted conversion scheme appears to be one of the best available.

It should be noted that the parallel-channel, binary-weighted decoder discussed in Section 3.13 is also used as a part of the binary-weighted encoder discussed in Section 3.12. This decoder is that part of the circuitry which receives the pulses from a controlling device and produces the comparison voltage. As the derived relationships have pointed out, this decoder is one of the most critical parts of the conversion equipment as regards operating speed and accuracy. Since the parallel-channel, binary-weighted decoder is also a critical part of the most favorable form of encoding device, it appears advantageous to study this type of decoder in fairly close detail. With this in mind, the following section analyzes several possible designs for such decoders.

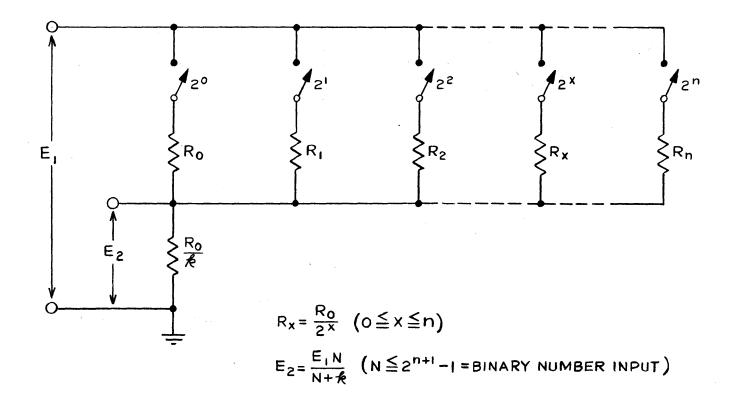

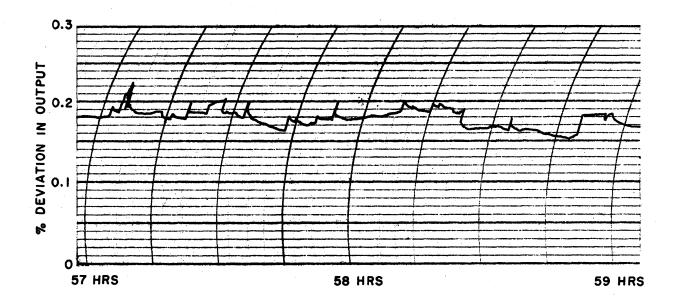

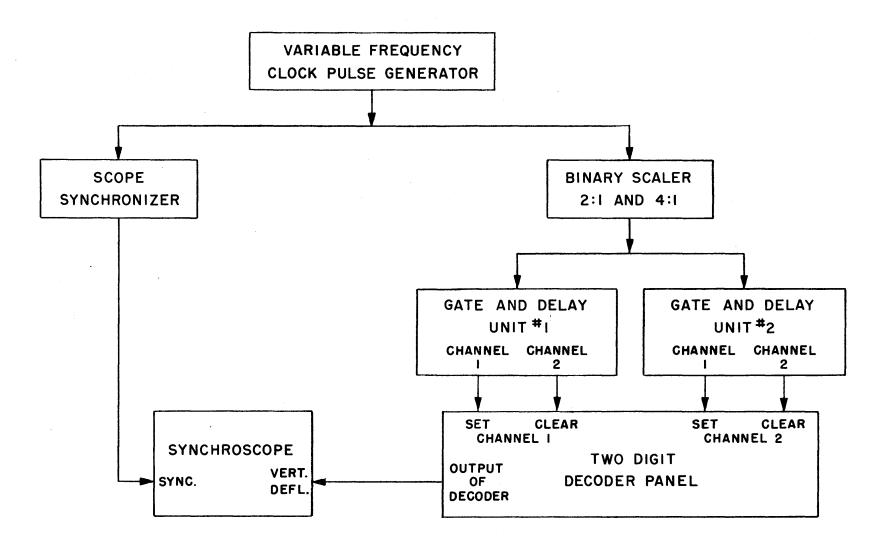

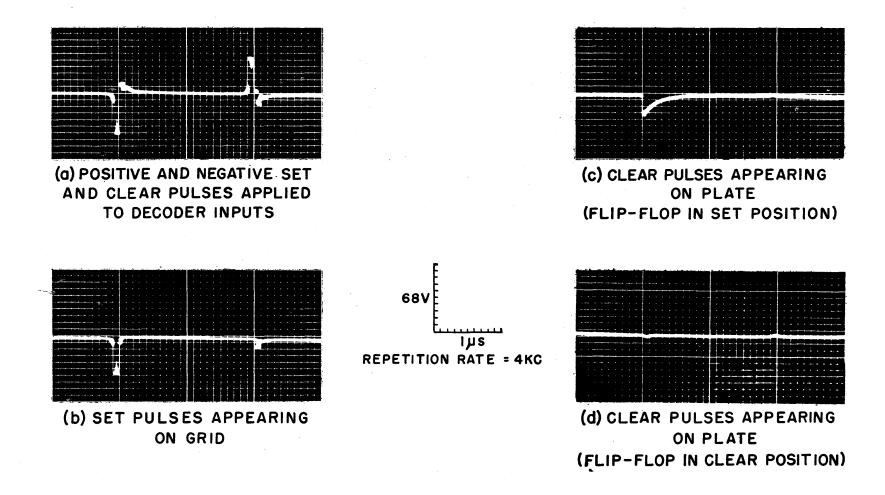

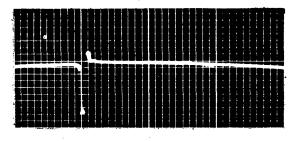

#### 4.0 SOLUTION OF THE DECODER PROBLEM BY BINARY-WEIGHTING METHODS