# PERFORMANCE SPECIFICATION 605 MEMORY SAVE CIRCUIT

|        | SPECIFICATION |

|--------|---------------|

| TO 122 | 315-0526407   |

| O.     | REVISION B    |

| Contract of the second |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _ | 7    | T- |    | _ | TC/ | ODE. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|----|----|---|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLUG-IN BOARD          | 315-0525118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   | ı    | ı  | ll |   |     |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                        | The second secon |   | Conc | -  |    | - | -   |      | and the same of th |

| В | 35ERO4643 RELEASED FOR PRODUCTION  35ERO7705  1. Revised Table 2 mo and adding T <sub>8</sub> , T <sub>9</sub> 2. Revised 3.1 adding range requirements | timings. regulated inpu                                         | , т <sub>6</sub> , т <sub>7</sub> , т | 4/11/ | 72  | 2000 |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------------|-------|-----|------|

| В | <ol> <li>Revised Table 2 mo and adding T<sub>8</sub>, T<sub>9</sub></li> <li>Revised 3.1 adding range requirements</li> </ol>                           | difying T <sub>1</sub> , T <sub>4</sub> timings. regulated inpu | , т <sub>6</sub> , т <sub>7</sub> , т |       |     |      |

| В | and adding T <sub>8</sub> , T <sub>9</sub> 2. Revised 3.1 adding range requirements                                                                     | timings. regulated inpu                                         |                                       | 8     |     |      |

|   | range requirements                                                                                                                                      | regulated input                                                 |                                       |       | , i |      |

|   | operation.                                                                                                                                              |                                                                 | it voltage<br>rcuit                   |       |     |      |

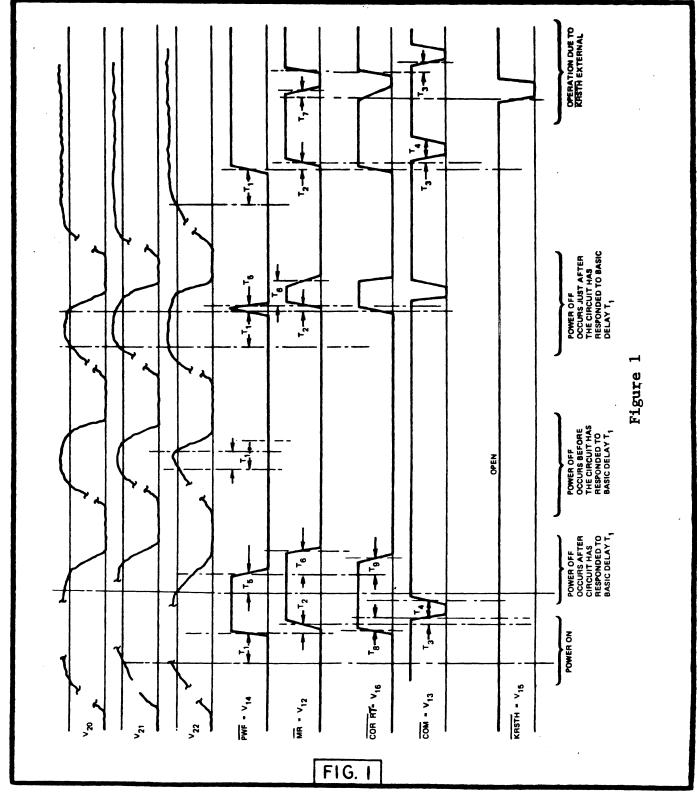

|   | <ol><li>Revised Figure 1 t<br/>in Table 2.</li></ol>                                                                                                    | o reflect timin                                                 | ngs mention                           | ed    |     |      |

|   | 4. Added Table 3, det output voltage req                                                                                                                |                                                                 | ce voltages                           | and   |     |      |

|   | <ol> <li>Revised sink curre<br/>and 16 under Para.</li> </ol>                                                                                           | nt requirement 3.2.2.                                           | for pin 12                            |       |     |      |

|   |                                                                                                                                                         |                                                                 |                                       |       |     |      |

|   |                                                                                                                                                         |                                                                 |                                       |       |     |      |

|   |                                                                                                                                                         |                                                                 |                                       |       |     |      |

|   |                                                                                                                                                         |                                                                 |                                       |       |     |      |

|   |                                                                                                                                                         |                                                                 |                                       |       |     |      |

|   |                                                                                                                                                         |                                                                 |                                       |       |     |      |

|   |                                                                                                                                                         |                                                                 |                                       |       |     |      |

| İ |                                                                                                                                                         |                                                                 |                                       |       |     |      |

|   |                                                                                                                                                         |                                                                 |                                       |       |     |      |

|   |                                                                                                                                                         |                                                                 |                                       |       |     |      |

| ĺ |                                                                                                                                                         |                                                                 |                                       |       |     |      |

|   |                                                                                                                                                         |                                                                 |                                       |       |     |      |

|   | •                                                                                                                                                       |                                                                 |                                       |       |     |      |

|   |                                                                                                                                                         |                                                                 |                                       |       |     |      |

# PERFORMANCE SPECIFICATION 605 MEMORY SAVE CIRCUIT

SPECIFICATION

315-0526407

REVISION B

### 1.0 INTRODUCTION

- 1.1 This circuit monitors the pre-regulator output voltages (regulated power supply voltages at any level within the specified range) and provides the proper timing signals to the system when the power is on and off.

- 1.2 This circuit has been designed for the 605 processor and memory.

- 1.3 This circuit is mounted on the regulator card in the power supply.

- 1.4 One circuit per card.

- 2.0 APPLICABLE DOCUMENTS

- 2.1 Circuit schematic, layout, and part list PIB No. 315-0525118.

- 3.0 INPUT REQUIREMENTS

- 3.1 Voltage Level

For description of voltages, refer to Table 1. The subindices correspond to the pin number \( \mathbf{S} \).

|                                                                                     | Inputs                             | Level                                              |

|-------------------------------------------------------------------------------------|------------------------------------|----------------------------------------------------|

| Regulated Power<br>Supply Voltages                                                  | +12 V Out<br>+5 V Out<br>-12 V Out | 5.5 to 12 Volts<br>2 to 5 Volts<br>-1 to -12 Volts |

| Nominal Value of<br>Threshold Voltage<br>V <sub>TH</sub> (Preregulated)<br>Voltages | +5 V Raw                           | 14.7 V ±3%<br>8.35 V ±3%<br>2.40 V ±3%             |

|                                                                                     | KRSTH                              | Logic "1" Open<br>Logic "0" 0 to 0.45 V            |

Power On: Each of 12 V Raw, +5 Raw, -12 V Raw >V<sub>TH</sub>

Power Off: Either of 12 V Raw, +5 V Raw, -12 V Raw (V<sub>TH</sub>

# PERFORMANCE SPECIFICATION 605 MEMORY SAVE CIRCUIT

SPECIFICATION

315-0526407

REVISION B

# 3.2 Output Requirements

For description of voltages refer to Table 1. Output voltages as per Table 3. The subindices correspond to the pin numbers.

|                      | Upper Level | Lower Level |

|----------------------|-------------|-------------|

| V <sub>12</sub> , 16 | 0pen        | 0 to 0.45 V |

| <sup>V</sup> 13, 14  | Open        | 0 to 0.45 V |

## 3.2.2 Current Level

NCR-DPD E-046 B 11/67

| Pin No. | Sinking Current  |

|---------|------------------|

| 12      | < 1 <b>1</b> 0ma |

| 13      | < 40ma           |

| 14      | < 40ma           |

| 16      | < 25ma           |

# PERFORMANCE SPECIFICATION 605 MEMORY SAVE CIRCUIT

SPECIFICATION

J15-0526407

REVISION B

### TABLE I

| TERMINAL    | DESCRIPTION                            |

|-------------|----------------------------------------|

| V12         | MR                                     |

| V13         | COM                                    |

| V14         | PWF                                    |

| V15         | KRSTH                                  |

| <b>V1</b> 6 | COR RT                                 |

| V20         | + 12 RAW                               |

| V21         | + 5 RAW                                |

| V22         | - 12 RAW                               |

|             | The subindex indicates the pin number. |

# 3.2.3 TIMING REQUIREMENTS

See Table 2 and Figure 1.

NCR

# PERFORMANCE SPECIFICATION 605 MEMORY SAVE CIRCUIT

SPECIFICATION

315-0526407

REVISION B

|                       | י                                                  | Table 2 Unit in SECS                                                                                                                                                                       |

|-----------------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | Timing                                             | Note                                                                                                                                                                                       |

| т1                    | .3 to 1.2                                          | At 5V <sub>out</sub> supply = 5 volts measured from the point where the slowest increasing voltage among V <sub>20</sub> , V <sub>21</sub> & V <sub>2</sub> pass the threshold level.      |

| т2                    | > 100 x 10 <sup>-9</sup>                           | Measured from 50% point on leading edge of PWF and 50% point on leading edge of MR signals.                                                                                                |

| т <sub>3</sub>        | > 20 x 10 <sup>-9</sup>                            | Measured from 0.8V point on positive going leading edge of MR and 50% point on negative going leading edge of Com.                                                                         |

| <sup>T</sup> 4        | 480ns to 4000 X 10 <sup>-9</sup>                   | Measured between 50% points on leading and trailing edge of Com.                                                                                                                           |

| <b>T</b> <sub>5</sub> | 0 to 600μs                                         | Measured from the point where the fastest decreasing voltage among V <sub>20</sub> , V <sub>21</sub> , and V <sub>22</sub> falls below threshold level. To 50% point on negative going PWF |

| т <sub>6</sub>        | 300 to 1000 x 10 <sup>-6</sup>                     | Measured from 50% points on trailing edge of PWF and 50% point on trailing edge of MR.                                                                                                     |

| т <sub>7</sub>        | < 1000 x 10 <sup>-6</sup>                          | Measured between 50% points on the negative going transitions of KRSTH and MR.                                                                                                             |

| т <sub>8</sub>        | 20 X 10 <sup>-9</sup> to 1000 X 10 <sup>-6</sup> ; | Measured from 0.8v point on the positive going leading edge of CORRT and 50% point on the negative going leading edge of Com.                                                              |

| т9                    | 300 to 1000 X 10 <sup>-6</sup><br>(Reference)      | Measured from 50% point on the trailing edge of $\overline{PWF}$ to 50% point on the trailin edge of $\overline{CORRT}$ .                                                                  |

NCR

PERFORMANCE SPECIFICATION

605 MEMORY SAVE CIRCUIT

315-0526407

REVISION B

### PERFORMANCE SPECIFICATION 605 MEMORY SAVE CIRCUIT

SPECIFICATION 315-0526497 REVISION B

|     | Tab                                                                                                                                                      | <u>le</u> 3 Ref. Sch. 315-05193                                                                                                                                                                                              | 93 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | Condition of the Circuit                                                                                                                                 | Output Voltages                                                                                                                                                                                                              |    |

| (1) | -12V out = 0V, +5V out = 0.5V $V_{20}$ , $V_{21}$ , $V_{22} < V_{TH}$ , +12V to be varied from 5.5V towards 12V.                                         | MR i.e. V <sub>12</sub> to be @ low logic level                                                                                                                                                                              |    |

| (2) | -12V out = 0, +12V out = 5.5V $V_{20}$ , $V_{21}$ , $V_{22} < V_{TH}$ +5 out to be varied from .5 to 5.volts                                             | MR i.e. V <sub>12</sub> to be at low logic level.                                                                                                                                                                            |    |

| (3) | +12V out = +12V<br>+5V out = +5V<br>V <sub>20</sub> , V <sub>21</sub> , V <sub>22</sub> <v<sub>TH<br/>-12V out to be varied<br/>from -1 to -12V.</v<sub> | Collector voltage of Q305 > .5V Q306 < .2V Q307 > .5V Q308 < .2V Q309 > .5V Q310 < .2V                                                                                                                                       |    |

| (4) | -12V out = -12V<br>+5V out =+5V<br>$V_{20}$ , $V_{21}$ , $V_{22}$ , $<$ $V_{TH}$<br>+12V out to be varied from<br>+2V towards +12V                       | $V_{14}$ and $V_{12}$ signals must be at low logic level when +12V out $\searrow 5.5$ V.                                                                                                                                     |    |

| (5) | -12V out = -12V<br>+12V out = +12V<br>V <sub>20</sub> , V <sub>21</sub> , V <sub>22</sub> , < VTH<br>+5V out to be varied from<br>0 - towards 5 volt     | Collector voltage of Q312 must be .8 volts when 5V out supply level is at 0.5V                                                                                                                                               |    |

| (6) | +12V out = +12V<br>+5V out = +5V<br>$V_{20}$ , $V_{21}$ , $V_{22}$ > VTH<br>-12V out to be varied<br>from -1V to -12V                                    | Collector voltage of Q305  2V and after basic delay of T1 seconds collector of Q307  2 volt Q308  5 volt Q309  2 volt Q310 = +5 volt variation of -12 volt from -1 to -12 volt, shall not change the value of above voltages |    |

PAGE 6 OF -THE NATIONAL CASH REGISTER COMPANY

# PERFORMANCE SPECIFICATION 605 MEMORY SAVE CIRCUIT

SPECIFICATION 315-0526407 REVISION B

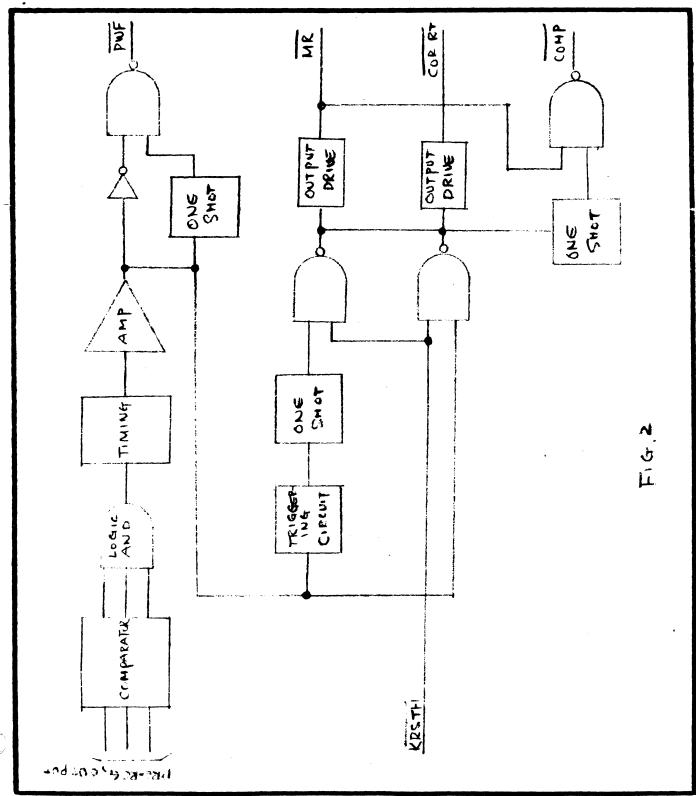

# DESCRIPTION OF OPERATION BLOCK DIAGRAM OPERATION

The functional diagram is shown in Figure 2. When the power is on and the preregulator output voltages increase above the predetermined values, the comparator outputs change from "Low" to "High". The "And" circuit "And's" them. Then the timing circuit starts the delay operation. At the end of the delay period, the slow triggering signal is amplified. The signal is delivered to the output driver (1) through the inverter. Then, PWF is released from "Low". Similarly, MR and COR RT are released from "Low" through Nand (2) - output driver (2) and Nand (2) - output driver (3). The negative-going short pulse is shown at  $\overline{\text{COMP}}$  through one shot (3) - Nand (3).

When the power is OFF, the comparator output goes "Low". In this case, this signal is transferred to the output stages through And - timing - Amp without any delay operation. This signal is delivered to the output driver (1) through the inverter. But the state change of this gate is disabled for  $100\mu$  sec by one-shot. And also with the Low-going comparator output, the triggering circuit triggers the one-shot (2) and delays grounding MR and COR RT. COMP does not change the state at this stage.

The input KRSTH with logic "o" state grounds MR and COR RT any time.

PERFORMANCE SPECIFICATION 605 MEMORY SAVE CIRCUIT

THE NATIONAL CASH REGISTER COMPANY

PAGE 8 OF 10

NCR

# PERFORMANCE SPECIFICATION 605 MEMORY SAVE CIRCUIT

SPECIFICATION

315-0526407

REVISION B

#### 4.0 DESCRIPTION OF OPERATION

### Reference Schematic Diagram 315-0519393

#### Operation

12V supply biases all the inverting inputs of  $M_1$ ,  $M_2$  OP. amps at 2.4V by way of 2.4V zener diode CR 306. As long as voltages at non inverting inputs of op amps  $M_1$  and  $M_2$  are below 2.4V, outputs of  $M_1$  and  $M_2$  will be at level of negative supply voltage. Anode of the diodes CR 307, 308 and 309 will be negative with respect to ground. Voltage levels at non-inverting inputs of op amps are established through resistor divider networks R 329, R 330; R 325 and R 326. Under the above circumstances Q 305 is open, Q 306 is closed, Q 307 is open, Q 308 is closed, Q 309 is open and Q 310 is closed. Output of  $G_1A$  which is tied to input of  $G_2A$  is high. Single shot  $M_3A$  is connected for triggering from low going signal at input 11, so  $M_3$  A is not actuated and pin 9 of  $M_3$  (pin 2 of  $G_2A$ ) is at high logic and FWF = 0.

Q 312 is saturated on account of the base drive from 5V out supply via R 345. Collector of Q 312 is at low level and output of  $G_1C$  gate is at high level. Also output of  $G_2B$  is at high level. Q 313 is saturated, so MR is low. Output of  $G_1D$  i.e. CORRT is low. Com is at high level.

#### Power On

When 12V row voltage reaches a value 14.70V, 5V row voltage reaches value = 8.35 and -12V row achieves value equal to 2.47 volts, outputs of all the op amps switches towards 12V positive supply. All diodes CR 307, CR 308 and CR 309 will be back biased and voltage at the common point anode will be 8V as decided by the resistor divider network of R 332, R333. Q 305 gets the base drive via above resistor and gets saturated. Collector of Q 306 starts rising as decided by R 336 and C 306. The time capacitor C 306 takes to charge up to voltage = 1.4V in the basic delay in the circuit. At this level of voltage, CR 310, 311 and base emitter diode of Q 307 comes out of the cut in region and Q 307 tends to saturate. Q 308 gets opened, Q 309 tends to close removing base drive from Q 310, thus pulling collector of Q 310 to high level. At the instant when voltage at the input pin 5 of G1A reaches towards V<sub>TH</sub> -.9, output of G<sub>1</sub>A will switch towards low level and output of G2A i.e. PWF will switch to high level. Also when the voltage at pin 13 of G2B reaches at the threshold level - 9V output of G2B switches to low level, thus initiating MR and CORRT signals.

THE NATIONAL CASH REGISTER COMPANY

PAGE 9 OF 10

# PERFORMANCE SPECIFICATION 605 MEMORY SAVE CIRCUIT

SPECIFICATION

315-0526407

REVISION B

### 4.0 CONT'd.

At the <u>falling</u> edge of the output of gate G1C or G2B, and rising edge of  $\overline{MR}$ , M3B will initiate 1 to 0 transition at pin 7, translating the output of G2C from zero to 1 transition for a time duration decided by R 354 and C 314 = 3 $\mu$ sec. COM signal getting initiated from <u>high</u> to low logic level for  $2\mu$ sec duration at the rising edge of  $\overline{MR}$ .

### Power Off

At the instant any of the voltage i.e. 12V raw 5V raw or -12V raw falls below the threshold voltage, junction of CR 309, CR 307, and CR 308 will return towards the negative supply voltage. Resistor R 334 clamps the negative voltage at the base to emitter of Q 305 to a value less than 1.3V. Q 305 opens and Q 306 saturates and capacitor C 306 discharges through Q 306. Discharge time constant is low as compared to the charging time constant. So Q 307 will open up, Q 308 will close, Q 309 opens and Q 310 closes. The delay which was active in the power turn on case is not active in the power off condition. As the negative going edge of voltage at collector of Q 310, M3A is initiated and pin 9 M3A gives a 1-0-1 pulse of 100µs duration decided by R 343 and C 310. So the input pin 2 of G2A is clamped to low logic for 100µsec, thus inhibiting the output of G2A from coming to low level for the duration of pulse width of M3A.

At the negative going collector voltage of Q 310, Q 311 will close. Sending positive pulse to input pin 12 of G1B, thus making output of G1B go to low level, C 312 will send negative pulse to base emiter junction of Q 312, thus opening Q 312 and pulling collector of Q 312 to high level, output of G1C will stay at low level till the time C 312 recharges through R 345, bringing Q 312 back to conduction after this delay. During the above delay period, MR & CORRT stay at high level. MR and CORRT signals go low after the above delay period. COM signal is not generated because single shot M3B is not activated.

#### External Input KRSTH

Input KRSTH with logic 0 state grounds MR and CORRT.