# SYSTEM REFERENCE GUIDE

# **APC System Reference Guide**

NEC NEC Information Systems, Inc.

819-000100-1003 4-83

#### LIMITED WARRANTY AND LIABILITY DISCLAIMER

NEC Information Systems, Inc. products are warranted in accordance with the terms of the applicable NEC Information Systems, Inc. products specification. Product performance is affected by system configuration, software, the application, customer data, and operator control of the system among other factors. While NEC Information Systems, Inc. products are considered to be compatible with most systems, the specific functional implementation by customers of the products may vary.

Therefore, the suitability of a product for a specific application must be determined by the customer and is not warranted by NEC Information Systems, Inc.

This manual is as complete and factual as possible at the time of printing, however, the information in this manual may have been updated since that time. NEC Information Systems, Inc. reserves the right to change the functions, features, or specifications of its products at any time, without notice.

NEC Information Systems, Inc. has prepared this document for use by NECIS employees and customers. The information contained herein is the property of NECIS and shall not be reproduced in whole or in part without prior written approval from NECIS.

First Printing - September 1982 Revised - December 1982 Revised - March 1983

Copyright 1982 NEC Information Systems, Inc. 5 Militia Drive Lexington, MA 02173

Printed in U.S.A.

#### FEDERAL COMMUNICATIONS COMMISSION RADIO FREQUENCY INTERFERENCE STATEMENT

"WARNING: This equipment generates, uses and can radiate radio frequency energy and if not installed and used in accordance with the instructions manual, may cause interference to radio communications. It has been tested and found to comply with the limits for a Class A Computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide protection against such interference. Operation of the equipment in a residential area is likely to cause interference in which case, the user will be required to take whatever measures may be required to correct the interference."

#### Manufacturer's Instructions and User's Responsibility to Prevent Radio Frequency Interference

#### **Manufacturer's Instructions**

The user must observe the following precautions when installing and operating this device:

- 1. Operate the equipment in strict accordance with the manufacturer's instructions for the model.

- 2. Ensure that the unit is plugged into a properly grounded wall outlet and that the power cord supplied with the unit is used and not modified.

- 3. Ensure that the unit is always operated with the factory-installed cover set on the unit.

- 4. Make no modifications to the equipment which would affect its meeting the specified limits of the Rules.

- 5. Properly maintain the equipment in a satisfactory state of repair.

#### **User's Responsibility**

The user has the ultimate responsibility to correct problems arising from harmful radio-frequency emissions from equipment under his control. If this equipment does cause interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one of the following measures. All of these responsibilities and any others not mentioned are exclusively at the expense of the user.

- 1. Change in orientation of the receiving device antenna.

- 2. Change in orientation of the equipment.

- 3. Change in location of equipment.

- 4. Change in equipment power source.

If these attempts are unsuccessful, install one or all of the following devices:

- 1. Line isolation transformers

- 2. Line filters

- 3. Electro-magnetic shielding

If necessary, the user should consult the dealer, NEC, or an experienced radio/television technician for additional suggestions. The user may find the following booklet prepared by the Federal Communications Commission to be helpful: "How to Identify and Resolve Radio-TV Interference Problems." This booklet is available from the U.S. Government Printing Office, Washington, D.C. 20402, Stock No. 004-000-00345-4.

"Note: The operator of a computing device may be required to stop operating his device upon finding that the device is causing harmful interference and it is in the public interest to stop operation until the interference problem is corrected."

### Contents

| PREFACE                     | xiii |

|-----------------------------|------|

| CHAPTER 1 HARDWARE OVERVIEW |      |

Page

### **CHAPTER 2 PROCESSOR PCB**

| 2.1  | MOTH  | ER BOARD/CARD CAGE INTERFACE   | 2-3  |

|------|-------|--------------------------------|------|

| 2.2  | MICRO | OPROCESSOR                     | 2-13 |

| 2.3  | DIREC | CT MEMORY ACCESS               | 2-14 |

| 2.4  | INTER | VAL TIMER                      | 2-19 |

| 2.5  | INTER | RUPT CONTROL                   | 2-20 |

| 2.6  | MEMO  | DRY                            | 2-26 |

|      | 2.6.1 | Main Memory                    | 2-27 |

|      | 2.6.2 | Battery-Backed Memory          | 2-28 |

|      | 2.6.3 | Read Only Memory               | 2-29 |

| 2.7  | PARAI | LLEL PRINTER CONTROL           | 2-29 |

|      | 2.7.1 | Interface                      | 2-29 |

|      | 2.7.2 | Programming Considerations     | 2-29 |

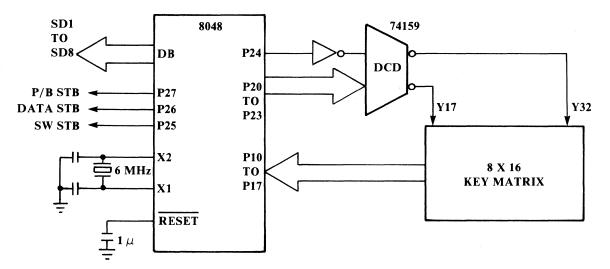

| 2.8  | KEYBO | DARD                           | 2-38 |

|      | 2.8.1 | Keyboard Layout and Scan Codes | 2-39 |

|      | 2.8.2 | Interface                      | 2-41 |

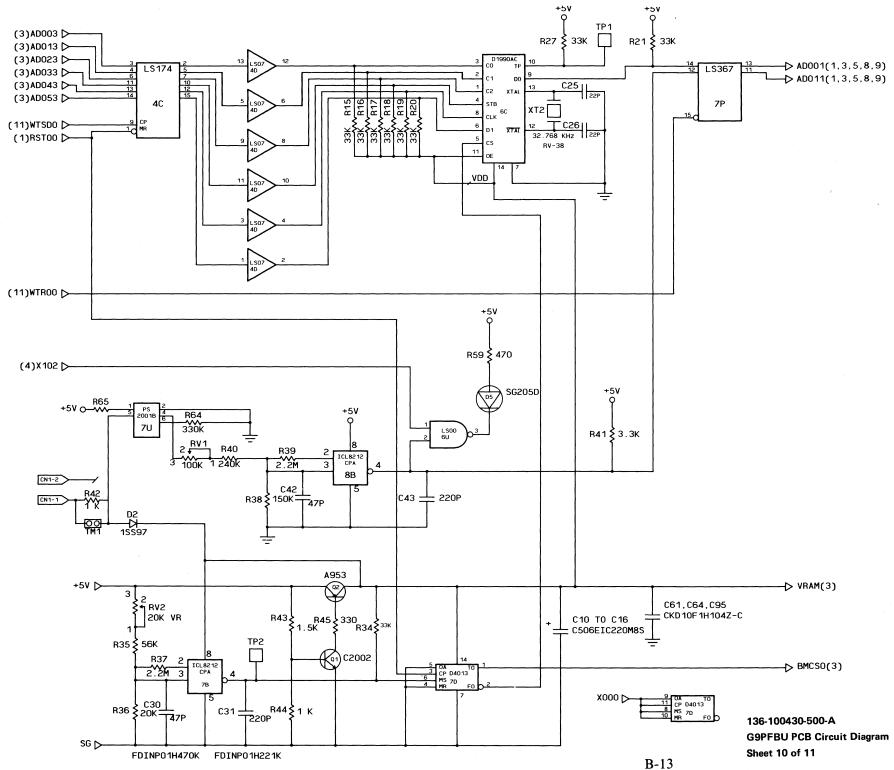

| 2.9  | CALEN | NDAR AND CLOCK GENERATOR       | 2-42 |

|      | 2.9.1 | Circuit Description            | 2-43 |

|      | 2.9.2 | Programming Considerations     | 2-44 |

| 2.10 | JUMPE | ER SETTINGS                    | 2-44 |

### **CHAPTER 3 CONTROLLER PCB**

| 3.1 | MOTH  | ER BOARD/CARD CAGE INTERFACE | 3-1  |

|-----|-------|------------------------------|------|

| 3.2 | CRT D | ISPLAY CONTROL               | 3-4  |

|     | 3.2.1 | Display Buffer Memory        | 3-5  |

|     | 3.2.2 | Programming Considerations   | 3-8  |

| 3.3 | CRT D | ISPLAY UNIT                  | 3-18 |

| 3.4 | FLEXI | BLE DISK DRIVE CONTROLLER    | 3-21 |

|     | 3.4.1 | Programming Considerations   | 3-24 |

|     | 3.4.2 | Drive A and B Interface      | 3-37 |

### Contents (cont'd)

| Page |  |

|------|--|

|------|--|

| 3.5 | FDD U   | NIT                              | 3-39 |

|-----|---------|----------------------------------|------|

|     | 3.5.1   | Specifications                   | 3-39 |

|     | 3.5.2   | Interface                        | 3-40 |

|     | 3.5.3   | Terminations and Jumper Settings | 3-40 |

| 3.6 | SERIAI  | L I/O COMMUNICATIONS CONTROLLER  | 3-43 |

|     | 3.6.1   | Specifications                   | 3-43 |

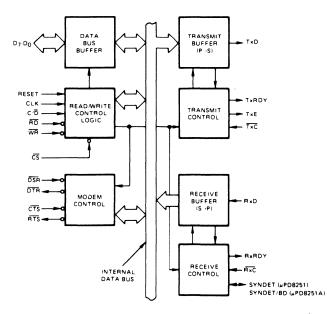

|     | 3.6.2   | Circuit Description              | 3-43 |

|     | 3.6.3   | Interface                        | 3-43 |

|     | 3.6.4   | Programming Considerations       | 3-43 |

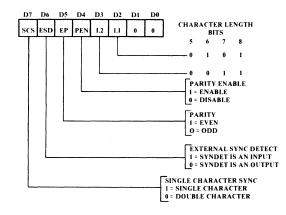

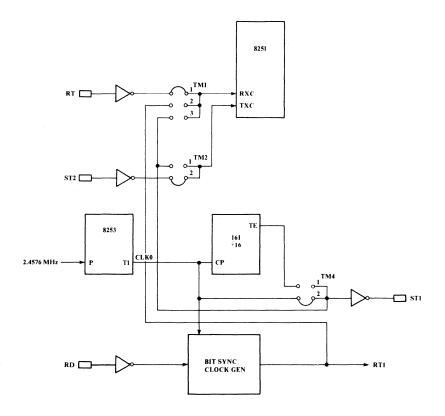

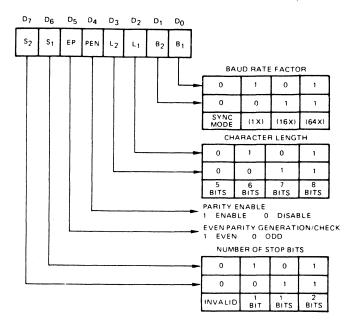

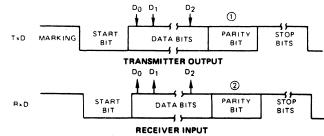

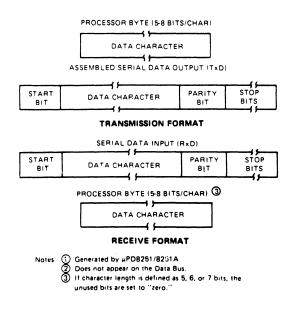

|     | 3.6.4.1 | Asynchronous Operating Mode      | 3-50 |

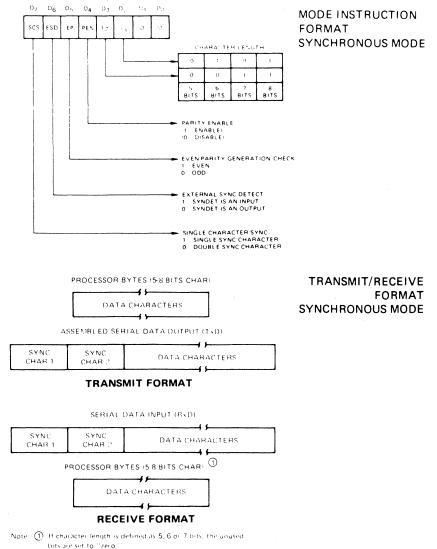

|     | 3.6.4.2 | Synchronous Operating Mode       | 3-53 |

|     | 3.6.4.3 | Business Machine Operating Mode  | 3-57 |

|     | 3.6.5   | Status Word Format               | 3-59 |

| 3.7 | SOUNE   | O CONTROL                        | 3-60 |

|     | 3.7.1   | Interface                        | 3-61 |

|     | 3.7.2   | Programming Considerations       | 3-62 |

| 3.8 | ARITH   | METIC PROCESSING UNIT            | 3-62 |

| 3.9 | JUMPE   | R SETTINGS                       | 3-64 |

### **CHAPTER 4 POWER SUPPLY**

### APPENDIX A INTEGRATED CIRCUIT DATA SHEETS

|    | 16-BIT MICROPROCESSOR A1-1                 |

|----|--------------------------------------------|

| A2 | PROGRAMMABLE COMMUNICATION INTERFACES A2-1 |

| A3 | SINGLE/DOUBLE DENSITY FLOPPY DISK          |

|    | CONTROLLER A3-1                            |

| A4 | GRAPHICS DISPLAY CONTROLLER A4-1           |

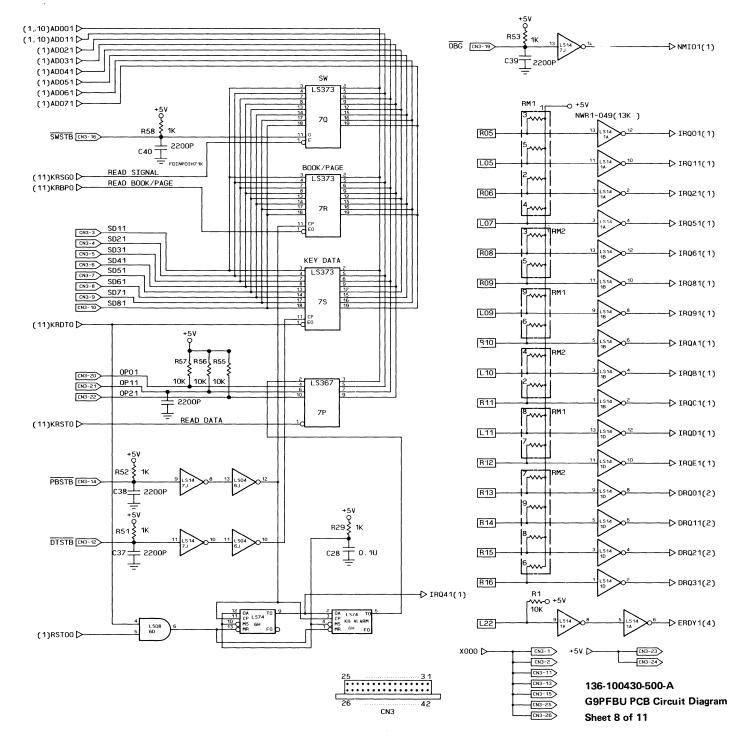

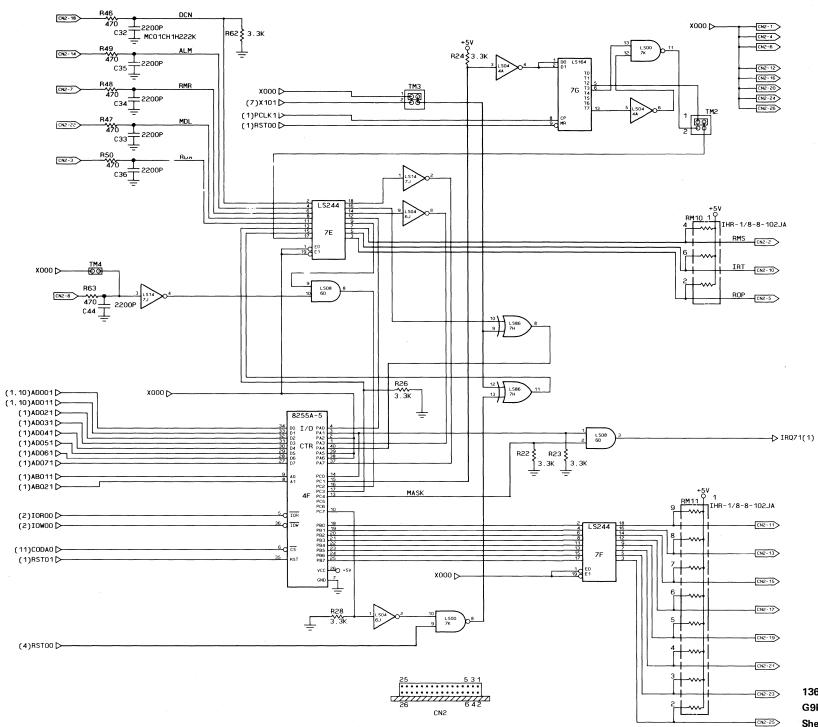

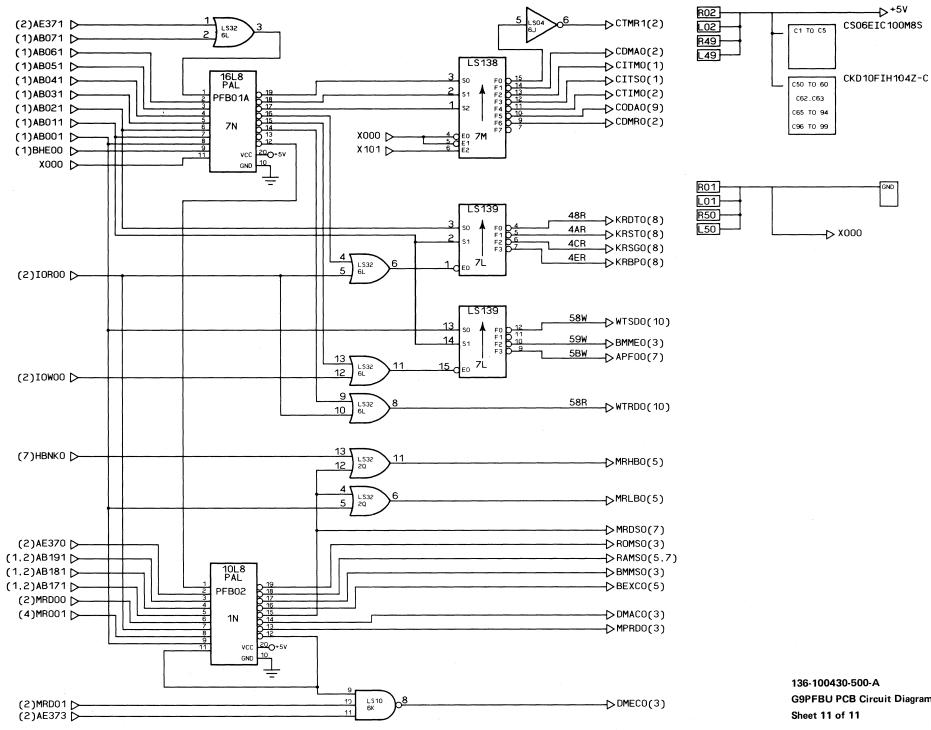

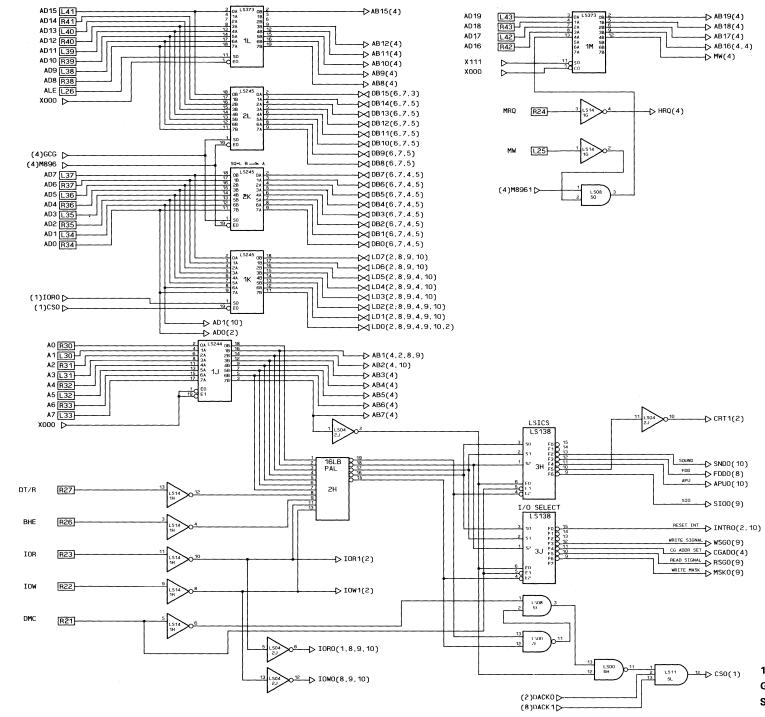

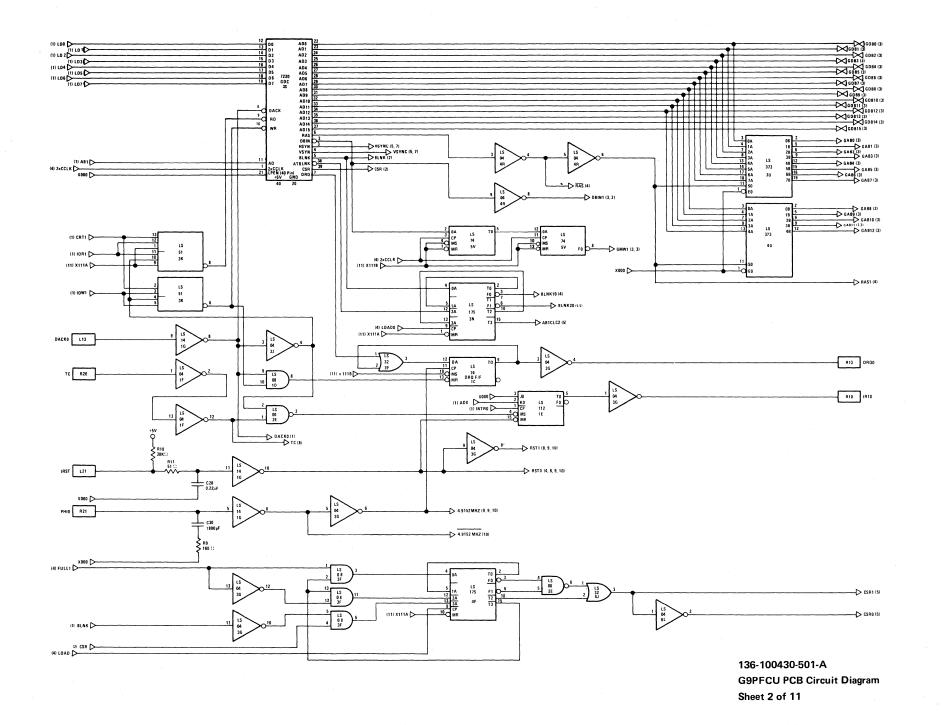

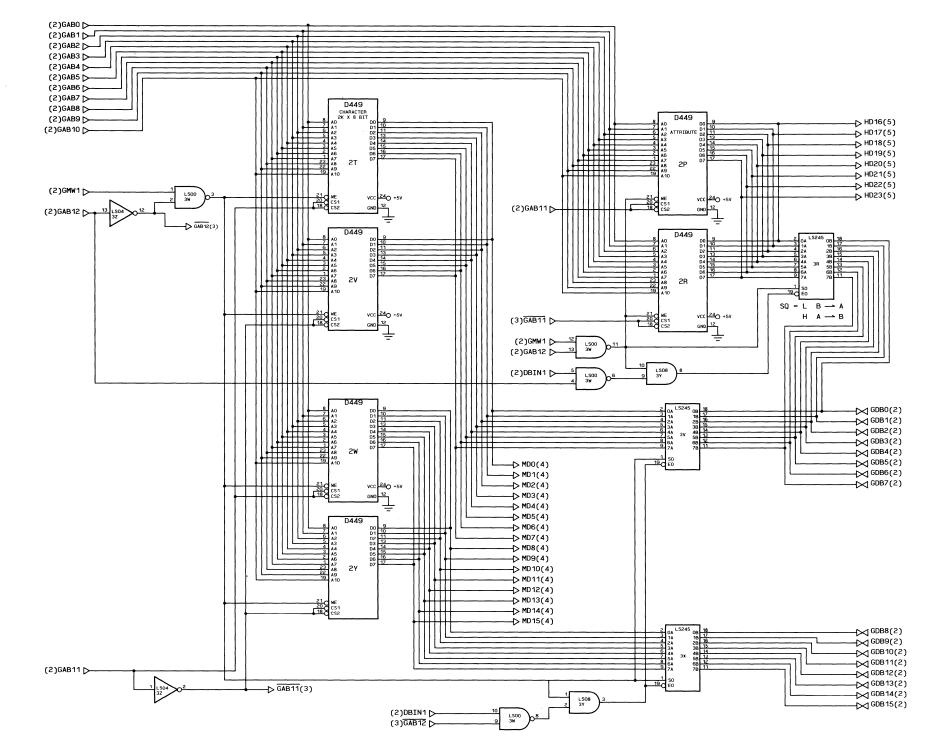

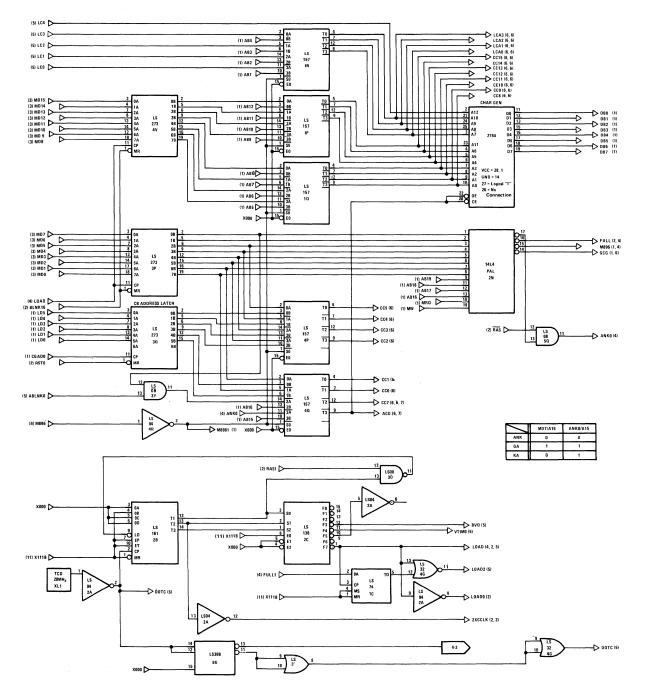

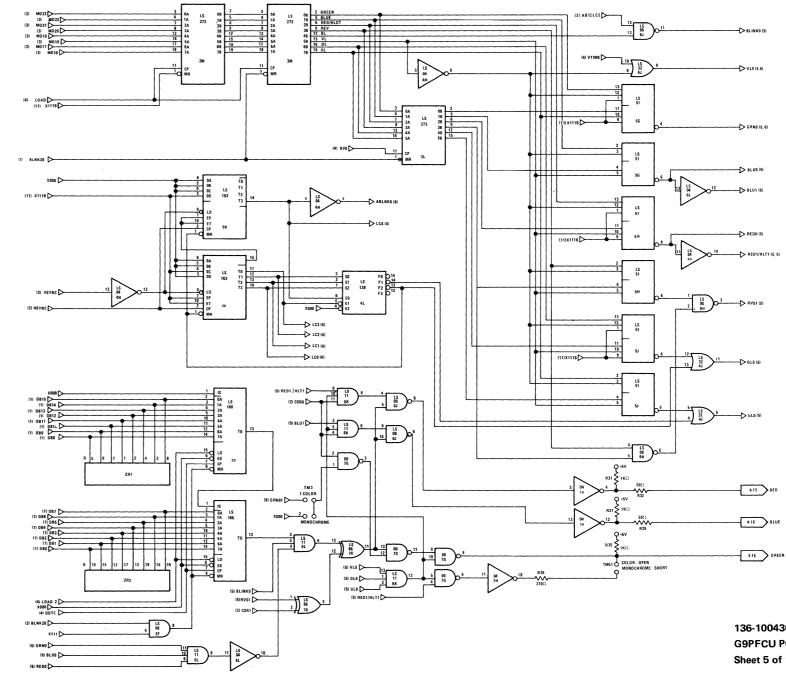

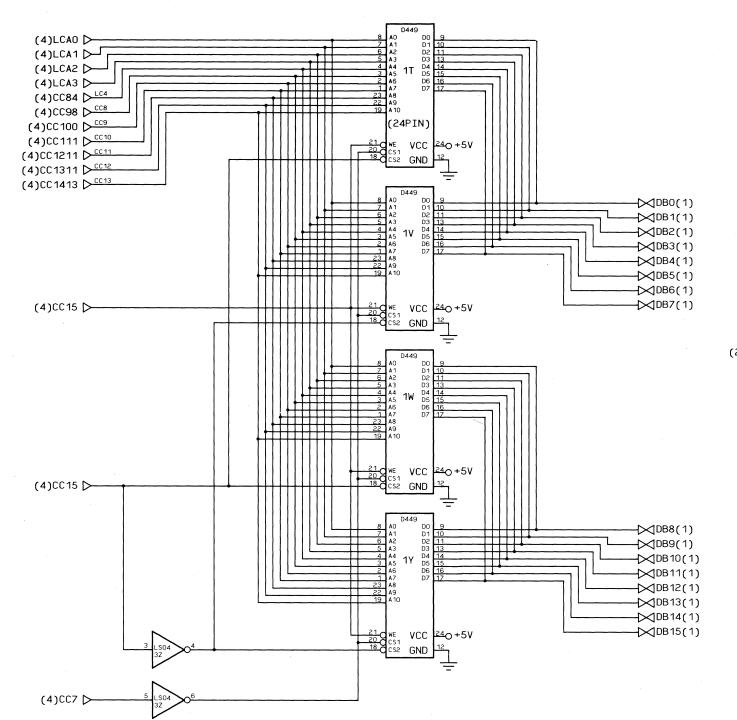

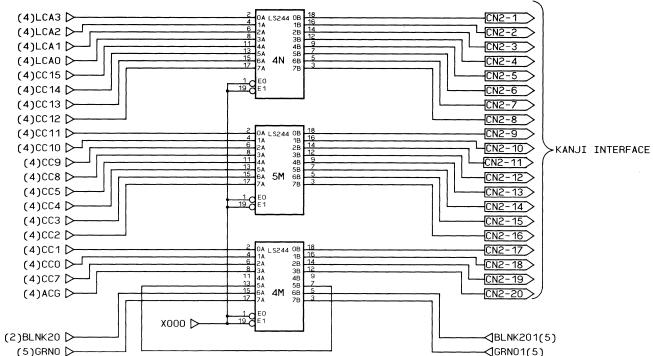

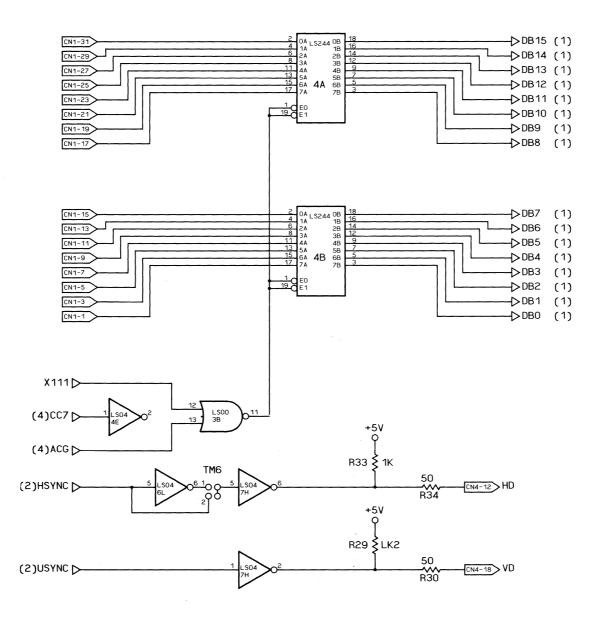

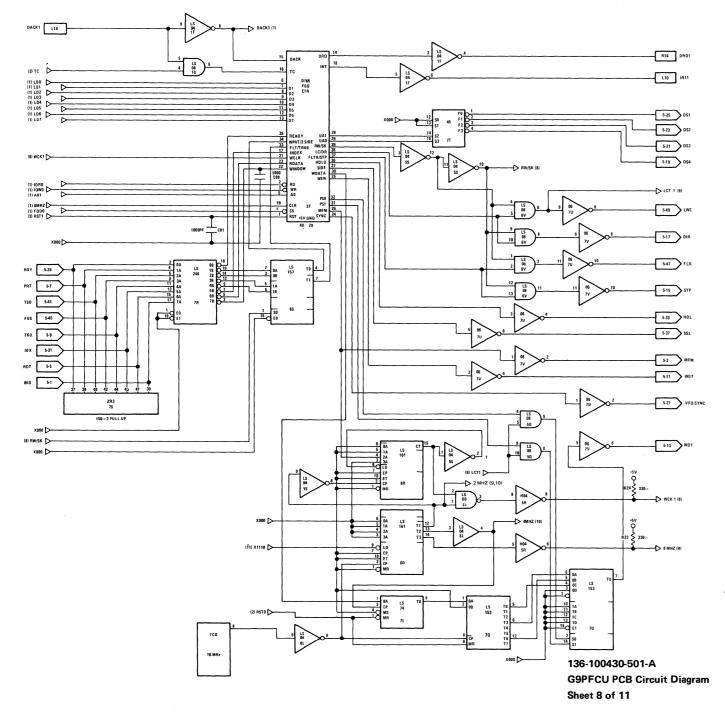

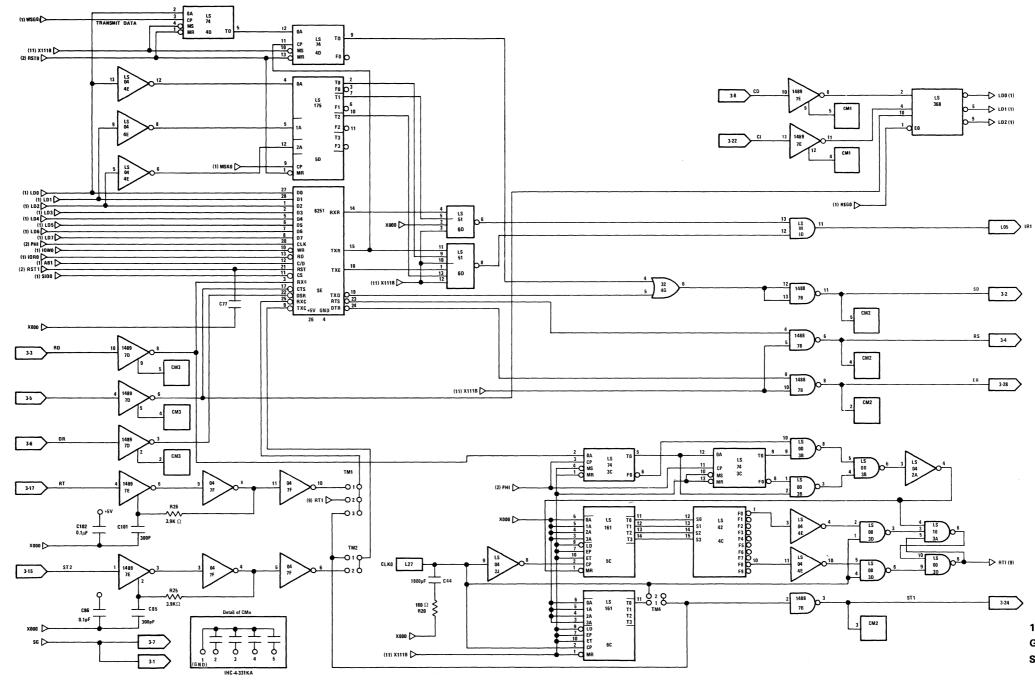

### APPENDIX B LOGIC AND SCHEMATIC DIAGRAMS

### Contents (cont'd)

### APPENDIX C PROGRAMMABLE ARRAY LOGIC DECODING SPECIFICATIONS

APPENDIX D CHARACTER CODE AND KEYBOARD INFORMATION

APPENDIX E I/O PORT ADDRESSES AND INSTRUCTIONS

APPENDIX F HARDWARE SPECIFICATIONS

### List of Illustrations

viii

| Figure | Title                                                     | Page |

|--------|-----------------------------------------------------------|------|

| 1-1    | System Block Diagram                                      | 1-2  |

| 2-1    | Processor PCB                                             | 2-1  |

| 2-2    | Processor PCB Block Diagram                               |      |

| 2-3    | Mother Board/Card Cage Interface                          |      |

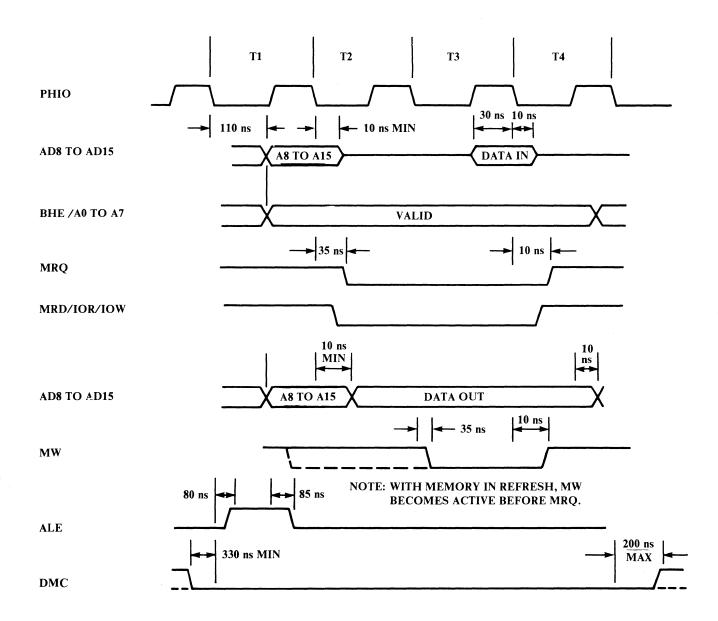

| 2-4    | Processor Timing                                          | 2-8  |

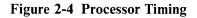

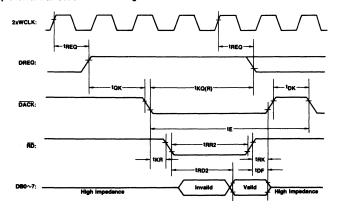

| 2-5    | DMA Timing                                                |      |

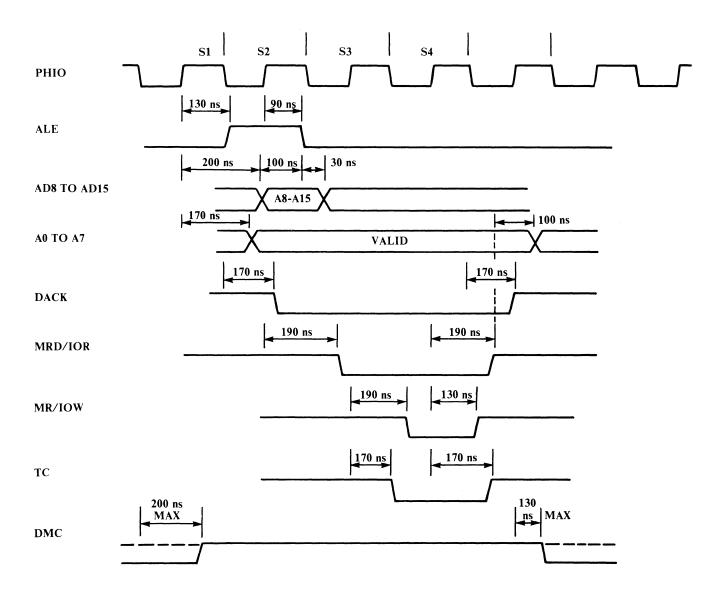

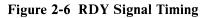

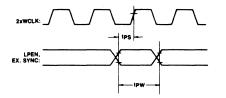

| 2-6    | RDY Signal Timing                                         | 2-10 |

| 2-7    | RFSH Signal Timing                                        |      |

| 2-8    | Processor <sup>T</sup> nterface Circuits                  |      |

| 2-9    | Device Interface Circuits                                 |      |

| 2-10   | DMA Command and Mode Registers                            |      |

| 2-11   | DMA Request and Mask Register                             | 2-17 |

| 2-12   | DMA Status Register                                       |      |

| 2-13   | Interval Timer Block Diagram                              |      |

| 2-14   | Interrupt Control Block Diagram                           | 2-21 |

| 2-15   | Interrupt Initialization Command Words                    |      |

| 2-16   | Interrupt Operation Command Words                         |      |

| 2-17   | System Memory Map                                         |      |

| 2-18   | Main Memory Block Diagram                                 |      |

| 2-19   | Battery-Backed Memory Block Diagram                       |      |

| 2-20   | Parallel Printer Control Block Diagram                    |      |

| 2-21   | Parallel Printer Cable Connections                        |      |

| 2-22   | Parallel Printer Controller Interface Timing              |      |

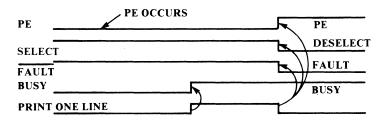

| 2-23   | Parallel Printer Controller Interface at Paper Out Status |      |

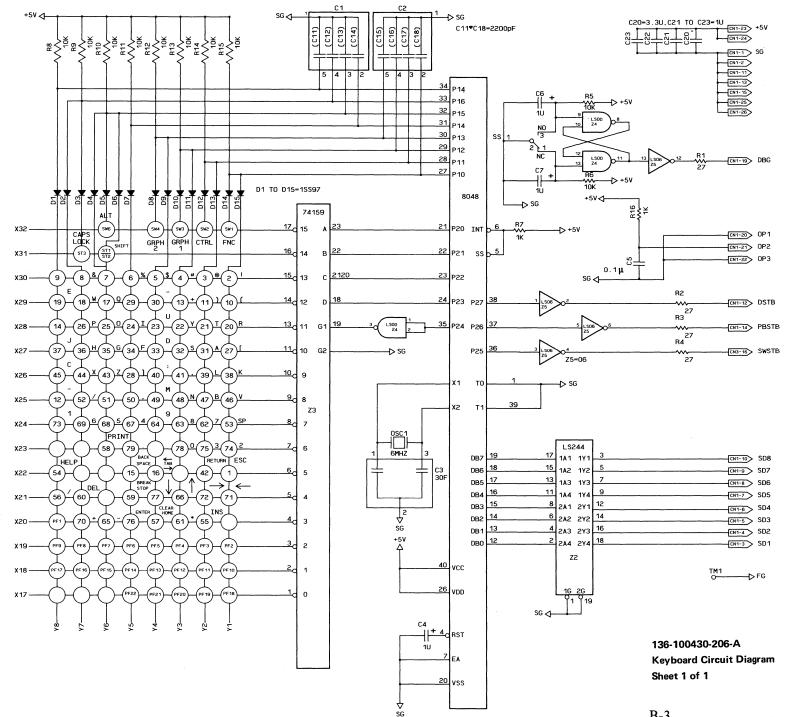

| 2-24   | Keyboard Block Diagram                                    |      |

| 2-25   | Keyboard Layout                                           |      |

| 2-26   | Keyboard Interface                                        |      |

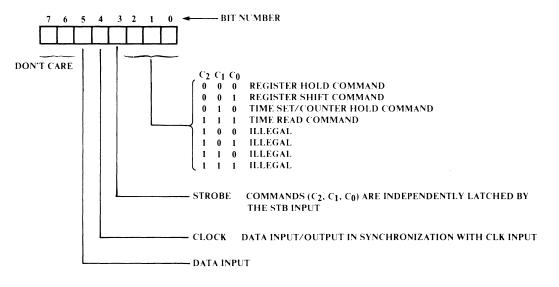

| 2-27   | Clock/Calendar Block Diagram                              |      |

| 2-28   | Clock/Calendar Format                                     |      |

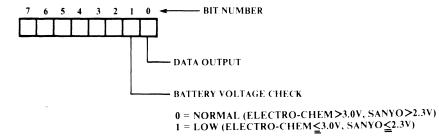

| 2-29   | Processor PCB Jumper Settings                             |      |

| 3-1    | Controller PCB                                            |      |

| 3-2    | Controller PCB Block Diagram                              |      |

| 3-3    | CRT Display Control Block Diagram                         | 3-5  |

| 3-4    | Character-Code Representation in the Character Code       |      |

|        | Buffer Memory                                             | 3-5  |

### List of Illustrations (cont'd)

| Figure | Title                                                          | Page |

|--------|----------------------------------------------------------------|------|

| 3-5    | Bit Map for Character Attribute Code                           | 3-6  |

| 3-6    | Display Buffer Memory Map                                      |      |

| 3-7    | Relationship Between Character Code, Character-Attribute Code, |      |

|        | Display Position, and Video Screen                             | 3-8  |

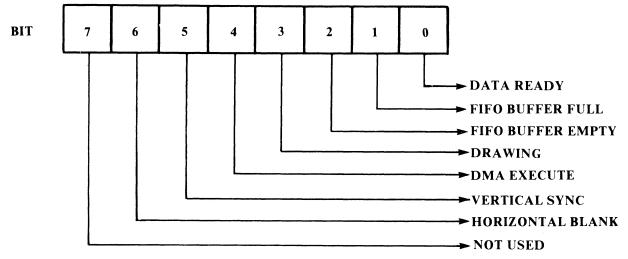

| 3-8    | GDC Status Register Bit Map                                    |      |

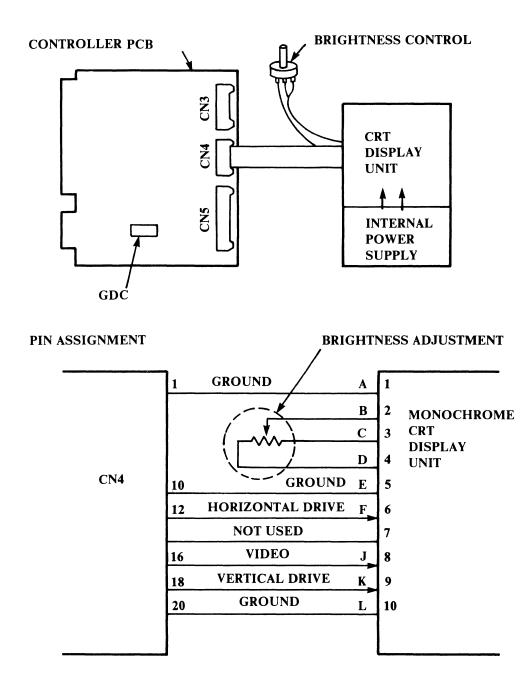

| 3-9    | Monochrome-CRT Display Interface                               | 3-19 |

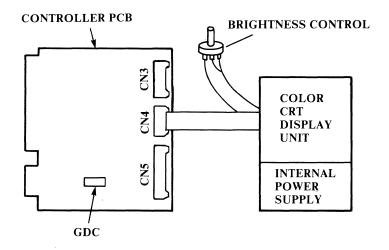

| 3-10   | Color-CRT Display Interface                                    | 3-20 |

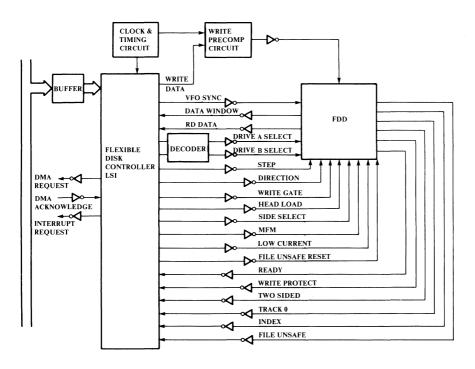

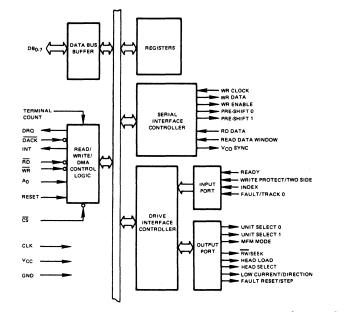

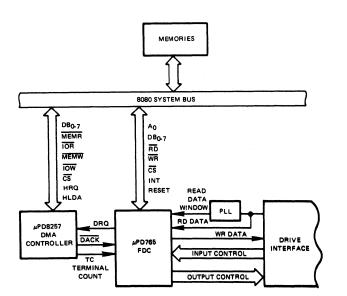

| 3-11   | FDC Block Diagram                                              | 3-22 |

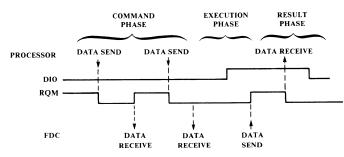

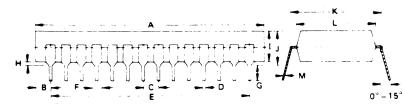

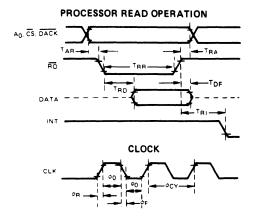

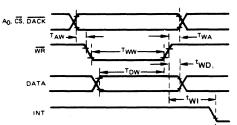

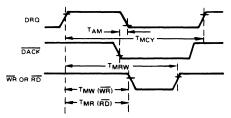

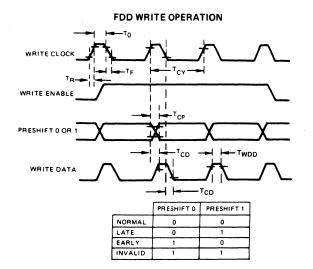

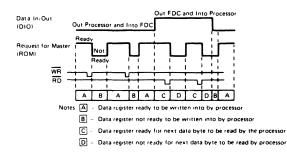

| 3-12   | FDC Timing Diagram                                             |      |

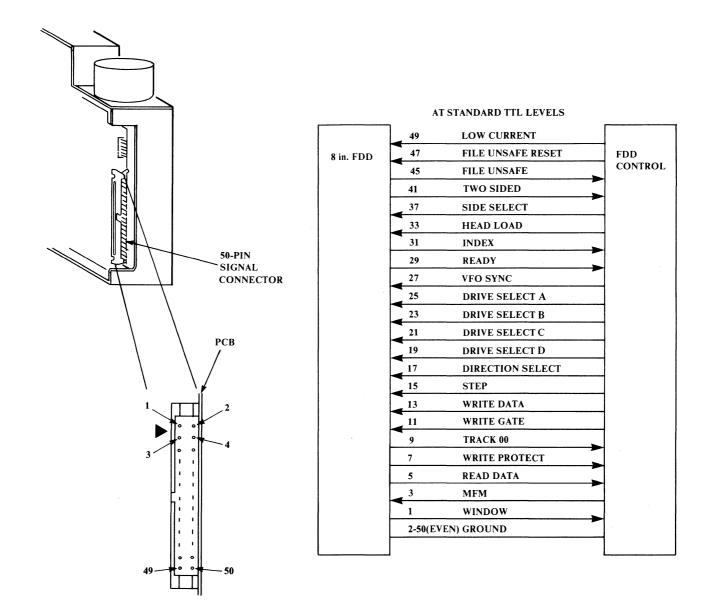

| 3-13   | FDD Signal Connector Interface and Pin Assignments             | 3-41 |

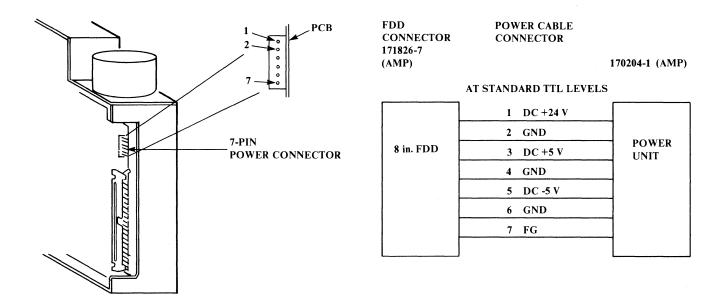

| 3-14   | FDD Power Connector Interfce and Pin Assignments               | 3-42 |

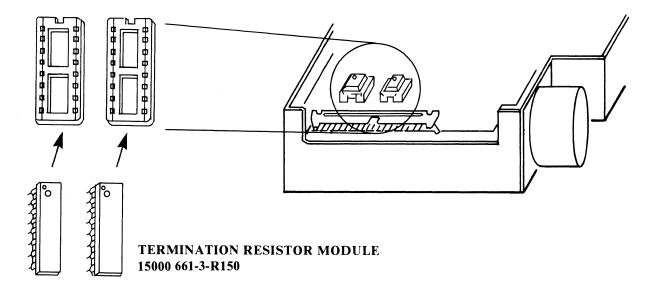

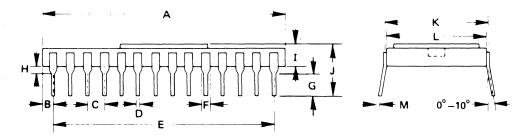

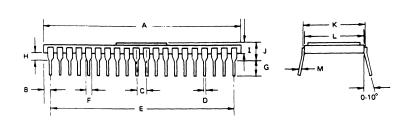

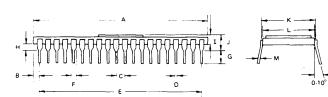

| 3-15   | FDD Termination Resistor Modules, Location                     |      |

|        | and Installation,                                              |      |

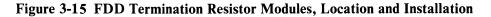

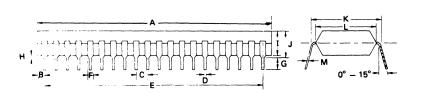

| 3-16   | FDD Jumper, Location and Proper Setting                        |      |

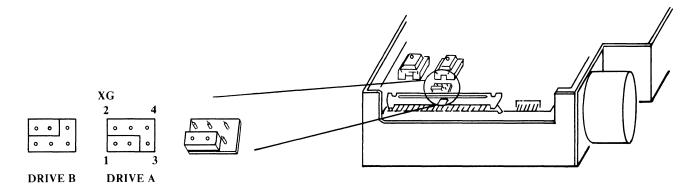

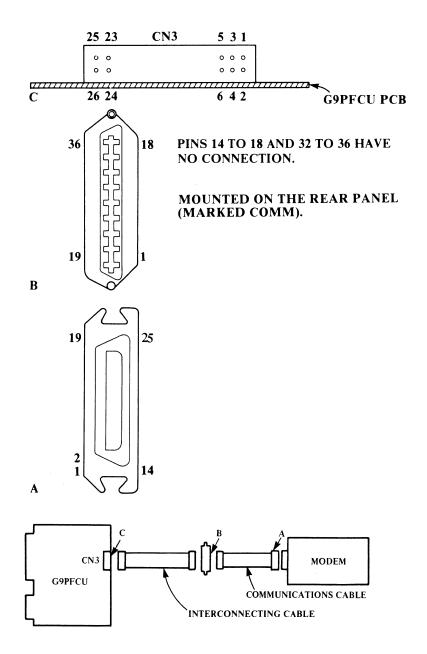

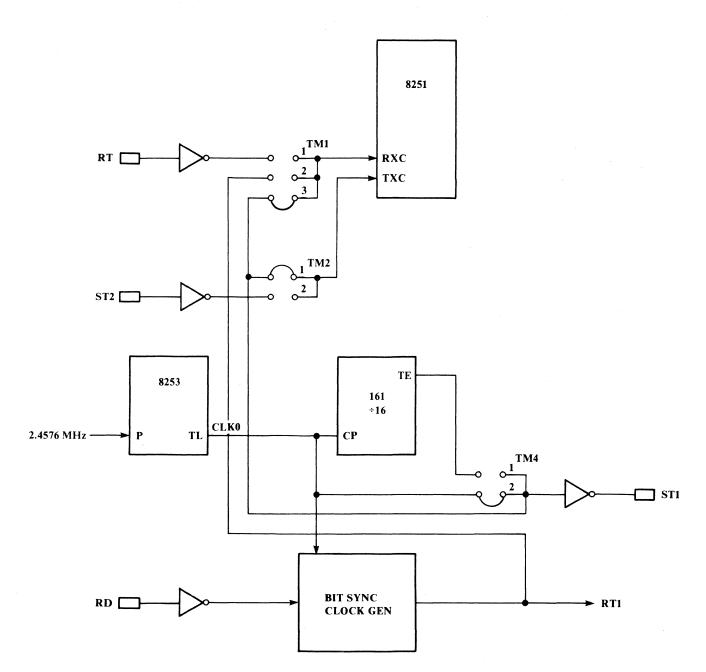

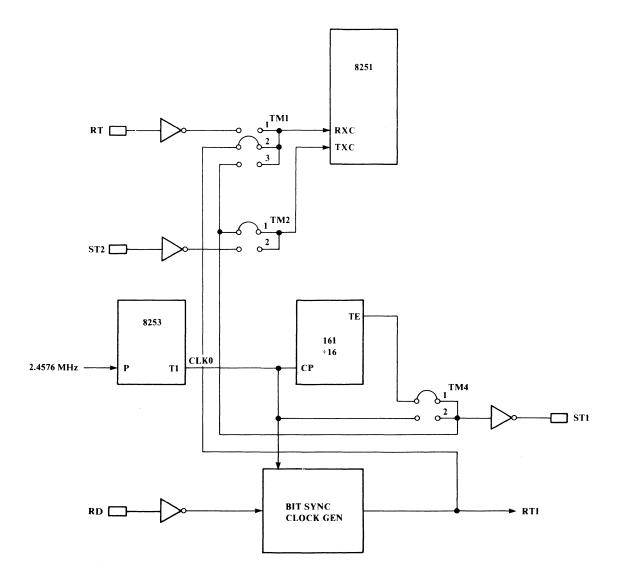

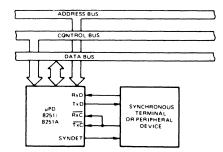

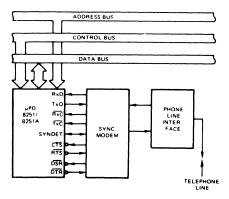

| 3-17   | Serial I/O Communications Controller Block Diagram             | 3-45 |

| 3-18   | Communications Controller Cable Connections                    |      |

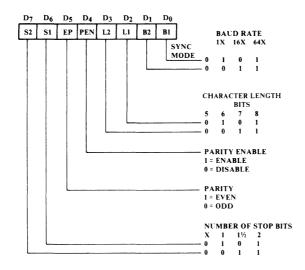

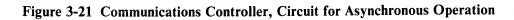

| 3-19   | Asynchronous Mode Instruction Word                             |      |

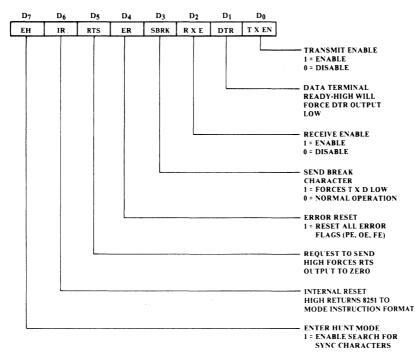

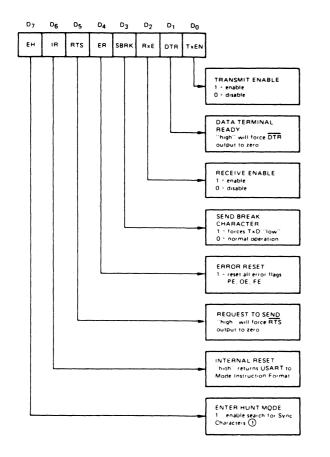

| 3-20   | Command Instruction Word Format                                | 3-51 |

| 3-21   | Communications Controller, Circuit for                         |      |

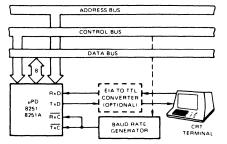

|        | Asynchronous Operation                                         |      |

| 3-22   | Synchronous Mode Instruction Word                              | 3-54 |

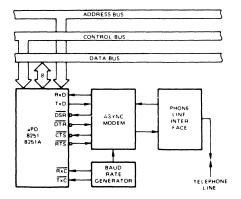

| 3-23   | Communications Controller, Circuit for Synchronous Operation   |      |

|        | Using External Clock                                           | 3-54 |

| 3-24   | Communications Controller, Circuit for Synchronous Operation   |      |

|        | Using Internal Clock                                           | 3-55 |

| 3-25   | Communications Controller, Circuit for                         |      |

|        | Business Machine Clock                                         | 3-57 |

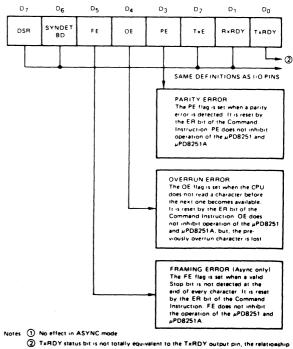

| 3-26   | Communications Controller, Status Word Format                  |      |

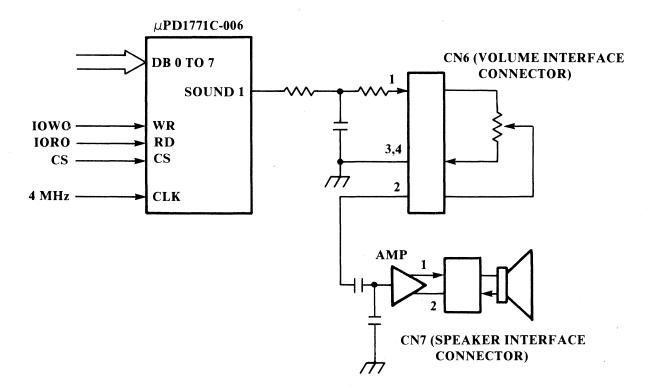

| 3-27   | Sound Control Block Diagram                                    |      |

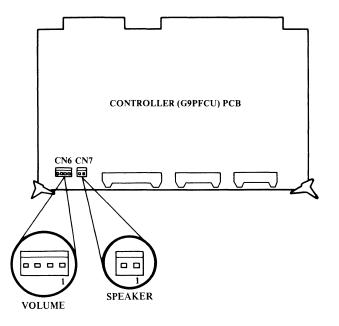

| 3-28   | Location of Sound Interface Connectors                         |      |

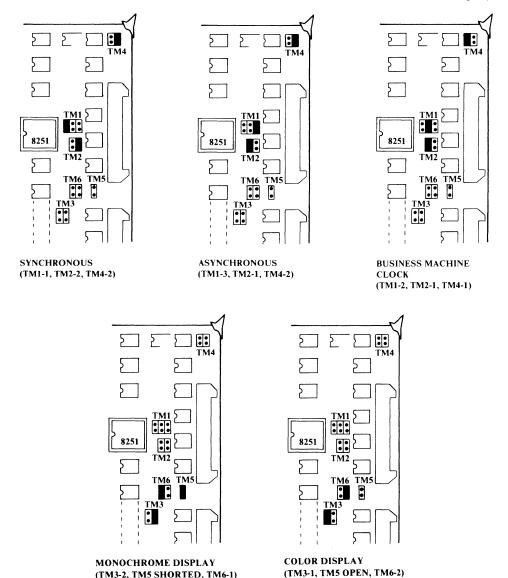

| 3-29   | Controller PCB Jumper Settings                                 | 3-65 |

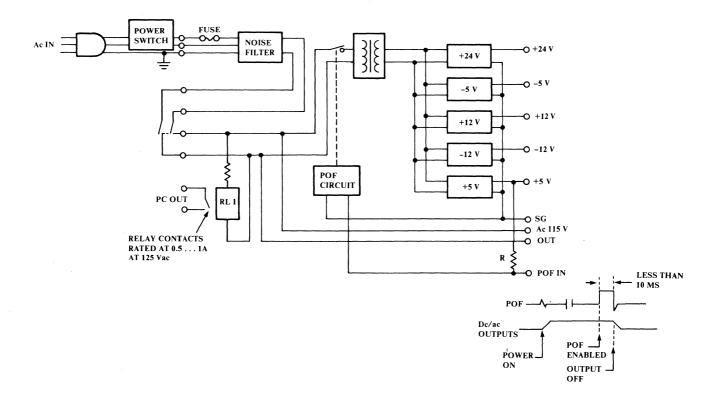

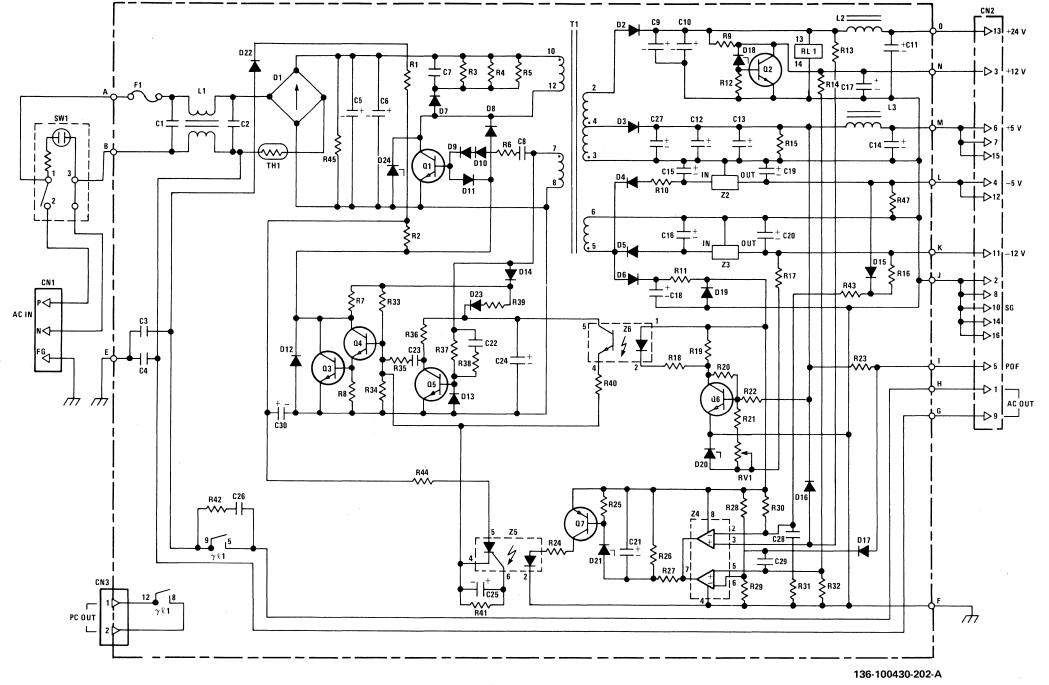

| 4-1    | System Power Supply Block Diagram                              | 4-2  |

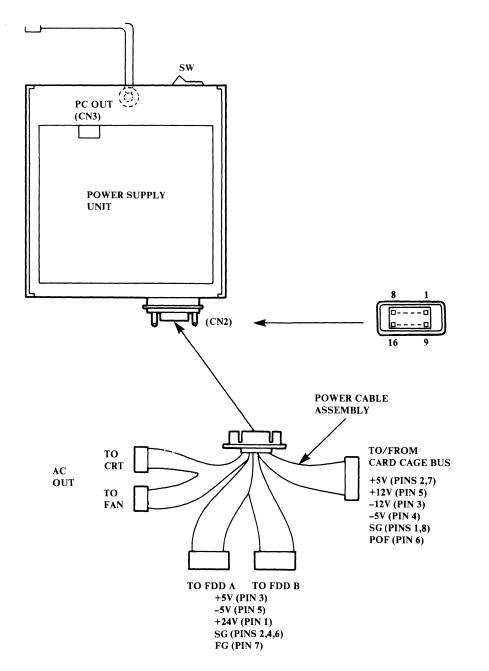

| 4-2    | Power Supply Interconnection Diagram                           |      |

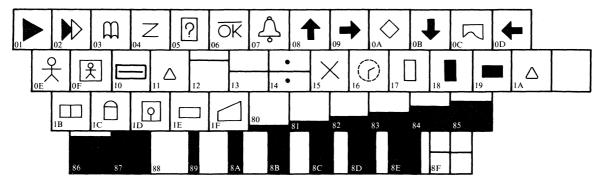

| D-1    | APC GRPH1 Characters                                           |      |

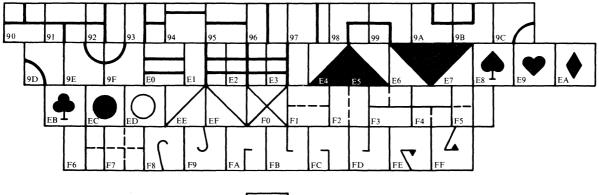

| D-2    | APC GRPH2 Characters                                           |      |

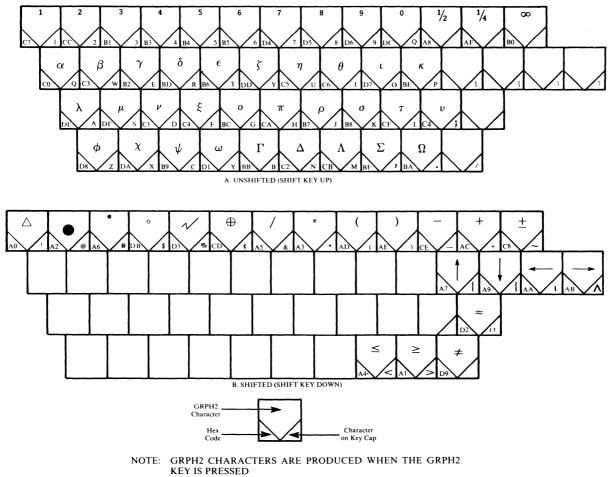

| D-3    | Keyboard Layout Showing Hex Codes                              |      |

|        | for Special Keys                                               | D-8  |

ix

### List of Tables

| Table | Title                                               | Page |

|-------|-----------------------------------------------------|------|

| 2-1   | Card Cage Socket Contact Assignments                | 2-4  |

| 2-2   | DMA Instructions                                    |      |

| 2-3   | Timer Commands                                      | 2-20 |

| 2-4   | Interrupt Lines                                     | 2-21 |

| 2-5   | Interrupt Control Commands Summary                  | 2-22 |

| 2-6   | Parallel Printer Connectors Pin Assignments         | 2-31 |

| 2-7   | Parallel Printer Interface Signals                  | 2-33 |

| 2-8   | Parallel Printer Controller Instruction             | 2-35 |

| 2-9   | Parallel Printer Controller Instruction Sequence    | 2-36 |

| 2-10  | Keyboard Scan Codes                                 | 2-39 |

| 2-11  | Keyboard Interface Lines                            | 2-42 |

| 2-12  | Clock/Calendar Instruction Format                   | 2-44 |

| 3-1   | Attribute Description for Character Attribute Code  | 3-6  |

| 3-2   | GDC I/O-Address and Bit Map                         |      |

| 3-3   | Contents of the GDC Status Register                 | 3-10 |

| 3-4   | GDC Symbols                                         | 3-11 |

| 3-5   | GDC Commands                                        | 3-14 |

| 3-6   | GDC Command Constants                               | 3-18 |

| 3-7   | Bit Description of the FDC Main Status Register     | 3-23 |

| 3-8   | FDC Symbols                                         | 3-24 |

| 3-9   | FDC Commands                                        | 3-27 |

| 3-10  | FDC Status Register 0                               | 3-33 |

| 3-11  | FDC Status Register 1                               | 3-34 |

| 3-12  | FDC Status Register 2                               | 3-35 |

| 3-13  | FDC Status Register 3                               | 3-36 |

| 3-14  | FDC Register I/O Addresses and Functions            | 3-36 |

| 3-15  | Output Signals                                      | 3-37 |

| 3-16  | Input Signals                                       | 3-38 |

| 3-17  | FDD Specifications                                  |      |

| 3-18  | Serial I/O Communications Controller Specifications | 3-44 |

| 3-19  | Serial I/O Commands                                 | 3-46 |

| 3-20  | Serial I/O Connector Pin Assignments                | 3-47 |

| 3-21  | Serial I/O Device Interface Connector               |      |

|       | Pin Descriptions                                    | 3-48 |

### List of Tables (cont'd)

| Table | Title                                                          | Page |

|-------|----------------------------------------------------------------|------|

| 3-22  | 8251A Instruction                                              | 3-50 |

| 3-23  | Communications Controller, Baud Rate Coding During             |      |

|       | Asynchronous Operation                                         | 3-53 |

| 3-24  | Communications Controller, Baud Rate Coding During             | 0 00 |

|       | Synchronous Operation                                          | 3-56 |

| 3-25  | Communications Controller, Baud Rate Coding During             |      |

|       | Operations with Business Machine Clocking                      | 3-58 |

| 3-26  | Sound Interface Pin Assignments                                | 3-61 |

| 3-27  | Sound Programming Read/Write Format                            | 3-62 |

| 3-28  | Sound Control Commands                                         | 3-62 |

| 3-29  | Sound Scale Commands                                           | 3-63 |

| 4-1   | Power Supply Pin Command Assignments                           | 4-4  |

| C-1   | Identification and Location of PAL Device                      |      |

| C-2   | PFB01B Inputs/Outputs                                          |      |

| C-3   | PFB02B Inputs/Outputs                                          |      |

| C-4   | PFC01 Inputs/Outputs                                           |      |

| C-5   | NMS02 Inputs/Outputs                                           |      |

| D-1   | Code Table                                                     |      |

| D-2   | ASCII Special Characters                                       | D-3  |

| D-3   | APC Special Characters                                         |      |

| D-4   | Quick Reference Guide for ASCII Special Character/APC Spe-     |      |

|       | cial Character Association                                     | D-5  |

| E-1   | I/O Port Address and Instructions for the DMA Controller       | E-2  |

| E-2   | I/O Port Addresses and Instructions for the Interrupt          |      |

|       | Controller                                                     | E-4  |

| E-3   | I/O Port Addresses and Instructions for the Internal Timer     | E-5  |

| E-4   | I/O Port Addresses and Instructions for the Serial I/O Commun- |      |

|       | ications Controller Number 1                                   | E-6  |

| E-5   | I/O Port Addresses and Instructions for the Serial I/O Commun- |      |

|       | ications Controller Number 2                                   | E-6  |

| E-6   | I/O Port Addresses and Instructions for the DMA Address        |      |

|       | Registers                                                      | E-7  |

| E-7   | I/O Port Addresses and Instructions for the CRT Controller     |      |

## List of Tables (cont'd)

| Table | Title                                                        | Page |

|-------|--------------------------------------------------------------|------|

| E-8   | I/O Port Addresses and Instructions for the Graphics Display |      |

|       | Controller                                                   | E-8  |

| E-9   | I/O Port Addresses and Instructions for the Keyboard         |      |

|       | Controller                                                   |      |

| E-10  | I/O Port Addresses and Instructions for the FDD Controller   | E-8  |

| E-11  | I/O Port Addresses and Instructions for the Clock and        |      |

|       | Calendar                                                     | E-9  |

| E-12  | I/O Port Address and Instruction for the BBM Enable          | E-9  |

| E-13  | I/O Port Addresses and Instructions for the APU              | E-9  |

| E-14  | I/O Port Address and Instruction for the Power Off Control   | E-9  |

| E-15  | I/O Port Addresses and Instructions for the Sound Control    | E-10 |

| E-16  | I/O Port Addresses and Instructions for the Timer            | E-10 |

| E-17  | I/O Port Addresses and Instructions for the ODA Controller   |      |

|       | Number 1                                                     | E-11 |

| E-18  | I/O Port Addresses and Instructions for the IDA Controller   | E-11 |

| E-19  | I/O Port Addresses and Instructions for the Communications   |      |

|       | Adapter                                                      | E-12 |

| E-20  | I/O Port Addresses and Instructions for the ASOP Controller  |      |

### Preface

This system reference guide provides hardware design and interface information for programmers, engineers, designers, and others who need to know how the APC is designed.

**Chapter 1, Hardware Overview**, familiarizes you with the Advanced Personal Computer and defines the principal components and devices.

**Chapter 2, Processor PCB**, includes descriptions and technical information for the devices contained on the Processor PCB along with programming considerations where appropriate.

Chapter 3, Controller PCB, includes information similar to that in Chapter 2 for the devices contained on the Controller PCB.

Chapter 4, Power Supply, contains detailed specifications for the system power source.

Appendices A to F include hardware reference information such as IC data sheets, logic diagrams, and data summaries.

### List of Abbreviations

| А                      | Ampere                     | ISR    | Read Inservice Register       |

|------------------------|----------------------------|--------|-------------------------------|

| ALE                    | Address Latch Enable       | KB     | Kilobyte                      |

| APC                    | Advanced Personal          | LED    | Light Emitting Diode          |

| me                     | Computer                   | LSB    | Least Significant Bit         |

| APU                    | Arithmetic Processing Unit | LSI    | Large-Scale Integration       |

| AT                     | Abnormal Termination       | MB     | Megabyte                      |

| BBM                    | Battery-Backed Memory      | MFM    | Modified Frequency            |

| CMOS                   | Complementary Metal        |        | Modulation                    |

| emob                   | Oxide Semiconductor        | MHz    | Megahertz                     |

| CPU                    | Central Processing Unit    | MOS    | Metal Oxide                   |

| CRT                    | Cathode Ray Tube           | mos    | Semiconductor                 |

| CS                     | Code Segment               | ms     | Millisecond                   |

| DCH                    | Device Control             | MSB    | Most Significant Bit          |

| DIP                    | Dual In-line Package       | ns     | Nanosecond                    |

| DMA                    | Direct Memory Access       | NT     | Normal Termination            |

| DMC                    | Direct Memory Access       | OCW    | Operational Command           |

| 21110                  | Cycle                      |        | Word                          |

| DS                     | Data Segment               | ODA    | Output Device Adapter         |

| EPROM                  | Erasable Programmable      | PAL    | Programmable Array            |

|                        | Read-Only Memory           |        | Logic                         |

| ES                     | Extra Segment              | PCB    | Printed Circuit Board         |

| FDC                    | Flexible Disk Drive        | POF    | Power Off Control             |

|                        | Controller                 | RAM    | Random Access Memory          |

| FDD                    | Flexible Disk Drive        | ROM    | Read-Only Memory              |

| FIFO                   | First-In First-Out         | rpm    | <b>Revolutions Per Minute</b> |

| $\mathbf{F}\mathbf{M}$ | Frequency Modulation       | SS     | Stack Segment                 |

| GDC                    | Graphic Display Controller | SW     | Switch                        |

| HEX                    | Hexadecimal                | TTL    | Transistor/Transistor         |

| Hz                     | Hertz                      | LICADT | Logic                         |

| IC                     | Integrated Circuit,        | USART  | Universal Synchronous/        |

|                        | Interrupt Code, Invalid    |        | Asynchronous Receiver/        |

|                        | Command                    | * 7    | Transmitter                   |

| ICW                    | Initialization Command     | V      | Volt                          |

| T/O                    | Word                       | VFO    | Variable Frequency            |

| I/O                    | Input/Output               | 117    | Oscillator                    |

| IP                     | Instruction Pointer        | W      | Watt                          |

| IRR                    | Read Interrupt Register    | μs     | Microsecond                   |

# Chapter 1 Hardware Overview

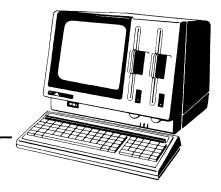

The NEC Advanced Personal Computer (APC) has two basic components: a Main Unit and a Keyboard. The Keyboard, which cable-connects to the Main Unit, is common to all APC models. The Main Unit, which houses the Central Processing Unit (CPU), memory, visual display, sound output, and peripheral controllers, is available in three models: (1) a Monochrome Cathode Ray Tube (CRT) Display with one 8-inch Flexible Disk Drive (FDD), (2) a Monochrome CRT Display with two 8-inch FDDs, and (3) a Color CRT Display with two 8-inch FDDs. Several options and accessories are available to enhance performance or to adapt the APC for special applications.

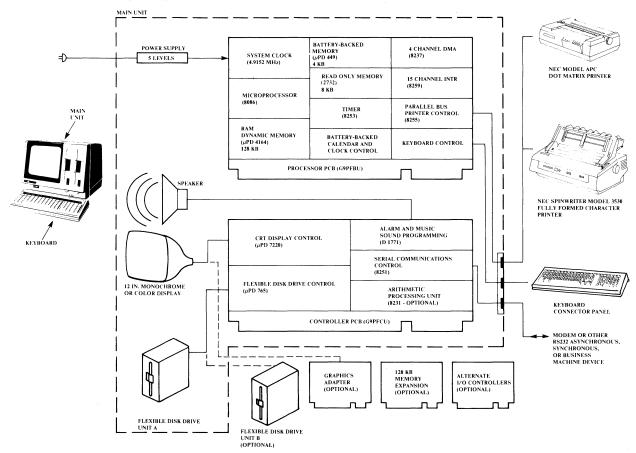

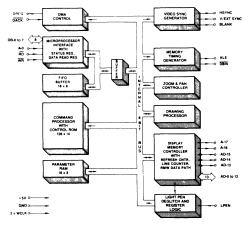

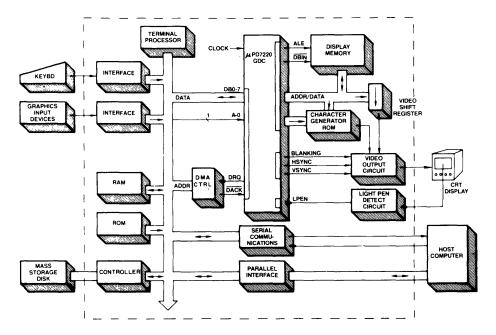

Figure 1-1 is a block diagram of the APC. The Main Unit, the heart of the APC, has a CRT Display, one or two 8-inch FDDs, an ON/OFF switch, and several controls associated with the CRT Display. Three Input/Output (I/O) cable connectors are available at the rear of the cabinet.

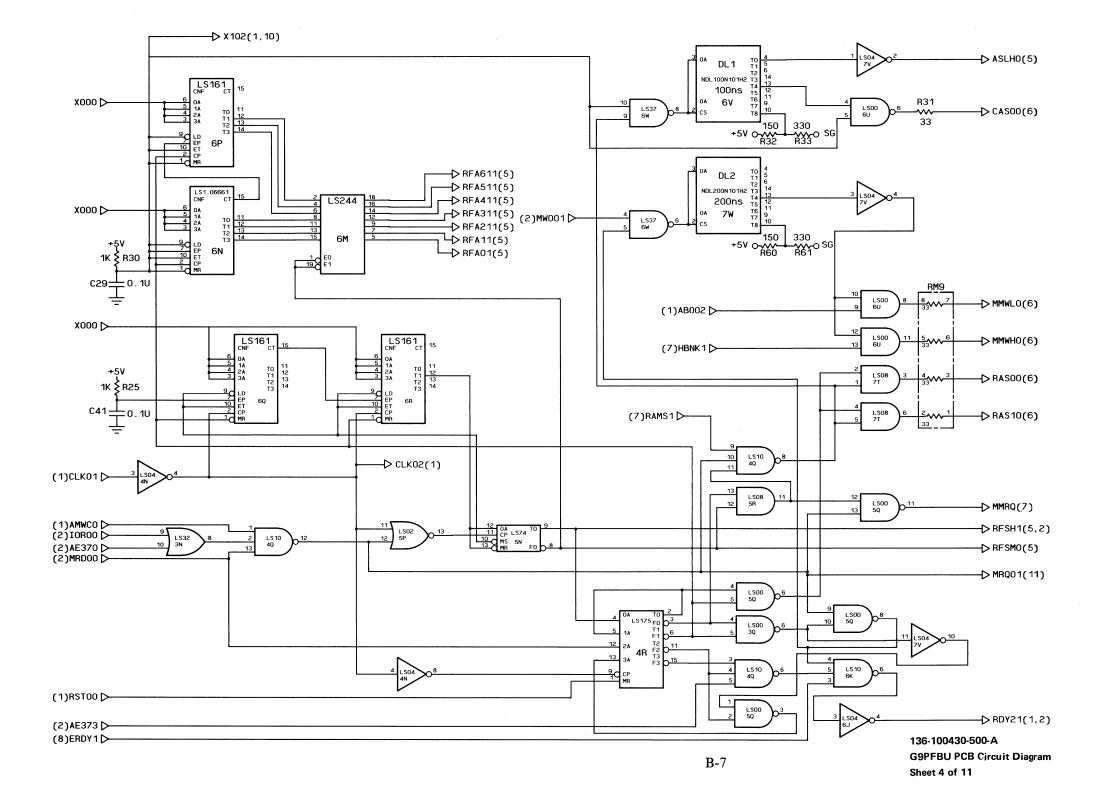

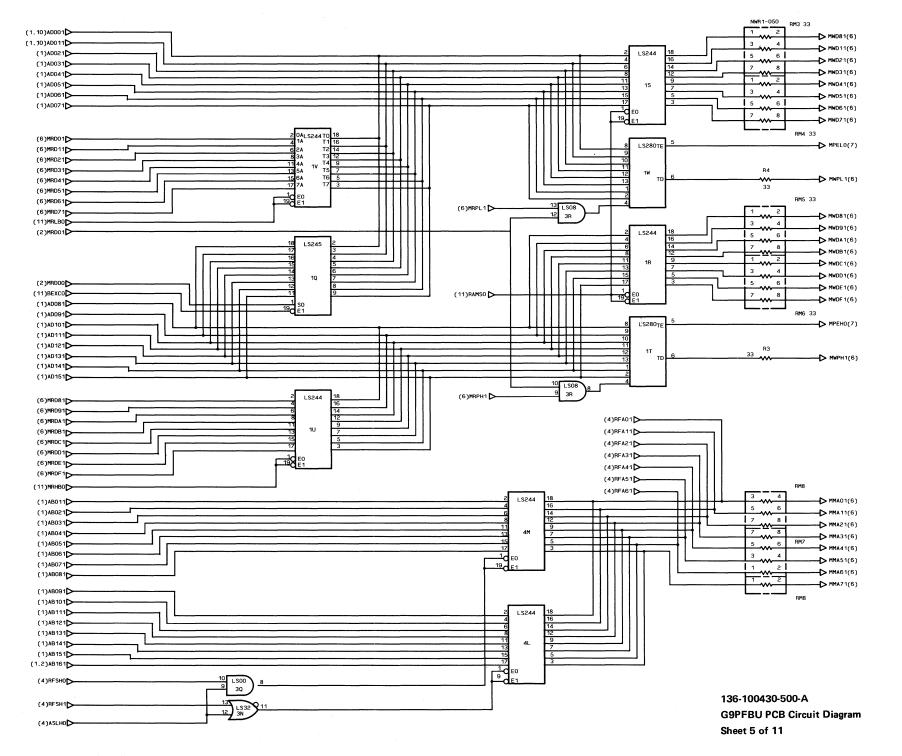

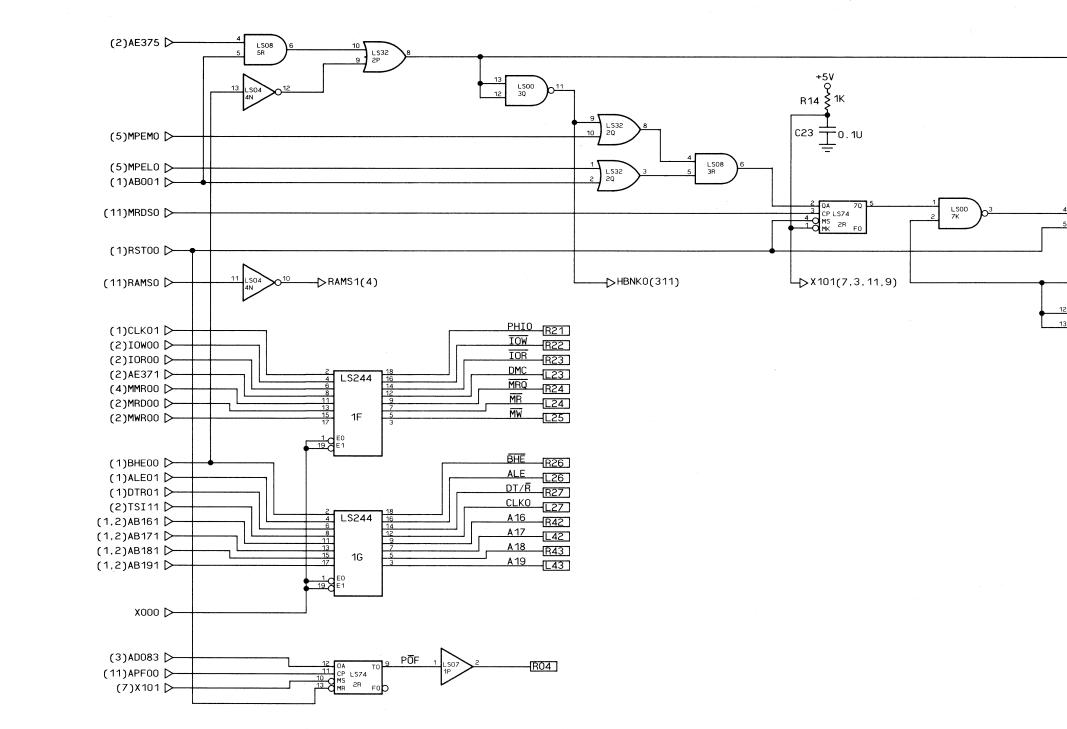

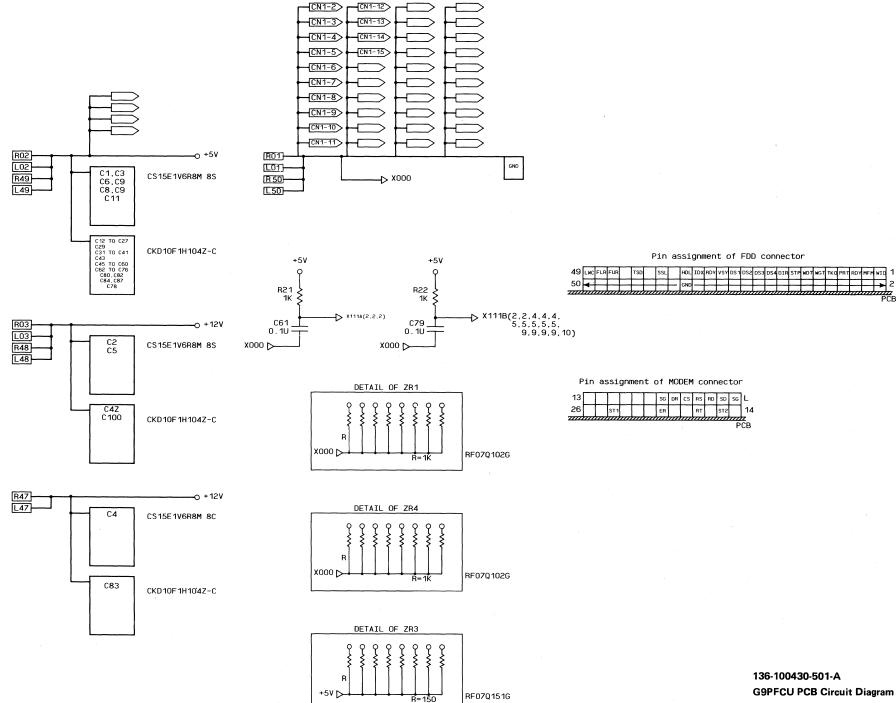

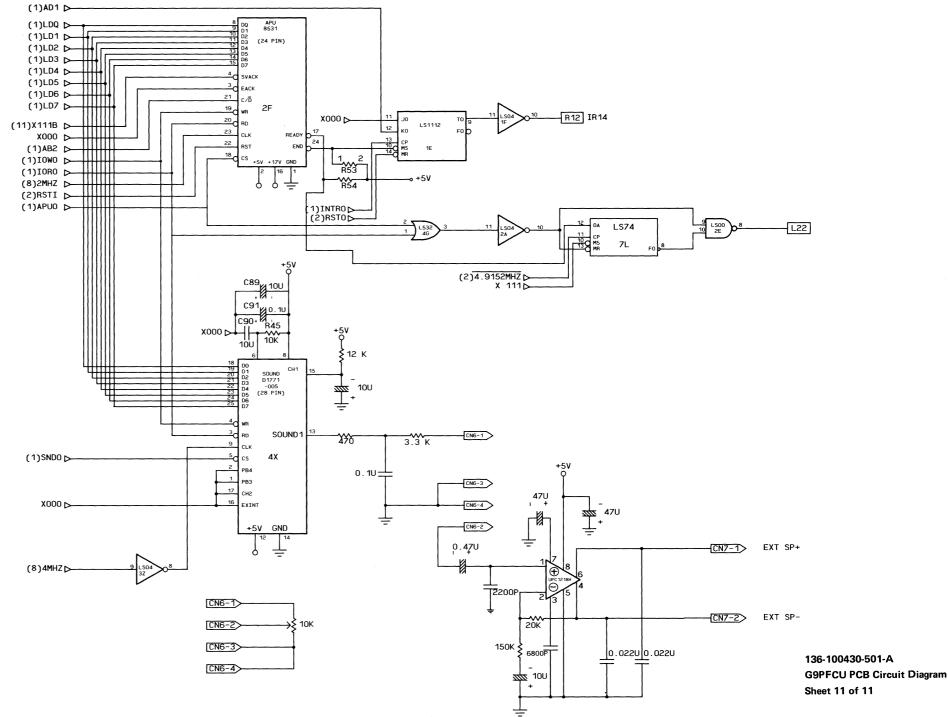

The CPU, memory, and basic control logic are contained in the Main Unit on two quad-layered Printed Circuit Boards (PCB): a Processor PCB (G9PFBU) and a Controller PCB (G9PFCU). These PCBs plug into a mother board interface bus that has the space and power for up to three additional (optional) PCBs.

The Processor PCB contains as standard equipment:

- A 16-bit 8086 Microprocessor

- An 8288 Bus Controller with 20-bits of addressing, making one megabyte (MB) of memory accessible

- 128 kilobytes (KB) (standard) of Random Access Memory (RAM)

- 8 KB of Read-Only Memory (ROM)

- 4 KB of CMOS Battery-Backed Memory, which remains refreshed for at least two years without ac power

- A 4-channel Direct Memory Access (DMA) Controller

Hardware Overview

### Figure 1-1 System Block Diagram

- A 15-channel Interrupt System

- Printer and Keyboard Controllers

- Calendar-and-Clock Controller, which keeps track of the month, date, day of week, hour, minute, and second, and runs on battery power when ac power is off, thus preserving the time/date setting.

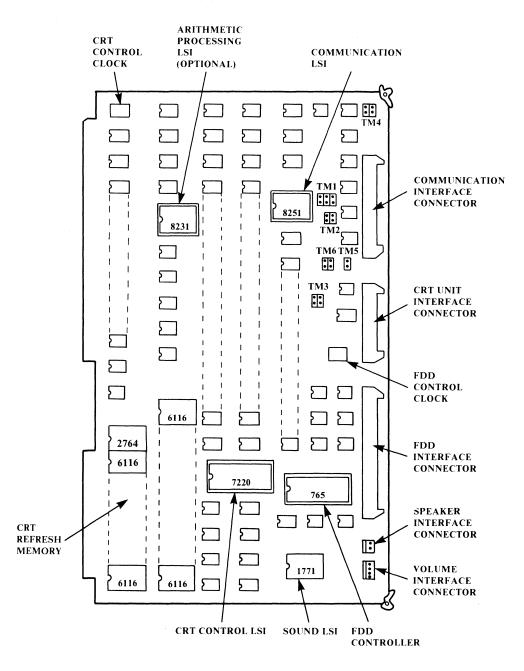

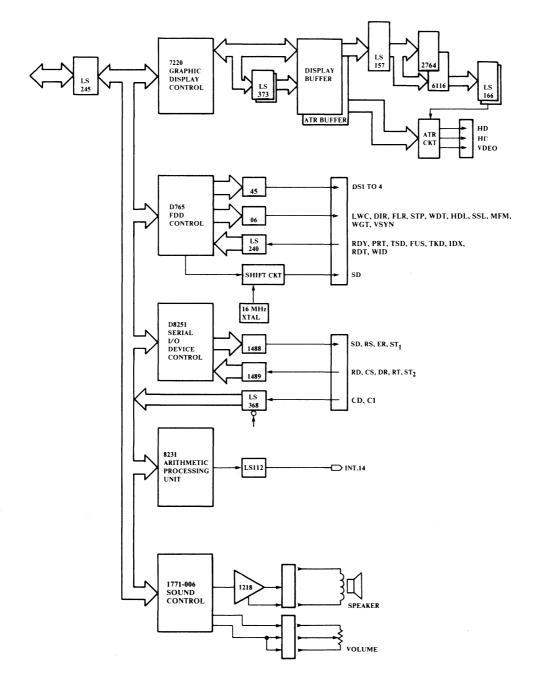

The Controller PCB contains as standard equipment:

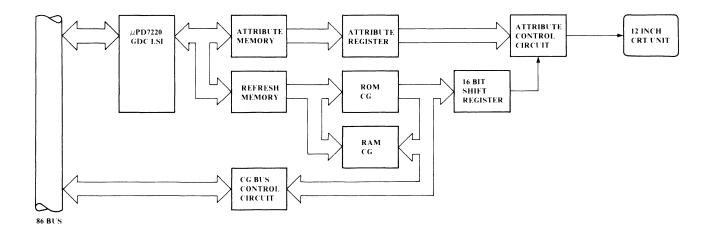

• CRT Display Control, which can generate 250 predefined characters and allows you to create and store on disk any number of sets of 256 other special characters

- Flexible Disk Drive Controller (FDC) to coordinate the reading of and the writing to one or two 8-inch flexible disks

- Alarm and Music Sound Programming System, which enables you to select alarm tones and generate music across two octaves, with selected tempos, volumes, and tone characteristics

- Serial Communications Adapter, which is a Universal Synchronous/ Asynchronous Receiver/Transmitter (USART), enabling the APC to communicate with almost any type of communications device.

The APC power supply is a 100-watt, 5-voltage-level switching regulator. It furnishes dc levels to all components — except to the CRT which has its own power unit — and has sufficient reserve capacity to handle future expansion. The power supply has a software-controlled Power-Off control (POF) circuit that enables you to turn off the system locally or remotely.

One or two 8-inch FDDs are integrated into the Main Unit. The FDC (NEC  $\mu$ PD765) can read from or write to dual-sided double-density disks (which store up to 1 MB of unformatted data) or single-sided single-density flexible disks (which can store about 260 KB of unformatted data). The disk drive is a compact, high-performance, energy-efficient design featuring direct drive by a dc motor. Head loading and positioning is microprocessor-controlled for greater accuracy and minimum wear and damage to the media surface. Variable Frequency Oscillation (VFO) is employed to improve data transfer.

The APC comes equipped with a 12-inch (diagonal) green-phosphor monochrome CRT or a 12-inch 8-color CRT. Either unit has a self-contained power supply. Both have a reduced glare surface and a high resolution screen. Standard alphanumeric characters are composed from an 8-by-19 dot matrix, allowing a display of 25 lines of 80 characters. Special symbols can be designed by the user with a dot matrix of up to 8-by-16.

The CRT Display has considerable versatility and provides you with capabilities for scrolling, partitioning (and scrolling within selected partitions), overbar, vertical bar, underscore, highlighting, blinking, and reverse video. The Color CRT Display has all these attributes plus a choice from eight colors.

With the special-character generator, you can design up to 256 characters dot-bydot, which can be saved on disk as one or more special character sets. Using a dot matrix printer, these special characters can be printed and displayed, making the APC especially adaptable to users who use non-Roman alphabets or scientific symbols. The APC also offers an optional Graphics Adapter based on the NEC  $\mu$ PD 7220. This self-contained single PCB plugs into the Main Unit and simplifies graphics applications, such as area shading, simulated movement, and solid or dashed lines, either straight or curved. By employing the Graphics Adapter with selected software packages, you can generate graphs, bar graphs, and three-dimensional pictures.

Also optional are two NEC printers. The Dot Matrix Printer provides rapid, high quality printing at a low cost. It prints in both directions at 100 characters per second on a 80-to-136-character column width. It prints special and graphic characters as well as standard alphanumeric characters.

The other printer is the NEC Model 3530 Spinwriter<sup>®</sup>, which produces high quality fully-formed characters. This printer features interchangeable print elements that contain up to 128 characters and are offered in several dozen type styles and symbol sets. It prints 35 characters per second at 10, 12, and 15 characters per inch or proportional spacing. It also prints bidirectionally and offers word processor functions, such as automatic underlining, shadowing, bold face printing, as well as several paper-handling accessories.

The standard APC comes equipped with 128 KB of RAM, which resides on the Processor PCB. With the optional memory-expansion kits, RAM can be expanded to 640 KB.

The asynchronous, synchronous serial I/O communications adapter is a standard feature of the APC. The interface is supported by the NEC 8251A Communications Controller, a USART, that is used as a peripheral and is programmed by the microprocessor to communicate using virtually any serial or parallel data-transmission technique, at programmable baud rates. For communications interface requirements beyond this standard controller, NEC offers special-purpose I/O Controllers on plug-in boards.

The Keyboard is not housed in the Main Unit; it attaches to the rear of the Main Unit with a single five-foot, coiled cable. The Keyboard has 109 keys, including a numeric keypad and 22 programmable function keys that facilitate data and word processing. Each function key has two shift-modes, making available 44 userdefinable functions with one or two keystrokes.

### NOTE

Only 32 of the 44 user-definable functions can be character strings.

1-4

# Chapter 2 Processor PCB

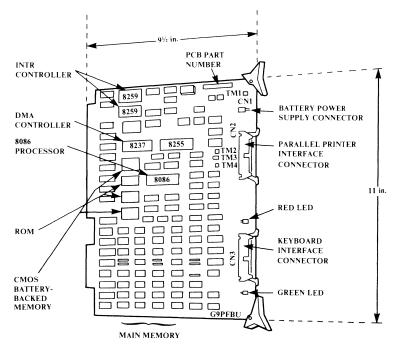

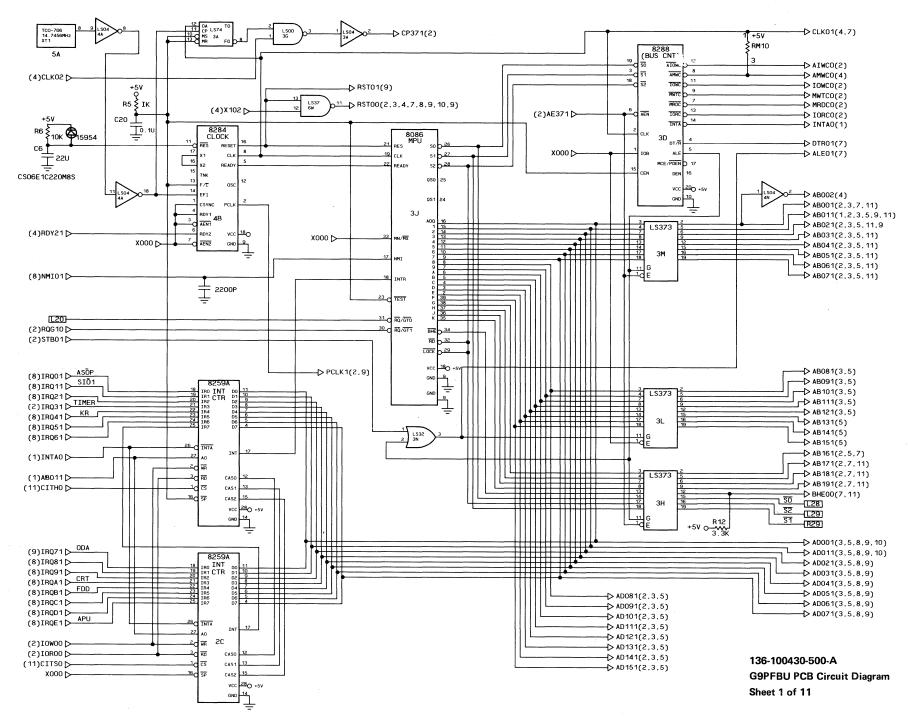

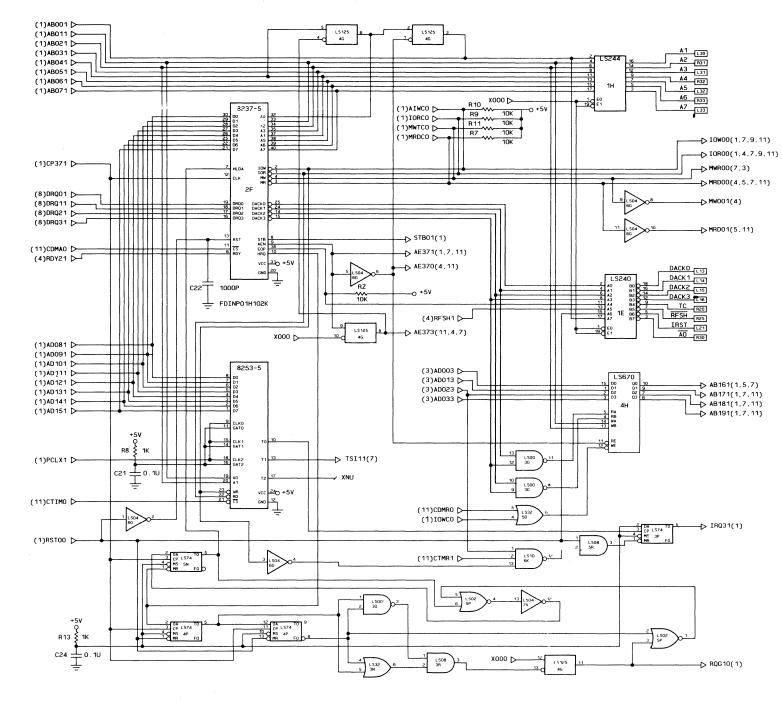

The Processor PCB (G9PFBU) fits vertically in the Main Unit and is 11 inches long by  $9\frac{1}{2}$  inches high (see Figure 2-1). It is composed of four sandwiched layers, including the signal, ground, and dc-power internal planes. It plugs into the third slot of the card cage with a 100-contact edge connector on the bottom of the PCB.

### Figure 2-1 Processor PCB

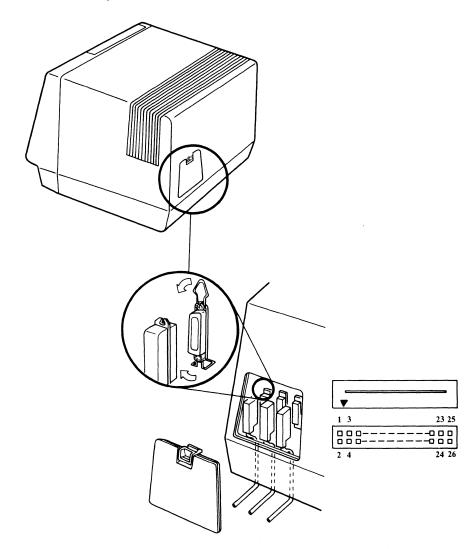

As shown in Figure 2-1, three cable connectors are on the Processor PCB; two are 26-pin connectors and the third is a 2-pin header connector. The Keyboard interface uses one of the 26-pin connectors, while the other connector provides a parallel printer (or other such device) interface. Battery power is supplied by the 2-pin connector.

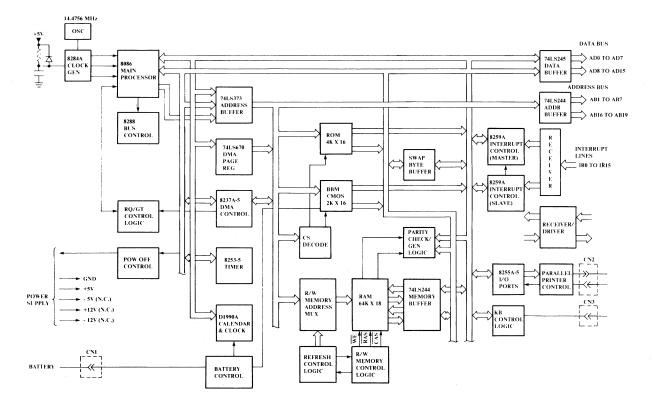

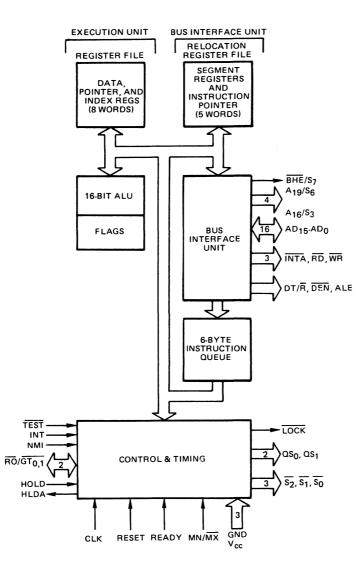

The principal functional components and their interrelationships are shown on the block diagram of the Processor PCB (see Figure 2-2). The major elements of the PCB consist of the following functional areas:

- An NEC  $\mu$ PD8086 microprocessor, which is

- 1) Fully compatible with the Intel 8086 microprocessor

- 2) Capable of addressing one MB of memory

- 3) Driven by an NEC  $\mu$ PD8284 clock generator at 4.9152 MHz

- A 20-bit bidirectional address bus, 16 bits of which serve also as the data bus, and related buffers, controls, and ports

- A DMA controller to permit high speed data transmission between input/ output devices without intervention of the microprocessor

Figure 2-2 Processor PCB Block Diagram

- A 15-channel interrupt controller to govern access to the microprocessor and data bus

- 8 KB (4K x 16 bits) of ROM, which carry out self-testing and flexible-disk bootstrap loading.

- 128 KB of RAM organized into sixteen 64K x 1 dynamic-memory chips, plus two more for parity check

- 4 KB (2K x 16 bits) of CMOS Battery-Backed Memory (BBM)

- Keyboard control logic, which controls and conveys data from the Keyboard to the data bus

- Parallel printer control, which interfaces with a connector on the APC rear panel for connection of a printer or similar device

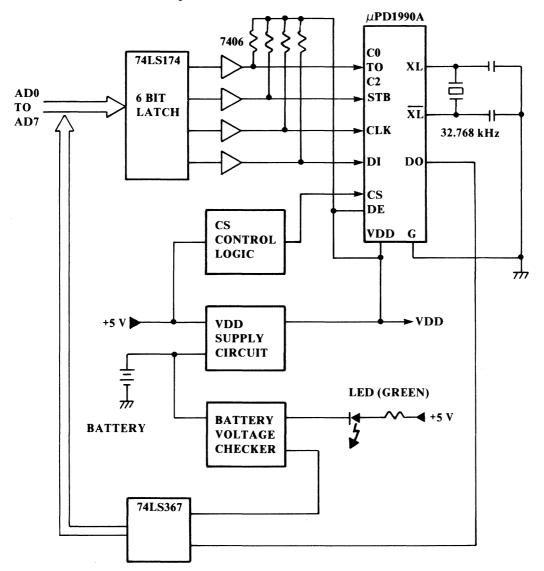

- Calendar and clock generator, supported by NEC  $\mu$ PD1990AC, which is battery-protected and generates day, month, day of the week, hour, minute, and second information.

### 2.1 MOTHER BOARD/CARD CAGE INTERFACE

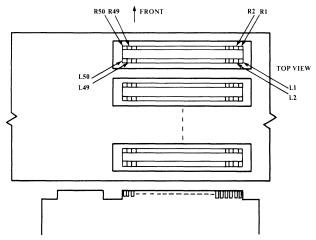

The Mother Board contains five card-edge socket connectors, each having 100 contacts, 50 on a side (see Figure 2-3). All contacts are connected as a bus to each PCB socket.

Figure 2-3 Mother Board/Card Cage Interface

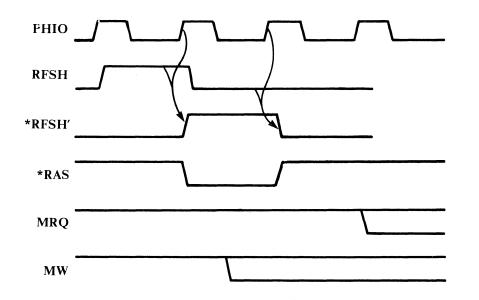

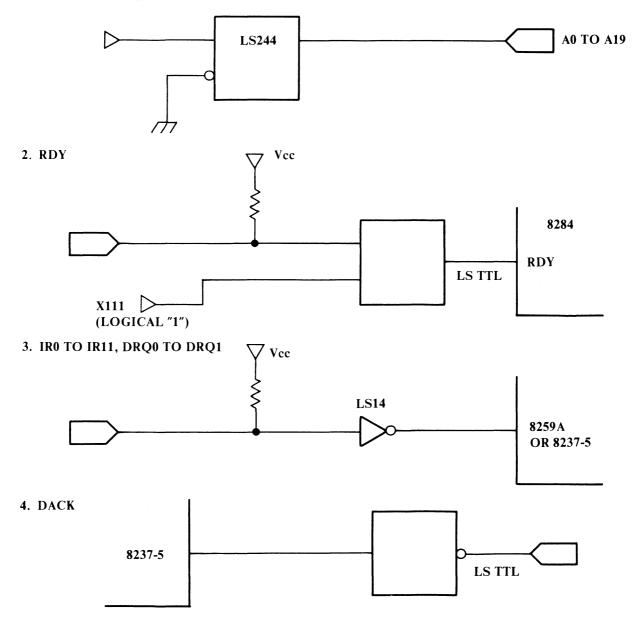

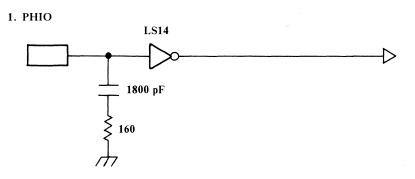

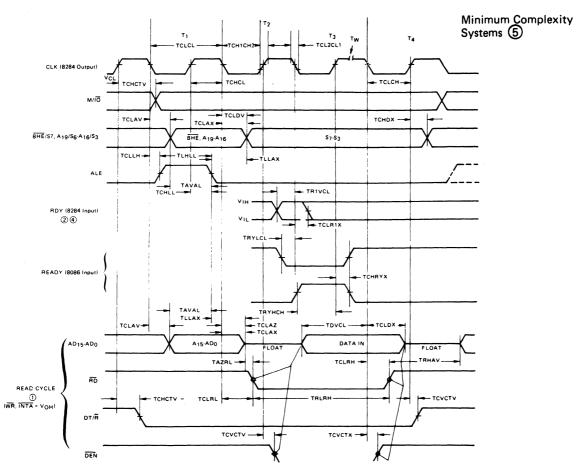

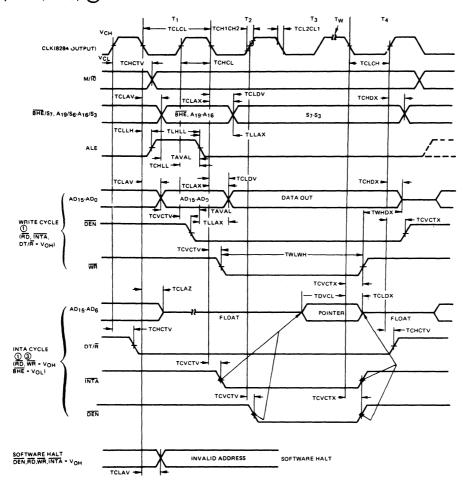

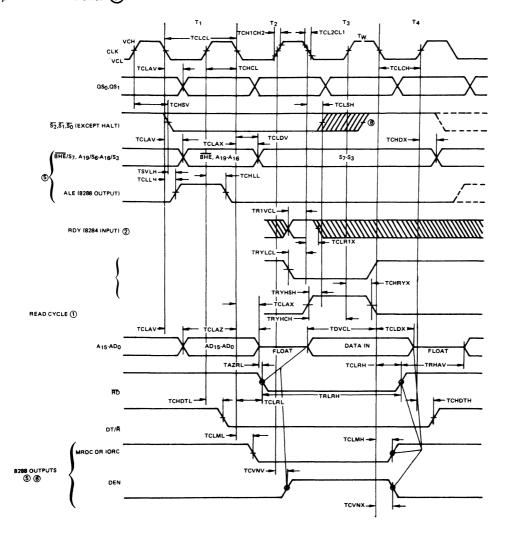

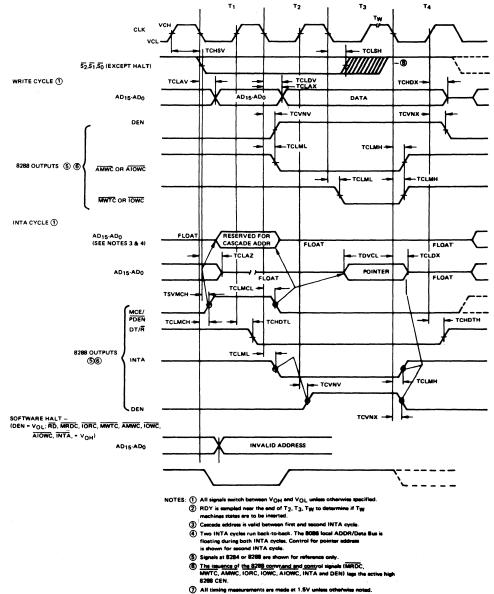

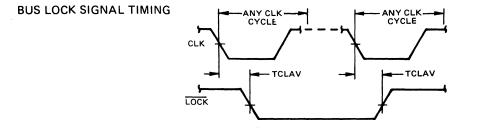

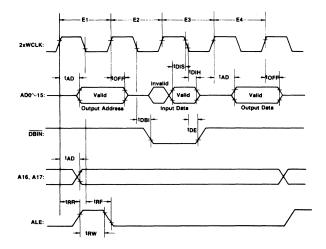

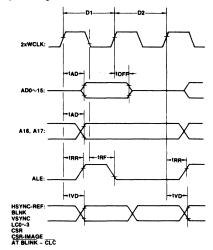

Table 2-1 lists the contact assignments for each socket. All signals on these contacts are Transistor/Transistor Logic (TTL) compatible. Time relationships between various contacts in the card cage bus are shown in Figures 2-4 through 2-7. I/O equivalent circuits for the affected contacts and devices are shown in Figures 2-8 and 2-9.

| PIN<br>NUMBER                                       | NAME              | READ/<br>WRITE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------------------------|-------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R1, R50<br>L1, L50                                  | GND               |                | Signal Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| R2, R49<br>L2, L49                                  | +5 V              |                | +5 Vdc Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| R3, R48<br>L3, L48                                  | +12 V             |                | +12 V Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| R47, L47                                            | -12 V             |                | -12 V Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| R46, L46                                            | -5 V              |                | -5 V Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| R4                                                  | POF               | W              | Power Off Control. Goes high to command power supply off.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| R5, L5<br>R6, L7<br>R8<br>R9, L9<br>R10, L10<br>R12 | IR0 to<br>IR14    | R              | Interrupt Request 0 Through 14. These 15<br>lines carry interrupt requests to the proces-<br>sor. When an I/O device requires processor<br>intervention, it signals the $\mu$ PD8259A inter-<br>rupt controller, which activates one of the 15<br>interrupt lines to the processor; the interrupt-<br>request signal is maintained until acknow-<br>ledgement from the processor. IR0 has the<br>highest priority and IR15 the lowest priority.<br>These lines are active Low. |

| R13, R14<br>R15, R16                                | DRQ0 to<br>DRQ3   | R              | DMA Request 0 Through 3. These lines trans-<br>mit requests by I/O devices for DMA service.<br>These signals remain active until DMA<br>acknowledgement is active on a correspond-<br>ing DACK line. Channel assignments are $0 =$<br>CRT, $1 =$ FDD, $2 =$ Graphics, $3 =$ AUX.                                                                                                                                                                                               |

| L13, L14<br>L15, L16                                | DACK0<br>to DACK3 | W              | DMA-Request Acknowledgement 0 Through<br>3. These lines signify that the DMA controller<br>has acknowledged the DMA request on a<br>corresponding DRQ line. DACK lines are<br>active High.                                                                                                                                                                                                                                                                                     |

Table 2-1

Card Cage Socket Contact Assignments

| Table 2-1 | Card Cage | Socket Contact | Assignments | (cont'd) |

|-----------|-----------|----------------|-------------|----------|

|-----------|-----------|----------------|-------------|----------|

| PIN<br>NUMBER | NAME | READ/<br>WRITE | DESCRIPTION                                                                                                                                                                                                                                                                     |

|---------------|------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R20           | ТС   | W              | <i>Terminal Count.</i> This line carries to the I/O device a one-clock-duration pulse indicating that the terminal count for the DMA channel has been reached. This pulse is active High.                                                                                       |

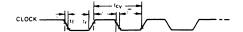

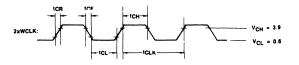

| R21           | РНІО | W              | System Clock. The pulse of the clock is transmitted on this line; the clock period is about 200 nsec (4.9152 MHz) and its duty cycle is 33 percent.                                                                                                                             |

| L21           | IRST | W              | <i>Initial Reset.</i> When this line goes High, every device in the system is initialized. This line is activated at power on.                                                                                                                                                  |

| R22           | IOW  | W              | <i>I/O Write.</i> A Low on this line instructs the I/O device to receive data from the data bus. Either the DMA controller or processor can activate the line.                                                                                                                  |

| L22           | RDY  | R              | <i>Ready.</i> A High on this line indicates that data<br>has been received by an I/O device or<br>memory, or that preparation of data is com-<br>plete. It is pulled Low by a device to lengthen<br>I/O memory cycles, allowing slower devices<br>to adjust to the I/O channel. |

|               |      |                | NOTE                                                                                                                                                                                                                                                                            |

|               |      |                | There is an <i>Interval-Ready</i> signal<br>within the G9PFBU PCB; it acti-<br>vates when memory access from<br>the processor or DMA controller<br>clashes with the memory-refresh<br>cycle.                                                                                    |

| Table 2-1 | <b>Card Cage Socket</b> | Contact Assignments (cont'd) |

|-----------|-------------------------|------------------------------|

|           |                         |                              |

| PIN<br>NUMBER | NAME | READ/<br>WRITE | DESCRIPTION                                                                                                                                                                                 |

|---------------|------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R23           | IOR  | W              | <i>I/O Read.</i> A Low on this line instructs the I/O device to transmit its data to the data bus. This instruction can come from either the DMA controller or the processor.               |

| L23           | DMC  | W              | <i>DMA Cycle.</i> A High on this line indicates the processor has been inhibited, thus giving system-bus control to the DMA controller.                                                     |

| R24           | MRQ  | W              | <i>Memory Request.</i> When this line is Low, it indicates the memory cycle is in operation. The line is inactive (High) during memory-refresh cycles.                                      |

| L24           | MR   | W              | <i>Memory Read.</i> This line instructs the additional memory to transmit its data onto the data bus. Either the processor or DMA controller can activate this signal, which is active Low. |

| R25           | RFSH | W              | <i>Memory Refresh.</i> When this line is Low, dynamic memory is refreshed.                                                                                                                  |

| L25           | MW   | w              | <i>Memory Write.</i> When Low, this line instructs the selected memory to receive the data on the data bus. It is activated by either the DMA controller or processor.                      |

| R26           | вне  | W              | Bus High Enable. When Low, this line indi-<br>cates that the most significant half of the data<br>line is ready to be read. This line is not used<br>during DMA cycles.                     |

| L26           | ALE  | w              | Address Latch Enable. When activated by the processor or DMA control, the signal on this line latches the address on the bus.                                                               |

| PIN<br>NUMBER                                                                                | NAME           | READ/<br>WRITE | DESCRIPTION                                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------|----------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R27                                                                                          | DT/R           | W              | Data Transmit or Receive. This line indicates<br>data transfer direction. When High, direction<br>is processor to I/O or memory; when Low,<br>direction is I/O or memory to processor.             |

| L27                                                                                          | CLK0           | W              | <i>Communication Clock.</i> This line, which is<br>energized by the 8253-5 Programmable Inter-<br>val Timer, conveys a synchronizing variable<br>frequency clock to the communications<br>control. |

| R30                                                                                          | A0             | W              | Address Bit 0. When this line is active (High), the memory or I/O device associated with the least significant half of the data is enabled to read or transmit its data.                           |

| R31, L30<br>R32, L31<br>R33, L32<br>L33                                                      | Al to A7       | W              | Address Bits 1 Through 7. These seven lines address the memory or I/O device. These signals are latched.                                                                                           |

| R34, L34<br>R35, L35<br>R36, L36<br>R37, L37<br>R38, L38<br>R39, L39<br>R40, L40<br>R41, L41 | AD0 to<br>AD15 | W              | Address and Data Lines 0 Through 15. These<br>16 lines are bidirectional and time multi-<br>plexed to convey address or data to the<br>address or data buses.                                      |

| R42, L42<br>R43, L43                                                                         | A16 to<br>A19  | W              | Address Lines 16 Through 19. These four lines,<br>used for addressing the memory, increase the<br>number of address lines to twenty, allowing<br>access to one megabyte of memory.                 |

Table 2-1

Card Cage Socket Contact Assignments (cont'd)

**Processor PCB**

2-8

Figure 2-5 DMA Timing

### NOTE: THE \*RFSH' AND \*RAS SIGNALS ARE GENERATED IN THE MEMORY FROM THE RFSH SIGNAL.

Figure 2-7 RFSH Signal Timing

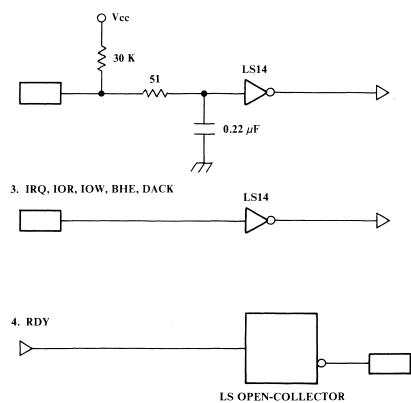

#### 1. A0 TO A19, IRQ, IOR, IOW, BHE, IRST, PHIO

Figure 2-8 Processor Interface Circuits

Processor PCB

2. IRST

5. IR0 TO IR11, DRQ0 TO DRQ1 (LS TTL)

Figure 2-9 Device Interface Circuits

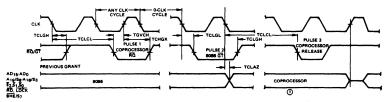

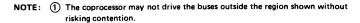

### 2.2 MICROPROCESSOR

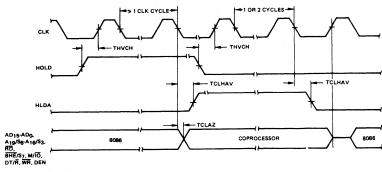

The functional heart of the Processor PCB is the NEC  $\mu$ PD8086 Microprocessor, an NEC-manufactured device physically and logically interchangeable with the Intel 8086.

The 8086 is a high-performance 16-bit CPU packaged in a single 40-pin Dual In-line Package (DIP) chip. It has a direct addressing capability to 1 MB of memory on a 20-bit address bus, of which bits 0 through 15 are time-multiplexed for the 16-bit data bus. It is driven at a 4.9152 MHz clock rate and is used in maximum operating mode (using an external 8288 bus controller).

In general, the 8086 processes a program by repeated cycling through four clock steps, T1 through T4:

- T1 fetches an instruction from memory

- T2 reads in any required operand

- T3 executes the instruction

- T4 writes any required result.

In the 8086, two separate processors perform these steps independently and simultaneously: (1) an execution unit that executes instructions, and (2) a bus interface unit that fetches instructions and queues them up for use by the execution unit.

All registers and data paths within the execution unit are 16 bits wide for fast operation. A 16-bit arithmetic-logic unit manages the general registers and instruction operands and maintains status and control flags. The execution unit is a strictly internal device and has no connection to the outside world. All instructions and memory access operations are accomplished by the bus interface unit.

The bus interface unit functions as a good secretary by anticipating the needs of the execution unit and lining up sequential instructions for ready access. These instructions are stored in an internal queue RAM with a capacity of six bytes. The bus interface unit is programmed to keep this RAM filled, fetching two bytes at a time from even addresses and one byte at a time from odd addresses. When the execution unit requests a memory or I/O read or write, the bus interface unit discontinues instruction fetching and responds to the execution unit request. If the instruction executed calls for control transfer to another location, the bus interface unit empties the queue RAM, fetches the instruction from the new location, and feeds it directly to the execution unit. Then the bus interface unit proceeds to refill the queue RAM from sequential instructions from the new location.

The 1,048,576 bytes of available memory space are addressed as if divided into logical segments of up to 64 KB each. The 8086 has direct access to four segments at a time, each of which has a base address carried in one of four segment registers: the Code Segment (CS), Data Segment (DS), Stack Segment (SS), and Extra Segment (ES). The Instruction Pointer (IP) register contains the present offset distance in bytes, which completes the logical address of the next address to be processed. The result of this memory organization is that the 20-bit physical memory address can be defined by a logical address consisting of two 16-bit bytes, the first specifying the base address of the selected segment and the second specifying the relative address within that segment, counting from the base address. To convert a logical address to a physical address, first shift the base address byte 4 bits to the left by multiplying it by sixteen, then add the result to the offset byte.

#### **2.3 DIRECT MEMORY ACCESS**

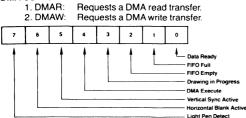

Because it bypasses processor intervention, DMA provides a much faster way of moving data between I/O devices and memory. Supported by the NEC LSI 8237-5 DMA Controller, DMA employs 16 address lines and 4 bits of page addressing, thus enabling it to address one megabyte of memory. Although the DMA is a synchronous device, it can interface with low-speed memory or I/O devices by using the external Ready line.

The four DMA channels are assigned as follows:

| Channel 0 | CRT                                    |

|-----------|----------------------------------------|

| Channel 1 | FDD                                    |

| Channel 2 | Reserved for graphic operations option |

| Channel 3 | Future.                                |

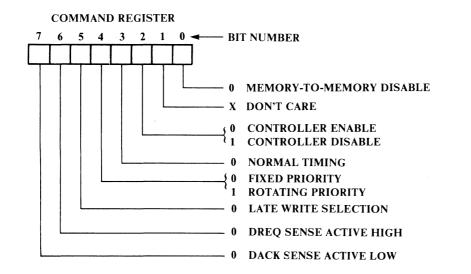

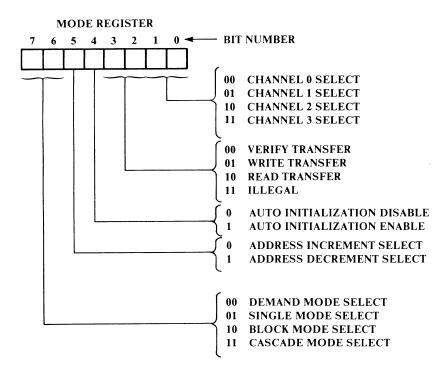

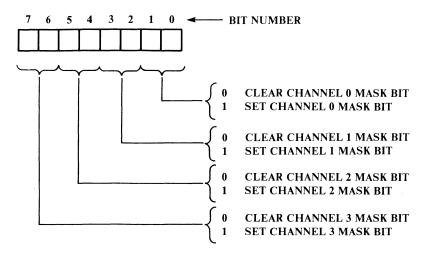

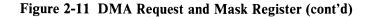

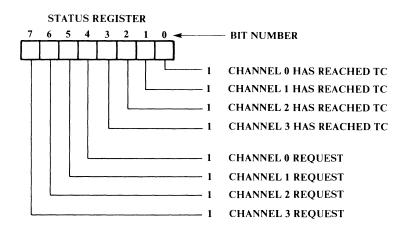

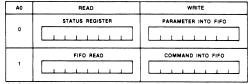

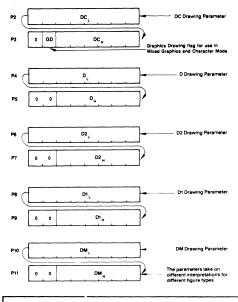

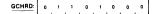

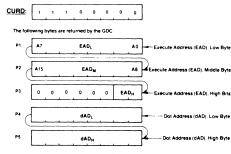

See Table 2-2 for a list of instructions and I/O addresses. Figures 2-10, 2-11, and 2-12 show the DMA registers.

| INSTRUCTION   | READ/<br>WRITE | I/O<br>Address | 7           | 6           | DA<br>5 | ГА В<br>4 | SUS<br>3    | 2           | 1           | 0           |

|---------------|----------------|----------------|-------------|-------------|---------|-----------|-------------|-------------|-------------|-------------|

| Write Command | W              | 09             | K<br>S      | D<br>S      |         |           | T<br>M      |             | A<br>H      | M<br>M      |

| Write Mode    | W              | 1B             | M<br>S<br>1 | M<br>S<br>0 | I<br>D  | A<br>T    | T<br>R<br>1 | T<br>R<br>0 | C<br>S<br>1 | C<br>S<br>0 |

Table 2-2

DMA Instructions

2-14

### Processor PCB

| INSTRUCTION       | READ/ | I/O     |             |             | DA          | τα Β        | SUS         |             |             |                           |

|-------------------|-------|---------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|---------------------------|

|                   | WRITE | ADDRESS | 7           | 6           | 5           | 4           | 3           | 2           | 1           | 0                         |

| Write RQ Register | W     | 19      | _           |             |             |             |             | R<br>B      | C<br>S<br>1 | C<br>S<br>0               |

| Write Single Mask | W     | 0B      | _           |             | _           |             |             | M<br>K      | C<br>S<br>1 | C<br>S<br>0               |

| Write All Mask    | W     | 1F      | _           |             |             | _           | M<br>B<br>3 | M<br>B<br>2 | M<br>B<br>1 | <b>M</b><br><b>B</b><br>0 |

| Read Status       | R     | 09      | R<br>Q<br>3 | R<br>Q<br>2 | R<br>Q<br>1 | R<br>Q<br>0 | T<br>C<br>3 | T<br>C<br>2 | T<br>C<br>1 | T<br>C<br>0               |

| CH0 DMA Address   | R/W   | 01      |             |             | A5<br>A13   |             |             |             | A1<br>A9    | A0<br>A8                  |

| CH0 DMA Count     | R/W   | 11      |             | -           | W5<br>W13   |             |             |             |             | W0<br>W8                  |

| CH1 DMA Address   | R/W   | 03      |             |             | A5<br>A13   |             |             |             |             | A0<br>A8                  |

| CH1 DMA Count     | R/W   | 13      |             |             | W5<br>W13   |             |             |             |             | W0<br>W8                  |

| CH2 DMA Address   | R/W   | 05      |             |             | A5<br>A13   |             |             |             |             | A0<br>A8                  |

| CH2 DMA Count     | R/W   | 15      |             |             | W5<br>W13   |             |             |             |             | W0<br>W8                  |

| CH3 DMA Address   | R/W   | 07      |             |             | A5<br>A13   |             |             |             |             | A0<br>A8                  |

| CH3 DMA Count     | R/W   | 17      |             |             | W5<br>4 W13 |             |             |             |             | W0<br>W8                  |

Table 2-2

DMA Instructions (cont'd)

| INSTRUCTION        | READ/ | EAD/ I/O |        |        |        |        | DATA BUS |          |         |         |  |  |  |

|--------------------|-------|----------|--------|--------|--------|--------|----------|----------|---------|---------|--|--|--|

|                    | WRITE | ADDRESS  | 7      | 6      | 5      | 4      | 3        | 2        | 1       | 0       |  |  |  |

| CH0 Page Register  | W     | 38       | 0      | 0      | 0      | 0      | A<br>19  | A<br>18  | A<br>17 | A<br>16 |  |  |  |

| CH1 Page Register  | W     | 3A       | 0      | 0      | 0      | 0      | A<br>19  | A<br>18  | A<br>17 | A<br>16 |  |  |  |

| CH2 Page Register  | W     | 3C       | 0      | 0      | 0      | 0      | A<br>19  | .A<br>18 | A<br>17 | A<br>16 |  |  |  |

| CH3 Page Register  | W     | 3E       | 0      | 0      | 0      | 0      | A<br>19  | A<br>18  | A<br>17 | A<br>16 |  |  |  |

| Read Temp Register | R     | 1D       | D<br>7 | D<br>6 | D<br>5 | D<br>4 | D<br>3   | D<br>2   | D<br>1  | D<br>0  |  |  |  |

| Master Clear       | W     | 1D       |        |        |        |        |          |          |         |         |  |  |  |

Table 2-2 DMA Instructions (cont'd)

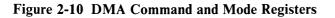

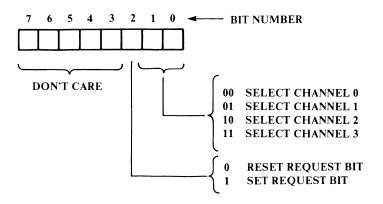

**REQUEST REGISTER**

SOFTWARE REQUESTS WILL BE SERVICED ONLY IF THE CHANNEL IS IN BLOCK MODE.

Figure 2-11 DMA Request and Mask Register

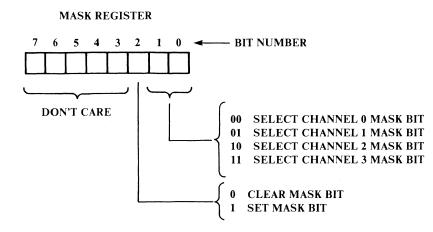

THE INSTRUCTION, WHICH SEPARATELY SETS OR CLEARS THE MASK BITS, IS SIMILAR IN FORM TO THAT USED WITH THE REQUEST REGISTER.

ALL FOUR BITS OF THE MASK REGISTER MAY ALSO BE WRITTEN WITH A SINGLE COMMAND.

THIS INFORMATION INCLUDES WHICH CHANNELS HAVE REACHED A TERMINAL COUNT AND WHICH CHANNELS HAVE A PENDING DMA REQUEST. BITS 0 THROUGH 3 ARE SET EVERY TIME A TC IS REACHED BY THAT CHANNEL OR AN EXTERNAL EOP IS APPLIED. THESE BITS ARE CLEARED UPON RESET AND ON EACH STATUS READ.

Figure 2-12 DMA Status Register

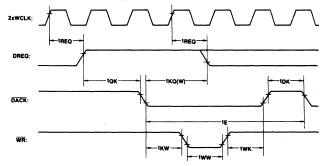

#### 2.4 INTERVAL TIMER

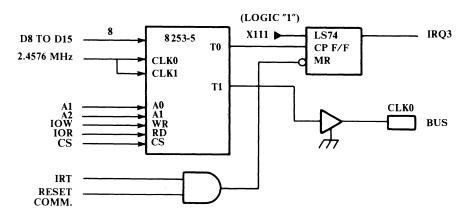

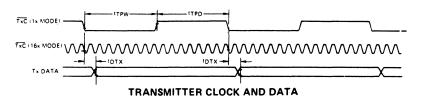

The NEC  $\mu$ PD8253-5 Programmable Interval Timer has three timer counter outputs: Channel 0 is attached to interrupt-request Channel 3; Channel 1 is sent to the synchronous/asynchronous communications controller on the Controller PCB (see Chapter 3); Channel 2 is not used. Figure 2-13 is a block diagram of the interval timer. Table 2-3 lists the timer commands.

Figure 2-13 Interval Timer Block Diagram

| INSTRUCTION    | READ/    | I/O     |     |        | Ι      | DAT | A BU | JS     |            |    |

|----------------|----------|---------|-----|--------|--------|-----|------|--------|------------|----|

|                | WRITE    | ADDRESS | 7   | 6      | 5      | 4   | 3    | 2      | 1          | 0  |

| Load Counter 0 | W        | 29      |     |        | C5     |     |      |        |            | C0 |

|                |          |         | C15 | C14    | C13    | C12 | C11  | C10    | С9         | C8 |

| Load Counter 1 | W        | 2B      |     |        | C5     |     |      |        |            | C0 |

|                |          |         | C15 | C14    | C13    | C12 | C11  | C10    | С9         | C8 |

|                |          |         | S   |        | R      |     |      |        |            | В  |

| Mode Set       | W        | 2F      | C   | C<br>0 | L<br>1 |     | M2   | M1     | <b>M</b> 0 | C  |

|                |          |         | 1   | 0      | 1      | 0   |      |        |            | D  |

| Timer Reset    | W        | 46      | x   | X      | X      | X   | X    | T<br>M | X          | Х  |

| X: Don't care. | <b>.</b> | ł       | 1   |        |        |     |      |        |            |    |

Table 2-3

Timer Commands

#### 2.5 INTERRUPT CONTROL

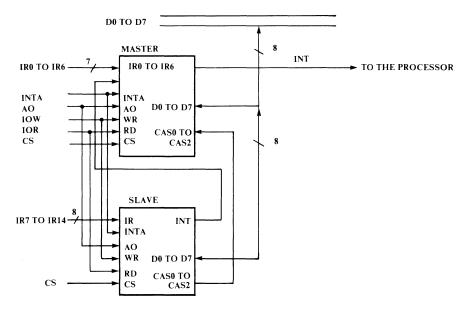

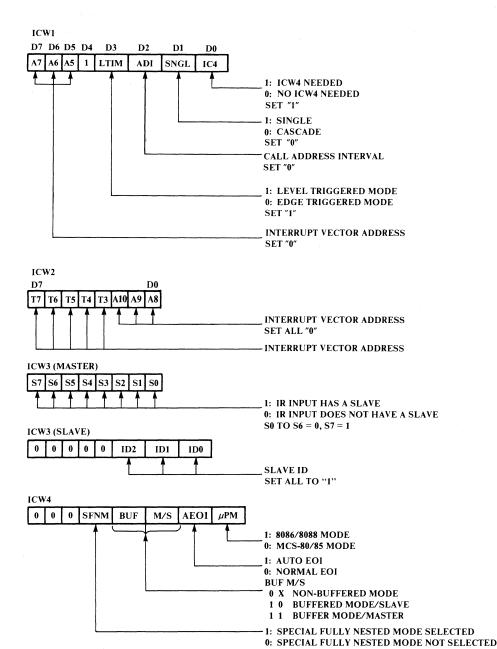

This interrupt function is controlled by two 8259 Metal Oxide Semiconductor (MOS) devices; each can handle up to eight vectored priority interrupts, as shown in Figure 2-14. The first 8259 device (master) supports IR0 through IR6, with IR7 cascaded from the second 8259 device (slave), which supports IR7 through IR14. These 15 available interrupt lines are assigned to service specific devices in order of priority. Table 2-4 lists the interrupt lines.

There are two interactions between the processor and the interrupt controller. The first is the acknowledgement process, during which the processor transmits acknowledgement of the interrupt request to the interrupt controller. During the second process, the interrupt controller transmits a byte of data to the processor (see Table 2-4).

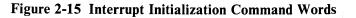

Control commands issued by the processor, consisting of Initialization Command Words (ICW) and Operational Command Words (OCW), are summarized in Table 2-5 and shown in Figures 2-15 and 2-16. Table 2-5 also includes poll mode, read interrupt register (IRR), read inservice register (ISR), and interrupt register words that are read into the data bus by the interrupt controller when so commanded.

Figure 2-14 Interrupt Control Block Diagram

| Table | 2-4 | Interrupt I | Lines |

|-------|-----|-------------|-------|

|-------|-----|-------------|-------|

| DEVICE | INTERRUPT<br>REQUEST LINE                                 | ASSIGNMENT                                                                         | INTERRUPT<br>VECTOR BYTE                             |

|--------|-----------------------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------|

| Master | IR0<br>IR1<br>IR2<br>IR3<br>IR4<br>IR5<br>IR6             | Not used<br>Communication<br>Not used<br>Timer<br>Keyboard<br>Not used<br>Not used | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |

| Slave  | IR7<br>IR8<br>IR9<br>IR10<br>IR11<br>IR12<br>IR13<br>IR14 | Printer<br>Not used<br>ORT<br>FDD<br>Not used<br>Not used<br>APU                   | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |

|        |             | READ/ | I/O     | DATA BUS |             |             |             |             |             |             |             |

|--------|-------------|-------|---------|----------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| DEVICE | INSTRUCTION | WRITE | ADDRESS | 7        | 6           | 5           | 4           | 3           | 2           | 1           | 0           |

| Master | ICW 1       | W     | 20      | 0        | 0           | 0           | 1           | 0           | 0           | 0           | 1           |

|        | ICW 2       | W     | 22      | T7       | T6          | T5          | T4          | Т3          | 0           | 0           | 0           |

|        | ICW 3       | W     | 22      | 1        | 0           | 0           | 0           | 0           | 0           | 0           | 0           |

|        | ICW 4       | w     | 22      | 0        | 0           | 0           | 0           | 0           | 0           | 0           | 1           |

|        | OCW 1       | W     | 22      |          | M6          | M5          | M4          | M3          | M2          | M1          | M0          |

|        | OCW 2       | W     | 20      | R        | S<br>L      | E<br>O<br>I | 0           | 0           | L2          | L1          | L0          |

|        | OCW 3       | W     | 20      | 0        | E<br>S<br>M | S<br>M<br>M | 0           | 1           | Р           | P<br>R      | R<br>I<br>S |

|        | Poll Mode   | R     | 20      | Ι        |             |             |             |             | W2          | W1          | W0          |

|        | Read IRR    | R     | 20      |          | I<br>R<br>6 | I<br>R<br>5 | I<br>R<br>4 | I<br>R<br>3 | I<br>R<br>2 | I<br>R<br>1 | I<br>R<br>0 |

|        | Read ISR    | R     | 20      |          | I<br>S<br>6 | I<br>S<br>5 | I<br>S<br>4 | I<br>S<br>3 | I<br>S<br>2 | I<br>S<br>1 | I<br>S<br>O |

|        | Read Mask   | R     | 22      |          | M6          | M5          | M-4         | M3          | M2          | M1          | M0          |

| Slave  | ICW 1       | W     | 28      | 0        | 0           | 0           | 1           | 0           | 0           | 0           | 1           |

|        | ICW 2       | W     | 2A      | T7       | T6          | Т5          | T4          | T3          | 0           | 0           | 0           |

|        | ICW 3       | W     | 2A      | 0        | 0           | 0           | 0           | 0           | 1           | 1           | 1           |

|        | ICW 4       | W     | 2A      | 0        | 0           | 0           | 0           | 0           | 0           | 0           | 1           |

Table 2-5 Interrupt Control Commands Summary

|        |             | READ/ | I/O     |          |             |             | DAT      | A BU        |         |         |             |

|--------|-------------|-------|---------|----------|-------------|-------------|----------|-------------|---------|---------|-------------|

| DEVICE | INSTRUCTION | WRITE | ADDRESS | 7        | 6           | 5           | 4        | 3           | 2       | 1       | 0           |

|        | OCW 1       | W     | 2A      | M14      | M13         | M12         | M11      | <b>M</b> 10 | M9      | M 8     | M7          |

|        | OCW 2       | W     | 28      | R        | S<br>L      | E<br>O<br>I | 0        | 0           | L2      | L1      | L0          |

|        | OCW 3       | W     | 28      | 0        | E<br>S<br>M | S<br>M<br>M | 0        | 1           | Р       | R<br>R  | R<br>I<br>S |

|        | Poll Mode   | R     | 28      | Ι        |             |             |          | <u></u>     | W2      | W1      | W0          |

|        | Read IRR    | R     | 28      | IR<br>14 | IR<br>13    | IR<br>12    | IR<br>11 | IR<br>10    | IR<br>9 | IR<br>8 | IR<br>7     |

|        | Read IRR    | R     | 28      | IS<br>14 | IS<br>13    | IS<br>12    | IS<br>11 | IS<br>10    | IS<br>9 | IS<br>8 | IS<br>7     |

|        | Read Mask   | R     | 2A      | M14      | M13         | 3 M12       | M11      | M10         | M9      | M8      | M7          |

Table 2-5

Interrupt Control Commands Summary (cont'd)

**Processor** PCB

2-25

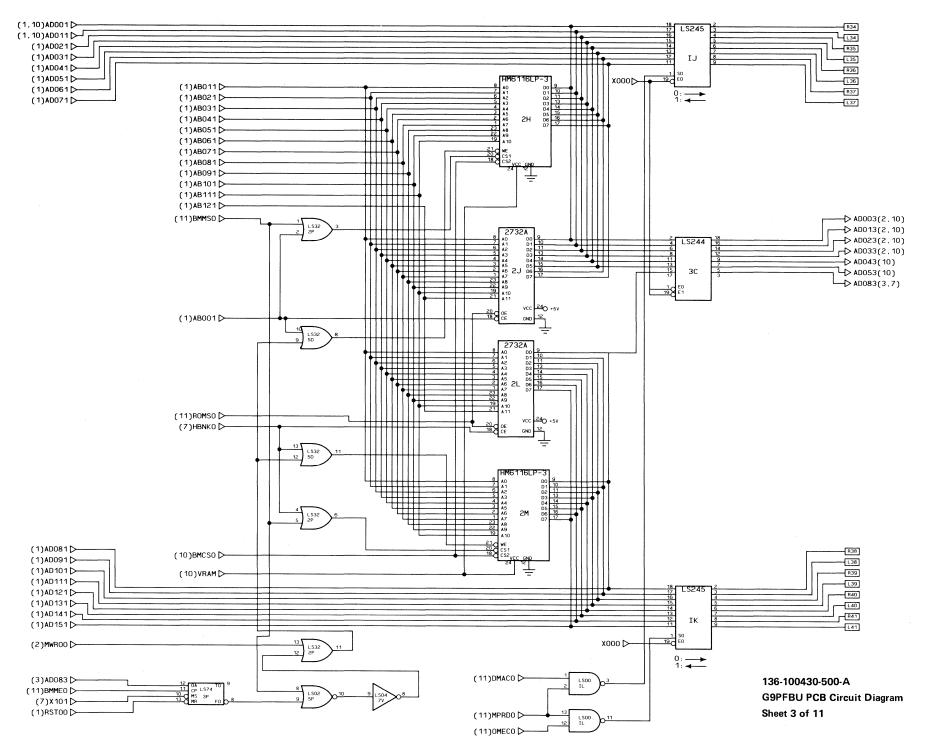

#### 2.6 MEMORY

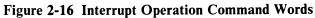

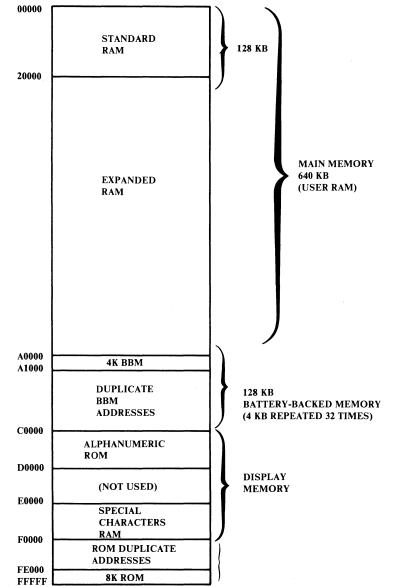

Figure 2-17 System Memory Map

#### 2.6.1 Main Memory

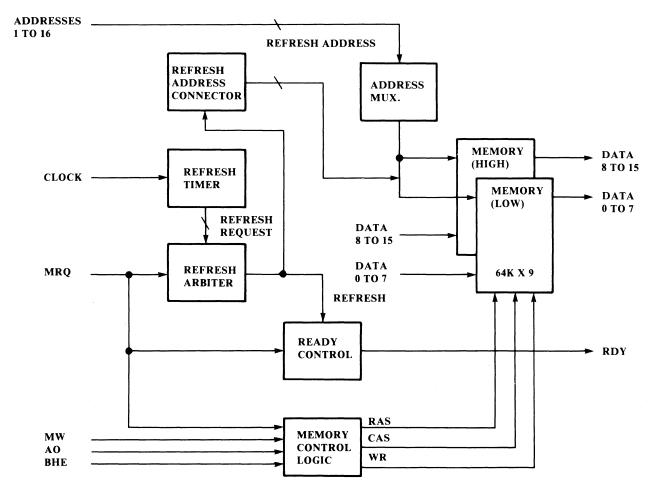

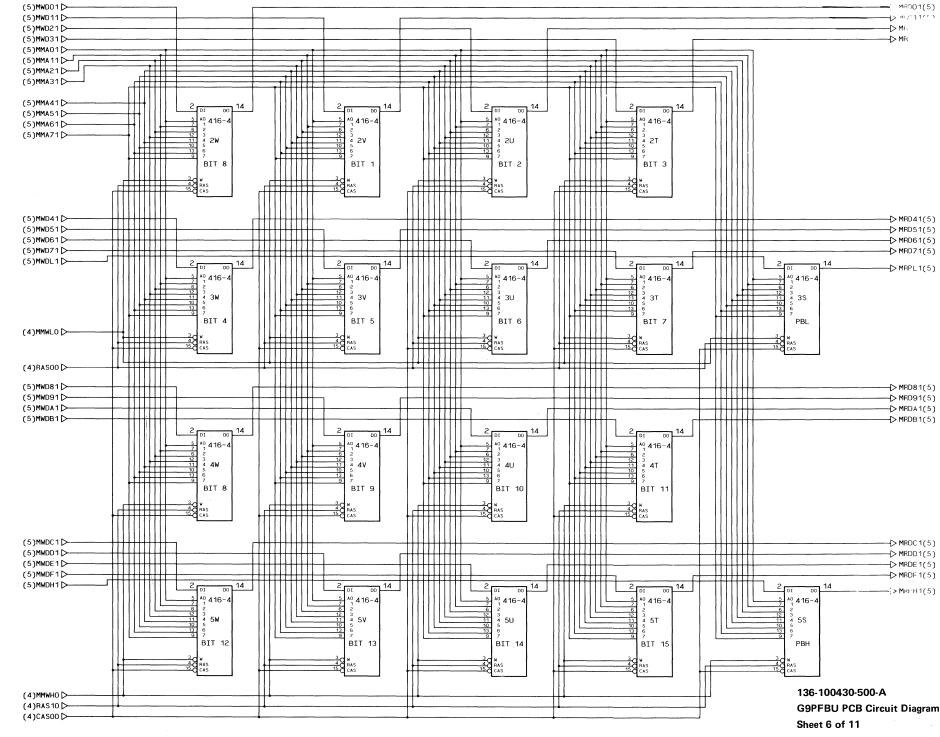

The Processor PCB contains 128 KB (64 Kwords: 16 bits of data, 18 bits wide, with 1 bit parity for each 8 bits) of RAM, organized into eighteen 64K x 1-bit dynamic memory chips. Figure 2-18 is a block diagram of the circuit. The RAM is refreshed during the non-memory-access cycle, and its access time is 200 ns. Parity check is carried out with two additional memory chips. A detected parity error lights the D4 red Light Emitting Diode (LED), located near the top edge of the Processor PCB.

As shown in Figure 2-17, the main memory is expandable to a maximum of 640 KB, of which 256 KB can be supported by the present APC equipment configuration.

Figure 2-18 Main Memory Block Diagram

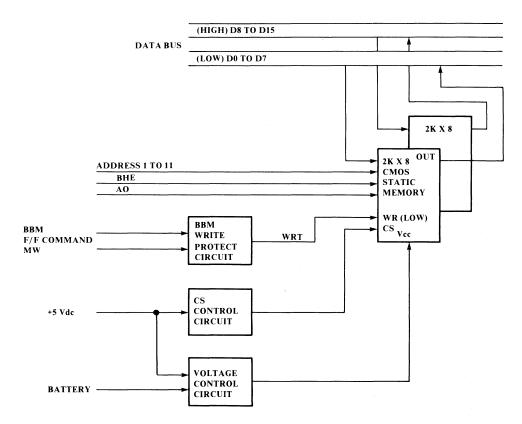

#### 2.6.2 Battery-Backed Memory

The BBM is composed of 4K (two 2K X 8-bit chips) of Complementary Metal Oxide Semiconductor (CMOS) static RAM and is addressable from A0000 through C0000 hexadecimal (HEX) in 32 4K visible sections of memory, each section containing the same data. The APC uses partial address decoding of this 128 KB of memory, which results in 4 KB of BBM. The BBM contains system information and is protected from loss for at least two years by the battery that plugs into the Processor PCB.

As shown in Figure 2-19, the BBM read/write operation is identical to that of the main memory except for a BBM write protect circuit that safeguards the BBM from unintentional data manipulation.

Figure 2-19 Battery-Backed Memory Block Diagram

2-28

The BBM write protect command I/O port address is 59(HEX). A logical "1" on the Least Significant Bit (LSB) position on the data bus enables writing to the BBM; a "0" sets the BBM for write protection.

#### 2.6.3 Read Only Memory

The Processor PCB contains 8K of ROM in two 4K x 8-bit Erasable Programmable Read-Only Memory (EPROM) chips. The ROM has two functions: flexible disk self-testing and bootstrap loading. As shown in Figure 2-17, the ROM occupies the 8K addresses from FE000 through FFFFF and is visible in eight duplicate 8K sections from F0000 through FFFFF. At APC power-on, the 8086 code segment and instruction-pointer registers are set to FFFF(HEX) and 0000(HEX) addresses respectively for loading and auto self-test, instructions for which are resident in the ROM.

#### 2.7 PARALLEL PRINTER CONTROL

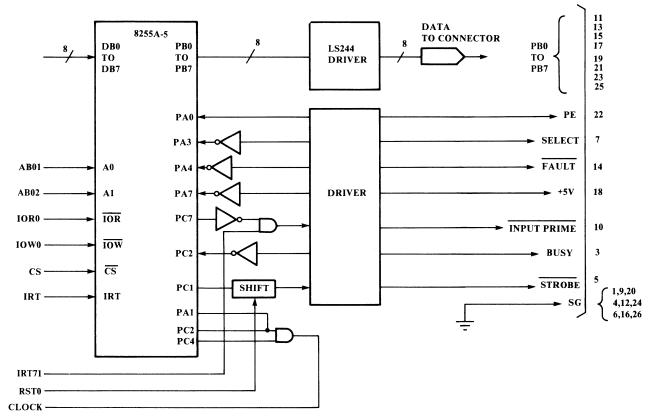

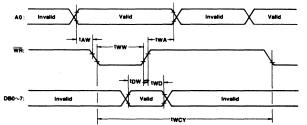

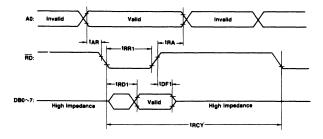

This portion of the logic provides an I/O TTL interface with an external paralleldata-bus printer.

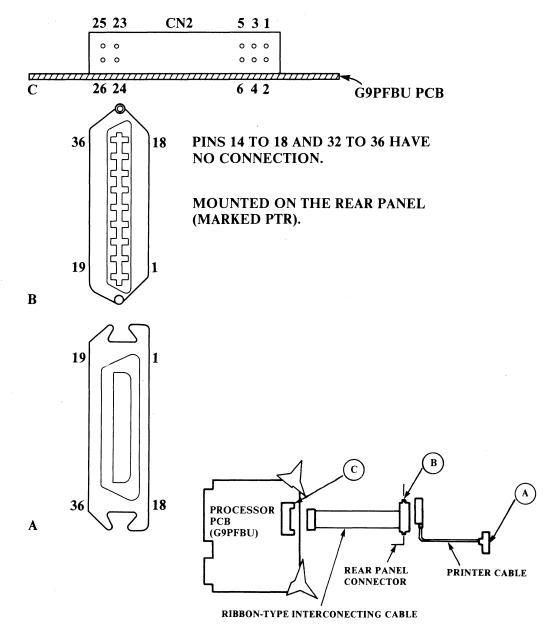

As shown in Figures 2-20 and 2-21, the parallel printer control consists of an NEC  $\mu$ PD8255A Programmable Peripheral Controller that interfaces with connector CN2 through LS244 drivers. A flat-type 26-conductor cable connects the CN2 board connector to a connector at the rear of the main unit that, in turn, goes to the printer. The pin connections are listed in Table 2-6. The interface is adaptable to either an Output Device Adapter (ODA) or Centronics-type printer by setting appropriate jumpers on TM2, TM3, and TM4 on the Processor PCB (see Figure 2-29).

#### 2.7.1 Interface

Table 2-7 lists the interface lines.

#### 2.7.2 Programming Considerations

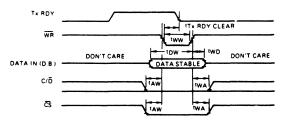

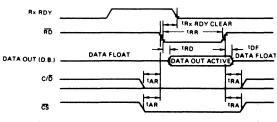

The 8255A device is operated in the APC as Mode 0 (basic I/O) in the Group A ports (Port A and upper 4 lines of Port C), and Mode 1 (strobed) in the Group B ports (Port B and lower 4 lines of Port C). The eight lines of Port B (PB0 through PB7) carry the strobed data to the printer; I/O control line levels are from Ports A and C.

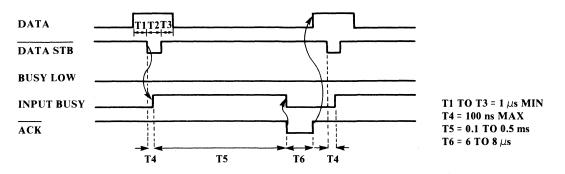

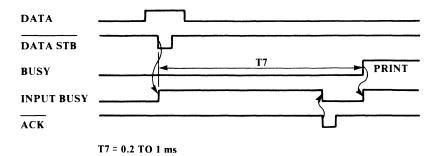

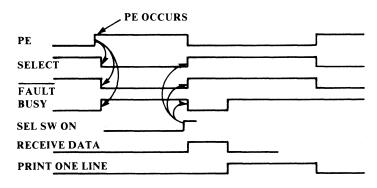

Programming and execution of the 8255 is accomplished using the instructions described in Tables 2-8 and 2-9. Figures 2-22 and 2-23 show interline timing under various operating conditions.

PRINTER CABLE CONNECTOR PIN NUMBERS

Figure 2-20 Parallel Printer Control Block Diagram

#### Processor PCB

|                 | PIN NUMBER | PIN NUMBER | PIN NUMBER | REMARKS   |

|-----------------|------------|------------|------------|-----------|

| SIGNAL          | AT A       | AT B       | AT C       |           |

| DATACTO         | 1          | 2          |            |           |

| DATA STB        | 1 2        | 3 6        | 2          |           |

| DATA 1          |            |            | 16         |           |

| DATA 2          | 3          | 7          | 4          |           |

| DATA 3          | 4          | 8          | 17         |           |

| DATA 4          | 5          | 9          | 5          |           |

| DATA 5          | 6          | 10         | 18         |           |

| DATA 6          | 7          | 11         | 6          |           |

| DATA 7          | 8          | 12         | 19         |           |

| DATA 8          | 9          | 13         | 7          |           |

| ACK             | 10         | 2          | 14         |           |

| Input Busy      | 11         | 22         | 9          |           |

| PĚ              | 12         | 29         | 25         |           |

| SELECT          | 13         | 4          | 15         |           |

| Signal Ground   | 14         | NC         | NC         |           |

| NC              | 15         | NC         | NC         |           |

| Signal Ground   | 16         | NC         | NC         |           |

| Chassis Ground  | 17         | NC         | NC         |           |

| +5 Vdc          | 18         | 27         | NC 24      | · · ·     |

| Twisted Pair -  |            |            |            |           |

| Ground (Pin 1)  | 19         | NC         | NC         |           |

| Ground (Pin 2)  | 20         | 20         | 8          |           |

| Ground (Pin 3)  | 21         | 21         | 21         |           |

| Ground (Pin 4)  | 22         | 5          | 3          |           |

| Ground (Pin 5)  | 23         | 24         | 10         |           |

| Ground (Pin 6)  | 24         | 26         | 11         |           |

| Ground (Pin 7)  | 25         | 28         | 12         |           |

| Ground (Pin 8)  | 26         | 30         | 13         |           |

| Ground (Pin 9)  | 27         | 31         | 26         |           |

| Ground (Pin 10) | 28         | NC         |            |           |

| Ground (Pin 11) | 29         | NC         |            |           |

| Ground (Pin 31) |            | NC         |            |           |

| Input Prime     | 31         | 23         | 22         |           |

| Fault           | 32         | 25         | 23         |           |

| Signal Ground   | 33         | NC         | NC         |           |

| NC              | 34         | NC         | NC         |           |

| NC              | 35         | 18         |            | 1         |

| Input Busy      | 36         | NC         | NC         |           |

| mput busy       | 50         |            |            |           |

| Input busy      | 50         | 19         | 20         | No signal |

Table 2-6 Parallel Printer Connectors Pin Assignments

NOTE: NC means No Connection.

Processor PCB

| SIGNAL | SOURCE  | DESCRIPTION                                                                                                                                                                                                               |

|--------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RMS    | АРС     | <i>Receive Machine Set.</i><br>This signal is used<br>with the ODA printer<br>interface only.                                                                                                                             |

| BUSY   | Printer | <ul> <li>Goes high to indicate that the printer cannot receive data:</li> <li>1. During data entry</li> <li>2. During printing operation</li> <li>3. In offline state</li> <li>4. During printer error status.</li> </ul> |

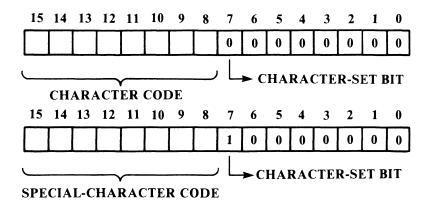

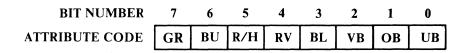

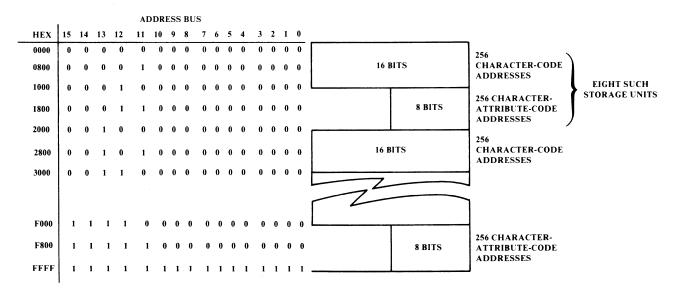

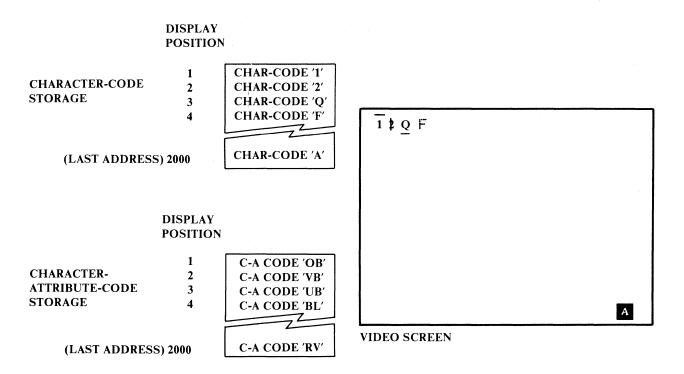

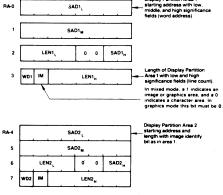

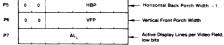

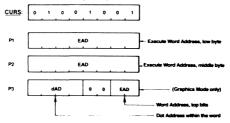

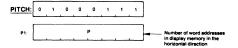

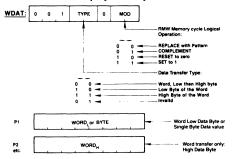

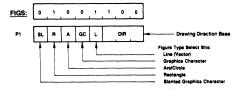

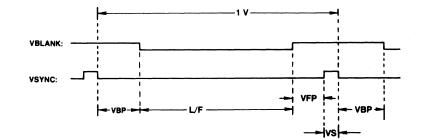

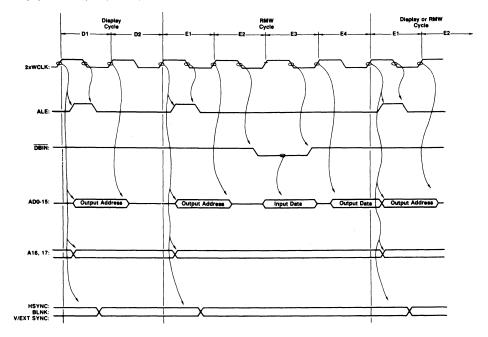

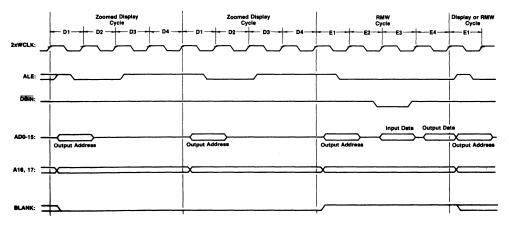

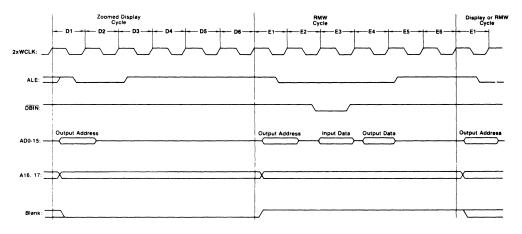

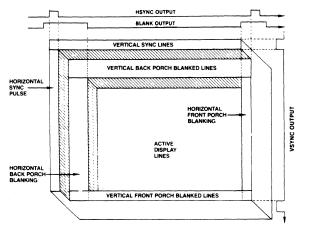

| STROBE | APC     | Strobe pulse to read<br>data in. The signal<br>level is normally<br>High. Read-in of data<br>is performed at the<br>Low level of this<br>signal.                                                                          |