## United States Patent [19]

## Harrison et al.

### [54] MODULAR UNITARY DISK FILE SUBSYSTEM

- [75] Inventors: Joel N. Harrison, Monte Sereno; William G. Moon, Sunnyvale; Randolph H. Graham, Fremont, all of Calif.

- [73] Assignee: **Plus Development Corporation**, Milpitas, Calif.

- [21] Appl. No.: 741,175

- [22] Filed: Jun. 4, 1985

- Int. Cl.4 ...... G06F 1/00; G11B 5/012 [51]

- - 360/97; D8/354

- [58] Field of Search ...... 360/78, 97-99; 361/395, 407, 413, 397; 364/708, 200 MS File, 900 MS File

#### [56] **References** Cited

#### **U.S. PATENT DOCUMENTS**

| Re. 32,075 | 1/1986  | Harrison et al                 |

|------------|---------|--------------------------------|

| 3,184,645  | 5/1965  | Schaeffer 317/101              |

| 3,656,130  | 4/1972  | Bucklin, Jr. et al 340/174.1 C |

| 3,727,168  | 4/1973  | Henschen et al 339/17 F        |

| 3,769,552  | 10/1973 | Cook et al 317/112             |

| 3,843,967  | 10/1974 | Mulvany                        |

| 3,973,817  | 8/1976  | Stalley et al                  |

| 3,993,935  | 11/1976 | Phillips et al                 |

| 4,006,388  | 2/1977  | Bartholomew 317/100            |

| 4,053,944  | 10/1977 | Dixon                          |

| 4,062,049  | 4/1976  | Dirks 360/78                   |

| 4,189,769  | 2/1980  | Cook et al                     |

| 4,218,742  | 8/1980  | Carlton et al                  |

| 4,272,793  | 6/1981  | Van Landingham 360/78          |

| 4,285,018  | 8/1981  | Mulvany et al                  |

| 4,314,295  | 2/1982  | Frandsen                       |

| 4,331,990  | 5/1982  | Frandsen                       |

| 4,399,487  | 8/1983  | Neumann                        |

| 4,413,328  | 11/1983 | Videki, II                     |

| 4,419,701  | 12/1983 | Harrison et al                 |

| 4,423,448  | 12/1983 | Frandsen                       |

| 4,506,323  | 3/1985  | Pusic et al                    |

| 4,509,116  | 4/1985  | Lackey et al                   |

| 4,516,177  | 5/1985  | Moon et al                     |

| 4,517,512  | 5/1985  | Petrich et al                  |

| 4,525,802  | 6/1985  | Hackamack                      |

| 4,538,193  | 8/1985  | Dimmick et al                  |

| 4,593,194  | 6/1986  | Graham et al 250/231           |

|            |         | A                              |

#### Date of Patent: Jan. 27, 1987 [45]

#### FOREIGN PATENT DOCUMENTS

0104941 4/1984 European Pat. Off. .

#### **OTHER PUBLICATIONS**

Data Zone Product Announcement/press Release, 5/6/85 (as Presented in W. Erickson Declaration Exhibits A and B).

Data Zone Product Announcement/flyer for Slot Drive Product and for FlexiDrive Product, 7/85 (as Presented in Moon Declaration).

Pennington & Recupero, "Digital Sector Servo System", IBM Tech. Discl. Bull. vol. 22, No. 6, Nov. 1979, pp. 2476-2481.

Advertisement, Xebec Owl Disk Drive, Electronics Week, Oct. 22, 1984, pp. 10-11.

IBM Personal Computer Technical Reference Manual 4/83 ed. pp. 1-7, 1-17 to 22.

Dictionary of Computers, Data Processing and Telecommunications, Wiley & Sons Copyright 1984, pp. 231, 232 329

PC World, Feb. 1984 pp. 13, 270-275, (vol. 2, No. 2).

"New Compact Hard Disk Drives and Hard Disk Controllers" Press Release, New Product Announcement, Data Zone, Inc. Published at Comdex Show, Atlanta, GA, on or about May 6, 1985.

Primary Examiner—James D. Thomas Assistant Examiner—C. H. Lynt

Attorney, Agent, or Firm-David B. Harrison

#### ABSTRACT [57]

A self contained fixed rotating disk expansion board subsystem may be installed and connected at an expansion slot location of a host computer. The subsystem includes an enclosed head/disk assembly, and circuit elements mounted on a printed circuit board which includes a connector for connecting to the control, data and address buses of the host computer at the expansion slot location. The head/disk assembly is mounted to a mounting substrate which may be the circuit board or which may be a frame to which the circuit board is also attached. Input/output routines are preferably provided to enable the host computer to make use of the subsystem without software driver modifications in the host operating system.

#### 20 Claims, 31 Drawing Figures

FIG. 8b

Sheet 12 of 28 4,639,863

Sheet 17 of 28 4,639,863

Sheet 18 of 28 4,639,863

Sheet 24 of 28 4,639,863

Sheet 27 of 28 4,639,863

SEQUENCER IN SOFT SECTOR MODE

INDEX MARK

U.S. Patent

Jan. 27, 1987

Sheet 28 of 28 4,639,863

# 18 IDENTICAL SECTORS 568 BYTES PER SECTOR

INDEX MARK 399

|                                     |                             | 18 IDENTICAL SECTORS 568 BTTES PER SECTOR |                    |                       |                     |             |                      |                       |                      |                         |                        |                                |                        |                         | - I                  |

|-------------------------------------|-----------------------------|-------------------------------------------|--------------------|-----------------------|---------------------|-------------|----------------------|-----------------------|----------------------|-------------------------|------------------------|--------------------------------|------------------------|-------------------------|----------------------|

|                                     |                             | RE-WRITTEN DURING WRITE UPDATE            |                    |                       |                     |             |                      |                       |                      |                         |                        |                                |                        |                         |                      |

| 1                                   | 1                           |                                           |                    |                       |                     |             | 1                    |                       |                      |                         |                        |                                |                        |                         | • •                  |

| FIELD                               | POST<br>INDEX<br>GAP        | ID<br>PRE<br>AMBLE                        | ID<br>SYNC<br>BITE | ID<br>MARKER<br>BYTE  | ID<br>DATA<br>FIELD | ID<br>ECC   | ID<br>Post-<br>Amble | DATA<br>PRE-<br>AMBLE | DATA<br>SYNC<br>BYTE | DATA<br>MARKER<br>BYTE  | DATA<br>FIELD          | DATA<br>ECC                    | DATA<br>POST-<br>AMBLE | INTER-<br>SECTOR<br>GAP | PRE-<br>INDEX<br>GAP |

| SEQ<br>CNT                          | 149                         | 12                                        | 1                  | I                     | 4                   | 2           | 3                    | 12                    | 1                    | 1                       | 512                    | 6                              | 3                      | 10                      | ۱*                   |

| SEQ<br>VAL                          | 33                          | FF                                        | 62                 | FE                    | AS<br>REQ'D         | AS<br>REQ'D | 33                   | FF                    | 62                   | F8                      | 33                     | AS<br>REQ'D                    | 33                     | 33                      | 33                   |

| SEQ-<br>STATE                       | I                           | 2                                         | 3                  | 4                     | 5                   | 6           | 7                    | 8                     | 9                    | 10                      | 11                     | 12                             | 13                     | 14                      | 15                   |

| MODE                                | START                       | RESTART                                   |                    |                       |                     |             |                      |                       |                      |                         |                        |                                |                        | LOOP                    | HOLD                 |

|                                     |                             |                                           |                    |                       |                     |             |                      |                       |                      |                         |                        |                                |                        |                         |                      |

| 1                                   |                             |                                           |                    |                       |                     |             |                      |                       |                      |                         | 1                      | 1                              |                        |                         |                      |

|                                     | POST INDEX GAP BREAKDOWN ID |                                           |                    |                       |                     |             | FIELD B              | REAKDO                | WN                   | INTER-SECTOR GAP USA    |                        |                                |                        | USAGE                   |                      |

| PURPOSE: SERVO INDEX<br>WEDGE DRIFT |                             | DER                                       |                    | CYLIN-<br>DER<br>HIGH | CYLIN<br>DER<br>LOW | HEAD        | SECTOR               | PURPOSE:              |                      | WRITE<br>UPDATE<br>LOSS | SPEED<br>TOLER<br>ANCE | AM<br>SEARCH<br>RESTART<br>PAD |                        |                         |                      |

| # OF                                | BYTES:                      | 130                                       |                    | 19                    | # OF                | BYTES:      | i                    | 1                     |                      | 1                       | # OF                   | BYTES                          | 3                      | 5                       | 2                    |

\* 43 BYTES NOMINAL

FIG. 20

30

#### MODULAR UNITARY DISK FILE SUBSYSTEM

1

#### BACKGROUND OF THE INVENTION

The present invention relates to rotating disk data storage peripheral equipment for digital computers. More particularly, the present invention relates to a miniaturized, plug-in rotating fixed disk file subsystem module.

#### REFERENCE TO RELATED PATENTS AND PATENT APPLICATIONS

The following U.S. Patents and co-pending patent applications are pertinent to the present disclosure:

U.S. Pat. No. 4,396,959 (now U.S. Pat. No. Re. 15 32,075) for Data Transducer Position Control System for Ratating Disk Data Storage Equipment;

U.S. Pat. No. 4,419,701 for Data Transducer Actuator Control System for Rotating Disk Data Storage Equipment:

U.S. Pat. No. 4,516,177 for Rotating Rigid Disk Data Storage Device:

U.S. patent application Ser. No. 06/439,897 filed on Nov. 8, 1982 for Aerodynamically Released Safety Latch for Data Transducer Assembly in Rotating Rigid 25 Disk Data Storage Device; now U.S. Pat. No. 4,538,193;

U.S. patent application Ser. No. 06/444,523 filed on Nov. 26, 1982, for Improvements in Rotating Disk Data Storage Device:

U.S. patent application Ser. No. 06/728,674 filed on Apr. 25, 1985, for Aerodynamic Latch for Disk File Actuator:

U.S. patent application Ser. No. 741,179, filed on the same date as this application for Optical Encoder As- 35 sembly:

U.S. patent application Ser. No. 741,178, filed on the same date as this application for Compact Head and Disk Assembly;

U.S. patent application Ser. No. 741,588, filed on the 40 same date as this application for Microprocessor Controlled Rigid Disk File Subsystem;

U.S. patent application Ser. No. 741,174, filed on the same date as this application for Improved Optical Encoder.

Disk drives (also known as disk files) have become standard equipment for storing and retrieving user data in both large and small digital computer systems. Such drives have used removable rigid, semi-rigid and flexible disks e.g. coated with magnetic media for storing the 50 data. Optical data storage techniques are also known.

Disk drives of the type employed by the present invention have also used non-removable rotating storage disks in sealed, dust free environments in which the data air cushion or bearing in accordance with what is known as "Winchester" technology. These disk drives store and retrieve data in concentric data tracks formed on the major surfaces of the data storage disk. Such non-removable or "fixed" disk based drives are able to 60 store a significant amount of user data on each storage surface, such as five million bytes of user data per storage surface.

By moving the data transducers radially relative to the rotating disks with electromagnetic disk actuator 65 mechanisms, disk drives are able to gain access to any data location within a very short period of time. Thus, such drives combine the features of substantial data

storage capacity and random rapid access to any selected concentric track containing the stored data.

Traditionally, disk drives have been bulky and have required multiple separate subparts: an enclosed head and disk assembly; control electronics for the head and 5 disk assembly, usually packaged with the head and disk assembly, a controller for controlling the formatting of the data storage surface and for thereafter controlling each data storage (write) and retrieval (read) operation 10 performed by the drive; and an interface, for interfacing both the controller and the drive control electronics to the host computer, so that its operating system may use the drive effectively as a data storage resource available to the computer user.

Small computer systems, sometimes referred to as "personal computers" and as exemplified by the IBM Personal Computer TM, typically provide attachment locations and electrical connections for a few accessory circuit cards. These accessory cards may provide disk 20 drive controller, video display, modem, additional memory, and other functions. Usually the space allocated for such accessory cards is narrow (one inch across) and elongated. Also, the power supply available for such additional accessories is quite limited.

One significant drawback of the traditional approach has been that the use of separate circuits for the control electronics, controller and interface has led to redundancies of circuitry, particularly control, address and data buffers, and consequent high power consumption levels. These power consumption levels have required host computer systems to be designed to supply the required higher levels, or have required separate or special power supplies to be used.

One other significant drawback of the traditional approach has been the physical space required to house the head and disk assembly, its control electronics, the controller and the interface. When separate housings have been employed, significant drawbacks have been the clutter presented by the multiple housings and requirement that housings be cabled together with cables carrying a large number of conductors. Such cablings and plugs, extending outside of the housings, are exposed and have been known to fail, thereby rendering 45 the disk drive subsystem inoperative and useless until repaired. Also, multiple housings have complicated the portability of small personal computer systems.

Fixed disk drive head and disk assemblies do not lend themselves to home or field repairs. The disk drive enclosure may only be opened safely for inspection and service in a "clean-room" environment. Thus, the servicing of small fixed disk files usually goes on in the factory or at one or a few central service locations.

In light of these and other drawbacks known to those transducers fly very close to the storage surface on an 55 skilled in the art, a hitherto unsolved need has arisen for a fully integrated, highly miniaturized, very low power rotating non removable disk data storage subsystem module for direct plug-in attachment to and use within small host computer systems, typically of the "personal or professional computer" (single user) type, without use of any cabling and without any modification of the host beyond plugging in the modular subsystem.

### SUMMARY OF THE INVENTION WITH OBJECTS

A general object of the present invention is to miniaturize and to integrate a complete disk file subsystem into a small unitary module for direct plug-in attachment to and removal from a host computer system in a manner which overcomes the limitations and draw-backs of prior art disk file subsystems.

A specific object of the present invention is to provide a miniaturized, fully integrated disk drive subsys-5 tem in a flat, elongated form factor for plug-in attachment to a single user computer so as to occupy a single accessory jack location provided in the computer for attachment of accessories.

A further object of the present invention is to provide 10 a miniaturized and fully self contained unitary disk file subsystem for direct plug-in attachment to a host computer of the single user type without requiring any hardware modification of the computer.

One more object of the present invention is to pro-15 vide a miniaturized and fully self contained unitary disk file subsystem which may be plugged into and used with a host computer of the single user type by the computer user without requiring any special skills or special tools for the installation or for use. 20

A further object of the present invention is to provide a compact and efficient electronic control system which uses a single microprocessor to supervise operations of the disk file.

A modular unitary disk file subsystem for a host com- 25 puter incorporating the principles of the present invention includes a thin, compact, and enclosed radially movable head and fixed rotating disk assembly. An elongated, planar support substrate is provided for mounting and supporting the head and disk assembly 30 and for mounting, carrying and connecting electronic circuit elements for moving the head radially relative to the disk. The electronic circuit elements are provided for controlling data storage operations for storing and retrieving data from among selected concentric data 35 tracks formed on a data storage surface of the fixed rotating disk through the head, and for interfacing the disk file subsystem with the host computer. The support substrate further includes a connector at a single location thereon, the connector being provided for obtain- 40 ing power, control and data signals from the host computer, and for supplying control, status and data signals to the host computer. Thus, the support substrate thereby carries and interconnects the subsystem with the host computer as a direct plug-in unit within the 45 housing of the host, without any cabling between the host and the subsystem.

These and other objects, advantages and features of the present invention will become more apparent from the following detailed description of a preferred em- 50 bodiment, presented in conjunction with the accompanying drawings.

#### **BRIEF DESCRIPTION OF THE DRAWINGS**

In the drawings:

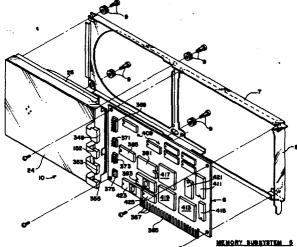

FIG. 1 is an exploded isometric and somewhat diagrammatic view of a compact, modular disk file subsystem including a mounting frame, the subsystem being in accordance with the principles of the present invention.

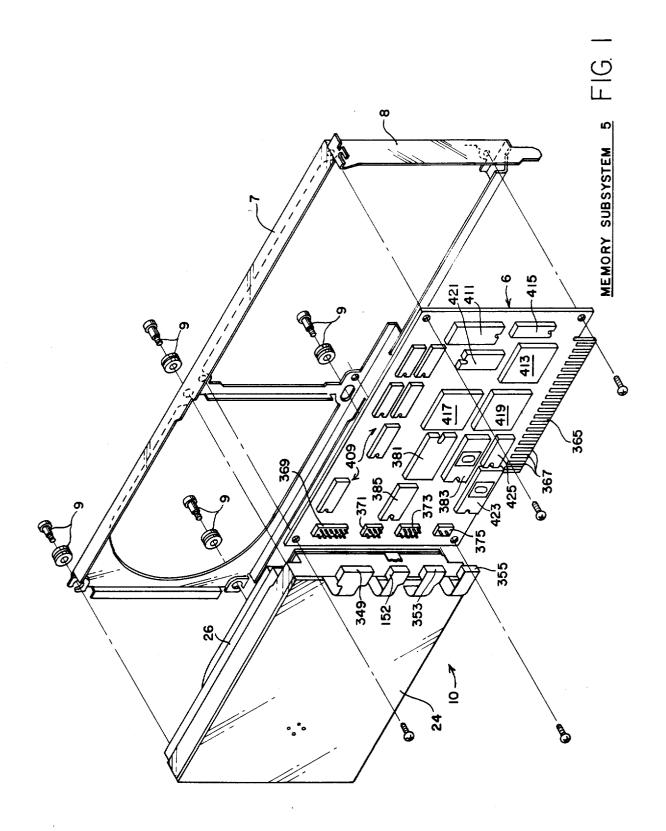

FIG. 2 is an exploded isometric and somewhat diagrammatic view of the subsystem of FIG. 1 wherein a printed circuit substrate is extended and provides the mounting substrate for the head and disk assembly.

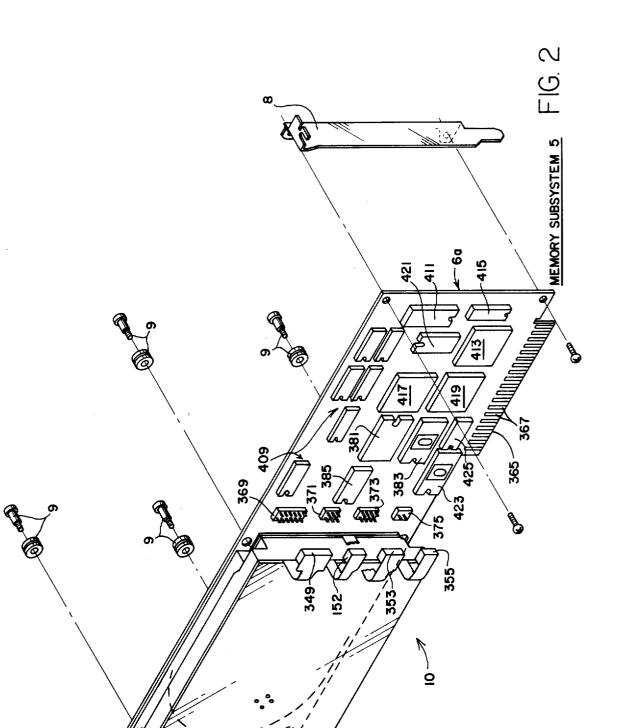

FIG. 3 is a somewhat diagrammatic and exploded view in perspective of an assembly of the elements 65 comprising the head and disk assembly incorporating the principles of the present invention. The elements depicted in FIG. 3 have been dispersed along broken explosion lines to facilitate illustration of the head and disk assembly.

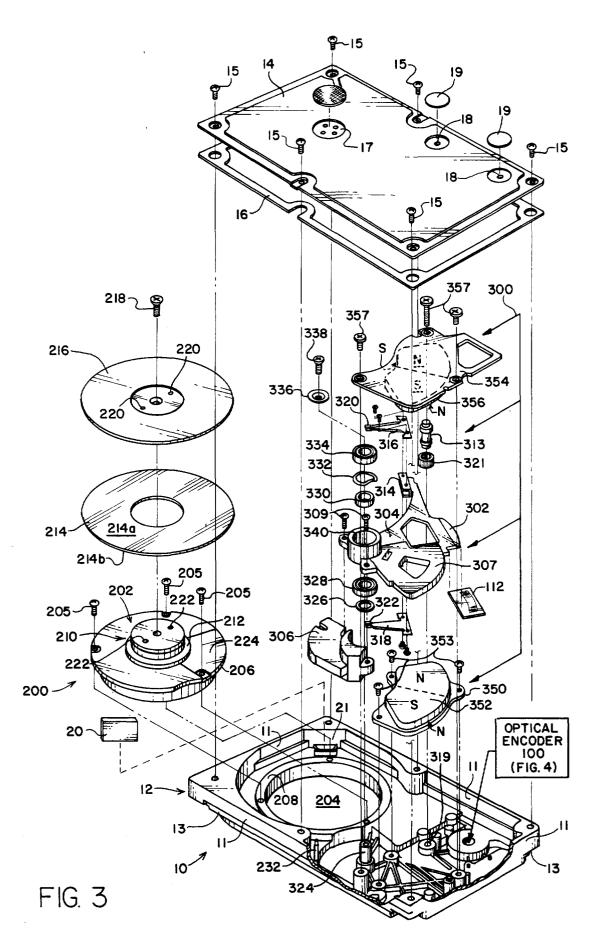

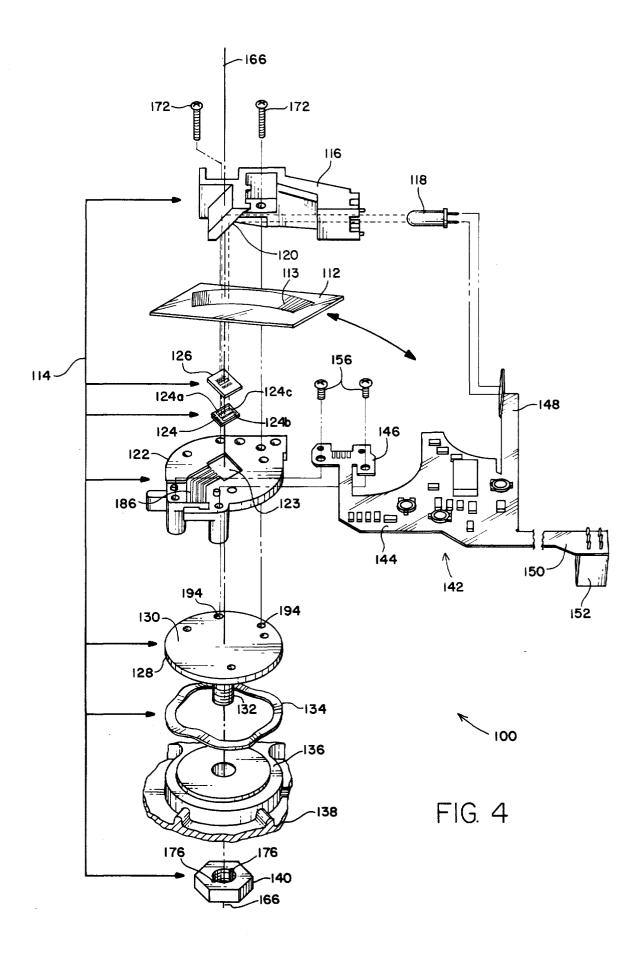

FIG. 4 is an exploded diagrammatic view in perspective along a single central axis of explosion of the structural elements comprising a compact optical encoder subassembly incorporated within the head and disk assembly depicted in FIG. 3.

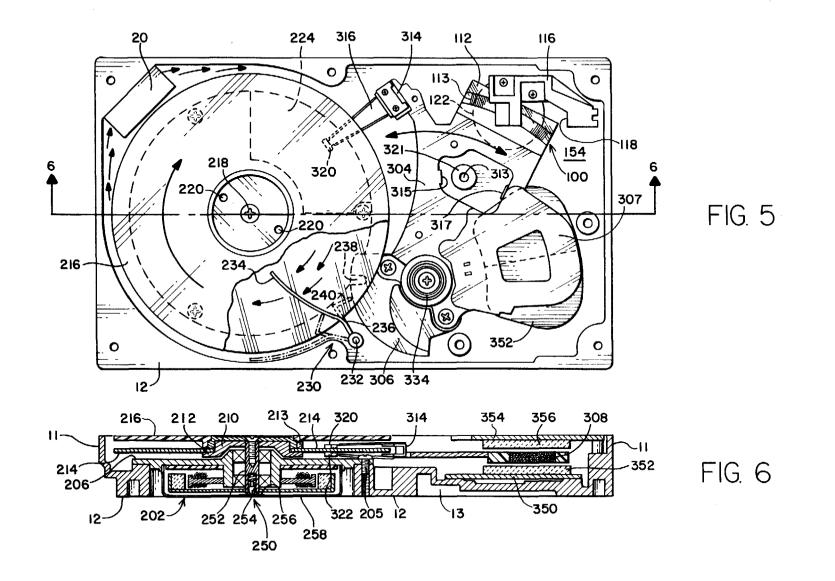

FIG. 5 is a diagrammatic top plan view of the head and disk assembly depicted in FIG. 3, showing the elements thereof in place, except for the upper magnet and flux return plate, and certain flexible connection substrates which have been omitted to facilitate clarity of explanation and understanding.

FIG. 6 is a longitudinal view in side elevation and section of the assembly of FIG. 3 through the axis of rotation of the spindle motor. The section is along the line 6-6 in FIG. 5.

FIG. 7 is a diagrammatic bottom plan view of the head and disk assembly depicted in FIG. 3.

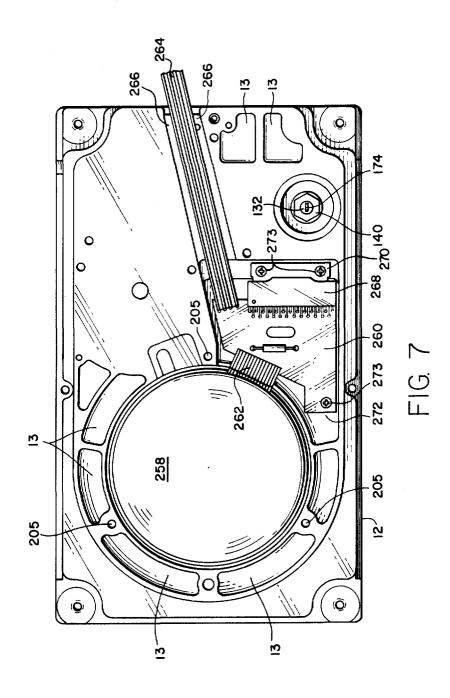

FIGS. 8A, and 8B are respectively an electronic schematic circuit diagram of the three phase, brushless spindle motor depicted in FIG. 3 and an electronic schematic circuit diagram of a driver circuit needed to operate and commutate the brushless DC spindle motor; and, a bottom or inside plan view of one preferred layout of a small circuit module for carrying the circuitry depicted in FIG. 8A.

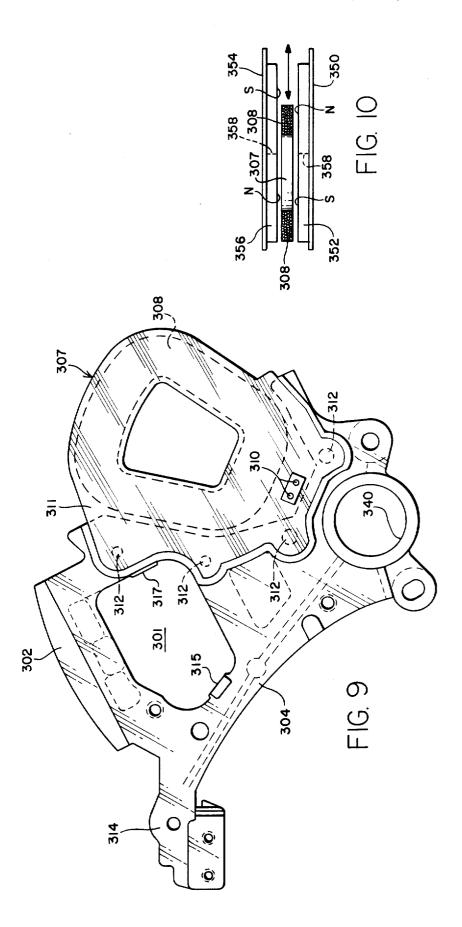

FIG. 9 is an enlarged top plan view of a rotary actuator element of the the head and disk assembly depicted in FIG. 3.

FIG. 10 is a diagrammatic view in side elevation and section of a portion of the rotary actuator motor, taken along the line 10–10 in FIG. 4.

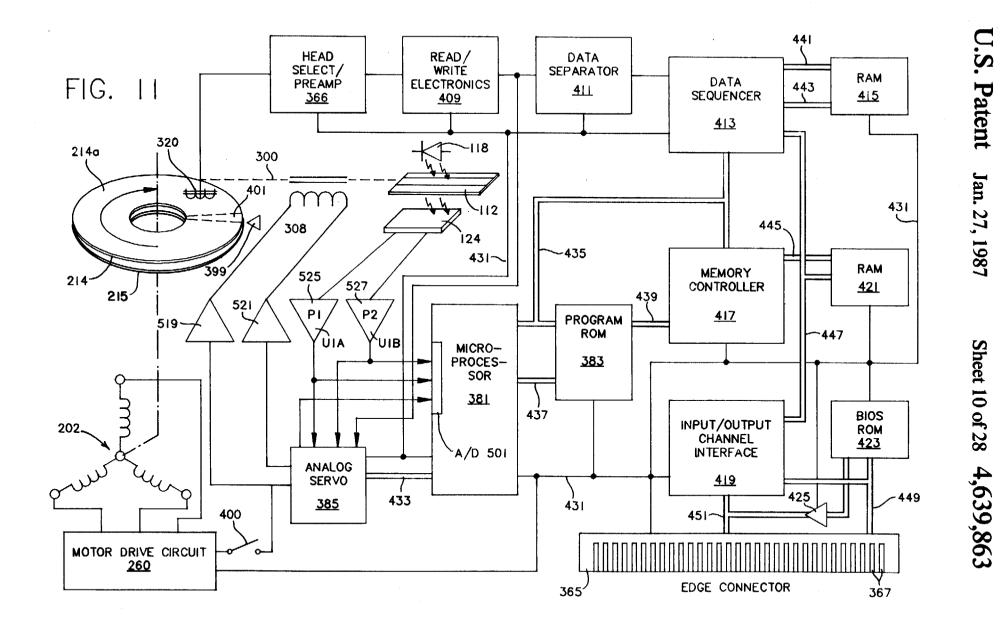

FIG. 11 is an electrical block diagram of the control electronics for the disk file subsystem depicted in FIG.

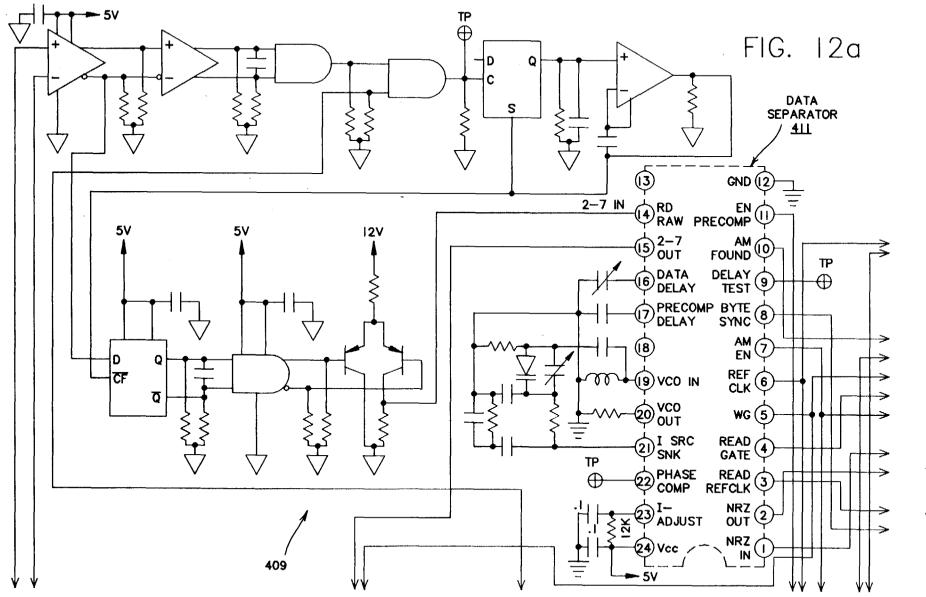

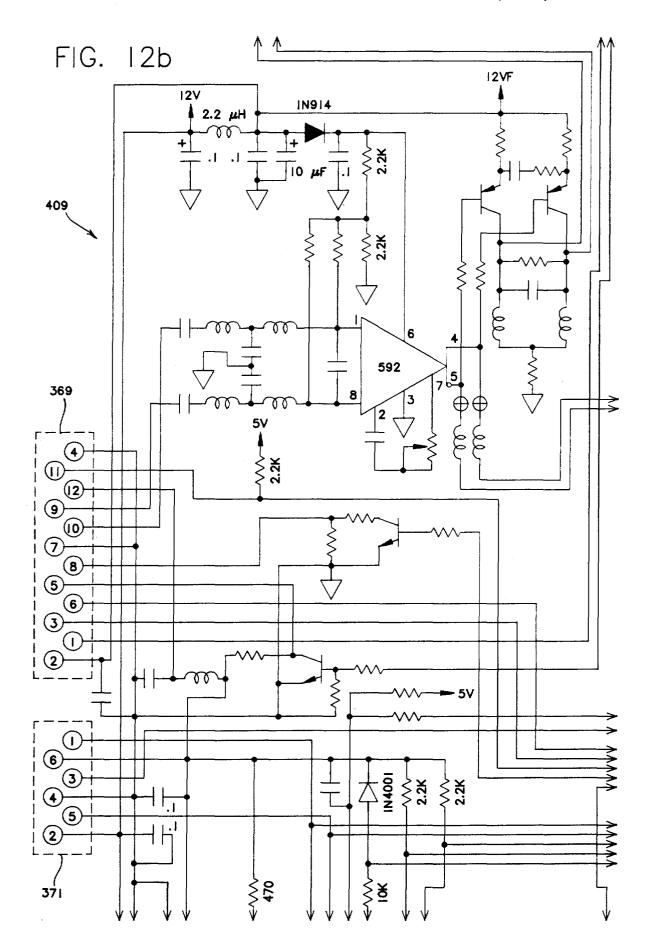

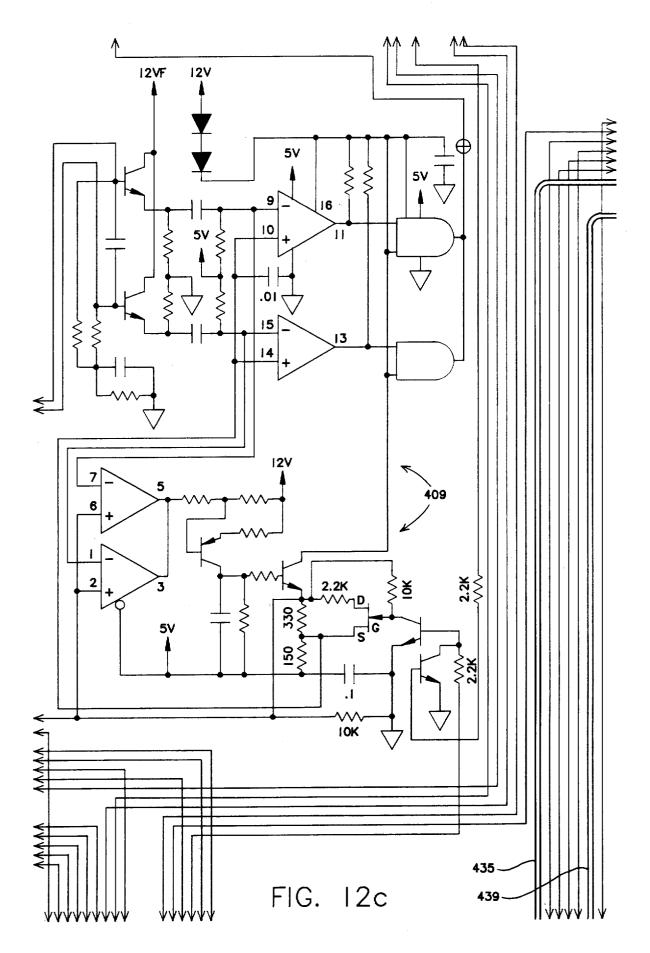

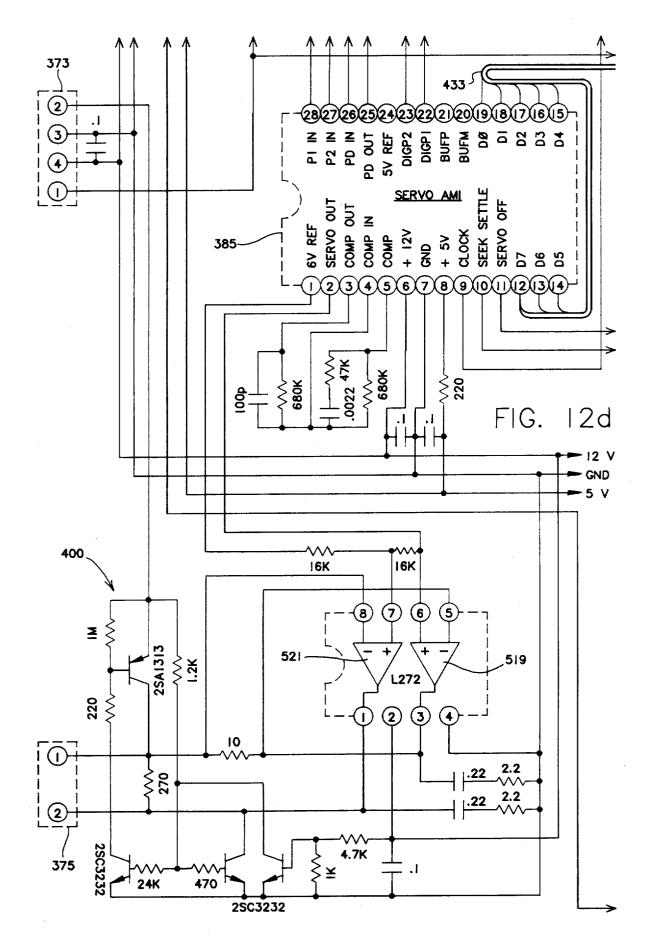

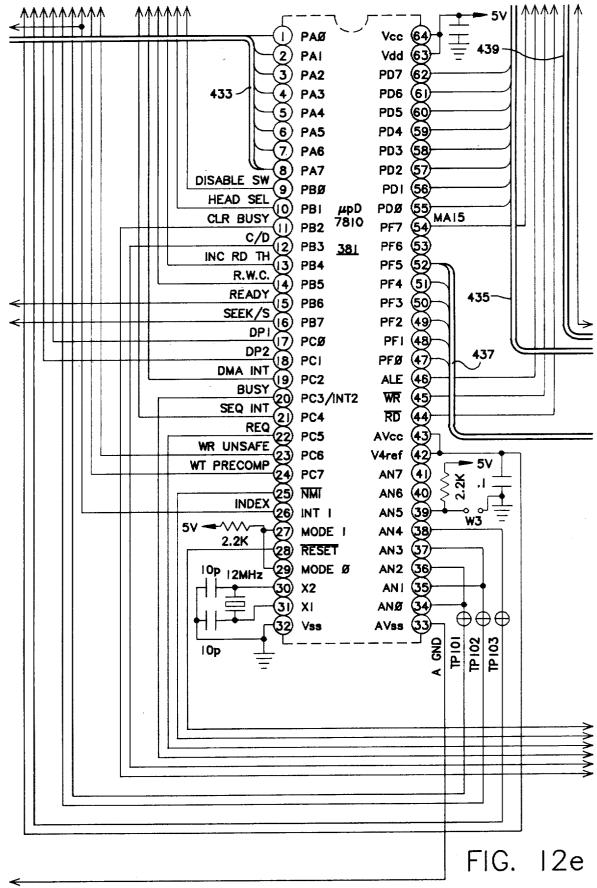

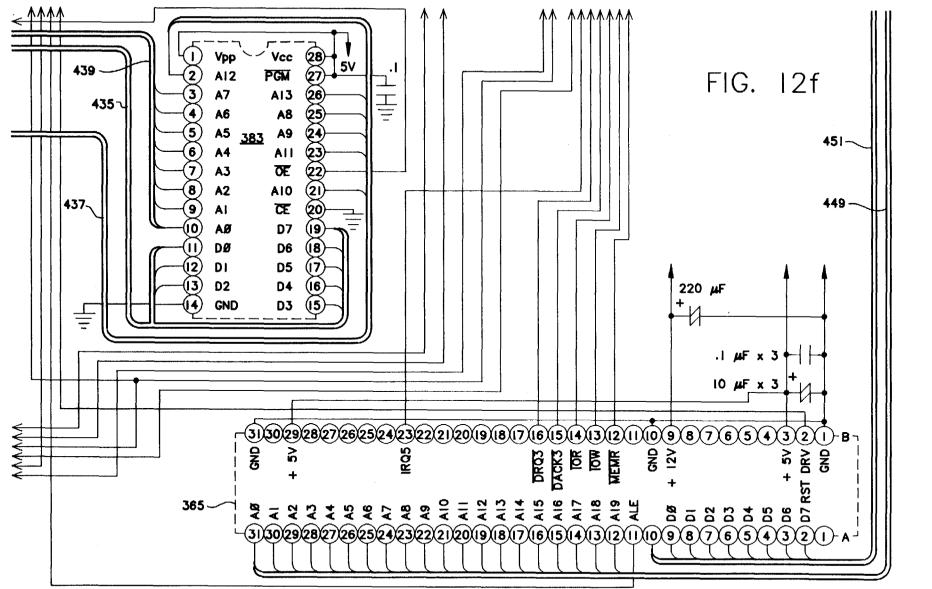

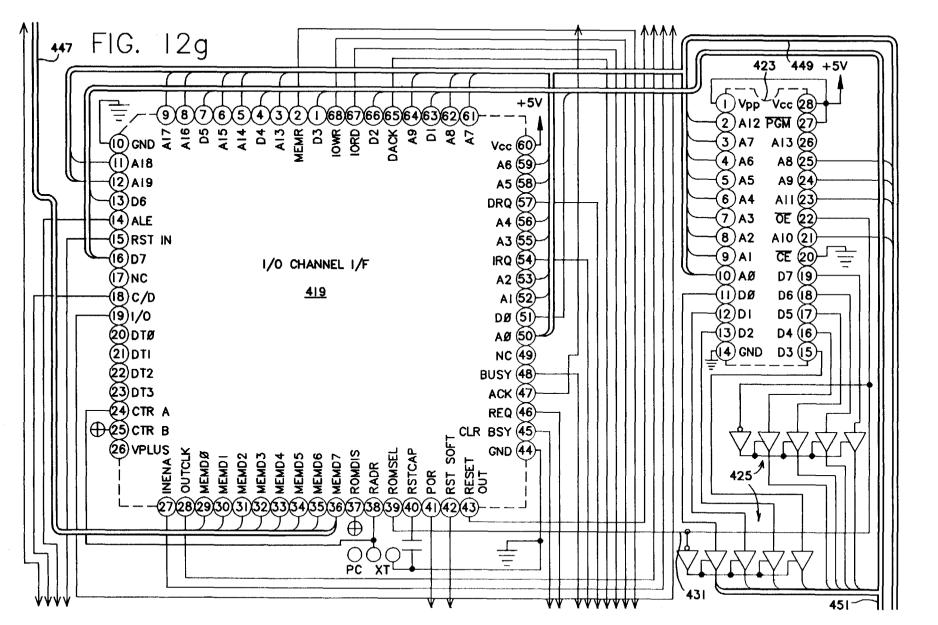

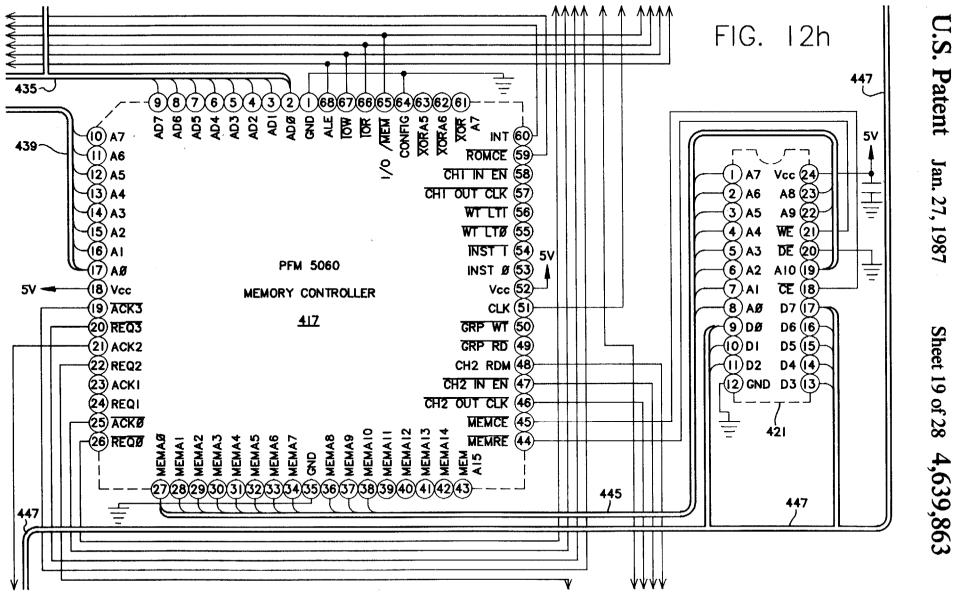

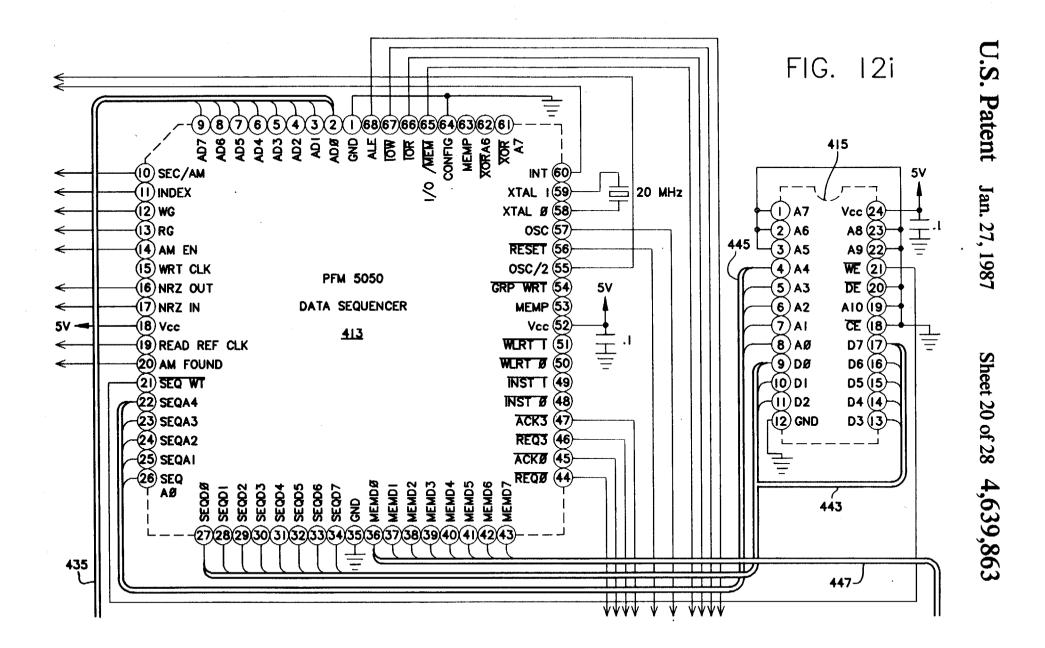

FIGS. 12a through 12i are nine sheets of drawing which together set forth a single electrical circuit schematic diagram of the electronics for the disk file subsystem depicted in FIG. 1. FIG. 12 is a layout plan for the nine sheets of FIGS. 12a through 12i, and explains how these sheets should be arranged together in order to provide the overall single electrical schematic.

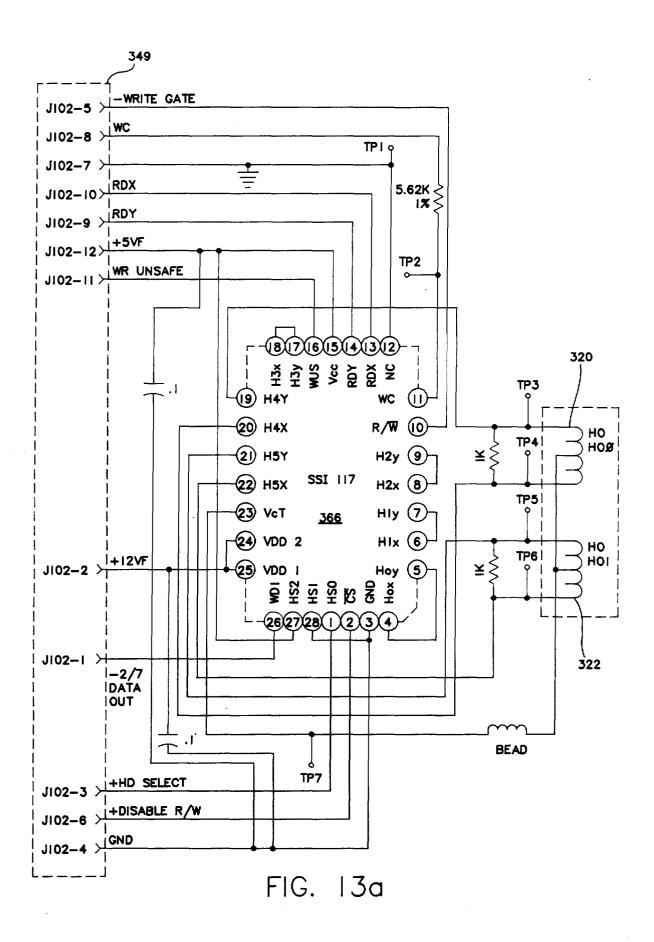

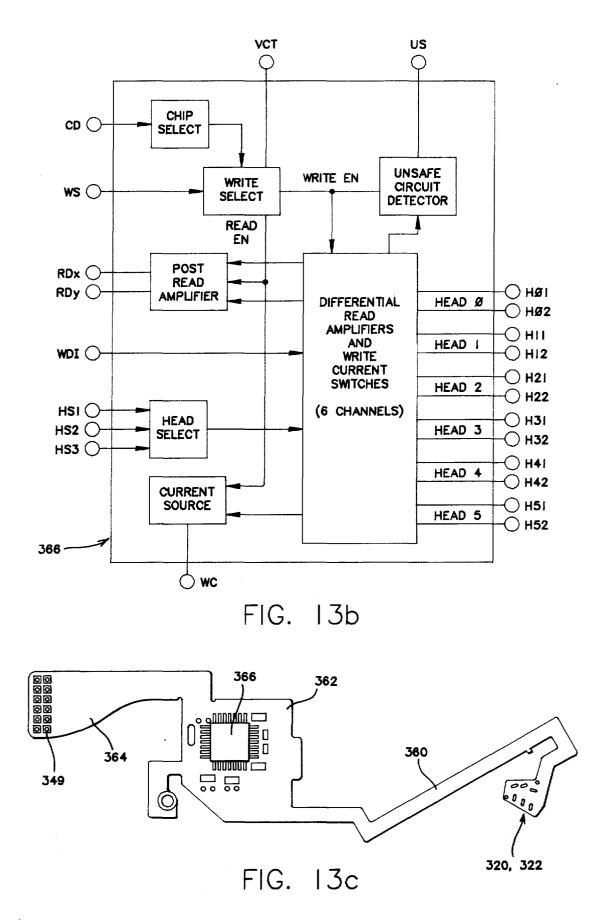

FIGS. 13A, 13B and 13C are respectively an electrical circuit schematic, a block diagram of a two channel monolithic read/write and head select circuit and a thin film flexible circuit substrate mounted within the head and disk assembly shown in FIG. 3, and which plugs into the read and write circuitry depicted in FIG. 12A.

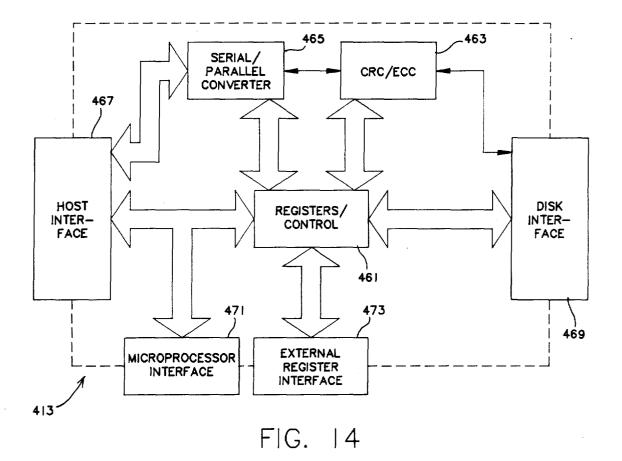

FIG. 14 is a detailed block diagram of the structure of a data sequencer included within the circuitry shown in FIG. 11.

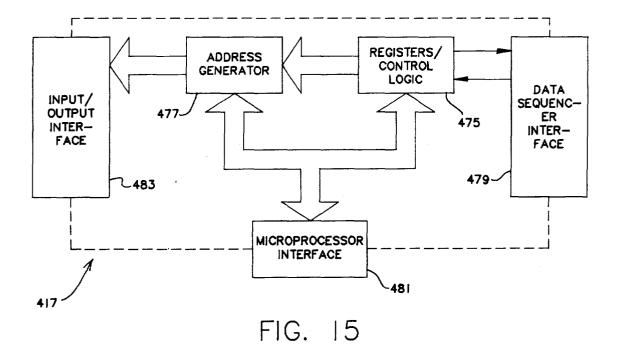

FIG. 15 is a detailed block diagram of the structure of 55 a memory controller included within the circuitry shown in FIG. 11.

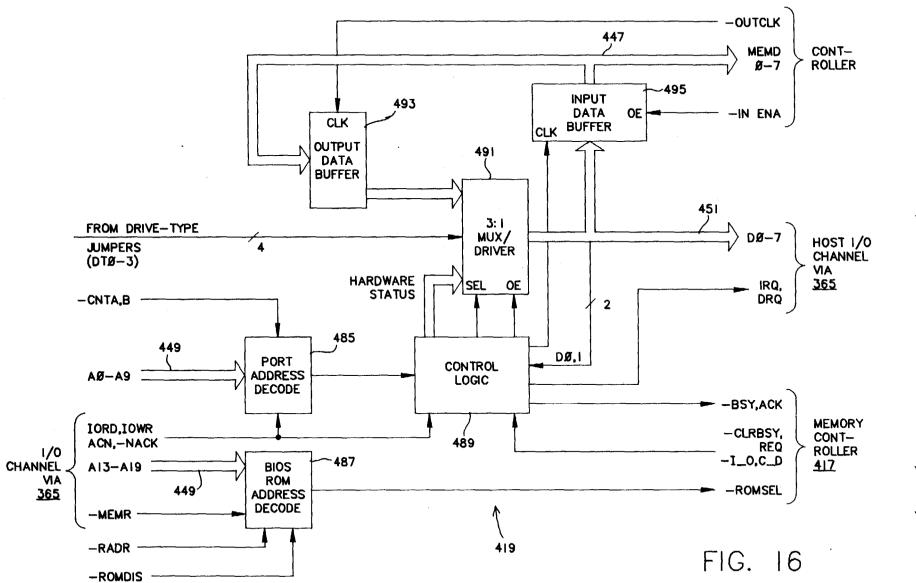

FIG. 16 is a detailed block diagram of the structure of an input/output channel interface included within the circuitry shown in FIG. 11.

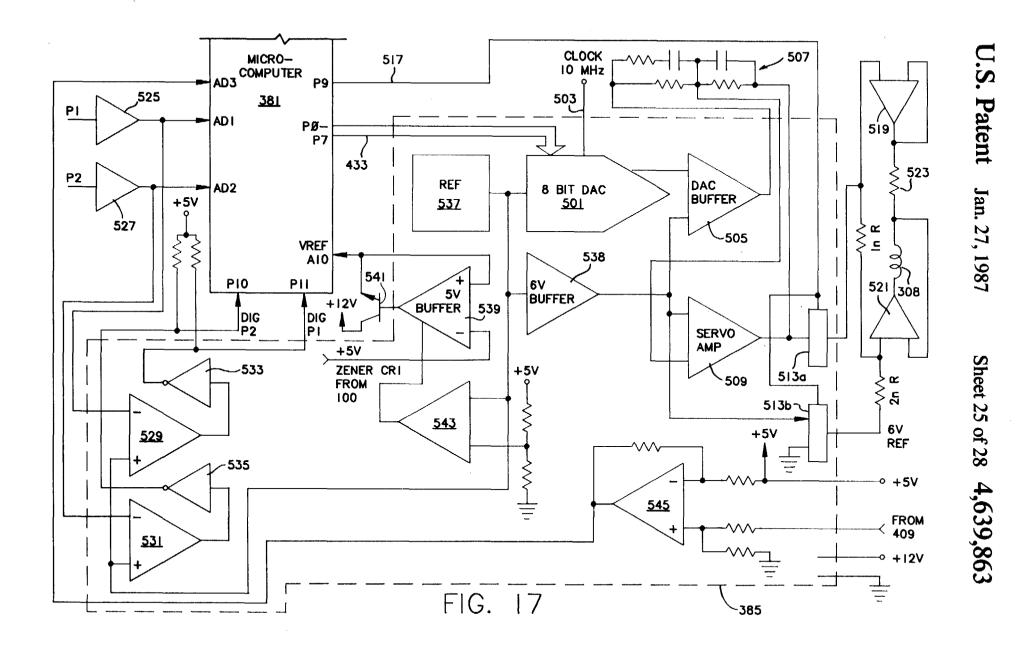

FIG. 17 is a detailed schematic and block diagram of the structure of an analog/digital servo circuit included within the circuitry shown in FIG. 3.

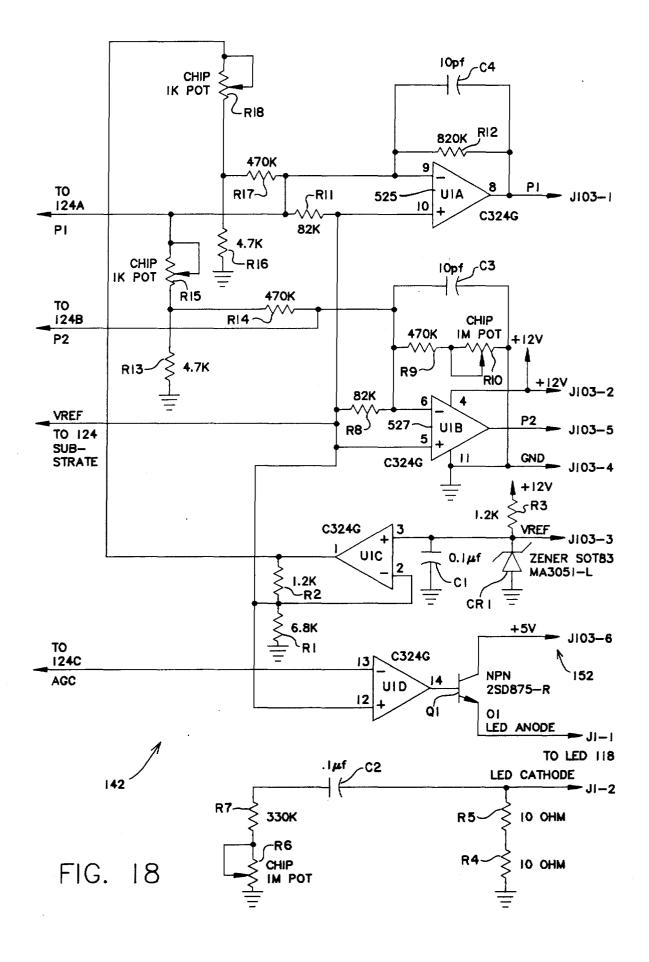

FIG. 18 is a detailed schematic diagram of an optical encoder circuit carried on the flexible circuit substrate depicted in FIG. 4.

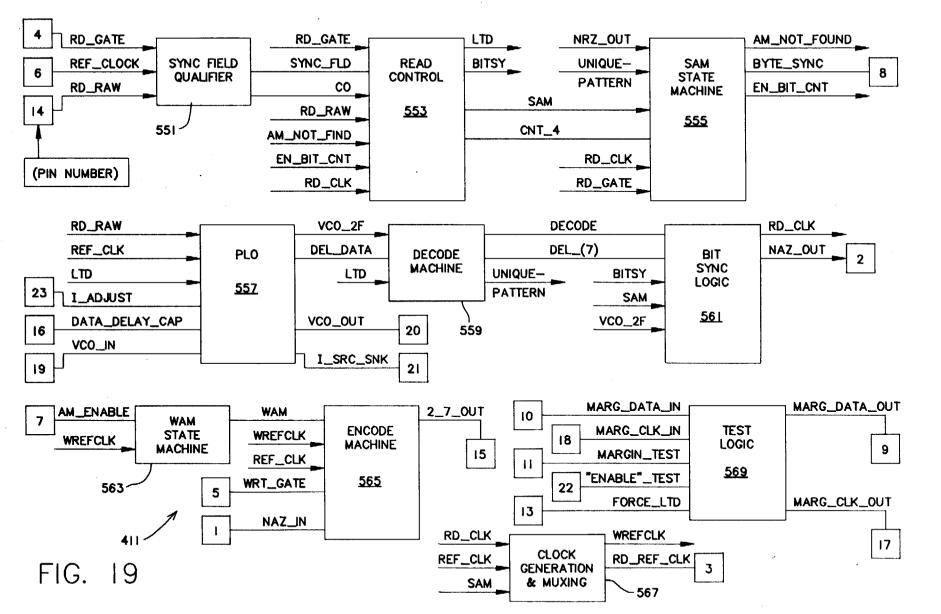

FIG. 19 is a detailed schematic and block diagram of a data separator element included within the circuitry shown in FIG. 11.

5

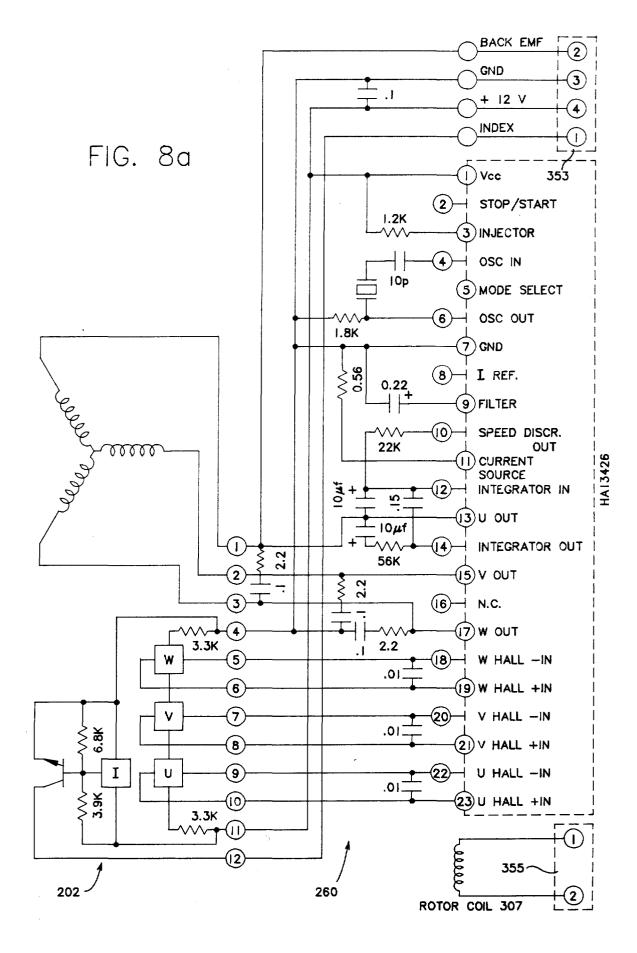

FIG. 20 is a diagram of track formatting followed in the disk file subsystem depicted in FIG. 1.

#### DETAILED DESCRIPTION OF A PREFERRED EMBODIMENT

As seen in FIGS. 1 and 2 a miniaturized rotating fixed disk data storage subsystem 5 includes in FIG. 1 a printed circuit card 6 carrying substantially all of the highly modularized and integrated electronic circuits required to operate the subsystem 5, and an elongated 10 frame 7 (shown in FIG. 1). The printed circuit card may be strengthened and elongated and be used as a supporting substrate 6a in lieu of the frame 7, as shown in FIG. 2. A mounting flange 8 formed as a part of the frame 7 (FIG. 1), or attached to the circuit card 6A by screws 15 (FIG. 2), enables the subsystem 5 to be mounted in and occupy a single accessory slot location of a single user computer, such as the IBM Personal Computer TM, for example and thereby achieve a direct plug-in electrical attachment thereto. 20

#### Head and Disk Assembly 10

A thin and compact head and disk assembly 10, depicted in detail in FIGS. 3-10 and discussed hereinafter, is attached to the frame 7 (FIG. 1) or to the printed 25 circuit board 6 (FIG. 2) via mounting hardware 9 which provides for some insulation of the assembly 10 from physical shocks to the host.

In FIG. 3, the assembly 10 is shown as including a housing 12, which functions to enclose, align, and/or 30 support all of the other elements included as part of the assembly 10. The housing 12 is preferably formed as a metal casting, such as of aluminum. The housing 12 may also be formed from stock by machining, and may also be formed by sintering of formed powdered metal, in 35 accordance with known technology. A continuous outer peripheral wall 11 and recesses 13 (FIG. 7) serve to reinforce the housing 12 and also to minimize the amount of material required in its fabrication.

A cover 14 attaches to the housing 12 via screws 15 40 and thereby encloses the interior thereof. A gasket 16 seals the interior of the housing 12 from the ambient, and prevents intrusion of foreign particulate material, such as dust, which would interfere with the operation of the assembly 10. A breather filter 17 enables the 45 pressure inside the housing 12 to equalize to exterior ambient. Two ports 18 are provided through the cover 14 to enable the interior to be purged of dust particles during the manufacturing operation. Seals 19 seal the two ports 18 after purging. 50

A micropore air filter 20 is mounted in one corner 21 of the housing 12 and filters internal air to remove any particulate contamination during operation.

The head and disk assembly 10 includes three major elements or subsystems: an optical encoder subassembly 55 100 described in connection with FIG. 4; a disk, spindle and direct drive spindle motor subassembly 200 described in connection with FIGS. 3 and 6–8, and a rotary actuator and motor subassembly 300, described in connection with FIGS. 3, 5, 6, 8, and 9. 60

#### **Optical Encoder Subassembly 100**

The encoder subassembly 100 includes three major parts. The first part is a moving scale 112 having alternating light translucent and opaque radial microlines 65 113. The scale 112 is mounted on a ledge 302 of a substantially planar rotary actuator frame 304 of limited angular displacement which is rotatably journalled to

the housing 12 as shown in FIGS. 3 and 5, and discussed hereinafter in greater detail. Thus, in this preferred embodiment the scale 112 is also of limited angular displacement, limited to a maximum of approximately thirty degrees of arc (30°).

The second part of the encoder 100 is a unitized encoder structure 114 comprising a light source holder 116 carrying an LED light source 118 and a mirror 120, a photocell array carrier 122 carrying and aligning a photocell array 124 and an overlying mask or reticle 126, a support bolt 128 having a widened circular head or table top 130 for mounting the light source holder 116 and the photocell array carrier 122 and having a threaded cylindrical shank 132. A wave spring washer 134 is interposed between the shank 132 and an annular machined plateau 136 surrounding a cylindrical opening formed through a bottom wall portion 138 of the housing 12. The cylindrical opening is sized to receive the shank therethrough in a freely rotating relationship. A 20 locking nut 140 threads onto the shank 132 after it is passed through the base portion 138 so as to secure the bolt 128 and the other elements it carries to the base portion 138. The photocell array 124 includes an upper photocell 124A, a lower photocell 124B, and an AGC cell 124C located between the two photocells 124A and 124B.

The LED light source holder 116 is secured to the support bolt 128 by screws 172 which pass through the holder 116, and also through the photocell array carrier 122 and into threaded openings 194 provided in the table top 130 of the support bolt 128, as shown in FIG. 4.

The photocell array carrier 122 includes a central well 123 in which the photocell array 124 is mounted. A small printed circuit board 186 is provided adjacent to a connection edge of the photocell array 124. Fine wires are then bonded between connection pads of the array 124 and corresponding traces of the circuit board 186. The reticle 126 is then directly mounted over the photocell array 124 in precise optical alignment, so that openings in the reticle 126, in cooperation with the radial microlines 113 of the scale 112, enable generation of polyphase incremental position electrical signals which are related to the position of the actuator frame 304 relative to the housing 12.

The threaded shank 132 of the bolt 128 passes through the housing at the location shown in FIGS. 3 and 7. The bolt 128 includes a slot 174 (FIG. 7) which enables the encoder assembly 114 to be rotated during final assembly and optical alignment in the housing 12. The nut 140 enables the assembly 114 to be locked at a precise height relative to the scale, by virtue of compression of the wave spring washer 134. The nut 140 includes two transverse grooves 176 at its threads. These grooves 176 enable the nut 140 to be glued effectively to the bolt 128 and to the housing 12 once proper alignment of the encoder and scale is achieved during the manufacturing process.

The third part of the subassembly 10 is an electronic circuit 142 which is preferably formed of electronic components secured to a flexible film printed circuit substrate 144. The substrate 144 is adapted to be placed inside the housing 12 adjacent to the encoder subassembly 100, in a well generally designated by the reference numeral 154 in FIG. 5.

The substrate 144 includes three integral flexible connection extensions, a first extension 146 enabling connection to the photodetector array 124 via the small circuit board by screws 156 at the locations indicated by the broken lead lines in FIG. 4. A second extension 148 extends to and enables connection of the circuit 142 to the LED light source 118, and a third extension 150 includes a suitable plug 152 for enabling direct overall 5 electrical connection of the subassembly 110 to the disk drive control electronics circuit card 6, 6a with which the head and disk assembly 10 may be used. This connection via the plug 152 is external to the housing 12, and the thin film extension 150 passes between the hous-10 ing 12 and the gasket 16 to the external connection location, with the electrical traces being adjacent to the insulating gasket 16 and with the mylar substrate being against the lip of the housing 12.

#### **Optical Encoder Circuit 142**

As depicted schematically in FIG. 18, an integrated circuit U1 contains four operational amplifiers U1A, U1B, U1C and U1D. The amplifier U1A is a current to voltage converter and has an inverting input connected 20 to the anode of the upper photocell 124A of the photodetector array 124, and the amplifier U1B is a current to voltage converter having an inverting input connected to the anode of the lower photocell 124B of the array. A negative feedback circuit comprising a capacitor C4 25 and a resistor R12 adjusts the frequency response and gain of the converter U1A, and a similar but adjustable network of capacitor C3 and series resistors R9 and R10 adjusts the frequency response and gain of the converter U1B. The resistor R10 is variable, so that the gain 30 characteristics of U1B may be made the same as those for the converter U1A.

A reference voltage Vref is derived from a 12 V supply bus from the host computer through a network comprising a series resistor R3 and 5.0 volt zener diode 35 CR1. The zener regulated 5.0 volts is applied to the non-inverting input of an operational amplifier U1C. A resistance network of resistors R2 and R1 provide at a common node a feedback path to an inverting input of the amplifier U1C and a reference voltage Vref which 40 connects to the common cathode substrate of the photodetector array 124 via a connector J2-2. The values of the resistors R1 and R2 establish the voltage present at the output of the amplifier U1C. This output voltage is supplied to two adjustable networks: the first network 45 comprising the resistors R16, R17 and R18 for controlling the operation of the converter U1A, and the second network comprising the resistors R13, R14 and R15 for controlling the operation of the converter U1B. Resistors R18 and R15 are individually adjustable so that the 50 electrical characteristics of the photocells 124A and 124B respectively may be individually controlled and equalized in terms of voltage output over the range of light to dark. These two adjustments R18 and R15 also enable each photocell 112, 114 of the polyphase encoder 55 100 to be trimmed to accomodate the particular gap between the scale 112 and the mask 126 without loss of current amplitude between the maxima of light and dark conditions at each photocell.

An automatic gain control (AGC) cell 124C of the 60 array 124 is connected to an inverting input of an operational amplifier U1D via a connector J2-31. The noninverting input of the amplifier U1D is connected to the Vref node. The output of the amplifier U1D is connected to a driver transistor Q1 which in turn supplies 65 current from a 5 volt bus of the host equipment to the anode of the LED light source 118. The cathode of the light source is connected through two current limiting

resistors R4 and R5 to ground. A series network of resistors R6 and R7, in combination with the current put out by the AGC photocell 124C controls the current put out by the operational amplifier U1D and actually applied to the LED through the driver transistor Q1. R6 is adjustable to control quiescent current through the LED 118.

#### Disk and Spindle Motor Subassembly 200

10 The disk and spindle motor subassembly 200 includes a very thin and flat direct drive, brushless spindle motor 202 which mounts in a well 204 of the housing 12 by three screws 205. The screws 205 pass through openings in a peripheral flange 206 of the motor 202 which 15 mates with a machined annular surface 208 adjacent to the open well 204. The lower surface of the flange 206 and the facing surface 208 of the housing 12 are machined, so that the motor 202 is thereby sealed in an airtight arrangement with the housing 12.

The motor 202 includes a rotating hub 210 which has a lower flange 212. A data storage disk 214 mounts over the hub 210 and against the flange 212. The flange 212 has a height adapted to align the data disk 214 properly within the interior of the housing 12. The disk 214 is coated on both major surfaces with a magnetic storage material such as a ferrous oxide or plating and provides the storage medium of the compact head and disk assembly 10. In the preferred embodiment, the disk has a diameter of approximately 95 millimeters, and has the capability of easily storing in excess of ten million bytes of formatted data.

An airflow generator disk 216, preferably formed of a low-mass plastic material, attaches to the top of the hub 210 by a single axial locking screw 218. Storage capacity may be doubled by replacing the airflow generator disk 216 with a second magnetic media data storage disk 215 and by adding additional data transducers and support arms to the rotary actuator assembly 300. A second data storage disk 215 is shown diagramatically in FIG. 11. Two opposed peripheral openings 220 through the disk 216 align with two openings 222 on the top of the hub 210. A spanner wrench is used to prevent the hub 210 from rotating while the screw 218 is tightened. The spanner wrench is provided with two pins aligned with the openings 220 and 222. The pins pass through the openings 220 and 222 and thereby align the top disk 216 and the hub 210 as the screw is locked into place. A spacer 213 between the top disk 216 and the data disk 214 locks the data disk 214 against the lower flange 212.

The top surface of the spindle motor 202 includes a recessed and shielded region 224, in which an electromagnetic shield is placed, in order to prevent contamination of data stored on the lower surface by the electromagnetic fields generated inside of the motor 202.

As seen in FIG. 5, an aerodynamically released shipping latch 230 is rotatably mounted on a vertical post 232 (FIG. 3) in the housing 12. A vane 234 and flag 236 of the latch 230 are deflected by airflow generated by clockwise rotation of the disks 214 and 216. The airflow is sufficient to overcome the force exerted by a bias spring (not shown) which urges the latch 230 in a clockwise direction. A notch 238 provided in a counterweight 306 of the rotary actuator 300 is engaged by a finger 240 when there is no rotation of the disks 214 and 216 (and no airflow). This arrangement latches the rotary actuator 300 into a landing zone position.

When power is removed from the head and disk assembly, the counter electromotive force generated by

rotation of the spindle motor 202 in response to the inertia stored in the motor 202, spindle 210 and disks 214, 216, is automatically applied to the rotary actuator 300 in order to return the actuator to the landing zone position before disk rotation ceases and the aerody- 5 namic latch 230 is no longer deflected by airflow. This electronic return spring feature is described hereinafter, in connection with the electrical circuit elements.

One important requirement for the head and disk assembly 10 is that the spindle 210 be effectively 10 grounded to the frame. Ordinarily, an electrical brush makes contact between the spindle shaft and the housing external to the motor. However, such arrangement adds significantly to the height of the motor and to the overall thickness of the head and disk assembly. Thus, it 15 has been discovered that a grounding mechanism 250 (FIG. 6) may be placed entirely within the spindle shaft 252 of the motor 202.

The preferred mechanism includes a spring loaded ball or tip 254 inside the hollow spindle shaft 252. The 20 tip 254 is of conductive material, such as a carbon impregnated plastic resin material, and it makes direct contact with a pad 256 of highly conductive hardened material such as stainless steel which is fixed and connected to the stationary enclosure 258 of the motor 202. 25 and in the planar dimension relative to the frame 304. The enclosure 258 is grounded to the housing 12 at the peripheral flange 206 by the screws 205.

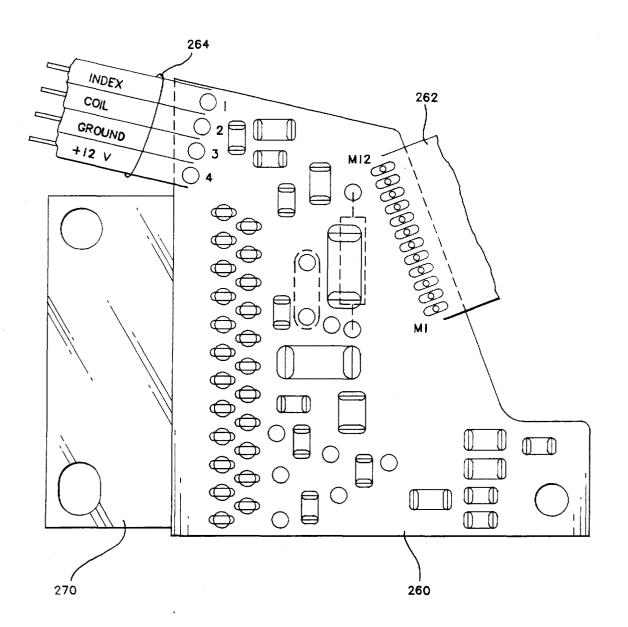

One important aspect of the present invention is that the electronic circuitry required to drive the multiple windings of the spindle motor 202 be sinked directly to 30 the housing. The arrangement shown in FIG. 7 makes direct heat sinking of the driving circuitry to the housing 12 possible. In FIG. 7, a small printed circuit module 260 plugs into a cable 262 from the motor 202 and also plugs into the circuit board 6 externally of the head 35 and disk assembly 10 via a cable 264 disposed in a channel 266 formed in the back of the housing 12.

An integrated circuit motor driver 268 such as type HA13426 supplied by HITACHI America, Ltd., Chicago, Ill. 60006 having its pins connected to the circuit 40 board 260 as shown in FIGS. 7 and 8A, includes a flange 270 which is directly mounted to the back of the housing 12 in a well 272 formed in the housing with a sufficient depth from the lower surface profile in order to hold the circuit board 260 and its components (FIG. 45 8B) most of which are located on the underside of the board 260. Screws 272 secure the heat sink flange 270 of the integrated circuit directly to the housing 12 inside the well 272.

The circuitry for the three phase motor 202 is de- 50 picted in FIG. 8A, which indicates that the motor is Y wound and generates three phase commutation signals by three Hall effect generators U, V, W responsive to a small permanent magnet disposed in the rotating permanent magnet in the armature of the motor, as is conven-55 tionally known and understood. A fourth Hall effect transducer I generates and puts out a once per revolution index signal which is ultimately supplied to the control electronics external to the head and disk assemblv 10.

A bottom or inside plan view of the modular circuit board 260 (FIG. 8B) indicates one acceptable form of layout for the discrete components on the circuit board 260, in which all but two of the discrete components are mounted between the printed circuit board and the 65 facing bottom wall of the housing 12. This arrangement protects these components from physical harm, and it enables ready attachment of test equipment should trou-

bleshooting of the circuit carried on the module 260 ever be required. Also, the cables plug into the circuit module 260, enabling it to be removed and replaced very easily, without disturbing any other circuitry, and without any need to enter the dust-free housing 12.

#### Rotary Actuator Subassembly 300

The third major subassembly of the head and disk assembly is a very flat and thin rotary actuator subassembly 300, depicted in various levels of detail in FIGS. 3, 5, 6, 7, 9 and 10. As already mentioned, the actuator 300 includes a planar frame 304, preferably formed of cast or stamped aluminum. The frame 304 includes four regions. The region 302 for supporting the scale 112 of the optical encoder 100 has already been discussed.

A second region of the frame 304 is for aligning and supporting a triangular electromagnetic coil 307 of a single winding 308 whose two ends are connectable at connection pins 310. The coil 307 is wound on a bobbin and is then integrally molded to the frame 304 with a suitable molding compound 311. Regions 312 denote holes passing through the frame 304 which are filled with potting material during the molding process, so that the coil 307 may be precisely aligned both radially

A third region of the frame 304 provides a support extension 314 for two arms 316, 318 supporting respectively two oppositely facing "flying head" data transducers 320, 322 which are disposed in proximity to the two major, data storage surfaces of the data disk 214, as shown in FIG. 6. During rotation of the disk 214, the transducers 320, 322 ride or "fly" upon an air bearing in very close proximity to the data surface in accordance with what is known as "Winchester" technology.

The fourth region of the frame 304, already mentioned, supports the counterweight 306, whose mass is selected to counterbalance the other regions of the frame 304, and also to cooperate with the aerodynamically released shipping latch 230, also previously explained. The counterweight 306 is attached to the frame 304 by screws 309.

The actuator frame 304 includes a central opening 301 which reduces its mass and inertia, and which provides a convenient location for a single crash stop post 313 which is adapted to engage oppositely facing surfaces 315, 317 formed on the inside walls of the frame 304 which define the opening 301. The post 313 is press fit into a suitable opening 319 in the housing 12. A cylindrical rubber gasket 321 slips over the post 313 and dampens the impact of the frame 304 upon the post 313. The crash stop post 313, in combination with the arc length between the surfaces 315, 317, limits the displacement of the actuator 300 to a predetermined maximum. This limitation of displacement is essential to prevent the transducers from coming off of the data disk 214, and from crashing into the lower flange 212 of the spindle hub 210.

A rotary actuator spindle includes a fixed shaft 324 mounted upwardly from the housing 12. A washer 326, 60 a lower bearing 328, a spacer 330, a wave spring washer 332, an upper bearing 334 and a locking washer 336 and screw 338 all cooperate to provide a freely rotating journal for the actuator frame 304. These elements are mounted and contained in an axial cylindrical opening 340 provided through the frame 304 and enable the frame 304 to move across an arc of approximately thirty degrees and thereby move the transducers radially across the data surfaces of the data disk 214 so that each of the multiplicity of concentric data tracks formed on each data surface of the disk 214 may thereby be accessed by operation of the rotary actuator 300.

A lower flux-return magnet plate 350 carrying a lower permanent magnet 352 is mounted to the housing 5 12 by screws 353; and, an upper flux-return magnet plate 354 carrying an upper permanent magnet 356 is mounted to the housing 12 by screws 357. As seen in FIG. 10, the coil 307 is disposed between the two oppositely facing permanent magnets 353 and 356. 10

Each magnet 352, 354 is magnetized to have two regions of pole reversal. The magnetic poles are at the major surfaces of the magnets 352, 354, and are complementary with each other so that a very strong flux region exists in the gap between the two opposed faces<sup>11</sup> of the two magnets 352 and 356 (FIG. 10). A polar reversal region 358 generally bisects each magnet 352, 354. This is so that the effect of the flux on e.g. the left side (FIG. 10) on the coil 307 with current passing through its adds to the effect of the flux on e.g. the right side, since current will be passing through the single winding 308 in one direction only.

#### Head Select and Amplifier Circuitry

A thin, highly flexible mylar circuit connection film 360 is provided for direct connection to the data transducers 320, 322. This elongated, highly flexible and durable connector film 360 extends from a larger flexible mylar printed circuit 362 which is preferably mounted on the upper flux return plate 354 and which carries some of the read and write drive circuitry and head select circuitry required for operating the transducers 320, 322. A plan view of the circuit 362 is depicted as FIG. 13C. A connection extension 364 for the 35 mylar circuit 362 extends outwardly from the drive between the gasket 16 and the upper face of the peripheral wall 11 along the same lineal edge thereof as passes the connection portion 150 for the optical encoder subassembly 100. The electrical circuit diagram of circuit 40 elements and connections for the circuit carried by the film is depicted FIG. 13A. Therein, a monolithic integrated circuit 366 provides a six channel (six head transducer) head select and amplification function (FIG. 13B). Only two head select channels, H4 and H5, are 45 active in selecting between the heads 320. 322 of the subsytem 5 (see FIG. 13a); if an additional data storage disk 215 is used, then four channels are active in the head select operation. This circuits 366, is preferably a type SSI 117, made by Silicon Systems Incorporated, or 50 equivalent.

#### Circuit Card 6

Four flexible circuit substrates extend from the head and disk assembly 10. These substrates may be conduc-55 tive traces formed upon thin, flexible mylar film, or they may be thin and flat wire cables. In any event, one leads to a jack 349 for connecting internal head read/write electronics with an external read/write channel, another leads to the jack 152 for connecting the optical 60 encoder subassembly 100 with an external analog/digital servo element, another leads to a jack 353 for connecting the spindle motor control module 260 with the circuit board 6 circuitry, and a final one 355 leads from the coil 307 of the rotary head positioning actuator 300 65 within the head and disk assembly 20 to external drive electronics, being part of the analog/digital servo element.

The small double sided printed circuit card 6 carries all of the electronics required for the control system of the present invention (except for the circuits within the head and disk assembly which have already been mentioned).

The circuit card 6 includes a conventional edge connector region 365 having properly aligned connection traces 367 for engaging corresponding contact pins of an accessory or peripheral circuit card connector of the system board or mother board of the personal computer (host system) in which the storage subsystem 5 is installed and connected solely via the traces 367 on the edge connector region 365.

Four plugs 369, 371, 373 and 375 are provided on the 15 circuit card for receiving respectively the jacks 349, 152, 353 and 355, previously described. These plugs enable the circuitry inside the head and disk assembly 10 to extend to and be connected to the circuitry carried on the circuit card 6 and to be supplied with power 20 from the host system via the edge connector 365.

#### **Electronics Overview**

The following major circuit elements are contained on the printed circuit card 6 generally in the positions 25 indicated in FIGS. 1 and 2. (These circuit elements are interconnected in accordance with the architectural overview of FIG. 11 and in accordance with the detailed connection diagram made up of FIGS. 12*a* through 12*i*, as arranged and read together in accor-30 dance with the FIG. 12 layout plan.

#### Microcomputer 381 and Program Memory 383

A single programmed, sequential state monolithic microcomputer 381, sometimes referred to as a "microprocessor", provides overall control of the subsystem 5. The microcomputer 381 is preferably a type 7810, manufactured by NEC Corporation, of Japan, or equivalent. The microcomputer 381 includes a single central processing unit (CPU) and a single arithmetic logic unit (ALU), as well as other internal supporting architecture. It executes only one instruction at a time.

The type 7810 is a single chip, five volt, eight bit microcomputer including an internal analog to digital converter having eight multiplex-selectable analog inputs. The analog to digital converter operates continuously by converting whatever voltage appears at a selected input into a digital value which may be read at any time by the microcomputer 381 under program control.

The microcomputer 381 also includes a 256 by eight bit RAM, multifunctional timer/event counters, general purpose serial and parallel interfaces and input/output ports, and maskable and non-maskable interrupt capability. The microcomputer 381 may also control external memory directly, and requires an external program memory for containing the instructions which it is to execute in carrying out the supervisory functions of the control system of the present invention. Each instruction cycle requires one microsecond, and the basic clocking frequency for the microcomputer 381 is 12 MHz. The software controlled functions of the microcomputer 381 are discussed in greater detail subsequently herein.

The microcomputer 381 utilizes a multiplexed bus structure, so that the same electrical lines may carry both address information and data information, at different times. These times alternate, so that in one machine cycle, a bus may be carrying addressing information, and at the next cycle, the same bus may be carrying data information, and so forth.

The 256 byte random access memory within the microcomputer 381 is used as a stack and provides all of the general purpose registers required for operations of 5 the microcomputer.

An eight kilobyte external read only program memory 383 is connected to the microcomputer 381, and it contains the instructions which the microcomputer 381 will execute during operations of the disk file subsystem 10 331. These instructions are presented as a listing at the end of this specification.

The microcomputer 381 is the heart of the control system and has two overall tasks: it supervises and controls radial head position via an electromagnetic voice 15 coil actuator 300 of the head and disk assembly 10 via servo control loops, and it responds to commands from the host computer system by initiating and monitoring transfers of blocks of data to and from the host and the disk data storage surfaces via the controller/interface. 20

It is important to remember that throughout the data read/write operations and data transfer operations the microcomputer 381 is monitoring the progress of such operations and it is simultaneously controlling the track servoing the heads 320, 322 at the centerline of the track at which data is being read or being written.

## Track Positioning and Following Servos

The subsystem servo performs two functions: First, it 30 must hold read/write data transducer heads in alignment with the centerline of each data track during track following operations. Second, it must be able to perform track seeking operations which cause the heads 320, 322 to be moved rapidly and accurately from a 35 known departure track location to a desired destination track location. All servo operations are controlled and supervised by the microcomputer 381 which controls the current which passes through the coil 308 of the voice coil actuator 300.

An analog/digital servo circuit 385 is connected to the microcomputer 381, and the circuit 385 provides circuit elements which are required to carry out servo control loop functions in data track seeking and track following operations of the head and disk assembly. 45 integrated circuit includes a flange which is directly This monolithic circuit 385 is explained in greater detail in conjunction with FIG. 18 hereinafter.

The optical encoder assembly 100, previously described, responds to relative light levels indicative of position of the scale 112 and converts the light levels 50 manent magnet in the armature of the motor 202, which into two phase signals P1 and P2 which are in phase quadrature. These phase signals are converted to voltages by the current to voltage converters U1A and U1B of the assembly 142 and are then supplied to the analog to digital converter within the microcomputer 381, via 55 out a once per revolution index signal on an index line. the analog/digital servo chip 385. The circuitry of the encoder is set forth and discussed herein in greater detail in conjunction with FIG. 18.

The analog/servo chip 385 and related circuitry converts digital position values to driving currents and 60 tem 31 out of service in the event that disk rotation is applies these currents through driving circuitry 390 to a winding 308 of the rotary actuator 300, symbolized in FIG. 11 by the broken line carrying reference numeral 300 and interconnecting a symbolic data transducer head 320, and the moving scale 112. The direction and 65 its amplitude value is sampled and sent to and digitized magnitude of current passing through the coil 308 determines the direction and velocity of the head 320 in moving among concentric data tracks formed on the

data storage major surface of the data storage disk 214. The servo circuit 385 is described hereinafter in greater detail in connection with FIG. 17.

#### Storage Disk 214

The disk 214 (and 215 in a 20 megabyte version of the subsystem 5) includes two major data storage surfaces 214a and 214b coated with a suitable magnetic data storage material. Each data storage surface provides storage room for a multiplicity of concentric data storage tracks, there being some 612 logical tracks available per data surface. Some 24 additional spare tracks are provided at the outer periphery of the disk surface 214a, 214b to be used in place of tracks having media defects so that the first tracks required by the host's operating system for directory purposes will be free of defects, and thereby be reliable in all cases.

An inner landing zone region LZ is provided so that the ferrite slider head 320, 322 comes into actual contact with its underlying data surface 214a, 214b, and subjects it to possible abrasion only in the landing zone region LZ. Each concentric data track nominally holds approximately 10,416 bytes, and is divided into eighteen data sectors, seventeen of them being for storage of following head position servo loop so that it is tightly 25 useful data and one of them being held in reserve in the event that a media defect renders any one of the other seventeen unusable. Each data sector contains approximately 568 bytes, including 512 bytes of useful data and the remainder being sector address headers, error correction, speed tolerance gap fillers, etc.

An index marker 399, generated by motor driver circuitry 260 controlling the spindle motor 202, marks the location in time for a narrow, approximately 200 microsecond, 130 byte wide, single servo sector 401 prerecorded with track centerline information for each data track upon one or more data storage surfaces 214a, 214*b* of the disk 214.

The disk 214 rotates at a substantially constant angular velocity, and the time period for each revolution is 40 nominally 16.67 milliseconds. The motor driver circuitry is illustrated in FIG. 8A and includes an integrated circuit motor driver, such as type HA 13426, provided by Hitachi America, Ltd., 707 W. Algonguin Road, Arlington Heights, Ill. 60006, or equivalent. This mounted to the base casting 12 for the head and disk assembly 10. The spindle motor 202 is Y wound and it generates three phase commutation signals by Hall effect transducers U, V and W responsive to a small perare used by the integrated circuit to generate the necessary phases to drive the motor 103, as is conventionally known and understood.

A fourth Hall effect transducer I generates and puts The microcomputer 381 monitors the index line from the motor control 105 and times the interval between each index marker 99 to be sure that the disk 96 is rotating at proper angular velocity, and it takes the subsysdetermined to be improper.

Two radially offset, time staggered bursts are provided for each concentric data track within the servo sector 401. The transducer 320 reads the first burst and by the microcomputer 381. The transducer 320 then reads the second burst and its amplitude value is sampled and sent to and digitized by the microcomputer

381. Differences in the digitized amplitude values are used by the microcomputer 382 to calculate centerline offset correction values which are stored and combined with a digitized phase value and sent to the coil 308 in order to maintain the head 320 in centerline alignment <sup>5</sup> with each track during track following operations.

The 612 tracks are divided into five contiguous zones, there being four zones of 128 tracks each and one zone of 100 tracks each. Track centerline data is acquired and stored for the tracks of each zone, and this data is used for initial correction whenever the actuator has placed the head **320**, **322** at a track within the zone. A zone timer is set for each zone, and times out after a predetermined interval, requiring that new centerline information for the zone be obtained before read/write operations will be permitted. These architectural features and operations of the fine servo loop and track zones are explained in further detail in the referenced U.S. Pat. Nos. 4,396,959, 4,419,701 and 4,516,177, the disclosures 20 of which are hereby incorporated by reference into the specification at this location.

# Electronic Return Spring 400

The aerodynamically released spring biased shipping <sup>25</sup> latch **230**, already described structurally above, is deflected by airflow generated by rotation of the disk **214**. This latch **230** includes a member which engages the rotary actuator **300**, thereby locking the heads **320**, **322** at landing zone positions over the landing zone LZ <sup>30</sup> whenever disk rotation is insufficient to generate an air bearing effect upon which the heads "fly" (in accordance with well-known Winchester technology).

In order to be sure that the actuator 300 returns the 35 heads 320, 322 to the landing zone LZ, an electronic return spring, symbolized by the switch 400 in FIG. 11 is provided in the subsystem 5. When power is lost or intentionally removed from the subsystem 5, this fact is sensed, and the operation of the spindle motor 202 is 40 reversed: i.e. it becomes a generator, and the electrical energy it generates, due to the kinetic energy stored in the rotating disk 214, is switched to the coil 308 of the rotary actuator 300. So long as there is disk rotation, the electrical energy generated thereby is sufficient to re- 45 turn the head to the inner landing zone LZ of the disk 214 and keep it thre so that the spring-biased latch 230 reengages the actuator 300 and thereby retains the heads 320, 322 at their inner landing zones LZ. The dynamics of the latch 230 and the electronic spring  $^{50}$ return 400 are designed so that the heads 320, 322 are returned to the landing zones LZ in good time before the latch 230 reengages.

Further details of the aerodynamic shipping latch 98 are set forth in the referenced co-pending U.S. patent application Ser. No. 06/728,674, filed on Apr. 29, 1985, for Aerodynamic Latch for Disk File Actuator.

A significant feature provided by the combination of the aerodynamic latch 230 and the electronic return 60 spring 400 is that the bias force applied to the actuator by a conventional mechanical return spring (and which must be continuously overcome during disk file operation) is eliminated completely. This means that the actuator 300 operates with significantly less power con-65 sumption, a consideration to be made when drawing all of the power for the subsystem 5 from the accessory socket of the personal computer host system.

# 16

# Read/Write Channel

The overall read/write channel includes a head select and preamp circuit 366 which is carried on the flexible 5 circuit substrate 362 within the head and disk assembly 10 and which is described herein in connection with FIGS. 13A, 13B, and 13C. The channel also includes read/write electronics 409 schematically illustrated in FIG. 12A, and a data separator 411. The data separator 10 411 encodes and decodes the data bits to and from an encoding format, such as 2,7 code, which is used in the actual record and playback process on the disk 214. The data separator 411 is described further in connection with FIG. 19.

#### Controller/Interface

The controller/interface of the control electronics for the disk file subsystem 5 includes a programmable data sequencer 413 having its own data sequencer random access memory 415, a memory controller 417, an input/output data random access memory 421 addressed by the memory controller 417 and temporarily storing data from the data sequencer 413 from an input-/output channel interface 419.

A BIOS (basic input/output system) read only memory 423 is associated with the input/output channel interface 419, and it contains basic input output program routines which are accessed and executed directly by the host CPU whenever its operating system wishes to make use of the subsystem 5. Actually, the BIOS memory 423 is not required for operation of the subsystem 5, and its inclusion is a matter of convenience for the user, thereby enabling the subsystem 5 to be plugged directly into a personal computer host system without requiring the user to add any software driver routines to the operating system which are needed in order to use the subsystem 5.

The BIOS memory 423 may also include a collection of error and status condition routines which are used by the operating system of the host system to determine and indicate to the user the status and/or error condition of the disk file subsystem 5 from time to time. An eight bit tri-state bus driver 425 is interposed in a data bus between the BIOS ROM 423 and the input/output channel interface 419 and edge connector 365 so that the BIOS program routines from the ROM 423 may be transferred via the host bus to the host CPU and executed whenever the operating system addresses the BIOS memory 423.

#### System Buses

A control bus 431 extends throughout the printed circuit card 6. This bus, shown symbolically in FIG. 11 as a single line, is actually many different lines. Not all lines extend to all elements. For purposes of convention, unless a bus line is a data bus or an address bus, it is considered to be a control bus line. Thus, the data and address buses shown symbolically in FIG. 11 for ease of understanding and in more detail in FIGS. 12A, 12B, 12C, and 12D, define by omission each of the lines making up the overall control bus.

An eight bit undirected data bus 433 enables the microcomputer 381 to send digital actuator control values to the analog servo chip 385. Digital data passes over the bus 433 from the microcomputer 381 to the analog servo 385 wherein it is converted to analog values and sent to control the position of the rotary actuator 300 during track seeking and following operations.

An eight bit time multiplexed data and address bus 435 interconnects the microcomputer 381, the program memory 383, the data sequencer 413 and the memory controller 417.

A six high order bit (A8-A13) address bus 437 inter- 5 connects the microcomputer 381 and the program memory 383. The low order eight address bits (A0-A7) for the program memory 383 are sent by the microcomputer 81 over the data/address bus 435 during address time to the memory controller 417 where they are 10latched and held in order to be sent over an address bus 439 to address the program memory 385.

A five bit address bus 441 and an eight bit data bus 443 interconnect the data sequencer 413 and its dedicated small random access memory 415, which stores at  $^{15}$ most only 32 bytes.

The input/output random access memory 421 is addressed via an eleven bit address bus 445 from the memory controller 417, while an eight bit data bus 447 connects the data sequencer 413 and the input/output chan-20 nel interface 419 with the buffer memory 421. The buffer memory 421 provides temporary input/output data storage and functions as a sector buffer, holding a maximum of two sectors of data which are in the process of being stored or retrieved from a data surface 25 214a or 214b of the disk 214, in addition to all status and control information which passes between the host and the subsystem 5.

A thirteen bit address bus 449 extends between the 30 edge connector 365, the BIOS ROM 423 and the input-/output channel interface 419; and, an eight bit data bus connects the BIOS ROM 423 with the interface 419 and edge connector 365 via the tri state bus driver 425.

### Data Sequencer 413

The data sequencer 413 is a monolithic large scale integrated circuit containing seven internal functional blocks, as shown in FIG. 14. These blocks include a registers/control logic block 461. This block 461 con- 40 tains 32 eight bit internal control registers and associated control logic. The registers may be individually written to initialize the paramaters that control data transfer, and individually read by the microcomputer 381 in order to obtain status information about se- 45 quencer command execution. This block 461 includes disk address registers for storing cylinder, head and sector identification data, status, etc., for the data block to be handled. The microcomputer 381 issues commands to the sequencer 413 by writing to these regis- 50 ters

An error correction code/cyclic redundancy check logic block 436 generates and checks error correction code (ECC) or cyclic redundancy check (CRC) bytes appended to the data and identification fields respec- 55 tively of each sector. This block enables use of either a standard CCITT 16 polynominal CRC or a programmable ECC. The particular polynomial may be up to 64 bits long and is determined at initialization time by values written into the registers/control block 461. 60

A serial/parallel conversion block 465 enables parallel data from the host to be serialized for the disk. This logic is implemented with high speed shift registers which effect the necessary format translation between parallel and serial data. 65

A host interface block 467 connects the sequencer to the buffer memory 421 via the data bus 447. The DMA memory controller 417 provides the addresses in the buffer memory 421 to which the data is to be transferred via the address bus 445.

A disk interface block 469 provides logic to generate and receive control signals such as read gate, write gate, address mark enable, etc., and it also passes the serial data to and from the disk via the data separator 411 and the read/write circuits 409 and 407.

A microprocessor interface 471 enables the microcomputer 381 to read and write the internal control registers of the block 461 to control operations of the sequencer 413 and to monitor its status.

An interface 473 to the external random access memory 415, via the address bus 441 and the data bus 443 provides access to 32 format parameter registers. These format parameter registers specify the size and content of the fields within each data sector on the disk. There are two registers for each field. One specifies the number of bytes in the particular field, and the other specifies the actual value contained in that field.

A monolithic integrated circuit, product code OMTI PFM 5050 Programmable Data Sequencer, available from Scientific Microsystems, Inc., 339 N. Bernardo Ave., Mountain View, Calif. 94043, is the presently preferred implementation of the data sequencer 413.

The function of the data sequencer 413 is to monitor the serial data stream coming from the data separator 411 in order to locate the precise sector of a track at which data is to be transferred. Once a sector address coming in from the data surface is determined by the sequencer 413 to correspond with the correct sector identification, data read or write operations are then carried out.

In the case of a read operation, the sequencer transfers the data from the correctly identified disk sector 35 (512 bytes) to the sector buffer 421 where it may then be passed through the interface to the host. In the case of a write operation, the sequence transfers 512 bytes of data from the host (stored in the sector buffer 421) through the write path and into the data region of the properly identified sector in the correct track on the selected disk surface 214.

The sequencer 413 is preprogrammed to carry out these transfers on a single sector basis. The microcomputer 381 commands the actuator 300 to servo on track while waiting until the sequencer has completed its operation before it executes any other commands. Once the transfer of a sector of data is completed, a completion signal is sent by the sequencer to the microcomputer 381. The microcomputer 381 then checks status registers within the sequencer 413 to be sure that no errors have occurred. In the case of a data read operation, the microcomputer 381 then programs the memory controller 417 to transfer the 512 bytes of data from the buffer 421 through the interface 419 to the host. The microcomputer 381 then continues to servo on track while waiting for that transfer to be completed successfully.

#### Memory Controller 417

The memory controller 417 is a low power monolithic integrated circuit for managing the flow of data between the data sequencer 413 and the buffer memory 421, and between the buffer memory 421 and the interface 419 and host computer. It controls the transfer of 512 byte blocks of user data stored on and retrieved from the selected data surface 214, and it also controls the transfer of command and status bytes to and from the microcomputer 381. Fundamentally, the function of

the memory controller 417 is to generate addresses which are sent to the buffer memory 421 via the address bus 445. It also resolves service request contentions during multiple block data transfers between the host and the subsystem 5, when data blocks are being moved 5 through the buffer 421.

Three channels of the memory controller 417 are used by the subsystem 5, and word count registers and address registers are provided internally for each of the channels. The microcomputer 381 programs the con-<sup>10</sup> troller with the address from or to which data is to be transferred, the number of bytes to be transferred, and the direction of the transfer. With these parameters loaded into the controller 417, it then executes the transfer.<sup>15</sup>

FIG. 15 sets forth a conceptural diagram of the structure of the memory controller 417. Inside the memory controller 417 a registers and control logic block 475 contains the write and read registers for each channel. The write registers may be individually written in order to initialize the parameters that control data transfer. Read registers are available and may be individually read by the microcomputer 381 in order to obtain status information about data block movement command execution.

An address generator 477 generates and puts out addresses to the buffer memory 421 via the address bus 445. These addressess locate the data to be transferred to the disk via the data sequencer 413 or to the microcomputer 381 or to the input/output interface 419. In the event of a block transfer the address generator 477 operates automatically to increment the address value to point to the next location in the buffer 421 until the entire block of data for the selected sector is transferred.

A data sequencer interface 479 connects the registers and control logic block 475 with appropriate control lines of the data sequencer 413 via the system control bus 431.

A microprocessor interface 481 enables the microcomputer 381 to read status registers and to write the control registers in order to monitor and control block data transfers. The memory controller 417 also is used to demultiplex (latch) program addresses for the 45 program memory 383 from the address/data bus 435, and these addresses, initiated under the control of the microprocessor 381, are applied to the program memory via the interface 481 and the address bus 439.

Finally, an input/output interface 483 enables the 50 memory controller 417 to control the operations of the input/output channel interface 419.

A monolithic integrated circuit, product code OMTI PFM 5060 Four Channel Memory Controller, available from Scientific Microsystems, Inc., 399 N. Bernardo 55 Avenue, Mountain View, Calif. 94043 is the present preferred implementation of the memory controller 417.

The memory controller 417 is preprogrammed to control the transfer of information, i.e. both data blocks 60 and command and status bytes between the subsystem 5 and the host system. In this regard, the controller 417 handles and coordinates the passing of data blocks and control and status bytes back and forth across the interface 419 with the host system. Once a sequence of con-65 trol bytes has been received from the host, (typically six successive bytes sent to one of four predetermined logical ports to which the subsystem is programmed to

respond), these bytes are then transferred to the microcomputer 381.

There is no data path directly between the microcomputer 381 and the buffer memory 421. In order for the microcomputer 381 to receive command bytes and to send out status bytes to the host via the buffer memory 421, it is necessary that such bytes pass through the data sequencer 413. In order to write a byte to the buffer memory 421, the microcomputer 381 sets up the third channel of the memory controller 417 for writing to the address of the buffer 421 to which the byte is to be written. Then, the microcomputer 381 writes the byte to a register address within the data sequencer 413, and the byte is thereupon automatically transferred to one buffer address by coordinated automatic action of the sequencer 413 and the controller 417. A similar, but 2-step procedure is followed to move a byte of data from the buffer 421 into the internal random access memory of the microcomputer 381. A prefetch is used after setting up the controller 417 by the microcomputer 381 to place the first byte into the sequencer 413. A fetch is then used to move the byte from the sequencer 413 into the processor's internal random access memory. Fetches are then used to transfer all remaining

The memory controller 417 passes data back and forth with the host on a byte by byte handshake basis. Once a block of data, usually a 512 byte sector amount, has been passed successfully, completion of the transfer 30 is signalled to the microcomputer 381.

The host computer normally handles data block transfers from and to the subsystem 5 on a direct memory access basis wherein after the six command bytes have been passed to the subsystem 5, the host central processing unit (CPU) relinquishes the data bus and data is directly transferred into the active memory of the host under the control of a host memory controller. Byte-by-byte data transfers are used between the storage subsystem 5 and the host for command and status bytes on a programmed input/output basis, wherein such bytes pass through the accumulator register of the host. Such transfers may be used for data blocks but would take far more time and greatly impair the speed advantages normally associated with rigid disk data storage devices.

### Input/Output Channel Interface 419

The input/output channel interface 419 is implemented as a special purpose low power VLSI monolithic circuit. This circuit 419 provides all of the circuitry necessary for interfacing the controller elements 413, 417, 381 and related circuitry of the Winchester disk subsystem 5 to the input/output channel bus of a selected host computer, such as the IBM Personal Computer TM. The circuit 419 provides a buffered data path to the host input/output channel, and it provides address decoding for access to eight host input/output address ports, address decoding for access to the external BIOS memory 423 via the buses 449 and 451, and circuitry for control of host bus interrupts and DMA transfers.

As seen in FIG. 16, the circuit 419 includes a port address decode block 485 which decodes address lines A0-A9 from the host I/O channel in order to enable selection of eight input/output ports: four write ports and four read ports (of which only three are used). Two user accessible address select input pins -CNTA and -CNTB are provided to change the address range of the host's input/output ports to enable the use of multiple storage subsystems 5 in the same host personal computer.