# United States Patent [19]

# Machado et al.

# [54] HIGH CAPACITY SUBMICRO-WINCHESTER FIXED DISK DRIVE

- [75] Inventors: Michael G. Machado, Boulder, Colo.; Ronald R. Moon, Los Gatos, Calif.; Thomas A. Tacklind, San Martin, Calif.; William G. Moon, Saratoga, Calif.; Bruce R. Peterson, San Jose, Calif.; Clifford M. Gold, Fremont, Calif.; Daniel E. Barnard, San Jose, Calif.; James H. Do, Milpitas, Calif.

- [73] Assignee: Quantum Corporation, Milpitas, Calif.

- [21] Appl. No.: 710,171

- [22] Filed: Jun. 4, 1991

# **Related U.S. Application Data**

- [63] Continuation-in-part of Ser. No. 569,065, Aug. 17, 1990, Pat. No. 5,170,299, which is a continuation-inpart of Ser. No. 650,791, Feb. 1, 1991, Pat. No. 5,241,546.

- [51] Int. Cl.<sup>5</sup> ..... G06F 1/00; G11B 5/584

- [58] Field of Search ...... 360/77.02, 77.05, 77.08, 360/75

# [56] References Cited

# **U.S. PATENT DOCUMENTS**

| 3,299,411 | 1/1967  | Capozzi et al 340/172.5   |

|-----------|---------|---------------------------|

| 4,016,603 | 4/1977  | Ottesen 360/135           |

| 4,669,004 | 5/1987  | Moon et al 360/77         |

| 4,819,153 | 4/1989  | Graham et al 360/75       |

| 4,890,174 | 12/1989 | Chalmers et al 360/77.05  |

| 4,933,785 | 6/1990  | Morehouse et al 360/78.04 |

| 5,005,089 | 4/1991  | Thanos et al 360/77.05    |

| 5,025,335 | 6/1991  | Stefansky 360/97.01       |

| 5,025,336 | 6/1991  | Morehouse et al 360/97.02 |

| 5,153,786 | 10/1992 | Sidman 360/77.02          |

| 5,170,299 | 12/1992 | Moon 360/77.08            |

Patent Number:

[11]

# [45] Date of Patent: Oct. 19, 1993

5,255,136

# FOREIGN PATENT DOCUMENTS

0471314 2/1992 European Pat. Off. .

# OTHER PUBLICATIONS

Cirrus Logic Preliminary data sheet CL-SH350, Nov. 1989 pp. 1-116.

National Semiconductor Preliminary Data Sheet, DP 8491.

Hard Disk Data Path Electronics, Sep. 5, 1991 pp. 1–99. Silicon Systems Preliminary Data Sheet, SSI 32C452. Storage Controller, Jul. 1990, pp. 7–23 to 7–54.

Primary Examiner-Timothy P. Callahan

Attorney, Agent, or Firm-David B. Harrison

# [57] ABSTRACT

A miniature disk drive achieves storage densities of at least approximately 1700 tracks per inch per storage surface of a storage disk defining a series of radially extensive servo sectors embedded within circumferential zones of data tracks. The sectors are recorded at a constant data transfer rate while each zone has a data transfer rate adapted to disk radius. The drive includes a head and head positioner, a read preamplifier for amplifying analog signals read from, and for amplifying signals to be written to, a storage surface. A circuit board carries drive electronics including a read channel, a servo processing circuit for recovering head location information from the servo sectors, a data block sequencer for sequencing data blocks between a buffer and the storage surface, a buffer memory controller for controlling the buffer, a bus level interface circuit for transferring data blocks between the buffer and a host computer, and a programmed digital controller which functions within a head position servo loop and which also controls the sequencer, buffer controller and bus level interface circuit. As one feature, the servo sectors split data blocks into segments. Segment byte counts in each data block header are used by the sequencer automatically to assemble the segments into data blocks during read and to divide the blocks into segments during write. A single VLSI circuit including the sequencer, servo processing circuit, memory controller and an interface to the microcontroller is disclosed.

# 30 Claims, 18 Drawing Sheets

FIG. -1

FIG. -3

Sheet 2 of 18

Oct. 19, 1993

**U.S.** Patent

5,255,136

٠

U.S. Patent

Oct. 19, 1993

Sheet 9 of 18

5,255,136

Oct. 19, 1993

Sheet 10 of 18

5,255,136

FIG. -12

5,255,136

FIG. - 13A

Oct. 19, 1993

364

FIG. - 13C

Oct. 19, 1993

Sheet 17 of 18

5,255,136

FIG. -14

5

# HIGH CAPACITY SUBMICRO-WINCHESTER FIXED DISK DRIVE

# **REFERENCE TO RELATED APPLICATIONS**

The present application is a continuation in part of U.S. patent application Ser. No. 07/569,065 filed on Aug. 17, 1990, now U.S. Pat. No. 5, 170, 299; and is a continuation in part of U.S. patent application Ser. No. 07/650,791 filed on Feb. 1, 1991 now U.S. Pat. No. <sup>10</sup> 5,241,546.

#### **REFERENCE TO MICROFICHE APPENDIX**

Reference is made to a microfiche appendix accompanying this patent application containing microcon- 15 troller routine program listings and detailed schematic circuit diagrams of a circuit board and a disk drive data sequencer circuit embodying principles of the present invention.

#### FIELD OF THE INVENTION

The present invention relates to high capacity, high performance miniature fixed disk drive data storage subsystems. More particularly, the present invention relates to a high capacity, submicro-Winchester fixed <sup>25</sup> disk drive employing embedded sector servo head positioning and automatic decoding and sequencing of split data fields.

# BACKGROUND OF THE INVENTION

Disk drives, particularly fixed disk drives, are valued on the basis of several factors including size (i.e. sometimes referred to as "form factor"), data storage capacity, random access times between data fields located in disparate concentric data tracks of the storage disk (i.e. 35 sometimes referred to as "access time" or "average access time"), cost per byte stored, and useful life (i.e. sometimes rated as "mean time between failures").

When data tracks are arranged as concentric circles on a circular storage surface, outer tracks or circles are 40 longer and therefore have more useful magnetic storage domains than inner tracks. Also, when storage disks are rotated at a constant angular velocity, the data transducer head "flies" at a faster and somewhat higher altitude above outer storage tracks where relative head 45 termined constant angular velocity. to disk velocity is greater, than inner tracks.

One known way to increase data storage capacity is to divide the data storage surface into radial zones of tracks, and to optimize data transfer rate to the smallest track (innermost track) within each particular zone. 50 reference. The data sequencer may include an en-This approach is sometimes called "zoned data recording". The number of data sectors or fields typically may vary from zone to zone. In order to switch from zone to zone, it is necessary for the disk drive to adapt itself in real time to the number of data sectors and to the new 55 four to three data compaction and therefore permits data rate applicable in the particular zone.

Other known ways to increase data storage capacity include varying disk rotation in function of radial position of the data transducer head while maintaining data transfer rate substantially constant as is done with opti- 60 decoding data sector overhead information in order to cal disk technology; and, varying data transfer rate with each track in function of the radial position of the head, while maintaining disk rotation constant, as is commonly employed in "flying head" or Winchester fixed disk technology.

Issues confronting the designer of a disk drive include head positioning, and data block transfer. Head positioning is typically carried out by a head positioner

servo mechanism and involves "track seeking operations" for moving the data transducer head from a departure track to a destination track throughout the radial extent of the storage area of the disk; and, "track following operations" for causing the data transducer head to follow precisely a particular data track during data block reading/writing operations. In order to provide precise head positioning, during both seeking and following, some servo information must be provided to the head positioner servo. This information may be contained on a special data surface written exclusively with servo information, (called a "dedicated servo surface"), or it may be externally supplied as by an optical encoder coupled to the head positioner arm, or it may be supplied from servo information interspersed or "embedded" among the data fields within each data track. One other approach worth mentioning is provided by the open loop stepper motor head positioner servo wherein positional stability of the head at each selected ata track location is provided by electromagnetic detents of the stepper motor.

When servo information is embedded on a data surface having zoned data recording, complications arise in reliably providing robust servo head position information. There must be sufficient embedded information to provide stability to the servo loop and to provide position feedback during high speed portions of track seeking operations, so that velocity or position profiles 30 may be adjusted, based on present head velocity or position at the time of the sample. If the servo information is recorded at the same data rate, and in positional relationship with the data blocks, as has been conventionally employed, the servo architecture is complex in the sense of having to switch data rate and servo position, as zones are crossed over. One example of data zones with switched servo sector locations is provided by the disclosure of Ottesen U.S. Pat. No. 4,016,603, for example. If the servo information is regularly spaced radially across the data storage surface and splits at least some of the data fields into segments, complications arise in reading each split data field as a single data block without error. Also, the disk rotational velocity must be monitored and carefully maintained at a prede-

Data fields are conventionally managed by a data sequencer. One example of a data sequencer is to be found in commonly assigned U.S. Pat. No. 4,819,153, the disclosure thereof being incorporated herein by coder/decoder for transforming NRZ data into a coded data format, such as 1,7 RLL code in order to achieve compression of data relative to flux transition density on the data surface. (1,7 RLL coding results in an overall more data to be recorded on the disk per the number of flux transitions that may be contained within the magnetic storage domains.)

A data sequencer conventionally performs the task of locate a desired storage location, and to obtain information relating to the correctness or validity of data read back from the storage location. Typically implemented as a state machine, a data sequencer conventionally 65 monitors incoming data flow to locate a data ID preamble field, a data ID address mark, a sector ID field, the data field itself, and usually some small number of error correction syndrome bytes appended to the end of the data field. The sequencer commands appropriate action be taken when each of the fields is located. For example, if a data block from the data field of a particular track and sector is being sought, the sequencer compares incoming sector ID field information with the 5 sought-after sector information stored in a register. When a positive comparison occurs, the sequencer causes the bytes read from the data field via a data transducer head and a read channel to be sent into a block buffer memory, and the error correction syn- 10 drome remainder bytes to be checked. If there are no detected errors in the data bytes as determined by analyzing the ECC remainder bytes, the block is then sent from the buffer memory to the host computer via a suitable interface, such as SCSI.

In the disk drive described in the referenced U.S. Pat. No. 4,669,004, each sector was handled individually in response to specific input from the supervisory microcontroller. As a particular sector was read, the microcontroller would inform the sequencer whether or 20 not to read the next data sector. This microcontroller intervention occurred for every sector.

In a later design, of which the disclosure found in commonly assigned U.S. Pat. No. 5,005,089, is incorporated herein by reference, a programmable sector 25 counter was preset by the microcontroller to a desired sector count, and the sequencer then processed sectors sequentially until the count in the sector counter was reached. The disk drive examples found in the referenced '004 and '153 patents did not include the compli-30 cation of zoned data recording and split data fields, and the '089 patent did not include embedded servo sectors. Positioner stability in the '089 disk drive example was provided by an optical encoder coupled between a rotary head positioner and the drive base, as was the 35 case of the disk drive example described in the referenced '153 patent.

Heretofore, while split data recording schemes have been proposed in the prior art, recent have typically tasked the data microcontroller with the responsibility 40 for managing each split data field layout in real time,leading to a tremendous level of bus traffic between the microcontroller and the data sequencer during data read and write operations, and precluding the microcontroller from performing other very useful tasks, 45 such as those related to head position servo supervision, error correction, command and status exchanges with the host computer over the interface bus structure, to cite a few examples. These prior approaches have therefore employed either a separate data transfer micro- 50 processor, or have sustained a significant reduction or impairment in performance.

As disk drive form factors become smaller and smaller, driven by storage needs of compact, lightweight and powerful notebook computers and intelli- 55. gent notepads, the amount of space and power available for data storage and for support electronics is increasingly diminished. Disk drives having very small form factors, such as those of the  $2\frac{1}{2}$  inch or 1.8 inch disk diameter form factor, typically have room for limited 60 magnetic storage cells or domains and support circuitry space is very constrained, leading to a minimum of discrete circuit components, such as only one microcontroller element, and a limited external bus structure to manage both head position servo information and also 65 manage data block exchanges with the host over a high level bus interface structure, such as SCSI. While downsize scaling of prior technologies and approaches

has been proposed to realize smaller disk drives, see e.g. U.S. Pat. No. 4,933,785, scaling by itself has not resulted in higher capacity, higher performance disk drives within the size-reduced form factor, simply because there is less room on the reduced diameter data storage disk for storing the desired amount of information. Yet, most contemporary full capability computing systems and applications require a minimum of about 40 Megabytes of formatted, hard disk data storage capacity.

10 Heretofore there has been no practical, efficient way to provide a miniaturized disk drive employing a uniquely selected combination of structural elements and functional features to realize higher data storage capacity and performance within a reduced size form 15 factor, such as 2.5 inch or smaller disk diameter.

# SUMMARY OF THE INVENTION WITH OBJECTS

A general object of the present invention is to provide an improved miniaturized disk drive overcoming limitations and drawbacks of the prior art.

Another general object of the present invention is to provide a highly miniaturized and size reduced submicro-Winchester fixed disk drive with increased data storage capacity and performance by uniquely combining structural elements and functional features, some of the elements and features being individually known in the prior art and others being unique in and of themselves.

A more specific object of the present invention is to provide a disk drive employing zoned data recording having data fields split into segments by intervening embedded servo sectors and having on-the-fly sequencing for writing data to and reading data from the split data fields in a manner which overcomes limitations and drawbacks of the prior art approaches.

Another specific object of the present invention is to provide a unique identification field for each data sector which supports directly on-the-fly data sequencing through each split data field without direct microprocessor intervention.

Another specific object of the present invention is to provide an improved data sequencer state machine for a disk drive which autonomously sequences through split data fields without requiring constant intervention by a microcontroller element to decode the particular format of each split data field, thereby freeing the microcontroller to perform other useful tasks.

One more specific object of the present invention is to provide an arrangement of application specific integrated circuits which integrate and tightly couple circuitry comprising disk drive operating elements regarding data read/write channel, disk data sector formatting, data flow between the storage disk and a buffer memory during data writing and reading operations, disk data flow between the buffer memory and an interface leading to a host computer, head positioning during head positioning operations, and spindle motor speed, for example.

A submicro-Winchester disk drive data storage subsystem for storing at least 40 megabytes of formatted user data on a single disk and at least 80 megabytes on two disks by incorporating principles of the present invention includes a bus-level interface circuit for connecting with a host computing system, at least one rotating disk having data storage surfaces defining a plurality of concentric data storage track locations, a data transducer head for each surface, the heads being radially

positionable among the track locations, a head positioning system for moving the data transducer heads between track locations during track seeking and settling, and for maintaining a selected one of the data transducer heads in alignment with centerline of a track 5 during track following operations during which data blocks are written to or read from the track being followed. Each data block includes an ID field containing block segment counts indicative of the spatial arrangement of said block. The storage surfaces define a series 10 The data segment address mark is preferably different of radially extensive servo sectors embedded within the data tracks at predetermined spaced apart circumferential locations across a data storage surface areas of the disk and thereby split at least some of the data blocks into segments. The subsystem further comprises a servo 15 for enabling a phase locked loop within a data separator processing circuit for locating and processing servo information located within each servo sector to determine present location of the data transducer head and to put out head position digital values indicative thereof, a buffer memory connected to the interface circuit for 20 abling the disk drive to resolve the particular sector temporarily storing data blocks being transferred between the system and the subsystem via the interface circuit, a data block sequencer directly responsive to the block segment counts for locating and assembling data blocks read from and written to the data storage 25 surfaces and for handling data block transfers between the disk storage surfaces and the buffer memory, a buffer memory controller for handling transfers between the buffer memory, the data sequencer, and the interface circuit, a programmed digital controller in- 30 cluding servo supervision routines for supervising operations of the servo processing means by generating and applying digital head position values to the head positioning system from the head position digital values generated by the servo processing circuit, and including 35 channel extending between the integrated circuit and data block transfer supervision routines for supervising operations of the data block sequencer, the buffer memory controller and the interface circuit.

Another facet of the present invention is found in a data storage pattern for a high capacity, submicro-Win- 40 chester disk drive including a storage disk rotating at substantially constant angular velocity and having at least one storage surface defining a multiplicity of concentric data tracks, and a data transducer head positionable at each of the tracks by a head positioning mecha- 45 the sequencer, a digital servo decoder responsive to nism operating within a digital servo loop. The data storage pattern comprises a series of circumferentially spaced apart, radially extending servo sectors, each servo sector being prerecorded with flux transition patterns defining a servo address mark, a servo sector 50 programmed microcontroller means, and a microconidentification number and servo centerline information, the transition patterns defining the sector identification number and the servo centerline information being resolvable by the disk drive into digital numbers representing head position relative to a said concentric track 55 digital servo decoder. containing the particular sector. The data tracks are grouped into a plurality of concentric track zones, each zone having a data transfer rate related to radial offset of said zone from a center of rotation of the disk. Each track within a zone is soft-formatted into a predeter- 60 mined number of data sectors of predetermined user data block storage length. At least some of said sectors are interrupted by at least one of the servo sectors into data segments. Each data sector has a data sector identification field including a plurality of user byte count 65 values indicating the user data storage capacity of each segment of the sector. The count values may therefore be read by the disk drive on-the-fly in order to read a

user data block from, and to write a user data block to, the segments.

In one aspect of this facet of the invention, each segment of a data sector includes a preamble field including an address mark, and each said data sector which is divided into plural segments by at least one servo sector includes a data sector identification field as a preamble of a first segment, and a subsequent segment includes a data preamble including a data segment address mark. than the address mark contained within the data sector identification field.

In another aspect of this facet of the invention, the preamble field includes a predetermined sync pattern of said disk drive to resolve the data transfer rate of the zone of the track containing the particular field, the address mark, an identification field including said count values, a sector and head identifier field for enlocation among the multiple data sectors, and an error detection field for enabling an error correction circuit of the disk drive to verify correctness of the values contained within the preamble field.

As a further facet of the present invention, a monolithic VLSI integrated circuit is provided for a disk drive data storage subsystem. The subsystem includes a disk rotating at a controlled, substantially constant angular velocity and defining a multiplicity of concentric data tracks; a head for reading data from a said track and for writing data to a said track, the head being positioned by a head positioning mechanism operating within a digital head position servo loop including a programmed digital microcontroller; and, a read/write the head. A buffer memory is connected between the integrated circuit and an interface circuit for connecting the subsystem with a host computing system via a bus level interface. The monolithic VLSI integrated circuit includes a data sequencer for sequencing blocks of data to and from the disk at defined data block storage locations thereof, a memory controller for generating and putting out addresses to the buffer memory for enabling the buffer memory to transfer data blocks to and from servo information embedded in servo sectors prerecorded on the data surface across the data tracks for decoding the embedded sector information read by the head and putting out digital head position values to said troller interface for enabling said programmed microcontroller to have direct access to storage locations of the integrated circuit for storing control values for said data sequencer, the memory controller and the

As aspects of this facet of the invention, the monolithic VLSI integrated circuit the servo information embedded in servo sectors may include in one of the servo sectors a unique index pattern denoting a onceper-revolution index marker. The digital servo decoder decodes the unique index pattern into the index marker. The chip further comprises a disk rotational speed monitoring and adjustment circuit responsive to the index marker for generating speed up and slow down control signals for controlling a spindle motor driver circuit. The chip may further include a pulse width modulator controlled by the programmed microcontroller for generating servo control pulses of controlled duration and

applying the control pulses to a servo actuator driver circuit within the head positioner. The chip may further include a programmable master clock for generating programmable clocking signals for controlling operation of the microcontroller, the memory controller and 5 an interface state machine within the interface circuit. The data sequencer within the chip may include an encoder/decoder for encoding and decoding user data values into and from a predetermined zero run length limited code, such as a 1,7 RLL code having a 3 data 10 bits to 2 code bits data compression ratio.

Another facet of the present invention comprises a submicro-Winchester fixed disk drive having at least one data storage disk with a diameter not substantially greater than 2.5 inches and a formatted user data stor- 15 age capacity of not less than about 40 megabytes per storage disk. The disk rotates at a controlled substantially constant angular velocity. A data transducer head reads data from and writes data to data sectors of concentric data tracks defined on a surface of the disk. A 20 mass balanced rotary voice coil actuator is included for positioning the data transducer head at each selected one of the data tracks for data reading and writing operations. The actuator is controlled by a digital servo control loop. The disk surface further defines a plurality 25 of radially extending, circumferentially spaced apart servo sectors containing prerecorded servo flux transitions at a constant data transfer rate. The flux transitions define a plurality of fields including a servo sync field, a servo address mark field, a servo data field and plural 30 servo centerline burst fields. The data tracks are arranged in plural circumferential zones wherein each zone has a data transfer rate selected in relation to radial displacement of the zone from a center of rotation of the disk. At least some of the data tracks in at least some of 35 the zones are split into segments by one or more of the servo sectors. The disk drive comprises:

a read/write channel connected to the data transducer head for converting digital pulses into analog transitions to be writtent to said surface during data 40 chip, the buffer memory and the interface circuit. writing operations and for converting analog transitions detected by the data transducer head into pulse transitions.

a servo digital decoding and processing circuit connected to the read/write channel for locating and de- 45 substantially not greater than 0.61 inch, a width substancoding into digital head position values the servo flux transitions located within each servo sector to determine present location of the data transducer head and to put out head position digital values indicative thereof,

computing system via a bus level interface,

a buffer memory connected to the host interface circuit for temporarily storing data blocks being transferred between the system and the subsystem via the interface circuit,

a data block sequencer connected to the read/write channel and directly responsive to the block segment counts for locating and assembling in real time from the segments the data blocks read from and written to the data storage surfaces and for handling data block trans- 60 fers between the disk storage surfaces and the buffer memory,

a buffer memory controller for handling transfers between the buffer memory and the interface circuit, and

a programmed digital controller including servo supervision routines responsive to the servo digital decoding and processing circuit for generating and applying digital head position values to a voice coil actuator driver circuit from the head position digital values generated by the servo processing circuit, and including data block transfer supervision routines for supervising operations of said data block sequencer, the buffer memory controller and the interface circuit.

As aspects of this facet of the invention, each said data sector has a data sector identification field including a plurality of user byte count values indicating the user data storage capacity of each said segment thereof, and the data block sequencer includes a register stack for receiving the user byte count values and a segment counter responsive to a byte clock and preloaded onthe-fly with a particular user byte count value for a present segment supplied from said register stack. Also, the read/write channel may comprise a first monolithic integrated circuit including a read preamplifier/write driver amplifier, a second monolithic integrated circuit chip including a pulse detector, a phase locked loop, and a frequency synthesizer supporting zoned data transfer rates, and a third monolithic VLSI integrated circuit including the servo digital decoding and processing circuitry, the data block sequencer and buffer memory control. The third chip may also include a spindle speed monitoring and correction signal generating circuit connected to the servo digital decoding and processing circuitry for monitoring a once-per-revolution index pattern recorded in a said servo sector and for generating and putting out a disk speed correction control signal to a disk spindle motor driver circuit controlling operation of a brushless DC spindle motor rotating the disk at the substantially constant angular velocity. Also, the third chip may include a microcontroller interface. The drive further comprises a control bus structure between the programmed microcontroller, the second chip, the microcontroller interface of the third chip, and the host interface circuit; and further comprises a data transfer bus structure between the third

As one other aspect of this facet of the invention, the submicro-Winchester data storage subsystem comprises a single data storage disk and is included entirely within a form factor in a horizontal orientation of a height tially not greater than 2.76 inches, and a depth substantially not greater than 3.94 inches.

As another aspect of this facet of the invention, submicro-Winchester disk drive data storage subsystem a host interface circuit for communicating with a host 50 comprises two data storage disks mounted in spaced apart relation on said hub and is included entirely within a form factor in a horizontal orientation of a height substantially not greater than 0.75 inch, a width substantially not greater than 2.76 inches, and a depth substan-55 tially not greater than 3.94 inches.

These and other objects, advantages, aspects and features of the present invention will be more fully understood and appreciated by those skilled in the art upon consideration of the following detailed description of a preferred embodiment, presented in conjunction with the accompanying drawings.

# BRIEF DESCRIPTION OF THE DRAWINGS

#### In the Drawings:

65

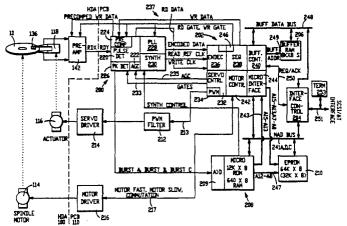

FIG. 1 is a plan view of a disk data storage surface including data track zones and radially/circumferentially aligned embedded servo sectors in accordance with the principles of the present invention.

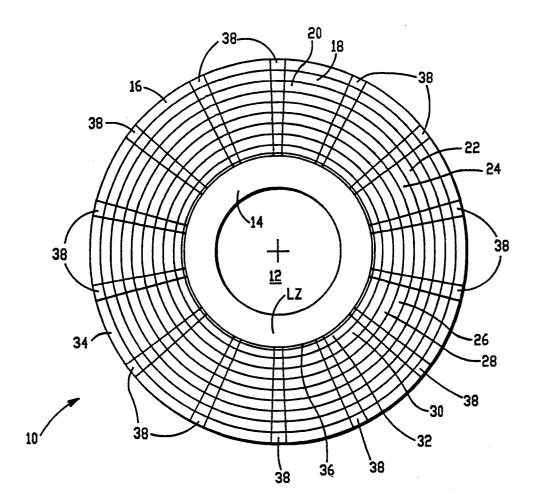

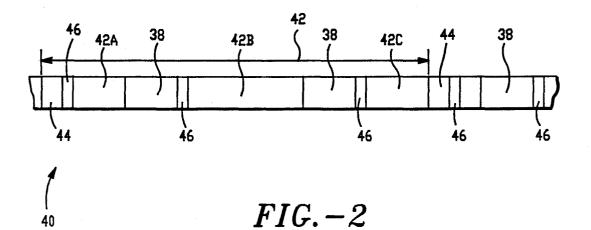

FIG. 2 is a graph of a segment of a data track showing a data field being split into segments by recurrent servo sectors. ID and data headers for the data segments include fault tolerant address marks in accordance with principles of the present invention. While the FIG. 2 5 graph is a rectilinear depiction, within disk drives, the tracks are typically concentric, and a truer representation would show the FIG. 2 segment as an arc segment of a circular track pattern.

track segment.

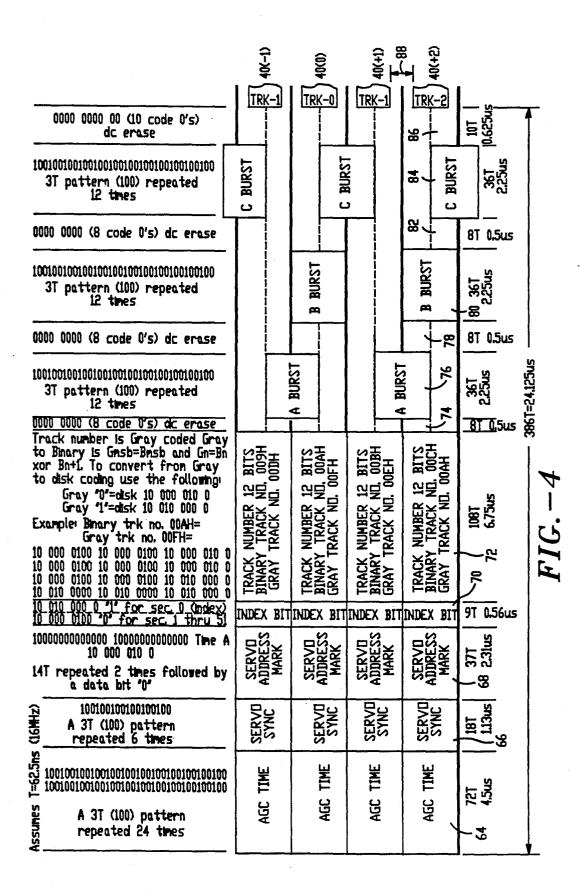

FIG. 4 is a detailed view of one of the plural embedded servo sectors shown in the FIG. 1 plan view.

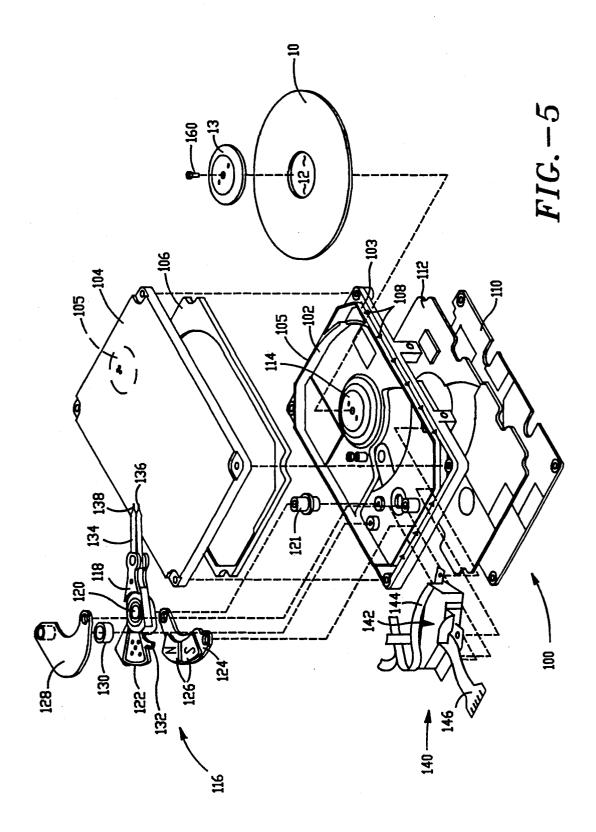

FIG. 5 is an exploded isometric view of a submicro-Winchester head and disk assembly (2.5" disk diameter) 15 incorporating aspects and principles of the present invention.

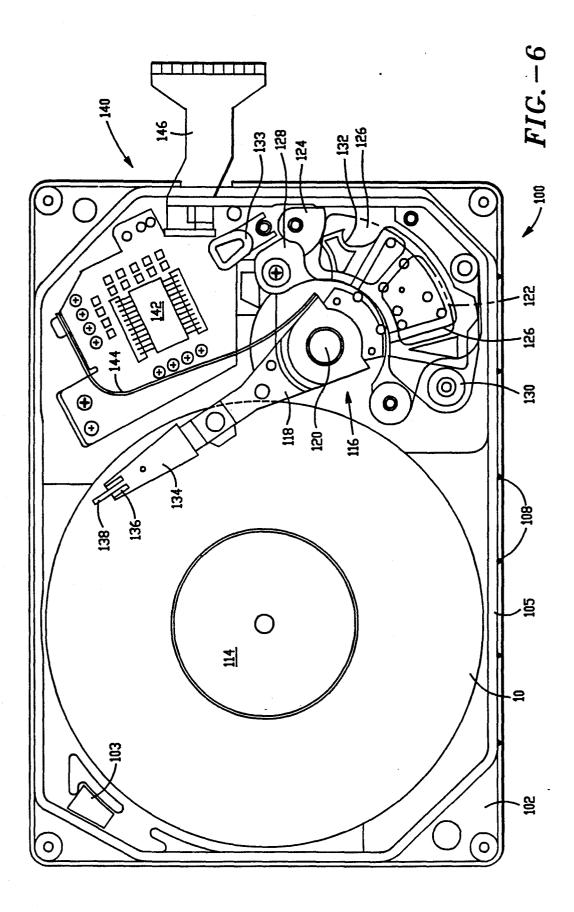

FIG. 6 is a plan view of the FIG. 4 head and disk assembly.

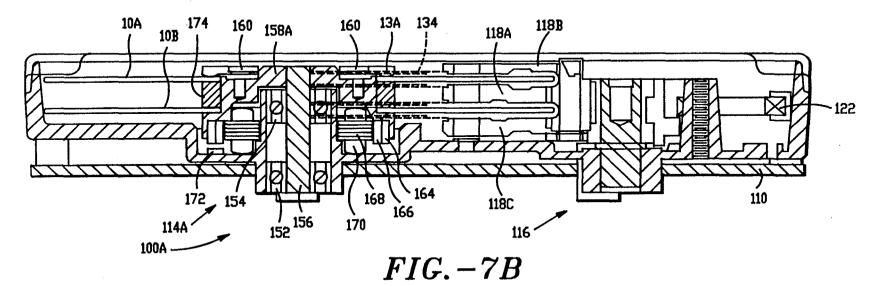

FIG. 7 is a side view in elevation and section of the 20 FIG. 6 head and disk assembly.

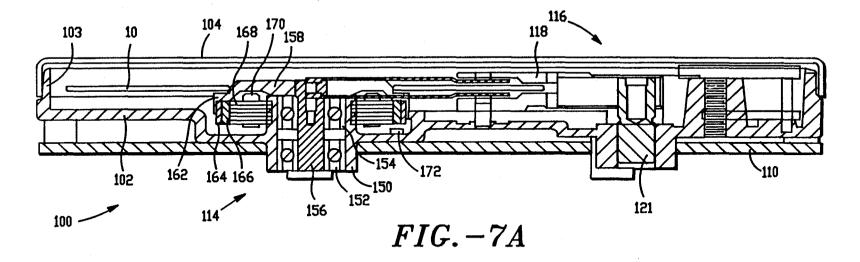

FIG. 7A is a side view in elevation and section of a two-disk alternative submicro-Winchester head and disk assembly.

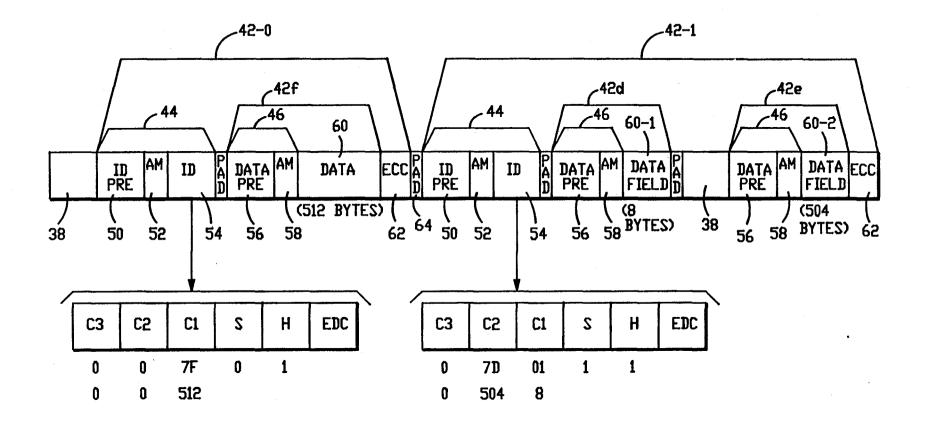

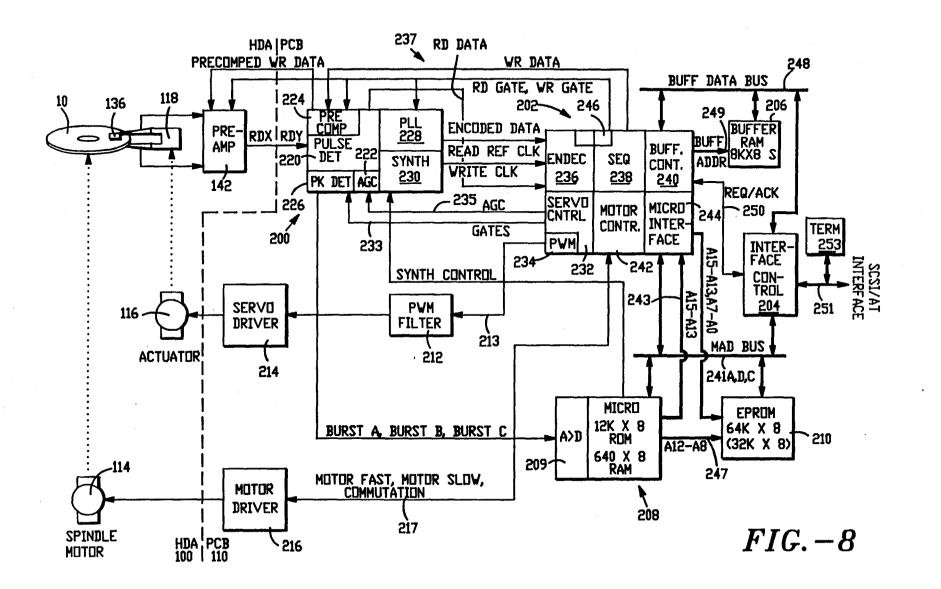

FIG. 8 is an overall block diagram of an electrical 25 control system for the miniature disk drive incorporating principles of the present invention.

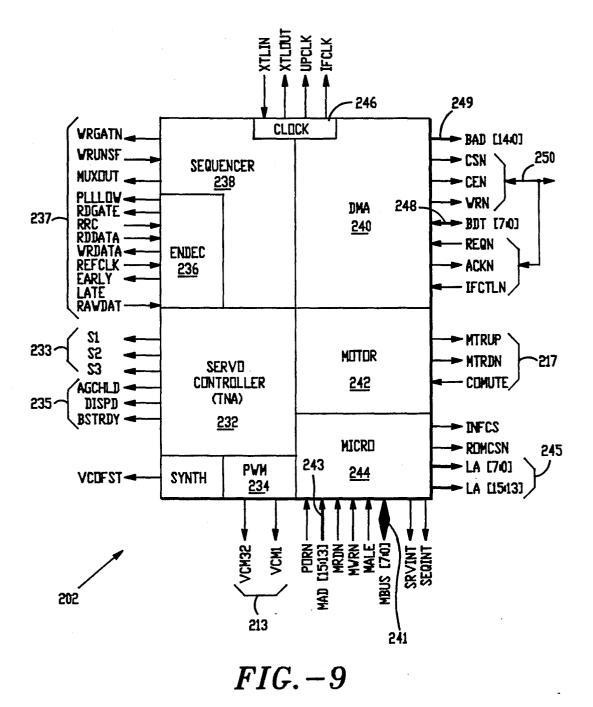

FIG. 9 is a more detailed block diagram of an integrated circuit combining a number of functional elements of the FIG. 7 system (Buffalo).

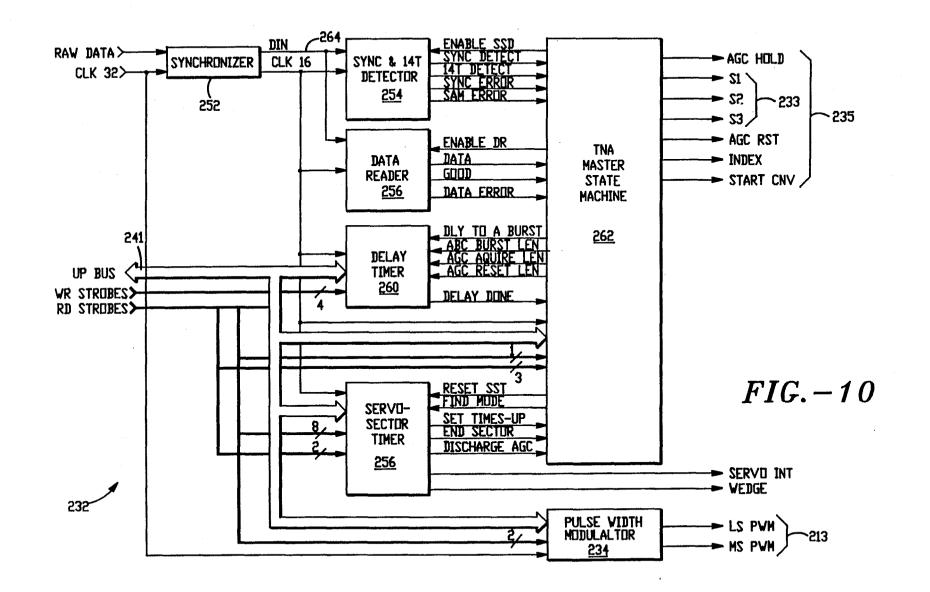

FIG. 10 is a more detailed block diagram of a servo timer and decoder subsystem included within the FIG. 8 integrated circuit.

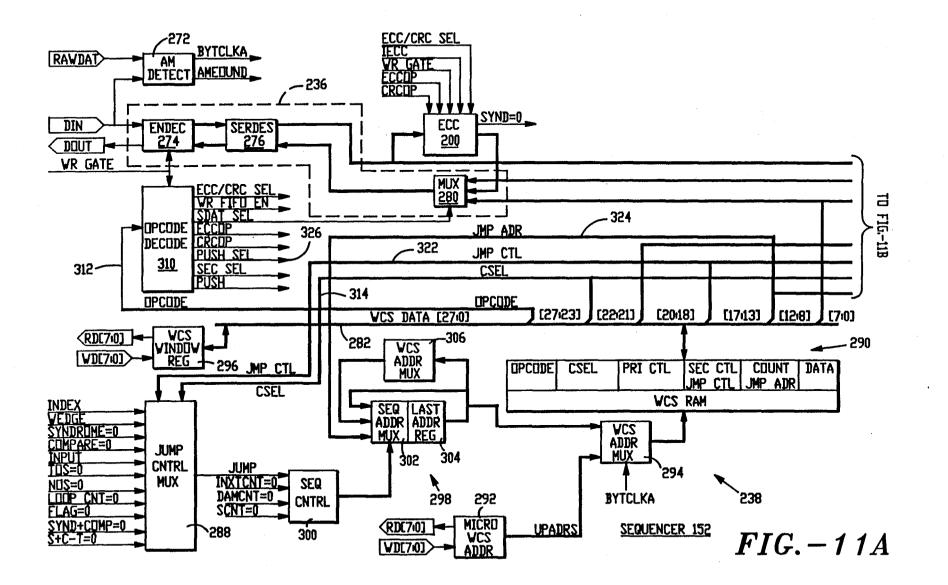

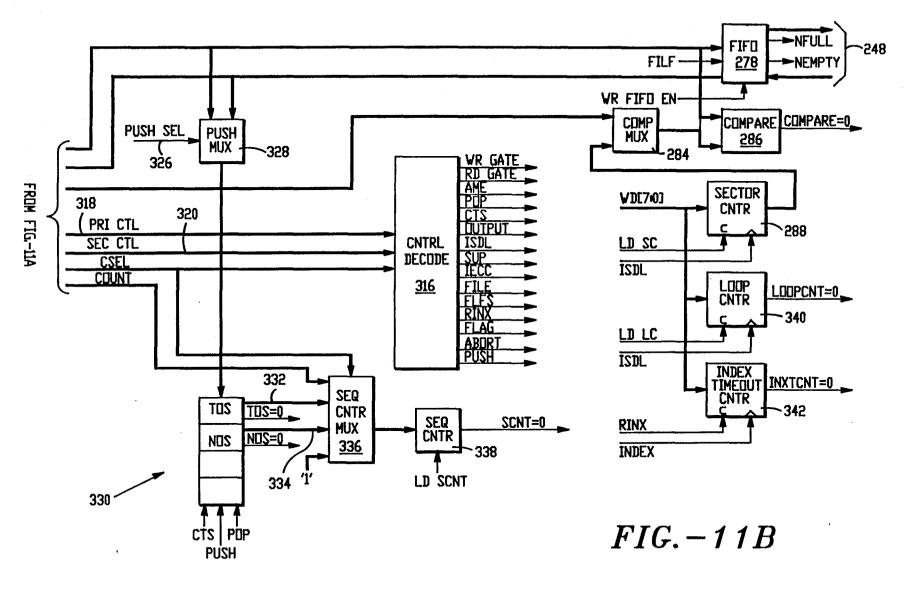

FIGS. 11A and 11B together provide a more detailed diagram of a data sequencer subsystem included within 35 the FIG. 8 circuit.

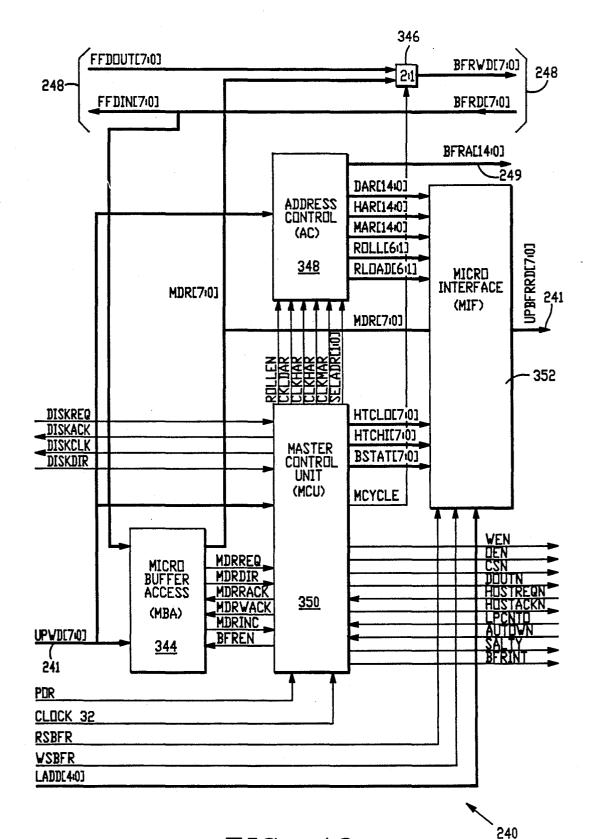

FIG. 12 is a more detailed block diagram of a memory controller subsystem included within the FIG. 8 circuit.

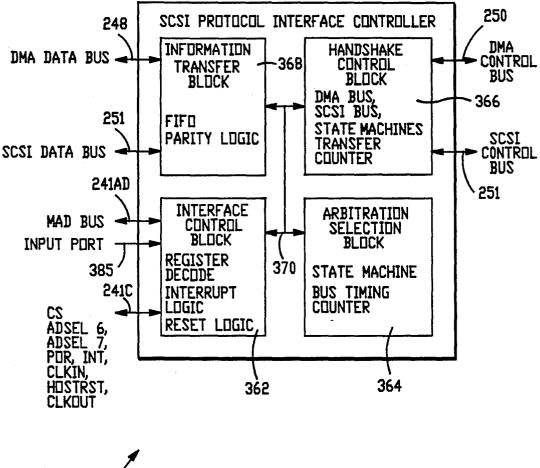

FIG. 13A is a more detailed overall block diagram of 40 an interface subsystem included within the FIG. 7 system illustrating an interface control block, an arbitration selection block, a handshake control block, and an information transfer block.

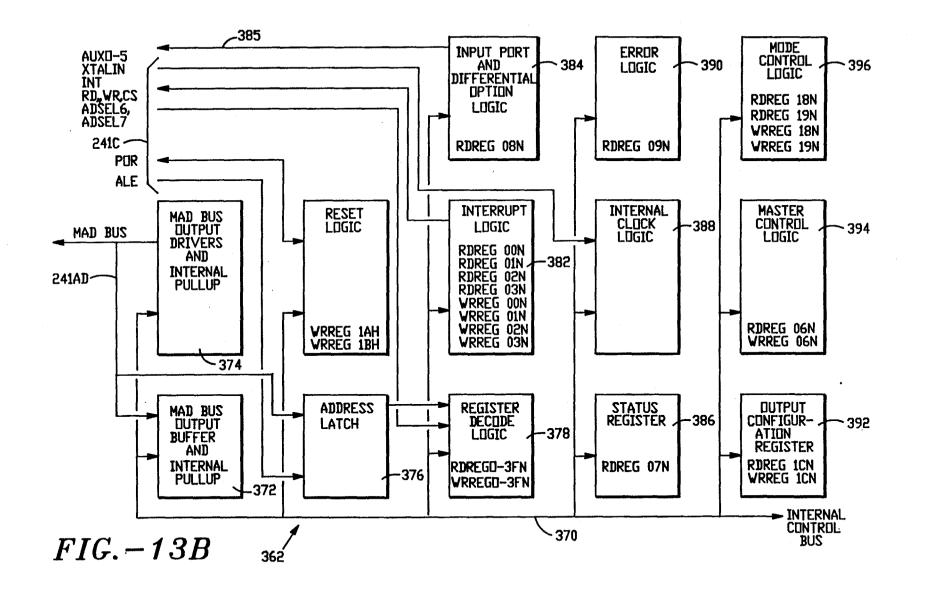

FIG. 13B is a detailed block diagram of the FIG. 13A 45 interface control block.

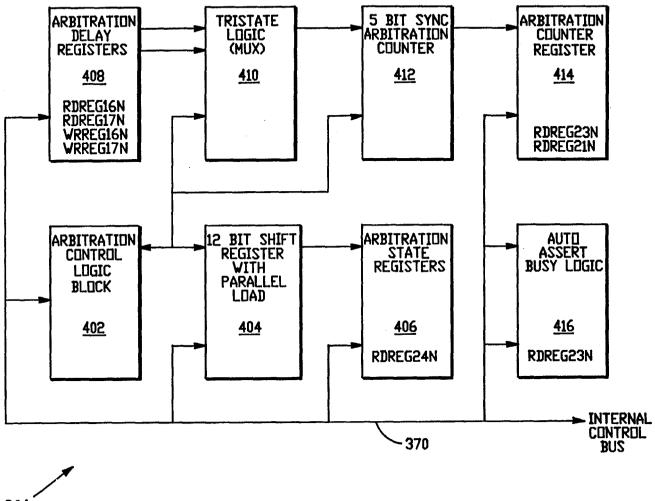

FIG. 13C is a detailed block diagram of the FIG. 13A arbitration selection block.

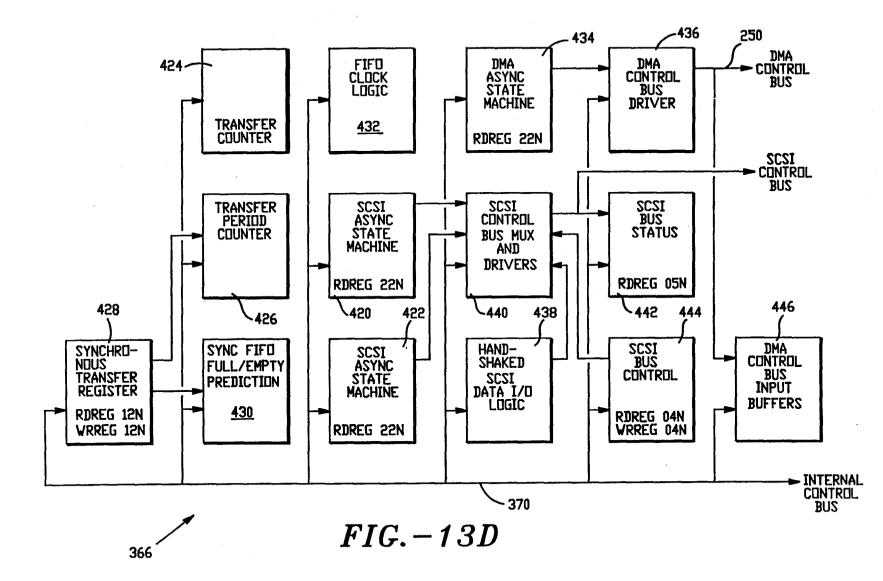

FIG. 13D is a detailed block diagram of the FIG. 13A handshake control block.

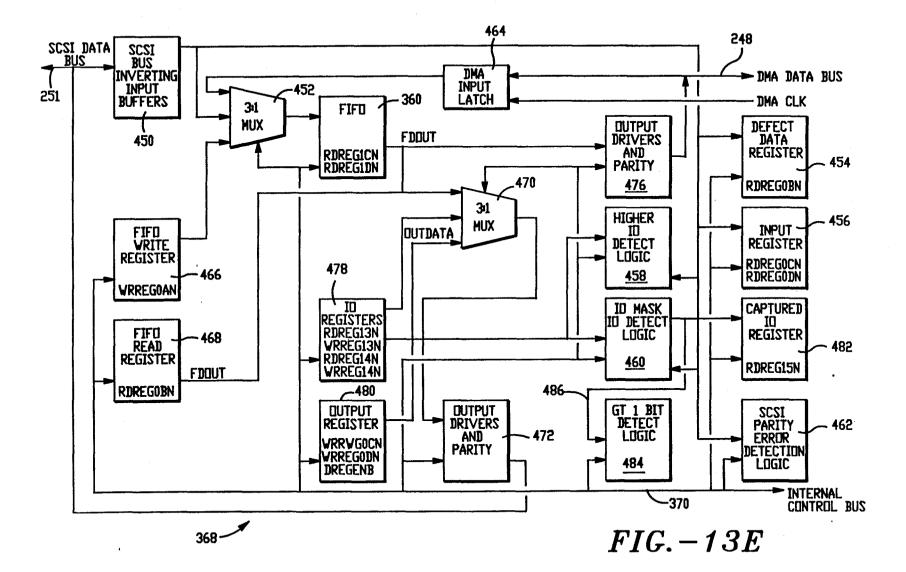

FIG. 13E is a detailed block diagram of the FIG. 13A information transfer block.

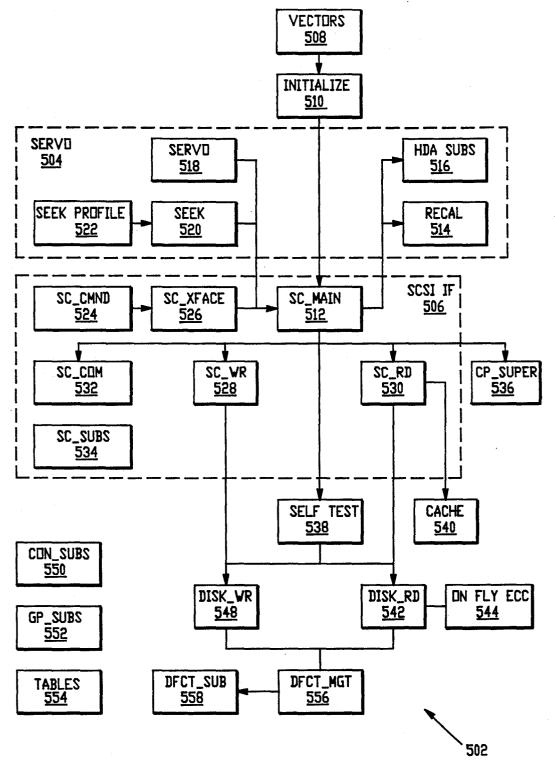

FIG. 14 is a block diagram illustrating overall arrangement and organization of firmware modules comprising a control program for controlling operation of 55 the disk drive of the present invention.

# DETAILED DESCRIPTION OF A PREFERRED EMBODIMENT

A submicro-Winchester data storage system 5 in ac- 60 cordance with principles of the present invention provides in a single disk version (FIG. 7A) a formatted storage capacity of approximately 42.9 megabytes, while a two disk version (FIG. 7B) doubles the formatted storage capacity to approximately 86.3 megabytes. 65 The drive 5, including spindle motor, head position and embedded data controller electronics achieves a very low profile, which is optimized to the number of storage

disks employed. A synchronous data transfer rate of up to 4.0 megabytes per second is achieved through a high level interface, such as SCSI or IDE (AT). An average seek time of approximately 19 milliseconds is realized. On-board look-ahead data caching during both data read and data write operations is achieved by virtue of a cache buffer memory, which may be from eight kilobytes up to 32 kilobytes. Briefly, write caching is accomplished by signalling a write-completion status to FIG. 3 is a more detailed view of the FIG. 2 data 10 the host while data actually remains in the buffer and before it is recorded on the disk. Read caching occurs by reading additional data blocks from the disk into the cache buffer in addition to the block(s) actually requested by the host.

> An on-the-fly error correction coding scheme, together with automatic data sequencing and error detection of data ID fields, is achieved with automatic retrys on read errors. Media defect mapping is handled on a basis which is transparent to the user by virtue of a high performance, in-line defective data sector skipping arrangement. Defective data sectors which are discovered during usage are automatically replaced by spare sectors without any requirement for reformatting the storage disk. A one to one interleave of data sectors is achieved for a high efficiency data throughput.

# Data Storage Disk 10

A submicro-Winchester rotating storage disk 10, which presently is most preferably 2.5 inches in diame-30 ter, but which may be 1.8 inches in diameter, or larger or smaller, is formed of suitably very flat and smooth substrate material such as aluminum metal or glass which is coated with e.g., a magnetic storage medium such as a high oerstead thin film magnetic storage medium vacuum sputter deposited onto the substrate thereby to realize bit densities in the 45,000 plus bits per inch range. The disk 10 defines a central opening 12 to enable a disk clamp 116 securely to clamp the disk 10 to a rotating disk spindle 114, see FIG. 5.

Returning to the disk 10 depicted in FIG. 1, between an inner landing zone area 14 and an outer peripheral zone 16, a data storage area of a multiplicity of concentric data tracks is defined. Because the length of a track at the inner diameter is less than that at the outer diameter, a multiple zone recording methodology is employed to optimize available storage space within the data storage tracks. The tracks are therefore arranged into e.g. eight data zones, 18, 20, 22, 24, 26, 28, 30 and 32, extending from a radially outermost zone 18 to a radially innermost zone 32. A system information region 34 lies radially outwardly just beyond the outer zone 18, and a diagnostics and guard region 36 lies just inside of the inner inner zone 32.

Outermost zone 18 includes e.g. 110 tracks, each having 58 data sectors, with a storage density of 43,334 bits per inch (32,500 flux changes per inch (FCI) encoded in 1,7 run length limited code). The raw data rate is 18.13 megabits per second (MBPS) with a raw code rate of 27.20 Megahertz (MHz). Zone 20 includes e.g. 109 data tracks, each having 56 data sectors per track, with a storage density of 44,269 bits per inch (32,202 FCI), a raw data rate of 17.45 MBPS and a raw code rate of 26.18 MHz. Zone 22 includes e.g. 109 concentric data tracks, each having 52 data sectors per track, a storage density of 42,382 MBPS (31,787 FCI), a raw data rate of 15.69 MBPS and a raw code rate of 23.53 MHz. Zone 24 includes e.g. 109 data tracks, each having 52 sectors per track, with a storage density of 45,334

50

MBPS (34,008 FCI) and a raw data rate of 15.69 MBPS and a raw code rate of 23.53 MHz. Zone 26 includes e.g. 109 data tracks, each having 47 data sectors per track, a storage density of 45,900 BPI (34,425 FCI), a raw data rate of 14.77 MBPS and a raw code rate of 22.15 MHz. 5 Zone 28 includes e.g. 108 data tracks, each having 44 data sectors, a storage density of 47,008 BPI (35,256 FCI), a raw data rate of 14.00 MBPS and a raw code rate of 21.00 MHz. Zone 30 includes e.g. 108 data tracks each having 41 data sectors, a storage density of 47,294 10 BPI (35,471 FCI), a raw data rate of 12.98 MBPS and a raw code rate of 19.43 MHz. Innermost data zone 32 includes e.g. 108 concentric data tracks each having 39 sectors per track, a storage density of 48,371 BPI (36,278 FCI), a raw data rate of 12.09 MBPS and a raw 15 code rate of 18.13 MHz. The outer system zone 34 includes e.g. 14 tracks following e.g. the Zone 32 format, and the inner diagnostics zone 36 includes 1 track also following the Zone 32 format. A guard band of four tracks lies immediately inside of the diagnostics 20 zone 36. A track density of, 1700 tracks per inch is realized, and the maximum linear flux density is 36,278 flux reversals per inch.

With this described arrangement of data zones, split data fields and embedded servo sectors, the disk 10 25 rupted throughout its circumferential extent. However, achieves the approximately 42.9 Megabytes rated data storage capacity. A two disk version of the data storage subsystem 5 achieves the approximately 86.3 Megabytes rated data storage capacity.

FIG. 1 also depicts a series of radially extending, 30 evenly spaced apart servo sectors 38. In this particular example, there are preferably 52 of the radial servo sectors 38 (shown diagrammatically as several narrow spokes in FIG. 1) equally spaced around the circumference of the disk 10. With rotation of the spindle 114 and 35 11) to determine on-the-fly the layout of the particular disk 10 maintained at 16.667 milliseconds per revolution (3600 RPM), each servo sector takes up about 24.125 microseconds of each rotational interval. The servo sector pattern is depicted in FIG. 4 and discussed hereinafter. Other drive overhead includes the FIG. 3 data 40 sector ID and data fields. While the number of data sectors in each zone varies, it is apparent from inspection of FIG. 1 that the number of embedded servo sectors in this particular example remains constant, and radially extensive as well as circumferentially equally 45 spaced apart throughout the extent of the storage surface of the disk 10.

As each data sector is of fixed storage capacity or length (e.g. 512 bytes of user data per data sector), and as the density and data rates vary from data zone to data 50 zone, it is intuitively apparent that the servo sectors 38 interrupt and split up at least some of the data sectors or fields, and this is in fact the case in this presently preferred example. The servo sectors 38 are preferably recorded at a single data cell rate and with phase coher- 55 ency from track to track across the disk 10 with a conventional laser guided servo writing apparatus at the factory. A laser servo writer and head arm fixture suitable for use with the servo writer are described in commonly assigned U.S. Pat. No. 4,920,442, the disclosure 60 of which is hereby incorporated herein by reference.

As shown in FIG. 2, a data track 40 includes a data block 42 for storage of a predetermined amount of user data, such as 512 or 1024 bytes of user data, recorded serially by 1,7 RLL code bits in data field areas of the 65 depicted track segment. The data block 42 is interrupted by several servo sectors 38 which contain embedded servo information providing head position in-

formation to the disk drive via a data transducer head (not shown) which is positionable radially with respect to the data surface in order to read the data and servo information contained in the track 40, for example, as well as some or all of the other data tracks on the particular surface. The data block 42 includes an ID header 44 at the beginning of the data block and a data header 46 at the resumption of a data field segment following interruption by a servo sector 38, and following each data header 44.

As shown in greater detail in FIG. 3, the ID header 44 typically may include an ID preamble 50, a data ID address mark 52, an ID field 54 including three or four count bytes, a sector number byte, a head number byte, and a Reed Solomon error detection code. The data ID field 54 is followed by a data preamble field 56, a data address mark 58, and a user data field 60 for storing the predetermined number of user data bytes, such as 512 bytes, for example. The user data field 60 is followed by an ECC field containing e.g. 12 ECC syndrome remainder bytes and two cross-check bytes. A pad field 62 follows the ECC field and separates a first data sector 42-0 from a second sector 42-1, for example.

The first sector 42-0 is shown in FIG. 3 as uninterthe sector 42-1 is interrupted by a servo sector 38 and includes two data segments 42d and 42e, for example. Each split data segment, such as the segments 60-1 and 60-2 shown in the second sector 42-1 of FIG. 3 are preceded by at least a data preamble field 56, and a data address mark 58. Immediately following the last data field segment 60-2 is the error correction field 62 containing the ECC remainder bytes.

The count bytes are used by a data sequencer (FIG. data sector 42, as to the manner by which it is interrupted by the servo sectors 38. In other words, in the FIG. 3 example the first data sector 42-0 is not split up into segments. Accordingly, count bytes C3, C2 and C1 it, are respectively 0, 0 and 7F(Hex, 127 decimal, the count bytes being divided by 4 to save register room in the sequencer 152). This pattern means that the first segment contains all of the data bytes, and there are no second (C2) or third (C3) segments.

A split data field example is provided with data sector 42-1. Therein, the count bytes C3, C2 and C1 are respectively 0, 70, 01. This pattern of count bytes indicates that the first data segment 60-1 (C1) contains eight user bytes, and the second data segment contains 504 bytes, and that there is no third segment in this particular example.

The count bytes are arranged in reverse order, so that they may be pushed onto a byte count stack 234 within the sequencer 152, as explained in greater detail hereinafter. The last count for the first segment 60-1 (C1), will be the first popped off the stack 234 and loaded into a byte counter 236 of the sequencer 152 as the first segment of the particular data sector 42 is being read from or written to in real time. When the next segment is reached, the next count for the second segment 60-2 (C2) is then popped off of the stack 234 and into the byte counter 236, and when the third segment is reached, the third count (C3) will be popped off of the stack 234 and loaded into the byte counter 236. This activity does not take place for byte count values of zero. In this manner, the data sequencer 152 is able to reassemble the data sectors 42 into unbroken continuous byte sequences which in the case of data reads from the

disk are sent into a data block buffer preparatory to being transferred to the host. For incoming data blocks when data is being written to a storage surface of the disk 10, the sequencer 152 uses the count bytes in order to know how many bytes to sequence to the disk surface 5 for each data sector segment.

As already noted, each data sector includes within the ID field several error detection bytes which are used to verify the integrity of the information read back code bytes (EDC) are preferably Reed Solomon syndrome remainder bytes which are coded from a code compatible with the error detection syndrome remainder bytes contained in the ECC fields 62. The EDC bytes as well as the ECC bytes are checked in real time 15 by an ECC circuit within the sequencer.

A presently preferred on-the-fly EDC/ECC circuit is described in connection with aspects of the present invention in referenced, commonly assigned, copending parent U.S. patent application, Ser. No. 07/650,791, 20 been found that two successive 14T patterns, followed filed on Feb. 1, 1991, the disclosure of which is hereby incorporated by reference.

#### Pattern for Servo Sector 38

FIG. 4 illustrates graphically the servo pattern for 25 each servo sector 38. The basic cell period (T) for the flux transitions within the servo sector is 62.5 nanoseconds (16 MHz). This constant cell period or rate remains invariant throughout the radial extent of the servo sectors 38, and in this manner differs from the 30 data storage zones 18-32. Each sector occupies e.g. 386 T or 24.125 microseconds.

In this particular example, there are e.g. 12 discrete, phase coherent fields within each servo sector 38. As illustrated in FIG. 2, the sector 38 begins with a 72T 35 AGC field 64 (a 3T pattern 100 repeated 24 times), followed by an 18T servo sync field 66 (a 3T pattern 100 repeated 6 times), followed by a 37T servo address mark field 68 (a 14T pattern repeated two times, followed by a data bit "zero"), followed by a 9T spindle 40 index field 70 (a data bit "one" for the index sector and a data bit "zero" for all other sectors), followed by a 108T track identification field 72 (twelve data bits encoded in Gray code), followed by a first 8T dc erase gap 74, followed by a first 36T A burst field 76 (a 3T pattern 45 100 repeated 12 times). followed by a second 8T dc erase gap 78, followed by a second 36T B burst field 80 (a 3T pattern 100 repeated 12 times), followed by a third 8T dc erase gap 82, followed by a third 36T C burst field 84 (a 3T pattern repeated 12 times), and finally 50 followed by a fourth 10T dc erase gap 86 which marks the boundary between the servo sector and the start or resumption of the data tracks 40. It will also be noted in FIG. 4 that each data track 40, as recorded, is narrower than the nominal space allotted for each track, leaving a 55 fields depicted in FIG. 2, a very robust and reliable guard band 88 between each track.

In this particular servo sector example, a data bit "one" has a cell format of 10 010 000 0; and, a data bit "zero" has a cell format of 10 000 010 0. In the case of a data bit one, or a data bit zero, there are never more 60 than five zero cells between flux transitions (denoted by 1). The first flux transition of the data bit provides a means for positively synchronizing the asynchronous data reader to the data bit sequence, as will be more particularly pointed out and explained hereinafter. 65 Thus, each servo data bit comprises three cell triads, a first or sync triad (010), a second triad (010 or 000) and a third triad (000 or 010).

In order to realize an effective, reliable and robust digital head positioner servo loop employing servo information within embedded sectors, it is necessary to be able to detect the location of each embedded sector. Detection of each embedded sector 38 requires detection of an unmistakable marker. The marker may be a hard servo sector pulse derived by e.g. a reluctance sensor from a code disk attached to the disk spindle, or in the present example, it most preferably may be a from the particular data ID field. These error detection 10 servo address mark decoded from patterns contained within the servo sector 38. A servo address mark will include at least one flux transition pattern which is not going to be mistaken for any legal data pattern in accordance with the selected data code.

In the present example, the design of a unique servo sector address mark is complicated by the presence of data zones, one or more of which may have a pattern which so resembles a servo address mark as to cause confusion within the servo loop. Accordingly, it has by a data zero triad pattern, i,e., 1000000000000 1000000000000 10 000 010 0 provides a very robust and reliable servo address mark. This design takes into account the 1,7 RLL coding employed in the data zones. This coding pattern implies that there may be a legal data pattern of 10000000 (i.e. a flux transition followed by seven zero flux transition intervals at the particular data rate). The actual time period for any legal 1,7 coding pattern employed within any one of the data zones will not equal or exceed the time period of the 14 T pattern within the servo sector. When bit shift tolerance of the present invention is taken into account, in which a 13T pattern will be decoded as a 14T pattern, the maximum time period cannot equal or exceed a 12T (servo frequency) time period. While it is conceivable that noise and other conditions might give rise to the detection of a data field pattern mistakenly thought to be a 14T pattern, the occurrence of such a pattern, followed immediately by another like 14T pattern, followed by a servo data bit zero pattern is most unlikely. Once the servo address mark is found, a servo sector timer is restarted, so that the next servo pattern may be located. The operation of the state machines which decode the 3T 14T and data bit one or zero patterns is discussed in much greater detail hereinafter. While the present patterns for the servo address mark are preferred, other patterns may be employed with very satisfactory results. For example, the first 14T code violating pattern may be followed by a data bit zero pattern which is then followed by a second 14T pattern. Also, the servo address mark patterns (and track identification numbers) may be recorded and/or decoded from patterns in alternating servo sectors, etc. While it is not necessary for each servo pattern to include all of the digital head position servo is realized by employing the information available in all of the fields as depicted.

The A burst, B burst and C burst fields 52, 56 and 60 are used in realizing an edge servo which is more particularly described with aspects of the present invention in the referenced, commonly assigned and copending parent U.S. patent application Ser. No. 07/569,065, filed on Aug. 17, 1990, now U.S. Pat. No. 5,170,299 the disclosure of which is hereby incorporated by reference. The servo data recovery circuit 130 of the present invention is primarily directed to the decoding of the servo address mark and the track number. However, before discussing the servo circuit, an overview of an exemplary disk drive data storage subsystem 100 incorporating the present invention follows.

# Head and Disk Assembly 100

Turning now to FIG. 5, a head and disk assembly 100 5 of an exemplary fixed disk drive data storage subsystem 5 is depicted in an isometric exploded assembly view. The head and disk assembly 100 includes a base 102 preferably formed as a precision injection casting. The base 102 includes a continuous peripheral sidewall 103 10 and thereby defines an interior space. A micropore filter 103 filters out any particles from air circulating within the interior space due to rotation of the disk 10. A stamped aluminum cover 104 fits over sidewall 103 of the base casting 102. The cover 104 is securely mounted 15 to the base 102 by four screws: one at each corner. A gasket 106 provides a hermetic seal between the base 102 and the cover 104 and provides a fully enclosed and sealed interior space for the disk 10 and a head actuator assembly 116, as well as for other component parts. A 20 breather filter element 105 mounted on the inside of the cover 104 enables internal air pressure to equalize with the external ambient air pressure.

Knife blade protrusions 108 extend upwardly and outwardly from the peripheral flange 103 of the base 25 encasing the coil 122 and engages an actuator latch casting 102 and bite into the cover 104, when it is clamped onto the base casting 102 and compresses the gasket 106. The protrusions 108 provide positive electrical grounding points between the base 102 and cover 104 and prevent electromagnetic interference or radio 30 frequency interference (EMI/RFI) from reaching the interior space enclosed thereby. Further details of the EMI/RFI suppression preferably employed are set forth in a commonly assigned U.S. patent application Ser. No. 07/674,385 filed on Mar. 25, 1991 by co-inven- 35 tor Thomas A. Tacklind and entitled "EMI/RFI Reduction for Head And Disk Assembly", the disclosure of which is incorporated herein by reference.

A printed circuit board 110 is mounted to the bottom of the base 102 by screws and carries all of the electron- 40 ics of the disk drive subsystem 5 (except for a read channel integrated circuit mounted on a plastic film circuit substrate 142 included within the enclosed interior space of the head and disk assembly 100 in order to be closer to the data transducer heads 138 and therefore 45 reduce the electrical noise on the sensitive read channel. The circuit board 110 also includes interface power and signal connectors. A plastic film 112 provides electrical isolation between the circuit board 110 and the bottom of the metal base 102. 50

A spindle assembly 114 is formed integrally with the base 102 and includes an in-hub DC brushless spindle motor assembly 115. The data storage disk 10 is clamped by the clamp 13 upon the rotating spindle assembly 114. The In-hub spindle motor 115 rotates the 55 driving currents to the coil 122 and to provide signal spindle assembly 114 relative to the base 102 at a predetermined constant angular velocity, most preferably 3600 rpm.

A mass balanced rotary actuator assembly 116 is included within the interior space defined by the base 60 102 and the cover 104. The actuator includes a rotary mounting block 118 which is mounted to bearings 120 journalled to a mounting post 121 which is press-fit into a dimensioned cylindrical opening defined by the base 102. A flat, wedge-shaped coil 122 is integrally molded 65 around an extension of the mounting block 118 with a suitable molding compound and may contain a masscounterbalance in order to counterbalance the actuator

assembly 116 and remove e.g. gravitational influences as the drive 5 is positioned in any relative orientation.

A magnet assembly includes a lower flux return plate 124 of suitable ferromagnetic material, such as low carbon steel. Two highly magnetized flat permanent magnets 126 are attached to the lower flux return plate by a suitable adhesive and have magnetic poles extending from major faces, one of the magnets providing a north pole (N) and the other of the magnets providing a south pole (S). The coil 122 is positioned so that one coil leg moves across the north pole face while the other coil leg moves across the south pole face as the actuator 116 moves throughout its limited range of angular displacement. Movements of the actuator are induced by passing direct currents through the winding of the coil 122, and actuator direction is determined by current flow direction. An upper flux return plate 128 completes the magnetic circuit and defines a magnetic gap through which the actuator coil 122 freely passes. Elastomeric bumpers 130 provide inner and outer crash stops for limiting the amount of angular displacement in a manner which does not cause harm to the delicate sliders carrying the thin film or MIG heads 136.

An integral latch arm 132 extends from the molding assembly 133 which is described in commonly assigned, co-pending U.S. patent application Ser. No. 07/696.629 filed on May 7, 1991, and entitled "Bistable Magnetic-/Electromagnetic Latch for Disk File Actuator", now U.S. Pat. No. 5,208,713, the disclosure of which is herein incorporated by reference.

Load beams 134 are mounted to arm extensions of the rotary mounting block 118 and support data transducer heads 136 most preferably formed as thin film elements, or formed as MIG heads, upon sliders which fly in very close proximity to the data storage surfaces of the disk 10, such as at about 4.5 to 5 microinches above the surface of the disk 10. Longitudinally reinforced loading tabs 138 extend from the load beams 134 beyond the heads and sliders 136 and are used to load initially the heads 136 onto the data surface 10 during drive assembly. Further details of the loading tabs are described in commonly assigned, copending U.S. patent application Ser. No. 07/610,306filed on Nov. 6, 1990, and entitled "Data Head Load Beam for Height Compacted, Low Power Fixed Head and Disk Assembly", now U.S. Pat. No. 5,027,241, the disclosure of which is hereby incorporated by reference.

A circuit subassembly 140 is formed upon a flexible plastic film substrate and includes a read channel preamplifier, write driver and head select circuit 142 which leads to a thin flexible plastic film connection cable 144 which attaches to the rotary mounting member 118 of the rotary actuator 116 in order to supply the electrical connections to the heads 136. Another cable 146 ends in a thin film plug which is engaged by a connector mounted on the circuit board 110. The flat plastic film cable 146 passes between the base 102 and the cover 104 to enable electrical connections from the subassembly 140 to pass through to the outside and connect to the circuit board 110.

As shown in FIG. 7A, the integral disk spindle and motor 114 includes a cylindrical portion 150 of the base 102. Two bearings 152 and 154 are secured within the cylindrical portion 150 by a suitable adhesive. A rotating central shaft 156 is press-fit into a cup-shaped flange 158 which aligns and supports the disk 10. The disk clamp 13 is clamped over the flange 158 and bears down on the disk 10 by virtue of a central screw 160 (FIG. 5). Returning to FIG. 7A, the flange 158 includes an outer annular extension 162 which is located beyond the central opening of the disk 12. Affixed to this annular exten- 5 sion 162 is an annular flux return plate 164; and, attached on the inside to the flux return plate 164 is a segmented permanent magnet 166. The segmented permanent magnet has alternating polar faces which adjacently face poles formed by stacked stator plates 168. 10 Driving coils 170 are wound around the stator plates 168. A three phase arrangement is presently preferred. Suitably phased driving currents passing through the coils 168 cause the magnet 166 to rotate, and with it the flange 158 forming the disk spindle 114. By forming the  $^{15}$ spindle 114 and DC brushless motor integrally with the base 102, a number of improvements are realized. The spindle is always aligned, and it does not shift its position relative to the actuator position over repeated thermal cycling as was the case frequently with separately <sup>20</sup> attached direct drive spindle motors of the prior art. Vertical offset is also likewise minimized. The base 102 may be strengthened at the vicinity of the spindle 114 and result in less susceptibility to vibrations in use.

depicted in FIG. 7B. This assembly 100A encloses two data storage disks 10A and 10B and four data transducer heads 136 which are positioned commonly by the rotary actuator 116. Arm extensions 118A, 118B and 118C of the rotary member 118 secure and align the four load beams associated with the four heads. The rotary flange 158A is slightly enlarged in the height dimension in order to accomodate the disks 10A and 10B, and a spacer ring 174 is placed between the two disks and a 35 top clamp 13A, which is secured to the flange 158A by plural screws 160. In addition, magnets 126 are also secured to the upper flux return plate 128 in order to provide additional magnetic flux for the actuator coil necessitated by the greater mass of the actuator.

The overall height of the assembly 100A is about 0.75 inch, which is slightly greater than the overall height of the single disk assembly 100 (0.61 inch). Other than these differences, the head and disk assembly 100A is substantially the same as the assembly 100. (The flux 45 in FIG. 8, the generally vertical dashed line represents return plates 124 and 128, and the magnets 126 of the rotary actuator 116 are not shown in FIG. 7B.) The width of both assembilies 100, 100A is approximately 2.76 inches, and the depth is approximately 4.00 inches.

One or more Hall effect sensors 172 may be placed 50 adjacent to the spindle magnet 166 in order to determine relative position of the magnetic poles thereof relative to the fixed poles of the stator 168 in order to provide feedback control for commutation of the motor, particularly to prevent reverse rotation of the spin- 55 dle motor at startup. A motor driver circuit (FIG. 8), such as a type HA134915 spindle motor driver, manufactured by Hitachi, may be employed in conjunction with the Hall effect sensors 172 to provide appropriately commutated driving currents to the three phase 60 coils 170 of the spindle motor for use within a single disk drive embodiment. A spindle motor for a dual disk drive embodiment is also preferably driven by the type HA134915 spindle motor driver, manufactured by Hitachi and connected in a configuration to provide greater 65 power output to the spindle motor.

A type ULN8901LBW driver made by Sprague, or equivalent, may be used if the Hall sensors 172 are not

used to commutate the three-phase windings of the brushless DC spindle motor.

A plurality of e.g. thin film data transducer heads 136 are respectively associated with opposite major data storage surfaces of the data storage disk 10, or disks 10A and 10B. The data transducer heads 136 are preferably mounted to the in-line aligned reversed flange load beams 134. The thin film heads 136 are formed on ferrite sliders which operate conventionally in a contact-startstop relationship with respect to the data surface, and they "fly" above and very close (e.g. within about 5 microinches) to the surface during operations upon an air bearing formed by disk rotation and airflow. Alternatively, and particularly when the disks 10 are formed of a glass substrate, the heads and sliders 136 may be dynamically loaded onto and unloaded from the data storage disk in accordance with the teachings of the referenced and commonly assigned U.S. patent application Ser. No. 07/610,306, now U.S. Pat. No. 5,127,241.

@Magnetic flux transitions comprising both user data and servo sector data 38, are written by or read by the selected head 136 during data write or read operations. The data read by the head 114 is passed through the preamplifier circuit 142 (FIG. 5) which also provides A slightly enlarged head and disk assembly 100A is <sup>25</sup> head selection and write driving functions during data write operations. A conventionally available integrated circuit, such as the SSI 32R4610 four channel thin film head read/write device made by Silicon Systems, Inc., Tustin, Calif., or equivalent, is presently preferred for implementation of the circuit 142. The circuit 142 enables four separate heads **136** to be individually selected. As already noted, the integrated circuit 142 is preferably mounted within a space defined within the head and disk assembly 100 upon a thin plastic film (Mylar) flex circuit substrate which carries conduction traces leading to connections at the external printed circuit board 10 carrying the other circuit elements of the disk drive 5. The circuit 142 is placed as close to the heads 136 as possible in order to reduce connection lead length, and 40 to improve signal to noise ratios for each of the heads 136.

# Electrical Block Diagram of Drive Subsystem 5

Turning now to the system block diagram provided a dividing line between the electromechanical head and disk assembly 100 and the printed circuit board 110 which carries all of the electronic circuit elements shown in FIG. 8 other than the preamplifier 142. Interconnections between the HDA 100 and board 110 are by way of thin film flex circuit conductor plugs and thin film receptor connectors mounted on the circuit board 110. One connector serves the rotary actuator 116 and preamplifier circuit 142, while another connector serves the spindle motor 114, for example.

The drive subsystem 5 has one read/write data transducer head 136 for each data surface. The signal path for the read channel begins at the selected read/write head 136. As the magnetic flux transitions recorded in a particular track pass under a corresponding head, lowamplitude differential output currents are induced in the head. These signals are amplified in the read channel preamplifier 142 and are then transmitted onto the main circuit board 110 via the flex circuit.

The circuit board 110 contains nine major electrical elements, together with a number of related discrete components, such as transistors, diodes resistors, capacitors, connectors, etc. The major electrical elements

30

include a pulse detector ASIC 200, a data sequencer and control ASIC 202, an interface ASIC 204, a single SRAM of either e.g. 8 kilobytes or 32 kilobytes capacity functioning as a cache buffer random access memory 206, a master microcontroller 208 having an on-board 5 multiplexed analog to digital converter 209 and being controlled by a control program contained in time-critical part within an internal program memory and contained in balance in an external program memory 210, an actuator low pass filter 212, an actuator driver 214, 10 hereby incorporated by reference. and a spindle motor driver 216.

The pulse detector ASIC 200 further amplifies, filters and processes the read signal in order to reduce ambiguities, such as drop-ins and drop-outs; and then converts the signal from the serial encoded data to a synchro- 15 nized data stream with its accompanying data clock. In order to perform these functions, the ASIC 200 includes a pulse detector section 220 which converts the analog flux transitions into data pulses having transitional edges. Gain of the pulse detector circuit 220 is con- 20 trolled by an AGC control circuit 222 which is also contained within the circuit 220. The pulse detector circuit 220 decodes the analog flux transitions into shaped digital edges or pulses representative of raw (unsynchronized) encoded data.

The circuit 200 also includes a write pre compensation circuit 224 for precompensating data to be written to the disk 10 during data writing operations, and a plurality of peak detector circuits 226 for detecting peak amplitudes of the A and B or C servo bursts contained 30 within the servo sectors 38 during track settling operations at the end of track seeking operations, and during track following or "on-track" operations. The three bursts A, B and C occur within each servo sector 38. During on-track operations the A and C bursts will be 35 at half amplitude; and for even tracks the B bursts will be at full amplitude, while for odd tracks the B bursts will be at minimum amplitude. The A and B bursts are used during settle mode at the end of a track seeking 40 operation.

The circuit 200 also includes a phase locked loop (PLL) 228 for locking onto incoming data at a data rate predetermined for the particular data zone, as previously explained. A data frequency synthesizer 230 is provided within the circuit 200 for selectively generat- 45 ing the data transfer rate applicable within each track zone and supplying the synthesized frequency to the PLL 134. Frequency selection is under the control of the master controller 208. The circuit 200 is preferably implemented as a single +5 volt low power VLSI pack- 50 cuit 204 and the microcontroller 208. Address lines 243 age, such as a type DP8491 made by National Semiconductor Corporation, or equivalent.

# Data Sequencer and Control Circuit 202

The data sequencer and control circuit 202 is also a 55 single low power VLSI package operating on a +5 V power supply, and it includes a servo data timer and decoder circuit 232. The circuit 202 also includes a pulse width modulator 234 for sending strings of controlled duty cycle pulses generated from values sup- 60 plied from the microcontroller 208 through the servo low pass filter 212 to the servo driver circuit 214. In response to the incoming control values from the low pass filter 212, the servo driver circuit 214 generates and applies bidirectional drive currents to the coil 122 of the 65 rotary actuator 116. Essentially, a digital servo is realized, as described in the referenced commonly assigned U.S. Pat. No. 4,669,004. However, there are improve-

ments over that disclosure which are described in the referenced copending parent U.S. patent application Ser. No. 07/ 569,065 filed on Aug. 17, 1990, entitled "Edge Servo For Disk Drive Head Positioner", now

U.S. Pat. No. 5,170,299, and commonly assigned, copending U.S. patent application Ser. No. 07/710,172, filed on Jun. 4, 1991 and entitled "Servo Data Recovery Circuit for Disk Drive Having Digital Embedded Sector Servo" the respective disclosures of which are

The circuit 202 also includes an encoder/decoder 236 which decodes incoming data from e.g. 1,7 RLL code to NRZ format, and encodes data from the host in NRZ format into e.g. 1,7 RLL code. The encoder/decoder 236 is substantially as described in a commonly assigned U.S. Pat. No. 4,675,652, the disclosure of which is hereby incorporated by reference. In actuality, while the encoder/decoder 236 is shown as a separate structural element, it is actually a part of a data sequencer 238. The data sequencer is described hereinafter in greater detail in conjunction with FIG. 11. It basically functions to sequence serial by bit coded data to and from the storage disk 10 and serial by byte unencoded data to and from the cache buffer memory 206 as con-25 trolled by a buffer memory controller 240 which is also included within the circuit 202.

The circuit 202 further includes a spindle motor speed regulation circuit 242 which monitors disk rotational speed by any suitable method, such as feedback from the motor driver circuit 216. Disk rotational speed may be determined by comparing actual disk rotation time with a crystal reference. Speed up or slow down signals are sent by the motor control circuit 242 to the motor driver 216. The master control circuit 202 also includes a microprocessor interface 244 which connects directly to an internal control bus structure over which control data and control address values are sent to and from the programmed digital microcontroller 208.

Finally, the circuit 202 includes a master clock 246 which generates all of the clocking signals for the drive subsystem 5 and supplies them e.g. to the microcontroller 208, the pulse detector circuit 200, the interface circuit 204 and throughout the other circuits contained within the master control circuit 202.

#### Bus Structures

A microcontroller multiplexed address-data bus 241 extends between the microcontroller interface circuit 244 of the master control ASIC 202, the interface cirfrom the microcontroller 208 pass into the microcontroller interface circuit 244 wherein latches hold certain bit positions (A15-A13, A7-A0) of the address values and supply them to the external program memory 210 over an address bus 245. Other address bit position values (A12-A8) are supplied directly from a port of the microcontroller 208 to the external program memory over an address bus 210. A buffer data bus 248 interconnects the buffer controller 240, the buffer memory 206 and the interface control ASIC 204. Buffer memory addresses generated by the buffer controller 240 are supplied to control addressing of the buffer memory 206 over a buffer address bus 249. A control bus 250 extends between the interface circuit 204 and the memory controller 240 to synchronize and facilitate data transfers between the interface 204 and the buffer memory 206. A SCSI or AT interface bus 251 extends from the interface control ASIC 204 to a host computing system or

other appliance with which the storage subsystem 5 is operatively connected for data storage and retrieval. Host commands and user data blocks to be written to disk 10 are received from, and subsystem status and user data blocks retrieved from the disk 10 are sent to, the 5 host system. A bus terminator 253 may be included to provide impedance matching for the data and control lines of the external bus 251.

FIG. 9 illustrates in greater detail the various lines and buses which lead to and from the functional circuits 10 and elements included within the master control circuit 202. Two output lines 213 extend from the PWM 134 to the servo low pass filter 212. Motor control lines 217 extend between the spindle motor driver 216 and the spindle speed monitor circuit 242. Gate control lines 15 from the servo controller 232 extend to the peak detectors 226 of the circuit 200. AGC control lines 235 extend to the AGC circuit 222 of the same ASIC 200. A number of lines collectively identified by the reference numeral 237 extend between the encoder/decoder 236 20 and sequencer 238, and the circuits 142 and 200.

# Servo Timer and Decoder 232 (FIG. 10)

The servo data decoder circuit 232 includes a synchronizer 252 for synchronizing incoming raw data 25 from the pulse detector 220 to an internal clock, a sync and unique pattern detector slave state machine 254 for detecting servo sync and a unique pattern within a servo address mark field, a data reader slave state machine 256 for decoding data bits included within the 30 servo address mark field 68 in index bit field 70 and a Gray coded data field 72 indicating the particular surface and track number. The servo timer and decoder circuit 232 also includes a sector timer 258 which generates and puts out expected servo sector times within the 35 circuit 232 based upon detection of each servo address mark, and a delay timer 260 for timing delay periods associated with centerline burst fields included within each servo sector 38, and for putting out delay gates, the gates being used to control operation of correspond- 40 ing ones of the peak detectors 226.

Functional operations within the servo decoder circuit 232 are managed and supervised by a servo master state machine 262 which monitors the slave state machines 254 and 256 and thereby determines detection 45 within a particular servo sector 38 of the servo address mark, an index mark, and collects the bits comprising the Gray coded track identification number. This track identification number is then passed to the microcontroller 208 which decodes it and determines head position during track seeking and settling operations of the drive.

FIG. 10 sets forth a more detailed block diagram of the servo data recovery circuit 232, including the particular control and data lines passing between the raw 55 data synchronizer 252, sync and 14T detector 254, data reader master state machine 262, delay timer 260, sector time 258, and pulse width modulators 234.

The raw data synchronizer 252 comprises four D type flip-flops 180, 182, 184, and 186, and a two-input 60 exclusive OR gate 188 configured so as to eliminate any metastable states resulting from the incoming unsynchronized raw data. The data synchronizer 252 functions to frame incoming raw data on the servo data path from-the pulse detector 220 with e.g. positive duty cy-65 cles of a master clock signal occurring at 16 MHz. The 16 MHz master clock signal is put out by the master clock 246. It will be remembered that the basic clock

frequency for the period T of the FIG. 4 servo sector data is 16 MHz, however spindle rotational tolerances and jitter for example may cause slight variations in the incoming raw data rate, and its phase will not normally be aligned with the phase of the reference clock signal.

In order to synchronize the raw data pulses from the pulse detector 220 to the 16 MHz signal from the master clock 246, the flip flops 180, 182, 184 and 186 are clocked on rising edges of the clocking signal. By the time that the incoming raw data pulses propagate through the logic network comprising the synchronizer 252, they have been offset in time so as to occur with the next rising edge of the 16 MHz reference clock.

The output from the raw data synchronizer 252 is a data input (DIN) signal which is passed via a line 264 to