# United States Patent [19]

## Simionescu et al.

### [54] EMBEDDED CACHE MANAGER

- [75] Inventors: Horia Cristian Simionescu, Foster City; Luan Kha Bui, Fremont, both of Calif.; James A. Henson, Bend, Oreg.; Clifford M. Gold, Fremont, Calif.

- [73] Assignee: Quantum Corporation, Milpitas, Calif.

- [21] Appl. No.: 09/327,293

- [22] Filed: Jun. 7, 1999

### **Related U.S. Application Data**

- [63] Continuation-in-part of application No. 08/940,074, Sep. 29, 1997, abandoned.

- [51] Int. Cl.<sup>7</sup> ...... G06F 12/12

### [56] **References Cited**

### **U.S. PATENT DOCUMENTS**

| 5,005,089 | 4/1991  | Thanos et al  | 395/77.08 |

|-----------|---------|---------------|-----------|

| 5,204,963 | 4/1993  | Noya et al    | 395/750   |

| 5,247,653 | 9/1993  | Hung          | 395/500   |

| 5,283,875 | 2/1994  | Gibson et al  | 395/400   |

| 5,317,713 | 5/1994  | Glassburn     | 395/425   |

| 5,465,343 | 11/1995 | Henson et al  | 395/439   |

| 5,603,002 | 2/1997  | Hashimoto     | 395/440   |

| 5,680,570 | 10/1997 | Rantala et al | 395/440   |

| 5,696,931 | 12/1997 | Lum et al     | 395/440   |

| 5,701,450 | 12/1997 | Duncan        | 395/595   |

# [11] Patent Number: 6,141,728

## [45] Date of Patent: Oct. 31, 2000

| 5,754,889 | 5/1998 | Packer  | 395/876 |

|-----------|--------|---------|---------|

| 5,768,617 | 6/1998 | Liu     | 395/825 |

| 5.890.213 | 3/1999 | Sokolov | 711/113 |

Primary Examiner-Eddie P. Chan

Assistant Examiner—Kevin L. Ellis

Attorney, Agent, or Firm-Michael Zarrabian

### [57] ABSTRACT

A method for managing data blocks in a cache buffer defining date block segments, and for automatically transferring data into and out of the cache buffer. A cache list comprises a plurality of entries each including information identifying a corresponding cache segment, and a set of consecutive data blocks stored in the cache segment. Providing cache status for a requested set of date blocks includes traversing the cache list to locate entries identifying the starting data block in the requested set, and consecutive data blocks successively following the starting data block without interruption, and identifying as a missing data block the first data block in said succession, including said starting data block, not identified in any entry. The missing data block is used to provide status: a full hit if the missing data block is not in the requested set; a miss if the missing data block is the starting data block in the requested set, or a partial hit otherwise. In response to a write command for a new set of data, the cache list is traversed to locate all entries identifying sets of data blocks overlapping the new set. If a located entry identifies a set of data blocks fully overlapping the new set, there is a full hit. If no entry is located, there is miss. Otherwise, there is a partial hit. The new set can be automatically transferred into a predesignated buffer area selected by the cache manager.

### 68 Claims, 30 Drawing Sheets

**U.S.** Patent

Oct. 31, 2000

# FIG. 5B

FIG. 6

FIG. 8

FIG. 9

FIG. 13

**U.S. Patent**

Oct. 31, 2000

Sheet 13 of 30

6,141,728

FIG. 15

**U.S.** Patent

6,141,728

FIG. 18A

| XFER MODE               |                    |                                                 |              |      |                                         |

|-------------------------|--------------------|-------------------------------------------------|--------------|------|-----------------------------------------|

|                         | >                  | +                                               | _            | CHK= |                                         |

| GET ENTRY<br><u>632</u> |                    |                                                 |              |      | get invalid                             |

| CHKENTRY1<br><u>646</u> | SRCH > =ES         | EE = ES+EVALID                                  | T1 = -SRCH   |      | get hit1                                |

| CHKENTRY2<br><u>648</u> | EE > SRCH          | NUMFOUND = EE-<br>SRCH                          | T1 = -ES     |      | get hit2                                |

| HIT1<br><u>621</u>      |                    | T1 = SRCH-ES                                    |              |      | SCRCHLBA = EE,<br>ENTRADDR = 0          |

| ACT1<br><u>656</u>      |                    | T1 = T1 + OFFSET                                | T2 = -ESIZE  |      |                                         |

| ACT2<br><u>658</u>      | sideA = T1 < ESIZE | T1 = T1-ESIZE?!A?<br>RCNT = T1-ESIZE<br>(!A?FF) |              |      | HnsBfrptr rollover for<br>hardsegment ? |

| ACT3<br><u>660</u>      |                    | HBptr = T1 + EBPTR                              | RCNT = -RCNT |      |                                         |

| ACT4<br><u>662</u>      | HBptr < Highbptro  | HBptr = HBptr – Bsizeo                          |              |      | HBptr rollover in Buffer<br>?           |

FIG. 20A

FIG. 20B

FIG. 23

|                                | A     |            |            | B      | С      | D<br>WE=EE |  |

|--------------------------------|-------|------------|------------|--------|--------|------------|--|

| I WS EE<br>ENTRY               | WS>ES | w5∠EE<br>0 | WE>ES<br>1 | 0<br>0 | 0<br>0 | 0<br>0     |  |

| ES EE<br>WR<br>ENTRY           | 1     | 0          | 1          | 1      | 0      | 0          |  |

| K WR<br>E                      | 0     | 0          | 1          | 1      | 0      | 0          |  |

| L WR<br>E                      | 0     | 0          | 1          | 1      | 1      | 0          |  |

| M WR<br>E                      | 0     | 0          | 1          | 0      | 0      | 1          |  |

| N WR E                         | 1     | 0          | 1          | 0      | 0      | 0          |  |

| WR   E                         | 0     | 0          | 1          | 0      | 1      | 0          |  |

| $(P) \qquad WR \\ E \qquad E$  | 1     | 0          | 1          | 0      | 0      | 1          |  |

| $\bigcirc \qquad \frac{WR}{E}$ | 0     | 0          | 1          | 0      | 1      | 1          |  |

| No                             |       | 1          | 1          |        |        |            |  |

| Overlop WR                     |       | 0          | 0          |        |        |            |  |

| ·                        |                   |                                                                                                                 |                 |               |                                    |

|--------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------|-----------------|---------------|------------------------------------|

| WR LBA SCAN<br>702       | >                 | +                                                                                                               | _               | CHK=          |                                    |

| GET ENTRY<br><u>710</u>  |                   |                                                                                                                 |                 |               | get invalid                        |

| CHKENTRY1<br><u>712</u>  | WE > ES cmp1      | EE = ES+VALID                                                                                                   | T1 = -ES        |               | get hit1                           |

| CHKENTRY2<br>714         | WS < EE cmp2      | $X_LO = WE - T1$                                                                                                | 71 = -WS        |               | get hit2                           |

| HIT1 (gt1)<br><u>716</u> | WS > ES gt1       | X_HI = EE-T1                                                                                                    | $T1 = -X_LO$    | WS = ES (eq1) | domark; !gt1 -> !trimlo            |

| HIT2 (gt2)<br><u>718</u> | WE > EE gt2       | (!gt1) VALID = VAL-XLO                                                                                          | (gt1) T1 = X_HI | WE = EE (eq2) | >> dotrimhi,lo,noth,invalid        |

| ACT1<br><u>720</u>       |                   | (Thi) VALID = V-Xhi<br>(Thi & !hard):SIZE = Nvalid<br>(Tlo & hard) OFFST = O+Xlo<br>(Tlo & !hard):SIZE = SZ-Xlo |                 |               | Operations depend on which<br>trim |

| ACT2<br>722              |                   | TIo: STBLA=+XIo                                                                                                 | T2 = -SIZE      |               |                                    |

| ACT3<br><u>724</u>       | OFFSET +X > SIZE  | (Tlo & hard): OFFS ?-Size<br>(Tlo & !hard) Ebptr = +Xlo                                                         | T2 = −Bufsizeo  |               | OFFSET gets dec if > size          |

| ACT4<br><u>726</u>       | Ebptr > Highbptro | Ebptr = ?-Bufsizeo                                                                                              |                 |               | EBPtr wraps around Bfr             |

| CRAMWR<br><u>732</u>     |                   |                                                                                                                 |                 |               |                                    |

(A) = EOFFSET: Leave things alone

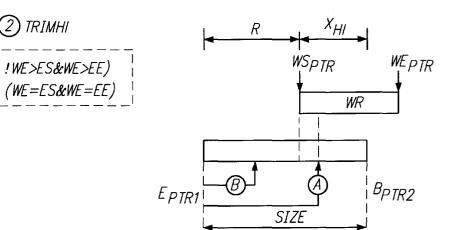

Modify size valid  $OFFSET=E_{OFFSET} - X_{LO}$   $BPTR=WE_{PTR}$   $SIZE=ESIZE - X_{LO} = R$   $=B_{PTR2} - WE_{PTR}$  VALID=EVALID if  $VALID \leq E_{SIZE} - E_{OFFSET}$  $else=E_{SIZE} - E_{OFFSET}$

NEWLBA=ESTLBA

$$\begin{aligned} \widehat{B} &= EOFFSET: agreement BPTR, ELBA.... \\ size valid \\ OFFSET=0 \\ BPTR=WE_{PTR} \\ SIZE=E_{SIZE} - X = R \\ SIZE=E_{SIZE} - X = R \\ ALID=0 if VALID \leq WE_{PTR} - (E_{OFFSET} + E_{BPTR}) \\ else=VALID - (WE_{PTR} - (E_{OFFSET} + E_{BPTR})) \\ else=VALID - (WE_{PTR} - (E_{OFFSET} + E_{BPTR})) \\ = E_{STBLA} + T(X - E_{OFFSET}) \end{aligned}$$

(A) OFFSET

OFFSET=0 BPTR=E<sub>PTR</sub> SIZE=ESIZE-X<sub>HI</sub>=R =WS<sub>PTR2</sub>-E<sub>BPTR1</sub> VALID=0 if EVALID ≤ E<sub>SIZE</sub> -E! OFFSET else VALID=E<sub>VALID</sub>-(ESIZE-E<sub>OFFSET</sub>) (Max=New Size) NEWLBA=E<sub>STLBA</sub> +(E<sub>SIZE</sub> -E<sub>OFFSET</sub>)

(B) = OFFSET

OFFSET=E<sub>OFFSET</sub> BPTR=E<sub>PTR1</sub> SIZE=E<sub>SIZE</sub> -X=R =WS<sub>PTR</sub>-E<sub>BPTR1</sub> VALID=EVALID if EVALID ≤ R-E<sub>OFFSET</sub> else=R-E<sub>OFFSET</sub>

NEWLBA=ESTLBA

# FIG. 27B

|                                  |                                          | smdec                                                                           | ode                                         |                                           | FIG. 28                                                                               |

|----------------------------------|------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------|-------------------------------------------|---------------------------------------------------------------------------------------|

| WR BFR SCAN                      |                                          |                                                                                 |                                             |                                           |                                                                                       |

| 704                              | >                                        | +                                                                               | _                                           | CHK=                                      |                                                                                       |

| GET ENTRY<br><u>710</u>          |                                          |                                                                                 |                                             |                                           | get invalid                                                                           |

| CHKENTRY1<br>                    | WE > ES cmp1                             | EE = ES+ESIZE                                                                   | 71 = -ES                                    |                                           | get hit1                                                                              |

| CHKENTRY2<br>                    | WS < EE cmp2                             | $X_{LO} = WE - T1$                                                              | T1 = -WS                                    |                                           | get hit2                                                                              |

| HIT1 (gt1)<br><u>716</u>         | WS > ES gt1                              | $X_{HI} = EE - T1$                                                              | $T1 = -X_LO$                                | WS = ES (eq1)                             | domark; !gt1 –> !trimlo                                                               |

| HIT2 (gt2)<br><u>718</u>         | WE > EE gt2                              | (!gt1) VALID = VAL-XLO                                                          | (gt2) T1 = -X_HI                            | WE = EE (eq2)                             | gt2->!trimlo<br>>> dotrimhi,lo,invalid                                                |

| ACT1<br><u>720</u>               | Tlo: Xlo > Eoffset                       | Tlo: NewSize=Sz–Xlo<br>Thi: R = Sz–Xhi                                          | T2 = -Eoffset                               |                                           | >>Tlo: !sideA ?                                                                       |

| ACT2<br><u>722</u>               | Thi: R > Eoffset                         | TloA: T1A = Esz–Eoffset<br>TloB: T1B = Xlo–Eoffset<br>Thi: NewSize=Sz–Xhi       |                                             |                                           | >> Thi: !sideA ?                                                                      |

| ACT3<br><u>724</u>               | TloA: Evalid > T1A<br>TloB: Evalid > T1B | TloA: Noffset = Eoffset-Xlo<br>ThiA: T2A = Esz-Eoffset<br>ThiB: T2B = R-Eoffset | ТюВ: ТХ = -Т1В                              | lastlba = highbptro>><br>Nbptr ? Lowbptro | TloA (Nvalid = ? T1A:Evalid)<br>TloB (Nvalid = ? TBC:doinv)<br>doinv:next > CRAMWR    |

| ACT4<br>726                      | ThiA: Evalid > T2A<br>ThiB: Evalid > T2B | TloB1: Nvalid = Evalid-T1B<br>ThiA: NstIba = EstIba+T2A                         | ThiA: $TX = -T2A$                           |                                           | ThiA (Nvalid = ? TBC: doinv)<br>ThiB (Nvalid = ? T2B: Evalid)<br>doinv: next > CRAMWR |

| ACT5<br><u>728</u>               |                                          | TloB1: Nstlba = Estlba-T1B<br>ThiA1: Nvalid = Evalid-T2A                        |                                             |                                           | TloB1: Nvalid = ? Nsize:<br>Nvalid                                                    |

| ACT6<br><u>730</u>               | ThiA1: Nvalid > Nsize                    |                                                                                 |                                             |                                           | ThiA1: Nvalid = ? Nsize:<br>Nvalid                                                    |

| WRCRAM<br><u>732</u>             |                                          |                                                                                 |                                             |                                           | Tlo, TloB: Nbptr = WE<br>TloB, ThiA: Noffset = 0                                      |

| TrimLo=!gt2 & !eq2<br><u>735</u> | ? TrimHi =(gt1 & gt2) <br>(gt1 & eq2)    |                                                                                 | Invalidate = (!gt1 &<br>gt2)   (!gt1 & eq2) |                                           |                                                                                       |

15

25

30

### **EMBEDDED CACHE MANAGER**

### Reference to Related Application

This is a continuation-in-part of U.S. patent application Ser. No. 08/940,074 filed on Sep. 29, 1997, now abandoned.

### FIELD OF THE INVENTION

The present invention relates to cache systems. More 10 particularly, the invention relates to a cache buffer manager and a method and apparatus for managing a cache buffer embedded within a storage device for transferring data between a host device and the storage device.

#### BACKGROUND

A cache buffer is a high speed memory buffer inserted between a host and a storage device, such as a disk drive, to store those portions of the disk drive data currently in use. Since the cache, typically implemented as semiconductor memory, is several times faster than the disk drive, using the cache can reduce the effective disk access time. Conventionally, a firmware cache manager has controlled transfer of data into and out of the cache buffer, and has managed the data stored in the cache buffer. A typical cache manager utilizes a cache directory containing data block memory addresses, and control bits for cache management and access control. The cache manager searches the cache directory to fetch and store data blocks in the cache buffer, and uses a replacement strategy to determine which data blocks to retain in the cache buffer and which to discard.

However, a major disadvantage of existing cache managers is slow operational speed in detecting data blocks in the cache buffer. This is because the cache manager must search through the cache directory and examine the entries therein to determine if one or more requested data blocks are in the cache buffer. This is a time consuming process, typically performed by a microprocessor executing instructions requiring multiple clock cycles. As such, existing cache managers commonly search for the first of a set of consecutive data blocks, and rarely search for all the data blocks in the set.

Most cache buffers are organized into multiple segments consecutive set of data blocks may exist as multiple subsets stored in different cache segments. Another disadvantage of existing cache managers is that, although all the data blocks of a requested set may exist as subsets stored in different cache segments, because of their slow operational speed, 50 existing cache managers can only search for the subset containing the first data block in the requested set. As a result, such cache managers record a partial hit and attempt to transfer the remaining subsets into the cache buffer from the disk drive. This is a very time consuming task that causes 55 cache hit. replacement of existing, and most likely useful, data blocks, wastes precious cache buffer space, and prevents seamless delivery of the requested consecutive data blocks to the host.

Yet another disadvantage of existing cache managers is their inability to effectively buffer data from the host. Every 60 time the host issues a write command, the cache manager is interrupted to store data from the host into the cache buffer and communicate with the disk drive. As such, there is little or no parallelism between the host and the cache manager in handling data. Further, the cache manager must take the time 65 to execute its replacement strategy to store the data into the cache buffer and keep the cache directory coherent. As

multiple write commands are issued by the host, existing cache managers have no ability to buffer the data, and keep the cache coherent, without multiple interruptions.

There is, therefore, a need for a method of managing a cache buffer which quickly, and efficiently, detects data in the cache buffer. There is also a need for such a method to quickly, and efficiently retrieve data stored in the cache buffer. There is also a need for such a method to quickly, and efficiently, buffer multiple data transfers into the cache buffer. There is also a need for an improved cache manager architecture embedded within a random access mass storage device, such as a hard disk drive.

### SUMMARY

The present invention satisfies these needs.

In one embodiment, the present invention provides method of managing the data in a cache buffer including data segments, and transferring data into and out of the cache buffer. The method of the present invention can be used to 20 respond directly to read and write commands from a host, and to provide a cache manager with cache status information such as cache miss, partial hit and full hit information. A cache list for organizing the data comprises a plurality of entries each including information identifying a corresponding cache segment, and a set of consecutive data blocks stored in the cache segment. Providing cache status for a requested set of data blocks includes traversing the cache list to locate entries identifying the starting data block in the requested set, and consecutive data blocks successively following the starting data block without interruption, and identifying as a missing data block the first data block in said succession, including said starting data block, not identified in any entry. The first missing data block is used to deter-35 mine status: a full hit if the missing data block is not in the requested set; a miss if the missing data block is the starting data block in the requested set; or a partial hit otherwise. Further, in case of a full or partial hit, the identity of said missing data block is also provided. The cache status infor-40 mation can be used by the cache manager to transfer the requested set of data blocks out of the cache buffer. Alternatively, the step of traversing the cache list can include locating entries identifying the starting data block, and consecutive data blocks successively following the starting each storing a set of data blocks. As a result, a logically 45 data block up to, and including, the last data block of the requested set. Therefore, only cache status of the requested data blocks is checked. After locating an entry identifying a data block next in sequence to the last data block of the requested set, indicating a full hit, the requested data blocks can be transferred out. Similarly, after locating a missing data block, all data blocks from the starting data block up to the missing data block can be transferred out. Additionally, this approach enables the firmware to fetch any missing or additional data blocks from disk, as in the case of a partial

> In response to a write command for a requested set of data, the cache list is traversed to locate all entries identifying sets of data blocks overlapping the new set to be written to cache. If a located entry identifies a set of data blocks fully overlapping the new set, there is a full hit. If no entry is located, there is a miss. Otherwise, there is a partial hit. This information can be reported to the cache manager to transfer the new set of data blocks into the cache buffer. The new set can be automatically transferred into a predesignated buffer area selected by the cache manager. In that case, each of said located entries is marked invalid so that they are not considered in response to subsequent read

5

25

50

commands. In case of a partial hit or a miss, the above steps can further include locating an entry previously marked invalid, and updating the information in the invalid entry to identify: (1) the predesignated buffer as a corresponding data segment, and (2) the new set as the set of data blocks stored in the corresponding data segment.

In case of a full hit, where a located entry identifies said starting data block, and the sequence of the last data block of the set identified in the entry matches or succeeds that of the last data block of the new set, the new set can be transferred to the corresponding data block locations in the segment identified in the entry. When data is transferred into the cache buffer in case of a full or partial hit, each located entry can be updated to identify a set of data blocks which do not overlap the new set.

The present invention provides efficient and quick scan of the cache list to find every data block requested and transfer the data if necessary. It saves the cache manager from the labor intensive task of searching for data, which reduces performance of the cache manager. Given a starting data block in a requested set, unlike existing systems, the present invention searches to find data blocks beyond the requested data blocks. As a result, after traversing the cache list, the cache manager can be provided with cache status based on the requested set, including a miss, partial hit, full hit, and the first missing data block which needs to be read into the cache buffer from the disk drive.

The transfer operation provides the ability to perform real-time data gathering of discontinuous pieces of data in the cache buffer, and to seamlessly provide the host with a  $_{30}$ single stream of data. This is because a cache list traverse provides information about what data is in the cache buffer and where it is. Therefore, the data can be transferred without spending time between successive searches to find the next piece of data to transfer to the host.

The present invention also provides buffering of data from the host. Multiple write commands from the host are buffered until the cache manager decides to write the buffered data to disk. This allows the cache manager to operate without interruption by every write command. Since subsequent writes can overlap one another, the present invention provides marking and trimming capabilities to resolve overlaps as described above. As such, all overlaps can be resolved in real-time, keeping the cache list coherent, and allowing for subsequent reads.

### BRIEF DESCRIPTION OF THE DRAWINGS

These and other features, aspects and advantages of the present invention will become better understood with regard to the following description, appended claims and accompanying drawings where:

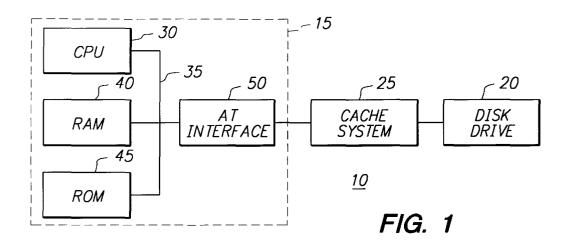

FIG. 1 is a block diagram of an example of a computer architecture in which the present invention can be implemented.

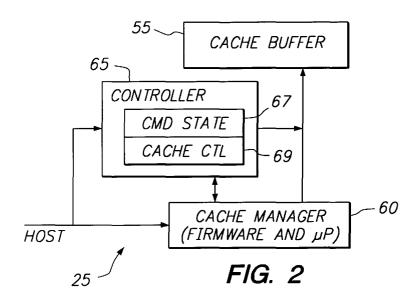

FIG. **2** shows a block diagram of a cache system including  $_{55}$ a cache buffer, a firmware-implemented cache manager, and a hardware controller including a command state machine and a cache control state machine according to principles of the present invention;

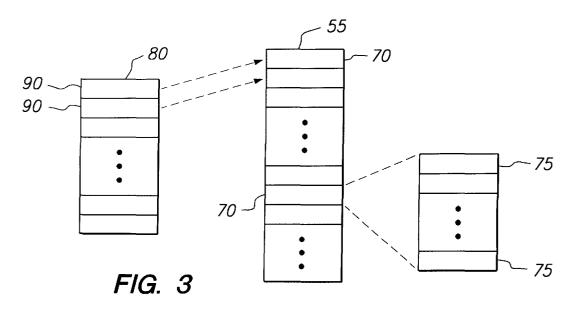

FIG. **3** shows a block diagram of a cache buffer organized into segments, and an embodiment of a cache list according to principles of the present invention for managing transfer of data into and out of the cache buffer;

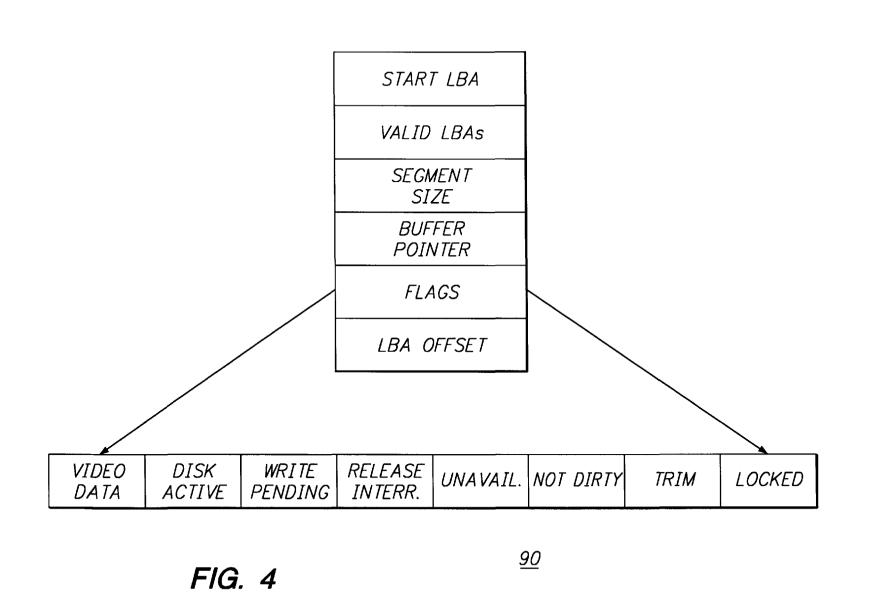

FIG. 4 shows an example cache list entry;

command state machine implementation of the command processing aspect of the present invention;

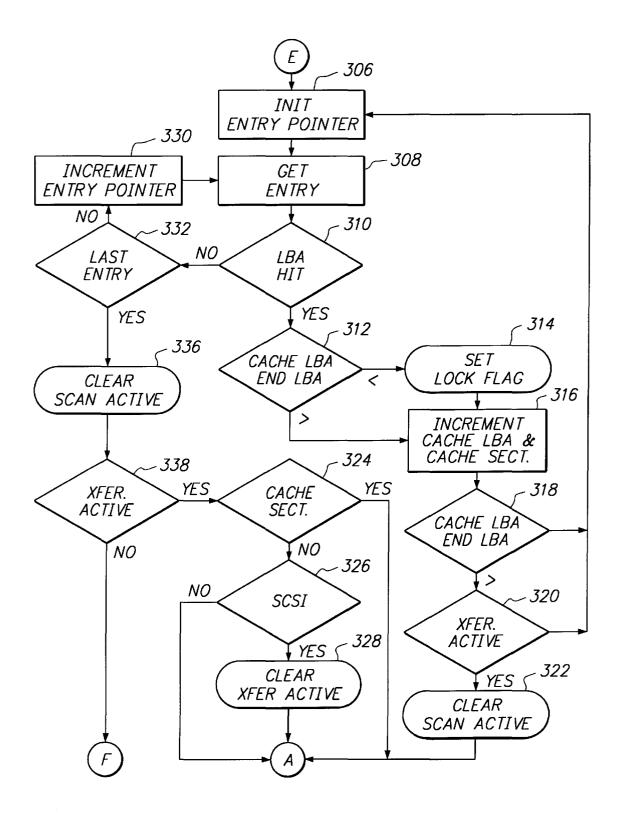

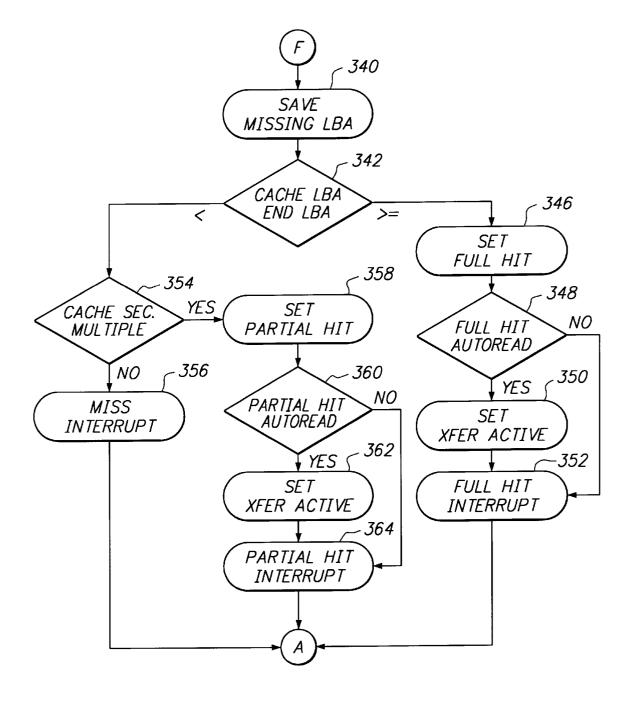

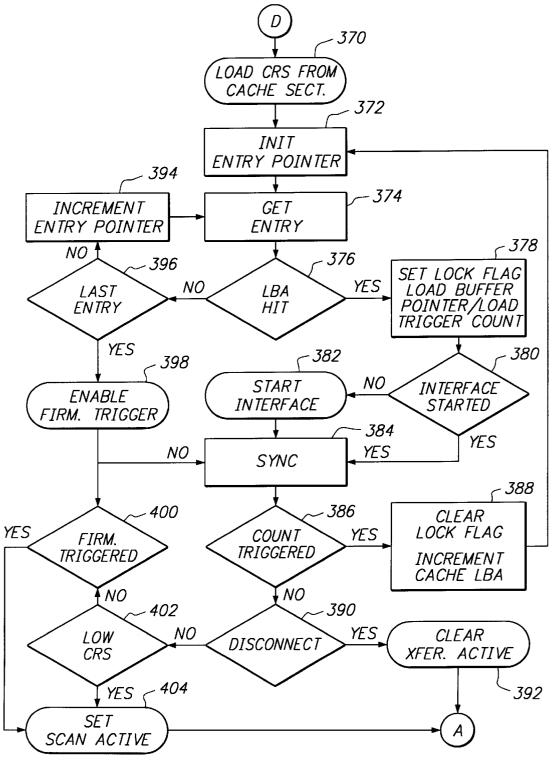

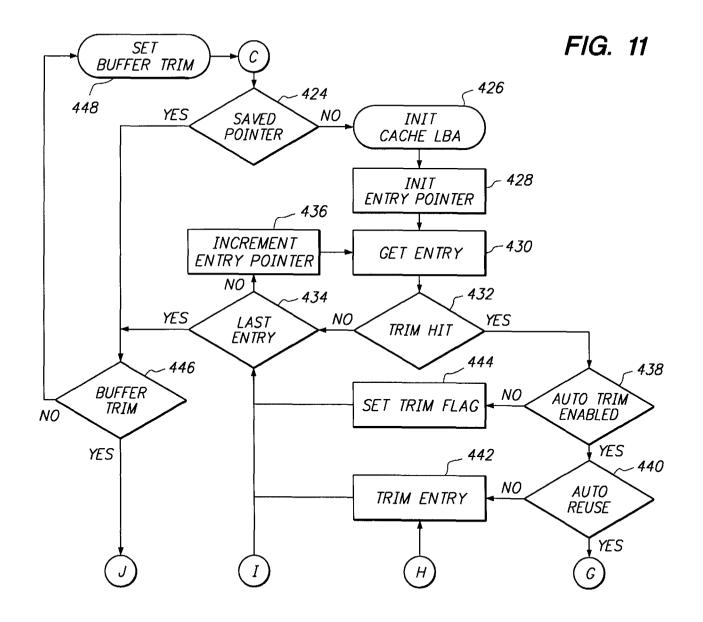

FIGS. 6-13 show a flowchart illustrating an example of a cache control state machine implementation of cache buffer management according to principles of the present invention:

FIG. 14 is a block diagram of a host-connected hard disk drive including a cache controller having a single cache controller state machine in accordance with principles of the present invention.

FIG. 15 is a more detailed block diagram of the cache 10 controller of FIG. 14.

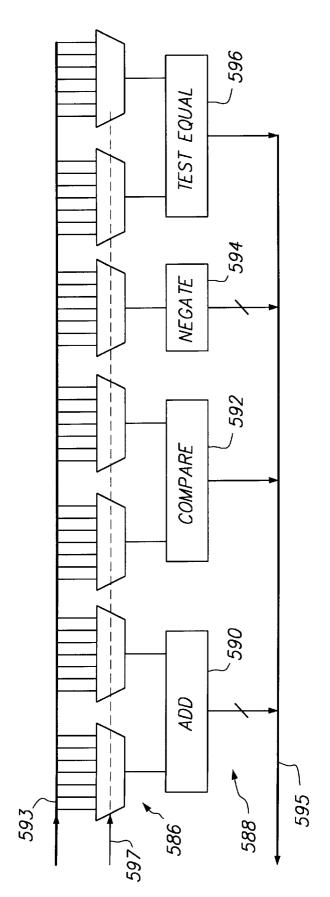

FIG. 16 is a more detailed block diagram of a dedicated arithmetic logic unit of the FIG. 15 cache controller.

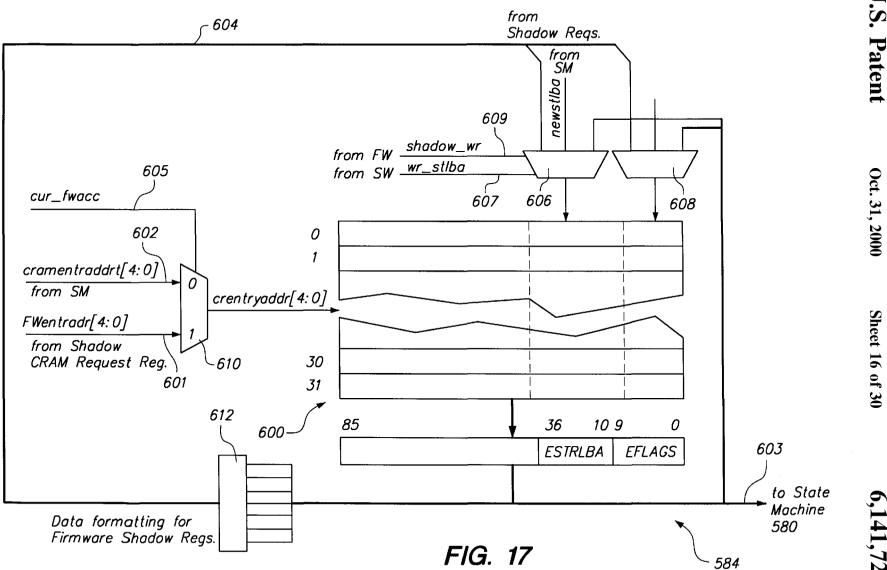

FIG. 17 is a more detailed block diagram of a cache list random access memory unit of the FIG. 15 cache controller.

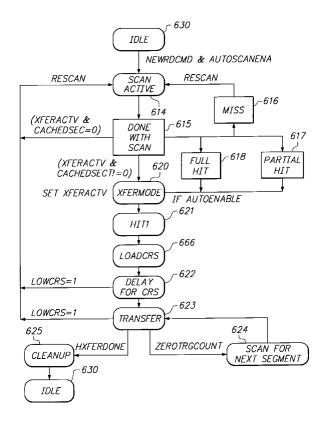

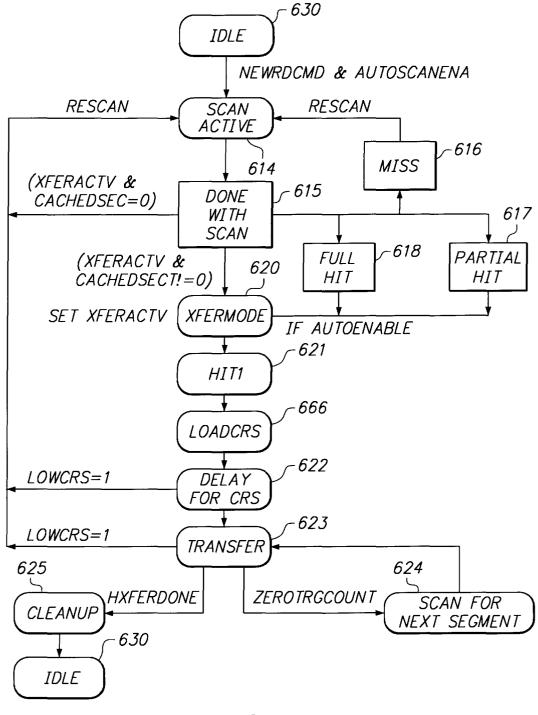

FIG. 18 is a state flow diagram of an overall cache read process carried out by the FIG. 15 cache controller.

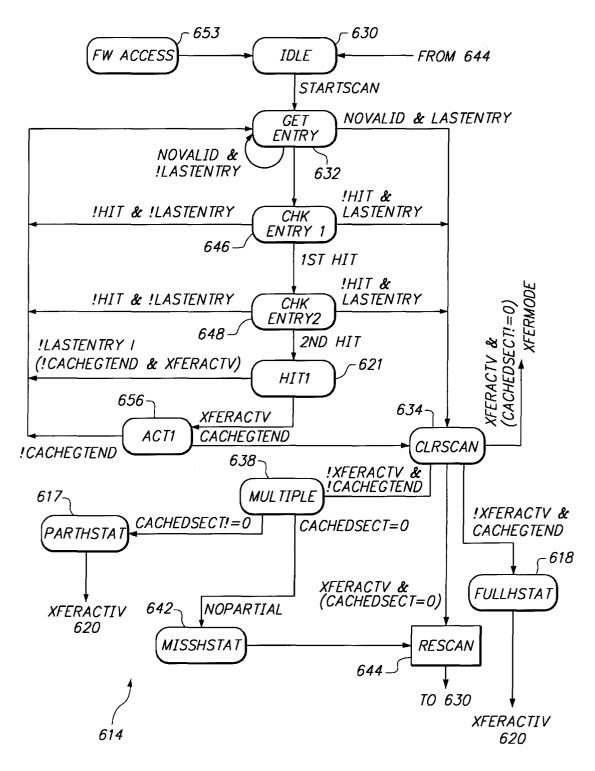

FIG. 18A is a state flow diagram of a cache read scan operation of the FIG. 15 cache controller state machine <sup>20</sup> within the overall cache read process flow of FIG. 18.

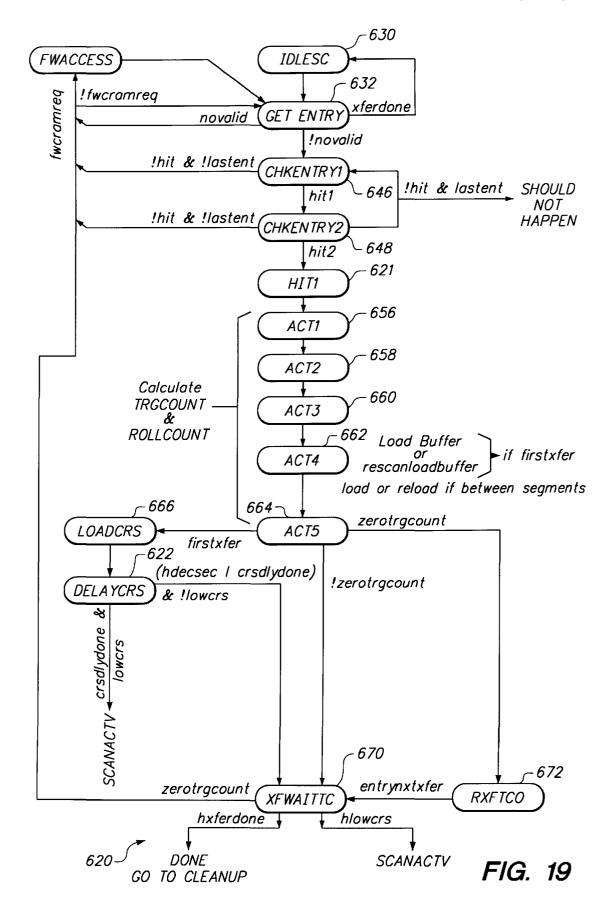

FIG. 19 is a state flow diagram of a cache read transfer process of the FIG. 15 cache controller state machine.

FIG. 20 is a functional matrix diagram showing simultaneous parallel processing steps carried out by the arithmetic logic unit of the FIG. 15 cache controller during the FIG. 19 cache read transfer process.

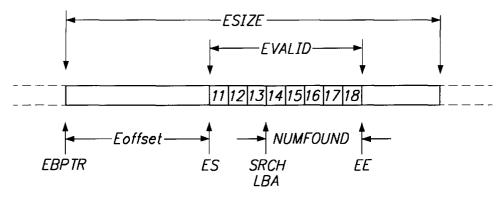

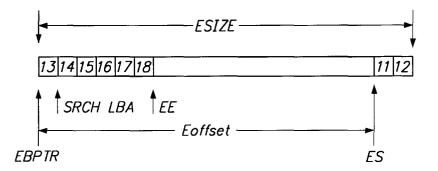

FIGS. 20A, 20B and 20C provide several cache read transfer process examples further illustrating the FIG. 20 processing steps.

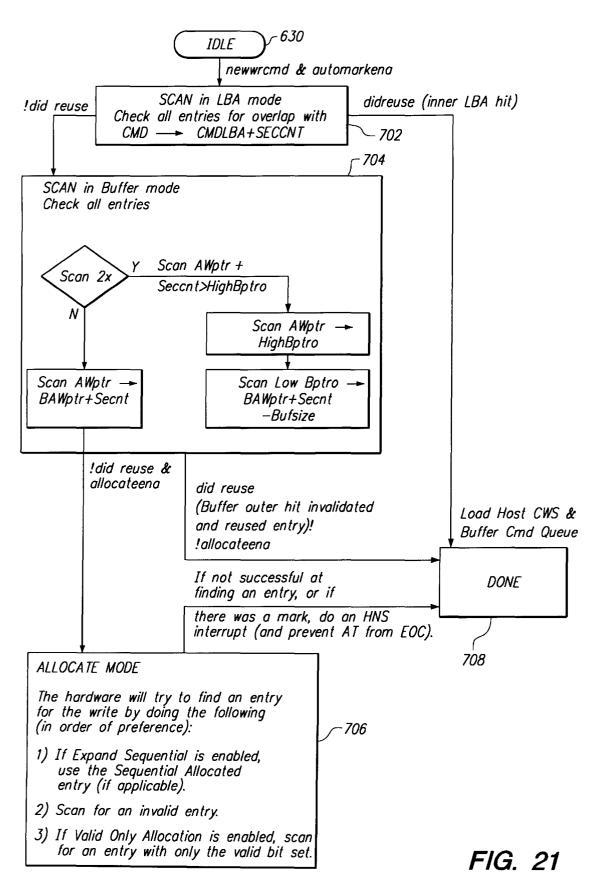

FIG. 21 is a state flow diagram of a cache write command scan flow process of the FIG. 15 cache controller state machine in handling host write commands.

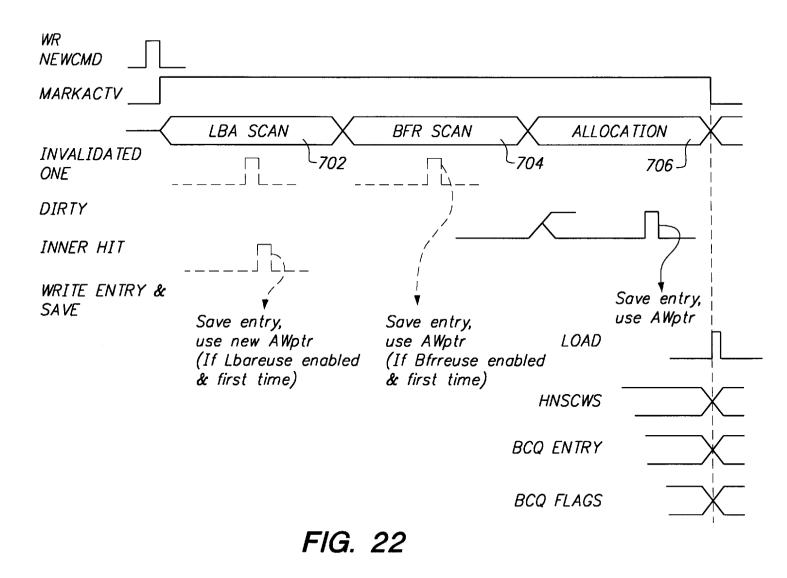

FIG. 22 is a series of timing diagrams illustrating write 35 scan process timing of the FIG. 15 cache controller state machine in accordance with the FIG. 21 state flow diagram.

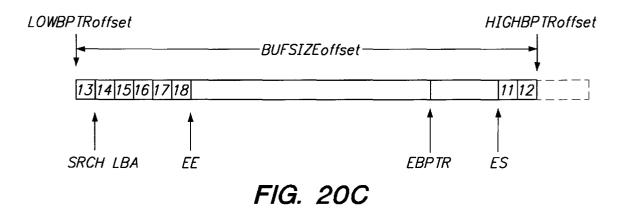

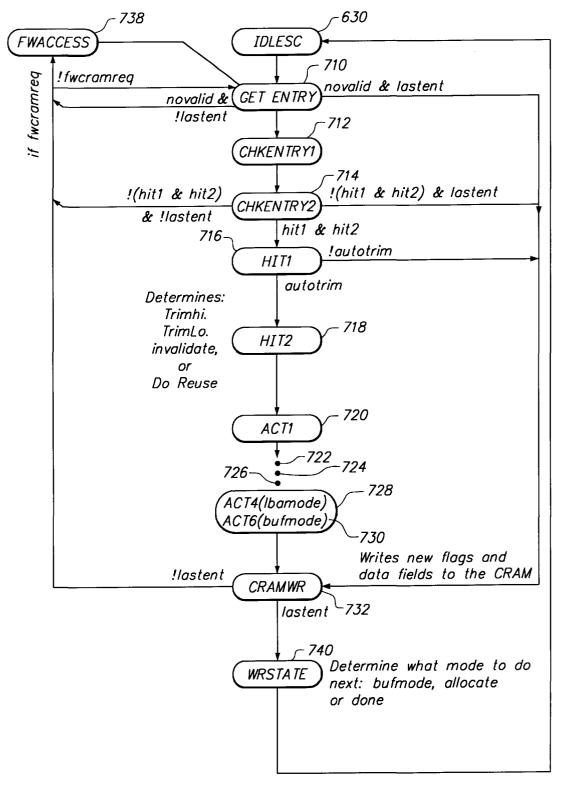

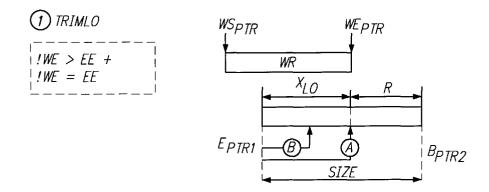

FIG. 23 is a state flow diagram of cache write scan of the FIG. 15 cache controller state machine carried out for write LBA scan and for write buffer scan modes of FIG. 21.

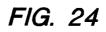

FIG. 24 is a table showing all possible overlap conditions which may be detected during an LBA mode write scan process.

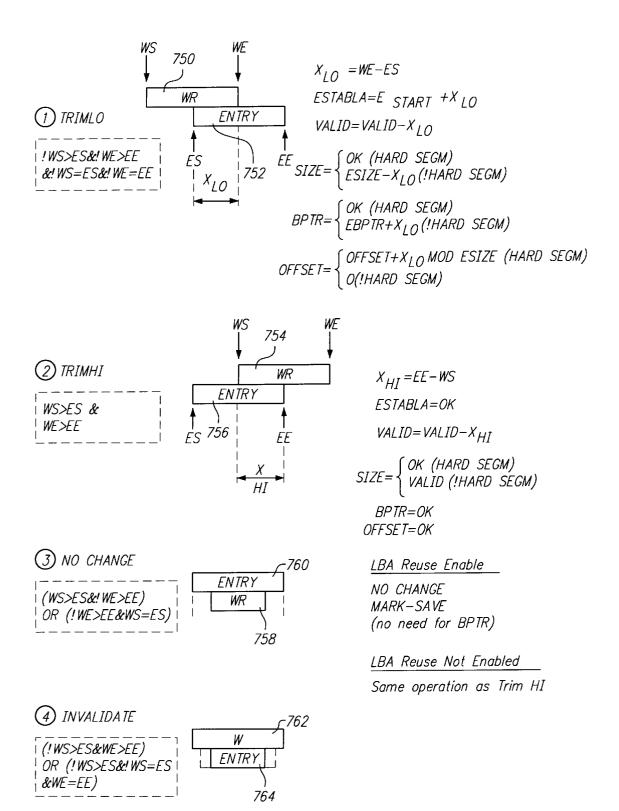

FIG. 25 shows four cache trim operations, one of which may be performed as a result of the LBA mode write scan 45 process.

FIG. 26 is a functional matrix diagram showing simultaneous parallel processing steps carried out by the arithmetic logic unit of the FIG. 15 cache controller during write LBA scan mode operation of the cache controller state machine in accordance with the FIG. 23 cache read transfer process.

FIGS. 27A and 27B show two cache trim operations, one of which may be performed as a result of the buffer mode write scan process.

FIG. 28 is a functional matrix diagram showing simultaneous parallel processing steps carried out by the arithmetic logic unit of the FIG. 15 cache controller during write buffer scan mode operation of the cache controller state machine carried out in accordance with the FIG. 23 cache read transfer process. 60

### DESCRIPTION OF PREFERRED EMBODIMENTS

FIG. 1 shows a block diagram of an exemplary computer FIGS. 5a-5b show a flowchart illustrating an example 65 system 10 in which a method embodying aspects of the present invention can be implemented. The computer system 10 typically includes a host 15 and a storage device, such as

5

15

25

30

35

40

45

a disk drive 20, interconnected via a cache system 25. The cache system 25 is utilized to buffer transfer of data between the host 15 and the disk drive 20 according to the present invention. As those skilled in the art will recognize, the present invention is capable of being implemented in a system having other storage devices. Additionally, the host 15 generally refers to a host/AT interface, which one skilled in the art will recognize to include, for example, a CPU 30 interconnected via a Bus 35 to a RAM 40, ROM 45 and an AT interface 50.

Referring to FIG. 2, a first embodiment of the presently preferred cache system 25 includes a cache buffer 55 and a cache manager 60 for storing data into and retrieving data from the cache buffer 55. In one aspect, the present invention provides a method of managing the data in the cache buffer 55, and transferring data into and out of the cache buffer 55 is implemented into a hardware controller 65 including a command state machine 67 and a cache control state machine 69. The method of the present invention can be used to respond directly to read and write commands from 20 the host 15, and to provide the cache manager 60 with cache status information such as cache miss, partial hit, and full hit information. The cache manager is most preferably implemented as firmware executed by a microprocessor.

Referring to FIG. 3, the cache buffer 55 is organized into a plurality of cache segments 70 each for storing one or more data blocks 75. To manage the data segments 70 and the data stored therein according to the present invention, a cache list 80 comprises a plurality of entries 90 each including information identifying: (1) a corresponding cache segment 70, and (2) a set of consecutive data blocks 75 stored in the cache segment 70.

Providing cache status for a requested set of data blocks 75 includes traversing the cache list 80 to locate entries 90 identifying the starting data block in the requested set, and consecutive data blocks 75 successively following the starting data block without interruption, and identifying as a missing data block a first data block in said succession of consecutive data blocks 75, including said starting data block, not identified in any entry 90. The missing data block is then used to provide cache status including: a full hit if the missing data block is not in the requested set; a miss if the missing data block is the starting data block in the requested set; or a partial hit otherwise. Further, in case of a full or partial hit, the identity of said missing data block is also provided. The cache status information can then be used by the cache manager 60 in order automatically to transfer the requested set of data blocks 75 out of the cache buffer 55.

As such, the cache manager 60 is provided with cache  $_{50}$ status for the requested data blocks, and a look ahead into the cache buffer 55 for all data blocks 75 therein which are in logical sequence with the staring data block. Alternatively, the step of traversing the cache list 80 can include locating entries 90 identifying the starting data block, and consecu- 55 tive data blocks 75 successively following the starting data block up to, and including, the last data block of the requested set. Therefore, only cache status of the requested data blocks 75 is checked.

In response to a read command, after locating an entry **90** 60 identifying a data block next in sequence to the last data block of the requested set, indicating a full hit, the requested data blocks 75 are transferred out by: (1) denoting the starting data block as a running data block, (2) traversing the cache list 80 to locate the particular entry 90 identifying the 65 running data block, (3) accessing the data segment 70 corresponding to the located entry 90, (4) transferring as

many of data blocks 75 therein within the range of the requested set, and (5) if the sequence of the last data block of the requested set succeeds that of the last data block of the set identified in the located entry **90**, denoting as the running block, the block next in sequence to said last block of the identified set, and repeating steps (2)-(4).

Similarly, in response to a read command, after locating a missing data block, all data blocks 75 from the starting data block up to the missing data block are transferred by: (1) <sup>10</sup> denoting the starting data block as a running data block, (2) traversing the cache list 80 to locate the entry 90 identifying the running data block, (3) accessing the data segment 70 corresponding to the located entry 90, (4) transferring as many of data blocks 75 therein within the range of the requested set, and (5) if the sequence of the missing data block succeeds that of the last data block of the set identified in the located entry 90 by at least two, denoting as the running block, the block next in sequence to said last block of the identified set, and repeating steps (2)-(4).

To service a write command for a requested set including a starting data block, the cache list 80 is traversed to locate all entries 90 identifying sets of data blocks 75 overlapping the requested set. If a located entry 90 identifies a set of data blocks 75 fully overlapping the requested set, there is a full hit. If no entry 90 is located, there is miss. Otherwise, there is a partial hit. This information can be reported to the cache manager 60 to transfer the requested set of data blocks 75 into the cache buffer 55.

Finding overlaps includes comparing the range of the data blocks 75 in the requested set to the range of data blocks 75 identified in each entry 90. Four basic types of comparisons include range checking for the starting data block of the requested set, for the last or ending data block of the requested set, for the starting data block of each set identified in the entries 90, and for the ending data block of each set identified in the entries 90.

In order to minimize fragmentation, the requested set is preferably stored in a contiguous area of the buffer 55. Therefore, the requested set can be automatically transferred into a predesignated buffer area selected by the cache manager 60. In that case, each of said located entries 90 is marked invalid so that they are not considered in response to subsequent read commands. In case of a partial hit or a miss, the steps can further include locating an entry 90 previously marked invalid, and updating the information in the invalid entry 90 to identify: (1) the predesignated buffer as a corresponding data segment 70, and (2) the requested set as the set of data blocks 75 stored in the corresponding data segment 70.

In case of a full hit, where the located entry 90 identifies said starting data block, and the sequence of the last data block of the set identified in the entry 90, matches or succeeds that of the last data block of the requested set, the requested set can be transferred into the corresponding data blocks 75 in the segment 70 identified in the entry 90.

When data is transferred into the cache buffer 55 in case of a full or partial hit, each located entry 90 can be updated to identify a set of data blocks 75 which do not overlap the requested set. In case of a buffer overlap, where the predesignated buffer overlaps a data segment 70 identified in an entry 90, all such entries 90 are updated to resolve overlaps by identifying a segment size which does not overlap the predesignated buffer.

Referring to FIGS. 2 and 4-13, an exemplary embodiment of the present invention, implemented as two interacting state machines 67 and 69 is described. The exemplary implementation is primarily specific to an AT interface. However, those skilled in the art recognize, the present invention is also capable of being implemented for other interfaces between a host device and a storage device.

The state machines include a Command State Machine 5 (CM) 67 and a Cache Control State Machine (CSM) 69. Both state machines 67, 69 can be implemented in a logic circuit, such as an ASIC, as described below. Generally, CM 67 stores commands issued by the host and keeps a command history. CSM 69 performs operations in response to 10 the commands to manage transfer of data into and out of a cache buffer 55. The cache buffer 55 is a portion of memory starting at a low address and proceeding to a high address whereupon it rolls over to the low address. The buffer 55 is organized into a variable number of segments, up to at least 15 thirty-two, each for storing a plurality of data blocks (Command Logical Block Address -LBA). In the following description the cache manager 60 is referred to as "firmware" as it is typically, although not necessarily, implemented as a firmware-programmed microprocessor embed- 20 ded within the storage device, e.g. disk drive.

CM 67 includes a Command FIFO in external RAM, comprising at least eight Command entries. For interfaces where command queuing is supported (SCSI) the Command FIFO already exists. Each Command entry includes: 25

Command LBA—the first LBA required by the Command.

Transfer Count-the number of LBAs to be transferred.

- Buffer Pointer/Cache Entry Pointer—the memory address of a Segment where data has been stored, or the pointer <sup>30</sup> to a Cache Entry describing that Segment.

- Referring to FIG. 4, the CSM 69 includes a Cache List comprising thirty-two entries each entry 90 including:

- Start LBA—lowest LBA stored in a corresponding Segment. 35

- Valid LBA—the number of contiguous valid LBAs in the Segment starting with the Start LBA.

- Segment Size—the size reserved for the Segment in the Buffer; expressed as the number of LBAs that can be  $_{40}$  stored therein.

- Buffer Pointer-starting address of the Segment in the Buffer.

- LBA Offset—the offset of the Start LBA relative to the starting address of the Segment. 45

Flags:

Locked—Segment locked by the CSM. Trim—Cache Entry needs to be trimmed by firmware.

Not Dirty—valid Cache Entry.

- Unavailable—set by firmware to prevent CSM from 50 using the Cache Entry.

- Release Interrupt—set by firmware asking CSM to generate an interrupt when the Cache Entry is released.

- Write Pending—there is write data in the Segment.

- Disk Active—the disk drive is reading or writing in the Segment (set by firmware).

55

65

Video Data—data in the Segment can be used for video only.

CM 67 and CSM 69 interact with one another, the 60 firmware 60, the host interface 50 and a disk drive interface 71 through the following registers:

Interrupt Register—includes flags associated with interrupts including:

CSM 69 generated interrupts:

CACHE MISS, PARTIAL HIT and FULL HIT, generated at the end of Detection operation. CLEANUP, generated at the end of a Cleanup operation.

MARK, generated at the end of a Mark operation. Host interface **50** generated interrupts:

- NEW COMMAND, AUTO WRITE and AUTO READ (i.e. type of command).

- Auto Enable Register—Configures CSM **69** to define the extent of its operation. The firmware can configure through this register:

- Auto Scan—when enabled, allows CSM **69** to scan for read hits. If Auto Scan is enabled, then:

- Auto Read Transfer—if there is a Full Hit, the data is transferred automatically.

- Auto Partial Transfer—if there is a Partial Hit, as much data as there is found in cache is transferred automatically.

- Auto Mark—when enabled, the CSM **69** is allowed to Mark for trimming all overlapping segments. If Auto Mark is enabled then:

- Auto Trim—CSM Trims Cache Entries.

- Auto Reuse—When Auto Trim enabled and Full Hit is detected, CSM **69** Reuses Cache Entry Segments, rather than Trims them.

- Auto Allocate—CSM **69** uses invalid Cache Entries to store information pertaining to buffered write commands, including, Start LBA, Valid LBAs, Segment Address, Segment Size and Write Pending flag.

- Auto EOC—CSM **69** writes buffer data and informs the host that write command is complete. Auto EOC allows stacking of write commands. In existing systems, transfer starts, but the host is not informed of its completion, until firmware resolves all overlaps.

The following definitions apply to the description below:

Auto Write interrupt—generated by CM to inform the firmware of Auto Write command.

- Auto Mark Active step—posted by CM 67 to trigger CSM 69 to auto Mark.

- Auto-Command—implies an automatic read or write command.

Command LBA-first LBA in a requested set of LBAs.

- Cache LBA register-used by CSM 69 to Scan.

- Cache Sector register—count of the number of sectors found for transfer.

- Current Write Sector register—containing the number of available sectors for a write.

- End LBA—contains sum of Command LBA and Transfer Count.

Entry Pointer-points to current Cache List entry.

- Full Scan-describe it as compares to regular Scan.

- Lock Flag—used to lock Segments during data transfer.

Maximum LBA—is the LBA boundary of the disk drive.

- Missing LBA register—contains the last LBA sequential to the Start LBA not found in the cache.

- Running LBA—used to scan the buffer, contains the identity of the last LBA Transferred, so subsequent LBAs can be Transferred.

Scan Active step—posted by CM to trigger CSM to Scan. Sector Address—computed based on Segment Address.

Trigger Count Register—loaded with the number of sectors (LBAs) to be transferred out of a Segment with a hit.

### Command State Machine (CM) 67

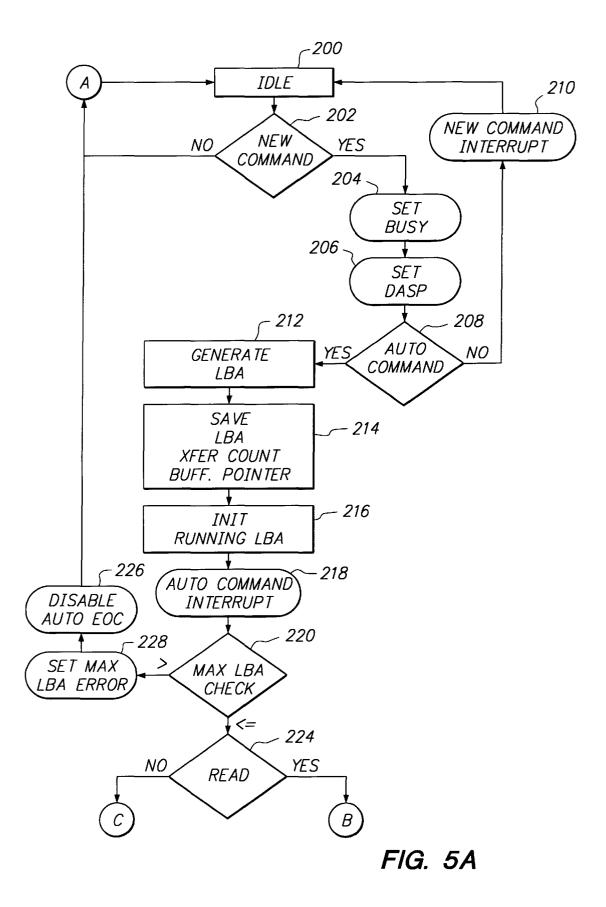

Referring to FIGS. 5*a*–5*b*, the operation of CM 67 is described. CM 67 idles at a step 200 and checks for a New

Command at a step 202. Upon detecting a New Command at step 202, CM 67 sets an AT Interface specific BUSY signal at a step 204 and a DASP signal at a step 206. If the New Command is not an Auto-Command as tested at a step 208, CM 67 generates an interrupt for the firmware to handle the New Command at a step 210. An Auto-Command implies an automatic read or write. If the New Command is an Auto-Command, CM 67 saves the New Command information in the Command FIFO by generating a Command Logical Block Address (LBA) at a step 212, and saves the 10 LBA, a Transfer Count and a Buffer Pointer at a step 214. The Buffer Pointer is provided by the firmware for writing data to a designated portion of the Buffer. CM 67 then initializes the Running LBA register to the Command LBA at a step 216. Having stored the information pertaining to the New Command in the Command FIFO, CM 67 issues an Auto-Command interrupt at a step 218 to inform the firmware that the New Command has been received.

CM 67 then compares the Command LBA with a Maximum LBA at a step 220 to determine if the Command LBA <sub>20</sub> is within the boundaries of the disk drive. If the Command LBA is not within a boundary, then CM 67 sets a Max LBA Error condition at a step 228 and disables Automatic End of Command at step 226 to allow the firmware to deal with the error. If the Command LBA is within the boundary, CM 67 determines if the New Command is a read or a write command at step 224.

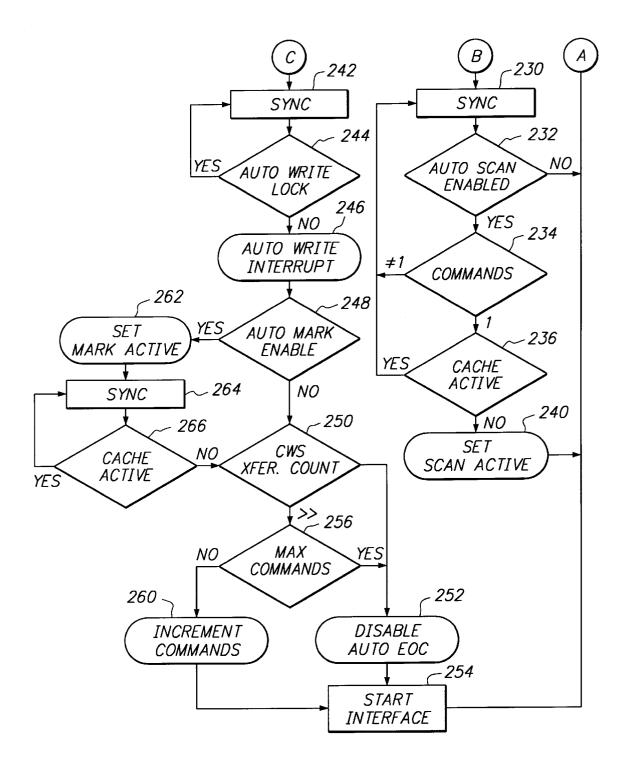

If the New Command is a read command, CM 67 synchronizes its operation with the CSM 69 and proceeds to determine if Auto Scan is enabled at a step 232. If Auto Scan 30 is not enabled, CM 67 is done and proceeds to a step A. If Auto Scan is enabled, Scan still cannot be performed until it is determined that there are no stacked write commands that have unresolved overlaps. To determine such, CM 67 checks if an unresolved command counter does not equal 35 "1" at a step 234. If the counter does not equal "1", CM 67 loops through steps 230-234 until firmware resolves the write command overlaps, which is indicated by the counter being decremented to equal "1". CM 67 then checks if the CSM 69 is active at a step 236. If CSM 69 is active, CM 67 40 loops through steps 230-236 until CSM 69 becomes inactive. Thereafter, CM 67 posts a Scan Active step at step 240 to trigger CSM to Scan, and proceeds to step A.

If the New Command is a write command, CM 67 synchronizes with CSM 69 at a step 242, and proceeds to 45 determine if the firmware has locked the Buffer at a step 244 to prevent a race condition with the hardware. When the Buffer is unlocked, CM 67 generates an Auto Write interrupt at a step 246 to inform the firmware of the Auto Write command. CM 67 then determines if Auto Mark is enabled 50 at a step 248; and, if so, posts a Mark Active step at a step 262 to trigger CSM 69 to auto Mark. CM 67 then waits for CM to complete auto Marking by synchronizing at step 264 and checking if CSM is active at step 266. When CSM 69 has completed auto Marking, CM 67 compares a Current 55 Write Sector (CWS) register, containing the number of available sectors for a write, with the Transfer Count for the write command at a step 250. If there are enough available sectors to completely buffer the write, CM 67 determines if the Command FIFO is full at step 256. If the Command 60 FIFO is not full, CM 67 increments the number of commands stored in the Command FIFO and starts the Interface at step 254 to transfer data from the host store into the Buffer starting from the Buffer Pointer. If the Command FIFO is full, or if there are not enough available sectors to com-65 pletely buffer the write, CM 67 disables Automatic End of Command at step 252, so the firmware completes the

command. CM 67 then starts the Interface at step 254, as above, to transfer as much data into the Buffer as possible, with the firmware completing the command and informing the host. CM 67 then proceeds to step A.

Therefore, CM **67** triggers CSM **69** in two possible ways by posting either: (1) a Scan Active at step **240**, or (2) a Mark Active at step **262**. CM **67** also starts the transfer Interface at step **254** to transfer data.

#### Cache Control State Machine (CSM) 69

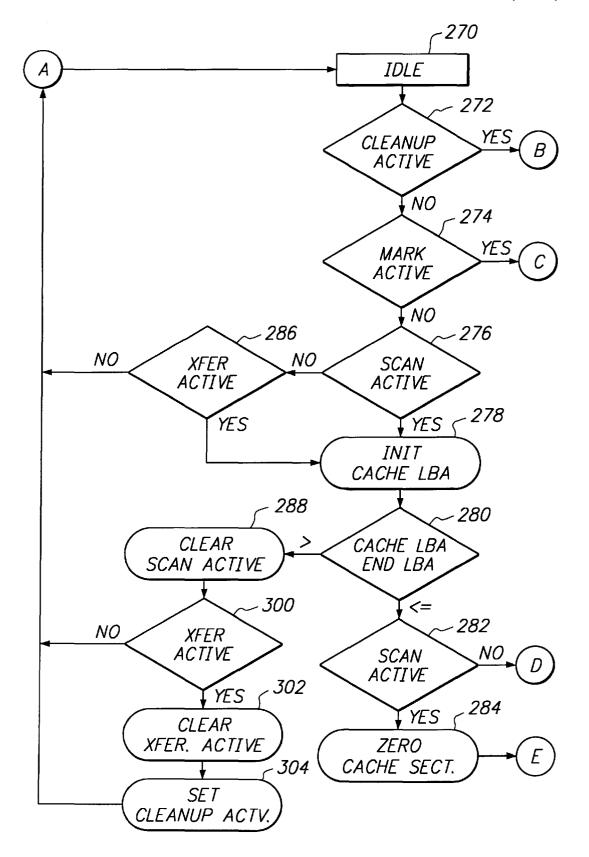

Referring to FIG. 6–13, the operation of CSM 69 is described. CSM generally includes eight classes of operations: Decode, Scan, Detection, Transfer, Cleanup, Mark, Reuse, and Allocate.

15 Decode

Referring to FIG. 6, in Decode, CSM 69 determines the actions to be performed. CSM 69 idles at a step 270 until triggered, and first determines if a Cleanup Active step is posted at a step 272. If so, CSM 69 proceeds to step B to Cleanup. Otherwise, if a Mark Active step is posted at a step 274, CSM 69 proceeds to step C to Mark. Otherwise, CSM 69 determines if a Scan Active step is posted at a step 276. If so, CSM 69 initializes the Cache LBA register to the Command LBA at a step 278. CSM 69 then compares Cache LBA to the End LBA register at a step 280 which contains the sum of the Command LBA and the Transfer Count. If End LBA is greater than the Cache LBA, CSM 69 determines if a Scan Active is posted at a step 282. If so, this is the first Scan for the New Command, and so the Cache Sector count, containing the number of sectors found for Transfer, is initialized to zero at a step 284. Thereafter, CSM 69 proceeds to step E Scan.

If Scan Active is not posted in step 276, CSM 69 determines if a Transfer Active is posted at a step 286. If not, there is no further action to perform and CSM 69 proceeds to idle step 270. Otherwise, the Cache LBA is initialized at step 278 to the value of the Running LBA, which contains the identity of the last LBA Transferred, to allow Transfer of subsequent LBAs requested by the New Command. As transfers take place, the Running LBA is updated. If Cache LBA is greater than End LBA as tested at step 280, the New Command is satisfied, and CSM 69 clears the Scan Active at step 288. Thereafter, CSM 69 determines if Transfer Active is posted at step 300, and if so, it is cleared at step 302. CSM 69 then posts Cleanup Active at step 304, to trigger Cleanup to free any segments remaining locked by Transfer, and proceeds to idle state 270. If Cache LBA is less than End LBA as tested in step 280, and Scan Active is not posted as tested at step 282 (Transfer Active only), CSM 69 proceeds to step D to Transfer data found by Scan.

Therefore, all possibilities of the active steps of CSM 69 are:

Cleanup Active only;

Mark Active only;

- Scan Active only—Scan to find (Detect) data in cache;

- Transfer Active only—Transfer data found by a previous Scan; and

- Scan Active and Transfer Active only—while Transferring data, Scan the cache to find new data to append to data being Transferred.

Scan

Referring to FIG. 7, when Scan Active step is posted, CSM 69 proceeds to step E, and begins by initializing the Entry Pointer to the first Cache List entry at step 306. CSM 69 accesses the contents of the entry at step 308 and determines if the Cache LBA is identified in this entry at step 310, i.e. an LBA hit.

If not, CSM 69 determines if the entry is the last Cache List entry at step 332, and if not, the Entry Pointer is incremented at step 330, and CSM 69 proceeds to the next entry at step 308. If the entry is the last entry, CSM 69 clears Scan Active at step 336, and determines if Transfer Active is posted at step **338**. If Transfer Active is not posted, CSM 69 proceeds to step F to Detect. Otherwise, CSM 69 checks the Cache Sector register to determines if any new cache sectors have been found for Transfer at step 324. If not, in SCSI mode at step 326, CSM 69 clears Transfer Active at 10 step 328 and proceeds to step A without any active steps. In AT mode, CSM 69 remains in transfer mode, and so, proceeds to step A with Transfer Active step set. If new cache sectors have been found at step 324, CSM 69 proceeds to step A, leaving Transfer Active set, for the found data 15 sectors to be Transferred.

If there is an LBA hit as found at step 310, CSM 69 determines if the Cache LBA is greater than End LBA at step 312. This is because during a Scan, if Transfer Active is not set, CSM 69 may Scan Cache List entries for LBAs well 20 beyond the New Command range, and so may find LBA hits beyond the End LBA. If the current LBA hit is beyond the New Command range, the Segment with the LBA hit therein need not be locked, as the Segment will not be used for the current Transfer. Therefore, if End LBA is greater than 25 Cache LBA, CSM 69 locks the Segment corresponding to the current Cache List entry at step 314. Otherwise, the Segment is not locked. CSM 69 then increments the Cache LBA and the Cache Sector at step 316 based on the number of valid LBAs data found in this Segment.

CSM 69 again determines if the Cache LBA is greater than the End LBA at step 318. If not, there are more LBAs in the command range to find, and so, CSM 69 proceeds to Scan again at step 306, where the Entry Pointer is initialized LBAs in the New Command range. However, if the Cache LBA is greater than the End LBA as tested at step 318, all LBAs in the command range have been found, and CSM 69 determines whether Transfer Active is posted at step 320. This allows CSM 69 to determine if it is in a Scan and 40 Transfer process or in a purely Scan process in which it performs a full Scan of the Cache List. If the former case, both Transfer Active and Scan Active are set, and in the latter case, only Scan Active is set, whereupon CSM 69 proceeds Although the Cache LBA is beyond the range of the New Command, the Scan process continues until no further LBA hits are found.

However, in a transfer process, there is no reason for CSM 69 to search for LBA hits beyond the New Command range, 50 whereupon CSM 69 clears Scan Active at step 322 and proceeds to step A to Decode. There, since Transfer Active is set, Decode triggers Transfer to transfer data from Segments with LBA hits therein.

Detection Referring to FIG. 8, in step F, CSM 69 interprets the "results" of the Scan process to provide information including a full hit, a partial hit or miss. CSM 69 also generates interrupts informing the firmware of such information, and based on the setting in the Auto Enable Register, transfers 60

data.

By step F, the Cache LBA contains the last LBA sequential to the Start LBA not found in the cache. CSM 69 saves the Cache LBA in the Missing LBA register at step 340, and begins the process of determining a FULL HIT, a PARTIAL 65 HIT, or a MISS. At the end of this determination process, CSM 69 proceeds to step A to Decode.

CSM 69 first determines if the Cache LBA is less than End LBA at step 342. If so, in this AT interface specific implementation, if the number of LBAs in the hit are smaller than a block count as determined at step 354, CSM 69 generates a MISS interrupt at step 354, otherwise, CSM 69 posts a PARTIAL HIT in the Interrupt Register at step 358. And, if Partial Hit Autoread is enabled, step 360, CSM 69 posts a Transfer Active at step 362, and generates a PAR-TIAL HIT interrupt at step 364. If Partial Hit Autoread is not enabled, CSM 69 generates a PARTIAL HIT interrupt at step 364, without posting Transfer Active step to trigger a Transfer, and proceeds to step A.

If Cache LBA is greater than or equal to End LBA as tested in step 342, CSM 69 posts the FULL HIT at step 346 in the Interrupt Register, and determines if Full Hit Autoread is enabled at step 348. If so, CSM 69 posts a Transfer Active at step 350, and generates a FULL HIT interrupt at step 352. If Full Hit Autoread is not enabled, CSM 69 generates a FULL HIT interrupt at step 352, without posting Transfer Active step to trigger a Transfer, and proceeds to step A. Transfer

Referring to FIG. 9, when Transfer Active is posted and Scan Active is not, CSM 69 proceeds to step D. In this AT specific implementation, CSM 69 loads an AT interface specific register, Current Read Sectors (CRS), with the number of sectors available for transfer from the Cache Sector register at step 370. Cache Sector contains the number of sectors found during Scan, now to be transferred. CRS is an interface register for the amount of data for the 30 interface to transfer.

To find the addresses of the aforementioned sectors in the Buffer, CSM 69 proceeds by initializing the Entry Pointer to the first entry of the Cache List at step 372, accesses that entry at step 374, and determines if the Cache LBA is to the first entry of the Cache List to find the remaining 35 identified in that entry at step 376, i.e. an LBA hit. If not a hit, CSM 69 determines if the entry is the last Cache List entry at step 396, and if not, increments the Entry Pointer to the next Cache List entry at step 394 and checks for an LBA hit again at step 376. When a hit is found, CSM 69 locks the entry Segment with the hit by setting the Lock Flag, loads the Buffer Pointer with the sector address of where the data is, and loads a Trigger Count register with the number of sectors to be transferred from the Segment at step 378. The sector address is computed based on the Segment address, its to Scan beyond the range of the New Command at step 306. 45 length, number of valid LBAs therein, and the current LBA, providing an offset for the sector in the Segment. CSM 69 then determines if the Interface has been started at step 380, and if not, CSM 69 starts the Interface at step 382, and synchronizes with the Interface at step 384 to transfers data from the sector pointed to by the Buffer Pointer based on the Trigger Count. With each sector transferred, the Interface decrements the Trigger Count. When the Trigger Count is zero as tested at step 386, all the data in the Segment has been transferred and the transfer for the next Segment with 55 an LBA hit can begin.

> To do so, CSM 69 again traverses the Cache List to find the next Segment and compute the next Buffer Pointer: CSM 69 clears the Lock Flag for the current Segment, and increments the Cache LBA at step 388 to the sum of the start LBA for the last transfer and the number of LBAs transferred. CSM 69 then proceeds to find the next Segment for transfer by traversing the Cache List at step 372. As such, CSM 69 seamlessly concatenates and transfers data from different Segments to the host.

> In the worst case, CSM 69 traverses the Cache List beginning to end only once to find all the data to be transferred. This is because the amount of data to be trans

ferred has already been determined in the previous full Scan and stored in CRS in step **370**. In a full Scan, the Cache List may be fully traversed more than once since the Cache LBA is incremented as an LBA in sequence with the Start LBA of the new Command is found.

Back in step 386, if count is not triggered, and there is a disconnect or abort 390, CSM 69 stops the transfer by clearing Transfer Active at step 392 and proceeds to step A. Otherwise, for this AT interface specific implementation, for multiple commands, data is transferred in blocks of a block 10 count value (e.g. four LBAs at a time). If CRS is lower than the block count, the Interface cannot transfer and generates a Low CRS signal as detected at step 402. In response, CSM 69 posts a Scan Active at step 404, and since Transfer Active has already been posted, CSM 69 proceeds to step A to 15 Decode and perform another Scan for data not yet accounted for (e.g., data transferred to the cache while the last Transfer was taking place).

As such, CSM 69 transfers data out the Buffer so long as new data is fed into the Buffer. This is accomplished as 20 follows: CM 67 initially loads the Running LBA with the Start LBA. CSM 69 then initializes the Cache LBA to the Running LBA in Decode. As data is transferred, the Running LBA is incremented to keep track. When CSM 69 begins Scan, it initializes the Cache LBA to the Running LBA, 25 whereupon a Scan of the Cache List to the end of the New Command range is performed to find LBA hits. Thereafter, CSM 69 returns to Transfer and loads the CRS register as described above to begin transferring the data found during Scan. After the found data is transferred, CSM 69 again 30 returns to Scan to find more data, and returns to Transfer to transfer the data out of the Buffer. The process continues and data is seamlessly transferred out of the Buffer so long as the request data is found in the Buffer.

Returning back to step **396**, if CSM **69** determines that the 35 entry is the last Cache List entry but the transfer is not complete, CSM **69** enables a firmware trigger mode at step **398** and loops in this step, waiting for firmware to set a trigger flag at step **400**. When the trigger flag is set, CSM **69** posts a Scan Active at step **404** and proceeds to step A to 40 perform another Scan. If, however, the trigger flag is not set, CSM **69** synchronizes with the interface at step **384** and proceeds as described above.

Cleanup

Referring to FIG. **10**, when Cleanup Active is posted, 45 CSM **69** proceeds to step B, and traverses the Cache List to ensure that all Segments locked during a Transfer are unlocked. This is because Transfer locks all the Segments with hits.

In steps **410–418** CSM **69** sequentially traverses the 50 Cache List and clears the Lock Flag in every entry. Thereafter, CSM **69** clears the Cleanup Active at a step **420**, generates a Cleanup Interrupt at a step **420**, and proceeds to step A to Decode.

Mark

Referring to FIG. **11**, when Mark Active is posted, CSM **69** proceeds to step C, where it ascertains both LBA and buffer overlaps. CSM **69** makes two passes through Mark, one for ascertaining LBA overlaps, and another for determining buffer overlaps.

In step 424, CSM 69 determines if a Saves Pointer to a Cache List entry exists, indicating a previous pass through Mark. If not, CSM 69 initializes the Cache LBA to the Running LBA, and initializes the Entry Pointer to the first entry of the Cache List at step 428. CSM 69 accesses the 65 entry at step 430, and determines if the New Command LBA range overlap the current LBA set identified in the entry at

step 432, i.e. a Trim Hit. If not a Trim Hit, and if the entry is not the last Cache List entry as tested at step 434, CSM 69 increments the Entry Pointer at step 436 and cycles to the next entry at step 430. If the current entry is the last entry at step 434, CSM 69 determines if the current pass through Mark is a buffer trim at step 446. If a buffer trim, Mark is complete and CSM 69 proceeds to step J to Allocate. If not a buffer trim, CSM 69 sets the Buffer Trim flag at step 448, and begins its second pass at step 424. The Cache LBA is initialized to a Buffer Pointer (not an LBA). Cache LBA is a generic register and its contents are interpreted based on the Buffer Trim flag. The same LBA hit steps are performed for the buffer to determine buffer overlap.

Back in step 432, if CSM 69 finds a Trim Hit, CSM then 15 determines if Auto Trim is enabled at step 438, and if not, it sets the Trim Flag at step 444 for the entry to prevent the entire entry from participating in subsequent read Scans. The flag also indicates to the firmware that the entry has to be trimmed by the firmware. If Auto-Trim is enabled, CSM 69 determines if Auto Reuse is enabled at step 440, and if not, it trims the entry at step 442 by changing the values in the current Cache List entry to reflect the new Segment after trimming. Based on the type of trimming (LBA or buffer trimming), trimming includes changing one or more of: the Start LBA, reducing the number of Valid LBAs, changing the Buffer Pointer, or reducing Segment Size. After trimming, the entry describes a section of the buffer that includes valid data which can be used by Scan and Transfer. Back in step 483, if Auto Reuse is enabled, CSM 69 proceeds to step G to Reuse. When CSM 69 completes ascertaining both LBA and buffer overlaps, it determines if a buffer trim took place at step 446, and if so, it proceeds to step J to Allocate.

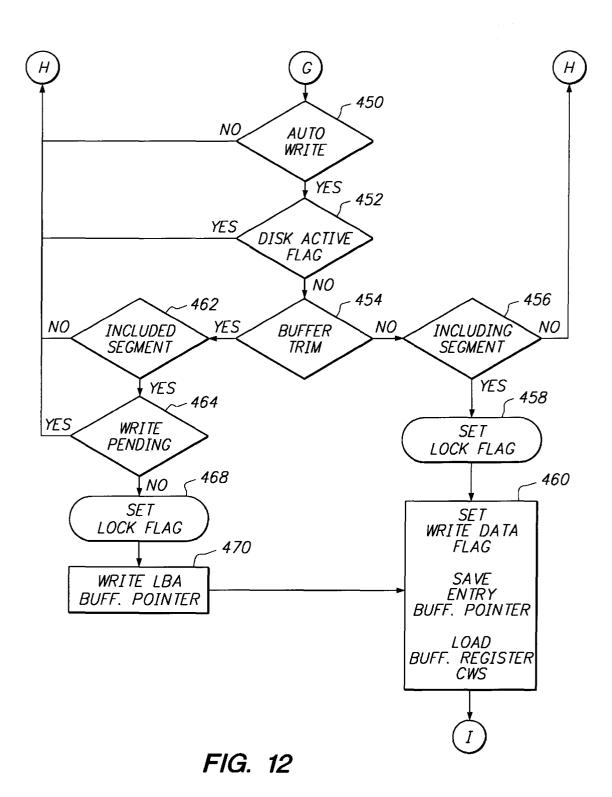

Reuse

Referring to FIG. 12, when Auto Reuse is enabled, CSM 69 proceeds to step G, where it provides for full hit data in a write command to be transferred directly into position in the hit Segment, rather then to a position indicated by Auto-Write Pointer.

In step 450 CSM 69 determines if trimming has been requested by an Auto Write New Command at step 450 (not by the firmware). If not, CSM 69 proceeds to step H to trim the Segment and the data is placed in the Buffer location pointed to by the Auto-Write Pointer. Otherwise, CSM 69 determines if the Segment is being used by the disk drive at step 452. If so, CSM 69 proceeds to step H to trim the Segment and the data is placed in the Buffer location pointed to by the AutoWrite Pointer. Otherwise, CSM 69 determines the type of overlap trim at step 454. If LBA trim, CSM 69 determines if the Segment completely includes the New Command segment (full hit) at step 456. If not, CSM 69 proceeds to step H to trim the segment and the data is placed in the buffer location pointed to by the Auto-Write Pointer. If the Segment is an including segment, CSM 69 sets the Lock Flag for the Segment at step 458, and then: (1) sets the 55 write data flag, (2) saves the entry Buffer Pointer back in the Command FIFO, replacing the Autowrite Pointer there with the Buffer Pointer which points to where the data will be stored in the Segment, and (3) provides the Buffer Pointer 60 the transfer Interface by loading the Buffer Register and updating CWS with the amount of data to be transferred at step 460. CSM 69 then proceeds to step I for Marking, where the Buffer Pointer saved by Reuse is used by Mark at step 424.

Back at step **454**, if the trimming is buffer trimming, CSM **69** determines if the current Segment is included in a new segment starting from the Auto-Write pointer at step **462**

(i.e. the new segment beginning before the start of the current segment, and ending beyond the end of the current segment). If so, the entry becomes invalid and can be reused to describe the new segment created. To do so, CSM 69 sets Segment Lock Flag at step 468, and a new Start LBA and Buffer Pointer are placed in the entry at step 470. Thereafter, CSM 69 performs step 460 described above and proceeds to step I. The entry and the corresponding Buffer area are reused in both buffer trim and LBA trim cases.

number of Valid LBAs in the entry to resolve overlaps. Allocation

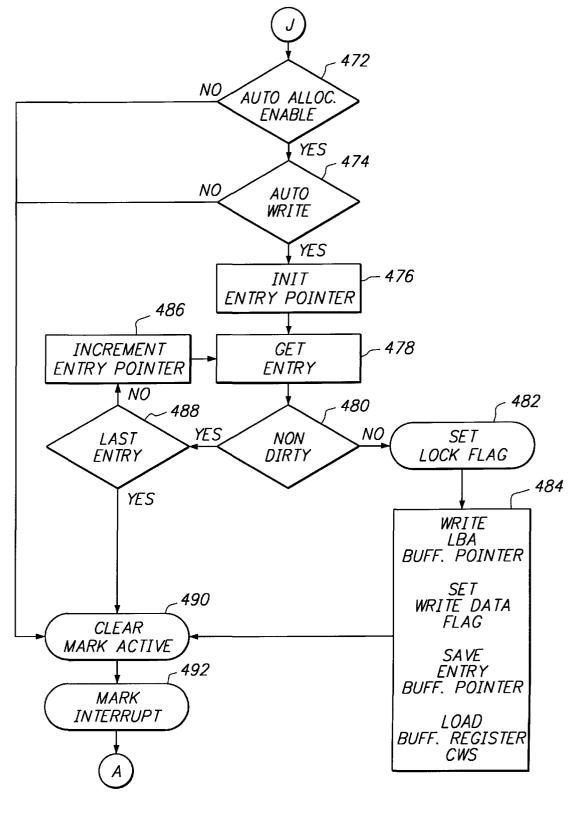

Referring to FIG. 13, CSM 69 proceeds to step G to look for an invalid Cache List entry to use as a new entry. In step 472, CSM 69 determines if Auto Allocation is enabled. If 15 not, CSM 69 clears Mark Active at step 490, generates a Mark Interrupt for the firmware at step 492, and proceeds to step A to Decode. If Auto Allocation is enabled, CSM 69 determines if the New Command is Auto Write at step 474, indicating to the CSM 69 that it is not under firmware 20 control. If the New Command is not Auto Write, CSM 69 clears Mark Active at step 490, generates a Mark Interrupt for the firmware at step 492, and proceeds to step A to Decode. If the New Command is Auto Write, CSM 69 begins searching the Cache List for all entries with Not Dirty 25 bits set, indicating they are invalid. CSM initializes the Entry Pointer at step 476 to the first entry of the Cache List, accesses the entry at step 478, and determines if it is invalid at step 480. If the entry is invalid, CSM 69 proceeds to lock the entry at step 482, and allocate a segment by writing the 30 LBA, writing the Buffer Pointer, setting the Write Data Flag, Saving the Entry back in the Command FIFO, and loading the Buffer Register and the CWS at step 484. This is an entry for the current write command. Therefore, subsequent reads may find hits in this segment and use the data therein. After 35 instructions to enable the microprocessor 502 to interact allocating an invalid entry, or if CSM 69 reaches the last entry at step 488 without finding any invalid entries, it clears Mark Active 490, generates a Mark Interrupt for the firmware to know that marking has been performed at step 492, and proceeds to step A to decode.

In CSM 69 the Scan, Transfer and Cleanup operations are self-triggered. The firmware 60 can also place CSM 69 to any of CSM steps describe above. CSM 69 performs the action associated with the directed step, based on the values ensure that the firmware and the CSM 69 do not compete, and the cache remains coherent, firmware disables CM 67 while CSM 69 is performing operations for the firmware.

Although in the above implementation, the cache list included 32 entries, other cache list sizes are also possible. 50 The number of entries in the cache list can be selected to suit different performance criteria in a given system. For example, a cache list can include 4000 entries to keep track of 4000 LBAs in a 2-megabyte buffer. However, longer lists can require relatively more time to search. Further, the 55 number of cache list entries can be less than the number of possible segments in the cache buffer. Due to locality of reference by the host, most data segments include a large number of consecutive data blocks. As such, the cache list need not reference all data segments to keep track of the data 60 in use by the host. Traversing the cache list can include sequential search, binary search, or other search schemes known to those skilled in the art.

The present invention can be implemented as program instructions to be performed by a processor or to configure 65 a logic circuit. The program instructions can be implemented in a high level programming language such as C, Pascal, etc.

which is then compiled into object code and linked with object libraries as necessary to generate executable code for the processor. The program instructions can also be implemented in assembly language which is then assembled into object code and linked with object libraries as necessary to generate executable code.

Preferably, the controller 65 is implemented in a logic circuit configured by the program instructions to perform the steps described above. The logic circuit can be an Applica-Trimming an entry includes increasing or decreasing the 10 tion Specific Integrated Circuit (ASIC). An ASIC is a device designed to perform a specific function as opposed to a device such as a microprocessor which can be programmed to performed a variety of functions. The circuitry for making the chip programmable is eliminated and only those logic functions needed for a particular application are incorporated. As a result, the ASIC has a lower unit cost and higher performance since the logic is implemented directly in a chip rather than using an instruction set requiring multiple clock cycles to execute. An ASIC is typically fabricated using CMOS technology with custom, standard cell, physical placement of logic (PPL), gate array, or field programmable gate array (FPGA) design methods.

> A dedicated logic circuit, such as an ASIC, provides higher performance than a microprocessor since the logic is implemented directly in the chip rather than using an instruction set requiring multiple clock cycles to be executed by a microprocessor.

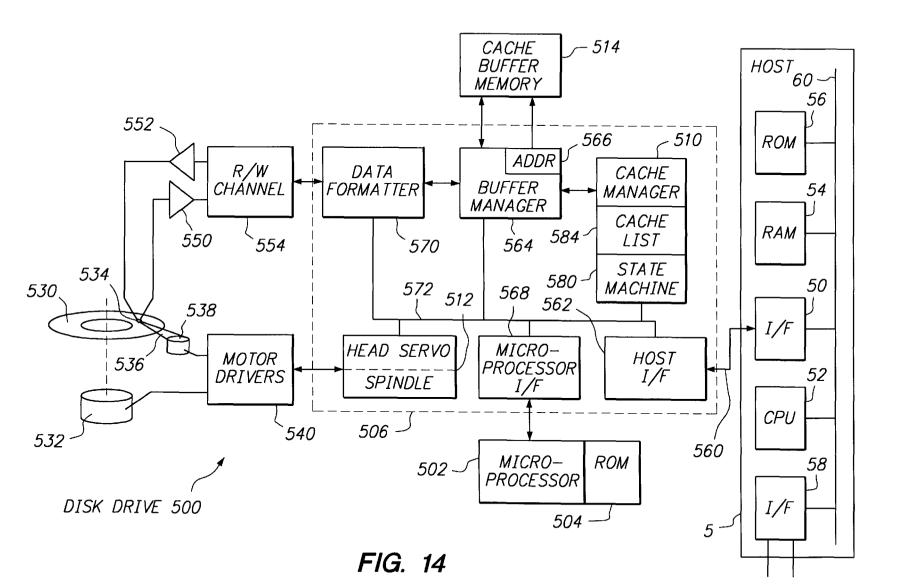

> Referring now to FIG. 14, an alternative preferred embodiment 510 of the controller logic circuit 65 can be embedded within a memory device, such as a hard disk drive 500 having at least one embedded microprocessor 502 and a ROM **504**. The cache manager/controller **510** is preferably included within a disk drive multi-function controller chip 506. Typically, the ROM 504 includes data and program with a spindle motor/voice coil motor controller 512 in the disk drive, and to oversee transfer of data between a host and the disk drive through the disk drive **500**. The disk drive **500** includes the cache buffer 514 for storing data into and retrieving data from the disk drive. The disk drive can also be used to store and maintain the cache list 80. Preferably, the cache list 80 is stored in a fast local memory 520 for efficient access by the cache controller 510.

The disk drive 500 also conventionally includes at least provided by the firmware in the Auto Enable Register. To 45 one rotating data storage disk 530 having a magnetic surface for storing user information in e.g. concentric data tracks. The disk 530 is rotated at a desired angular velocity by a spindle motor 532 controlled by the spindle motor controller 512. A data transducer head 534, including write and read elements, flies in close proximity to the data storage surface upon an air bearing. A head positioner 536 including e.g. a voice coil motor positions the head 534 at desired radial locations for random access to storage locations for writing/ reading operations. A motor driver 540 supplies controlled driving currents to the spindle motor 532 and to the voice coil motor 538 of the head positioner 536. A read preamplifier 550 amplifies minute signals derived from the read element during data reading from disk, while a write driver 552 provides write current to the write element for data writing to the storage disk 530. A read/write channel 554 provides coding, decoding and signal processing in order to encode data for writing to disk and in order to recover data from magnetic flux transitions read from disk.

> The disk multi-function chip 506, the buffer memory array 514, microprocessor 502, along with the read/write channel chip 554 and motor driver chip 540, comprise the principal discrete elements of drive electronics of the disk

drive 500. A host bus 560 following a known convention such as AT (IDE), SCSI, or IEEE 1394, enables the disk drive **500** to be connected to the host interface **50**.

The disk multi-function chip 506 includes several important functions including a host interface controller 562, a buffer manager 564 (including an address generator 566), the embedded cache manager 510 in accordance with principles of the present invention, a microcontroller interface 568, a disk data formatter/sequencer 570, and the spindle/ head controller 512, all being internally connected within 10 the chip 506 via an internal bus structure 572. The interface controller 562 connects to the host 50 via the bus structure 560. The buffer manager 564 connects to and controls the buffer memory array 514.

The formatter/sequencer 570 directly connects to the 15 read/write channel chip 554. The spindle/head position controller 512 connects to the motor driver chip 540. The microcontroller interface 568 directly connects to the microprocessor 502. In some embodiments of the disk multifunction chip **506**, a microcontroller core may be directly 20 integrated within the silicon structure thereof instead of being a separate chip as shown in FIG. 14. In the FIG. 14 example, the drive-embedded cache system essentially comprises the buffer memory 514, the buffer manager 564 and address generator 566, the interface 562 and the embedded 25 block 586. cache manager 510.

Also shown within FIG. 14 is the host computer 5. The host computer 5 includes the interface 50 connected to the bus 560. The interface 50 is necessarily compatible with the interface controller 562 of the disk drive as well as with the 30 machine 580 to the ALU 582. bus structure 560. The host 5 also conventionally includes a central processing unit 52, a random access memory array 54, a read only memory 56, and a plurality of input/output ports 58 enabling other peripherals such as keyboard, used. An internal host bus structure 60 interconnects the CPU 52 with disk interface 50, RAM 54, ROM 56, and I/O 58.

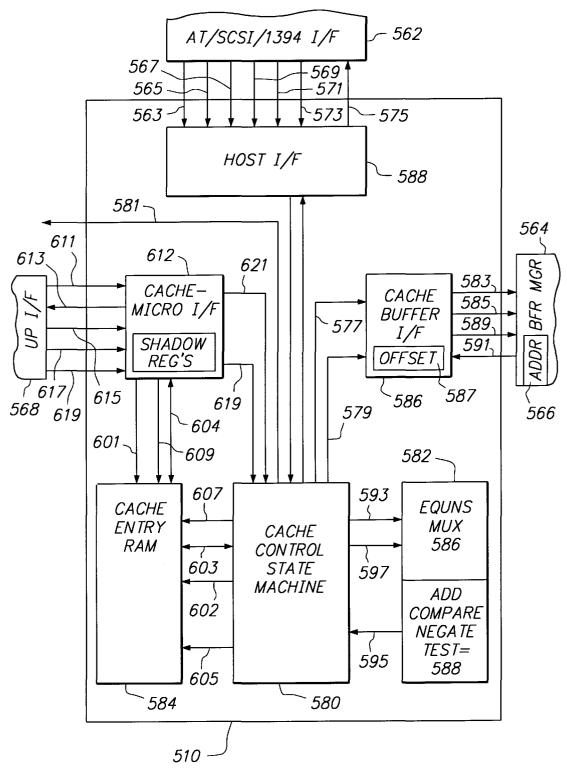

The embedded cache manager 510 is illustrated in greater detail in FIG. 15. Referring to FIG. 15, the embedded cache 40 manager 510 of the present embodiment includes a single multi-state cache control state machine 580, an arithmetic/ logic unit (ALU) 582 and the cache list RAM 584. The buffer manager interface 586 connects directly to the buffer manager 564 and includes a word offset block 587 which 45 enables the cache controller 510 to control automatic addressing of multiple cache segments within the cache buffer memory array 514 without firmware intervention. A cache-host interface 588 directly interfaces with the host interface controller 562. A cache microprocessor interface 50 read. 612 includes a bank of firmware shadow registers which are written to and read by the microprocessor 502 via microprocessor interface 568 enable firmware and the cache controller 510 to coordinate respective cache management activities. Shadow registers enable the microprocessor **502** to write entries directly to the cache list RAM 584. The cache microprocessor interface 612 provides control and status handshaking between the microprocessor 502 and the cache controller state machine 580. Shadow registers are most preferably provided for valid LBA, start LBA low, start 60 LBA high, segment size, buffer pointer, LBA offset, and flags fields of the cache entries, see FIG. 17, discussed below.

A series of data paths and control lines are shown interconnecting the functional blocks of FIG. 15. A series of 65 paths extend between the host interface controller 562 and the cache-host interface block 588. These paths include a

scan request line 563, a read/write control line 565, a path 567 providing command LBA and sector count information, a sector start control line 569, a sectors available path 571, a transfer done line 573, and a path 575 providing sectorsavailable, load-sector control, buffer pointer/entry, and flags information to the host.

A path 577 sends a zero trigger count value from the cache controller state machine 580 to the cache buffer interface 586. A path 579 provides rollover and reload values from the cache controller state machine 580 to the cache buffer interface 586. A firmware interrupt control line 581 from the cache controller state machine 580 causes regular program execution by the microprocessor 502 to be interrupted in order to provide data transfer operations under firmware control whenever a cache miss, or partial cache hit is detected by the cache controller 510.