# Theory of Operation

# COMPUTER MODEL 920

SDS 900005D

March 1966

SCIENTIFIC DATA SYSTEMS • 1649 Seventeenth Street • Santa Monica, Calif. • (213) 871–0960

© 1964, 1966, Scientific Data Systems, Inc.

## PREFACE

The SDS 900 Series Computers are solid state, general purpose, digital machines which use a parallel, random access, coincident current, magnetic core memory and serial arithmetic operation.

These computers are completely modular, contain all silicon components, and have positive true logic. Internal operations are binary and two's complement arithmetic is used.

This manual is presented in four sections. These cover Computer Logic, W Buffer and Input/Output Operations, Magnetic Core Memory, and BCD Typewriter and Tape Punch. Each section has its own lists of Contents and Illustrations which define the referenced pages.

# TABLE OF CONTENTS

| Section |                                                        | Page |

|---------|--------------------------------------------------------|------|

| I       | COMPUTER LOGIC                                         | ·    |

|         | INTRODUCTION                                           | 1.1  |

|         | BASIC COMPUTER STRUCTURE AND OPERATION                 | 1.3  |

|         | INSTRUCTION AND WORD FORMAT                            | 1.7  |

|         | Instruction Format                                     | 1.7  |

|         | Data Word Format                                       | 1.8  |

|         | Two's Complement Arithmetic                            | 1.8  |

|         | PULSE COUNTER                                          | 1.15 |

|         | Pulse Decoding                                         | 1.16 |

|         | PHASE CONTROL                                          | 1.17 |

|         | Phases                                                 | 1.17 |

|         | Phase Counter                                          | 1.18 |

|         | Single-Cycle Instructions                              | 1.20 |

|         | Two-Cycle Instructions                                 | 1.20 |

|         | Three-Cycle Conditional Skip Instructions              | 1.21 |

|         | Two-Cycle Conditional Skip Instructions                | 1.21 |

|         | Three-Cycle Memory Increment or Decrement Instructions | 1.22 |

|         | Multiplication and Division Instructions               | 1.23 |

|         | N-Cycle Shift Instructions                             | 1.23 |

|         | Three-Cycle Plus N Output Instructions                 | 1.24 |

|         | Four-Cycle Plus N Input Instructions                   | 1.24 |

|         | Three-Cycle Store Instructions                         | 1.25 |

|         | One-Cycle Unconditional Branch Instructions            | 1.26 |

|         | Program Operator Instructions                          | 1.26 |

|         | REGISTERS                                              | 1.27 |

| `       | P Register                                             | 1.27 |

|         | S Register                                             | 1.28 |

# Contents

# TABLE OF CONTENTS (Cont.)

| Section |                                                                                   | Page |

|---------|-----------------------------------------------------------------------------------|------|

|         | M Register                                                                        | 1.29 |

|         | C Register                                                                        | 1.32 |

|         | O Register                                                                        | 1.33 |

|         | A Register                                                                        | 1.34 |

|         | B Register                                                                        | 1.35 |

|         | X Register                                                                        | 1.35 |

|         | Word Assembly Register (WAR)                                                      | 1.36 |

|         | MEMORY CONTROL                                                                    | 1.39 |

|         | ADDER                                                                             | 1,43 |

|         | INSTRUCTION OPERATORS                                                             | 1.45 |

|         | Index Operation                                                                   | 1.45 |

|         | Indirect Address Operation                                                        | 1.46 |

|         | Program Operator                                                                  | 1.46 |

|         | MANUAL AND TIMING CONTROL                                                         | 1.51 |

|         | Interrupt                                                                         | 1.51 |

|         | Time-Share (Memory Interlace)                                                     | 1.58 |

|         | Control Switch                                                                    | 1.61 |

|         | Register Switch                                                                   | 1.65 |

|         | Manual Control Switches                                                           | 1.67 |

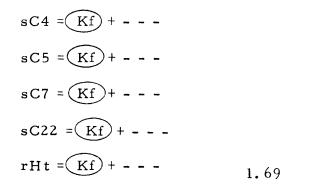

|         | Start and Fill Switches                                                           | 1.69 |

|         | INSTRUCTIONS                                                                      | 1.73 |

|         | Skip and Branch Instructions (01, 40, 50, 52, 53, 70, 72, 73, 73, 74, 41, 43, 51) | 1.73 |

|         | Memory Increment Instructions (60, 61)                                            | 1.79 |

|         | Store Instructions (35, 36, 37)                                                   | 1.79 |

|         | Load Instructions (71,75,76,77)                                                   | 1.80 |

|         | Input Instructions (30, 32, 33)                                                   | 1.81 |

|         | Output Instructions (10, 12, 13)                                                  | 1.83 |

# TABLE OF CONTENTS (Cont.)

# Section

Π

Page

| Control Instructions (23,00,02,20)                   | 1.84  |

|------------------------------------------------------|-------|

| Logical Instructions (14, 16, 17)                    | 1.85  |

| Register Change Instructions (46)                    | 1.86  |

| Shift Instructions (66, 67)                          | 1.87  |

| Arithmetic Instructions (54, 55, 56, 57, 63, 64, 65) | 1.91  |

| Multiply Example                                     | 1.95  |

| Divide Example                                       | 1.100 |

| MEMORY PARITY                                        | 1.101 |

| Parity Generation                                    | 1.101 |

| Parity Checking                                      | 1.101 |

| IMPLEMENTATION                                       | 1.103 |

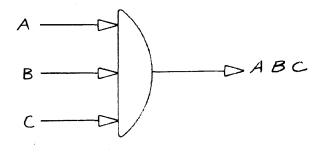

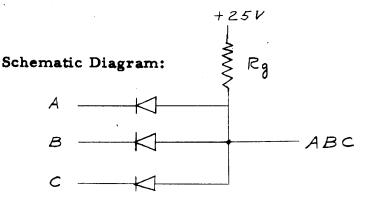

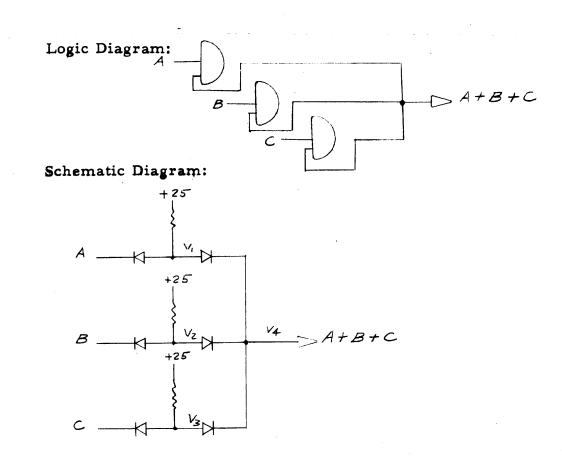

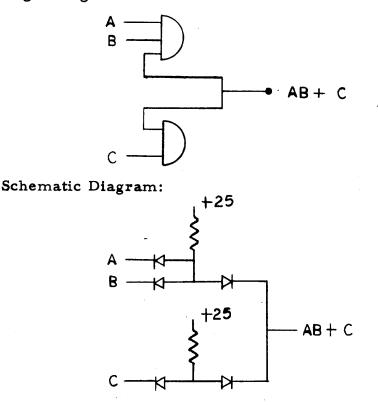

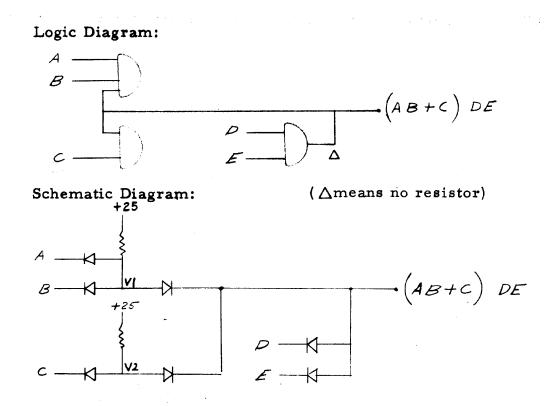

| Gates                                                | 1.103 |

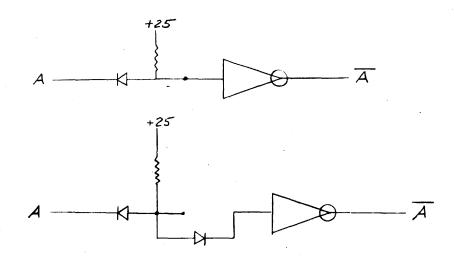

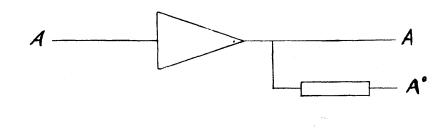

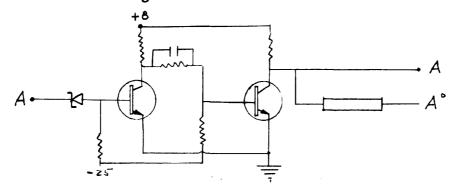

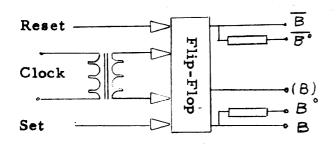

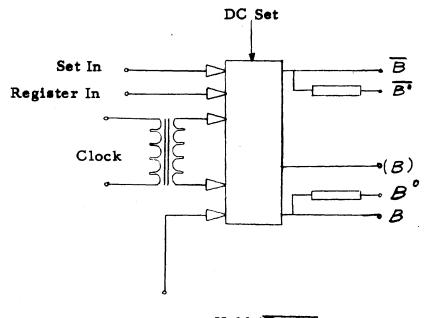

| Inverters, Buffer Amplifiers and Flip-Flops          | 1.106 |

| DICTIONARY OF COMPUTER LOGIC TERMS                   | 1.111 |

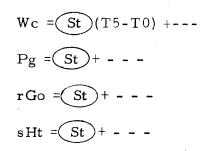

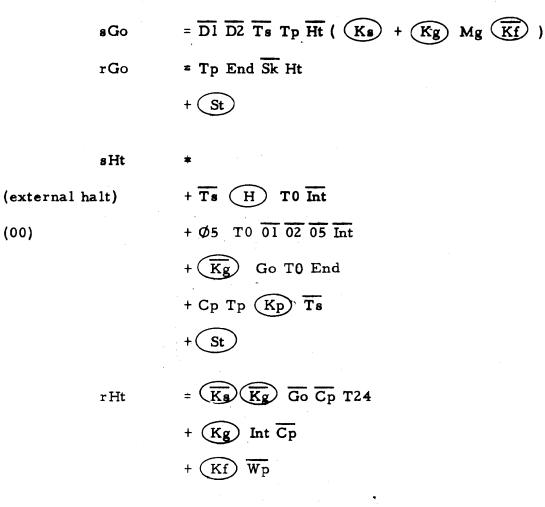

| CONDENSED COMPUTER LOGIC EQUATIONS                   | 1.117 |

| A Register                                           | 1.117 |

| B Register                                           | 1.119 |

| C Register                                           | 1.121 |

| S Register                                           | 1.143 |

| Scope Signals                                        | 1.152 |

| SKS                                                  | 1.154 |

| X Register                                           | 1.156 |

| W BUFFER AND INPUT/OUTPUT OPERATIONS                 |       |

| INTRODUCTION                                         | 2.1   |

| GENERAL W BUFFER OPERATION                           | 2.3   |

| Input Process ( <del>W9</del> )                      | 2.6   |

| Output Process (W9)                                  | 2.17  |

1.vii

# Contents

# TABLE OF CONTENTS (Cont.)

| Section |                                     | Page |

|---------|-------------------------------------|------|

|         | Scan ( <del>W</del> 9 W10 W11)      | 2.28 |

|         | Erase (W9 W10 W11)                  | 2.29 |

|         | Fill                                | 2.31 |

|         | Time-Share Interlace                | 2.32 |

|         | Photo-Reader 1                      | 2.38 |

|         | DICTIONARY OF BUFFER LOGIC TERMS    | 2.41 |

|         | W BUFFER AND INPUT/OUTPUT EQUATIONS | 2.45 |

|         | Unit Address Register               | 2.45 |

|         | Input/Output                        | 2.45 |

|         | Character Counter                   | 2.45 |

|         | Clock Counter                       | 2.46 |

|         | Computer Interlock                  | 2.46 |

|         | Interrupt Signals                   | 2.46 |

|         | Time-Share Calling Signal           | 2.46 |

|         | Halt Detector                       | 2.47 |

|         | Error Detector                      | 2.47 |

|         | Single Character Register           | 2.47 |

|         | Load W from C                       | 2.48 |

|         | Clock Signal                        | 2.48 |

|         | Word Assembly Register              | 2.49 |

|         | Clear and Set Signals               | 2.49 |

|         | Halt Interlock                      | 2.49 |

|         | Magnetic Tape Control Signals       | 2.49 |

|         | INTERLACE LOGIC                     | 2.50 |

|         | PHOTO-READER 1                      | 2.52 |

|         | Enable Signal                       | 2.52 |

|         | Pinch Roller and Lamp Drivers       | 2.52 |

# TABLE OF CONTENTS (Cont.)

| Section |                               | Page |

|---------|-------------------------------|------|

|         | Reader Signals                | 2.52 |

|         | Brake Driver                  | 2.52 |

|         | Y BUFFER OPERATIONS           | 2.53 |

|         | Y BUFFER EQUATIONS            | 2.55 |

|         | Unit Address Register         | 2.55 |

|         | Input/Output                  | 2.55 |

|         | Character Counter             | 2.55 |

|         | Clock Counter                 | 2.56 |

|         | Computer Interlock            | 2.56 |

|         | Interrupt Signals             | 2.56 |

|         | Time–Share Calling Signal     | 2.56 |

|         | Halt Detector                 | 2.57 |

|         | Error Detector                | 2.57 |

|         | Single Character Register     | 2.57 |

|         | Load Y from C                 | 2.58 |

|         | Clock Signal                  | 2.58 |

|         | Word Assembly Register        | 2.59 |

|         | Clear and Set Signals         | 2.59 |

|         | Halt Interlock                | 2.59 |

|         | Magnetic Tape Control Signals | 2.59 |

| III     | MAGNETIC CORE MEMORY          |      |

|         | INTRODUCTION                  | 3.1  |

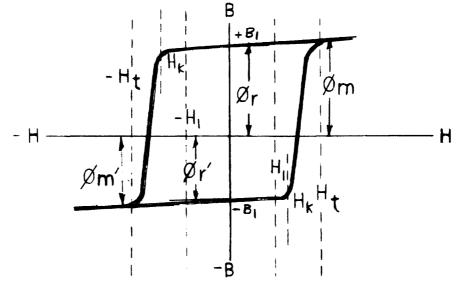

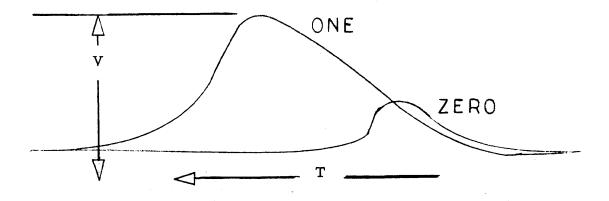

|         | MAGNETIC CORE STORAGE THEORY  | 3.5  |

|         | BASIC OPERATION               | 3.9  |

|         | Addressing                    | 3.9  |

|         | Read Cycle                    | 3.13 |

|         | Write Cycle                   | 3.16 |

# **Contents**

# TABLE OF CONTENTS (Cont.)

Page

# Section

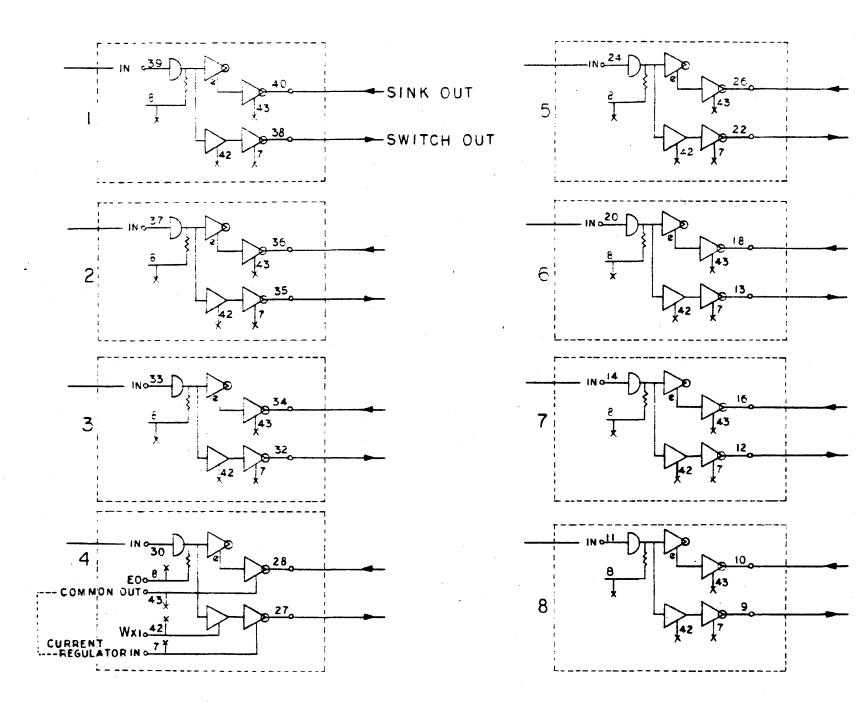

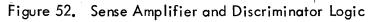

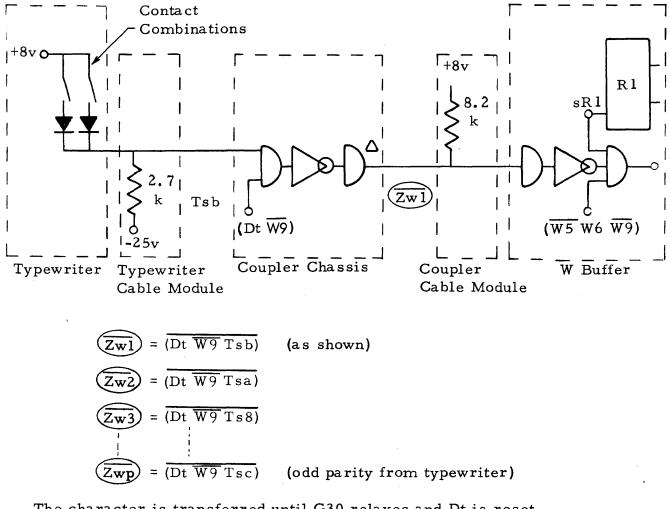

MEMORY EXPANSION 3, 19 MODULE OPERATION 3.21 Decoder 3.21 Selector Control 3.21 XY Selector 3.21 Current Regulator 3.24 Voltage Regulator 3.24 Z Driver 3.24 Sense Amplifier 3.24 Discriminator 3.28 BCD TYPEWRITER AND TAPE PUNCH INTRODUCTION 4.1 4.3 **Functional Description TYPEWRITER CODES** 4.4 Theory of Operation – Input 4.5 4.7 Theory of Operation – Output 4,10 Adjustments DICTIONARY OF BCD TYPEWRITER LOGIC TERMS 4.15 BCD TYPEWRITER LOGIC EQUATIONS 4.17 TAPE PUNCH 4.19 4.19 **Functional Description** Theory of Operation 4.19 **Circuit Considerations** 4.24 4,24 Adjustments DICTIONARY OF TAPE PUNCH LOGIC TERMS 4.29 TAPE PUNCH LOGIC EQUATIONS 4.30

IV

# LIST OF ILLUSTRATIONS

.

| Figure | Title                                     | Page |

|--------|-------------------------------------------|------|

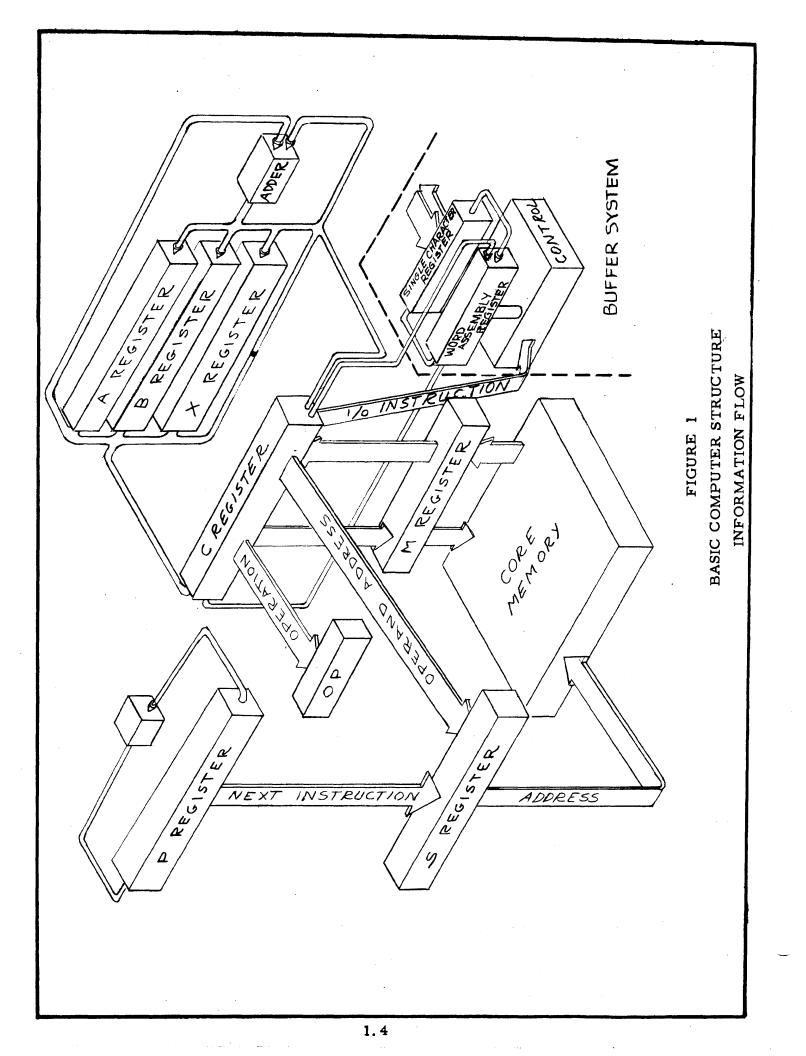

| 1      | Basic Computer Structure Information Flow | 1.4  |

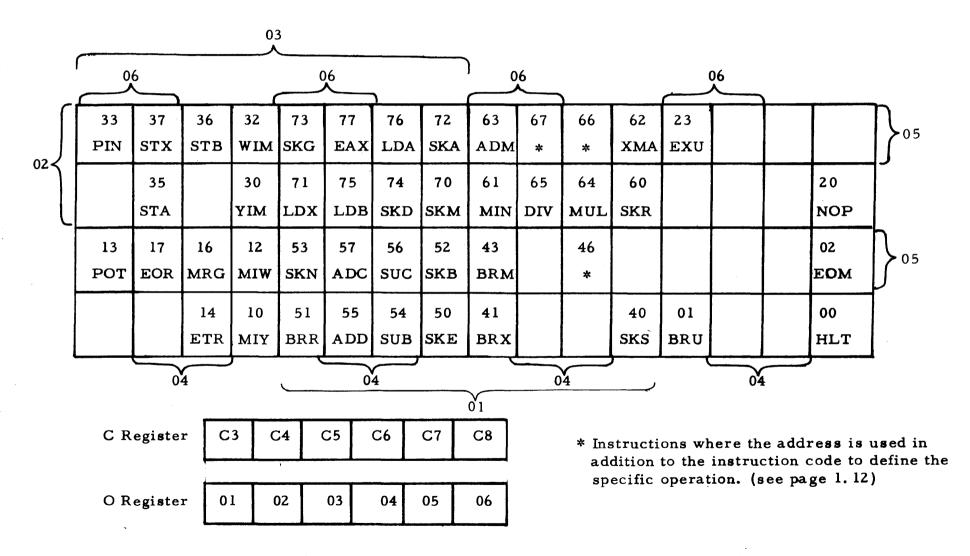

| 2      | Instruction List                          | 1.10 |

| 3      | Instruction Decoding                      | 1.13 |

| 4      | Pulse Sequence                            | 1.14 |

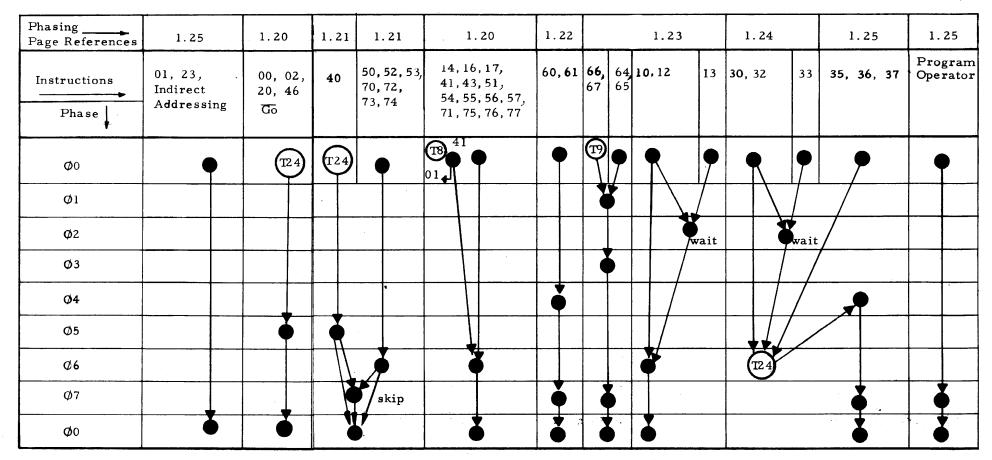

| 5      | Phase Sequence Chart                      | 1.19 |

| 6      | Accessing an Instruction                  | 1.31 |

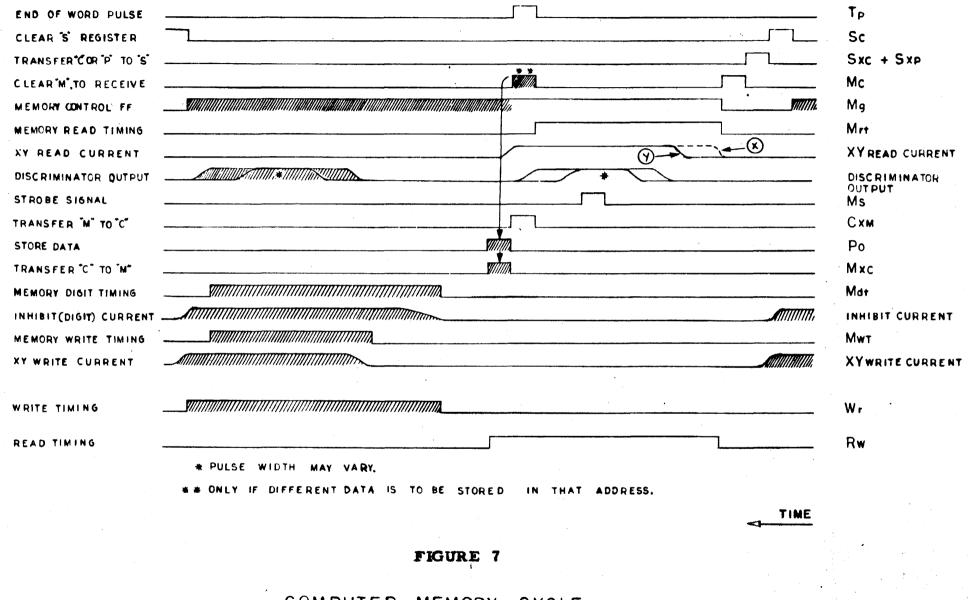

| 7      | Computer Memory Cycle                     | 1.40 |

| 8      | Program Operator                          | 1.49 |

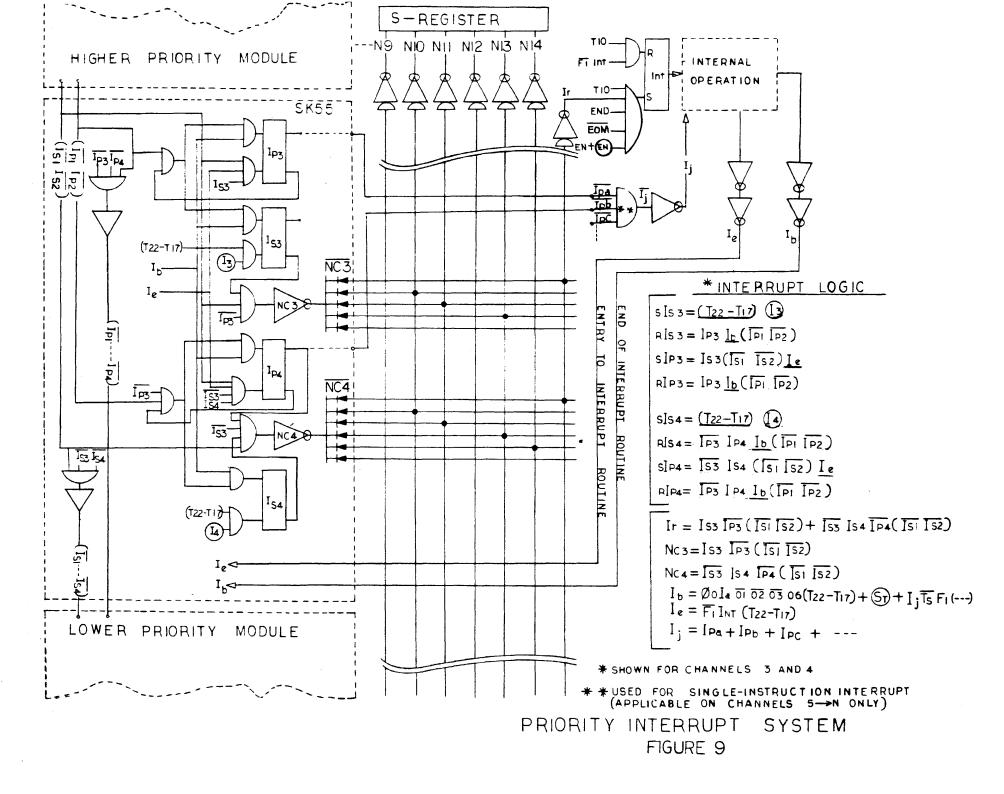

| 9      | Priority Interrupt System                 | 1.52 |

| 10     | Interrupt Timing A                        | 1.54 |

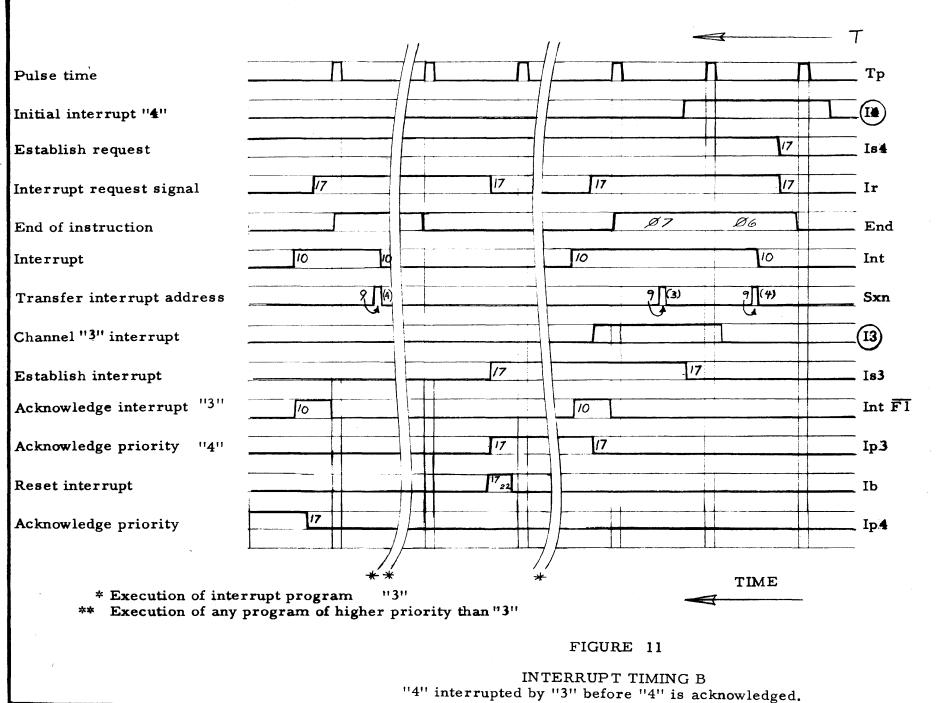

| 11     | Interrupt Timing B                        | 1.55 |

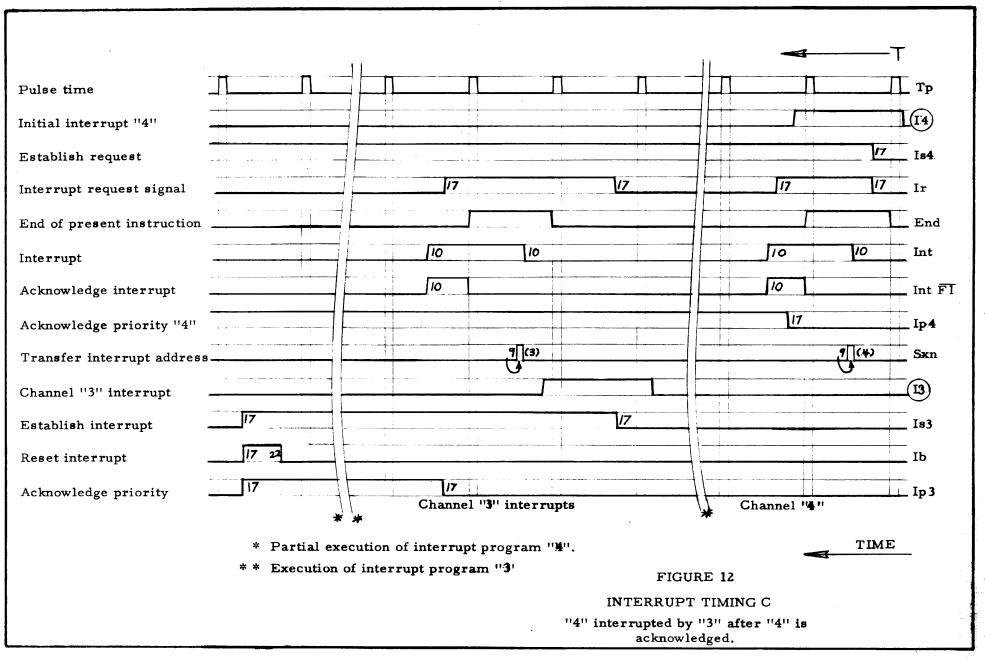

| 12     | Interrupt Timing C                        | 1.56 |

| 13     | Interrupt Timing D                        | 1.57 |

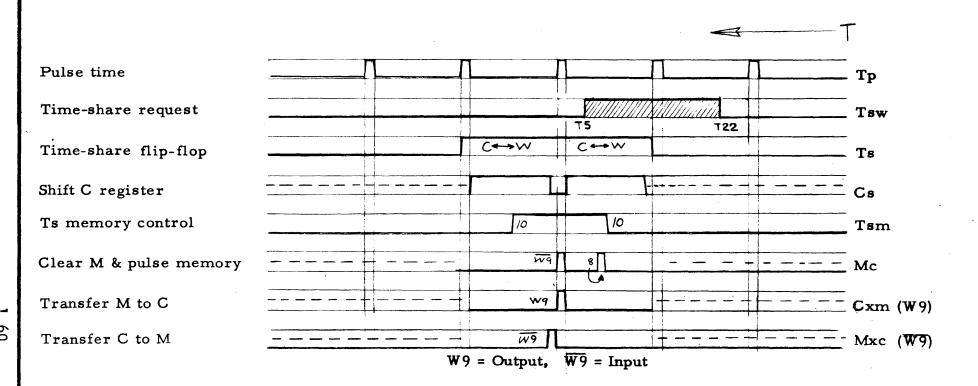

| 14     | Interlace Timing (Time-Share)             | 1.60 |

| 15     | Control Switch                            | 1.63 |

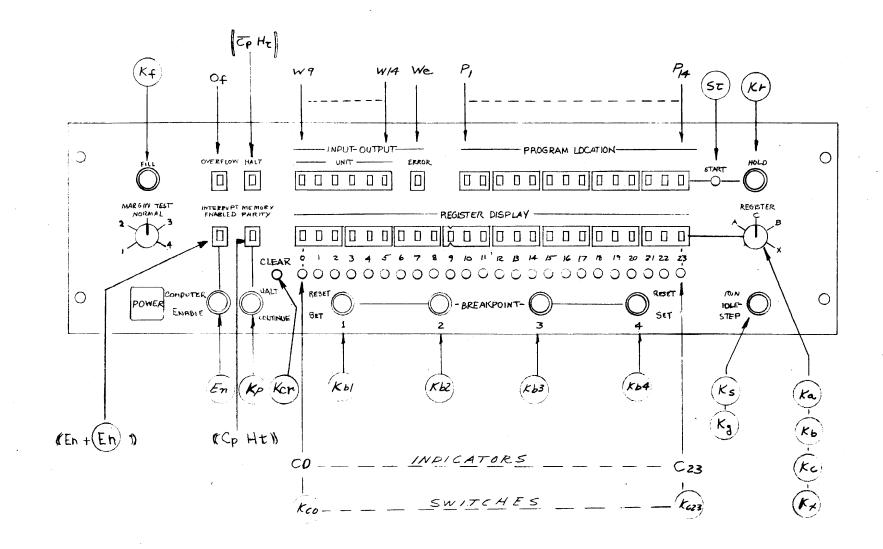

| 16     | Control Panel                             | 1.64 |

| 17     | Timing: Instruction 41 (BRX)              | 1.76 |

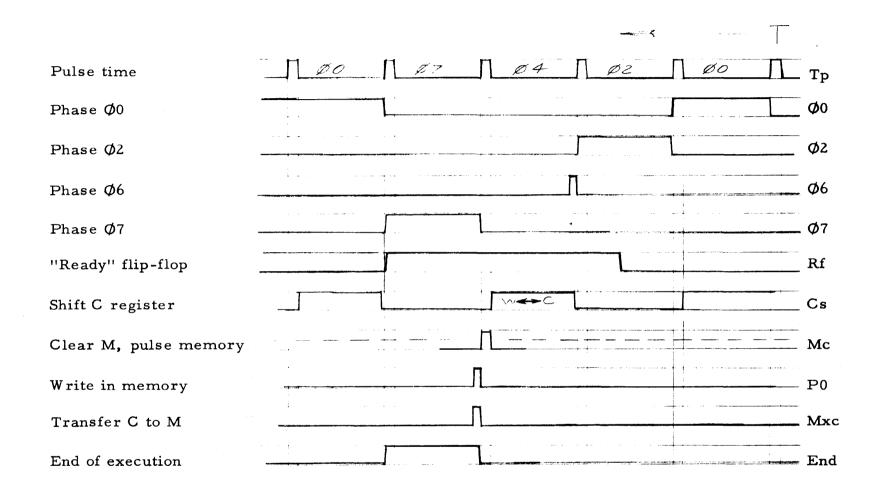

| 18     | Timing: Instructions 30, 32               | 1.82 |

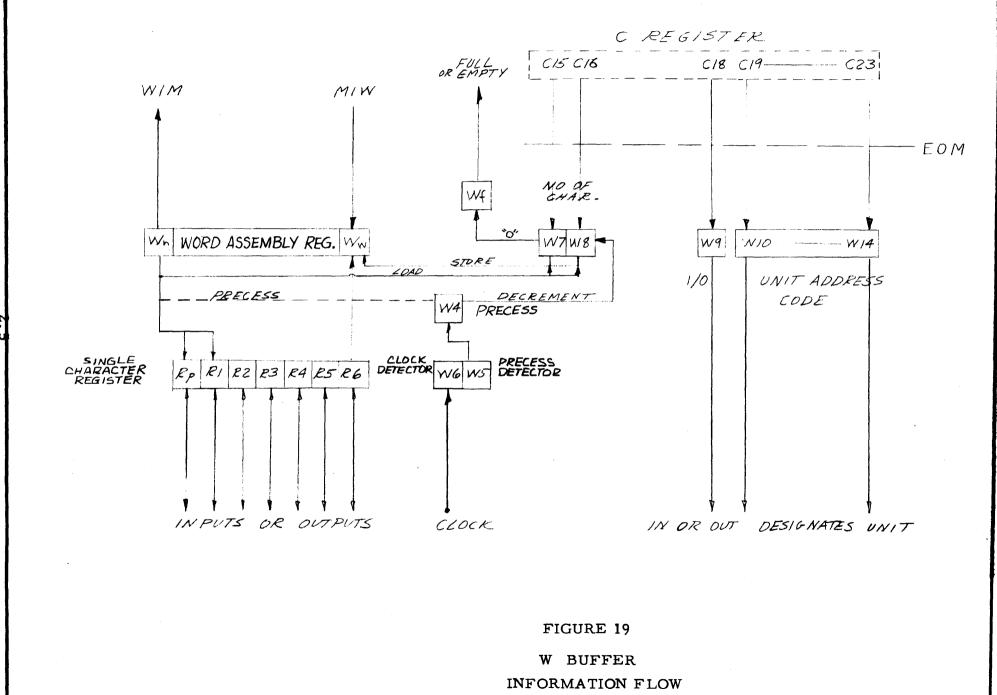

| 19     | W Buffer Information Flow                 | 2.5  |

| 20     | Input Timing Chart                        | 2.7  |

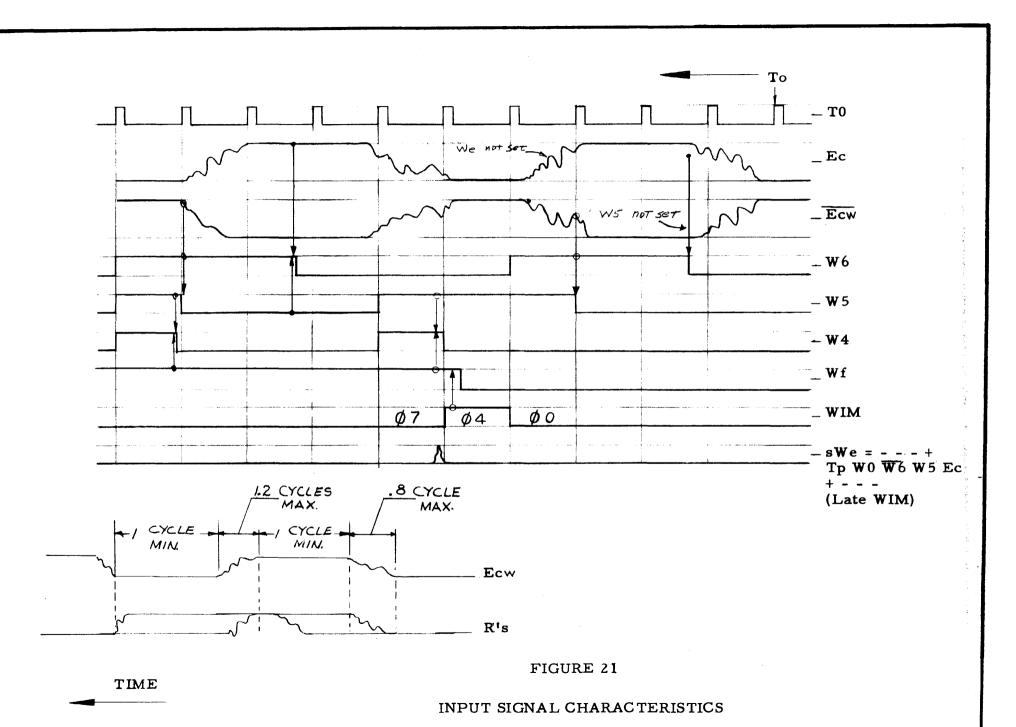

| 21     | Input Signal Characteristics              | 2.9  |

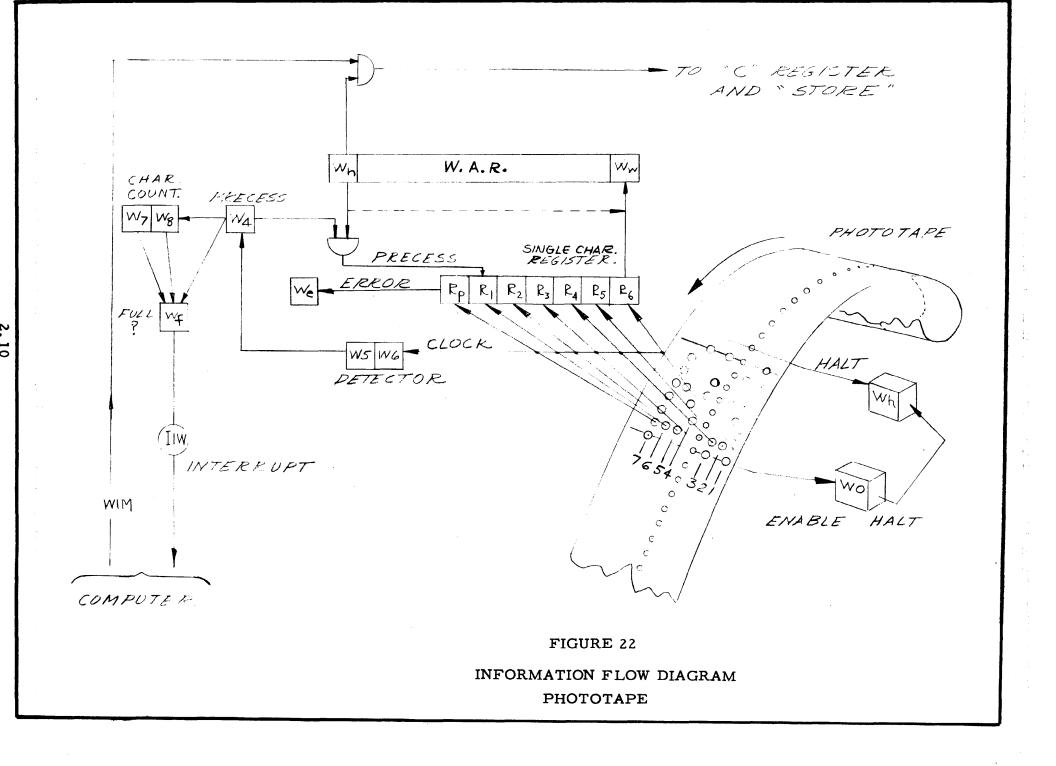

| 22     | Information Flow Diagram Phototape        | 2.10 |

| 23     | Termination Timing A Phototape Input      | 2.12 |

| 24     | Termination Timing B Phototape Input      | 2.13 |

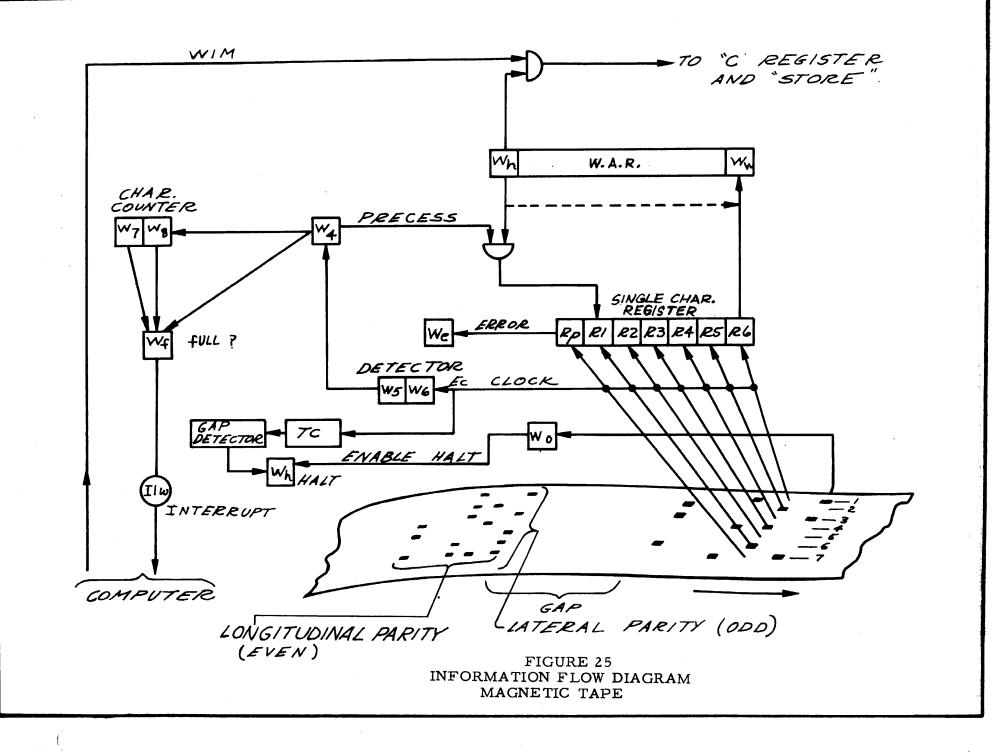

| 25     | Information Flow Diagram Magnetic Tape    | 2.14 |

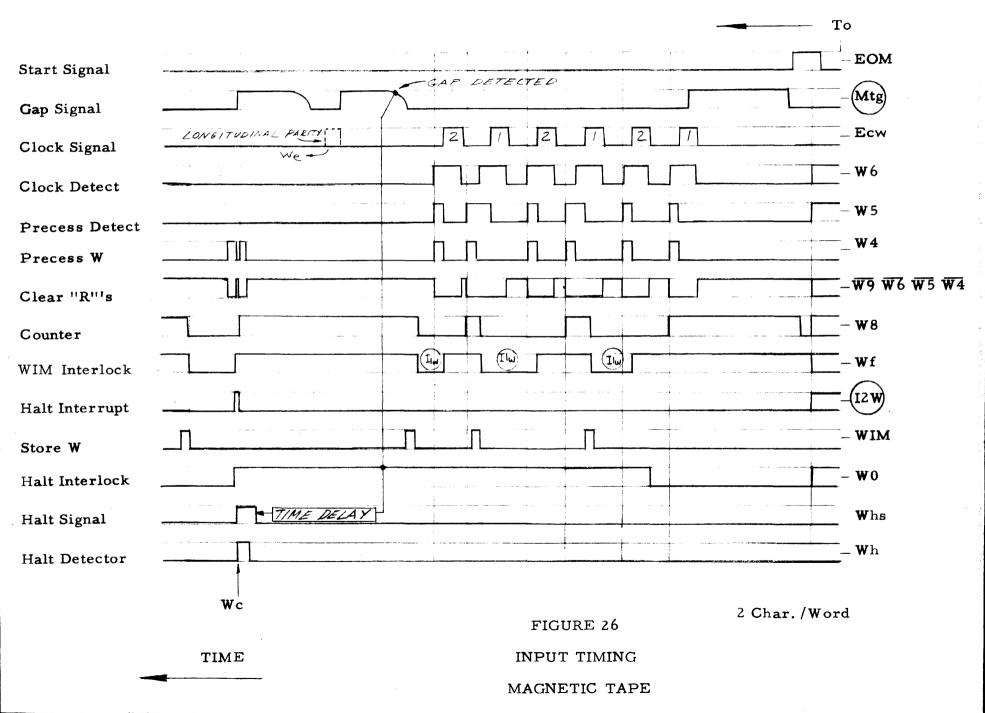

| 26     | Input Timing Magnetic Tape                | 2.15 |

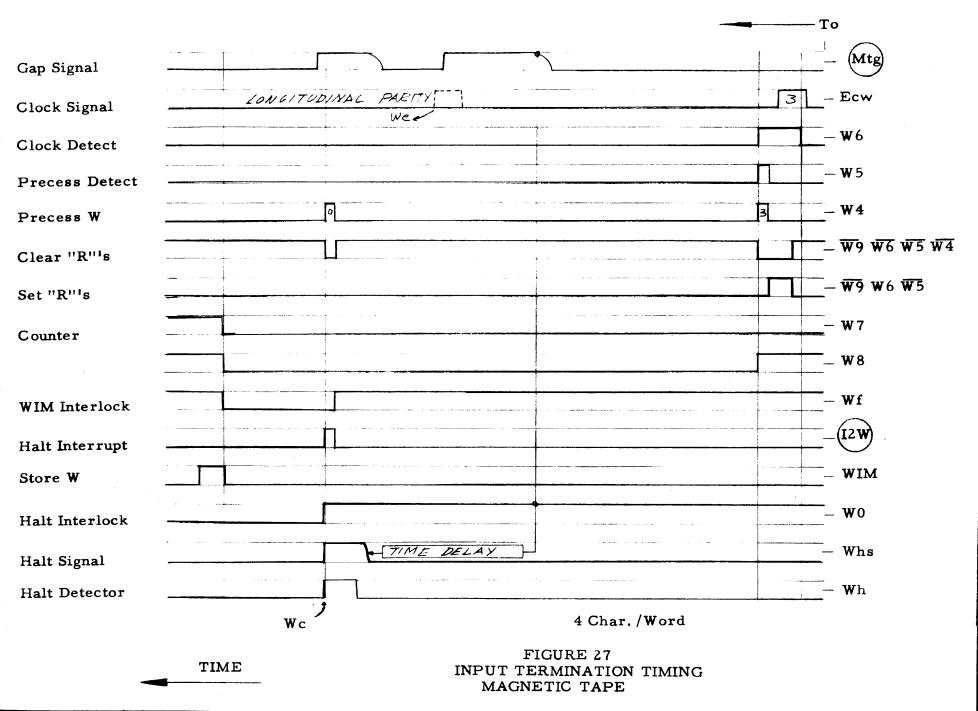

| 27     | Input Termination Timing Magnetic Tape    | 2.16 |

Illustrations

# LIST OF ILLUSTRATIONS (Cont.)

| Figure | Title                                            | Page  |

|--------|--------------------------------------------------|-------|

| 28     | Flow Diagram Output Process                      | 2.18  |

| 29     | Output Timing Chart 1                            | 2.20  |

| 30     | Output Timing Chart 2                            | 2.21  |

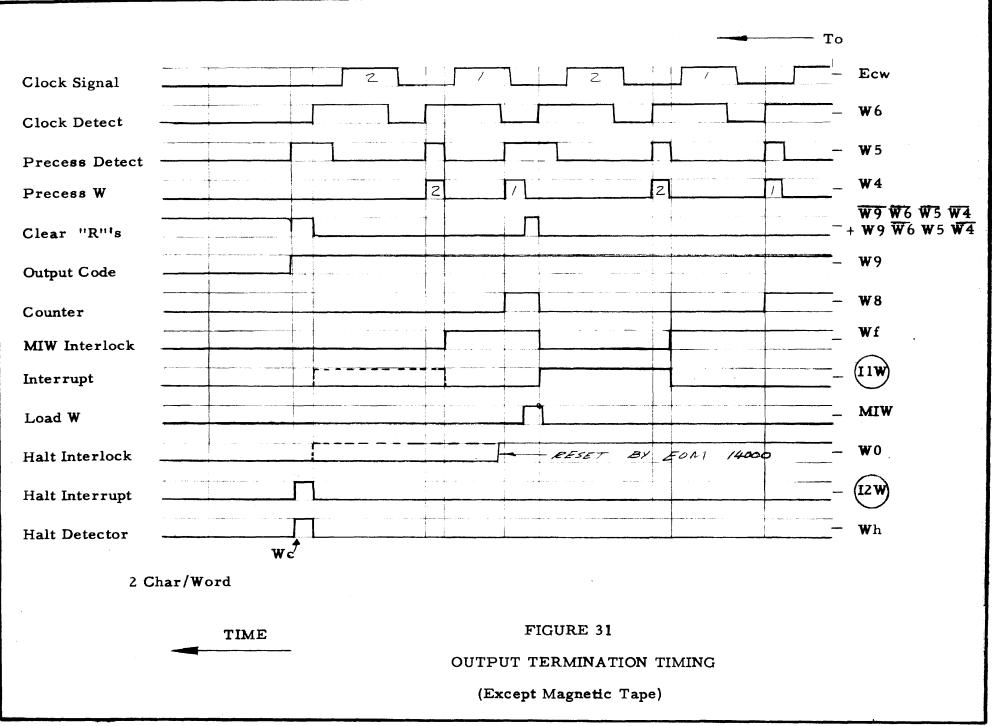

| 31     | Output Termination Timing (Except Magnetic Tape) | 2.22  |

| 32     | Output Termination Timing Magnetic Tape          | 2.23  |

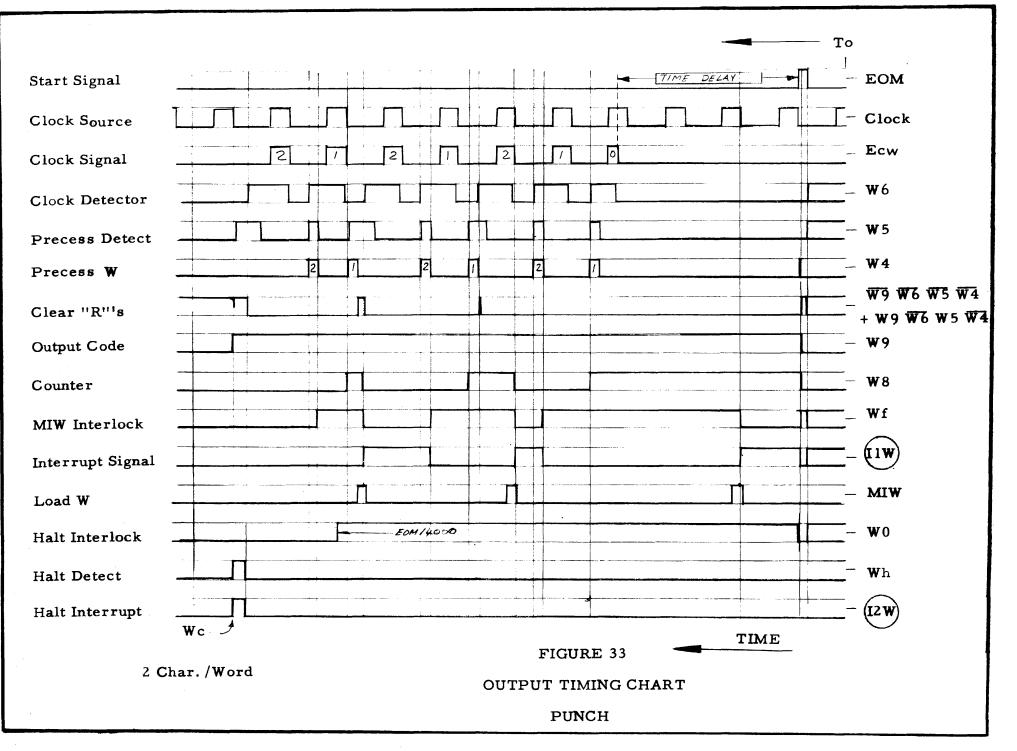

| 33     | Output Timing Chart Punch                        | 2.24  |

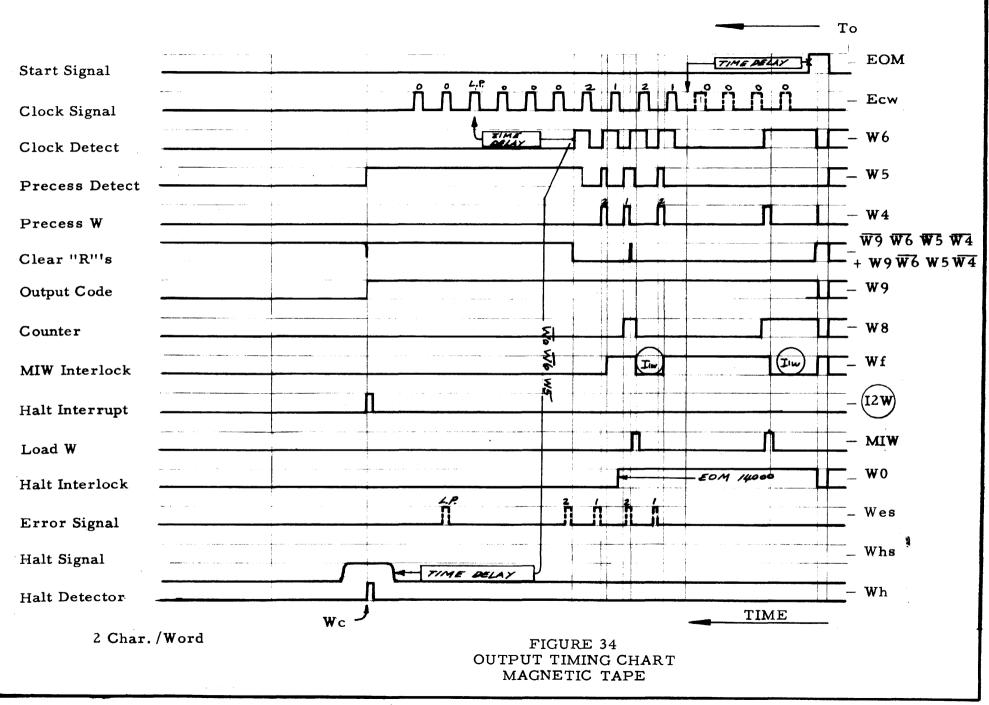

| 34     | Output Timing Chart Magnetic Tape                | 2.26  |

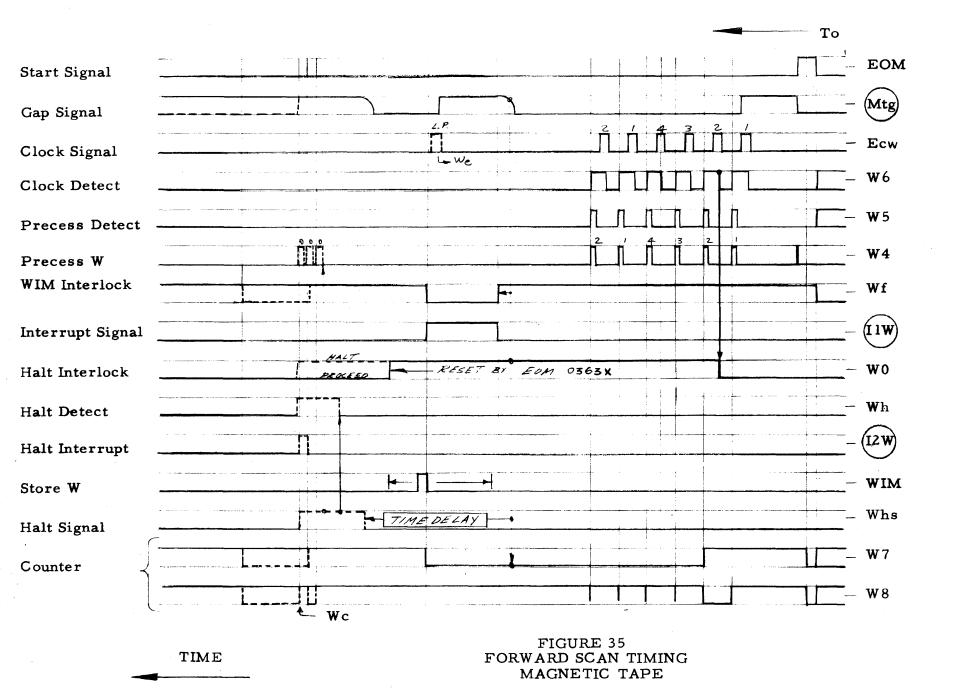

| 35     | Forward Scan Timing Magnetic Tape                | 2.27  |

| 36     | Reverse Scan Timing Magnetic Tape                | 2.30  |

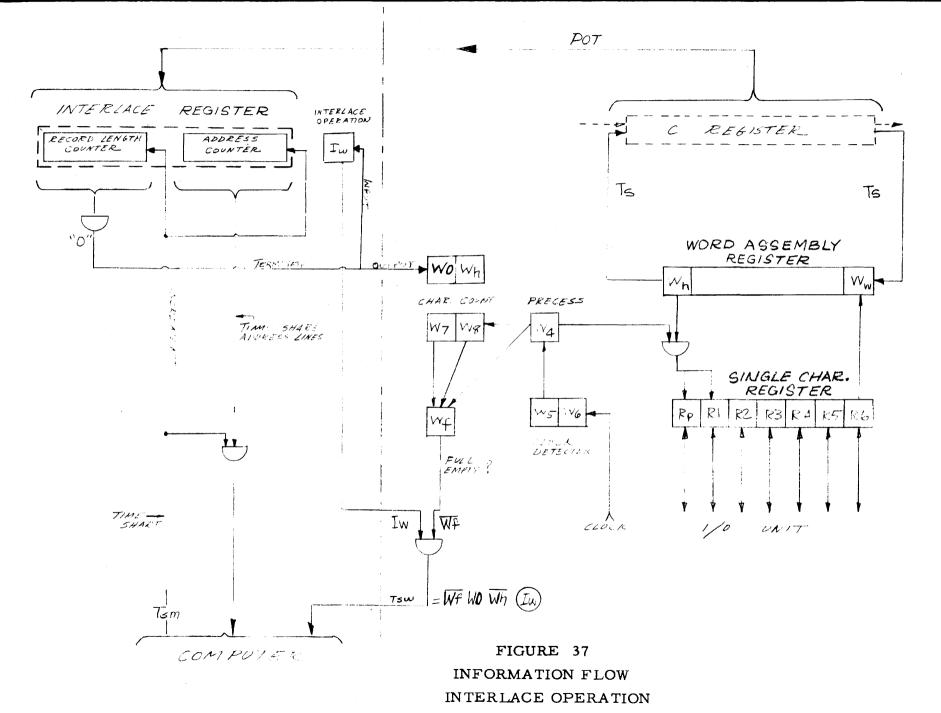

| 37     | Information Flow Diagram Interlace Operation     | 2.33  |

| 38     | Loading the Interlace Register                   | 2.35  |

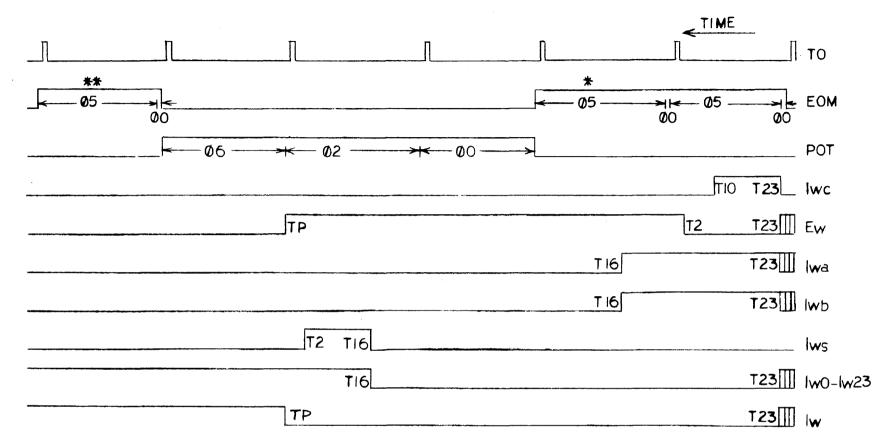

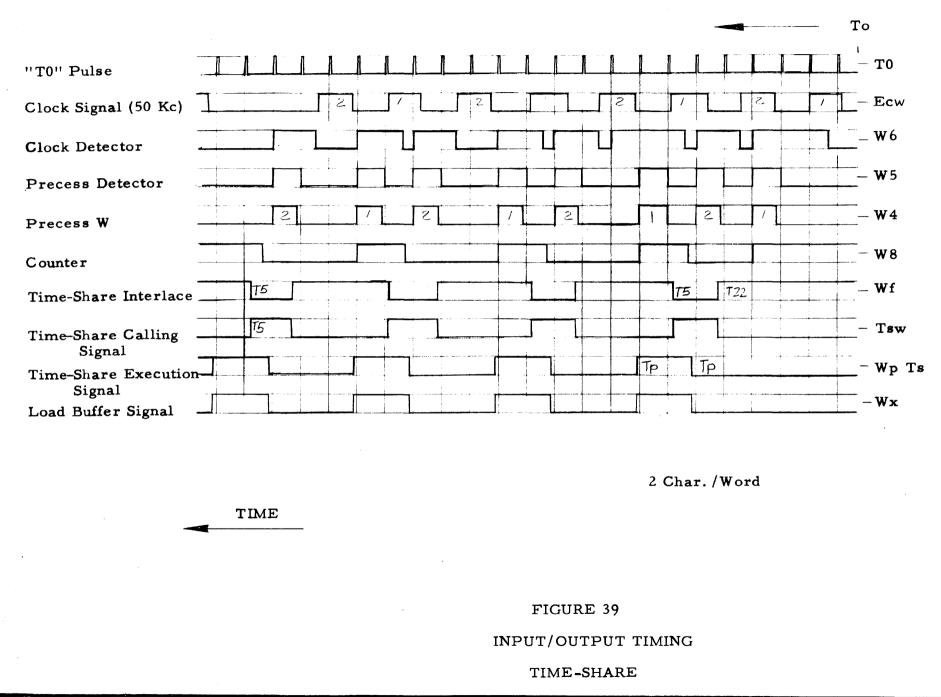

| 39     | Input/Output Timing Time-Share                   | 2.36  |

| 40     | Input Termination Timing Time-Share              | 2.37  |

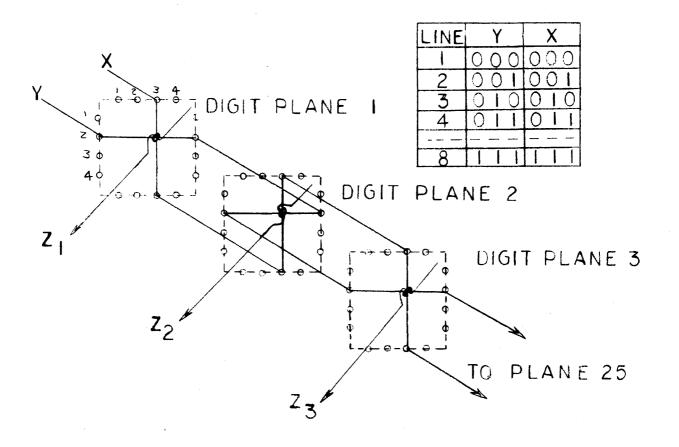

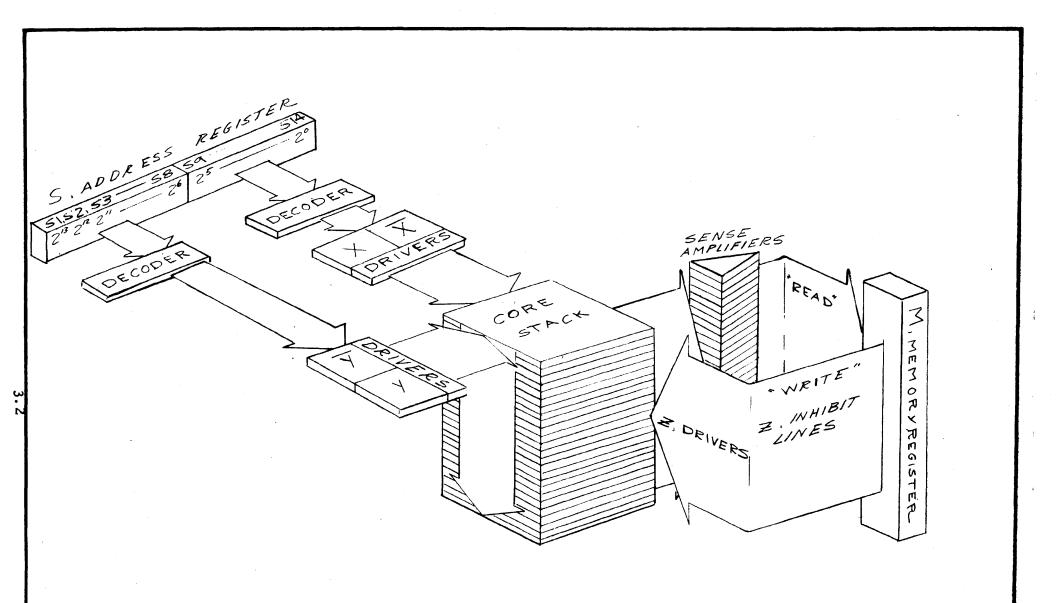

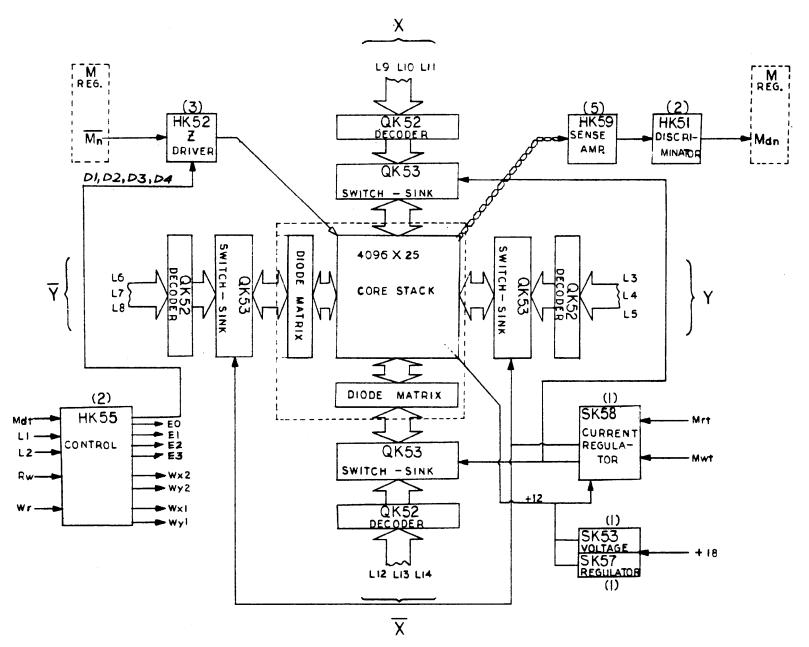

| 41     | Block Diagram – Magnetic Core Memory             | 3.2   |

| 42     | Hysteresis Loop                                  | 3.5   |

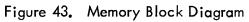

| 43     | Memory Block Diagram                             | 3.11  |

| 44     | Operation of Address 3037                        | 3.12  |

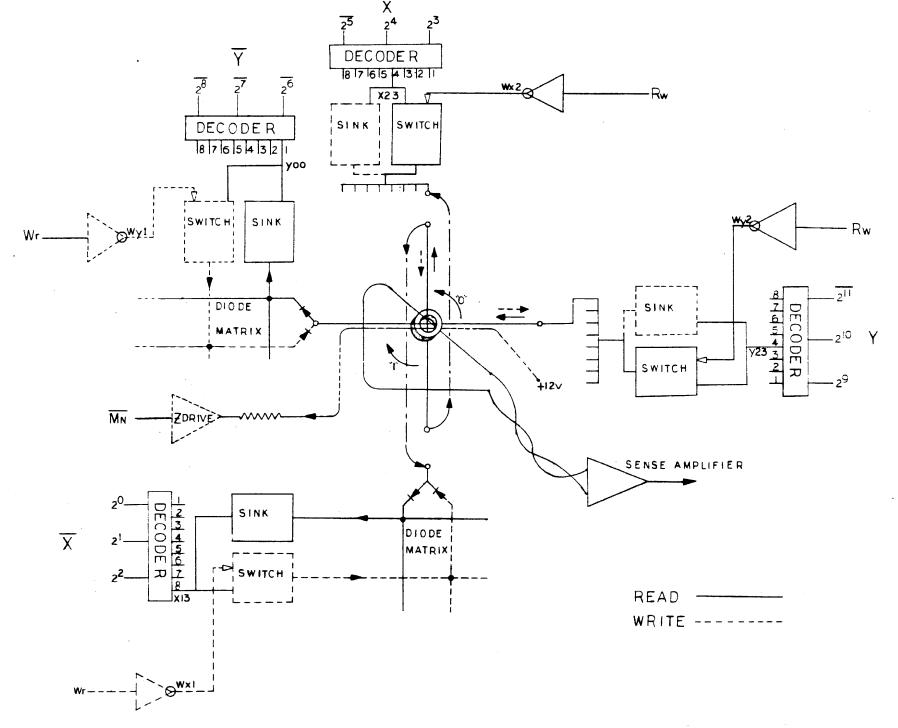

| 45     | Computer Memory Cycle                            | 3.14  |

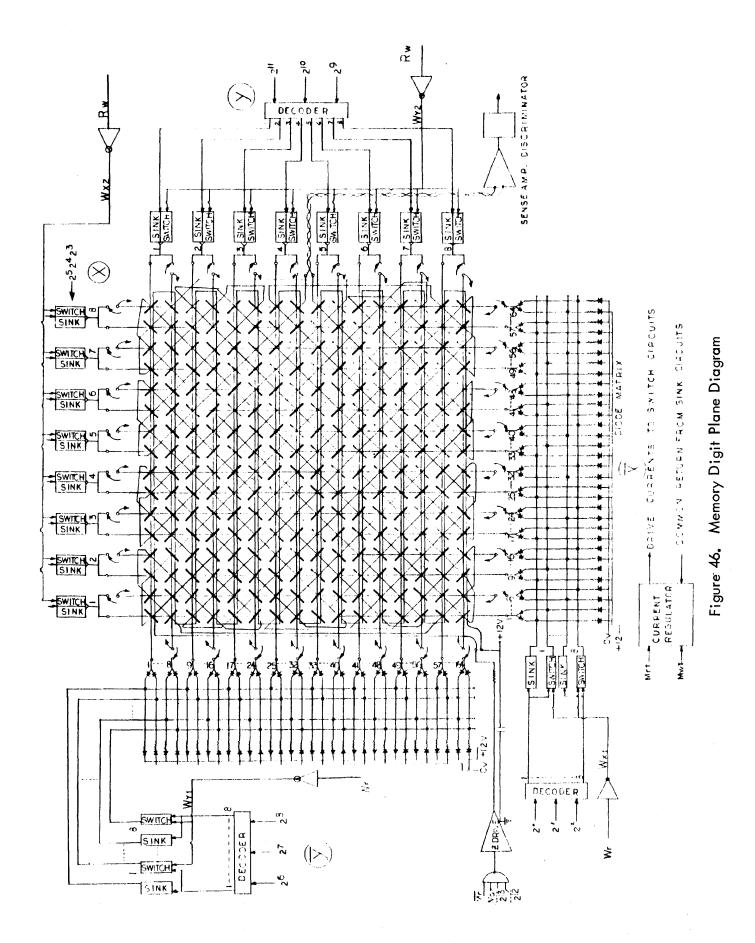

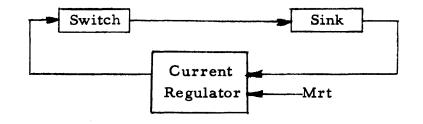

| 46     | Memory Digit Plane Diagram                       | 3.15  |

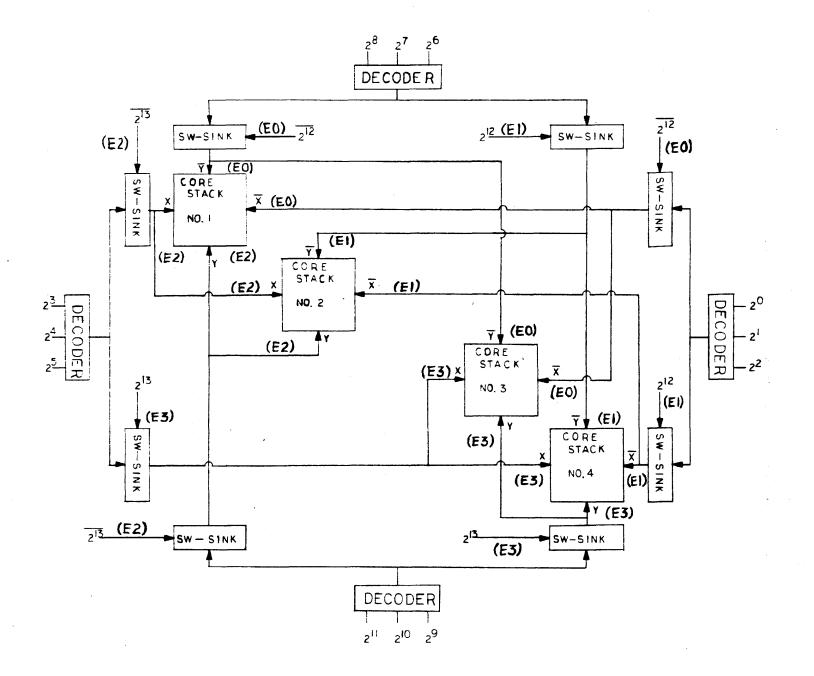

| 47     | Block Diagram – Memory Expansion                 | 3.20  |

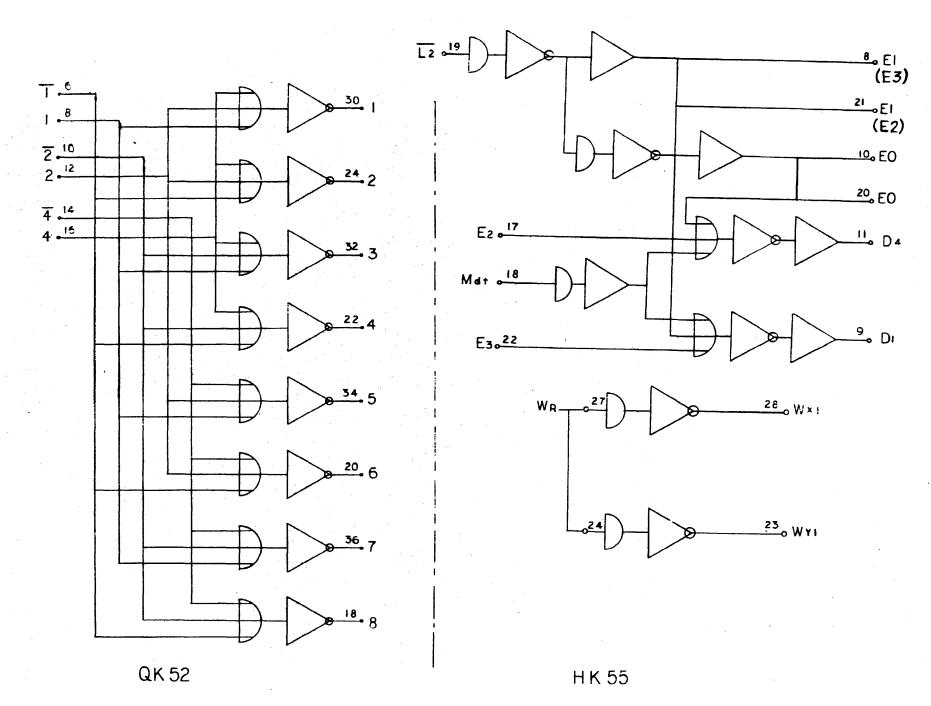

| 48     | Decoder and Selector Control Logic               | 3. 22 |

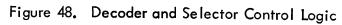

| 49     | XY Selector Logic                                | 3.23  |

| 50     | Voltage Regulator and Current Regulator          | 3.25  |

| 51     | Z Driver Schematic                               | 3.26  |

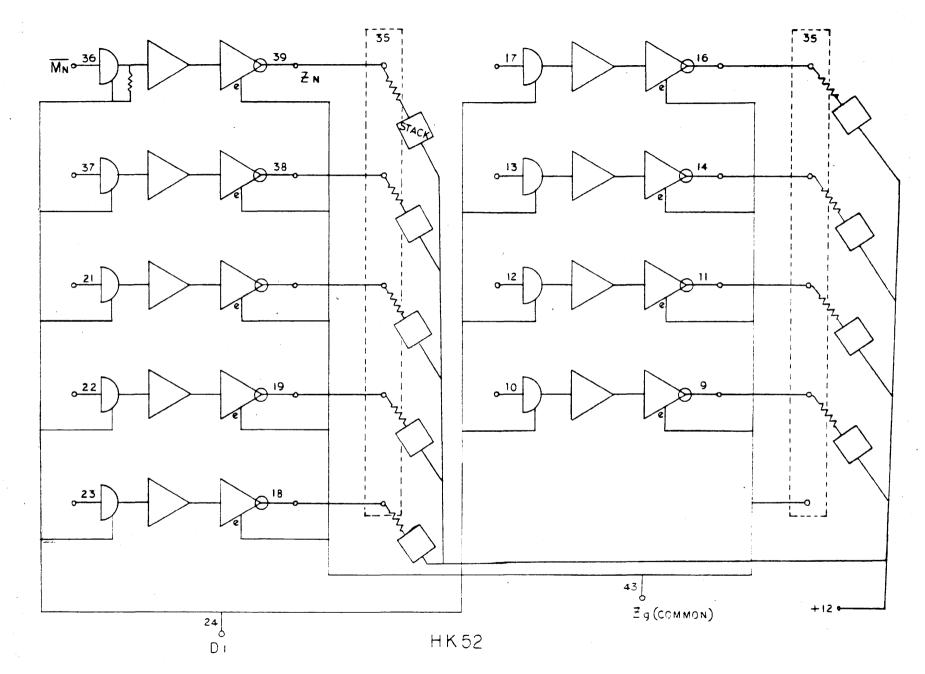

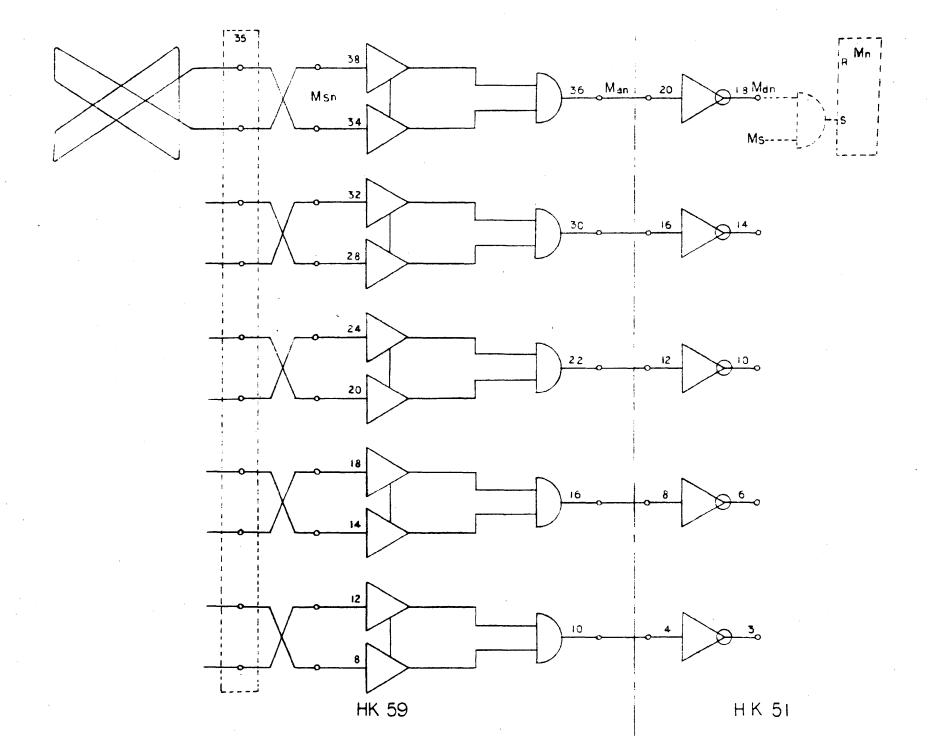

| 52     | Sense Amplifier and Discriminator Logic          | 3.27  |

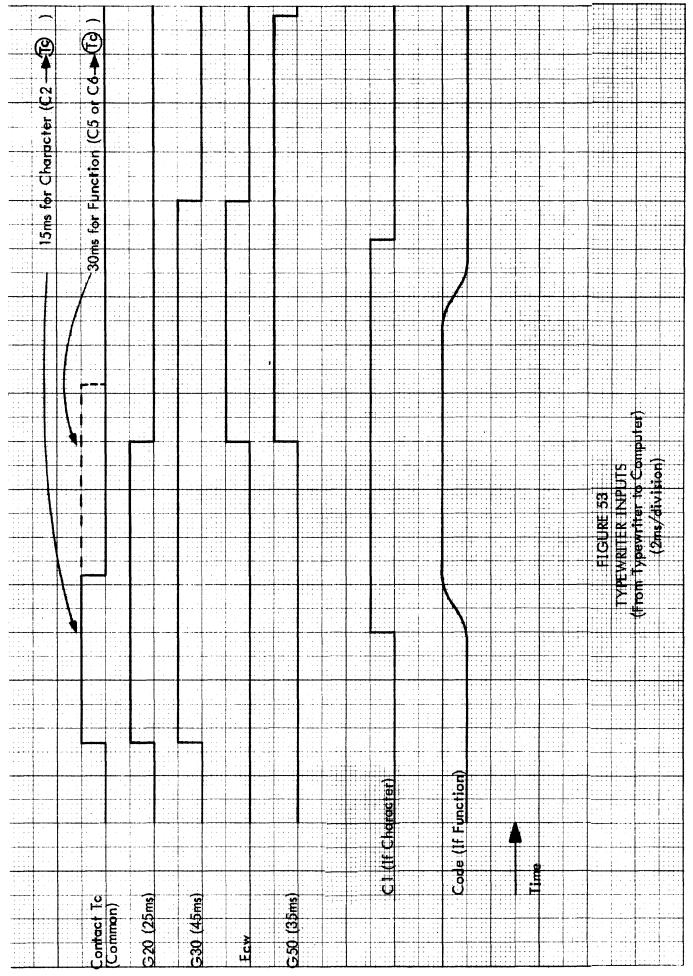

| 53     | Typewriter Inputs                                | 4.12  |

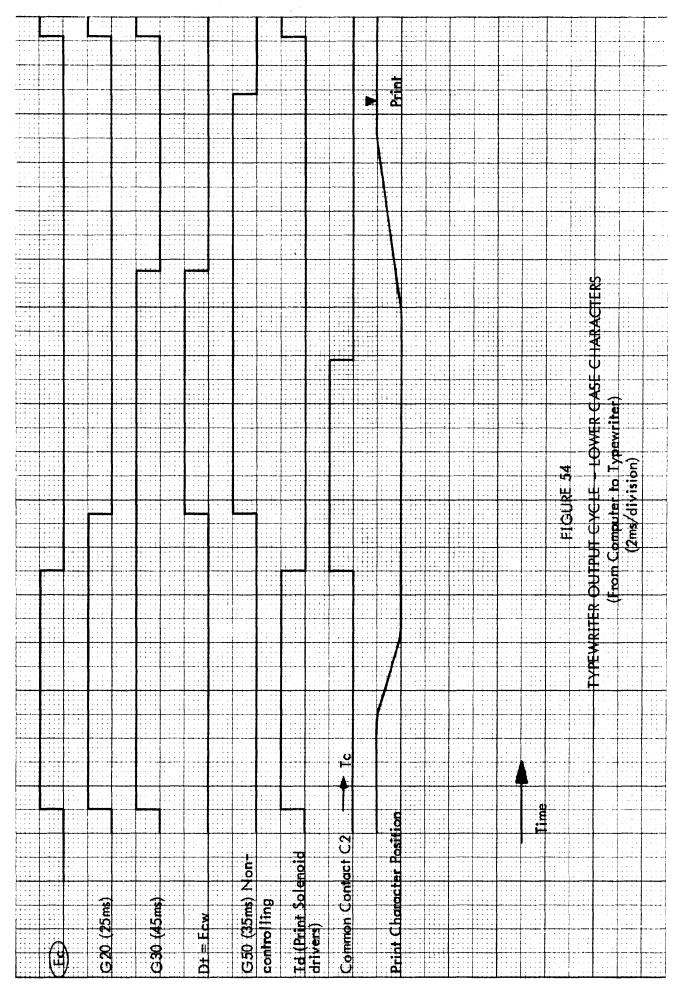

| 54     | Typewriter Output Cycle – Lower Case Characters  | 4.13  |

# Illustrations

# LIST OF ILLUSTRATIONS (Cont.)

| Figure | Title                                                                                      | Page |

|--------|--------------------------------------------------------------------------------------------|------|

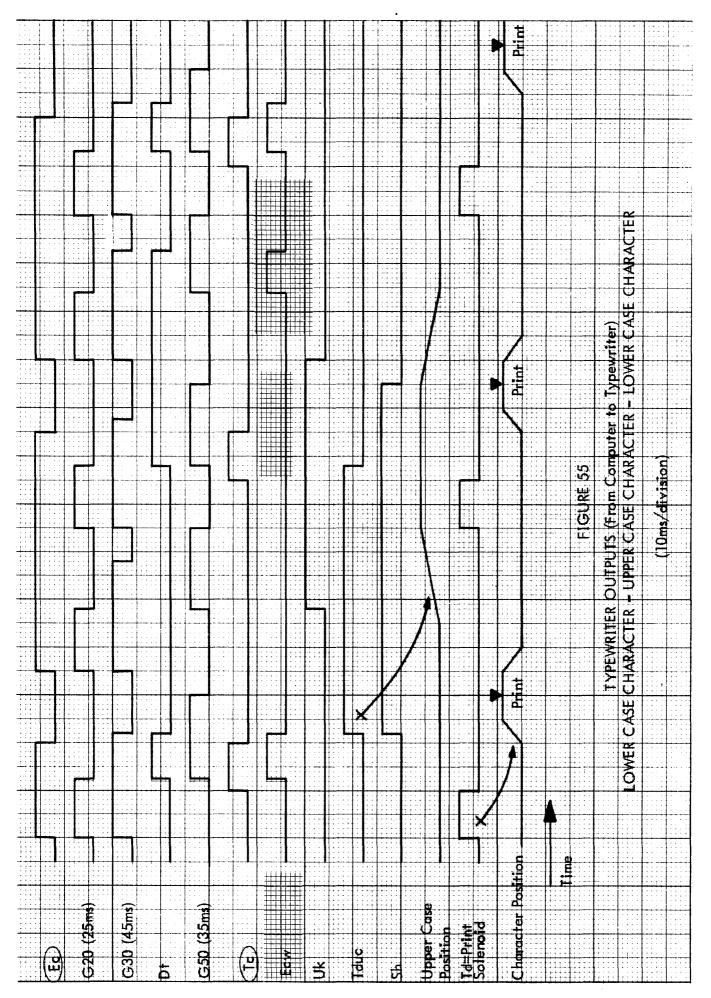

| 55     | Typewriter Outputs – Lower Case Character –<br>Upper Case Character – Lower Case Character | 4.14 |

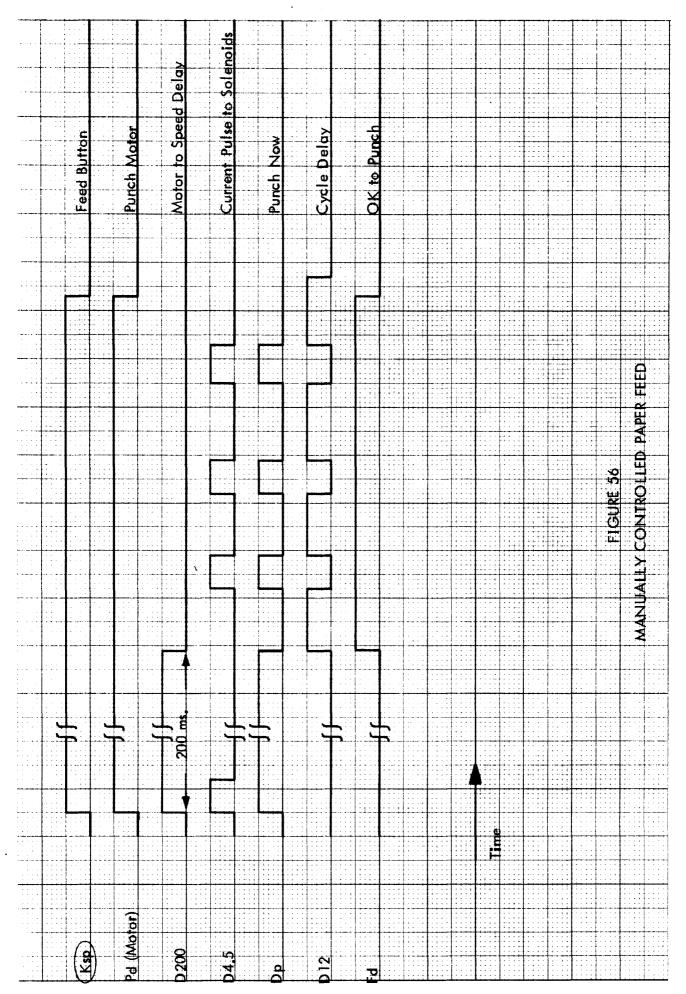

| 56     | Manually Controlled Paper Feed                                                             | 4.20 |

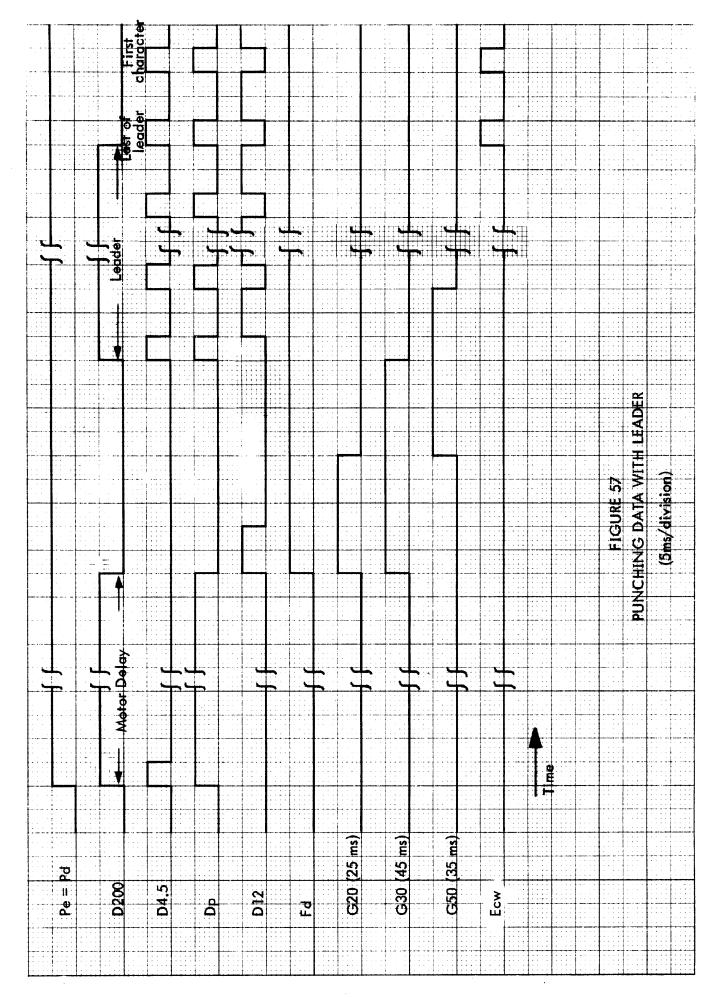

| 57     | Punching Data with Leader                                                                  | 4.26 |

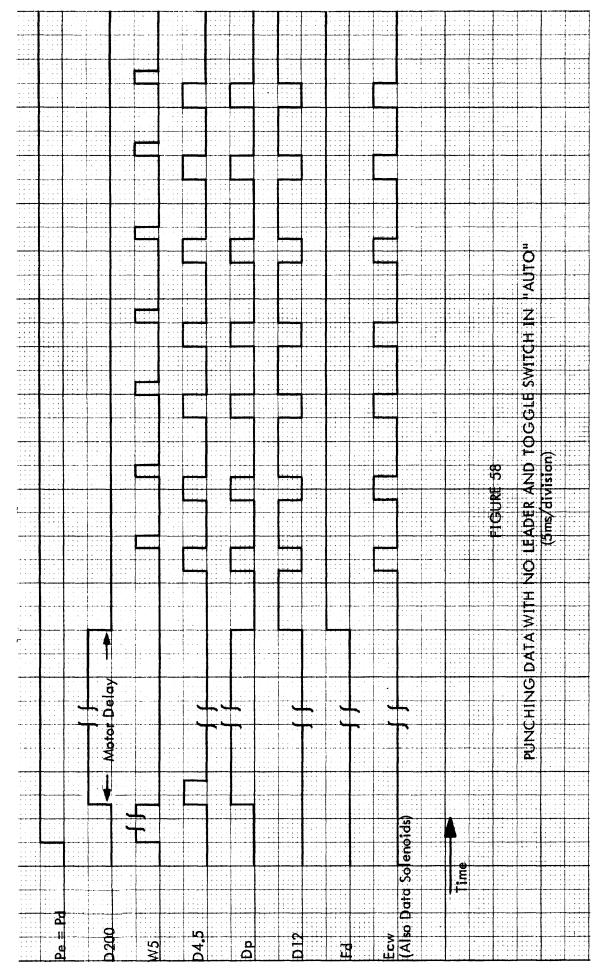

| 58     | Punching Data with No Leader and Toggle Switch<br>in "Auto"                                | 4.27 |

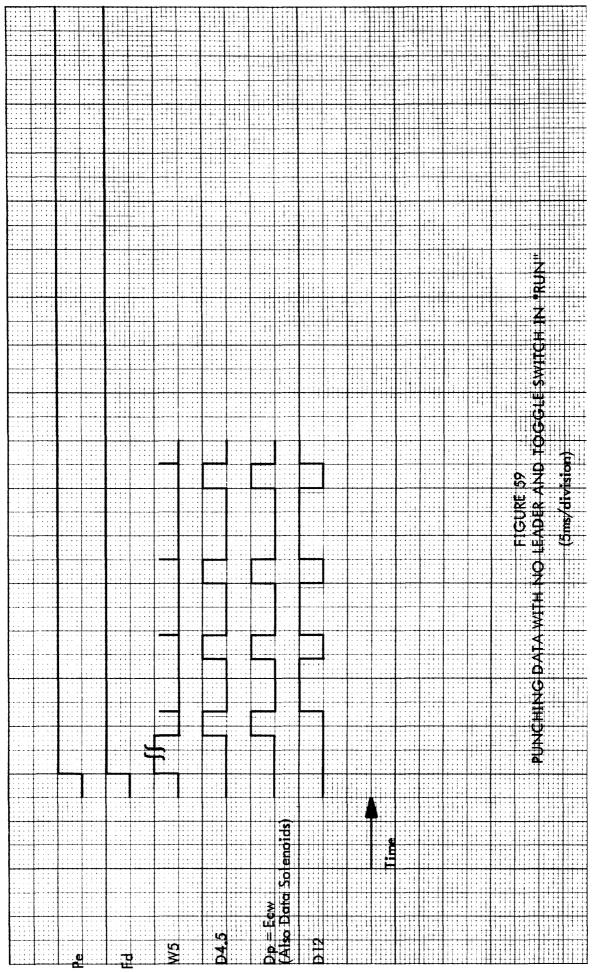

| 59     | Punching Data with No Leader and Toggle Switch<br>in "Run"                                 | 4.28 |

# SECTION I

{

# COMPUTER LOGIC

# INTRODUCTION

The Computer Logic Section describes the logical operation of the computer in detail. It is primarily intended for engineering, checkout, training and maintenance use. Descriptions are presented with the assumption that the reader has a working knowledge of Boolean algebra and basic digital operations.

For proper use of this publication, the reader should be familiar with the SDS Reference Manual for this computer.

# BASIC COMPUTER STRUCTURE AND OPERATION

NOTE: The description below includes only the most common conditions. Further details and qualifications are given later in this section.

The computer uses a 24-bit, single-address instruction:

| Instruction |   |   |   |   |   |   |   | Address |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|-------------|---|---|---|---|---|---|---|---------|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|             | • |   | x | X | X | x | x | x       | • | X  | x  | x  | x  | X  | x  | x  | x  | х  | х  | х  | x  | x  | x  |

| 0           | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8       | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 |

The instruction code occupies the six bit positions 3 through 8 and determines the operation which will be executed. For example, the binary configuration 101100 represents an octal "54", which is the designation for a subtraction instruction. The address field occupies the 14 bit positions, 10 through 23. In general, the address field represents the address of the operand. For example, it may represent the address of the number which is to be subtracted from the A register (accumulator) upon execution of a subtraction instruction.

The computer has nine registers, as represented in Figure 1. The P register (program counter) holds the 14-bit address of the next instruction to be executed. This 14-bit flip-flop register is incremented by one before reading a new instruction since the instructions are generally read in numerical sequence, i.e.,

| 10046 |  |

|-------|--|

| 10047 |  |

| 10050 |  |

| 10051 |  |

The address held in the P register is transferred in parallel to the 14-bit S flipflop register (memory address) where it sets up the address lines in the core memory for access to the word position addressed. The contents of the desired word are then transferred in parallel to the 24-bit M register from memory. During memory accessing or storing the S register will always hold the desired address and the M register will contain the operand or accept it from memory.

The instruction in the M register, after being received from memory, is transferred in parallel to the 24-bit C register where its fields are distributed as follows: The 6-bit instruction code field is transferred in parallel to the 6-bit flip-flop "O" (instruction code) register where it will be used to control execution of the instruction.

Depending upon the instruction to be executed, the address field containing the memory address of the desired operand is transferred in parallel to the S register. For example, the M register accepts the operand from memory and transfers it in parallel to the C register. At this point the code of the operation to be performed is held in the O register and the operand, upon which the operation is to be performed, is held in the C register.

During the execution of the instruction the operand is serially shifted out of the C register and into the Word Assembly register (WAR), Adder, A register, B register, or X register.

During the execution of "Store" instructions the operand address of the instruction is transferred to the S register to set up the Store address. The data to be stored is then shifted into the C register from its present location, and the information is transferred in parallel to the M register which stores it in memory.

To communicate with external devices such as a photo-reader, magnetic tape unit, punch and typewriter, the computer uses the WAR with its associated single character register (SCR) as shown in Figure 1. During an input process 6-bit characters from the external device are transferred into the SCR in parallel. When the Buffer "control" detects that a character has been received, it shifts the character into the WAR, and when the WAR contains the desired number of characters, a signal is sent to the computer to store the information held in the WAR into memory.

On output, the inverse operation is used; the information is shifted from the C register to the WAR and the computer returns to its previous program. The WAR now shifts one character at a time into the SCR where it is sent out in parallel to the external device in operation. When the buffer control detects that the WAR is empty, it signals the computer to load the WAR with another word for output.

When studying the information which follows, frequently refer to the Reference Manual to properly integrate the programming nomenclature and discussion with that of the internal operation.

# LOGICAL DESCRIPTION

# INSTRUCTION AND WORD FORMAT

The instruction list for the computer is shown in Figure 2. The instructions are numbered from 00 through 77 octally and are listed with their respective mnemonic codes and execution times. The execution time for a specific instruction is the number of word times (machine cycles) which elapse during the accessing of the instruction and its complete execution, including the accessing or storing of any operands.

# INSTRUCTION FORMAT

The instruction format is:

### 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23

| 0 | xx | Operation | x | Address |

|---|----|-----------|---|---------|

| Ł |    |           |   |         |

| 0:                        | Relative address bit (not used in logic) |

|---------------------------|------------------------------------------|

| 1 :                       | Index bit                                |

| 2:                        | Program operator                         |

| 3> 8 :                    | 6-bit instruction code                   |

| 9:                        | Indirect address bit                     |

| $10 \longrightarrow 23$ : | l4-bit address                           |

The programming functions of the above fields are:

# Index Register Bit:

A "1" in this position causes the contents of bits 10 through 23 of the index register (X register) to be added to the address portion of the instruction prior to execution.

# Program Operator Bit:

A "1" in this position causes the program operator bit and the 6 bits of the instruction code to be interpreted as an entry address for a subroutine.

# Instruction Code:

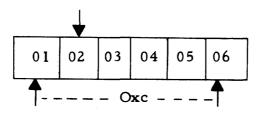

The 6 bits of the instruction code contain the 2-digit octal code for the instruction to be executed. This information is transferred to the "O" register flip-flops, 01, 02, 03, 04, 05, and 06.

# Indirect Address Bit:

A "1" in this position causes the computer to interpret bits 10 through 23 of the instruction (possibly modified by indexing) as the memory location where the effective address of the instruction may be found. A "0" causes bits 10 through 23 of the instruction to be interpreted as the effective address.

# Address:

The address is defined by bits 10 through 23 of the instruction. The address generally represents the memory location of the operand.

### DATA WORD FORMAT

The data word format is:

Tp 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24

Arithmetic is performed using the binary two's complement number system. The sign bit can then be considered to be integral with the data word. Data words consist of eight octal digits, each octal digit consisting of three binary digits (bits).

During all serial operations the 23rd bit position (least significant end) appears first in time.

# TWO'S COMPLEMENT ARITHMETIC

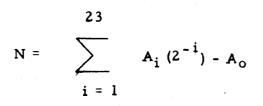

Considering the machine to be a fixed point, fractional computer, using two's complement arithmetic, any number stored in memory can be expressed by the following general formula:

$$N = A_0 (-2^{\circ}) + A_1 (+2^{-1}) + A_2 (+2^{-2}) + - - + A_{23} (+2^{-23}),$$

or it can be expressed as:

From this it can be seen that the largest allowable positive number is:

#

The minimum positive number is:

The maximum negative number is:

The minimum negative number is:

1. 1111111111111111111111111111

Numbers of negative magnitude are expressed in two's complement form and arithmetic operations, where the operands and answers are within the allowable range, maintain the negative numbers in two's complement form.

| Time | Code | Mne -<br>monic | Function                           | Time | Code | Mne-<br>monic | Function                                     |

|------|------|----------------|------------------------------------|------|------|---------------|----------------------------------------------|

| 1    | 00   | HLT            | Halt                               | 1, 2 | 40   | SKS           | Skip if M not set                            |

| 1    | 01   | BRU            | Branch to M                        | 1,2  | 41   | BRX           | $(X) + 1 \rightarrow X$ , branch if X9 = 1   |

| 1    | 02   | EOM            | Energize M                         |      | 42   |               |                                              |

|      | 03   |                |                                    | 2    | 43   | BRM           | (P) $\rightarrow$ M, BRU $\rightarrow$ M + 1 |

|      | 04   |                |                                    |      | 44   |               |                                              |

|      | 05   |                |                                    |      | 45   |               |                                              |

|      | 06   |                |                                    | 1    | 46   | *             |                                              |

|      | 07   |                |                                    |      | 47   |               |                                              |

| 2+   | 10   | MIY            | $(M) \longrightarrow Y$ when ready | 2,3  | 50   | SKE           | Skip if $(A) = (M)$                          |

|      | 11   |                |                                    | 2    | 51   | BRR           | $(M) + 1 \rightarrow P (BRU)$                |

| 2+   | 12   | MIW            | (M)→W when ready                   | 2,3  | 52   | SKB           | No skip if (B)(M) = 1 anywhere               |

| 3+   | 13   | POT            | Parallel out, when ready           | 2,3  | 53   | SKN           | Skip if (M) negative                         |

| 2    | I4   | ETR            | Extract                            | 2    | 54   | SUB           | (A) – (M) → A                                |

|      | 15   |                |                                    | 2    | 55   | ADD           | (A) + (M) → A                                |

| 2    | 16   | MRG            | Merge: (A) or (M)→A                | 2    | 56   | SUC           | (A) - (M)-Carry - A                          |

| 2    | 17   | EOR            | Exclusive OR                       | 2    | 57   | ADC.          | (A) + (M) + Carry → A                        |

\* \* Instructions where the address is used in addition to the instruction code to define the specific operation (See page 1.12)

FIGURE 2

INSTRUCTION LIST

1.10

.

| Time | Code | Mne -<br>monic | Function                | Time | Code | Mne-<br>monic | Function                        |

|------|------|----------------|-------------------------|------|------|---------------|---------------------------------|

| 1    | 20   | NOP            | No operation            | 3    | 60   | SKR           | (M)-1 -> M Skip if negative     |

|      | 21   |                |                         | 3    | 61   | MIN           | (M) + 1 →M                      |

|      | 22   |                |                         | 3    | 62   | XMA           | (M) (Exchange)                  |

| 1    | 23   | EXU            | Execute                 | 3    | 63   | ADM           | $(M) + (A) \longrightarrow M$   |

|      | 24   |                |                         | 4    | 64   | MUL           | Multiply                        |

| ·    | 25   |                |                         | 28   | 65   | DIV           | Divide                          |

|      | 26   |                |                         | **   | 66   | *             | <b>**</b> 2 + N/2 even          |

|      | 27   |                |                         | **   | 67   | *             | 2 + (N + 1)/2 odd               |

| 3+   | 30   | YIM            | (Y) — M when ready      | 2, 3 | 70   | SKM           | Skip if (A) = (M) on B mask     |

|      | 31   |                |                         | 2    | 71   | LDX           | (M) <b>→</b> X                  |

| 3+   | 32   | WIM            | (W) -> M when ready     | 2,3  | 72   | SKA           | No skip if (A) (M) = 1 anywhere |

| 4+   | 33   | PIN            | Parallel in, when ready | 2,3  | 73   | SKG           | Skip if $(A) > (M)$             |

|      | 34   |                |                         | 2,3  | 74   | SKD           | Difference Exponents and Skip   |

| 3    | 35   | STA            | (A) → M                 | 2    | 75   | LDB           | (M) → B                         |

| 3    | 36   | бтв            | (B) → M                 | 2    | 76   | LDA           | (M) <b>→</b> A                  |

| 3    | 37   | STX            | (X) → M                 | 2    | 77   | EAX           | Eff. address — X                |

\* Instructions where the address is used in addition to the instruction code to define the specific operation (see page 1.12).

FIGURE 2

INSTRUCTION LIST (CONTINUED)

-

# Instruction code 46

The specific operation to be executed for instruction code 46 is determined by the bits in the address portion of the instruction as follows:

| Address Bit |                  |

|-------------|------------------|

| 23          | Clear A          |

| 22          | Clear B          |

| 21          | Copy (A) into B  |

| 20          | Copy (B) into A  |

| 19          | Copy (B) into X  |

| 18          | Copy (X) into B  |

| 17          | Bits 15-23 only  |

| 16          | Copy (X) into A  |

| 15          | Copy (A) into X  |

| 14          | Copy -(A) into A |

|             |                  |

where the above functions can operate simultaneously if they do not conflict.

# Instruction codes 66 and 67

| 66 | 0 | 00NN | Right shift AB |

|----|---|------|----------------|

| 66 | 2 | 00NN | Right cycle AB |

| 67 | 0 | 00NN | Left shift AB  |

| 67 | 2 | 00NN | Left cycle AB  |

| 67 | 1 | 00NN | Normalize AB   |

The last two digits of the address specify the number of shifts or cycles to take place.

1.13

| PULSE COUNTER |             |    |    |    |    |    |    |  |

|---------------|-------------|----|----|----|----|----|----|--|

| Gray Count    | Pulse Time  | Q1 | Q2 | Q3 | Q4 | Q5 | 26 |  |

| 0             | Tl          | 0  | 0  | 0  | 0  | 0  | 1  |  |

| 1             | то          | 0  | 0  | 0  | 0  | 1  | 0  |  |

| 6             | END Tp      | 0  | 0  | 1  | 0  | 1  | 1  |  |

| 7             | START T24   | 0  | 0  | 1  | 0  | 0  | 0  |  |

| 8             | T23         | 0  | 1  | 1  | 0  | 0  | 1  |  |

| 9             | T22         | 0  | 1  | 1  | 0  | 1  | 0  |  |

| 10            | T2 1        | 0  | 1  | 1  | 1  | 1  | 1  |  |

| 11            | T20         | 0  | 1  | 1  | 1  | 0  | 0  |  |

| 12            | T19         | 0  | 1  | 0  | 1  | 0  | 1  |  |

| 13            | T18         | 0  | 1  | 0  | 1  | 1  | 0  |  |

| 14            | T17         | 0  | 1  | 0  | 0  | 1  | 1  |  |

| 17            | <b>T</b> 16 | 1  | 1  | 0  | 0  | 1  | 0  |  |

| 18            | T15         | 1  | 1  | 0  | 1  | 1  | 1  |  |

| 19            | T14         | 1  | 1  | 0  | 1  | 0  | 0  |  |

| 20            | T13         | 1  | 1  | 1  | 1  | 0  | 1  |  |

| 21            | T12         | 1  | 1  | 1  | 1  | 1  | 0  |  |

| 22            | T11         | 1  | 1  | 1  | 0  | 1  | 1  |  |

| 23            | T10         | 1  | 1  | 1  | 0  | 0  | 0  |  |

| 24            | Т9          | 1  | 0  | 1  | 0  | 0  | 1  |  |

| 25            | Т8          | 1  | 0  | 1  | 0  | 1  | 0  |  |

| 26            | T7          | 1  | 0  | 1  | 1  | 1  | 1  |  |

| 27            | Т6          | 1  | 0  | 1  | 1  | 0  | 0  |  |

| 28            | Т5          | 1  | 0  | 0  | 1  | 0  | 1  |  |

| 29            | T4          | 1  | 0  | 0  | 1  | 1  | 0  |  |

| 30            | Т3          | 1  | 0  | 0  | 0  | 1  | 1  |  |

| 31            | T2 🗸        | 1  | 0  | 0  | 0  | 0  | 0  |  |

|               |             |    |    |    |    |    |    |  |

|               |             |    |    |    |    |    |    |  |

# FIGURE 4

# PULSE SEQUENCE

# PULSE COUNTER

A pulse counter consisting of flip-flops Ql, Q2, Q3, Q4, Q5 and Q6 that counts the pulses that make up the twenty-six pulse times of each computer word.

The pulse counter is a modified gray code counter with Ql as the most significant bit.

The gray code is off-set from the 26-bit pulse count and certain counts are eliminated to facilitate decoding and counter design.

Note that computer pulse times are designated in reverse order, with respect to time.

Q6 acts as a straight binary counter generating the output which is counted by the gray code counter Q1 through Q5.

$$sQ6 = \overline{Q6}$$

$$rQ6 = Q6$$

The least significant gray code stage Q5 counts in gray sequence with the addition of (Q1 + Q3) on the reset side to force a skip of gray counts 15 and 16.

$sQ5 = \overline{Q5} Q6$ rQ5 = Q5 Q6 (Q1 + Q3)

Q4 counts in gray sequence with the addition of (Q1 + Q3) on the set side to force the skip of gray counts 2, 3, 4 and 5.

$$sQ4 = \overline{Q4} Q5 \overline{Q6} (Q1 + Q3)$$

$rQ4 = Q4 Q5 \overline{Q6}$

Q3 counts in gray sequence with the addition of T0 to force the skip of gray counts 2, 3, 4 and 5.

$sQ^{3} = \overline{Q3} Q4 \overline{Q5} \overline{Q6} + T0$  $rQ^{3} = Q3 Q4 \overline{Q5} \overline{Q6}$

Q2 and Q1 count in a gray sequence but the forced skip of gray counts 2, 3, 4, 5, 15 and 16 simplifies their set and reset expressions.

$$sQ^{2} = \overline{Q1} \ \overline{Q5} \ \overline{Q6}$$

$$rQ^{2} = Q1 \ \overline{Q4} \ \overline{Q5}$$

$$sQ^{1} = \overline{Q3} \ Q5 \ Q6$$

$$rQ^{1} = \overline{Q3} \ \overline{Q4} \ \overline{Q5}$$

1.15

# PULSE DECODING

Several multiple and single pulse times are decoded from the pulse counter for use in the computer logic:

Data word,  $\overline{\text{Tp}} \ \overline{\text{T24}} = \Omega 1 + \Omega 2 + \overline{\Omega 3}$ Most significant or Sign bit,  $T0 = \overline{\Omega 1} \ \overline{\Omega 2} \ \overline{\Omega 3} \ \Omega 5$ Least significant bit,  $T23 = \overline{\Omega 1} \ \Omega 2 \ \overline{\Omega 4} \ \overline{\Omega 5}$ Guard and first bit of word,  $T24 = \overline{\Omega 1} \ \overline{\Omega 2} \ \Omega 3 \ \overline{\Omega 5}$ Guard and last bit of word,  $Tp = \overline{\Omega 1} \ \overline{\Omega 2} \ \Omega 3 \ \Omega 5$ Address field,  $(T23 - T10) = \Omega 2$ Indirect address bit,  $T9 = \Omega 1 \ \overline{\Omega 2} \ \Omega 3 \ \overline{\Omega 4} \ \overline{\Omega 5}$

For additional requirements, the following pulse times are also decoded:

$(T22-T17) = \overline{Q1} Q2 \overline{T23}$   $(T21+T22) = \overline{Q1} Q2 Q3 Q5$   $T14 = Q1 Q2 \overline{Q3} \overline{Q5}$   $T10 = Q1 Q2 \overline{Q4} \overline{Q5}$   $(T5-T0) = \overline{Q2} \overline{Q3}$   $T1 = \overline{Q1} \overline{Q3} \overline{Q4} \overline{Q5}$

### PHASE CONTROL

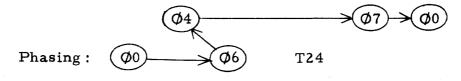

The various internal operations, such as transfers of information, clearing registers, read from memory, etc., which must take place during the reading and execution of instructions, are controlled by eight phases, designated phase Ø0 through phase Ø7. A general description of these eight phases is given below, followed by more detailed discussions on control of the phase sequence by the instruction code.

# PHASES

A phase chart is shown on page 1. 19 which indicates the phase sequencing for the various operation codes. Usually, each dot on the diagram represents one cycle time from Tp until the next Tp.

### Phase 0 $(\phi 0)$

This phase is the beginning of all instructions. Instructions start at Ø0 T24, with the new instruction in the C register and the instruction register cleared to "NOP" (20).

Indexing and indirect addressing are processed in phase  $\emptyset 0$ . Also, the memory regenerates the instruction (writes it back in memory because of destructive read-out) and fetches the operand. This process may require more than one cycle time, as in the case of indirect addressing, executing and transferring. This phase steps directly to phase  $\emptyset 5$  (at  $\emptyset 0$  T24) for some instructions requiring only one cycle time for execution.

At Ø0 T24 the instruction code is transferred to the OP code register (01, 02, 03, 04, 05 06).

#### Phase 1 ( $\emptyset$ 1)

This phase is the set-up or preparation phase for the shift, multiplication and division instructions. Phase 1 inhibits pulsing the memory for an operand.

# Phase 2 ( $\emptyset$ 2)

This phase is the wait phase for the input/output instructions, (10), (12), (13); (30), (32), (33). The computer waits in this phase until the data is ready. If the data is ready before the instruction is given, then phase Ø2 is by-passed, except for the parallel input/output instructions, (13), (33), where phase Ø2 will last only one cycle time for data to be transferred.

# Phase 3 (Ø3)

This phase is the execution phase for shifting, multiplication and division. It usually requires several word times. The duration of this phase in shifting is dependent upon the number of shifts required.

#### Phase 4 (Ø4)

This phase is the second cycle time of three-cycle instructions which write data into the memory. These three cycles are  $\phi_0 \rightarrow \phi_4 \rightarrow \phi_7$ . During phase  $\phi_4$  the P register is incremented for accessing the next instruction, and the word to be stored is shifted serially into the C register.

#### Phase 5 (05)

This phase is the execution phase for some single-cycle instructions. The C register does not shift and parity is not checked.

# Phase 6 $(\emptyset 6)$

This phase is the main execution phase of instructions requiring an operand, but no memory modification. These instructions are the two-cycle instructions, and include conditional skips which may require three cycles.

# Phase 7 ( $\phi$ 7)

During this phase memory regeneration (or new storage) and next instruction access are performed. The P register is not incremented unless the Skip flip-flop is high.

# End Cycles

An End is defined as the last cycle of execution for the particular instruction being performed. The End term designates that the next phase is to be phase  $\emptyset 0$  unless the instruction causes a skip.

End =  $\phi 5 + \phi 6 + \phi 7 + \phi 0 (- - - -)$

The last term is for unconditional branches.

#### PHASE COUNTER

A three-flip-flop counter, Fl, F2 and F3, controls the sequence and advancement of phases:

| Fl              | F2 | F3 | = | Ø0         |

|-----------------|----|----|---|------------|

| $\overline{F1}$ | F2 | F3 | Ξ | Øl         |

| <u>F1</u>       | F2 | F3 | = | Ø2         |

| Fl              | F2 | F3 | = | Ø3         |

| F1              | F2 | F3 | = | <b>Ø</b> 4 |

| Fl              | F2 | F3 | = | <b>Ø</b> 5 |

| Fl              | F2 | F3 | = | Ø6         |

| Fl              | F2 | F3 | = | Ø7         |

1.18

1

•

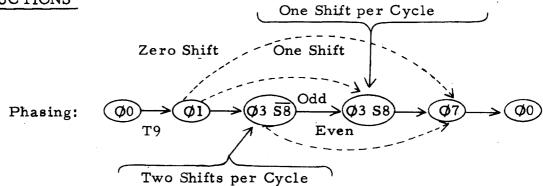

FIGURE 5

PHASE SEQUENCE CHART

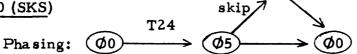

The following discussion indicates the actions of the phase counter during execution of the various instruction groups shown in the phase diagram.

SINGLE-CYCLE INSTRUCTIONS

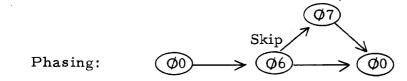

Phasing:

$$(00 \xrightarrow{T24} 05 \longrightarrow 00)$$

Instructions 00, 02, 20 and 46 advance directly to phase Ø5 from phase Ø0.

$$sF1 = T24 Ia \phi 0 Go C5 C8 C2 (C3 + C4) + - - - sF3 = T24 Ia \phi 0 Go C5 C8 C2 (C3 + C4) + - - -$$

The output of the C register flip- flops must be used for the instruction code, as the transfer to the O register is not made until T24.

The la term represents the indirect address flip-flop and need not be considered for this instruction group. Go is the control term which allows computation.

To reset to phase Ø0, F1 and F3 are reset at the first Tp,

$$rF1 = Tp End Sk$$

$rF3 = Tp End Sk$

where:

$$End = F1 F3 \overline{Ts} + F1 F2 \overline{Ts} + - - -$$

Ts is a time-share signal and freezes the internal operation of the computer for two machine cycles while external devices control access to memory. Sk is the flip-flop which signals for a skip condition and need not be considered in this instruction group.

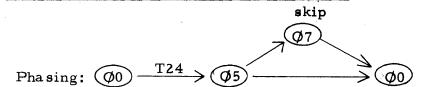

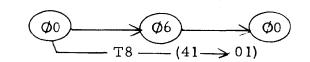

#### TWO-CYCLE INSTRUCTIONS

Phasing:

$$\emptyset 0 \rightarrow \emptyset 6 \rightarrow \emptyset 0$$

Instructions 14, 16, 17, 41, 43, 51, 54, 55, 56, 57, 71, 75, 76 and 77 advance to phase Ø6 from Ø0 at the first Tp, if there was no indirect addressing.

$sF1 = Tp Ia \phi 0 03 04 + Tp Ia \phi 0 01 04 + - -$  $sF2 = Tp Ia \phi 0 03 + Tp Ia \phi 0 01 02 + - - -$

If there had been an indirect addressing bit, Ia would be true and phase  $\emptyset 0$  would have been extended one or more additional word times until Ia was reset by the effective address. The computer resets to phase  $\emptyset 0$  at the first Tp of phase  $\emptyset 6$ .

$$rF1 = Tp End Sk$$

$rF2 = Tp End Sk + - - -$

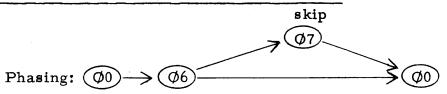

#### THREE-CYCLE CONDITIONAL SKIP INSTRUCTIONS

Instructions 50, 52, 53, 70, 72, 73 and 74 advance to phase  $\phi_6$  at the end of phase  $\phi_0$ .

$sF1 = Tp Ia \phi 0 01 \overline{04} + Tp Ia \phi 0 03 04$   $sF2 = Tp Ia \phi 0 03 + -$  $rSk = \phi 0 T0 + - - -$

These instructions are conditional skip instructions where the Sk (Skip) flip-flop is left in a set condition at the end of phase  $\phi 6$ , if a skip is to occur. If Sk is true, the phase counter advances to phase  $\phi 7$ .

$\mathbf{s}\mathbf{F3} = \mathbf{Tp} \ \mathbf{Sk} \ \mathbf{\overline{Ts}} + \mathbf{---}$

Sk will be reset during phase Ø7.

rSk = 07 T0 + - - -

If Sk was left in a reset condition at the end of phase  $\phi 6$ , the phase counter will reset directly to phase  $\phi 0$ .

rFl = Tp End Sk rF2 = Tp End Sk + - - rF3 = Tp End Sk

Note that phase  $\phi 6$  and  $\phi 7$  are both end cycle phases, and if a skip occurs, End will be true for two cycles. The conditions under which Sk is set during phase  $\phi 6$  are discussed in the material on "Skip and Branch Instructions".

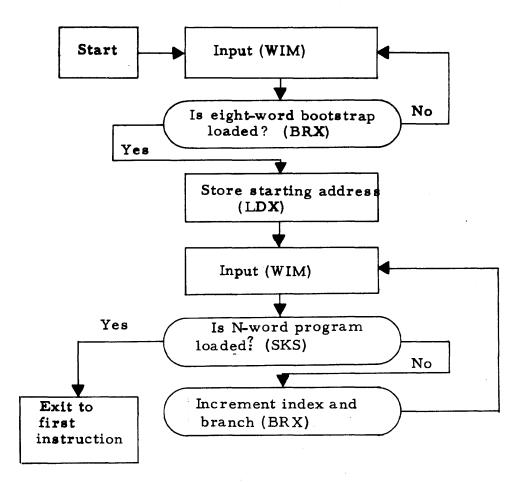

TWO-CYCLE CONDITIONAL SKIP INSTRUCTIONS

Instruction 40 advances directly to phase Ø5 at Ø0 T24.

$\mathbf{sF1} = \mathbf{T24} \ \overline{\mathbf{Ia}} \ \phi 0 \ \mathbf{Go} \ \overline{\mathbf{C5}} \ \overline{\mathbf{C8}} \ \overline{\mathbf{C2}} \ \overline{\mathbf{(C3} + \mathbf{C4})} + - - \\ \mathbf{sF3} = \mathbf{T24} \ \overline{\mathbf{Ia}} \ \phi 0 \ \mathbf{Go} \ \overline{\mathbf{C5}} \ \overline{\mathbf{C8}} \ \overline{\mathbf{C2}} \ \overline{\mathbf{(C3 + C4)}} + - - -$

This phase advancement is identical to the single-cycle operation discussed under Phase Control.

During phase Ø5, instruction 40 tests to see if M (external signal) is in a true or false condition. If the signal is false, then the Sk (Skip) flip-flop will be set and a skip will occur.

$sSk = T0 \ 05 \ 01 \ \overline{04}$  (external signal) + - - -

If Sk is set at T0, then the phase counter advances to phase Ø7 at Tp to perform the skip.

$$sF2 = Tp Ts Sk - - + - - -$$

At the completion of phase  $\emptyset$ 7, or at the completion of phase  $\emptyset$ 5, (if the skip condition were false and Sk was not set) the phase counter is reset to phase  $\emptyset$ 0.

$rF1 = Tp End \overline{Sk}$  $rF2 = Tp End \overline{Sk} + - -$  $rF3 = Tp End \overline{Sk}$

Sk is reset during phase Ø7.

rSk = Ø7 T0 + - - -

Note that phases Ø5 and Ø7 are both end-cycle phases, and if a skip occurs, End will be true for two cycles.

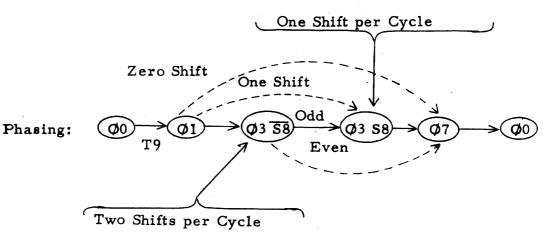

# THREE-CYCLE MEMORY INCREMENT OR DECREMENT INSTRUCTIONS

Phasing:

$$(\phi_0) \longrightarrow (\phi_4) \longrightarrow (\phi_7) \longrightarrow (\phi_0)$$

Instructions 60 and 61 advance to phase Ø4 at the completion of phase Ø0. During Ø0 indexing or indirect addressing may have been performed.

$$sFl = Tp Ia 00 01 04 + - - -$$

At the completion of phase Ø4 (one cycle), during which the contents of memory are decremented for 60 or incremented for 61, the phase counter is advanced to phase Ø7.

$\mathbf{sF2} = \mathrm{Tp} \ \overline{\mathrm{Ts}} \ \mathbf{\phi}4 + \mathbf{-} - \mathbf{-}$  $\mathbf{sF3} = \mathrm{Tp} \ \overline{\mathrm{Ts}} \ \mathbf{\phi}4 + \mathbf{-} - \mathbf{-}$

If during Ø4 of a 60 instruction C is negative, Sk will be set causing a skip to occur during Ø7. During phase Ø7 the modified number is stored in memory and the next instruction is accessed. At the completion of phase Ø7 the counter is reset to phase Ø0.

> $rF1 = Tp End \overline{Sk}$  $rF2 = Tp End \overline{Sk} + - -$  $rF3 = Tp End \overline{Sk}$

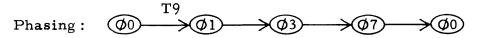

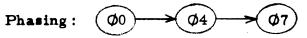

### MULTIPLICATION AND DIVISION INSTRUCTIONS

Ø0 ØI Ø3 Phasing:

Instructions 64 and 65 require four phases. Each phase has a duration of one cycle time in multiplication. In division, phase Ø3 lasts 25 cycles (Ø3  $\overline{S8}$  for 24 cycles, Ø3 S8 for one cycle). F3 is set at Ø0 Tp to form Ø1.

$sF3 = Tp Ia \phi 0 02 \overline{03} 04 + - - -$

At the following Tp the phase counter progresses to  $\phi$ 3.

$$sF2 = Ø1 Tp + - - -$$

During Ø3 the Sk flip-flop is set to force Ø7.

$sSk = Ø3 \overline{05} \overline{06} T24$  (64) + Ø3 T0 S8 (65) + - -  $sFl = Tp \overline{Ts} Sk + - - -$

Instruction 65 requires S8 to be set before Sk is set. S8 is set after 24 cycles that are counted in flip-flops S9 through S13.

Count S = Ss =  $\phi$ 3 T23  $\overline{Mh}$ sS8 =  $\overline{F1}$  F3  $\overline{Ts}$  Tp  $\overline{S9}$   $\overline{S10}$   $\overline{S11}$   $\overline{S12}$   $\overline{S13}$   $(04 \ \overline{05} \ \overline{06})$

The P register is incremented in phase Ø7 since Sk is set.

$sIa = T24 \phi 7 Sk + - - -$

+ - - -

N-CYCLE SHIFT INSTRUCTIONS

Instructions 66 and 67 terminate phase Ø0 at pulse time T9 to advance to phase Ø1 for pulse times T8 through Tp.

$sF3 = T9 Ia \phi 0 02 \overline{03} 04 05 + - - -$

During phase Ø1 (10 pulse times) the registers and shift counter are prepared for shifting. At Tp the counter advances to phase Ø3.

$sF2 = Tp \phi 1 + - - -$

The shift operation occurs during phase Ø3 and is terminated when the Sk flip-flop is set, indicating that the shift counter has reached zero or that a normalized condition exists. Upon termination, the phase counter advances to phase Ø7 from phase Ø3 (or phase Ø1 if the shift count was originally zero).

$$sFl = Tp Sk \overline{Ts} + - -$$

$sF2 = Tp Sk \overline{Ts} + - - -$

During phase Ø7 the next instruction is accessed and at Tp the counter is reset to phase Ø0.

$rFl = Tp End \overline{Sk}$  $rF2 = Tp End \overline{Sk} + - -$  $rF3 = Tp End \overline{Sk}$

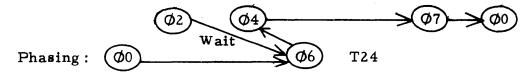

#### THREE-CYCLE PLUS N OUTPUT INSTRUCTIONS

Phasing:

$$\phi_0 \rightarrow \phi_2$$

Wait  $\phi_6 \rightarrow \phi_0$

Instructions 10, 12 and 13 are output instructions which are interlocked with a flip-flop designated Rf, which indicates when the external device is "ready" for output. Instructions 10 and 12 advance the counter to phase  $\emptyset 6$ , if Rf is set during phase  $\emptyset 0$ .

$sFl = Tp \overline{Ts} \overline{01} 03 \overline{04} \overline{Ia} \overline{Fl} \overline{F3} Rf + - -$  $sF2 = Tp \overline{Ia} \phi 0 03 + - - -$

If Rf was not set, the counter is advanced to phase Ø2 (a wait phase).

$sF2 = Tp Ia \phi 0 03 + - - -$

Instruction 13 always advances the counter to phase  $\phi$ 2 for at least one cycle time.

When Rf is set during phase  $\emptyset 2$  the counter advances to phase  $\emptyset 6$ .

$sF1 = Tp Ts \overline{01} 03 \overline{04} \overline{Ia} \overline{F1} \overline{F3} Rf + - -$

At the completion of phase  $\emptyset 6$ , during which output was executed, the counter is reset to phase  $\emptyset 0$ .

$rF1 = Tp End \overline{Sk}$   $rF2 = Tp End \overline{Sk} + - -$   $rF3 = Tp End \overline{Sk}$  $rRf = Tp End \overline{Sk}$

#### FOUR-CYCLE PLUS N INPUT INSTRUCTIONS

Instructions 30, 32 and 33 are input instructions which are interlocked with the Rf (Ready) flip-flop.

If Rf is not set during phase  $\emptyset^0$ , the counter advances to phase  $\emptyset^2$ .

$sF2 = Tp Ia \phi 0 03 + - - -$

Instruction 33 always advances the counter to phase  $\emptyset 2$ . When Rf is set during phase O2, or if Rf was set during phase  $\emptyset 0$ , the counter advances to phase  $\emptyset 6$ .

$sF1 = Tp Ts \overline{01} 03 \overline{04} Ta \overline{F1} \overline{F3} Rf + - - sF2 = Tp Ia <math>\phi 0 03 + - -$

The counter remains in phase Ø6 for one pulse time (T24) and is reset to phase Ø4 where the input is executed.

$rF2 = \phi 6 \overline{01} 02 03 T24 + - - -$

At the completion of phase  $\emptyset 4$  the counter is set to phase  $\emptyset 7$ .

$sF2 = Tp \overline{Ts} \phi 4 + -$  $sF3 = Tp \overline{Ts} \phi 4 + - -$

At the completion of phase Ø7 the counter is reset to phase Ø0 and Rf is reset.

$\mathbf{r}\mathbf{R}\mathbf{f} = \mathbf{T}\mathbf{p} \ \mathbf{E}\mathbf{n}\mathbf{d} \ \mathbf{\overline{S}k}$

THREE-CYCLE STORE INSTRUCTIONS

Instructions 35, 36 and 37 advance to phase Ø6 at the completion of phase Ø0.

$sFl = Tp Ia \phi 0 03 04 + - -$  $sF2 = Tp Ia \phi 0 03 + - -$  $rF2 = T24 \phi 6 \overline{01} 02 03 + - - -$

After one pulse time in phase Ø6 the counter is reset to phase Ø4 where the information is shifted to the C register for storage. At the completion of phase Ø4 the counter advances to phase Ø7.

$$sF2 = Tp Ts \emptyset 4 + - -$$

$sF3 = Tp Ts \emptyset 4 + - -$

During phase Ø7 the data is stored in memory and the next command is accessed. At the completion of phase Ø7 the counter is reset to phase Ø0.

> $rF1 = Tp End \overline{Sk}$   $rF2 = Tp End \overline{Sk} + - -$  $rF3 = Tp End \overline{Sk}$

# ONE-CYCLE UNCONDITIONAL BRANCH INSTRUCTIONS

(Ø0 Phasing:

The 01 (Unconditional Branch) and 23 (Execute) instructions occur within phase  $\emptyset 0$ , and there is no change in the phase counter. A similar operation occurs when there is an indirect address bit in the instruction and phase  $\emptyset 0$  is extended as a new address is read from memory.

#### PROGRAM OPERATOR INSTRUCTIONS

Phasing: ( Ø0 Ø7

All instructions affected by the program operator bit act as follows :

The program operator bit acts as the instruction code and the counter  $z \ge z$  is advanced to phase Q7.

$sF1 = Tp \overline{Ts} P0 - - + -$   $sF2 = Tp \overline{Ts} P0 - - + - -$  $sF3 = Tp \overline{Ts} P0 - - + - - -$

During phase Ø7 the program operator bit and the instruction code are combined as an entry address to a subroutine and are transferred to the P register, which contains the address of the next instruction to be accessed. At the completion of phase Ø7 the phase counter is reset to phase Ø0.

> $rFl = Tp End \overline{Sk}$   $rF2 = Tp End \overline{Sk} + - -$  $rF3 = Tp End \overline{Sk}$

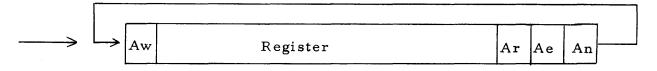

# REGISTERS

There are nine registers in the SDS 920 Computer. These registers are implemented in three different methods. The S, M and O registers use the usual RS-type flip-flops. The P and C registers use flip-flops designated as "repeaters." These flip-flops will automatically reset, if there is no set input. However, these flip-flops will not set or reset unless they receive an "enable" signal.

The A, B, X and Word Assembly registers are one-word recirculating registers using dynamic, serial, shift circuits with repeater flip-flops at the "read and write" ends. To hold information, these registers must constantly circulate in a fashion similar to delay lines.

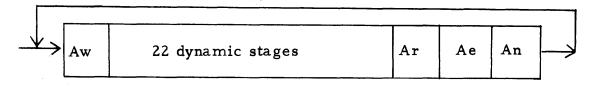

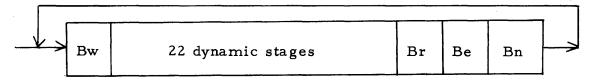

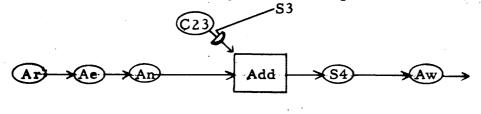

The first or "write" flip-flop (repeater) of the register is designated "w", i.e., Aw, and the last flip-flop, which may or may not be driven by an intermediate "read" flip-flop, is designated by an "n", i.e., An, which means "now". The "read" flip-flop is designated by "r", i.e., Ar.

During normal recirculation the output of the "n" (now) flip-flop is fed to the "w" (write) flip-flop which, in turn, feeds the dynamic register stages. The output of the last register stage either feeds the "n" (now) flip-flop directly or feeds an intermediate "r" (read) flip-flop which, in turn, feeds the "n" (now) flip-flop. In this case, the number of dynamic stages would be reduced by one to allow for the added delay of the "read" flip-flop. In the 920 a flip-flop Ae (early) is between Ar and An.

When writing into these recirculating registers a "not recirculate" term is enabled for the register involved, i.e., Anr (A register not recirculated).

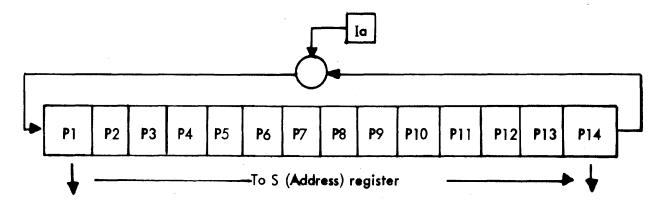

#### P REGISTER

#### Function:

The P register is the program counter. It contains the location from which the instruction was taken. It is increased by one, just preceding the time when the memory must be addressed for the next instruction. Since it must transfer its contents to the S (address) register in parallel, in order to keep the memory going at full rate, it is composed of 14 repeater flip-flops. These flip-flops are the repeater type since P is basically a shifting register. It is incremented by ring-shifting right for one complete revolution using the Ia flip-flop as a carry in a half adder.

14 repeater flip-flops

# Control Terms:

The P register is enabled by Pg. The P register recirculates during pulse times T23 through T10 and for phases Ø4, Ø5, Ø6 and Ø7, and increments by one during phases Ø4, Ø5 and Ø6, and sometimes during phase Ø7.

Pg = Q2 Ts Go F1 - - - + - - -

For certain instruction codes incrementing will occur during phase Ø7. Incrementing is performed using the Ia (Indirect Address) flip-flop as a carry in a half adder.

The sum is implemented on setting P1.

sP1 = 1a P14 F1 - - - + 1a P14 F1 - - - + - -

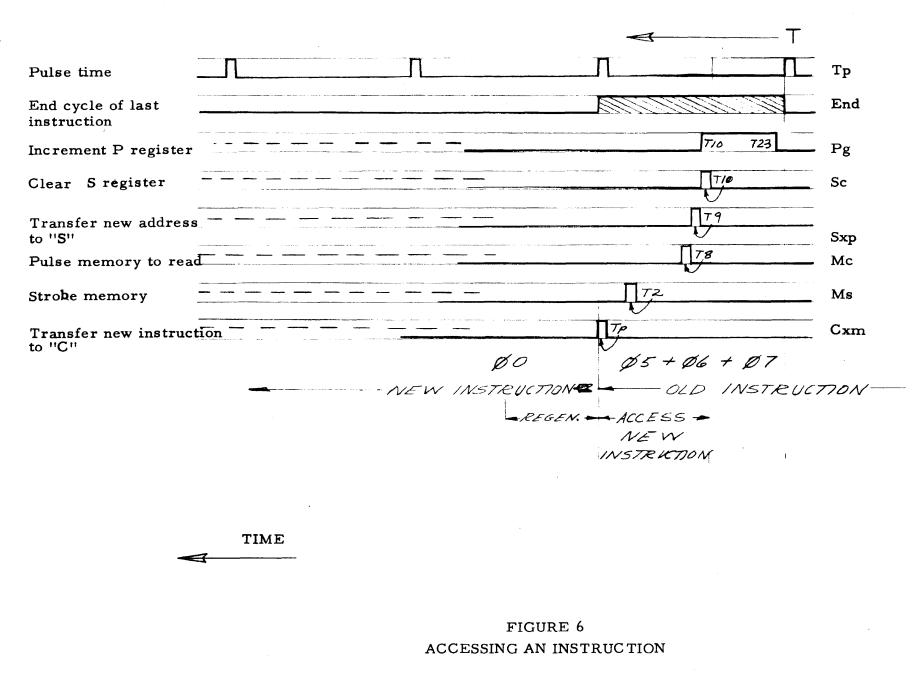

The P register is always loaded serially. The new instruction address is transferred to the S (Address) register at pulse time T9 of each End cycle.

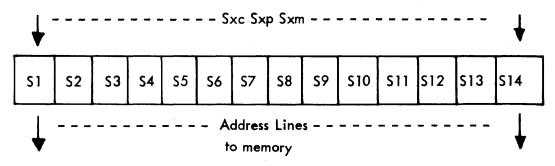

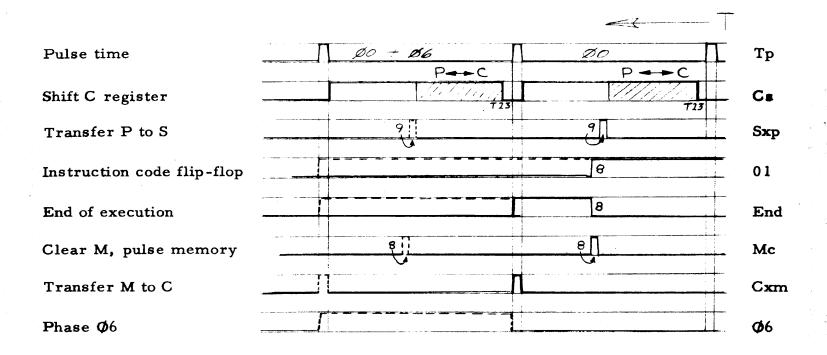

# S REGISTER

# Function:

The S register holds the address of the memory location to be accessed. It must remain in a static state when memory is actively reading or writing. The S register receives its address information in parallel from the P register, the C register (the address field of the instruction is in the C register), or from the interrupt address lines.

The S register does not shift and only receives information.

14 RS flip-flops

# Control Terms;

The S register is reset or cleared by Sc just prior to receiving the address of the next instruction (T10 End), or the address of the operand (T10  $\emptyset$ 0).

Sc = T10 (End +  $\overline{Ts}$   $\overline{F1}$   $\overline{F2}$ ) + - - -

At T9 the S register receives the address of the next instruction from the P register.

Sxp = T9 Int End +  $\phi 0$  (Branch Commands)

During phase Ø0 the S register receives the address of the operand from the C register which now contains the instruction.

$Sxc = T9 \ 00 \ \overline{P0} \ (Ia + 03 + 02)$

During the "interrupt" operation the S register receives its address from external address lines designated "N", where "Int" is the Interrupt signal.

Sxn = T9 Int  $\overline{Ts}$

The S register does not control the memory during shift instructions, multiplication and division. Instead, the individual S register flip-flops aid in the execution of those instructions. The basic equations for the S flip-flops are:

#### M REGISTER

#### Function:

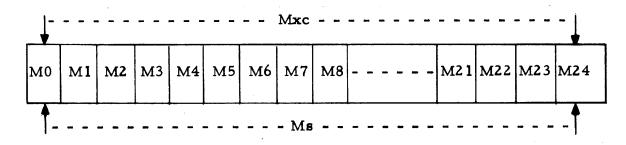

The M register is the Read-Write register for the core memory. It receives the information from memory during a read process and holds the information for storing in memory during a write process.

25 RS flip-flops

# Control Terms:

The M register is cleared or reset by Mc just prior to receiving information to be stored or just prior to receiving information from memory. Mc also acts as the pulse which signals memory to start a read-write cycle.

Prior to writing new data:

Mc = Tp P0 + Tp  $\phi$ 4 + Tp  $\overline{02}$   $\overline{03}$  05  $\phi$ 0  $\overline{Ia}$

+ - - -

Prior to reading:

$Mc = Q1 \overline{Q2} Q3 \overline{Q4} Q5 (F1 + \overline{F3} + Ts) (Tsm + \overline{Ts}) + - - -$

Note that the above pulse time is T8 and phases are  $\emptyset 0$ ,  $\emptyset 2$ ,  $\emptyset 4$ ,  $\emptyset 5$ ,  $\emptyset 6$ ,  $\emptyset 7$ , excluding phases  $\emptyset 1$  and  $\emptyset 3$ .

The contents of the C register are transferred to M for storage at T24, when writing new data into memory.

Mxc = T24 P0

In this case, P0 is time-shared and remembers that the data in C is to be stored.

The equations for the M flip-flops are:

$$sM0 = Md0 Ms + Mxc C0$$

$rM0 = Mc$

$i$

$i$

$sM24 = Md24 Ms + Mxc C24$

$rM24 = Mc$

Ms is the strobe pulse which loads the M register from memory, and Md0 - Md24 represent the data signals from memory.

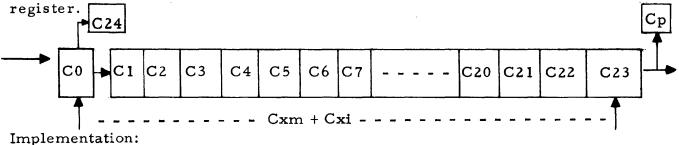

# C REGISTER

#### Function:

The C register acts as a central transfer station for all information going to and from memory. During certain arithmetic operations C acts as an arithmetic

Implementation.

24 repeater and 2 RS flip-flops.

# Control Terms:

The C register receives information in parallel from the M register. Instructions are transferred to the C register at Tp time of an End cycle.

Cxm = Tp End Go + - - -

Operands are transferred to C from M during phase Ø0 with the exception of instructions 40, 41, 43, 46, which are branch, skip, or register change instructions.

$Cxm = Tp \overline{P0} \phi_0 \left[ \overline{\phi_0 \overline{Ia} \overline{02} \overline{03} 01} \right] + - - -$

For instruction 33 the C register receives its information in parallel from external signals.

$$Cxi = Ø2 02 06$$

The C register is shifted to the right by a term designated Cs. Cs shifts to the right during phases Ø0, Ø1, Ø4 and Ø6; it also shifts to the right during exchange of registers and time-share, which are discussed in their respective sections.

$Cs = \overline{Tp} \ \overline{T24} \ F1 \ \overline{F3} + \overline{Tp} \ \overline{T24} \ \overline{F1} \ \overline{F2} + - - -$

Since repeater flip-flops are used in the C register, it is "enabled" to receive information by a term designated Cg.

$$Cg = Cs' Tp T24 + Cxm' Tp + Cxi Ql + - - -$$

Some of the <u>basic</u> equations for the C register flip-flops are:

sC0 = Cxm M0 + Cxi Cd0 + (Kc0)

+ - - - - + - - - - - -

(NOTE: Other C0 inputs are described in Instruction explanations.)

$$sCl = Cs C0 + Cxm Ml + Cxi Cdl + (Kc)$$

$$sC^{2}3 = Cs C^{2}2 + Cxm M^{2}3$$

+ Cxi Cd23 + (Kc23)

Kci) is the Ci manual set button on the control panel.

# O REGISTER

# Function:

The O register usually contains the 6-bit instruction code during the execution of the instruction. This register does not shift and only receives information.

Implementation:

6 RS flip-flops.

Control Terms:

The O register is cleared or reset by a term designated Oc at the end of each End cycle and at the end of phase Ø0 for Instruction 23.

Oc = Tp End  $\overline{Sk}$  +  $\overline{01}$   $\overline{03}$  05 Tp  $\overline{Ia}$  + - - -

The O register is always reset to a (20) by setting 02 and resetting 01,03,04,05 and 06,

The O register receives the instruction code from the C register at T24 of  $\phi 0$ .

Oxc = T24 Ø0 Go Ia C2

In this equation C2 represents the P0. (program operator) bit, in which case the instruction code would remain a (20).

The basic equations for the O register flip-flops are:

| s01 = Oxc C3              | s04 = Oxc C6 |

|---------------------------|--------------|

| r01 = Oc                  | r04 = Oc     |

| <b>s</b> 02 = Oc          | s05 = Oxc C7 |

| $r02 = Oxc \overline{C4}$ | r05 = Oc     |

| s03 = Oxc C5              | s06 = Oxc C8 |

| r03 = Oc                  | r06 = Oc     |

1.33

# A REGISTER

# Function:

The A register is the accumulator for the computer and is employed in all arithmetic, logical and shifting operations.

# Implementation:

The write flip-flop (repeater) is followed by 22 stages of dynamic relay. The "early" flip-flop (Ae) and the "now" flip-flop (An) are both RS flip-flops. The "read" circulation in the Aw and Ar flip-flops are always enabled. The A register is exactly 26 bits in length and must recirculate to maintain internally stored information as in a delay line.

# Control Terms:

The Ae flip-flop always reads Ar except when S8 is reset during right shift instructions.

| $\mathbf{s}\mathbf{A}\mathbf{e} = \mathbf{A}\mathbf{r}$ | $[(0^3 \ 0^5 \ \overline{06}) \ (Q1 + Q2 + S8 \ \overline{Q3})]$                                              | + Ar S8              |

|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|----------------------|

| $\mathbf{rAe} = \overline{\mathbf{Ar}}$                 | $\left[\left(\overline{\phi}3\ 05\ \overline{06}\right)\ \left(Q1\ +\ Q2\ +\ S8\ \overline{Q}3\right)\right]$ | $+ \overline{Ar} S8$ |

The An flip-flop reads Ae except during right shift.

sAn = Ae  $[\overline{(}\overline{\phi}3\ 05\ \overline{06})\ (Q1 + Q2 + S8\ \overline{Q3})]$ rAn = Ae  $[\overline{(}\overline{\phi}3\ 05\ \overline{06})\ (Q1 + Q2 + S8\ \overline{Q3})]$

The recirculation of the A register is inhibited by Anr (A not recirculate). The recirculation of the A register is blocked during the execution ( $\emptyset$ 6) of logical instructions and Add and Subtract instructions.

Anr =  $\overline{02}$  03 04  $\phi$ 6 + - - -

It is inhibited during the loading of A from memory (76).

Anr = 01 02 03 04 05  $\overline{06}$   $\phi 6$  + - - -

It is inhibited during the register change (46) when applicable.

Anr =  $\overline{02} \ \overline{03} \ 04 \ \overline{\text{Ts}} \ (C23 + C20 + C16) + - -$

It is also inhibited during Multiply (64), Divide (65), Right Shift (66) and Left Shift (67).

$$Anr = \phi 3 + - - -$$

The basic recirculation equation is:

$\mathbf{A}\mathbf{W} = \overline{\mathbf{A}\mathbf{n}\mathbf{r}} \mathbf{A}\mathbf{n} \overline{\mathbf{T}\mathbf{p}} + - - -$

Ar is fed from the last dynamic stage of the A register.

# B REGISTER

#### Function:

The B register acts as an extension of the least significant end of the A register for double precision operations and for shift operations. The B register holds operands for the multiply (64) and divide instructions (65).

#### Implementation:

The B register is implemented in the same manner as the A register.

# Control Terms:

The recirculation of the B register is inhibited by Bnr (B not recirculate). The contents of the B register are inhibited during the loading of B from memory (75).

Bnr = 01 02 03 04  $\overline{05}$  06  $\phi$ 6 + - - -

It is inhibited during the register change instruction (46) when applicable.

Bnr =  $\overline{02} \ \overline{03} \ 04 \ \overline{Ts} \ (C22 + C21 + C18) + - -$

It is also inhibited during shift (66, 67) and Multiply, Divide (64, 65) instructions.

$Bnr = \phi 3 + - - -$

The basic recirculation equation for the B register is shown below. Additional input terms are described under instructions.

$sBw = \overline{Bnr}Bn + - - -$

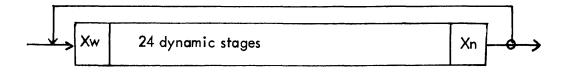

#### X REGISTER

#### Function:

The X register is the Index register. The least significant 14 bits will be added to the address of the instruction before execution if there is an index tag in position T1 of the instruction. Indexing takes place during phase  $\emptyset 0$  and is discussed in detail under Indexing.

The Xw flip-flop (repeater) is followed by 24 stages of dynamic delay and the last dynamic stage feeds the Xn (now) repeater:

# Control Signals:

The Xw and Xn repeaters are always enabled to maintain recirculation. Recirculation of the X register is inhibited by Xnr (X not recirculate) during certain instructions.

Recirculation is inhibited during the loading of X from memory (71),

$Xnr = 01 02 03 \overline{04} \overline{05} 06 \emptyset 6 + - - -$

Increment X and branch (41),

$Xnr = \emptyset 0 \ 01 \ \overline{02} \ \overline{03} \ \overline{05} \ Ia + - - -$

and during normalize (67) and copy effective address to X (77),

$Xnr = \emptyset 3\ 06\ S2 + 01\ 02\ 03\ 04\ 05\ 06\ \overline{Ia}\ \emptyset 0\ Q2$

S2 is time-shared during normalize. The basic recirculation term for the X register is:

$sXw = \overline{Xnr} Xn + - - -$

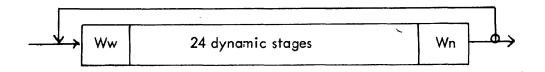

# WORD ASSEMBLY REGISTER (WAR)

# Function:

The WAR is part of the Buffer System and is described in detail in the W Buffer section. Its basic function is to hold information on input and output.

The WAR is implemented in the same manner as the X register.

# Control Terms:

Refer to the W Buffer Section.

# MEMORY CONTROL

The computer generates the basic timing signals used by the core memory.

The M (memory) register receives the information in parallel from the sense amplifiers during reading and controls the Z inhibit lines to the core memory during writing.

The memory cycle is out of phase with the computer cycle. Reading is started at T7 and the word read is strobed into the M register at T2, so that the word is ready for the computer to use before Tp. The memory write cycle is performed during the first part of the computer cycle, from T21 through T11.

The address that controls the memory is usually set up in the computer S register. This register is cleared at T10 time and loaded in parallel at T9 time from the C or P registers. At T8 the Mc signal clears the M register and starts the memory cycle. The memory is cycled every computer cycle, except when the computer is in phase Ø1 or Ø3 for shift, multiplication and division instructions, and except during the second cycle of a time-share interlace operation.

$$Mc = Q1 \overline{Q2} Q3 \overline{Q4} Q5 (F1 + \overline{F3} + Ts) (Tsm + \overline{Ts})$$

where:

$$Q1 \overline{Q2} Q3 \overline{Q4} Q5 = T8$$

This signal (Mc) clears the M register. It also sets Mg, the flip-flop that gates all timing signals to the memory.

$$sMg = Mc Ql (Me) \overline{St}$$

$rMg = Ql Q2 Q3 \overline{Q4} Mg = Tl$

The Me signal is a signal from the automatic "start-up, shut-down" relays and it is normally true.

1

The read timing signal is true from T7 through T0.

$Mrt = Mg \ \overline{Q2} \ (\overline{Q3} + Q4)$

The contents of the addressed memory cell are strobed into the M register at T2 by Ms.

$Ms = Mg (T5 - T0) Q1 \overline{Q4} Q5$  sM0 = Ms Md0 + - - isM24 = Ms Md24 + - - -

####

COMPUTER MEMORY CYCLE

1.40

If the M (memory) register is to be copied in parallel to the C register, it is done at Tp by Cxm. The contents of the M register are then regenerated (written back) into memory. If new information is to be stored in memory, then the M register is cleared at Tp by Mc.

This sets the P0 flip-flop, if it was not already set. P0 then remembers to transfer the contents of C to M at the following T24 time for storage.

sP0 = Mc Tp rP0 = T24 P0 Mxc = T24 P0

The write timing signal to the memory is true from T18 through T12.

$Mwt = Mg Q2 (Q1 Mdt + \overline{Q3} Q5)$

The two terms in the OR gate overlap in time so that there is no cross-over voltage spike.

The digit timing pulse supplied to the memory is true from T21 through T12.

$$Mdt = Mg Q2 (\overline{Q3} + Q4)$$

Two signals control the direction of the current through the cores, as the current must be reversed between the "Read" and "Write" periods.

$\mathbf{Rw} = \overline{\mathbf{Q2}} \operatorname{Mg}$  $\mathbf{Wr} = (\mathbf{Q2} \operatorname{Mg}) (\mathrm{Mdt} + \mathbf{Q1})$

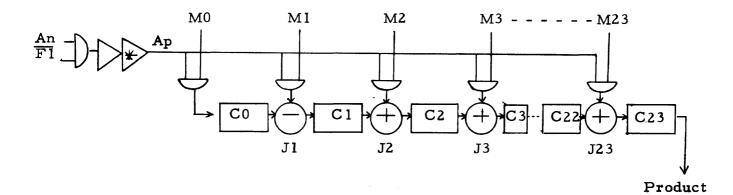

# ADDER

The adder is a full adder composed of the Xz (augend) input, the Yz (addend) input and the Cz carry flip-flop. It is completely serial and there is no "logical" delay through the adder.

The Yz input always delivers the word from memory. The adder is used in many instructions and during indexing. The basic equations are shown below. The adder is discussed in additional detail under Instructions and Indexing.

$Add = Xz Yz Cz + Xz \overline{Yz} \overline{Cz}$  $+ \overline{Xz} Yx \overline{Cz} + \overline{Xz} \overline{Yz} Cz$  $\overline{Add} = \overline{Xz} \overline{Yz} \overline{Cz} + \overline{Xz} Yz Cz$  $+ Xz \overline{Yz} Cz + Xz Yz \overline{Cz}$

# INDEX OPERATION

All instructions begin at  $\emptyset 0$  T24 with the instruction in the C register. During phase  $\emptyset 0$  the C register is shifted right, through the adder, and back to itself.

Shift C register:

$Cs = \overline{Tp} \overline{T24} \overline{F1} \overline{F2} + - - -$

As it is shifted right, through the adder, it enters through Yz.

$Yz = C23 \overline{F1} \overline{F3} + - - -$

The carry flip-flop Cz starts in a reset condition.

$\mathbf{rCz} = \mathbf{\emptyset} \mathbf{0} \ \overline{\mathbf{Ix}} \ \overline{\mathbf{Tp}} + \mathbf{-} \mathbf{-} \mathbf{-}$

If there is an index bit in C1 at Ø0 T24, the Index flip-flop will be set.

$sIx = T24 \ Q0 \ C1 + - - -$

It is reset at the end of phase  $\phi 0$ .

$rIx = Tp \overline{Mh} + - - - (\overline{Mh} \text{ is true except during the execution of the multiply instruction})}$

During the addition the Index register (X) is selected by Xz (augend input), if Ix is set.

$Xz = Xn \overline{F1} \overline{F3} Ix \overline{Ts} + - - -$

If the Index flip-flop Ix is not set, then zero will be added to the C register and the address will remain the same.

$sC0 = 00 \text{ Add } Q2 \overline{P0} (00 \overline{Ia} \overline{02} \overline{03} 01) + - - -$

Note that the addition only takes place from T23 through T10. The last term is to inhibit indexing in this manner during branch instructions 41 and 43. Branch instructions (01, 41, and 43) are indexed by running the adder directly into Pl.

$$sP1 = (\emptyset 0 \ \overline{Ia} \ \overline{02} \ \overline{03}) \text{ Add}$$

$$Pg = (Kr) Q2 \ \overline{Ts} \ Go \ \emptyset 0 \ \overline{Ia} \ \overline{02} \ \overline{03}$$

At T9 the address has shifted completely around so that it is in the upper half of the C register and, at this time, it is transferred in parallel to the S register in order to access the operand.

$$Sxc = T9 \ 00 \ \overline{P0} (--+03+02) + - - -$$

#### INDIRECT ADDRESS OPERATION

All instructions begin at Ø0 T24 with the complete instruction in the C register. At the end of pulse time T24 the 6-bit instruction code is transferred to the instruction register.

$$Oxc = T24 \ \phi 0 \ Go \ Ia \ C2$$

If the instruction contains an indirect address bit in C9 during T24 Ø0, the indirect address flip-flop, Ia, is set.

$sIa = T24 \overline{Ia} \text{ Go } \emptyset 0 \overline{C2} C9 + - - -$

C2 is the program operator bit which inhibits indirect addressing.

An indirect address bit programmed with a single-cycle instruction (except BRU and EXU) has no effect, since the Ia flip-flop is set in any event to increment the P register (Program Counter). The indirect addressing in this case is ignored.) For any other instruction the Ia flip-flop inhibits the phase count and allows an additional cycle of phase  $\phi 0$ .

Indexing may occur on the first address during phase  $\emptyset 0$  and at T9 the address (of the "indirect instruction") is transferred to the S register for accessing. At pulse time Tp the indirect instruction is transferred from M to the C register.

At T24 of this second cycle of phase Ø0 the transfer of the instruction code to the O register is inhibited by Ia.

Oxc = Ø0 T24 Ia C2 Go

Ia is reset at this second T24 unless another indirect address bit is present. In this case it is not reset and another cycle of indirect address takes place.

rIa = T24  $\emptyset 0 \overline{C9}$  Ia Go + - - -

C9 represents the new indirect address bit. When Ia is finally reset at some T24, the real operand (effective address) is obtained from memory and the instruction is executed.

Indexing will take place on any indirect address cycle where an index bit is present.

#### PROGRAM OPERATOR

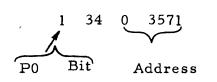

When an instruction is executed that has a "program operator" bit, the computer stores the contents of the P register in memory word zero and transfers control to the address specified by the seven-bit instruction code, including the program operator bit itself. For example, an instruction,

will cause a transfer to word 134 after storing the contents of the P register (location of above instruction) in word zero. The contents of the overflow flipflop are stored in the sign position of word zero and the overflow flip-flop is reset. An indirect address bit is also stored in word zero. The addressed subroutine can then indirect address word zero, which, in turn, can indirect address the location of the above instruction, which, in turn, will address the operand in 03571.

At time Ø0 T24 (start of the instruction) the P0 (program operator) flip-flop is set, if C2 in the C register contains a "program operator" bit.

$$sP0 = C2 (O0 \overline{Ia} T24 Go) + - - -$$

It is reset at the start of the next cycle.

$$rP0 = T24 P0 + - - -$$

The operation takes two cycle times. The phasing is shown below with one cycle time in each phase.

During Ø0 Q2 the P register is shifted into C for eventual storage in word zero.

$$sC0 = (P0 \ Q0) \ Q2 \ P14 + (P0 \ Q0) \ T9 + (P0 \ Q0) \ Of \ T0 + - -$$

The second term above inserts an indirect address bit in word zero so that the true operand of the original instruction can be easily accessed indirectly. The third term inserts the contents of the Of (overflow) flip-flop in the sign position,

$$rOf = 00 P0 T0 + - - -$$

and the overflow flip-flop is reset.

The O register is not set at  $\phi$ 0 T24 as usual, because the transfer is inhibited.

Oxc = Ø0 T24 Ia C2 Go

The O register remains reset in the 20 (NOP) configuration. As P is shifting into C, the 7-bit instruction code, which is now the transfer address in C, is shifted into the P register.

$sP1 = C8 P0 Q0 \overline{Q1} Q2 + - - -$

This is followed by 7 zeros into the P register.

$$Pg = (Kr) Q2 \overline{Ts} Go P0 \phi 0 + - - -$$

At Ø0 Tp the memory register is cleared and memory is pulsed for storage,

$$Mc = Tp P0 + - - +$$

and at T24 Ø7 the word constructed in C is transferred to the M register for storage and P0 is reset.

$$Mxc = T24 P0$$

rP0 = T24 P0 + - -

The S register is cleared at T10 Ø0, as usual, for receiving the address of the operand,

$Sc = T10 \overline{Ts} \overline{F1} \overline{F2} + - - -$

But P0 inhibits the usual C to S transfer.

$Sxc = T9 \ \phi 0 \ \overline{P0} \ (Ia + 03 + 02)$

Therefore, the address remains zero. At Tp  $\phi 0$  the phase changes to phase  $\phi 7$ .

sF1 = sF2 = sF3 = Tp Ts P0 + - - -

During phase Ø7 word zero is stored, P is transferred to S at T9 and the instruction from this new address is accessed.