#### Xerox Data Systems

5 November 1970

To Data Processing Sales:

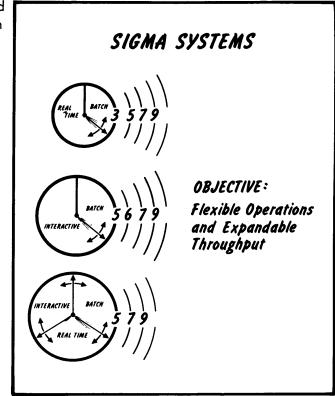

With this announcement of the Sigma 9, XDS significantly broadens its computer power within the Sigma memory-oriented architecture. Increased speed, more advanced interrupt structure, larger memory, unique data manipulation techniques – all offer our customers a giant step in the Sigma line.

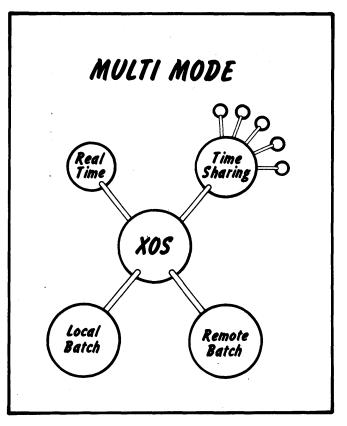

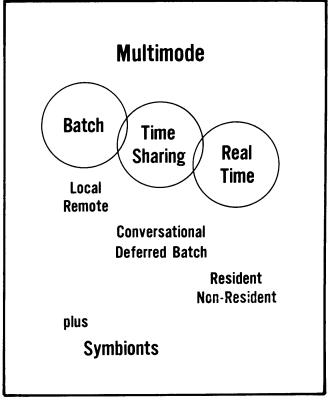

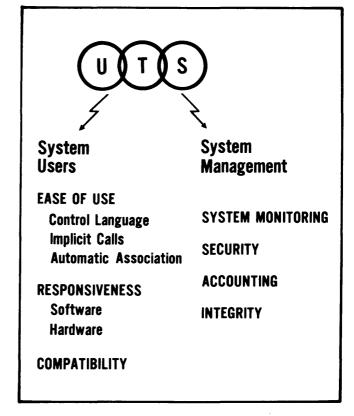

On the other side of the "Sigma 9" coin are two sophisticated operating systems – UTS and XOS. UTS, as you are aware, will be installed before the end of the year. With Sigma 9 it offers extensive multi-use facilities – interactive time-sharing services along with concurrent real-time, local and remote batch – and efficient use of core memory. An excellent system to expand our traditional marketplace.

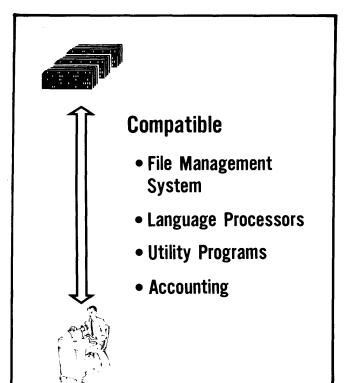

XOS, an operating system of tremendous versatility, has been under development for over four years. The Sigma 9/XOS system extends the XDS arm strongly into new more commercially-oriented marketplaces, offering these customers a highly sophisticated File Management System, a true multiprogramming system, and a versatile and powerful communications management system. XOS is also available on the Sigma 6 and the Sigma 7.

This notebook, as well as the other material included in this announcement package, has been designed to support you in every phase of your selling effort – from the Sales Presentation Material for initial customer introduction, to a comprehensive Competitive Analysis for effective selling, to names of key support contacts and benchmark procedures.

Sigma 9 truly is "The Big Difference". Let it be the big difference in meeting your quota. Good Luck!

Low firell

Rigden Currie

ps

# TABLE OF CONTENTS

| Section |      |                |            |                                                     | Page |  |  |

|---------|------|----------------|------------|-----------------------------------------------------|------|--|--|

| I       | GEN  | IERAL INI      | FORMATIC   | N ·                                                 |      |  |  |

| II      | SPEC | SPECIFICATIONS |            |                                                     |      |  |  |

|         | 2.0  | Introduc       | ction      |                                                     | 2-1  |  |  |

|         | 2,1  | Central        | Processing | Unit                                                | 2-1  |  |  |

|         |      | 2.1.1          |            | Operation                                           |      |  |  |

|         |      |                | 2.1.1.1    | Master Mode (PSD 8=0, PSD 9=X, PSD 40=0)            |      |  |  |

|         |      |                | 2.1.1.2    | Slave Mode (PSD 8=1, PSD 9=X, PSD 40=X) · · · · · · | 2-2  |  |  |

|         |      |                | 2.1.1.3    | Master Protected Mode (PSD 8=0, PSD 9=1, PSD 40=1)  | 2-3  |  |  |

|         |      | 2.1.2          | Types of A | Addressing                                          | 2-3  |  |  |

|         |      |                | 2.1.2.1    | Real Addressing                                     | 2-3  |  |  |

|         |      |                | 2.1.2.2    | Virtual Addressing                                  | 2-3  |  |  |

|         |      |                | 2.1.2.3    | Real Extended Addressing                            | 2-4  |  |  |

|         |      | 2.1.3          | CPU Fast   | Memory                                              | 2-8  |  |  |

|         |      |                | 2.1.3.1    | General Registers                                   | 2-8  |  |  |

|         |      |                | 2.1.3.2    | Memory Map                                          | 2-8  |  |  |

|         |      |                | 2.1.3.3    | Access Protection Storage                           | 2-8  |  |  |

|         |      |                | 2.1.3.4    | Write Lock Storage                                  | 2-9  |  |  |

|         |      | 2.1.4          | Interrupt  | System                                              | 2-9  |  |  |

|         |      |                | 2.1.4.1    | Organization of the Interrupt System                | 2-9  |  |  |

|         |      |                | 2.1.4.2    | Control of the Interrupt System                     | 2-9  |  |  |

|         |      |                | 2.1.4.3    | Interrupt Entry Addressing                          | 2-10 |  |  |

|         |      | 2.1.5          | Trap Syste | em                                                  | 2-10 |  |  |

|         |      |                | 2.1.5.1    | Trap Entry Procedure                                | 2-10 |  |  |

|         |      |                | 2152       | Non-Allowed Operation Trap                          | 2-11 |  |  |

| Section |     |         |              |                                                        | Page |

|---------|-----|---------|--------------|--------------------------------------------------------|------|

|         |     |         | 2.1.5.3      | Memory Parity Trap                                     | 2-12 |

|         |     |         | 2.1.5.4      | Instruction Exception Trap                             | 2-12 |

|         |     | 2.1.6   | Sigma 9      | Instructions                                           | 2-12 |

|         |     |         | 2.1.6.1      | New Instructions for Sigma 9                           | 2-13 |

|         |     |         | 2.1.6.2      | Modified Instructions                                  | 2-13 |

|         | 2.2 | Core N  | lemory       |                                                        | 2-14 |

|         |     | 2.2.1   | Basic Me     | emory                                                  | 2-15 |

|         |     | 2.2.2   | Memory       | Size Options                                           | 2-15 |

|         |     | 2.2.3   | Port Opt     | ions                                                   | 2-16 |

|         |     | 2.2.4   | Memory       | Organization                                           | 2-16 |

|         |     | 2.2.5   | Interleav    | ring                                                   | 2-16 |

|         |     | 2.2.6   | Memory       | Options                                                | 2-17 |

|         |     |         | 2.2.6.1      | Operational Mode · · · · · · · · · · · · · · · · · · · | 2-17 |

|         |     |         | 2.2.6.2      | Diagnostic Mode                                        | 2-17 |

|         | 2.3 | Input/C | Dutput Syste | em                                                     | 2-17 |

|         |     | 2.3.1   | Multiple     | xor IOP (MIOP)                                         | 2-18 |

|         |     |         | 2.3.1.1      | Channels                                               | 2-19 |

|         |     |         | 2.3.1.2      | I/O Interface                                          | 2-20 |

|         |     |         | 2.3.1.3      | Memory-to-Memory Move (MMM)                            | 2-21 |

|         |     |         | 2.3.1.4      | I/O Instructions                                       | 2-21 |

| •       |     |         | 2.3.1.5      | Maintenance Interface                                  | 2-23 |

|         |     |         | 2.3.1.6      | Alternate Processor Bus                                | 2-23 |

|         |     | 2.3.2   | High Spe     | ed RAD IOP (HSRIOP)                                    | 2-23 |

|         |     |         | 2.3.2.1      | Options                                                | 2-23 |

|         |     |         | 2.3.2.2      | Maintenance Interface                                  | 2-23 |

| Section |     |                                                                 |              |                                                                      | Page |  |  |  |

|---------|-----|-----------------------------------------------------------------|--------------|----------------------------------------------------------------------|------|--|--|--|

|         | •   |                                                                 | 2.3.2.3      | I/O Instructions · · · · · · · · · · · · · · · · · · ·               | 2-24 |  |  |  |

|         |     |                                                                 | 2.3.2.4      | I/O Operations ······                                                | 2-24 |  |  |  |

|         | 2.4 | Config                                                          | urations ••  |                                                                      | 2-24 |  |  |  |

|         | 2.5 | UTS Co                                                          | onfiguration | ,                                                                    | 2-24 |  |  |  |

|         | 2.6 | Transit                                                         | ion and Upg  | grade Configurations · · · · · · · · · · · · · · · · · · ·           | 2-24 |  |  |  |

|         |     | 2.6.1                                                           | RBM Use      | rs                                                                   | 2-26 |  |  |  |

|         |     | 2.6.2                                                           | BPM Use      | rs                                                                   | 2-26 |  |  |  |

|         |     | 2.6.3                                                           | BTM Use      | rs                                                                   | 2-26 |  |  |  |

| III     | OPE | OPERATING SYSTEMS                                               |              |                                                                      |      |  |  |  |

|         | 3.0 | Sigma 9 Operating Systems · · · · · · · · · · · · · · · · · · · |              |                                                                      |      |  |  |  |

|         | 3.1 | Universal Time-Sharing System (UTS)                             |              |                                                                      |      |  |  |  |

|         |     | 3.1.1                                                           | Introduct    | ion                                                                  | 3-1  |  |  |  |

|         |     | 3.1.2                                                           | Operatio     | n Features · · · · · · · · · · · · · · · · · · ·                     | 3-1  |  |  |  |

|         |     |                                                                 | 3.1.2.1      | UTS System                                                           | 3-1  |  |  |  |

|         |     |                                                                 | 3.1.2.2      | The Sigma Hardware                                                   | 3-4  |  |  |  |

|         |     | 3.1.3                                                           | System D     | escription                                                           | 3-4  |  |  |  |

|         |     |                                                                 | 3.1.3.1      | Local Batch Processing                                               | 3–7  |  |  |  |

|         |     |                                                                 | 3.1.3.2      | Remote Batch Processing                                              | 3-7  |  |  |  |

|         |     |                                                                 | 3.1.3.3      | Terminal Batch Entry                                                 | 3-9  |  |  |  |

|         |     |                                                                 | 3.1.3.4      | Critical Real Time Tasks                                             | 3-9  |  |  |  |

|         |     |                                                                 | 3.1.3.5      | On-Line Terminal Processing                                          | 3-10 |  |  |  |

|         |     | 3.1.4                                                           | System M     | anagement ·····                                                      | 3-11 |  |  |  |

|         |     |                                                                 | 3.1.4.1      | User State Queues · · · · · · · · · · · · · · · · · · ·              | 3-11 |  |  |  |

|         |     |                                                                 | 3.1.4.2      | Schedule and Swapping Routines · · · · · · · · · · · · · · · · · · · | 3-11 |  |  |  |

| Section |       |                  | ·                                                           | Page |

|---------|-------|------------------|-------------------------------------------------------------|------|

|         |       | 3.1.4.3          | Memory Management                                           | 3-12 |

|         |       | 3.1.4.4          | RAD Management                                              | 3-14 |

|         |       | 3.1.4.5          | Character Oriented Communications (COC) Handling            | 3-16 |

|         | 3.1.5 | System Se        | ervices                                                     |      |

|         |       | 3.1.5.1          | Log-On                                                      | 3-16 |

|         |       | 3.1.5.2          | File Management                                             | 3-17 |

|         |       | 3.1.5.3          | Reporting                                                   | 3-17 |

|         |       | 3.1.5.4          | Accounting                                                  | 3-18 |

| •       |       | 3.1.5.5          | System Integrity · · · · · · · · · · · · · · · · · · ·      | 3-19 |

|         | 3.1.6 | On-Line          | Processors ······                                           | 3-21 |

|         |       | 3.1.6.1          | TEL                                                         | 3-21 |

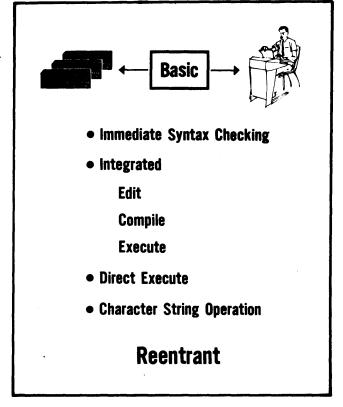

|         |       | 3.1 <b>.6.</b> 2 | UTS BASIC ·····                                             | 3-22 |

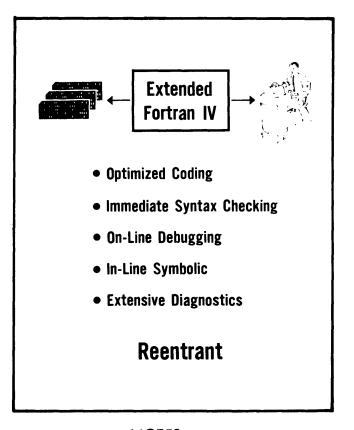

|         |       | 3.1.6.3          | Extended XDS FORTRAN IV · · · · · · · · · · · · · · · · · · | 3-23 |

|         |       | 3.1.6.4          | FDP                                                         | 3-24 |

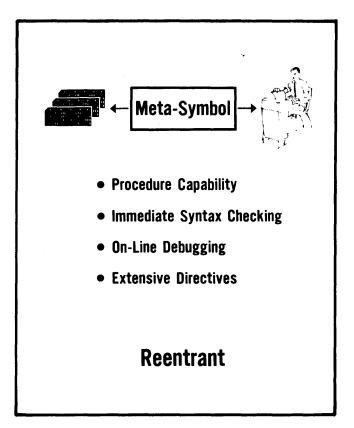

|         |       | 3.1.6.5          | META-SYMBOL · · · · · · · · · · · · · · · · · · ·           | 3-24 |

|         |       | 3.1.6.6          | EDIT                                                        | 3-25 |

|         |       | 3.1.6.7          | PCL                                                         | 3-26 |

|         |       | 3.1.6.8          | DELTA · · · · · · · · · · · · · · · · · · ·                 | 3-26 |

|         |       | 3.1.6.9          | SYMCON                                                      | 3-27 |

|         |       | 3.1.6.10         | LINK                                                        | 3-27 |

|         |       | 3.1.6.11         | SUPER                                                       | 3-27 |

|         |       | 3.1.6.12         | CONTROL                                                     | 3-27 |

|         | 3.1.7 | System Fl        | exibility ·····                                             | 3-28 |

|         |       | 3171             | Terminal Startun/Shutdown                                   | 3-28 |

| Section |     |         |             | Pag                                   | jе |

|---------|-----|---------|-------------|---------------------------------------|----|

|         |     |         | 3.1.7.2     | System Tuning 3-2                     | 28 |

|         |     |         | 3.1.7.3     | Configuration Flexibility 3-2         | 29 |

|         | 3.2 | Xerox ( | Operating S | System (XOS) 3-3                      | 30 |

|         |     | 3.2.1   | Introduct   | ion 3-3                               | 30 |

|         |     | 3.2.2   | The Job     | Stream 3-3                            | 30 |

|         |     |         | 3.2.2.1     | Local Batch Processing · · · · · 3–3  | 30 |

|         |     |         | 3.2.2.2     | Remote Batch Processing · · · · · 3-3 | 31 |

|         |     |         | 3.2.2.3     | Real Time Processing 3–3              | 31 |

|         |     |         | 3.2.2.4     | Time-Sharing 3-3                      | 1  |

|         |     |         | 3.2.2.5     | Data Base Sharing 3-3                 | 1  |

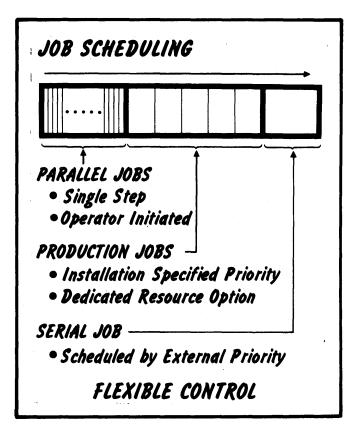

|         |     | 3.2.3   | Multi-Pro   | ogramming Features3-3                 | 12 |

|         |     |         | 3.2.3.1     | Parallel Job Class 3-3                | 2  |

|         |     |         | 3.2.3.2     | Operation Job Class 3-3               | 2  |

|         |     |         | 3.2.3.3     | Serial Job Class                      | 3  |

|         |     |         | 3.2.3.4     | Multiprogramming Rates 3-3            | 3  |

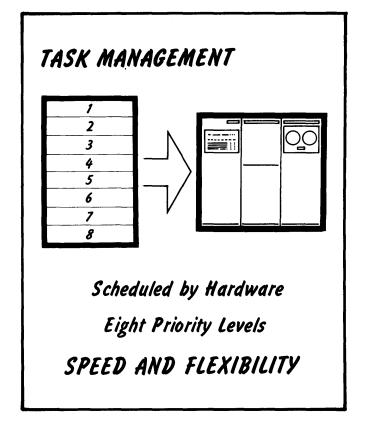

|         |     | 3.2.4   | Basic Fun   | ctions 3-3                            | 3  |

|         |     |         | 3.2.4.1     | Task Management 3–3                   | 3  |

|         |     |         | 3.2.4.2     | Memory Management 3-34                | 4  |

|         |     |         | 3.2.4.3     | Input/Output Supervisor 3-34          | 4  |

|         |     | 3.2.5   | Service F   | unctions 3-35                         | 5  |

|         |     |         | 3.2.5.1     | Operator Communications 3-35          | 5  |

|         |     |         | 3.2.5.2     | Symbionts 3-35                        | 5  |

|         |     |         | 3.2.5.3     | Command Card Analysis 3-30            | 6  |

| Section |      |                       |             |                                         | Page |  |

|---------|------|-----------------------|-------------|-----------------------------------------|------|--|

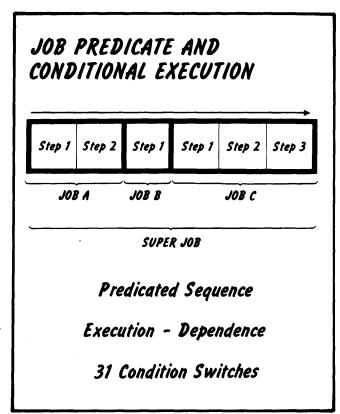

|         |      | 3.2.6                 | Superviso   | ory Functions                           | 3-36 |  |

|         |      |                       | 3.2.6.1     | Job Scheduler                           | 3-37 |  |

|         |      |                       | 3.2.6.2     | Job Management                          | 3-39 |  |

|         |      | 3.2.7                 | Monitor     | Services                                | 3-39 |  |

|         |      |                       | 3.2.7.1     | Management of Job Storage Space         | 3-39 |  |

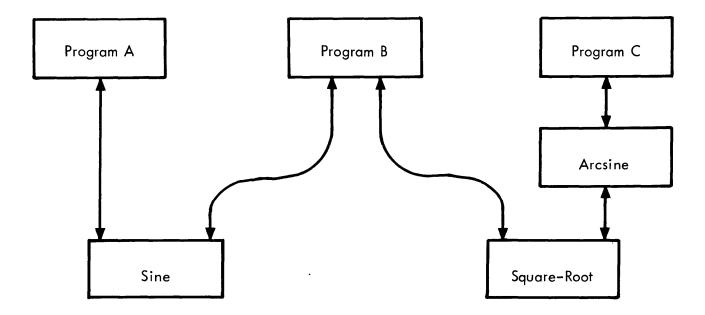

|         |      |                       | 3.2.7.2     | Program Management                      | 3-40 |  |

|         |      |                       | 3.2.7.3     | Checkpoint/Restart Services             | 3-40 |  |

|         |      |                       | 3.2.7.4     | Trap Management                         | 3-40 |  |

|         |      |                       | 3.2.7.5     | Input/Output Services                   | 3-40 |  |

|         |      |                       | 3.2.7.6     | Debug Control                           | 3-41 |  |

|         |      |                       | 3.2.7.7     | Miscellaneous Services                  | 3-41 |  |

|         |      | 3.2.8                 | File Man    | agement System (FMS)                    | 3-41 |  |

|         |      |                       | 3.2.8.1     | File Organizations                      | 3-42 |  |

|         |      |                       | 3.2.8.2     | File Access                             | 3-42 |  |

|         |      |                       | 3.2.8.3     | Other FMS Features                      | 3-43 |  |

|         |      | 3.2.9                 | System P    | rocessors                               | 3-44 |  |

|         |      |                       | 3.2.9.1     | Linkage Editor                          | 3-44 |  |

|         |      |                       | 3.2.9.2     | System Generator                        | 3-45 |  |

|         |      |                       | 3.2.9.3     | FMS Utilities                           | 3-45 |  |

|         |      | 3.2.10                | Language    | Processors ·····                        | 3-46 |  |

| IV      | APPI | APPLICATIONS PROGRAMS |             |                                         |      |  |

|         | 4.0  | Introduc              | tion ·      | • • • • • • • • • • • • • • • • • • • • | 4-1  |  |

|         | 4.1  | XDS Ap                | plications  | Programs                                | 4-1  |  |

|         | 4.2  | Users' L              | ibrary Prog | ırams                                   | 4-3  |  |

| Section |                      |          |                                                                                 | Table       |  |  |

|---------|----------------------|----------|---------------------------------------------------------------------------------|-------------|--|--|

| ٧       | PRO                  | DUCT PER | RFORMANCE/COMPETITIVE INFORMATION                                               |             |  |  |

| VI      | MARKETS/APPLICATIONS |          |                                                                                 |             |  |  |

|         | 6.0                  | Introduc | tion                                                                            | 6-1         |  |  |

|         | 6.1                  | The Edu  | cation Marketplace                                                              | 6-2         |  |  |

|         |                      | 6.1.1    | Areas of Involvement                                                            | 6-4         |  |  |

|         |                      |          | 6.1.1.1 Administration                                                          | 6-5         |  |  |

|         |                      |          | 6.1.1.2 Instruction ······                                                      | 6-6         |  |  |

|         |                      |          | 6.1.1.3 Research                                                                | 6-8         |  |  |

|         |                      | 6.1.2    | Sigma 9 — UTS and XOS · · · · · · · · · · · · · · · · · · ·                     | 6-9         |  |  |

|         |                      |          | 6.1.2.1 UTS                                                                     | 6-9         |  |  |

|         |                      |          | 6.1.2.2 XOS                                                                     | 6-11        |  |  |

|         |                      | 6.1.3    | Summary ·····                                                                   | 6-11        |  |  |

|         | 6.2                  | General  | Scientific ······                                                               | 6-12        |  |  |

|         |                      | 6.2.1    | Industry Description                                                            | 6-12        |  |  |

|         |                      | 6.2.2    | Typical Industry Areas and Applications                                         | 6-12        |  |  |

|         |                      | 6.2.3    | UTS                                                                             | 6-13        |  |  |

|         |                      | 6.2.4    | XOS                                                                             | 6-14        |  |  |

|         |                      | 6.2.5    | Application Programs · · · · · · · · · · · · · · · · · · ·                      | 6-14        |  |  |

|         | 6.3                  | Time-Sh  | Time-Sharing Services · · · · · · · · · 6                                       |             |  |  |

|         |                      | 6.3.1    | Industry Description · · · · · · · · · · · · · · · · · · ·                      | 6-15        |  |  |

|         |                      | 6.3.2    | Service Bureau Needs·····                                                       | 6-16        |  |  |

|         |                      | 6.3.3    | Sigma 9/UTS/XOS Time-Sharing Capabilities · · · · · · · · · · · · · · · · · · · | 6-17        |  |  |

|         |                      | 6.3.4    | Primary Applications of Time-Sharing · · · · · · · · · · · · · · · · · · ·      | 6-18        |  |  |

|         |                      |          | 4 2 4 1 Parking                                                                 | <b>4 10</b> |  |  |

| Section |      |          |             | Page                                                   |

|---------|------|----------|-------------|--------------------------------------------------------|

|         |      |          | 6.3.4.2     | Manufacturing – Industrial Goods · · · · · 6–19        |

|         |      |          | 6.3.4.3     | Manufacturing - Consumer Goods · · · · · · 6-19        |

|         |      |          | 6.3.4.4     | Investment 6-20                                        |

|         |      |          | 6.3.4.5     | Transportation - Public Utility 6-20                   |

|         |      |          | 6.3.4.6     | Management Consulting · · · · · · 6-21                 |

|         |      | 6.3.5    | Summary     | 6–21                                                   |

|         | 6.4  | Data Pr  | ocessing ·  | 6-22                                                   |

|         |      | 6.4.1    | Financia    | Control and Planning · · · · · · · 6–23                |

|         |      | 6.4.2    | Production  | on and Manufacturing Control · · · · · · · · 6-25      |

|         |      | 6.4.3    | Procurem    | ent                                                    |

|         |      | 6.4.4    | Non-Inde    | ustrial Uses of the Computer · · · · · · · · · 6–26    |

|         |      |          | 6.4.4.1     | Finance and Banking · · · · · · 6-26                   |

|         |      |          | 6.4.4.2     | Retail                                                 |

|         |      | 6.4.5    | Sigma 9     | Operating Systems · · · · · · · · · · · · · · · · 6-27 |

|         |      |          | 6.4.5.1     | UTS 6-27                                               |

|         | •    |          | 6.4.5.2     | XOS 6-28                                               |

|         |      | 6.4.6    | XDS Com     | nmercial Software · · · · · · · 6–29                   |

|         |      |          | 6.4.6.1     | File Management System (FMS) · · · · · · 6-29          |

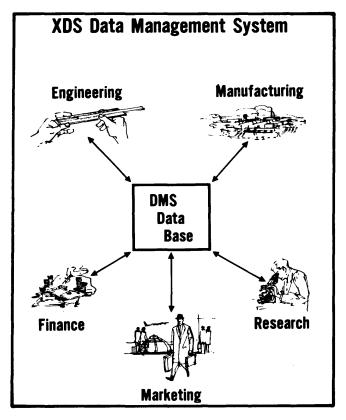

|         |      |          | 6.4.6.2     | Data Management System (DMS) · · · · · · 6-30          |

|         |      | 6.4.7    | Trends in   | Commercial Business Data Processing · · · · · · 6-30   |

|         |      | 6.4.8    |             | ial Account Penetration · · · · · · · · · 6–30         |

|         |      | 6.4.9    | Summary     | 6–33                                                   |

| VII     | SALE | S PRFSFI | NOITATION I | MATERIAL                                               |

| V 11    |      | _        |             |                                                        |

| Section |              |                                                        | Page |

|---------|--------------|--------------------------------------------------------|------|

|         | 7.1          | Sigma 9 Material · · · · · · · · · · · · · · · · · · · | 7-1  |

|         | 7 <b>.</b> 2 | Existing Applicable Material                           | 7-2  |

| VIII    | PRO          | POSAL MATERIAL                                         |      |

| IX      | SUPF         | PORT                                                   |      |

|         | 9.0          | Introduction                                           | 9-1  |

|         | 9.1          | Demonstrations                                         | 9-1  |

|         | 9.2          | Benchmarks · · · · · · · · · · · · · · · · · · ·       | 9-1  |

|         | 9.3          | Responsible Sigma 9 Personnel                          | 9-2  |

#### SECTION I

#### GENERAL INFORMATION

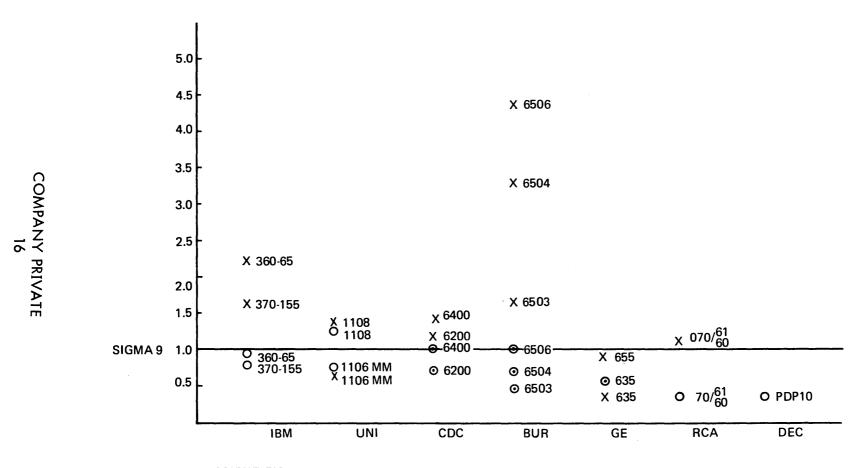

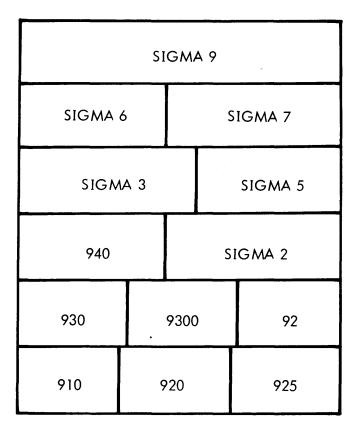

Xerox Data Systems introduces the Sigma 9, the latest and most powerful member of the Sigma family. This announcement is one of the most significant ever made by XDS. The power of the Sigma 9 opens entirely new areas of applications and, together with the successes in our traditional markets, puts XDS in the challenging position for the 70's.

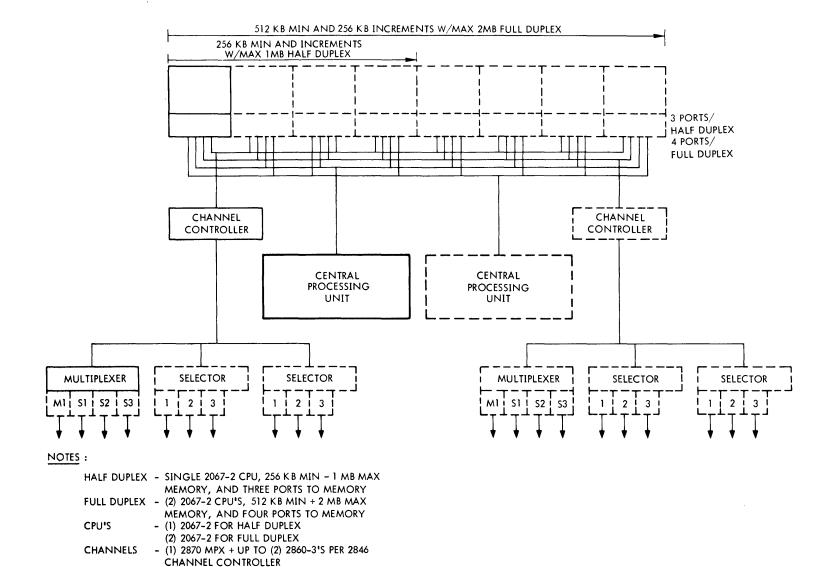

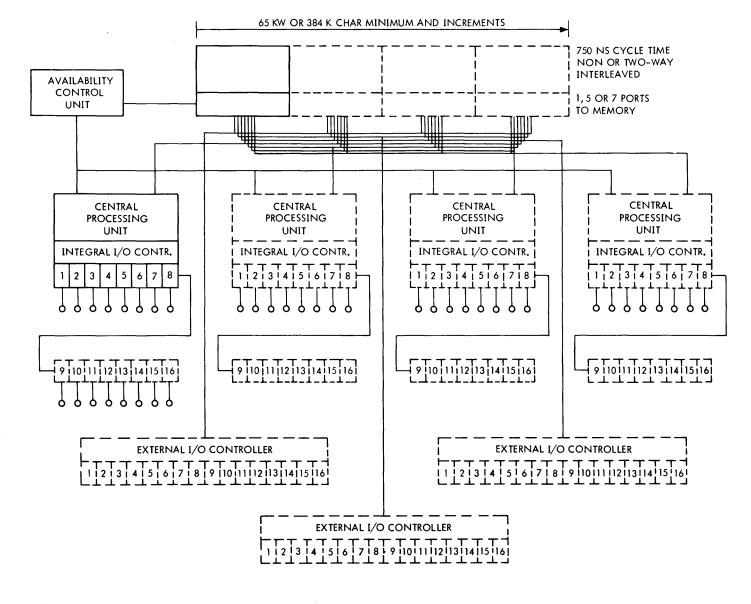

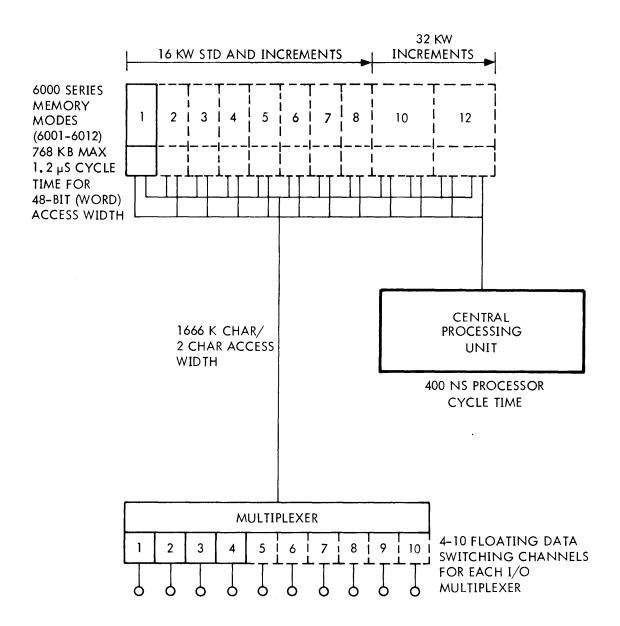

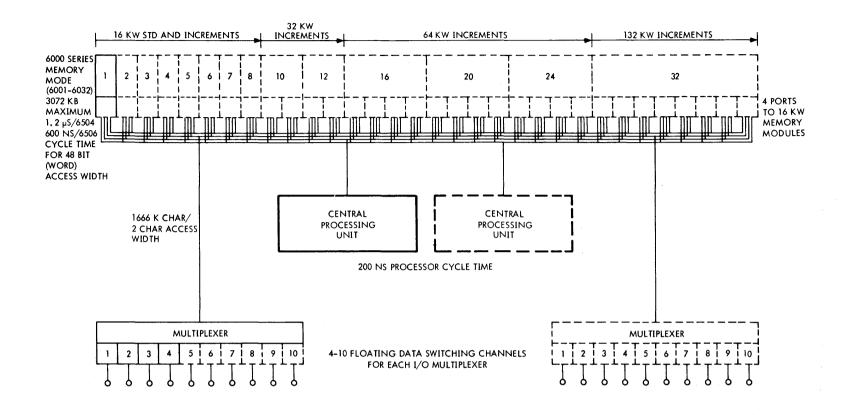

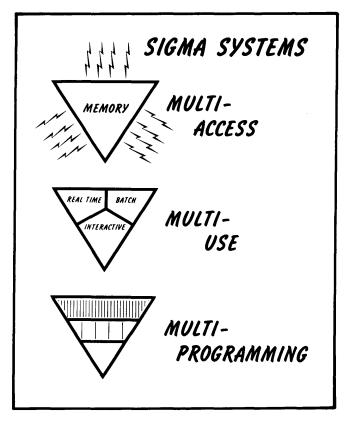

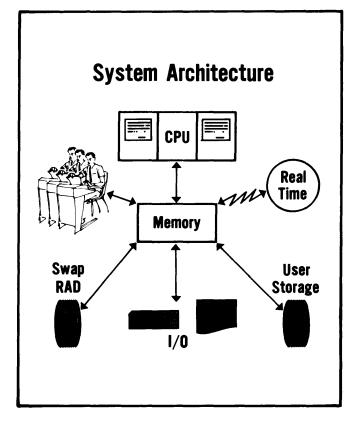

Sigma 9 is an extension of the Sigma line; its architecture retains the conceptual framework of the Sigma family. The Sigma 9 is memory oriented — with larger memories than previously available with Sigma. The Sigma 9 memory is multi-ported — with more ports than previously available. The Sigma 9 is the system designed to meet the requirements of an expanding multi-programmed, multi-application market, permitting more users per system with excellent response time and throughput.

The Sigma 9 is designed to be fully compatible with the other members of the Sigma family. User programs now running on a Sigma 5, Sigma 6, or Sigma 7 will run without alteration on a Sigma 9 of equivalent or larger configuration.

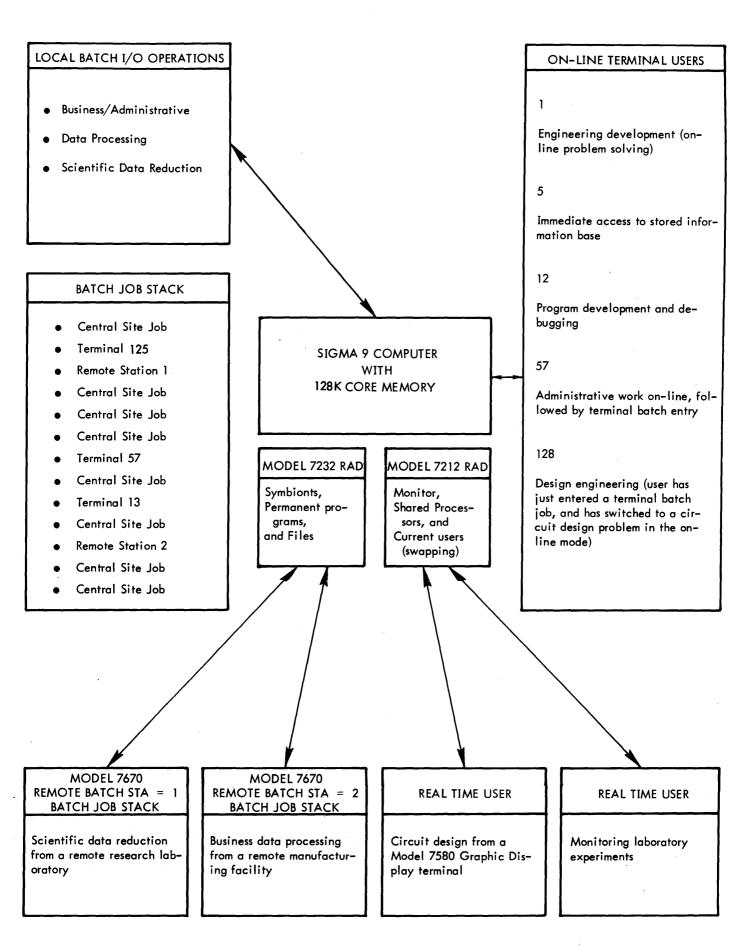

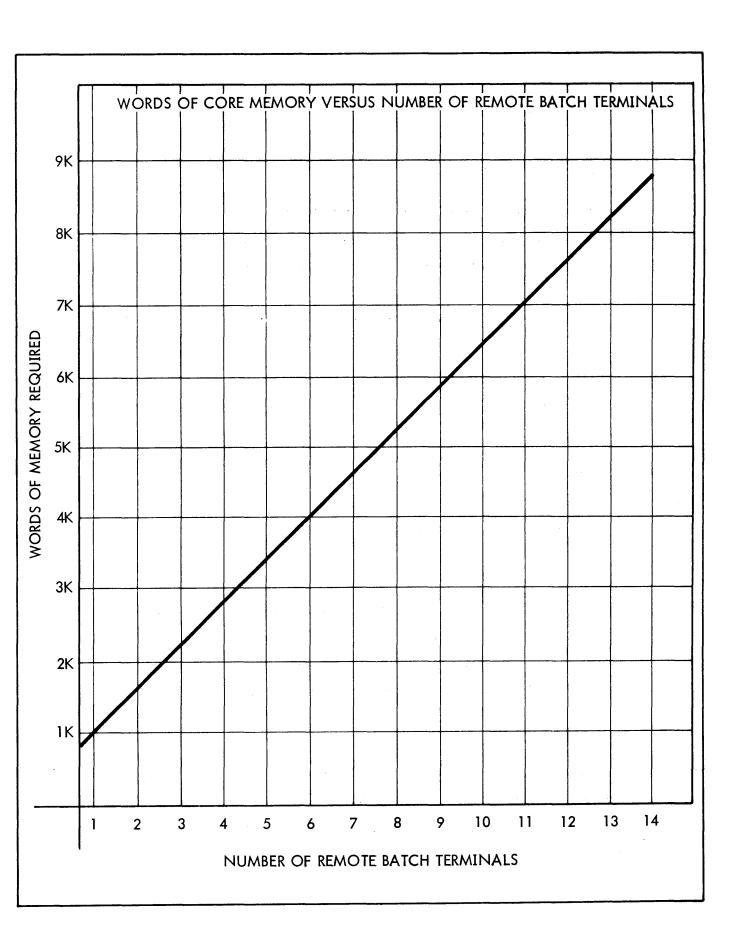

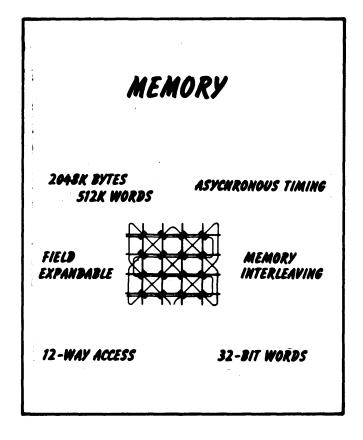

The Sigma 9 offers the user the greatest growth potential of any system in its class. Memory capacity can grow to 2 million bytes (512K words). The UTS operating system has the capacity to service 128 on-line users, even in a real time environment, and maximize throughput for concurrent batch operations. The XOS operating system incorporates all the ability of UTS with the significant addition of multi-programming. XOS permits an unlimited number of jobs to be core resident with each being serviced on a priority basis since XOS allocates available resources — I/O, memory, CPU time — automatically with minimum overhead.

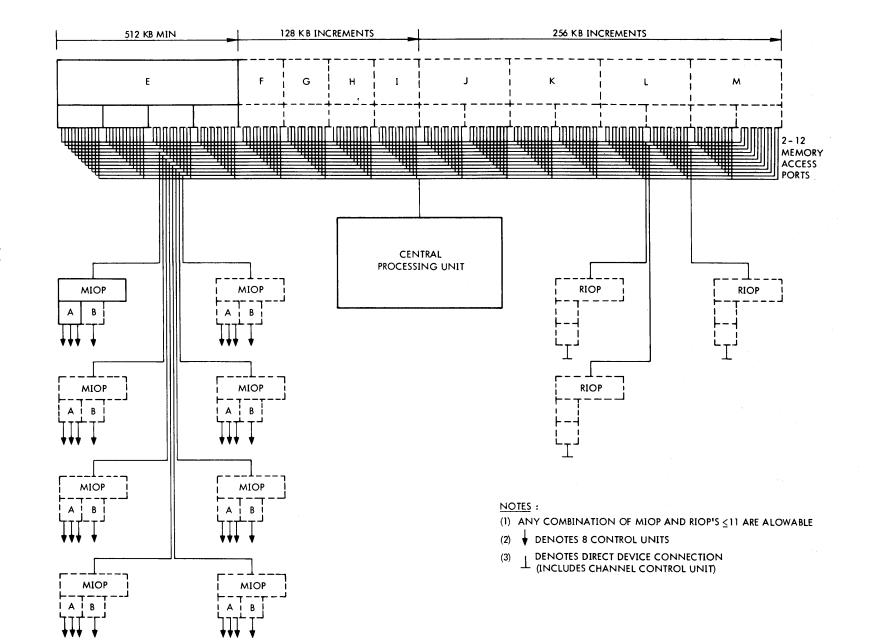

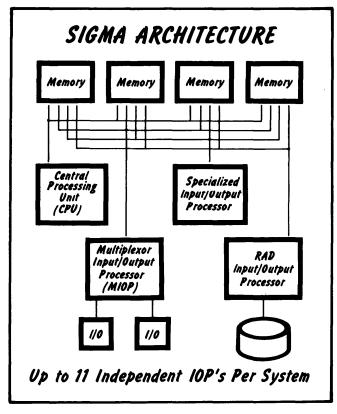

The new memory with Sigma 9 has greater port capacity; Sigma 9 memory can accommodate up to 12 ports. There may be as many as 11 input/output processors on a system.

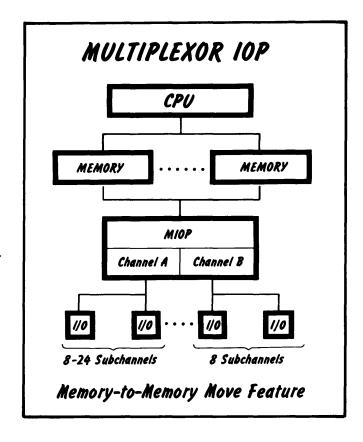

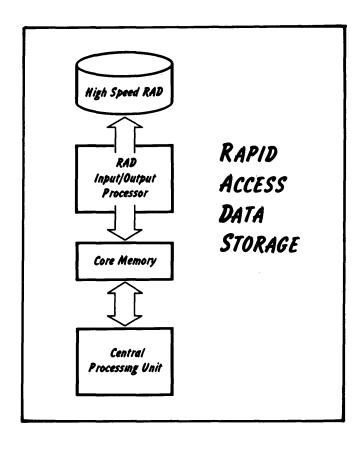

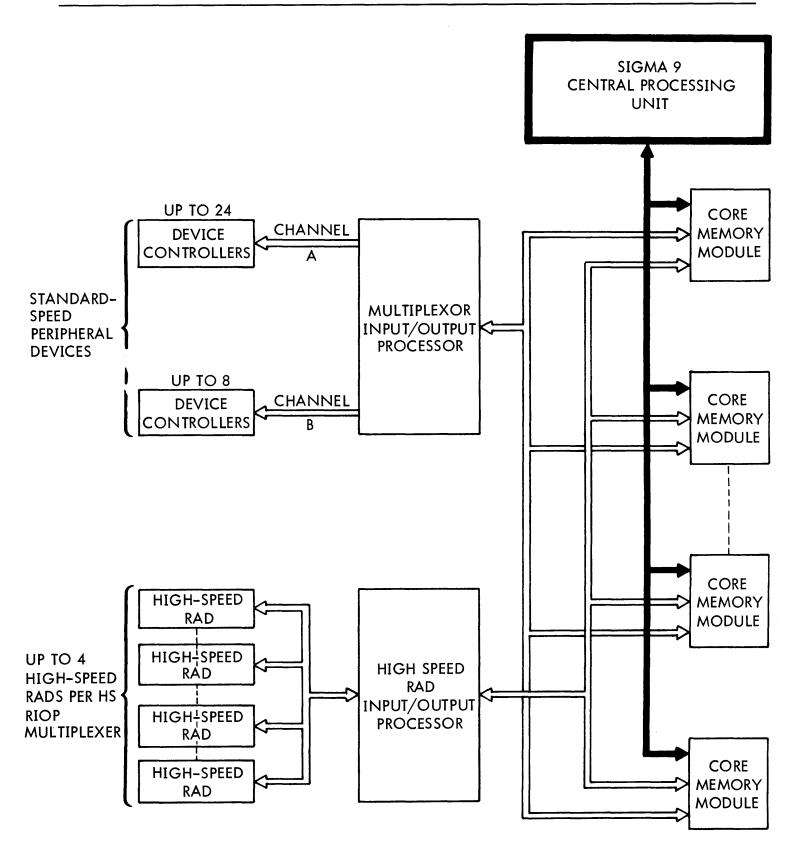

To complement the new CPU and memory of the Sigma 9, a new series of IOP's is being introduced. The new MIOP is designed with a 2-channel capacity. Channel A can interface with as many as 24 device controllers each serviced in a multiplexed mode. Channel B extends the multiplexing operation to an additional eight device controllers. The data rates attainable on the new MIOP are higher than ever before offered by XDS (470,000 bytes/channel). A second IOP being introduced with the Sigma 9 is the HIGH SPEED RAD IOP (HSRIOP). The new HSRIOP incorporates the functions of a selector IOP and a high speed controller in one unit. Up to four high speed RAD's can be connected to this unit, each operating in the burst mode.

Very significant innovations have also been made in the area of system availability, maintainability, and reliability. These improvements assist Field Engineers in keeping the system up and locating system faults. Among these improvements, which are mostly internal hardware, is the capability to perform on-line diagnostics without disturbing system operation.

UTS, available with Sigma 9, offers more time-sharing capability than any other operating system now available. Further, XOS expands the high throughput capability of Sigma 9 by introducing multiprogramming.

In summary, XDS is introducing a significantly new system. The Sigma 9 is a logical upward extension of the current Sigma family. Programs running on current systems are compatible with the Sigma 9, yet Sigma 9 offers wide capability for expansion. Importantly, the concept of system availability has influenced the Sigma 9 design. The customer's basic problem centers around availability and XDS has the solution. Lastly, XDS offers two extremely sophisticated operating systems to match the power of the hardware.

# SECTION II SPECIFICATIONS

# 2.0 INTRODUCTION

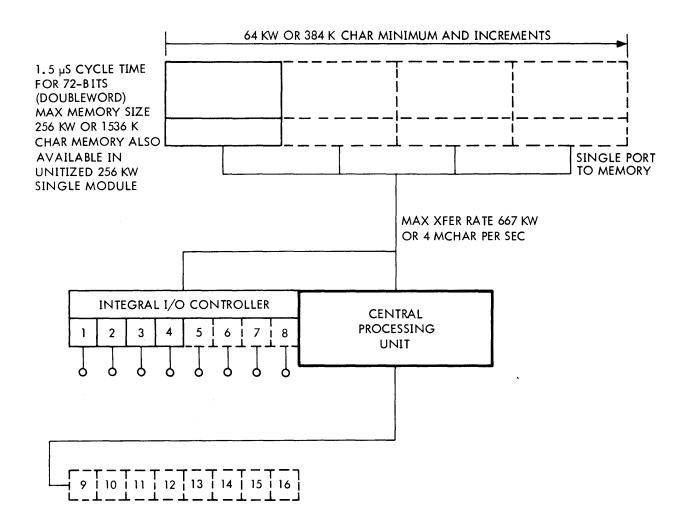

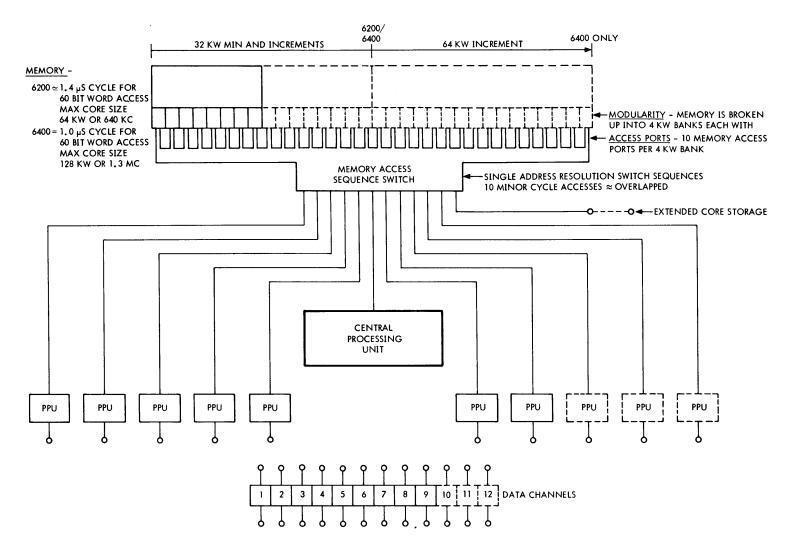

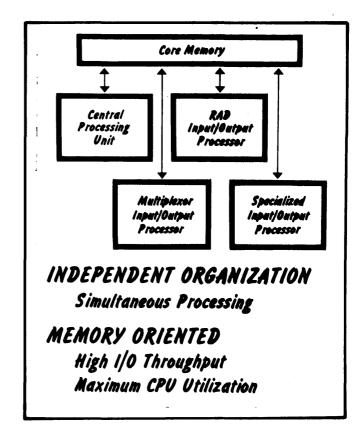

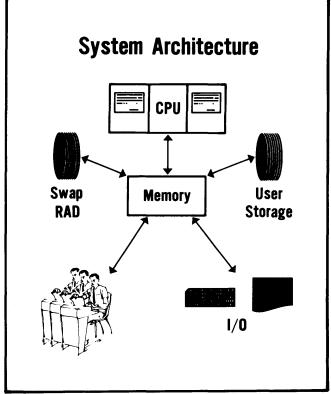

The Xerox Sigma 9 computer system is a versatile, multi-purpose, digital computer. The system is primarily organized around a high speed central processing unit, fast magnetic core memories, and flexible input/output processors controlling I/O device controllers and I/O devices. Each of the major system elements performs asynchronously with respect to other elements in the system. Modular design facilitates system expansion to readily accommodate a vast range of computing and data processing requirements.

In the section that follows, a description of the features of the Sigma 9 Central Processing Unit (CPU), Memory and Input/Output Processors (IOP's) is offered. Also included is a discussion of the major differences between Sigma 9 and the Sigma 7, and a brief statement concerning the expected marketplace of the Sigma 9 computer.

## 2.1 CENTRAL PROCESSING UNIT

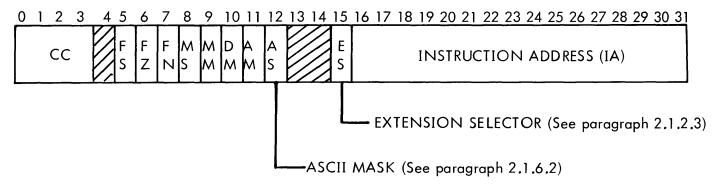

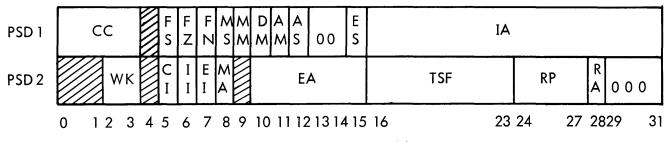

Sigma 9 is a logical extension of the successful Sigma family of computers. As an extension of the Sigma family, Sigma 9 merges the unique architecture of Sigma 5/6/7 with the increased speed and memory addressing capability of its CPU. The Sigma 9 PSD is shown in the figure on the following page.

## 2.1.1 MODES OF OPERATION

The Sigma 9 can operate in three different modes. Two of these are identical to the modes available on Sigma 7; they are the Master and Slave modes. Sigma 9 has a third mode called the Master Protected mode. The modes of operation are determined by the condition of three bits in the Program Status Doubleword.

#### <u> PSW 1</u>

#### PSW2

Sigma 9 Program Status Doubleword

# 2.1.1.1 Master Mode (PSD 8=0, PSD 9=x, PSD 40=0)

In this mode of operation, the CPU can perform all of its control functions and can modify any part of the system. The only restriction placed upon the CPU's operation in this mode is that imposed by the write locks on certain protected parts of memory.

Master mode operation is indicated whenever bit 8 of the current PSD is zero. In addition, bit 40 (the mode altered FLAG) must also be zero for Sigma 7 compatibility in the Master mode.

# 2.1.1.2 Slave Mode (PSD 8=1, PSD 9=x, PSD 40=x)

This mode is identical to the Slave mode on Sigma 7. No privileged instruction may be executed and, if mapping is invoked, the access protection codes always apply to the Slave mode program.

The Slave mode of operation is indicated when the Master/Slave bit (PSD8) is equal to one.

### 2.1.1.3 Master Protected Mode (PSD 8=0, PSD 9=1, PSD 40=1)

The Master Protected mode is a new mode of operation for Sigma mainframes. A modification of the Master mode, it is designed to provide a certain amount of additional protection for programs which operate in the Master mode.

The Master Protected mode of operation can only occur when operating in the Master mode with virtual addressing. In this mode, if the program makes a reference to a virtual page to which access is prohibited by the current setting of the access protection codes, a trap will occur to the Memory Protection Violation Trap as it does in all Slave mapped programs.

The Master Protected mode of operation is in effect when the Master/Slave bit (PSD 8) is zero and when both the memory map bit (PSD 9) and Mode Altered bit (PSD 40) are set to one. The Mode Altered flag is new on Sigma 9.

#### 2.1.2 TYPES OF ADDRESSING

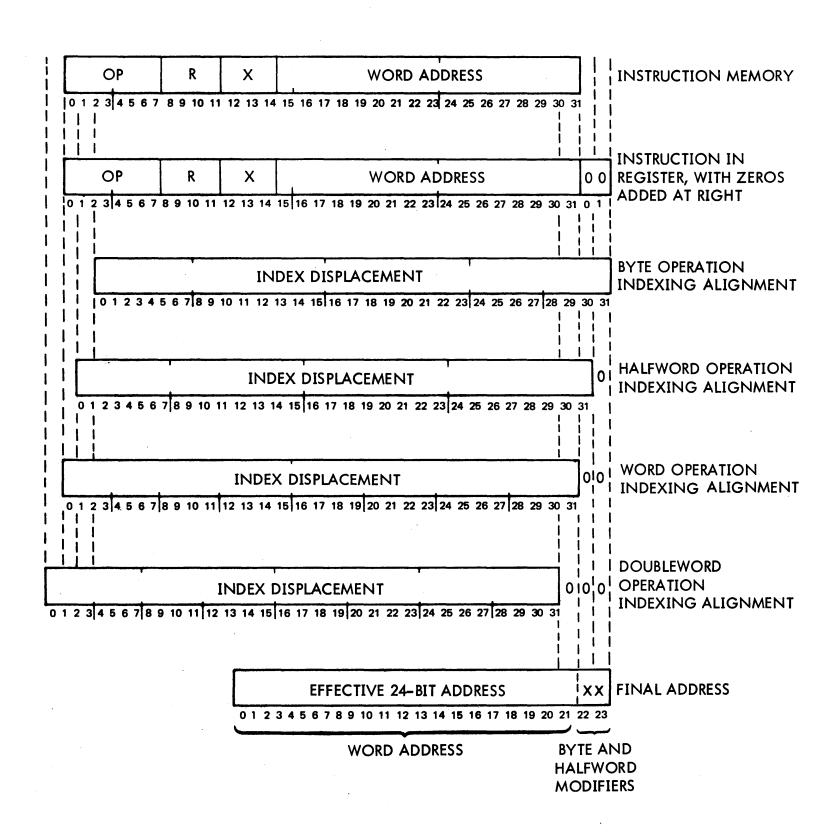

There are three major types of addressing available on Sigma 9. Two of the major types are identical to the corresponding types of addressing on Sigma 7. The third is an extension required due to the fact that Sigma 9 is capable of having a very large memory.

### 2.1.2.1 Real Addressing

Real Addressing occurs whenever the memory map is not used and the extended type of addressing is not invoked. This is identical to the unmapped type of operation on Sigma 5/6/7. All addresses are 17-bit real word addresses. This type of addressing allows only the first 128K words of memory to be referenced in an instruction.

#### 2.1.2.2 Virtual Addressing

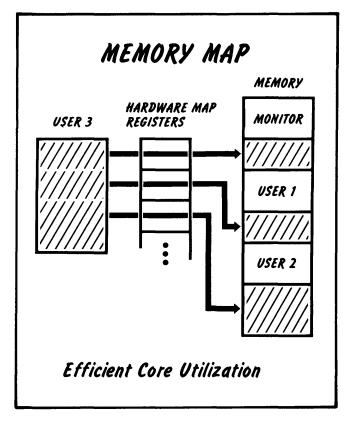

Virtual Addressing is invoked whenever the memory map indicator is set to one. This type of addressing may be in effect during either the Master or Slave modes of operation. In operation, it is almost identical to the mapped mode of operation on Sigma 6 and Sigma 7. The mapping registers on Sigma 6 and 7 contained eight bits each. On Sigma 9, the mapping register has been extended to 13 bits each. The mapping feature works as follows: The high order eight bits of the original 17-bit reference address in an instruction are used as a pointer to one of the 256 mapping registers. The

13-bit contents of the mapping register replaces the eight high order bits in the original reference address. The 13 bits from the mapping register, combined with the remaining nine bits in the original reference address, give a 22-bit real memory address. This 22-bit address provides addressing of up to four million words of memory.

The compatibility with Sigma 7 operation takes place in the manner in which the map is loaded. When it is loaded by a Sigma 7 program, using only those instructions known to a Sigma 7 program, the lower eight bits of each 13-bit map register are loaded with significant information and the upper five bits will be set to zero. A Sigma 9 program that wishes to take advantage of the large memory may load the map with up to 13 significant bits instead of the eight bits used by Sigma 7.

The virtual memory for any given user at any time can be up to 256 pages (512 words per page). The 512K word memory available on the initial Sigma 9 could contain up to four of these maximum sized users.

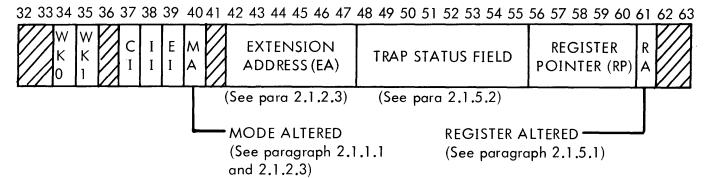

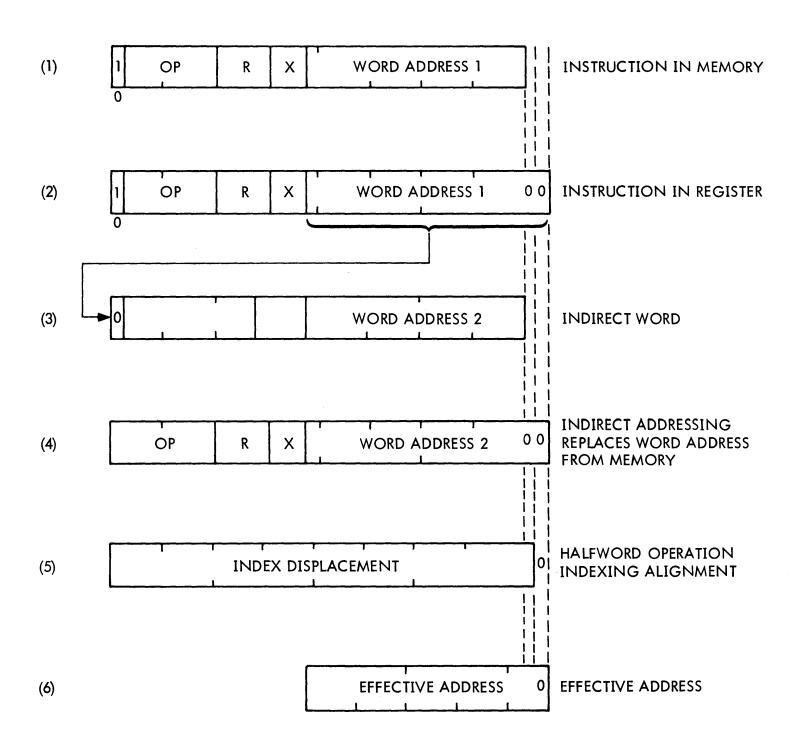

## 2.1.2.3 Real Extended Addressing

Real Extended Addressing is invoked whenever the memory map indicator is zero and the Mode Altered flag is equal to one. Real Extended Addressing is provided on Sigma 9 in order to ease the burden of operating with a large memory for certain types of programs. Specifically, it is intended for the operating system when that system is manipulating users directly and is, in fact, working with real memory and not with the virtual memory of any given user. It also provides a method for writing programs, be they real time or other special purpose programs, which may operate any place within the memory continuum and not be dependent upon the memory map for their execution.

Real Extended Addressing is discussed in three parts:

- Instruction Addresses and Reference Addresses in Instruction

- Other Addresses and Displacements

- Branching and Branch Addresses

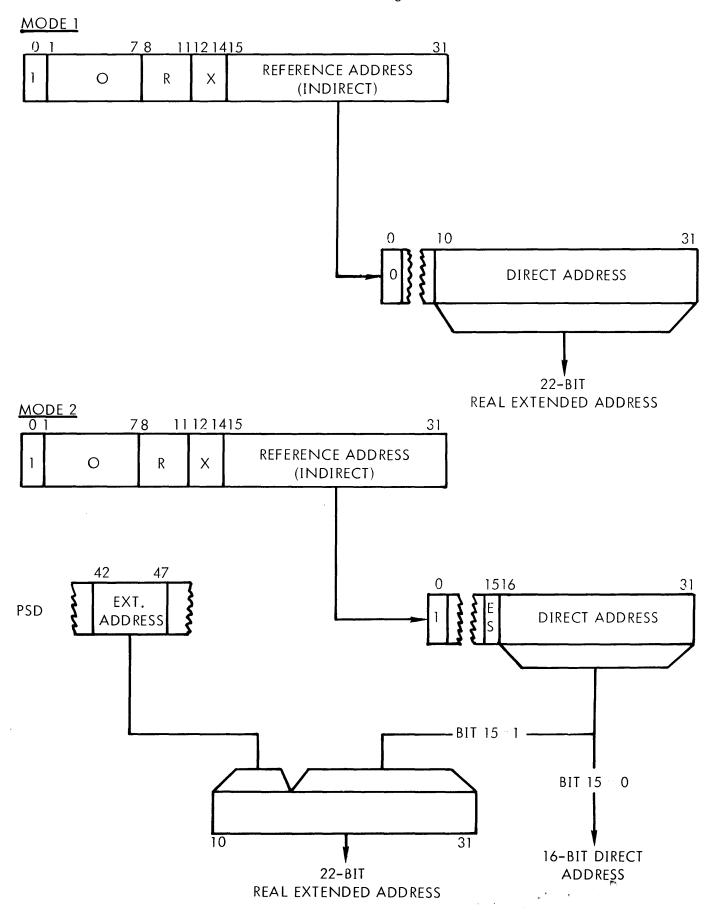

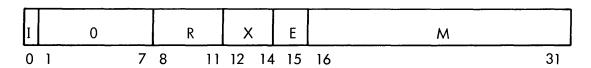

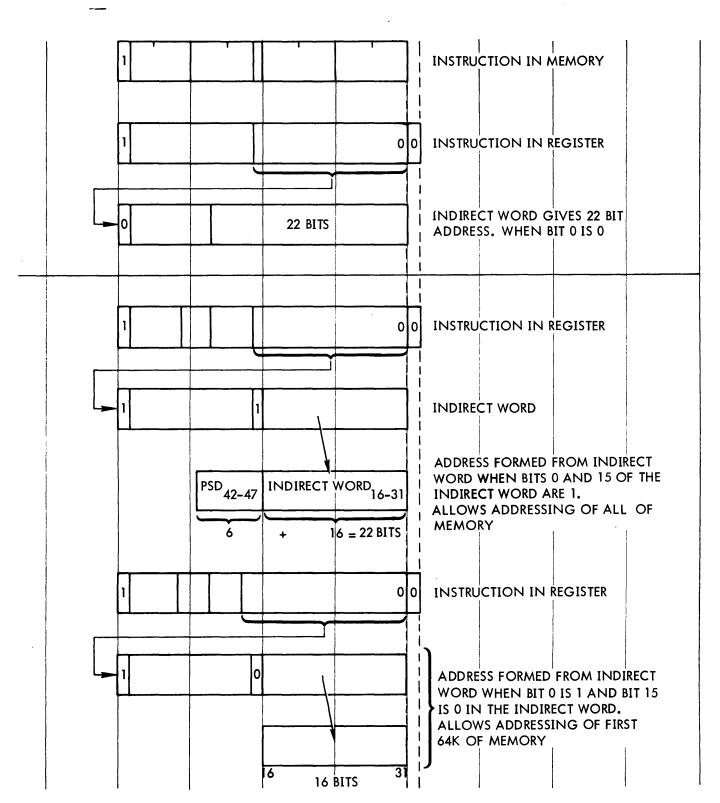

Instruction Addresses and Reference Addresses in Instruction — The Instruction Address field of the PSD and the Reference Address field of each instruction is only 17 bits in length. This is enough to address only 128K words of memory. To extend the addressing capability, the 17-bit address fields in the PSD and instructions are divided into a 1-bit flag field and a 16-bit displacement field (reference the figure on the following page).

Real Extended Addressing

The flag field (bit 15) is called the Extension Selector. Several new fields have been added to the PSD. Two of these are the Extension Selector (PSD 15) and the Extension Address (PSD 42-47). If the Extension Selector is a zero, then the 16-bit displacement address points to a word within the first 64K of memory.

If the Extension Selector is a one, then the 16-bit displacement addresses a word in the 64K region that is identified by the contents of the Extension Address. In other words, when bit position 15 is equal to 1, a full memory address is formed by concatenating PSD 42-47 with bits 16-31 of the address field. This gives a 22-bit word address to allow the instructions to address all of memory.

Other Addresses and Displacements — Outside of reference address fields and the instruction address field of the PSD, all address and displacement fields are extended into adjacent previously undefined fields in order to address all of memory directly. The areas affected are as follows:

- Indirect address location contains either a full word address of 22 bits, or a 16-bit address which is linked to the extension address bits of the PSD (see figure on the following page)

- Index registers contain a full displacement of from 21 to 24 bits for doubleword, word, halfword, and byte references

- The stack pointer for PUSH-PULL instructions contains a full 22-bit word address

- The registers which describe the source and destination byte address for byte string instructions are 24-bit byte addresses

Branching and Branch Addresses — The Extension Address field of the PSD is modified automatically by branch instructions. If the effective address of a branch instruction (however generated) is outside of the first 64K of real memory, then the higher order six bits of this full effective address will automatically be loaded into the Extension Address field of the PSD if the branch is taken. The remaining part of the effective branch address will be loaded into position 16–31 of the PSD. In addition, bit 15 of the PSD (the Extension Selector) will be set to 1. If the effective address of the branch is within the first 64K, then the Extension Address is not modified, the Extension Selector is set to zero, and the effective address is placed in bits 16–31 of the PSD. This means that once the Extension Address has been set it will remain set until it is either changed

by loading a new PSD, or by the actual branching into another 64K region of memory.

A branch and link instruction in Real Extended Addressing will store the full address of the next instruction in the link register. If the Extension Selector in the PSD is zero at the time of the branch and link, then the address stored in the link register will be the incremented 16-bit displacement from position 16-31 of the PSD. If the extension selector in the PSD is equal to one, then the address stored will be the incremented 16-bit displacement (PSD 16-31) plus the contents of the Extension Address (PSD 42-47) into bit positions 10-31 of the link register.

#### 2.1.3 CPU FAST MEMORY

Sigma 9 contains a fast memory within the CPU. This section describes its general usage.

### 2.1.3.1 General Registers

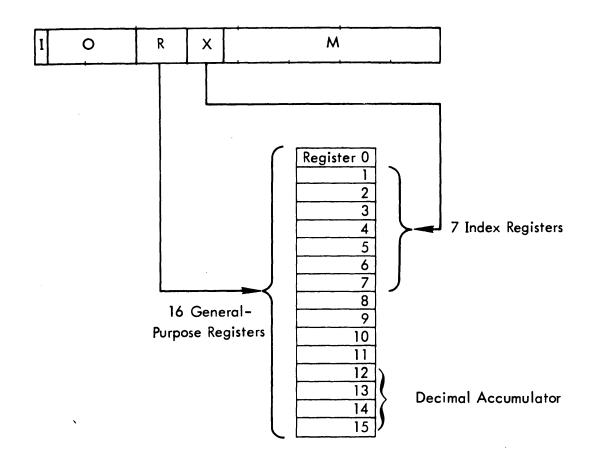

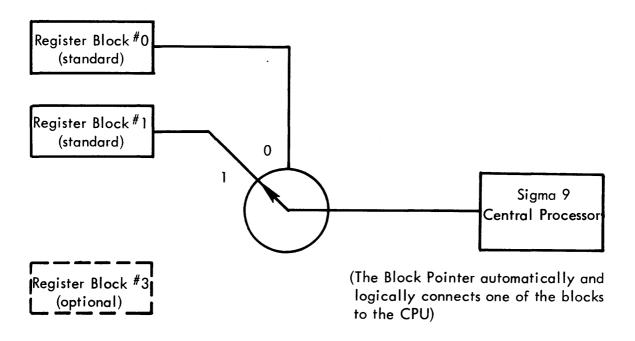

The general register format for Sigma 9 is identical to Sigma 7. There are 16 registers in a block, seven of which may be used as index registers. The last four registers are the decimal accumulator used in decimal operations. The major difference between Sigma 7 and Sigma 9 registers is that Sigma 9 may have only four blocks of registers installed in the CPU. Two blocks are standard and two are optional.

#### 2.1.3.2 Memory Map

The memory map on a Sigma 9 is held in fast memory within the CPU. The map storage is an array of 256 elements where each element is 13 bits in length. Only one map may be installed in a CPU.

#### 2.1.3.3 Access Protection Storage

The access protection is a feature of the memory map. On Sigma 9, it is identical to the access protection of Sigma 7. The access protection requires 256 two-bit elements of fast memory. The access protection is loaded independently of the map storage in the CPU fast memory.

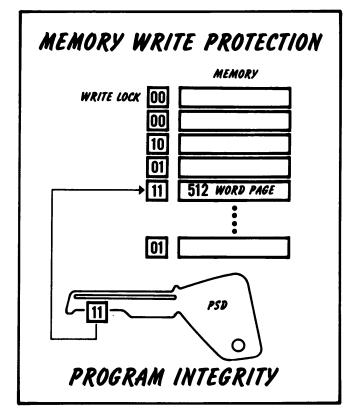

### 2.1.3.4 Write Lock Storage

The write lock storage consists of 256 two-bit elements in the CPU's fast memory. This is identical to the write lock storage on Sigma 7. It provides write protection for the first 256 pages or 128K words of real memory. There is no plan to provide write lock protection for real memory beyond 128K words.

#### 2.1.4 INTERRUPT SYSTEM

This section describes the interrupt system of Sigma 9. The interrupt system is similar, but not identical, to that of Sigma 7. This section concentrates primarily on describing the difference from Sigma 7.

# 2.1.4.1 Organization of the Interrupt System

There are two changes in the interrupt organization of Sigma 9 which cause it to be different from Sigma 7. First, the memory parity interrupt of Sigma 7 (location x '56') has been replaced by a system fault interrupt. The system fault interrupt is used to notify the CPU in the system that some system element has detected an error in itself. The second change is the addition of a memory fault interrupt to location x '57'. The memory fault interrupt reports memory faults to the CPU. Uncorrectable read and write errors, data for checks, address bus checks, and port selection errors are the types of error conditions which cause the memory fault interrupt. At the time of interrupt, the snapshot feature in memory records the conditions existing in the failed memory for later examination by diagnostic programs.

#### 2.1.4.2 Control of the Interrupt System

All control functions of Sigma 7 are retained for Sigma 9. In addition, one new Write Direct and three new Read Direct functions are added to Sigma 9. These new functions are designed to allow the programmer to interrogate the condition of the interrupt system at any time and to restore that system at a later time.

The new Write Direct function allows the programmer to set active all selected levels currently in the armed or waiting state. This new function allows interrupts to be returned to the active state. This was the only state to which direct control was not possible on Sigma 7.

Sigma 7 did not have any capability for reading the condition of an interrupt level. All the Read Direct functions for interrupt control are therefore new on Sigma 9. The three new functions allow the programmer to determine which interrupts are in the armed or waiting states, which are in the waiting or active states, and which interrupts are enabled.

# 2.1.4.3 Interrupt Entry Addressing

Because Sigma 9 can have a memory much larger than Sigma 7, the addresses of instructions used in interrupt locations have been extended from 17 to 20 bits. This has been done to ease the problem of where to place exchange tables and clock counters. For the XPSD instruction, this poses no problem since the high order three bits that make up the 20 bits were reserved on Sigma 7. This extension will, however, make indexing on modify and test instructions no longer possible, but it will allow any interrupt instruction to address one million words directly.

If the interrupt instruction makes an indirect reference, the indirect word may contain a 22-bit, four million word main memory address. This type of addressing is called objective addressing because it is not subject to any volatile state of the CPU.

#### 2.1.5 TRAP SYSTEM

The trap system of Sigma 9 is similar to that on Sigma 7. There is one interrupt on Sigma 7 which is now a trap on Sigma 9. There are also some modifications of the Sigma 7 traps as they are used on Sigma 9. These modifications are described in the following subsections.

# 2.1.5.1 <u>Trap Entry Procedure</u>

Trap routines are entered by the execution of a <u>Trap Instruction</u>. An XPSD is the <u>only</u> Sigma 9 instruction intended for use as a trap instruction and has two options which are not operative at any other time.

One of these options involves the manner in which the exchange table of the XPSD is addressed. The table may be addressed either objectively or subjectively. If the addressing is subjective, the addressing is the same as the current type of addressing used by the program that was trapped. If objective addressing is used, the XPSD may address memory independently of the current type of addressing being used. The addressing is independent of any aids outside of the instruction itself or the memory. Bit 10 of the XPSD determines what type of addressing will be used. The state of bit 10 has no affect on the operation of an XPSD except when that XPSD is used in a trap location.

In the event of a trap entry, bit 61 of the PSD will be set if any general register or core memory location has been altered as a result of the execution or partial execution of the instruction which caused the trap.

# 2.1.5.2 Non-Allowed Operation Trap

The non-allowed operation trap has been changed from the manner in which it operated on Sigma 7. When operating in the Master Protected mode, a memory protection violation may occur if the access protection for a given page is violated.

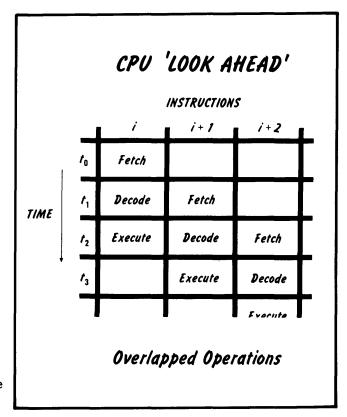

Because the CPU is attempting to work on instructions and operands ahead of current execution, certain anomalies may occur. When most branch instructions branch, therefore, the CPU will (in many cases) try to access the instruction addressed by the branch as soon as possible. If the address generated results in a violation of protection or reference to nonexistent memory, the trap will not occur unless the branch conditions are actually met. In other words, if the instruction that follows a branch is a valid instruction generating no violation, then no trap occurs because the hardware attempted to anticipate the program's needs.

All instructions which reference a series of locations in the course of their execution that might cross a page boundary will test for trap conditions before commencing execution. If an access protection, memory protection, or nonexistent memory reference should occur during the course of the execution, the trap will now occur before execution begins.

When a non-allowed operation trap occurs as the result of a mapped operation that violates the memory protection feature, the virtual page address that caused the trap to occur will be stored in bits 48-55 of the doubleword pointed to by the effective address of the XPSD instruction. This solves the problem of determining where the violation occurred.

### 2.1.5.3 Memory Parity Trap

This is a new trap for Sigma 9. It represents a change from the memory parity interrupt on Sigma 7 to a trap on Sigma 9. The memory parity trap to location X'4C' will occur whenever a memory unit detects an error it cannot correct, as a result of a request from the CPU. Errors caused by requests from other processors will not cause this trap.

# 2.1.5.4 Instruction Exception Trap

The instruction exception trap is also a new feature on Sigma 9. Any new trap condition detected and allowed to cause a trap during the trap sequence (including execution of the XPSD instruction, or during the interrupt sequence, including execution of the XPSD, MTW, MTH, or MTB instruction), is defined as an instruction exception trap and causes a trap to location X'4D'. Many other errors will also cause the instruction exception trap; some of these are:

- An illegal instruction found in a trap or interrupt location

- Using an odd-numbered register with some of the doubleword and byte addressing instruction

- The register block pointer set to a non-existent register block

This trap clearly provides a solution to the problem arising from misuse of instructions.

#### 2.1.6 SIGMA 9 INSTRUCTIONS

The Sigma 9 instructions are an extension of the Sigma 7 instruction set. This section describes the new instructions for Sigma 9 and also changes to Sigma 7 instructions.

# 2.1.6.1 New Instructions for Sigma 9

There are three new instructions for the Sigma 9; they are: Load Real Address (LRA); Load Memory Status (LMS); and Load and Set (LAS).

Load Real Address loads into a general register the real effective address of the operand pointed to by the instruction. The address loaded can be of a byte, halfword, word, or doubleword as determined by the setting of the condition codes at the beginning of execution. This means that the programmer can use LRA to obtain the real memory address of an operand under real, virtual, or real extended addressing.

The <u>Load Memory Status</u> instruction is used to interrogate the status of a memory bank. It can also be used to perform a diagnostic action on a memory bank. The effective address of the instruction is used to determine which memory bank is to be referenced. The setting of the condition codes just prior to execution determines what diagnostic action is to be performed. The LMS instruction could be used, for example, to retrive under program control the contents of the memory snapshot registers. This feature may be used by the operating system for error logging or by a diagnostic program to assist in fault locating.

The <u>Load and Set</u> instruction will not have an immediate use on the Sigma 9. Load and Set is used in a multiprocessor system to prevent a given CPU from accessing a memory location already being used by another CPU. Load and Set will, however, have a definite use for Sigma 9 enhancements.

#### 2.1.6.2 Modified Instructions

The extended capabilities of Sigma 9 have required the modification of some of the Sigma 7 instructions. Most of the changes are concerned with the extended addressing capability of the Sigma 9. There are, however, totally new options available on some instructions.

Byte string instructions run five to six times faster on Sigma 9 when bytes are transferred on byte boundaries. Sigma 9 also has a speed advantage when bytes are transferred on word boundaries.

A new shift type instruction has been added. A number of applications require that a single bit marker be located within a word or doubleword filled with these markers. The new shift instruction allows the programmer to perform a searching shift on either a word or doubleword to determine the presence or absence of a particular bit or flag. The shift may be either left or right and will provide a count of the bits shifted while searching.

The floating point arithmetic on Sigma 9 is the same for Sigma 7 except for the following difference — the floating point is standard on Sigma 9 and is not an option. All floating point instructions will yield identical results with Sigma 7.

Sigma 9 decimal operation differs from Sigma 7 in that Sigma 9 decimal instructions are much faster than Sigma 7 (2 to 3 times faster). Also, Sigma 9 decimal instructions are capable of generating either EBCDIC or ASCII preferred sign and zone codes. This option allows the programmer to choose the mode of operation most convenient for him.

The Read Direct and Write Direct instructions have had several important optional forms added to their formats. The Read Direct instruction is now capable of reading the snapshot register within the CPU. The information held in the snapshot register can be used for diagnostic purposes to discover the nature of a fault in the CPU. The Read Direct instruction is now also capable of reading the state of the interrupt inhibits and sensing the various status of the individual interrupt levels within the CPU interrupt system. The ability to sense and record the status of individual interrupts becomes extremely useful when combined with a new feature of the Write Direct instruction. This new feature of the Write Direct gives the programmer the ability to set the state of the interrupts (all states including active). As an example, the programmer (using the Read Direct) may now sense and record the status of the interrupts and, at a later time (using the Write Direct) re-establish that same status in the interrupt system. The Write Direct instruction has also been modified to allow it to set the interrupt inhibits and to arm the snapshot feature. In arming the snapshot feature, the Write Direct supplies a clock counter and a condition select. The condition select describes what information is to be taken in the snapshot and the clock counter tells when it should be taken.

With one exception, the functions of the I/O instruction on Sigma 9 are identical with those on Sigma 7. The exception is a modification of the Halt I/O instruction that serves to generate a reset function for an entire IOP. This modification is called Reset I/O (RIO). RIO causes the selected IOP to generate an I/O reset signal to all devices attached to it. The use of several RIO instructions in sequence will cause the entire I/O system to be reset one IOP at a time. (Refer to Paragraph 2.3.1.4 for details of I/O instructions.)

## 2.2 CORE MEMORY

The core memory developed for Sigma 9 combines and extends the successful designs of the Sigma line memories. It offers significant improvements in the port structure to accommodate up to 12 processor interfaces for each concurrently operating memory unit, and with additional error detection hardware improves system viability. Sigma 9 core memory is large, flexible, fast, and easy to maintain.

#### 2.2.1 BASIC MEMORY

A Sigma 9 basic memory (minimum allowable memory in a Sigma 9 system) is 128K (K = 1024words) with two ports. This configuration is physically contained in four memory cabinets with 32K words in each cabinet. This minimum configuration allows two processors (CPU and IOP) to interleave between two 16K banks in modulo 2 fashion, or between four 16K banks in modulo 4 fashion. Both processors can access separate 16K banks simultaneously.

#### 2.2.2 MEMORY SIZE OPTIONS

Core memory is expandable from 128K to 256K in 32K increments, and from 256K to 512K in 64K increments.

The maximum allowable core memory for Sigma 9 is 512K words, which physically occupy 16 memory cabinets with 32K in each cabinet. CPU's and IOP's in the Sigma 9 system have memory addressing capability of 4096K words; however, any requirements for memory sizes greater than 512K words must be handled on an RPQ basis.

#### 2.2.3 PORT OPTIONS

Additional ports may be added to each memory unit as more processors are added to the Sigma 9 system. The two basic memory ports are numbered 1 and 2 with port 1 high and port 2 low in priority. The first port expansion to the basic memory configuration would be port 3, which would have a lower priority than ports 1 and 2. Subsequent port expansion may be made one at a time, up to a maximum of 12 ports. The lowest numbered port has the highest priority; the highest numbered port has the lowest priority. This hard-wired priority scheme may be selectively overridden by any processor connected to a port. If, for example, a processor on port 4 has a critical requirement to access a memory unit at the same time that the three other higher priority ports are trying to access the same memory unit, the processor on port 4 may send a "high priority request" signal to the memory unit that will allow him to override the hard-wired priority scheme and gain access before the other three ports.

Any requirement for port expansion beyond 9 ports must be handled on an RPQ basis.

#### 2.2.4 MEMORY ORGANIZATION

A Sigma 9 memory system consists of a number (4 – 16) of independent memory units with each memory unit having two 16K banks. Each bank may be accessed independently of, and concurrently with any other bank in the memory system.

Each 32K memory unit may have from 2 to 12 ports connected to it and either bank within a memory unit may be accessed by any port (it is possible for one or two ports to be accessing both banks simultaneously).

#### 2.2.5 INTERLEAVING

Interleaving is permissible between two 16K banks within a 32K memory unit (modulo 2) and between four 16K banks in two separate 32K memory units (modulo 4). Thus, interleave group sizes may be 32K or 64K. Each bank in an interleave group must be the same size and each

interleave group must begin on an address boundary equal to a multiple of the interleave group size.

#### 2.2.6 MEMORY OPERATIONS

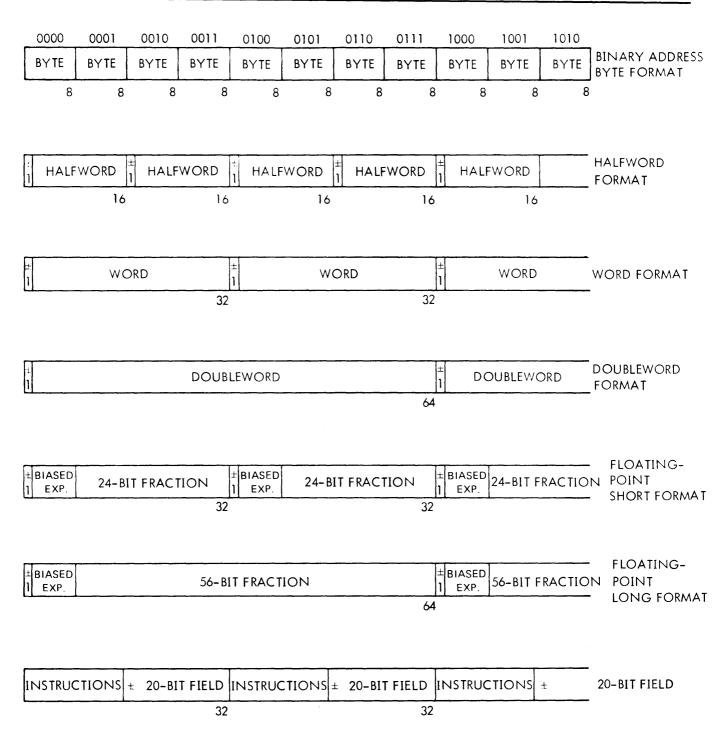

Sigma 9 core memory is capable of storing and transferring bytes, halfwords, and words in either an operational or diagnostic mode.

# 2.2.6.1 Operational Mode

The operational mode performs the normal read, full write, and partial write operations associated with storing and fetching data and instructions. Nominal access time for read and full write modes is 900 nanoseconds, and nominal access time for partial write mode is 1060 nanoseconds.

# 2.2.6.2 Diagnostic Mode

The diagnostic mode performs a variety of operations associated with diagnostic and multi-processor (CPU) configurations. The diagnostic mode is set by a CPU. Generally, the diagnostic mode allows a CPU to interrogate a memory bank to determine its environmental status. In this mode, the memory can transmit back to the CPU either normal data from core or status information from a 3-word snapshot register. The snapshot register contains status information such as:

- Memory fault type

- Port number

- Interleave mode

- Bank size

- Memory unit number

- Memory unit size

# 2.3 INPUT/OUTPUT SYSTEM

The input/output system for Sigma 9 represents major improvements over earlier Sigma I/O systems in throughput and flexibility. Two different types of input/output processors (IOP's) are available for use in a Sigma 9 system:

- Multiplexor IOP (MIOP) which controls up to 32 device controllers

- HIGH SPEED RAD IOP (HSRIOP) which controls up to four Model 7212 high speed RAD storage units

The minimum Sigma 9 system configuration includes one MIOP. As many as 10 additional MIOP's and HSRIOP's may be added to a monoprocessing system in any mix. In multiprocessing systems, the number of allowable IOP's in the system is reduced by the number of CPU's (maximum of four) added to the system. Since each processor (CPU or IOP) must have its own port to memory, a maximum of 12 processors can be configured in a Sigma 9 system.

In all systems, Homespace Bias is transmitted to the IOP from the controlling CPU during I/O instruction execution. The Homespace Bias is added to the address values of X'20' and X'21' for CPU/IOP communication via core memory during the execution of I/O instructions.

## 2.3.1 MULTIPLEXOR IOP (MIOP)

The MIOP controls up to 32 device controllers in a dual-channel mode of operation similar to the earlier configuration of an MIOP with a bus-sharing IOP (BSMIOP). The MIOP has both 1-byte (standard) and 4-byte (optional) interfaces. With the 4-byte option, the MIOP can operate in a "burst" mode which causes the MIOP and a device controller to exchange complete records of data during a single service connection. This is similar to the operation of the earlier Selector IOP (SIOP), thus maximizing the throughput of a single device during times when data overruns on other devices are not probable. Transfer rates of an MIOP are typically 470 kb/sec on a 1-byte interface and 940 kb/sec on the optional 4-byte interface.

A unique memory-to-memory move option (MMM) allows the MIOP to move a maximum of 16K words from one area in core memory to another. Unlike similar operations using CPU instructions such as move byte string (MBS), MMM is performed as an I/O operation which means the CPU does not have to be tied up performing block movements of core memory data.

## 2.3.1.1 Channels

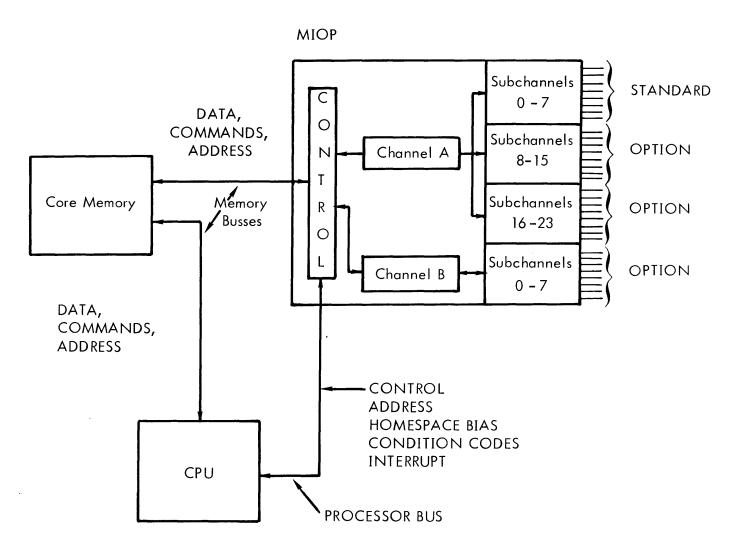

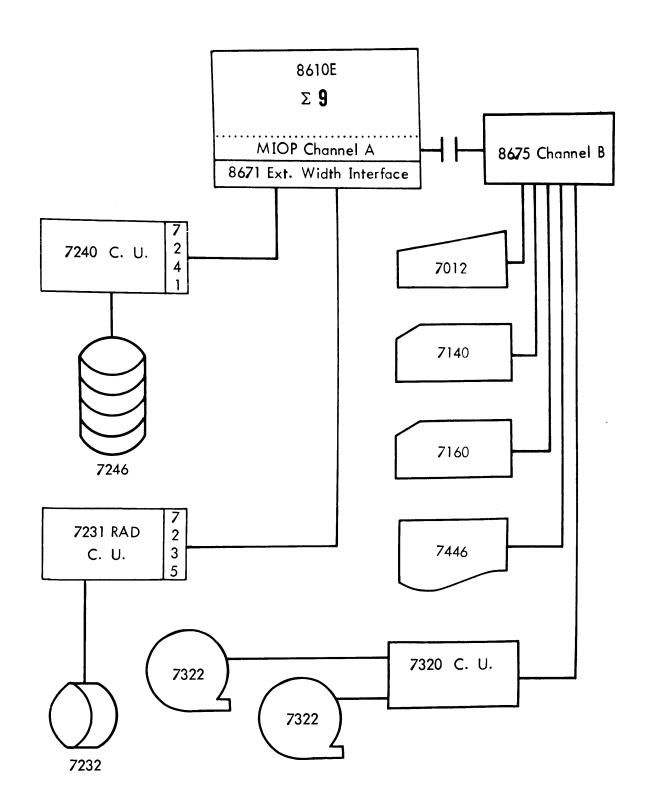

The MIOP is functionally divided into two separate operating channels, Channel A and B (reference the following figure). Both channels can operate concurrently except for sharing the core memory bus (interface). I/O instructions provide for channel discrimination in their addressing scheme. Both channels are contained in a functional assembly called a Channel Control Unit (CCU), which provides the interface logic to core memory and the CPU's in the system. A third interface is provided for diagnostic uses and allows the IOP to be interrogated and controlled during preventive and corrective maintenance routines.

Multiplexor IOP - Functional Diagram

Channel A — Channel A is standard in the MIOP and comes with eight subchannels (numbered 0-7). Each subchannel controls one device controller. The basic set of eight subchannels can control both multi-unit device controllers (with up to 16 devices) and single unit device controllers. Subchannels can be added in groups of eight to increase the number of channel A subchannels to 8-15. The second increment adds subchannels 16-23. Subchannels numbered 8-23 can control only single unit device controllers. Subchannels 8 and 9 have special significance when the memory-to-memory move (MMM) option is installed.

Channel B — Channel B is an option which comes with eight subchannels. Channel B subchannels (numbered 0-7) can control both multi-unit device controllers (with up to 16 devices) and single unit device controllers. Thus, with both Channel A and Channel B installed, the MIOP can accommodate up to 32 device controllers. The ability of the Sigma 9 MIOP to control up to 16 multi-unit device controllers is an increase in flexibility over earlier IOP's where only eight multi-unit device controllers can be installed. Each subchannel has storage facilities (fast-access memory registers) in the MIOP to contain all the control parameters needed to operate a device controller. To improve accuracy and MIOP viability, parity generation/checking is performed on all subchannel storage registers.

# 2.3.1.2 I/O Interface

Both channels come standard with a 1-byte interface which allows each device controller to exchange a single byte of data every time it connects to the MIOP for service.

An optional 4-byte interface may be installed to each channel which then allows those device controllers that have similar interfaces to exchange up to four bytes of data every time it connects to the MIOP for service. Further, if the device controller is capable of exchanging more than four bytes during a service connection, it may initiate a "burst mode" operation and remain connected to the MIOP, exchanging data until zero byte count or channel end is encountered. The burst mode capability is available as part of the 4-byte option.

### 2.3.1.3 Memory-to-Memory Move (MMM)

A common requirement in efficient core memory management is the dynamic relocation of programs and data within core memory. In the past it has been incumbent upon the CPU to perform this task of relocating blocks of data within core memory at the expense of increasing CPU overhead time and sacrificing valuable program execution time. With the MMM option, this task is transferred to the MIOP and is performed as a simulated I/O operation.

To accommodate this option, the MIOP must have the Channel A expansion option which provides subchannels 8 – 15. Subchannels 8 and 9 are dedicated to MMM when it is installed. The MMM option interfaces to subchannels 8 and 9 as I/O device controller simulators. Subchannel (device controller) 8 is used to specify the area in memory to which the data is to be moved (destination) and acts as an input device. Subchannel (device controller) 9 is used to specify the area in memory from which the data is to be moved (source), and acts as an output device. The MMM is mechanized within the MIOP and only transfers data on a word basis. Because all data transfers are accomplished internal to the MIOP, the 4-byte interface option is not required. The MMM is controlled by I/O instructions addressed to Channel A, device controllers 8 and 9. The MMM transfers data at approximately 143K words per second (572 kb/sec).

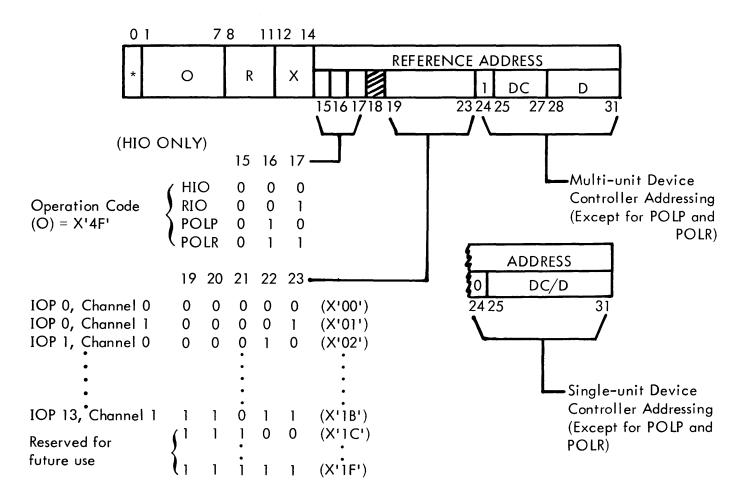

# 2.3.1.4 I/O Instructions

The I/O instructions available for the Sigma 9 I/O system are as follows:

- SIO Start I/O

- TIO Test I/O

- TDV Test Device

- AIO Acknowledge I/O

- HIO Halt I/O

- RIO Reset I/O

- POLP Poll Processor

- POLR Poll Processor and Reset

The instructions RIO, POLP, and POLR are new and consist of variations of the HIO instruction. The SIO, TIO, TDV, AIO, and HIO instructions operate as they did in Sigma 5/6/7 systems. To accommodate additional IOP's and to take advantage of the bus sharing feature of Channels A and B, the format of I/O instructions has been modified as shown in the following figure. The AIO instruction format is essentially unchanged. The POLP and POLR instructions cause the addressed IOP to return fault status to a CPU general register and are usually executed as a result of a Processor Fault Interrupt (PFI).

SIO, TIO, HIO, TDV Instruction Format

#### 2.3.1.5 Maintenance Interface

The Sigma 9 MIOP contains a maintenance interface which allows the MIOP to respond to Read Direct (RD) and Write Direct (WD) instructions executed by the CPU. The primary function of the maintenance interface is to enhance the maintainability of the MIOP by allowing the CPU to interrogate IOP internal control elements (via a snapshot register) and to single phase an IOP to analyze details of an I/O operation for diagnostic purposes.

### 2.3.1.6 Alternate Processor Bus

The Alternate Processor Bus option is a group of modules which provide an additional bus to connect IOP's and CPU's in the Sigma 9 system and enables IOP's to be partitioned in a multiprocessor system for diagnostic purposes.

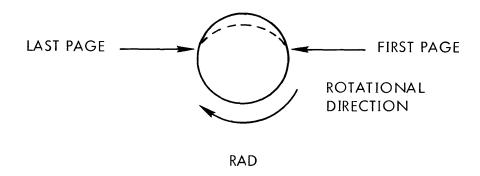

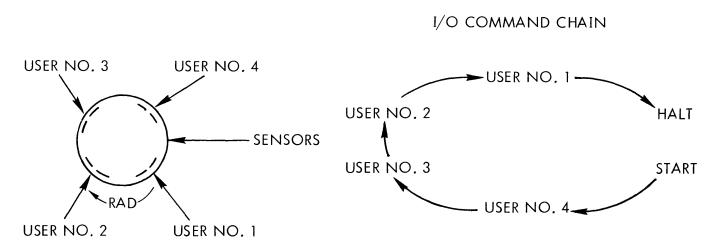

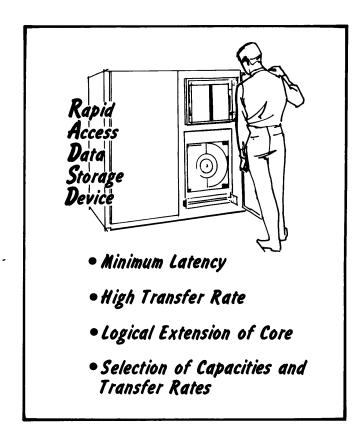

#### 2.3.2 HIGH SPEED RAD IOP (HSRIOP)

The HSRIOP is a combination of an IOP and a device controller. Specifically, the field-proven designs of the Sigma 5/6/7 Selector IOP (SIOP) and the Model 7211 High Speed RAD controller have been integrated into a single unit now called the HSRIOP. The HSRIOP is solely dedicated for use with the existing Model 7212 High Speed RAD Storage Units. The HSRIOP may have as many as four Model 7212's connected to it with transfer rates up to 3MB per second. Each storage unit has a capacity of approximately 5.4MB.

# 2.3.2.1 Options

The only HSRIOP option is the Alternate Processor Bus described in Paragraph 2.3.1.6.

#### 2.3.2.2 Maintenance Interface

The HSRIOP contains the same Maintenance Interface described in Paragraph 2.3.1.5.

# 2.3.2.3 I/O Instructions

The HSRIOP responds to the same I/O instructions described in Paragraph 2.3.1.4 except that it is not sensitive to channel addresses (bit 23 in the I/O instruction format).

#### 2.3.2.4 I/O Operation

The HSRIOP and Model 7212 High Speed RAD Storage Unit always exchange data in the burst mode, and only one storage unit can be exchanging data with the HSRIOP at any given time.

#### 2.4 CONFIGURATIONS

As mentioned earlier, user programs currently running on a Sigma 5, 6, or 7 are fully compatible with a Sigma 9 of equivalent or larger configuration. The RBM, BPM, and BTM operating systems will be modified so that they will also be compatible with Sigma 9. There will be, however, certain minor differences in operating systems. These differences will be totally transparent to the users and all discrepancies between hardware systems will be resolved by XDS's programming department.

#### 2.5 UTS CONFIGURATION

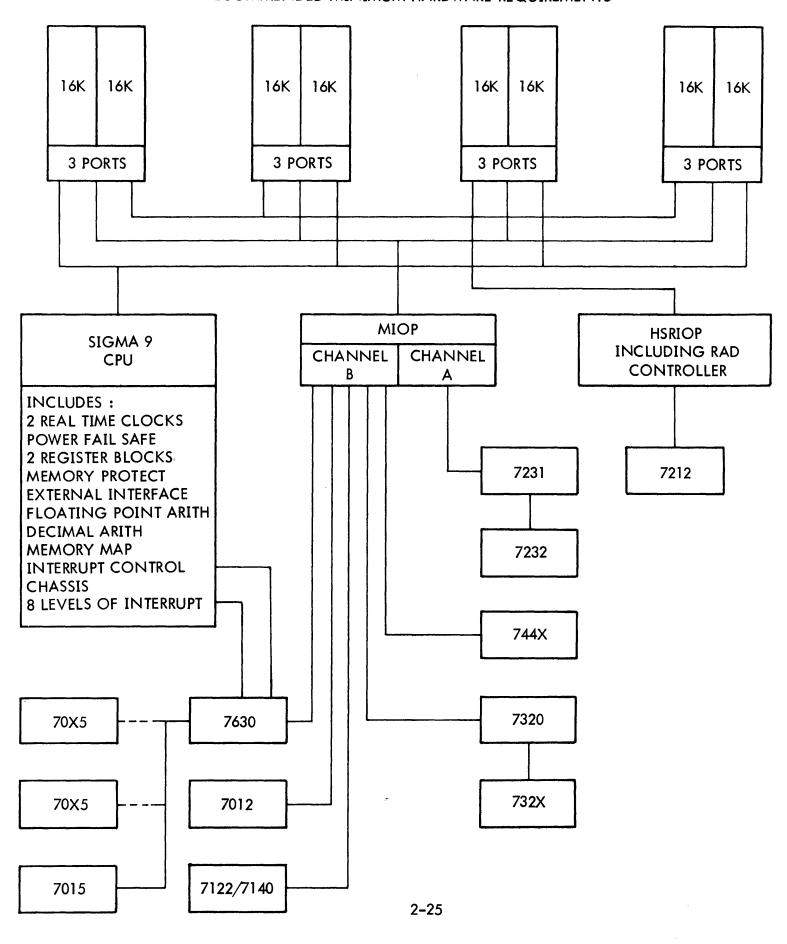

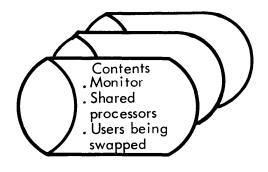

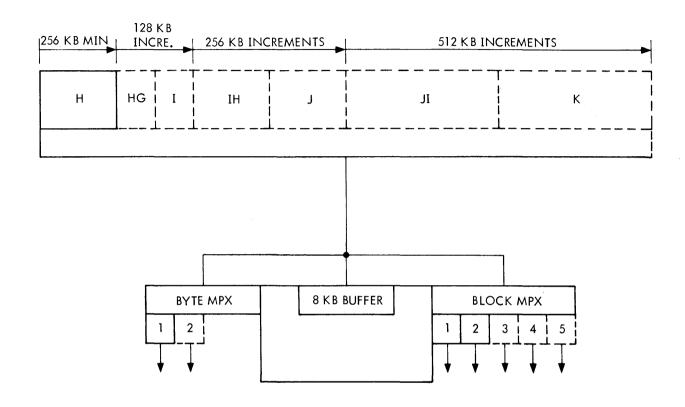

The recommended minimum UTS configuration for a Sigma 9 system (shown on the following page) is conceptually identical to the recommended minimum UTS configuration for the Sigma 7. Since the equipment list for Sigma 9 is different, there are some hardware differences. Most importantly, only one port to memory is required to interface a memory bus to a 32K block of memory, while each separate 16K bank can be simultaneously active. The effect of this is to reduce the number of ports required. Actual operation is as in the past.

# 2.6 TRANSITION AND UPGRADE CONFIGURATIONS

Existing installations present the possibility of upward expansion to a Sigma 9 system. These installations pose no difficulty if they are currently operating under UTS. If another operating system is involved, the transition to Sigma 9 UTS will require examination, but will be smooth due to the compatibilities designed into UTS.

#### SIGMA 9 UNIVERSAL TIME SHARING SYSTEM

# RECOMMENDED MINIMUM HARDWARE REQUIREMENTS

#### 2.6.1 RBM USERS

RBM will be modified to run on the Sigma 9. Sigma 9, however, is not designed for a user whose primary applications are Real Time and since UTS provides comprehensive real time services along with time-sharing and batch processing, an upgrade to Sigma 9 should only be considered if the customer has an application which can use all of the power available in a Sigma 9 UTS system.

#### 2.6.2 BPM USERS

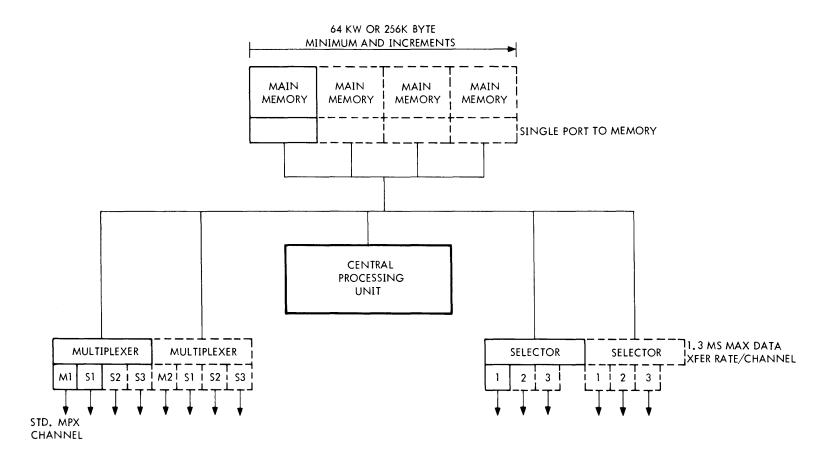

BPM will also be modified to run on Sigma 9. However, in a batch only environment or in batch and a small real time environment, Sigma 9 and XOS is the best system. If the customer's needs are growing, he should be considering the flexibility and adaptability of a universal system — Sigma 9 with XOS.

#### 2.6.3 BTM USERS

While BTM will be modified to run on Sigma 9, it is a considerably less powerful operating system, than UTS. UTS is more efficient in swapping, resource use, and throughput. BTM users should be most anxious to upgrade to UTS, especially if they have a large number of time-sharing users or any real time applications.

Although RBM, BPM, and BTM will be modified to run on the Sigma 9, they will not support any hardware that is unique to Sigma 9 (i.e., they will support a maximum of 128K words, etc.). Using Sigma 9 with any of the systems probably would not take advantage of the features that Sigma 9 offers and a better solution would be UTS or XOS. UTS or XOS are designed to take maximum advantage of Sigma 9 and will give the customer the maximum performance for his investment.

XOS MINIMUM CONFIGURATION

# **EQUIPMENT LIST**

| Quantity | Model        | Description                                                                                                                                                                                                                                                                                            |

|----------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 8610E        | Sigma 9: 512K bytes Core Storage Decimal Arithmetic Unit Floating Point Arithmetic Unit Memory Map Write Protection Two Register Blocks Two Real Time Clocks Power Fail-Safe External Interface Interrupt Control Chassis Eight Interrupt Levels Multiplexor I/O Processor Channel A Eight Subchannels |

| 1        | 8671         | Motor Generator Set Extended Width Interface                                                                                                                                                                                                                                                           |

| 1        | 8675         | MIOP Channel B w/8 subchannels                                                                                                                                                                                                                                                                         |

| 1 .      | 7012         | Keyboard Printer                                                                                                                                                                                                                                                                                       |

| 1        | 7140         | Card Reader (1500 CPM)                                                                                                                                                                                                                                                                                 |

| 1        | 7160         | Card Punch (300 CPM)                                                                                                                                                                                                                                                                                   |

| 1        | <b>723</b> 1 | Extended Performance RAD Controller                                                                                                                                                                                                                                                                    |

| 1        | 7232         | RAD Storage Unit                                                                                                                                                                                                                                                                                       |

| 1        | 7235         | Extended Width Interface/7231                                                                                                                                                                                                                                                                          |

| 1        | 7240         | Removable Disk Controller                                                                                                                                                                                                                                                                              |

| 1        | 7241         | Extended Width Interface/7240                                                                                                                                                                                                                                                                          |

| 1        | 7244         | Disk Pack (11–High)                                                                                                                                                                                                                                                                                    |

| 1        | 7246         | Single Spindle Disk Storage Unit                                                                                                                                                                                                                                                                       |

| 1        | 7320         | Tape Controller                                                                                                                                                                                                                                                                                        |

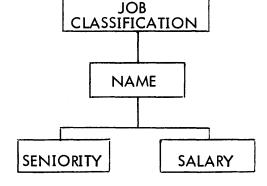

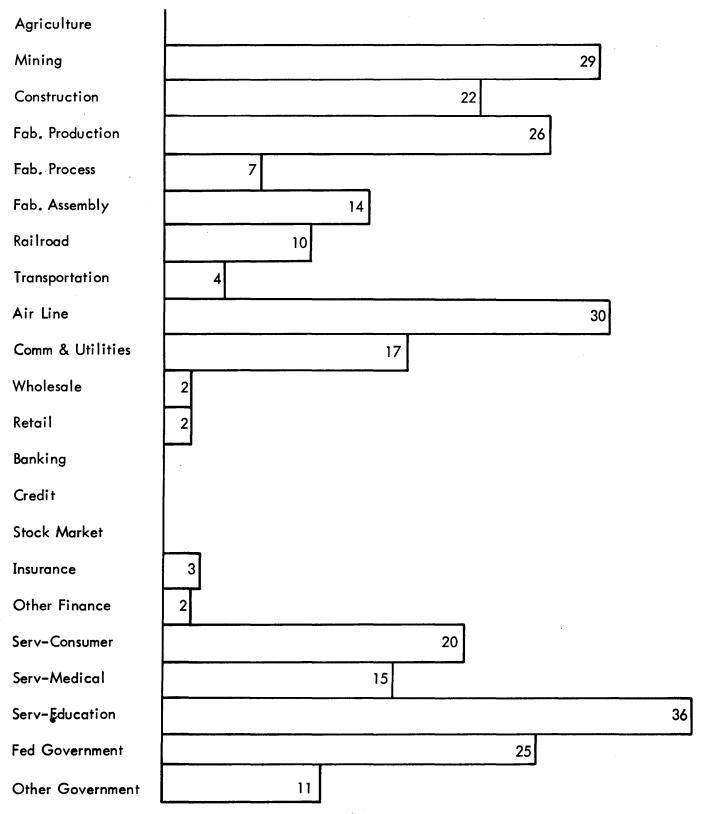

| 2        | 7322         | Tape Unit (9-Track)                                                                                                                                                                                                                                                                                    |