David R. Bennion

Senior Research Engineer Engineering Sciences Laboratory Stanford Research Institute

Hewitt D. Crane

Staff Scientist Engineering Sciences Laboratory Stanford Research Institute

#### David Nitzan

Senior Research Engineer Engineering Sciences Laboratory Stanford Research Institute

New York

San Francisco

MCGRAW-HILL BOOK COMPANY

Toronto

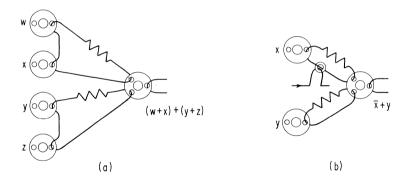

London

Sydney

Copyright © 1969 by McGraw-Hill, Inc. All Rights Reserved. Printed in the United States of America. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher. *Library of Congress Catalog Card Number* 68-28411.

04699

#### 1234567890 MAMM 754321069

### INTRODUCTION

This book deals with a class of digital magnetic-core circuits that consist of magnetic components and interconnecting conductors, and which offer extremely high reliability, long life, and adaptability to special environments, e.g., high-intensity radiation. The history of such *core-wire circuits*, as we refer to them in this book, spans some 15 to 20 years, from the first discussions of theoretical possibility to the large array of techniques and variations at present.

Four potential areas of study for any device and circuit technology are (1) the physics of the devices, (2) the development of engineering models for use in circuit analysis, (3) the development of circuit synthesis techniques, and (4) the development of quantitative circuit-design methods. Part I is concerned with areas (3) and (4) and is based on the use of a highly abstracted magnetic-core model that greatly simplifies the discussion of basic circuit principles. The bulk of the writing in Part I covers many different core-wire techniques and represents an attempt to integrate the published work of many different authors. Parts of Chaps. 6 and 10 are concerned with circuit-design methods not previously published. Part II covers areas (1) and (2), based on use of more detailed, precise consideration of magnetic phenomena. Chapter 11 provides a condensed summary of the physics of magnetism for readers wishing some insight into the behavior of square-loop cores. Chapter 12 covers recently developed core models that permit accurate representation of flux switching in square-loop cores.

Part I is a step-by-step development of the principles of magnetic-core circuit techniques. In Chap. 1 we introduce the language of flux linkage and current linkage, and show how basically different the circuit action is when a core is loaded with resistive, inductive, or capacitive elements. In Chap. 2 we consider

INTRODUCTION

flux transfer from one core to another core, in which case a change in flux linkage from the switching of a first core induces a coupling-loop current that switches the second core; the change in flux level,  $\Delta\phi$ , becomes our basic signal. We are primarily interested in the ratio of received flux to transmitted flux, i.e., the flux-transfer ratio G, which is generally a function of the transmitted flux level  $\Delta\phi_T$ . Of special interest are the conditions for G > 1, that is, for  $\Delta\phi$  gain.

In Chap. 3 we show that in order to achieve bistable gain characteristics, G must exhibit a certain form of functional dependence on  $\Delta \phi_T$ . Proper balancing of flux-gain and flux-loss mechanisms permits the realization of the required functional form. To maintain this transfer characteristic between two cores embedded in a chain of similar cores, certain requirements on forward and backward isolation must be met. It is shown how diodes readily serve in this role, which is the basis of the well-known core-diode logic circuits.

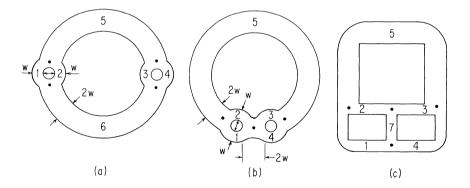

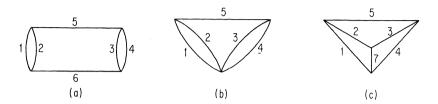

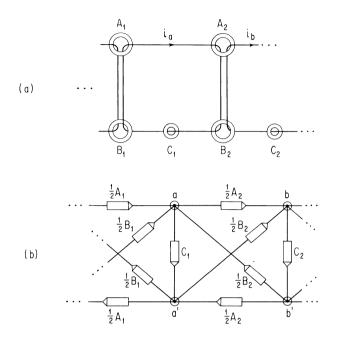

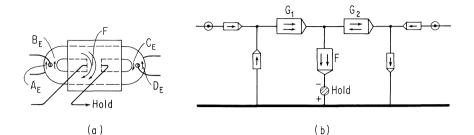

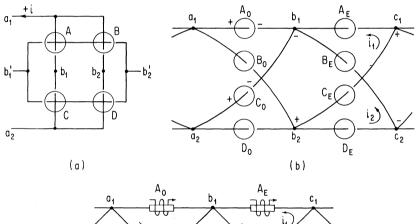

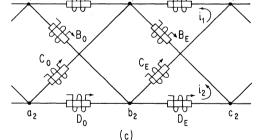

In Chap. 4 we introduce several varieties of core-wire circuits. This begins as an effort to replace the diodes in a corediode circuit by other toroidal cores. A systematic replacement procedure is developed, and we show how any core-diode circuit can in fact be realized in core-wire form, i.e., as a circuit consisting simply of toroidal cores and interconnecting wire. We then extend the class of core-wire circuits and develop new circuit forms that have no equivalent core-diode forms. We also introduce more complex core shapes, i.e., multileg cores, and show their advantages over functionally equivalent arrays of simple toroidal cores.

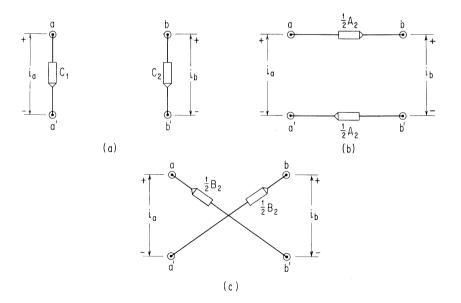

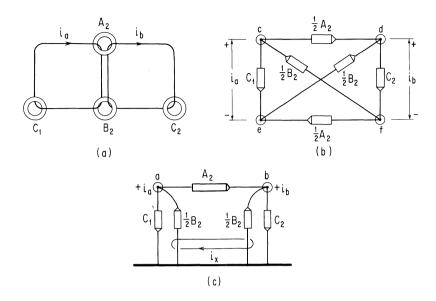

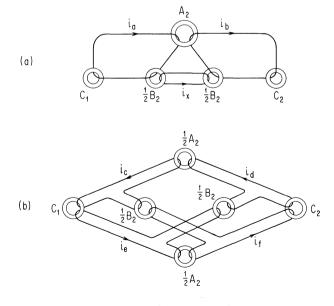

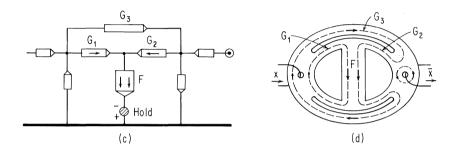

In Chap. 5 we show how to transform a core circuit to a magnetic-network representation in which rate of flux change is the flow variable. The network representation provides a common language for flux-transfer schemes. Many schemes that superficially appear different can be shown by the network representation to be functionally equivalent. Also, it is generally simpler to convert from one type of scheme to another after transforming to the network domain. Examples of transformations and reverse transformations are given. In particular, it is shown that any given network may often have many different forms of physical realization.

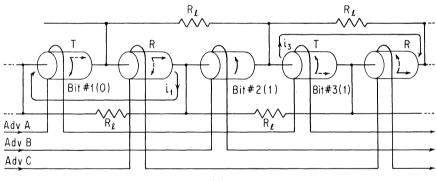

In Chap. 6 we treat a specific core-wire scheme, designated by the term MAD-R, that has been studied and applied more than any other scheme. A quantitative design method for this form of circuit is presented, and it is shown that circuits of this type can be designed to operate with very wide tolerances on temperature and power-supply conditions.

The core-wire schemes known today were invented by many different persons and generally in a rather *ad hoc* and random fashion, a situation that characterizes the early advances in many fields. In Chap. 7, a technique is described by means of which one can search for all possible schemes for a given configuration of magnetic elements. Certain new schemes derived in this fashion, as well as a formal "re-inventing" of certain of the schemes discussed in Chaps. 4 and 5, are given by way of example. The method itself offers interesting insight into the operation of these circuits.

A comment is in order on scheme identification as generally used throughout these chapters. Because it was not easy to develop nomenclature that clearly distinguishes between various schemes (in the fashion of the terms DCTL, TRL, and the like, as applied to transistor circuits), we decided instead to identify a scheme or method of approach by the name of the person with whom it is associated, as far as we know, either by patent disclosure or publication. We depart from this policy in the case of better-known schemes when a name has been established (e.g., the MAD-R scheme).

In Chaps. 8 and 9 we introduce other methods of approach to circuit synthesis that open up whole new families of schemes, some of which offer significant potential for future practical application. Three different techniques are introduced in Chap. 8, each leading to new scheme types. Together these techniques pave the way in Chap. 9 for an important class of bipolar schemes. In the bipolar representation, the binary states (designated *one* and *zero*) are symmetrically represented; i.e., they are characterized by flux transfer of equal amplitudes but opposite polarities, as opposed to high and low levels of flux transfer in the unipolar schemes. A number of especially interesting schemes based on the use of coherent rotation of magnetization in thin films fall into the bipolar category.

Through Chap. 9 we are concerned strictly with the development of basic transfer schemes, i.e., flux transfer along a simple, iterative chain of circuits, without regard to logical fan-in or fan-out. In Chap. 10 we investigate methods of general logic synthesis with core-wire circuits.

Part II is concerned with the magnetic devices themselves. Chapter 11 is a highly condensed, step-by-step exposition of the physics of magnetism that leads to the basic square-loop characteristic and the basic mechanisms of flux switching. It provides the reader with some background to appreciate the empirical models for flux switching that are discussed in detail in Chap. 12.

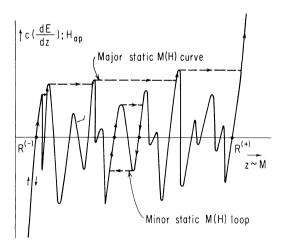

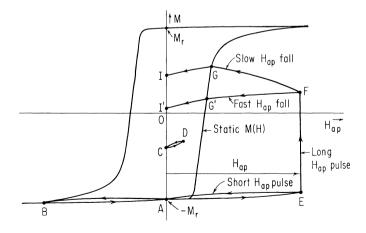

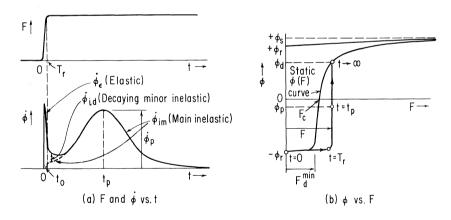

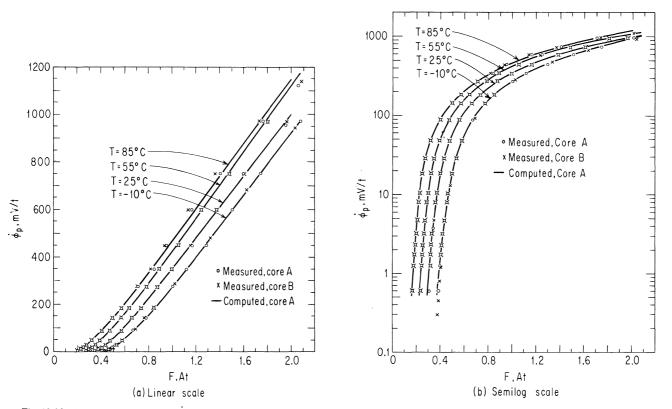

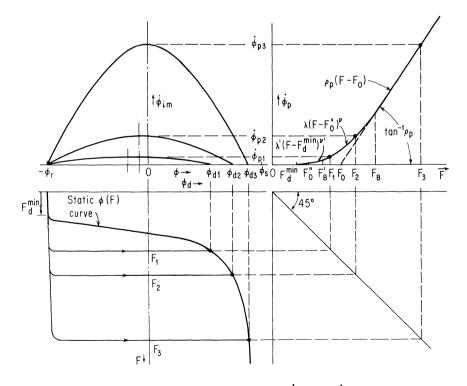

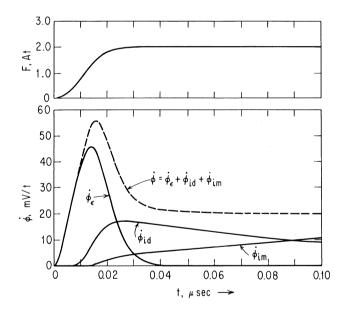

The goal of Chap. 12 is to model the static and dynamic flux properties of square-loop magnetic cores. It is shown that a pair of simple mathematical equations can model the major hysteresis loop of a typical ferrite material, from which hysteresis loops for thick-walled toroidal cores are derived and shown to fit experimental data quite accurately. Parameters derived from these static hysteresis curves are used in the dynamic switching models. From the results of basic flux-switching experiments, it is shown that the familiar elastic and inelastic components of flux switching can best be modeled in terms of two components each. The two components of elastic switching are due to rotation of magnetization and local domain-wall movements; the two components of inelastic switching relate to what are referred to as minor and major wall displacements. Mathematical equations for all four components are derived, and it is shown how these relations quite accurately model flux switching of ferrite cores over a large range of drive amplitudes, conditions of loading, and switching speed (from nanoseconds to microseconds). Computational methods for the models are also discussed. These models are presently being applied with considerable success to computer-aided analysis of complex magnetic-core circuits.

Two primary reasons can be singled out for the erratic development of core-wire logic circuits over the past fifteen years: the general lack of background, training, and understanding of magnetics by engineers who are the potential users; and the rapid growth of semiconductor technology, which has generally offered circuits with performance superior to that of core circuits under most, though not all, conditions. This book was begun over seven years before publication, and the enthusiasm for following it to completion has been similarly erratic. We finally came to the conclusion, independently of short-time variations in general interest, that core-wire or other magnetic-core logic circuits in one form or another will likely find their niche-if not based on ruggedness and reliability one year, then on radiation immunity and absence of standby power the next. This factor provided a major impetus to complete the book. But equally important, although the underlying thread of this book is the highly specialized technology of core-wire circuits, much of the material is relevant to magnetic devices and circuits in general.

## **CONTENTS**

v

25

27

|   |      | PART I CORE-WIRE CIRCUITS                          |    |

|---|------|----------------------------------------------------|----|

| 1 | Eler | nentary Circuits                                   | 3  |

|   | 1-1  | Introduction                                       | 3  |

|   | 1-2  | Resistive Load; $\Delta \phi$ Dissipation          | 8  |

|   | 1-3  | Inductive Load; $\Delta \phi$ Storage              | 9  |

|   | 1-4  | Capacitive Load; $\Delta \phi$ Transformation      | 12 |

|   | 1-5  | Summary                                            | 15 |

| 2 | Cou  | pled Pair of Cores; $\Delta \phi$ Transfer         | 17 |

|   | 2-1  | Flux Transfer Ratio G                              | 17 |

|   | 2-2  | Requirement on Turns Ratio for $G > 1$             | 19 |

|   | 2-3  | Limit on Loop Resistance                           | 19 |

|   | 2-4  | Effect on G of Transmitter and Receiver Thresholds | 21 |

|   | 2-5  | Effect on G of Coupling-Loop Inductance            | 23 |

|   | 2-6  | Effect on G of Receiver Loading                    | 23 |

2-6 Effect on G of Receiver Loading

#### 2-7 Flux Pumping 2-8 Direct-Current Drive; Implicit Phasing

Introduction

|   | 2-9  | Summary                                         | 29 |

|---|------|-------------------------------------------------|----|

| 3 | Digi | tal Transfer in Iterative Core Circuits         | 30 |

|   | 3-1  | Binary Shift Register                           | 31 |

|   | 3-2  | Digital Transfer                                | 32 |

|   | 3-3  | Gain and Loss Mechanisms                        | 35 |

|   | 3-4  | Forward Decoupling in a Magnetic Chain          | 37 |

|   | 3-5  | Backward Isolation; Core-Diode Transfer Schemes | 38 |

|   | 3-6  | Transfer Schemes Using Capacitance              | 41 |

|   | 3-7  | Summary                                         | 44 |

|   |      |                                                 |    |

| CON. | TEN | TS |

|------|-----|----|

|------|-----|----|

| 4 | Intro       | oduction to Core-Wire Transfer Schemes                     | 45  |

|---|-------------|------------------------------------------------------------|-----|

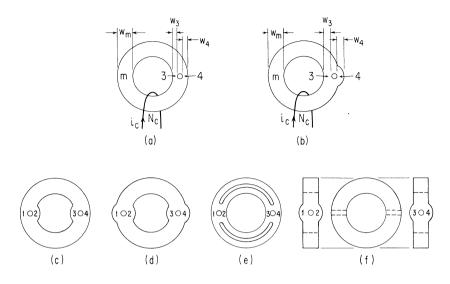

|   | 4-1         | Simulation of Diode Action                                 | 46  |

|   | 4-2         | Core-Wire Scheme with No Core-Diode Equivalent             | 49  |

|   | 4-3         | Replacement of Loop Resistance by a Core                   | 50  |

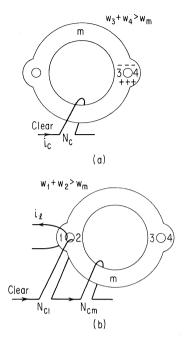

|   | 4-4         | Extra Isolation with Multileg Cores                        | 52  |

|   | 4-5         | Isolation of Input and Output in Separate Apertures        | 56  |

|   | <b>4-</b> 6 | Summary                                                    | 61  |

| 5 | Mag         | netic Network Representation of Core-Wire Schemes          | 63  |

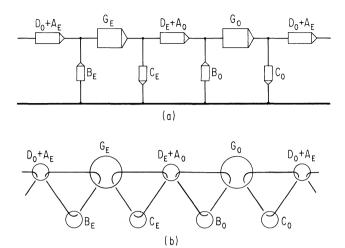

|   | 5-1         | Network Representation                                     | 65  |

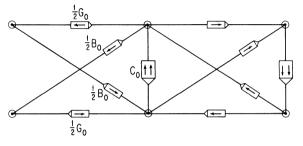

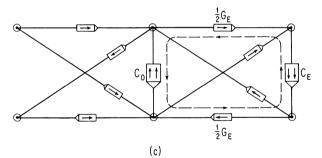

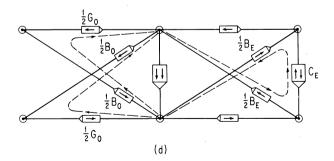

|   | 5-2         | Ladder and Lattice Networks                                | 75  |

|   | 5-3         | Manipulation of Nodes; Reverse Transformations             | 80  |

|   | 5-4         | Flux-State Sequencing in Magnetic Networks                 | 84  |

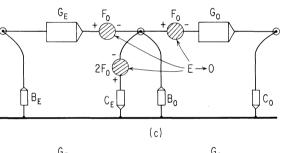

|   | 5-5         | The Flux-Doubling Scheme and Its Network Representation    | 92  |

|   | 5-6         | Summary                                                    | 98  |

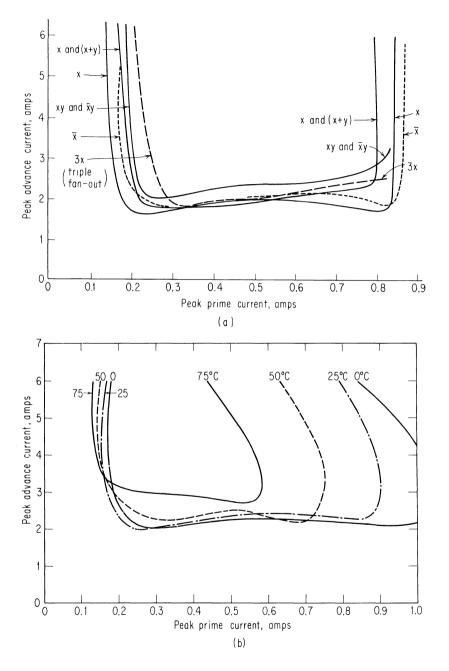

| 6 | MAI         | D-R Scheme                                                 | 100 |

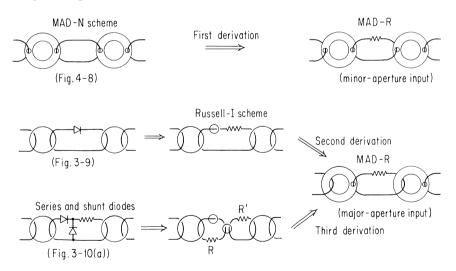

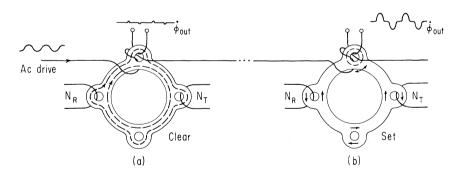

|   | 6-1         | Derivation from MAD-N Scheme                               | 101 |

|   | 6-2         | Second Derivation, from Russell Type-I Scheme              | 107 |

|   | 6-3         | Third Derivation, Based on Series-Shunt Core-Diode Circuit | 110 |

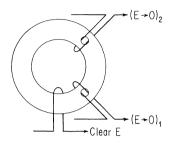

|   | 6-4         | Minor-Aperture Input and Output                            | 112 |

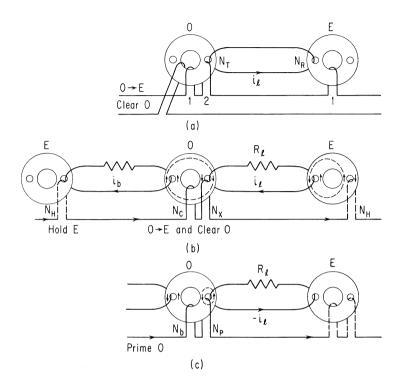

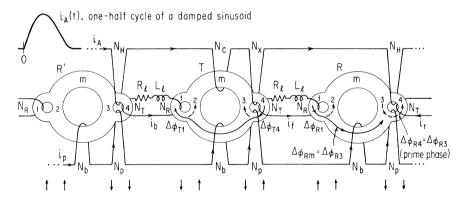

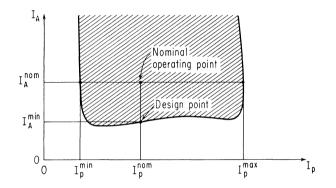

|   | 6-5         | An Approach to Circuit Design                              | 114 |

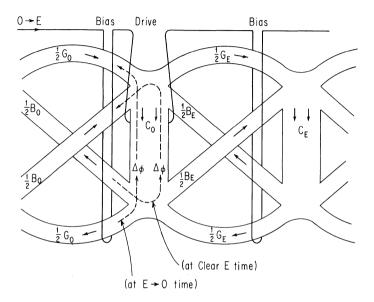

|   | 6-6         | Design of Coupling Loops and Advance Circuit               | 115 |

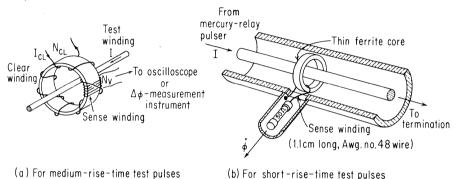

|   | 6-7         | Measurement of Design Parameters                           | 125 |

|   |             | Design of Priming Circuitry                                | 132 |

|   |             | Core Design                                                | 141 |

|   |             | Summary                                                    | 145 |

| 7 | Forr        | nal Derivation of Transfer Schemes                         | 147 |

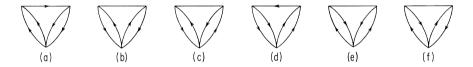

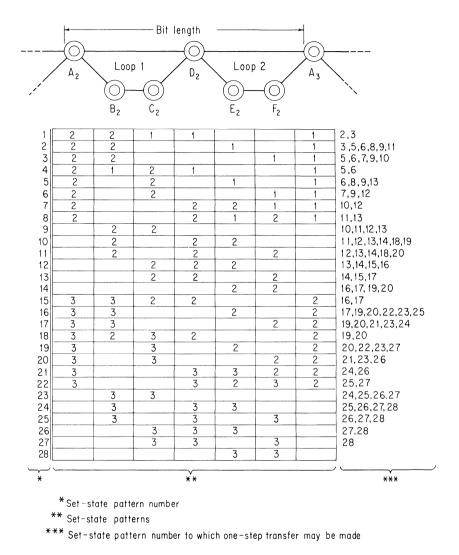

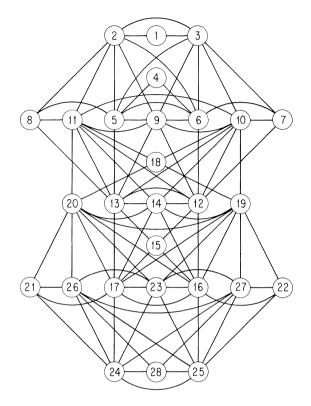

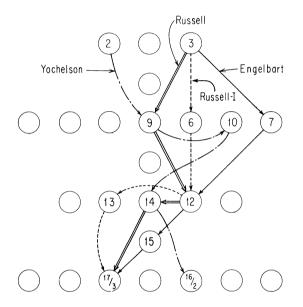

|   | 7-1         | Van De Riet Representation                                 | 148 |

|   | 7-2         | Set-State Chart                                            | 153 |

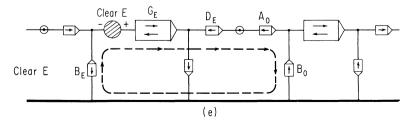

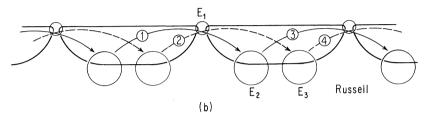

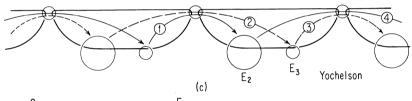

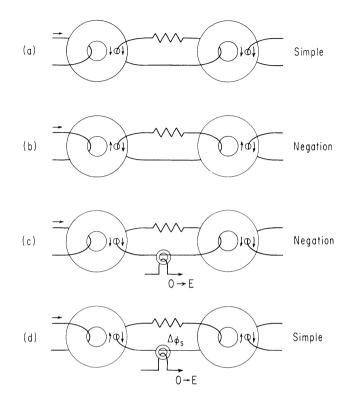

|   | 7-3         | Schemes with Configuration (c)                             | 157 |

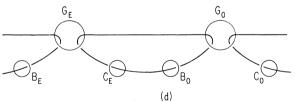

|   | 7-4         | Schemes with Configuration (d)                             | 158 |

|   | 7-5         | Summary                                                    | 164 |

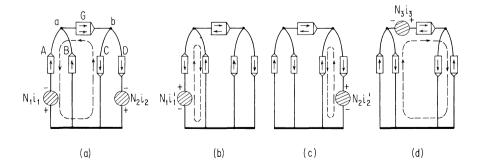

| 8 | Flux        | Sources, Orthogonality, and Dynamic Biasing                | 165 |

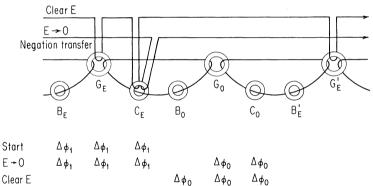

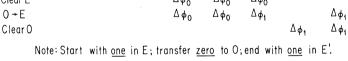

|   | 8-1         | Negation-Transfer Schemes                                  | 166 |

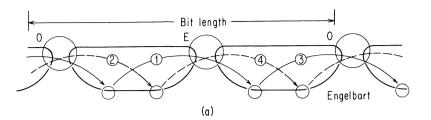

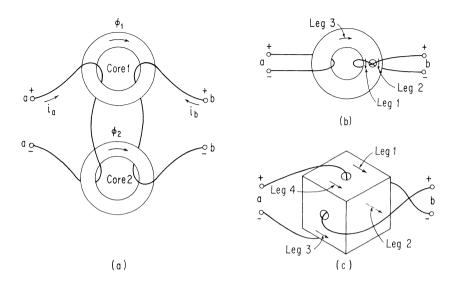

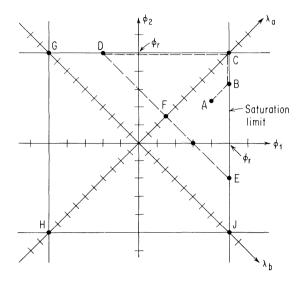

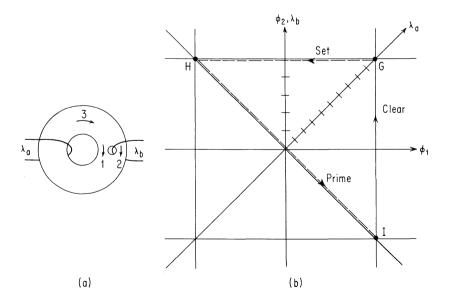

|   | 8-2         | Engelbart Orthogonal-Mode Technique                        | 175 |

|   | 8-3         | Dynamic Bias                                               | 182 |

|   | 8-4         | Summary                                                    | 190 |

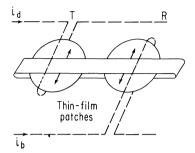

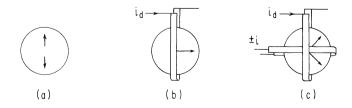

| 9 | Bipo        | lar Representation and Thin-Film Schemes                   | 191 |

|   | 9-1         | Bipolar Schemes                                            | 192 |

|   | 9-2         | Thin-Film Schemes                                          | 199 |

|   | 9-3         | Non-Return-to-Reference Schemes                            | 209 |

|   | 9-4         | Summary                                                    | 212 |

х

| CON | NTENTS      |                                                         | xi         |

|-----|-------------|---------------------------------------------------------|------------|

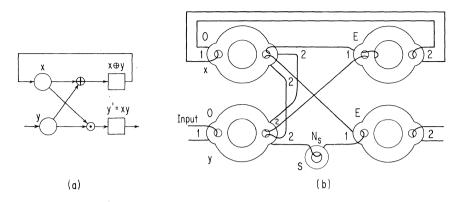

| 10  | Syntl       | nesis of General Logic Circuits                         | 215        |

|     | 10-1        | Introduction                                            | 215        |

|     | 10-2        | Synchronous Logic System                                | 216        |

|     |             | Magnetic Synchronous Logic System                       | 218        |

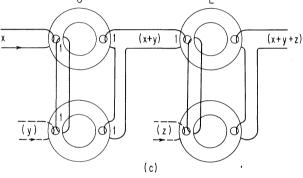

|     | 10-4        | Combinational Logic                                     | 221        |

|     | 10-5        | Design Example: Decimal Arithmetic Unit                 | 234        |

|     |             | Extension of the MAD-R Scheme to General Logic          |            |

|     |             | Synthesis                                               | 240        |

|     | 10-7        | Summary                                                 | 248        |

| Re  | ferenc      | es for Part I                                           | 249        |

|     | Р           | ART II MAGNETISM AND FLUX-SWITCHING MODELS              |            |

| 11  | <b>T</b> 21 |                                                         | 255        |

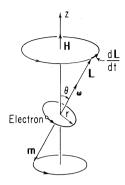

| 11  |             | entary Physics of Magnetism                             | 255<br>256 |

|     | 11-1        | Magnetization                                           | 250<br>261 |

|     |             | Types of Magnetism                                      | 261        |

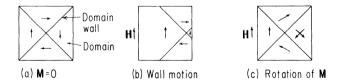

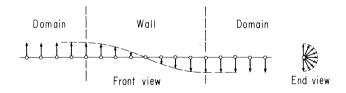

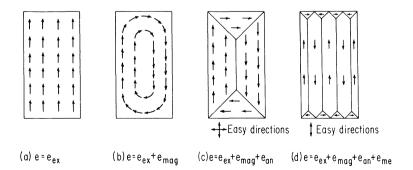

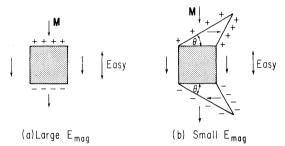

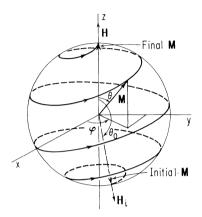

|     |             | Domain Theory                                           | 200<br>274 |

|     |             | Mechanisms of Magnetization Switching                   |            |

|     | 11-5        | Summary                                                 | 284        |

| 12  | Magn        | etic Flux-Switching Models                              | 286        |

|     | 12-1        | MMF and Flux in Magnetic Cores                          | 287        |

|     | 12-2        | Flux-Switching Experiments                              | 291        |

|     | 12-3        | Static $\phi(F)$ Models                                 | 295        |

|     | 12-4        | Elastic $\dot{\phi}(t)$ Models                          | 301        |

|     | 12-5        | Inelastic $\dot{\phi}(t)$ Models                        | 315        |

|     | 12-6        | Computation of Flux Switching in Magnetic-Core Circuits | 332        |

|     | 12-7        | Summary                                                 | 346        |

| Re  | ferenc      | es for Part II                                          | 348        |

| Ind | lex         |                                                         | 353        |

# Part I CORE-WIRE CIRCUITS

## ELEMENTARY CIRCUITS

| 1-1 | Introduction                                  |   |  |   |   |  |  |  |  |   | <br>• |   |  |  |  |   | 3  |

|-----|-----------------------------------------------|---|--|---|---|--|--|--|--|---|-------|---|--|--|--|---|----|

| 1-2 | Resistive Load; $\Delta \phi$ Dissipation     |   |  |   |   |  |  |  |  |   | <br>• |   |  |  |  |   | 8  |

| 1-3 | Inductive Load; $\Delta \phi$ Storage         |   |  | • | • |  |  |  |  | • | <br>• |   |  |  |  | • | 9  |

|     | Capacitive Load; $\Delta \phi$ Transformation |   |  |   |   |  |  |  |  |   |       |   |  |  |  |   |    |

| 1-5 | Summary                                       | • |  |   |   |  |  |  |  |   | <br>• | • |  |  |  |   | 15 |

In order to develop some background for dealing with flux transfer between cores, which is basic to any digital magnetic-core circuit, we consider in this first chapter the properties of simple circuits utilizing a single magnetic element in combination with certain of the more common electrical components. The primary intent is qualitative understanding rather than engineering detail.

#### 1-1 Introduction

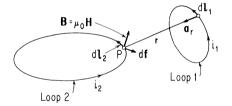

Let us first review the fundamental rules governing induced electromotive force (emf) and induced magnetomotive force (mmf). Consider a vector field B representing magnetic flux density at any point in space. If B changes with time, then an electric field E is induced, as described by one of Maxwell's equations, namely

curl

$$\mathbf{E} \equiv \nabla \times \mathbf{E} = -\frac{\partial \mathbf{B}}{\partial t}$$

(1-1)

By vector manipulation, Eq. (1-1) may be converted to the integral form

$$\oint_{P} \mathbf{E} \cdot \mathbf{d}l = -\frac{\partial}{\partial t} \int_{A} \mathbf{B} \cdot \mathbf{dA}$$

(1-2)

3

usually referred to as Faraday's law of induction, where P is any closed path, and A is any surface bounded by P. The line integral of E along P is the loop emf e, and  $\int \mathbf{B} \cdot d\mathbf{A}$  is the magnetic flux linking the closed loop P. When the same quantity of flux  $\phi$  is encircled N times by the loop P, that is, a winding of N turns, then, effectively

$$\int \mathbf{B} \cdot \mathbf{dA} = N\phi \qquad (1-3)$$

and for this case, Eq. (1-2) may be rewritten as

$$e = -N \frac{d\phi}{dt} \tag{1-4}$$

The minus sign in Eq. (1-4) implies that the induced emf tends to produce current with associated flux linkage opposing the original  $Nd\phi/dt$ , in accordance with Lenz's law and use of a left-hand rule. Normally we will be concerned with a coupling loop, i.e., a closed path formed by an electrical conductor, in which the current that flows is such that the total voltage drop around the loop is always equal to the induced emf e.

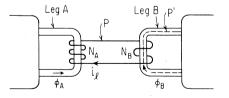

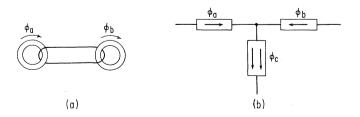

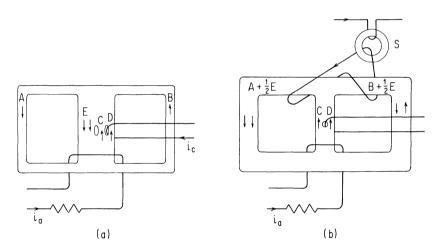

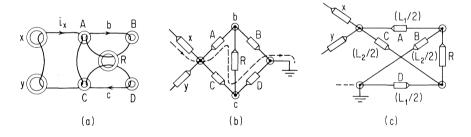

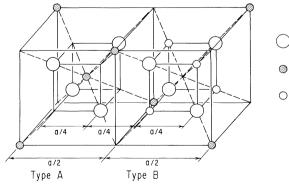

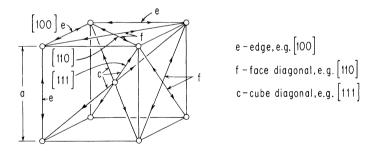

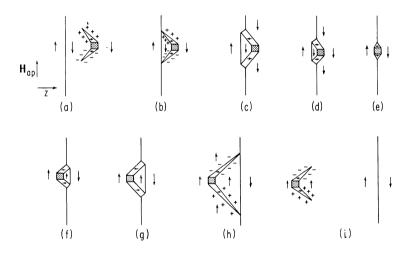

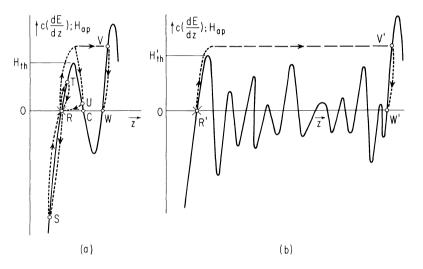

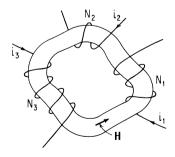

In core circuits we are primarily concerned with magnetic fields that are concentrated within the surface boundaries of cores. In Fig. 1-1, assume that the field B is confined entirely to the two core legs A and B with total flux values of  $\phi_A$  and  $\phi_B$ , respectively. The flux in each of these legs closes through some external magnetic structure. If the closed path P encircles these legs  $N_A$  and  $N_B$  times, as shown, then the total flux linking the path is actually  $N_A \phi_A + N_B \phi_B$ .

Fig. 1-1. Interconnecting two magnetic legs with a coupling loop of  $N_A$  and  $N_B$  turns; polarities are consistent with  $+d\phi_A/dt$  or  $+d\phi_B/dt$  inducing a positive loop current  $i_{\rm f}$ .

Consider next a vector current density J that generates a magnetic field, according to another of Maxwell's equations ELEMENTARY CIRCUITS

$$\operatorname{curl} \mathbf{H} \equiv \nabla \times \mathbf{H} = \mathbf{J} \tag{1-5}$$

The displacement-current term  $\partial D/\partial t$  that normally belongs in this equation is omitted here because it is generally negligible in the circuits in which we are primarily interested. Equation (1-5) can be converted to the integral form

$$\oint_{P'} \mathbf{H} \cdot d\mathbf{l} = \oint_{A'} \mathbf{J} \cdot d\mathbf{A}$$

(1-6)

usually referred to as Ampere's law, where P' is a closed path and A' is any surface bounded by P'. The line integral of H is the loop mmf F, and  $\int \mathbf{J} \cdot d\mathbf{A}$  is the total current linkage of the closed loop P'. For a set of discrete currents  $i_j$  linking P' we can rewrite Eq. (1-6) as

$$F = \sum_{j} N_{j} i_{j} \tag{1-7}$$

If P' follows along Leg B, then the component of mmf generated by current  $i_{\ell}$  is  $N_B i_{\ell}$ , with direction given by the familiar right-hand rule.

From Fig. 1-1 we see that any flux change in Leg A threads the electric loop  $N_A$  times and that any loop current encircles Leg A the same number of times. This illustrates that the number of *inter* linkages between a magnetic leg and an electric loop is actually independent of which one wraps around the other. It also brings out the distinction between total flux linkage through an electric loop, versus simply the flux in a magnetic leg, and similarly for total current linkage through a magnetic core versus simply the current in a conductor.

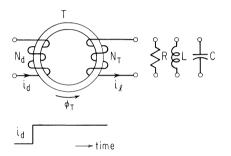

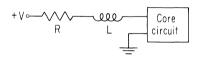

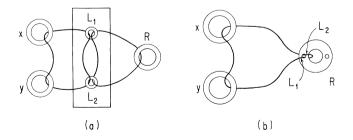

Figure 1-2 shows the general circuit configuration to be considered in the following sections, in which we analyze separately the effects of resistive, inductive, and capacitive loads on a core connected to a drive current  $i_d$  applied through  $N_d$  turns. We will assume some highly simplified core characteristics that are adequate for the purposes of this chapter, and, in fact, for most of Part I.

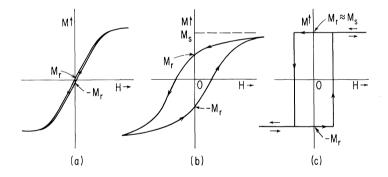

First we assume that the core exhibits the idealized static  $\phi$ -F hysteresis loop shown in Fig. 1-3(a). By the term *static*, it is meant that this is the curve that would be traced out if the mmf F were changed very slowly (quasi-statistically) in time and the corresponding  $\phi$  values plotted. The horizontal top and bottom of the loop represent positive and negative flux saturation levels and the

vertical sides imply that flux changes between negative and positive saturation with |F| only slightly greater than the *threshold* value  $F_0$ . An actual curve has finite slopes at the top and bottom, which account for an inductive component in switching, often referred to as the elastic-flux component. (The source of this component is discussed in detail in Chap. 12.) In any case, if a core is driven into saturation and the drive is then reduced to zero, that is, F = 0, the resulting remanent flux level is designated as  $\phi_r$ . A core with a hysteresis loop approaching the ideal shape shown in Fig. 1-3(a) is commonly referred to as having a square-loop characteristic.

Fig. 1-2. General circuit to be analyzed with a resistive, inductive, or capacitive load connected separately.

Fig. 1-3. Equivalent circuit for a core, based on an idealized  $\phi$  – F loop.

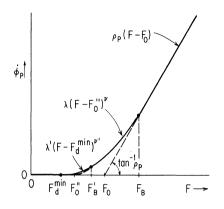

In addition to this simple static model, we assume for most purposes in Part I that dynamic change of flux  $\dot{\phi} \equiv d\phi/dt$  in the range  $-\phi_r < \phi < \phi_r$  is governed by the relation

$$\dot{\phi} = \overline{\rho}(F - F_0) \quad \text{for } F > F_0$$

$$\dot{\phi} = \overline{\rho}(F + F_0) \quad \text{for } F < -F_0$$

(1-8)

and

where  $\overline{\rho}$  (the average value of the inelastic switching parameter  $\rho$ ) is a constant and where F is equal to the mmf  $\sum_j N_j i_j$ . According to this model, the rate of flux change is proportional to the *excess* mmf, i.e., the amount by which F exceeds the threshold  $F_0$ . In Chap. 12 it is shown that the switching parameters are by no means constant, as assumed here for  $\overline{\rho}$  and  $F_0$ , but depend strongly on the instantaneous flux state, on how this state was reached, and also on F itself. Since the models for  $\rho$  and  $F_0$  developed in Chap. 12 are relatively complex, we have chosen here to assume constant values of  $\overline{\rho}$  and  $F_0$  for mathematical simplicity in demonstrating principles. Curves subsequently calculated from the switching model of Eq. (1-8) are therefore accurate only in their grosser aspects.

Based on this model, there is a simple electrical equivalent circuit for a core under the conditions that  $|\phi| < \phi_r$  and  $F \ge F_0$ . In Fig. 1-3(b) is shown a core with no coupling-loop load. For simplicity, the winding for  $i_d$  is drawn as if to link the core only once, but  $N_d$  linkages are assumed. The emf  $e_d$  due to switching is

$$e_{d} = \bar{\rho}N_{d}(N_{d}i_{d} - F_{0}) = N_{d}^{2}\bar{\rho}\left(i_{d} - \frac{F_{0}}{N_{d}}\right)$$

(1-9)

This expression may be represented by the equivalent circuit of Fig. 1-3(c), where the diode is assumed to have zero forward resistance and infinite back resistance. This ideal diode and the current generator  $F_0/N_d$  in parallel with it together behave as a current sink accepting all input current  $i_d$  up to the value  $F_0/N_d$ , without supporting any voltage. For  $i_d > F_0/N_d$ , the diode is cut off and  $e_d > 0$ . The equivalent circuit is valid until the core saturates, i.e., until a time  $\tau$  such that  $\phi = +\phi_r$  or  $\Delta\phi = 2\phi_r$ , where

$$\int_{0}^{\tau} \dot{\phi}_{T} dt = \frac{1}{N_{d}} \int_{0}^{\tau} e_{d} dt = 2\phi_{r}$$

(1-10)

assuming the core starts in negative saturation  $-\phi_r$ . When the core saturates at  $+\phi_r$ , and therefore terminates switching, the equivalent switching resistance becomes zero and the core effectively represents a short circuit except for the inductance term due to the elastic-flux component, which is ignored in this chapter.

#### 1-2 Resistive Load; $\Delta \phi$ Dissipation

Consider the case in which the coupling loop of Fig. 1-2 connects the core T, called a transmitter core, to a resistive element. The loop inductance is assumed negligible. The core is driven by a step  $i_d(t)$  current pulse from an initial state  $\phi = -\phi_r$ . During the the pulse the net mmf drop F in the core is  $N_d i_d - N_T i_\ell$  and hence from Eq. (1-8)

$$\dot{\phi}_{T} = \bar{\rho} (N_{d} i_{d} - N_{T} i_{\rho} - F_{0})$$

(1-11)

Current  $i_{\ell}$  is equal to  $e_T/R$ , where  $e_T = N_T \dot{\phi}_T$ . Hence

$$i_{\ell} = \frac{N_T \phi_T}{R}$$

(1-12)

Solution of the above two equations yields

$$\dot{\phi}_T = \overline{\rho} (N_d i_d - F_0) \frac{R}{R + N_T^2 \overline{\rho}}$$

(1-13)

and

$$i_{\ell} = \overline{\rho} (N_d i_d - F_0) \frac{N_T}{R + N_{\pi}^2 \overline{\rho}}$$

(1-14)

Note that the effect of the resistive loading is to reduce the rate of switching by the factor  $R/(R + N_T^{2\rho})$ , relative to the noload case. If  $R \to 0$ , then  $\dot{\phi}_T \to 0$ , and the core cannot be switched in finite time. For the case R = 0, there is in a sense no "receiver" in the coupling loop to accept any transmitter flux-linkage change  $N_T \Delta \phi_T$ . This is a useful interpretation that is worth pursuing further. By integration of Eq. (1-12) with respect to time, we have

$$N_T \Delta \phi_T = \int_0^t Ri_\ell dt = Rq_\ell$$

(1-15)

where  $q_{\ell}$  is the net electric charge flow in the loop. The quantity  $Rq_{\ell}$  may be viewed as an equivalent flux-linkage change  $N\Delta\phi = Rq_{\ell}$  absorbed by the resistance. It is sometimes useful to think of this process as "dissipation" of flux linkage, or alternatively as  $\Delta\phi$  dissipation of an amount  $Rq_{\ell}/N_T$ . When flux transfer from a transmitter core to a receiver core is considered in Chap. 2, dissipation of a  $\Delta\phi$  in the coupling-loop resistance will be found to be an

8

important loss term subtracting from the  $\Delta\phi$  otherwise available to the receiver core.

We could also derive Eqs. (1-13) and (1-14) by extending the equivalent circuit introduced in Fig. 1-3. Let Eq. (1-11) be rewritten in the form

$$e_{d} = N_{d} \dot{\phi}_{T} = \overline{\rho} N_{d}^{2} \left( i_{d} - \frac{F_{0}}{N_{d}} - \frac{N_{T}}{N_{d}} i_{\ell} \right)$$

(1-16)

The term  $N_T i_{\ell}/N_d$  is the only one not accounted for in the previous equivalent circuit, and it may be viewed as a current in the secondary of an ideal transformer of turns ratio  $N_d:N_T$ , as shown in Fig. 1-4. The ideal transformer and the load R may in turn be replaced by an equivalent resistance  $\left(N_d^2/N_T^2\right)R$ , and from this equivalent circuit Eqs. (1-13) and (1-14) can be derived directly.

Fig. 1-4. Equivalent circuit of a core driven by current  $i_d$  through  $N_d$  turns and loaded by resistance R across  $N_T$  turns.

For the simple flux-switching model assumed here, the circuit within the dashed boundary in Fig. 1-4 is valid regardless of the nature of the excitation and load at the terminals as long as  $F > F_0$  and  $|\phi| < \phi_r$ . In conventional transformer terms, the differential switching resistance  $N_d^{2\rho}$  is just a core-loss resistance (in ferrite cores, due primarily to internal damping effects rather than eddy currents). This loss element and the current sink of value  $F_0/N_d$  represent the departures from an ideal transformer. It should be emphasized once more that for quantitative analysis of core dynamics, it is necessary to make use of the more accurate flux-switching models described in Chap. 12.

#### 1-3 Inductive Load; $\Delta \phi$ Storage

Let us next consider the case where the transmitter core in Fig. 1-2 is loaded only by a linear inductance. The emf  $Ldi_{\rho}/dt$

induced in the load must be exactly balanced by the emf across the core, since we are assuming zero loop resistance. Hence

$$N_T \frac{d\phi_T}{dt} = L \frac{di_\ell}{dt}$$

(1-17)

or, by integration

$$N_T \Delta \phi_T = L \Delta i_{\theta} \tag{1-18}$$

Recalling that self-inductance is defined as the change in flux linkage per unit change of current in the same element, then  $L\Delta i_{\ell}$  is simply the change in flux linkage for a change  $\Delta i_{\ell}$  in loop current. This quantity represents all the flux linkage of the loop outside the core, including the contribution from wire inductance as well as any lumped inductance in the loop.

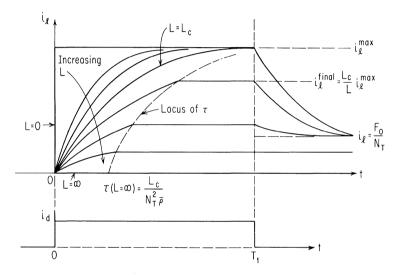

Assume now that the step  $i_d(t)$  current pulse causes the core to switch, given the initial conditions  $\phi = -\phi_r$  and  $i_{\ell} = 0$ . As flux switches, the load current  $i_{\ell}$  increases according to  $i_{\ell} = (N_T/L) \Delta \phi_T$ . But, in accordance with Eq. (1-11), as  $i_{\ell}$  increases, the rate of flux switching necessarily decreases. By substituting Eq. (1-11) into Eq. (1-17) we obtain

$$\frac{di_{\ell}}{dt} + \left(\frac{N_T^2 \overline{\rho}}{L}\right) i_{\ell} = \left(\frac{N_T \overline{\rho}}{L}\right) (N_d i_d - F_0)$$

(1-19)

Since  $i_d$  is constant during switching, Eq. (1-19) is simply a first-order linear differential equation whose solution is

$$i_{\ell} = \frac{N_d i_d - F_0}{N_T} \left( 1 - e^{-(N_T^2 \bar{\rho}/L)t} \right)$$

(1-20)

Thus, any changes in output current  $i_{\ell}$  are associated with an L/R time constant, where  $R = N_T^2 \overline{\rho}$  is the equivalent resistance of the core as viewed across the  $N_T$  turns.

Equation (1-20) is valid only so long as the core flux does not reach saturation. If  $\phi_T$  reaches the value  $+\phi_r$ , then  $\dot{\phi} = 0$  and we see from Eq. (1-18) that  $i_\ell$  remains constant at the value  $N_T (2\phi_r)/L$ . Otherwise, we see from Eq. (1-20) that  $i_\ell$  approaches the asymptotic value

$$i_{\ell}^{\max} = \frac{N_d i_d - F_0}{N_T}$$

(1-21)

and the net current linkage of the core is then equal to the threshold value  $F_{0}$ .

For a given amplitude of  $i_d$ , there exists a unique value of inductance  $L_c$  for which  $\Delta \phi_T$  approaches  $2\phi_r$  exactly in conjunction with  $i_\ell$  approaching the maximum value given by Eq. (1-21). For this value of inductance, in other words, the net mmf  $N_d i_d - N_T i_\ell$ drops toward threshold just as the core approaches positive saturation. From Eqs. (1-18) and (1-21) we have

$$\frac{N_T(2\phi_r)}{L_c} = \frac{N_d i_d - F_0}{N_T}$$

(1-22)

$\mathbf{or}$

$$L_{c} = \frac{N_{T}^{2}(2\phi_{r})}{N_{d}i_{d} - F_{0}}$$

(1-23)

For  $L < L_c$ , the loop current reaches it maximum value before the core saturates, and we see from Eqs. (1-18), (1-21), and (1-23) that

$$\Delta \phi_T^{\text{final}} = \frac{L}{L_c} (2\phi_r) \tag{1-24}$$

For  $L > L_c$ , the core saturates before the loop current reaches  $i_{\rho}^{\max}$ , and the final value of  $i_{\rho}$  is

$$i_{\ell}^{\text{final}} = \frac{L_c}{L} i_{\ell}^{\max}$$

(1-25)

For  $L > L_c$ , the time  $\tau$  that it takes for the core to saturate can be found by solving Eq. (1-20) for the time required for the current to build up to  $i_{\ell}^{\text{final}}$ . We find

$$e^{-(N_T^2\bar{\rho}/L)\tau} = 1 - \frac{L_c}{L}$$

(1-26)

$\mathbf{or}$

$$\tau = \frac{L}{N_T^{2\rho}} \ln\left(\frac{1}{1 - (L_c/L)}\right)$$

For  $L = \infty$ , (that is, for an open secondary), the simple result  $\tau = 2\phi_r/\overline{\rho}(N_d i_d - F_0)$  can be derived from Eqs. (1-26) and (1-23).

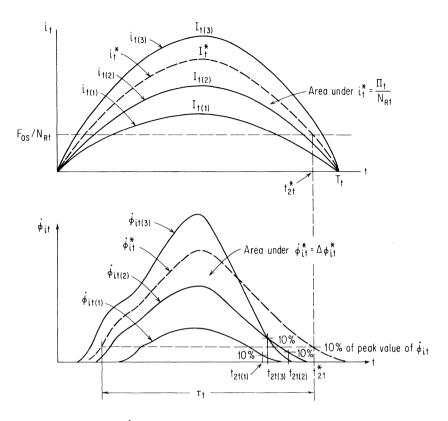

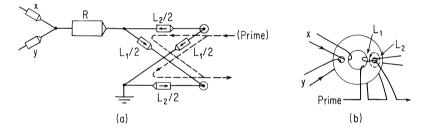

A family of curves of load current as a function of time, for a rectangular drive pulse of duration  $T_1$ , is shown in Fig. 1-5. Note that the load current is in a direction tending to switch the core back toward  $-\phi_r$ . If  $i_l > F_0/N_T$  at  $t = T_1$ , then for  $t > T_1$ ,  $i_l$  decays towards a final value of  $F_0/N_T$  with the same time constant  $L/N_T^{2\bar{\rho}}$  found in Eq. (1-20). As a result, the core switches back by the amount  $(L/N_T)[i_l - (F_0/N_T)]$ , and the net flux change is  $LF_0/N_T^2$ , in agreement with Eq. (1-18).

Fig. 1-5. Loop current  $i_l$  as a function of time in the circuit of Fig. 1-2 with an inductive load.

It is very useful to consider the notion of a flux-linkage change  $Li_{\ell}$ , or flux change  $\Delta \phi = Li_{\ell}/N_T$ , as being "stored" in the inductance. This is based on the observation that the inductor can actually drive the core, returning some flux linkage to it (the inductance being the transmitter in this case), provided the loop current exceeds the core threshold  $F_0/N_T$  after the drive  $i_d$  terminates. However, in any actual circuit where loop resistance is not zero,  $\Delta \phi$  storage in inductance can only be temporary, since any flux linkage not returned to the transmitter core is eventually dissipated in the resistance.

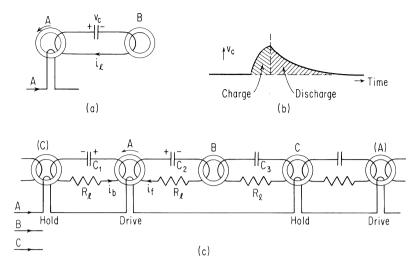

#### 1-4 Capacitive Load; $\Delta \phi$ Transformation

The effects of capacitive loading are qualitatively different from those for inductive loading, although one might correctly

#### ELEMENTARY CIRCUITS

guess that there is an RC time constant associated with the load current, where  $R = N_T^2 \overline{\rho}$  is again the switching resistance of the core, as viewed from the capacitor.

Consider the circuit of Fig. 1-2 with only the capacitor attached. Assuming that the capacitor is not charged initially, the voltage across the core winding must also be zero initially, implying a starting value of load current  $i_{\ell} = (N_d i_d - F_0)/N_T$ . As the capacitor charges and its voltage increases, the load current must decrease to permit the core to switch correspondingly faster. The equation of voltage buildup can be obtained as follows. Substitution of the relations  $i_{\ell} = C dv_C/dt$  and  $v_C = e_T = N_T \dot{\phi}_T$  into Eq. (1-11) results in

$$\frac{dv_C}{dt} + \frac{v_C}{RC} = \frac{\overline{\rho}N_T(N_d i_d - F_0)}{RC}$$

(1-27)

with the solution

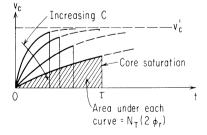

$$v_C = \bar{\rho} N_T (N_d i_d - F_0) (1 - e^{-t/RC})$$

(1-28)

where  $R = N_T^2 \overline{\rho}$ . A family of curves of  $v_C$  versus t, with C as a parameter, is shown in Fig. 1-6. Note that all curves tend to build to the same asymptotic value of voltage,  $v'_C = \overline{\rho} N_T (N_d i_d - F_0)$ . This is not surprising, for if the core did not saturate, equilibrium would finally be reached with zero load current and a constant output voltage  $v'_C = N_T \dot{\phi}_T$  whose value would depend only on the drive strength. Thus, with a capacitive load, a switching voltage  $N_T \dot{\phi}_T$  can be sustained without any load current  $i_\ell$ , whereas with an R or L load, a nonzero value of  $\dot{\phi}$  is not possible unless a loop current  $i_\ell$  is flowing (and changing in the latter case).

Fig. 1-6. Output voltage  $v_C$  as a function of time in the circuit of Fig. 1-2 with a capacitive load.

Integrating Eq. (1-28) in order to find the flux change, we obtain

$$N_T \Delta \phi_T \doteq \int_0^t v_C \, dt = v'_C \, RC \left[ \frac{t}{RC} - (1 - e^{-t/RC}) \right]$$

(1-29)

From this equation we see that flux switched in the core increases monotonically with time until the core saturates. Saturation occurs at a time found by substituting  $\Delta\phi_T = 2\phi_r$  into Eq. (1-29). When the core saturates at  $+\phi_r$ , the switching resistance of the core drops to zero, and the capacitor discharges rapidly, the discharge current driving the core still further into positive saturation. There is, of course, an abrupt drop in voltage when saturation is reached, as indicated in the family of curves of Fig. 1-6. (In actual practice, there would be a damped oscillation after saturation is reached because of the saturation inductance of the core and the parasitic inductance and resistance of the coupling loop.) The areas under the curves in Fig. 1-6 are clearly identical, since each curve represents the same magnitude of flux switching, namely,  $2\phi_r$ .

Here we must note a very important difference between capacitive and inductive loading. An inductive load tends to maintain the load current in the same direction after termination of drive, whereas the capacitive discharge current is opposite to that of the initial charging current. Thus, whereas the inductor discharge current tends to switch the core back toward its original state, the capacitive discharge current tends to keep the core switching in the *same* direction as originally (see the examples in Fig. 12-30).

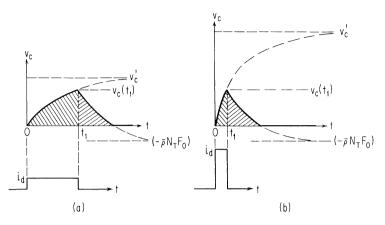

Let us finally consider the case of terminating the drive current before saturation is reached, at time  $t_1$  in Fig. 1-7. From the arguments above, the capacitor discharge current will keep the core switching in the same direction for some time. The pertinent equation in this case is

$$\frac{dv_C}{dt} + \frac{v_C}{RC} = -\frac{\overline{\rho}N_TF_0}{RC}$$

(1-30)

with the solution

$$v_{C} = v_{C}(t_{1})e^{-t/RC} - \overline{\rho}N_{T}F_{0}(1 - e^{-t/RC})$$

(1-31)

where again  $R = N_T^2 \overline{\rho}$ , and  $v_C(t_1)$  is the value of voltage reached when the drive is terminated. A typical response curve is shown in Fig. 1-7(a).

Fig. 1-7. Changing the ratio of flux switched during the drive pulse to that switched after the drive pulse from >1 in (a) to <1 in (b), by varying the magnitude of  $i_{d}$ .

An important observation is that the magnitude of flux switched subsequent to drive termination can actually be *larger* than that switched by the drive itself. We can see this from the following argument. With a stronger drive, the voltage builds towards a higher asymptotic value, and therefore the capacitor can be charged to the same value in shorter time. Thus, the area under the buildup portion of the curve can, in principle, be made vanishingly small, although the curve during discharge is totally unaffected by the initial drive strength. For example, compare the curves of Fig. 1-7(a) and (b). In the limit of very strong drive, we have the possibility of charging the capacitor to any specified voltage with a negligible amount of core flux being switched.

A capacitor thus offers an interesting capability of  $\Delta\phi$  transformation, the capacitor being able to deliver to the core more, or less, flux linkage than the core delivers to the capacitor during the charging phase. There is nothing particularly mysterious about this, since there are no basic constraints on the integral of capacitor voltage, even though the voltage itself is unique for any particular charge state. Similarly, in the case of an inductor, the current is fixed for any given flux-linkage state, but there is no basic constraint on the integral of current, i.e., on charge.

#### 1-5 Summary

Using a very simple core model, we have treated separately the cases of core switching with resistive, inductive, and capacitive

loads. With a resistive load, the loop current is simply proportional to  $\dot{\phi}$ , and flows, therefore, only so long as flux is switching (the flux switching is dissipative). With an inductive load, the loop current is directly proportional to the magnitude of flux change  $\Delta \phi$  and this we interpret simply as flux-linkage storage. in the sense that the same magnitude of flux linkage in the core is. so to speak, regenerated in the linear inductance. We are able to define an L/R time constant, where R is the equivalent resistance of the switching core as viewed from the coupling loop winding. With a capacitive load. we find an RC time constant, where R is the same as in the inductive case, and steady state is reached when the voltage generated in the core winding exactly equals that across the capacitor, and no loop current flows. In this case, the magnitude of equivalent flux linkage stored in the capacitor during charge can be less than, equal to, or greater than the flux linkage subsequently delivered from the capacitor during discharge. This is an important property interpreted as  $\Delta \phi$  transformation.

This simplified treatment is of little value in quantitative prediction, and is primarily for developing insight into manipulation of flux change as a signal parameter. It should be intuitively clear that the ability to dissipate, store, and transform this parameter is important in circuit synthesis. Quantitative analysis of core switching with various sorts of loads, using a better engineering model for the core, is treated in Sec. 12-6.

## COUPLED PAIR OF CORES; ∆¢ TRANSFER

| 2-1 | Flux Transfer Ratio G                                 |

|-----|-------------------------------------------------------|

| 2-2 | Requirement on Turns Ratio for $G > 1$                |

| 2-3 | Limit on Loop Resistance                              |

| 2-4 | Effect on G of Transmitter and Receiver Thresholds 21 |

| 2-5 | Effect on G of Coupling-Loop Inductance               |

| 2-6 | Effect on G of Receiver Loading                       |

| 2-7 | Flux Pumping                                          |

| 2-8 | Direct-Current Drive; Implicit Phasing                |

| 2-9 | Summary                                               |

In the previous chapter we saw that loading a core with a resistance, an inductance, or a capacitance results in  $\Delta\phi$  dissipation, storage, or transformation, respectively. Now let us consider loading a core with another core, in which case we have the possibility of  $\Delta\phi$  transfer, i.e., transmission of flux from a transmitter core to a receiver core.

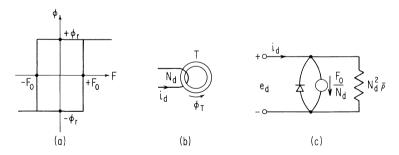

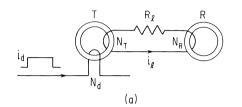

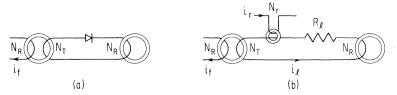

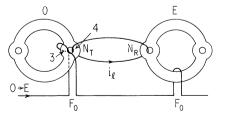

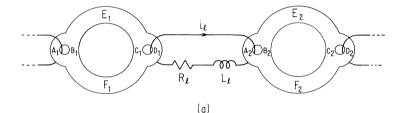

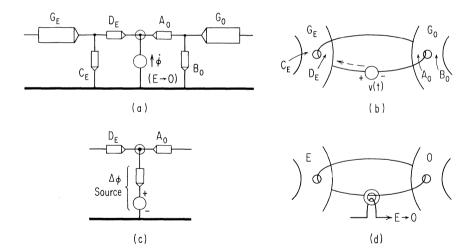

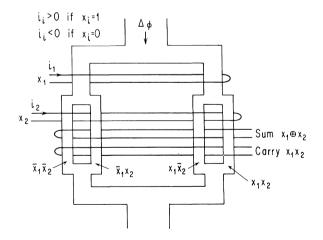

#### 2-1 Flux Transfer Ratio G

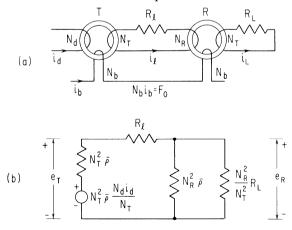

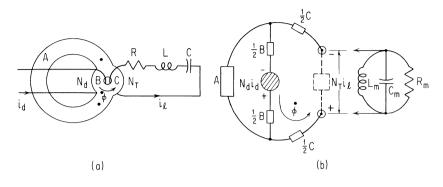

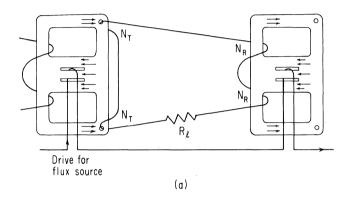

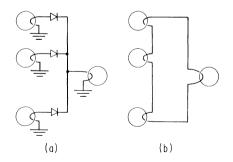

The flux transfer takes place through an electrical coupling loop which is assumed for the moment to be purely resistive (Fig. 2-1(a)). For such a coupled pair of cores, we are generally concerned with the  $\Delta\phi$  transfer ratio

$$G(\Delta \phi_T) = \frac{\Delta \phi_R}{\Delta \phi_T}$$

(2-1)

<u>م</u> ب

2

where  $\Delta \phi_R$  and  $\Delta \phi_T$  are the flux changes in the receiver and transmitter, respectively. In contrast with conventional electronic circuits, the appropriate signal parameter here is  $\Delta \phi$ , rather than voltage or current, and of special concern are the conditions for achieving a transfer ratio G > 1.

(b)

Fig. 2-1. Flux transfer from Transmitter Core T to Receiver Core R.

Assume that each of the coupled cores starts in the  $-\phi_r$  flux state and switches towards the  $+\phi_r$  state, as governed by the fluxswitching model of Eq. (1-8). A transmitter drive pulse  $i_d$  of constant magnitude is also assumed. Under these assumptions, the rates of change of flux  $\dot{\phi}_T$  and  $\dot{\phi}_R$  are independent of time (as long as neither core reaches positive saturation), and the transfer ratio *G* is simply equal to the ratio of switching rates, or

$$G = \frac{\Delta \phi_R}{\Delta \phi_T} = \frac{\dot{\phi}_R}{\dot{\phi}_T}$$

(2-2)

#### COUPLED PAIR OF CORES; $\Delta\phi$ TRANSFER

In this chapter we are primarily concerned with the general effects on the transfer ratio of turns ratio, loop impedance, receiver threshold, and receiver loading resistance.

#### 2-2 Requirement on Turns Ratio for G > 1

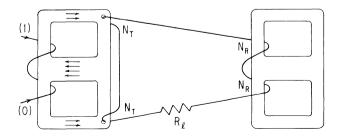

In the circuit of Fig. 2-1(a), the coupling loop is assumed to have a resistance  $R_{\ell}$ , but negligible inductance. Equating the net emf around the loop to the voltage drop in  $R_{\ell}$ , we have

$$N_T \dot{\phi}_T - N_R \dot{\phi}_R = R_\ell i_\ell \tag{2-3}$$

Integrating each term with respect to time, and rearranging, we obtain

$$N_T \Delta \phi_T = N_R \Delta \phi_R + R_\ell q_\ell \tag{2-4}$$

where  $q_{\ell} = \int_0^t i_{\ell} dt$ . This equation is similar to Eq. (1-15) for resistive loading except that of the transmitted flux linkage here, only part, namely,  $R_{\ell}q_{\ell}$ , is dissipated as a loss in  $R_{\ell}$ , and the remainder  $N_R \Delta \phi_R$  reaches the receiver core.

Based on Eqs. (2-1) and (2-4), we may write

$$G = \frac{N_T}{N_R} - \frac{R_\ell q_\ell}{N_R \Delta \phi_T} = n \left( 1 - \frac{R_\ell q_\ell}{N_T \Delta \phi_T} \right)$$

(2-5)

where *n* is the turns ratio  $N_T/N_R$ . Thus, despite the inevitable loss of flux linkage during transfer, transfer gain G > 1 is nevertheless possible if n > 1 by an amount sufficient to overcome the effect of the subtractive term  $R_{\ell}q_{\ell}/N_T\Delta\phi_T$ . Note that this term is just the ratio of dissipated flux linkage to transmitted flux linkage.

#### 2-3 Limit on Loop Resistance

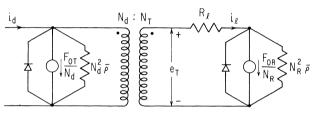

Let us now assume that n > 1 and consider how large  $R_{\ell}$  can be while maintaining  $G \ge 1$ . Based on our simple model, the circuit of Fig. 2-1(a) may be represented by the equivalent circuit shown in Fig. 2-1(b). The cores are assumed identical, with the same  $\bar{\rho}$  and the same threshold value  $F_0 = F_{0T} = F_{0R}$ , though the latter symbols are kept distinct for the purpose of discussing transmitter and receiver thresholds separately.

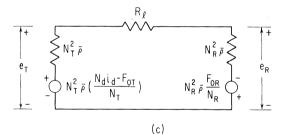

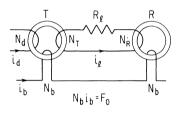

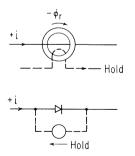

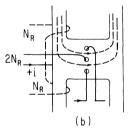

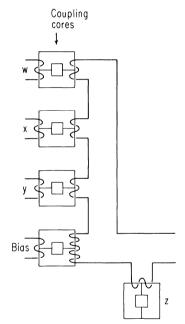

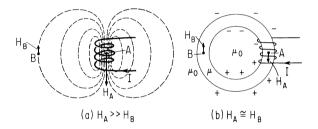

Assuming that the drive current  $i_d$  is large enough to make  $N_{R}i_{\ell} \geq F_{0R}$ , the diodes in the core model are nonconducting and may be neglected. Then with current generators transformed to equivalent voltage generators, and all quantities referred to the transformer secondary, we obtain the equivalent circuit of Fig. 2-1(c) where  $e_T = N_T \dot{\phi}_T$  and  $e_R = N_R \dot{\phi}_R$ . Under the specified condition of  $G \ge 1$ , it is clear that the highest upper limit on loop resistance is obtained when the effective receiver threshold is equal to zero. This condition can be approached with strong driving so that  $N_d i_d \gg F_0$ . Alternately, the receiver threshold can be effectively reduced by applying a bias mmf  $N_b i_b = F_0$ , as shown applied to both cores in Fig. 2-2. The term bias is used in the usual electrical engineering sense of determining an operating point, the bias signal by itself nominally not causing any flux switching. It may be either a dc bias or a constant-amplitude pulse synchronized with the current  $i_d$ .

Fig. 2-2. Use of a bias mmf to overcome the switching thresholds of transmitter and receiver.

With the transmitter and receiver each biased to threshold, that is, with  $N_b i_b = F_0$ , we simply have

$$\dot{\phi}_R = \overline{\rho} N_R i_{\ell} \qquad (2-6)$$

and

$$\dot{\phi}_T = \overline{\rho} (N_d i_d - N_T i_{\ell}) \qquad (2-7)$$

Equations (2-6) and (2-3) may be solved for G in the form

$$G = \frac{\dot{\phi}_R}{\dot{\phi}_T} = n \frac{N_R^2 \overline{\rho}}{R_\ell + N_R^2 \overline{\rho}}$$

(2-8)

This result is also clear from the equivalent circuit of Fig. 2-1(c), where, with receiver threshold cancelled out, the emf ratio  $e_R/e_T = N_R \dot{\phi}_R/N_T \dot{\phi}_T$  is readily seen to be equal to  $N_R^2 \bar{\rho} / (R_\ell + N_R^2 \bar{\rho})$ .

The above results may be interpreted as follows: of the total flux linkage  $N_T \Delta \phi_T$  injected into the loop, a fraction G/n reaches the receiver core, and the remaining portion 1 - G/n is lost by dissipation in  $R_\ell$ . The exact division of transmitted flux linkage is generally very dependent on drive magnitude  $N_d i_d$ , and is independent of drive here only because of our assuming idealized core properties and the biasing of the receiver core exactly to threshold.

#### COUPLED PAIR OF CORES; $\hat{\Delta}\phi$ TRANSFER

Based on the requirement that  $G \ge 1$ , we obtain directly from Eq. (2-8) an upper limit on  $R_{\ell}$ , namely

$$R_{\boldsymbol{\rho}} \leq (n-1)N_{\boldsymbol{B}}^{2}\overline{\boldsymbol{\rho}} \tag{2-9}$$

from which we see that there is no limit on the ratio  $R_{\ell}/N_R^{2}\overline{\rho}$  so long as *n* can be made arbitrarily large. But by rewriting Eq. (2-9) in terms of transmitter resistance  $N_T^{2}\overline{\rho}$ , we find

$$R_{\ell} \leq \left(\frac{n-1}{n^2}\right) N_T^{2\overline{\rho}} \tag{2-10}$$

and thus see that the upper limit on  $R_{\ell}/N_T^{2\rho}$  is 1/4, which is obtained with a two-to-one turns ratio (n = 2), in which case  $N_R^{2\rho} = R_{\ell}$ . In other words, for  $G \ge 1$  the loop resistance can never be more than 1/4 the transmitter resistance.

There are many other important factors relevant to choice of coupling-loop turns ratio. The simple result here is most likely to be significant where there is practical difficulty in constructing a low-resistance coupling loop. In that case, it may be helpful to specify  $N_T/N_R = 2$  in order to allow as large a value of  $R_\ell$  as possible relative to  $N_T^{2\rho}$ .

#### 2-4 Effect on G of Transmitter and Receiver Thresholds

It is not always possible, or even desirable, to eliminate the core thresholds by bias, so it is necessary to understand the effects of threshold on the transfer ratio. Let us consider the case of constant drive and no biasing at all. From the equivalent circuit of Fig. 2-1(c), we can write

$$i_{\ell} = \frac{N_T^{2\bar{\rho}} \left[ (N_d i_d - F_{0T}) / N_T \right] + N_R^{2\bar{\rho}} (F_{0R} / N_R)}{N_T^{2\bar{\rho}} + R_{\ell} + N_R^{2\bar{\rho}}}$$

(2-11)

and

$$e_T = N_T \dot{\phi}_T = N_T^2 \overline{\rho} \left( \frac{N_d i_d - F_{0T}}{N_T} - i_\ell \right)$$

(2-12)

For substitution into Eq. (2-5), we obtain the ratio

$$\frac{R_{\ell}q_{\ell}}{N_{T}\Delta\phi_{T}} = \frac{R_{\ell}\int_{0}^{t}i_{\ell}dt}{N_{T}\int_{0}^{t}\dot{\phi}_{T}dt} = \frac{R_{\ell}i_{\ell}}{N_{T}\dot{\phi}_{T}}$$

(2-13)

Substitution of this ratio, as evaluated from Eqs. (2-11) and (2-12), into Eq. (2-5) yields

$$G = n \left( \frac{n N_R^2 \overline{\rho} (N_d i_d - F_{0T}) - (R_{\ell} + N_T^2 \overline{\rho}) F_{0R}}{n (R_{\ell} + N_R^2 \overline{\rho}) (N_d i_d - F_{0T}) - N_T^2 \overline{\rho} F_{0R}} \right)$$

(2-14)

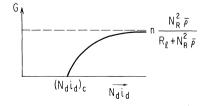

Equation (2-14) is valid only if  $N_d i_d$  is large enough that  $N_R i_l \ge F_{0R}$ . The limiting condition G = 0, corresponding to  $N_R i_l = F_{0R}$ , is obtained when  $N_d i_d$  has the critical value

$$(N_{d}i_{d})_{c} = F_{0T} + n\left(1 + \frac{R_{\ell}}{N_{T}^{2\overline{\rho}}}\right)F_{0R}$$

(2-15)

For any lower value of drive, G = 0 also.

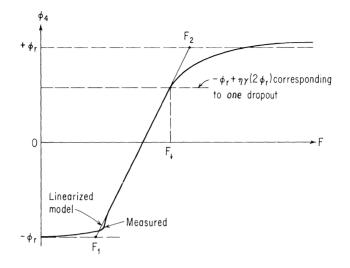

The form of G as a function of  $N_d i_d$  has been sketched in Fig. 2-3. Note that for  $N_d i_d \gg (N_d i_d)_c$ , G approaches asymptotically the value given by Eq. (2-8), since the threshold terms become relatively insignificant. Also note that if we view  $F_{0T}$  and  $F_{0R}$  as the effective thresholds, then for the previous case of receiver biasing, that is,  $F_{0R} = 0$ , Eq. (2-14) again reduces to Eq. (2-8). In this case, the transmitter threshold has no effect on the transfer ratio G, although the individual rates of switching are lower than they would be if  $F_{0T}$  were zero also. In fact, from Eq. (2-14) we see that the effect of nonzero  $F_{0T}$  on G may always be overcome simply by increasing  $N_d i_d$  by the amount  $F_{0T}$ , which is equivalent to biasing the transmitter. The effect of nonzero  $F_{0R}$  in reducing G,

Fig. 2-3. Sketch of flux-transfer ratio as a function of drive strength, from Eq. (2-14).

22

however, cannot be completely overcome with any finite value of  $N_d i_d \boldsymbol{.}$

#### 2-5 Effect on G of Coupling-Loop Inductance

The control of coupling-loop inductance  $L_{\ell}$  is often as important as the control of the resistance  $R_{\ell}$ . When  $L_{\ell}$  is taken into account, the values of  $i_{\ell}$  and  $\phi$  are no longer constant in time. Omitting detailed analysis here, it can be reasoned that storage of the flux linkage  $L_{\ell}i_{\ell}$  in  $L_{\ell}$  is at least a temporary flux loss en route to the receiver. Furthermore, if the receiver stops switching at time  $T_S$ (whether due to saturation or to lack of sufficient mmf), then a flux linkage equal to  $L_{\ell}i_{\ell}(T_S)$  is left stored in  $L_{\ell}$ , and this is transformed into a permanent flux-linkage loss dissipated in  $R_{\ell}$  as  $i_{\ell}$  decays exponentially.

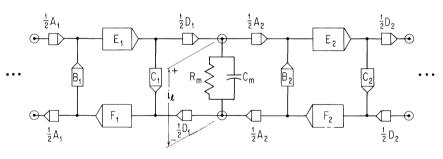

#### 2-6 Effect on G of Receiver Loading

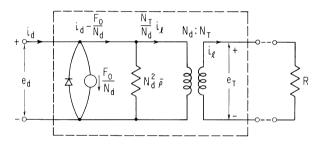

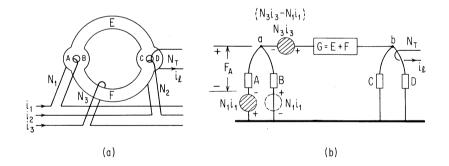

For the circuit of Fig. 2-2, we say that  $G \ge 1$  can be obtained for any value of  $R_{\ell}$  by making the turns ratio *n* sufficiently large. However, if the receiver is also loaded, it may not be possible to obtain  $G \ge 1$  for any value of *n*. Consider, for example, the case in Fig. 2-4(a), where the secondary winding of the receiver contains the same number of turns  $N_T$  as that of the transmitter. For

Fig. 2-4. Loading the receiver with resistance  $R_L$  through a winding of  $N_T$  turns.

the special case of  $R_L = R_{\ell}$ , this circuit may be viewed as deriving from an iterative core circuit in which the next core in the chain beyond Core R is in some manner prevented from switching.

For simplicity of analysis, and in order to minimize the effect of receiver loading, both cores are again assumed biased to threshold. The equivalent circuit of Fig. 2-1(c) may then be expanded to include the load by connecting  $R_L$  as shown in Fig. 2-4(b). Solving for the ratio  $e_R/e_T$  from this circuit and noting that

$$G = \frac{\phi_R}{\dot{\phi}_T} = \frac{e_R/N_R}{e_T/N_T}$$

we obtain

$$G = \frac{n}{n^2 (R_{\ell}/R_L) + (R_{\ell}/N_R^2 \overline{\rho}) + 1}$$

(2-16)

For the case of equal loop resistances  $R_L = R_\ell$ , Eq. (2-16) reduces to

$$G(n, R_{\ell}) = \frac{n}{n^2 + (R_{\ell}/N_{P}^{-2}\overline{\rho}) + 1}$$

(2-17)

With respect to  $R_{\ell}$ , the largest value of G,

$$G(n) = \frac{n}{n^2 + 1}$$

(2-18)

is obtained as  $R_{\ell}/N_R^2 \overline{\rho} \to 0$ , and maximization of Eq. (2-18) with respect to the turns ratio  $n = N_T/N_R$  yields

$$G_{\max} = \frac{1}{2}$$

(2-19)

for n = 1. Thus, with  $R_L = R_{\ell}$  it is not only impossible to achieve  $G \ge 1$  with a large turns ratio, but rather n = 1 results in the highest possible value of G. Furthermore, with  $R_L = R_{\ell}$ , we obtain the highest gain not by making  $R_L$  large, but rather for the heaviest possible receiver loading, i.e., as  $R_L \to 0$ . The latter result merely means that G is more affected by the coupling-loop resistance than by the loading resistance.

Since  $G \ge 1$  cannot be obtained for  $R_L = R_\ell$ , let us derive the minimum value of  $R_L/R_\ell$  for which the condition G = 1 can be

achieved. To emphasize the  $R_{\ell}/R_L$  dependence, let us assume that  $R_{\ell}$  is already small compared with  $N_R^{-2\rho}$  so that Eq. (2-16) becomes

$$G = \frac{n}{n^2 (R_{\ell}/R_L) + 1}$$

(2-20)

Hence, for  $G \geq 1$

$$\frac{R_L}{R_{\ell}} \geq \frac{n^2}{n-1}$$

For G = 1, the minimum value

$$\frac{R_L}{R_{\rho}} = 4$$

(2-21)

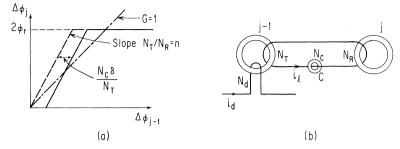

is obtained for turns ratio n = 2. Thus, with all conditions idealized, it is necessary to have loading resistance at least four times the loop resistance to obtain  $G \ge 1$ . This result has considerable significance in connection with the iterative core circuits that we shall treat, beginning in the next chapter.

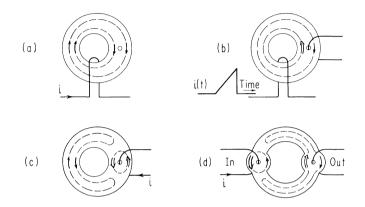

#### 2-7 Flux Pumping

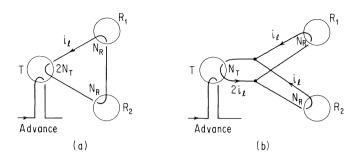

The use of a turns ratio greater than unity could be viewed as the gain mechanism for achieving  $G \ge 1$  in the manner shown in the previous sections. We will later describe other gain mechanisms by which it is possible to achieve G > 1 even in cases where  $N_T/N_R \le 1$ . To illustrate this possibility, let us show here that by the use of multiple transfers we can "pump" the receiver to a fully switched condition even when the transfer ratio is less than unity on any single transfer.

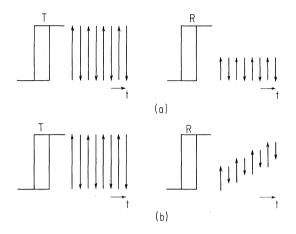

In the circuit of Fig. 2-4(a), suppose that both cores are initially in negative remanence and that we apply a symmetrical pattern of positive and negative currents that drive the transmitter repeatedly between  $-\phi_r$  and  $+\phi_r$ . With G < 1, the receiver will then be driven repeatedly between  $-\phi_r$  and some flux level lower than  $+\phi_r$ . The resulting history is sketched in Fig. 2-5(a). With a suitable asymmetry, however, so that the receiver switches less flux in the negative-going direction, the operating level in the receiver approaches closer and closer to positive saturation, as suggested in Fig. 2-5(b). In other words, we can ultimately achieve a net gain  $(G \ge 1)$  relative to the  $\Delta \phi_T$  transmitted during a single transfer. This is true even if the receiver is heavily loaded with a value of  $R_{I_c} < R_{f}$ .

Fig. 2-5. Illustrating symmetrical switching cycles in (a), and showing receiver pumping effect with asymmetrical switching cycles in (b).

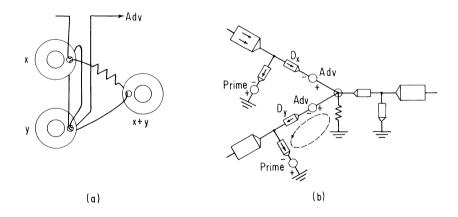

As shown by Eq. (2-14), G is a function of drive strength as long as the receiver threshold is nonzero. Hence, suitable asymmetry could be achieved merely by using different drive strengths in the two directions of switching, as in Fig. 2-6(a). A different method is shown in Fig. 2-6(b), where a dc receiver bias aids the loop current in the positive switching direction, but opposes it in the negative switching direction.

**Fig. 2-6.** Two different ways to apply dc bias to achieve asymmetrical switching in (a, b); pumping a single transmitter to fully switch a number of identical receiver cores in (c).

If a number of receiver cores are linked by the loop, as in Fig. 2-6(c), all could be pumped to a fully switched level with a

sufficient number of cycles. By doubling the number of pumping cycles, i.e., by doubling the time, we can double the net gain. This becomes a "gain-bandwidth" problem for digital transfer (Chap. 3), since the maximum bit rate is inversely proportional to transfer time. Even within a single cycle there is a gain-bandwidth relation. Net gain per cycle could be increased if the amount of flux switched back during the negative half cycle were reduced. In the limit, if loop current magnitude during the negative half cycle were below the effective receiver threshold, no receiver flux would switch back at all. In this case, the loop resistance would dissipate the entire flux linkage  $N_T(-2\phi_r)$  injected by the transmitter, and the time for this operation would be correspondingly increased. We will see that this is an important mode of circuit operation, i.e., a transmitter slowly dissipating a flux-linkage change in loop resistance.

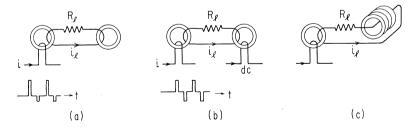

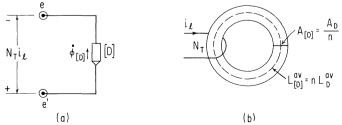

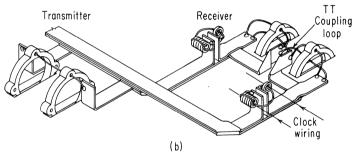

## 2-8 Direct-Current Drive; Implicit Phasing

A dc mmf less than threshold can serve as a bias source in the conventional sense of setting an operating point. A dc mmf greater than threshold can cause significant switching, however, and therefore act as a driver. For example, in Fig. 2-7 a negative dc mmf

normally holds the first core in saturation. Upon application of a positive pulse large enough to overcome the dc mmf plus the core threshold, the first core can be switched to positive saturation, and flux is transmitted to the second core. Upon termination of the pulse, the dc mmf drives the first core back to its original condition. If the dc drive is less than the net positive drive, then with repeated application of the drive pulse, the second core can be pumped as shown in Fig. 2-5(b).

Fig. 2-7. Two-phase operation with a single pulse source and a dc mmf large enough to switch the core back to its original state.

With a dc mmf just slightly above threshold, the first core switches back slowly, and essentially all flux linkage is dissipated in loop resistance during the negative half cycle.

We see that it is possible to have more phases of circuit operation than there are explicit pulse drivers. We can think of the circuit of Fig. 2-7 as having a two-phase nature though only one clock-pulse is needed, the second phase being achieved implicitly. The use of dc current for this purpose is not only practical but often results in considerably simplified driver systems.

There are two points to note about dc current sources in this type of application. First, there cannot be any *net* energy exchange between the dc current source and any core linked by this source. Starting at time t = 0, the net energy transferred from the current source  $I_{dc}$  to the core of Fig. 2-7 can be expressed simply as

$$W = \int_{t=0}^{t} I_{dc} e dt = I_{dc} \int_{t=0}^{t} N \frac{d\phi}{dt} dt = I_{dc} N (\phi_f - \phi_i) = I_{dc} N \Delta \phi$$

where *e* is the induced emf in the winding, and  $\phi_f$  and  $\phi_i$  are the final and initial values of the flux, respectively. Thus, there is as much energy delivered from the current source during one polarity of flux change as is delivered back to the source during the opposite polarity of flux change. After each complete cycle of switching,  $\phi_f = \phi_i$ , or  $\Delta \phi = 0$ , and there is no net exchange of energy, no matter how complex the circuitry attached to the core.

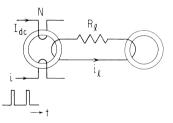

Fig. 2-8. Use of a series inductance to stabilize a dc current source of magnitude  $I_{dc} = V/R$ .

A current source is often synthesized with a large voltage source V and large series resitance R(where V/R is the desired current), V being large compared to the largest expected voltage drop in the driven circuitry. However, the power lost in the series resistance makes

this type of current source very inefficient. A large improvement can generally be achieved by incorporating an inductance in series with the load. Thus, for a relatively large L in Fig 2-8, a fluxlinkage change  $\sum N_i \Delta \phi_i$  across the core circuit can be absorbed, or balanced, by a current change on the order of  $\Delta I \approx \sum N_i \Delta \phi_i/L$ , which can be made arbitrarily small with a large inductance. This is similar to the result in Eq. (1-18) where a change in flux linkage results in a certain change in loop current that subsequently decays with a time constant L/R, where R is the circuit resitance. The use of a series inductance often simplifies the dc-source design and permits the use of much smaller values of V and R than would otherwise be possible. This technique is particularly useful for magnetic-core circuits that are cyclically operated because of the bipolar nature of the load voltages. With unipolar loads, it would be necessary to delay a certain number of L/R time constants

## COUPLED PAIR OF CORES; $\Delta \phi$ TRANSFER

between switching operations in order to prevent cumulative current changes.

## 2-9 Summary

In this chapter we have treated specifically the case of a second core acting as a load on a first core. Primary interest is in the flux transfer ratio G, the ratio of flux change in the receiving core to the flux change in the transmitting core, and more particularly, in achieving transfer ratios greater than unity, i.e., actual signal gain. An important method for achieving G > 1 is to use a turns ratio greater than unity in the coupling loop between transmitter and receiver. We make some basic observations on the effect on the gain of various circuit and device parameters such as loop resistance, loading resistance, and the static thresholds of the transmitter and receiver elements. In particular, maximum limits on loop resistance and load resistance are derived for the condition  $G \ge 1$ . Another gain mechanism, namely, flux pumping, is also considered, although this is mainly of academic interest. Finally, we consider the practically important case of core switching with a dc current, which, upon termination of a switching pulse, automatically restores the core to its original state.

# DIGITAL TRANSFER IN ITERATIVE CORE CIRCUITS

| 3-1 | Binary Shift Register                             | 31  |

|-----|---------------------------------------------------|-----|

| 3-2 | Digital Transfer                                  | 32  |

|     | $\Delta \phi$ Gain Requirements                   | 33  |

|     | Drive-Current Tolerances                          | \$4 |

| 3-3 | Gain and Loss Mechanisms                          | 5   |

| 3-4 | Forward Decoupling in a Magnetic Chain 3          | 37  |

| 3-5 | Backward Isolation; Core-Diode Transfer Schemes 3 | 38  |

| 3-6 | Transfer Schemes Using Capacitance 4              | 1   |

|     | Core-Capacitor Scheme                             | 1   |

|     | Core-Diode-Capacitor Scheme 4                     | 3   |

| 3-7 | Summary                                           | 4   |

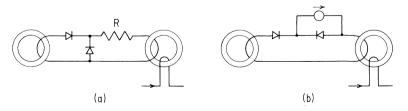

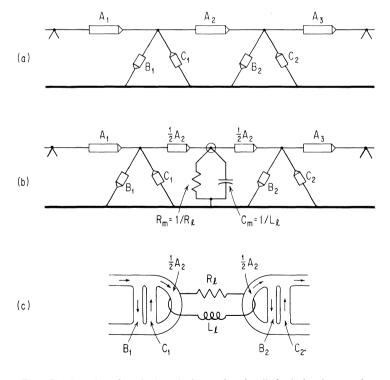

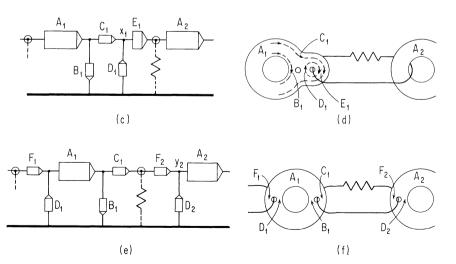

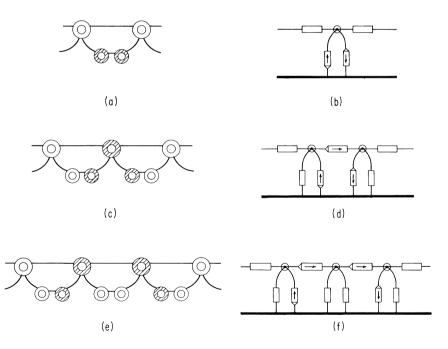

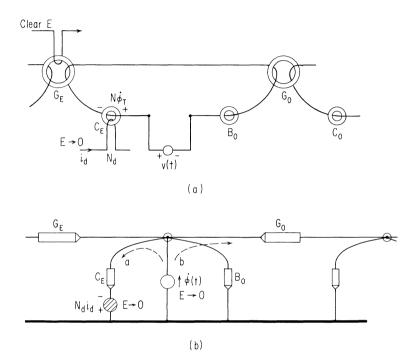

We wish now to consider some of the basic requirements for synthesizing digital transfer systems. In particular, we will show how cores and diodes, or alternately cores and capacitors, can be used in combination to achieve circuits for digital transfer. Since core-diode circuits are discussed in detail elsewhere, for example, by Meyerhoff (1960), their treatment in this book is limited to the material of this section. Discussion of core-capacitor schemes is also limited to this section, since such circuits are mainly of academic interest and in any case are outside the primary interest of this book. It is considered worthwhile to introduce these schemes before starting the treatment of core-wire schemes in order to develop insight into  $\Delta \phi$  gain and loss mechanisms, and into methods for achieving isolation between various parts of a magnetic core circuit. Diodes are obvious devices for achieving isolation, and it is therefore easy to illustrate the principles of digital transfer with core-diode circuits. In Chap. 4 we will use certain of these

3

core-diode schemes as an introduction to the general synthesis of core-wire schemes.

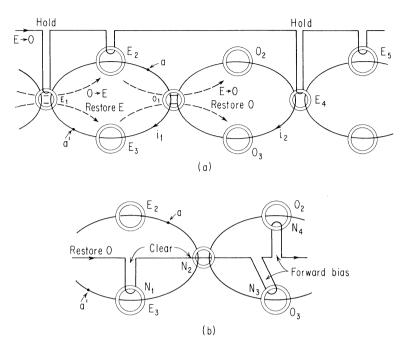

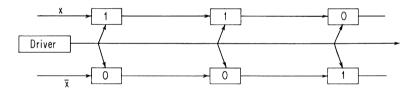

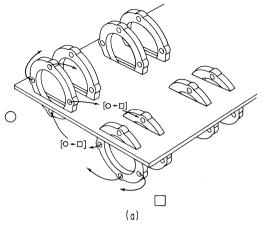

## 3-1 Binary Shift Register

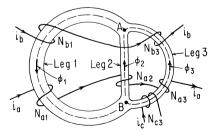

A general logic network is a highly interconnected network of digital circuits through which binary variables can be stably transmitted. If we follow any one path of the network, we find many other paths merging with it (fan-in), and other paths branching off from it (fan-out). To simplify the study of digital transmission, it is convenient to concentrate on just the requirements for stable storage and transfer of binary variables along a simple path with no side branches, i.e., a common binary shift register. If a particular circuit scheme can be used to build a shift register, then the basic scheme can almost invariably be expanded for general logic realization. Thus, we can profitably evaluate and compare schemes on the basis of shift register synthesis alone, without becoming much involved in general logic techniques.

A binary shift register is basically a chain of storage elements, such as flip-flops or magnetic cores, so interconnected that the stored binary pattern can be shifted along the chain. The chain may be arbitrarily long and may be closed on itself so that a binary pattern can be continually circulated in the closed loop. We generally speak of an N-bit shift register, where N is the capacity of the register, i.e., the number of bits in the shifting pattern.

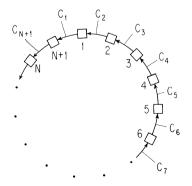

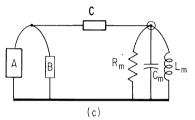

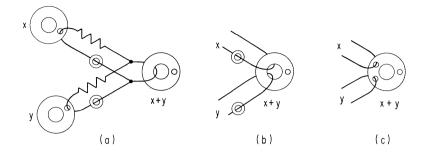

There are many ways to structure a register. Suppose, for example, that we have an N-bit binary pattern held in Cells 1 through N of a closed ring of N + 1 storage cells, such as in Fig. 3-1. Upon

application of clock pulse  $C_1$ , the bit stored in the first cell is advanced into Cell N + 1, formerly empty. Upon application of clock pulse  $C_2$ , the bit stored in Cell 2 is advanced into Cell 1, and so on. The shifting occurs in caterpillar fashion in this case, and shifting an N-bit pattern requires N + 1 clock sources.

A more common method of structuring is to arrange for shifting all data simultaneously. This mode requires more storage cells but only a small, fixed number of clock drivers,

Fig. 3-1. N-bit register with (N + 1) cores and (N + 1) clock sources.

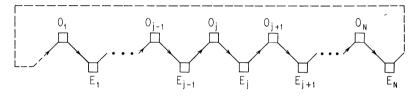

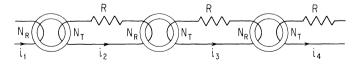

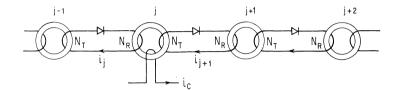

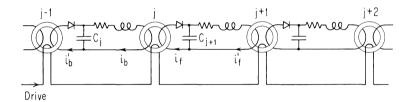

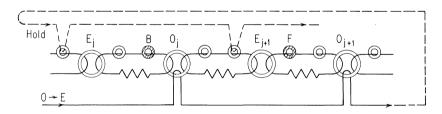

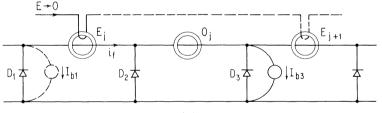

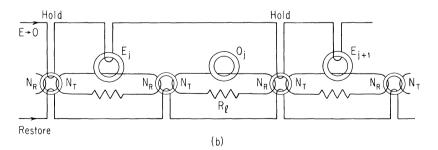

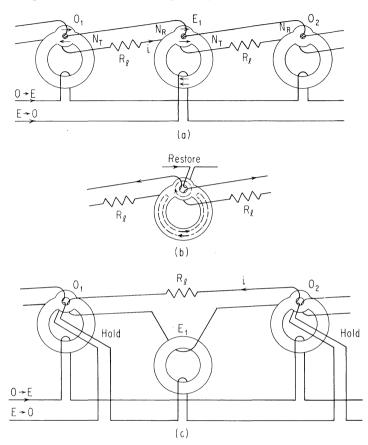

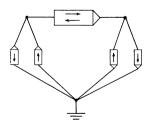

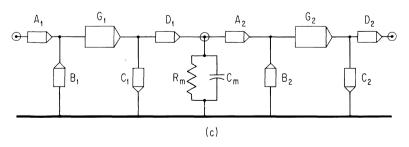

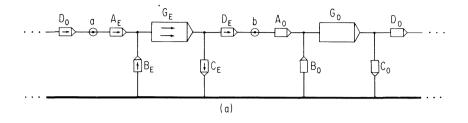

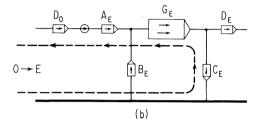

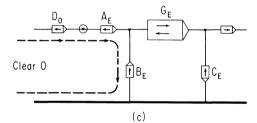

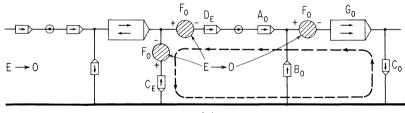

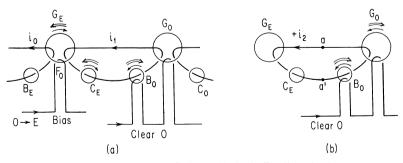

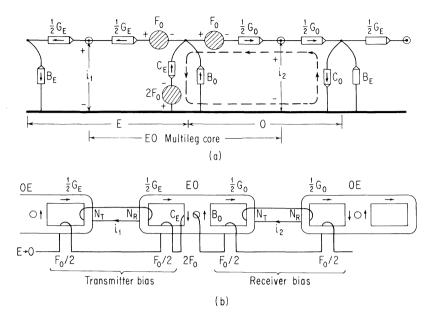

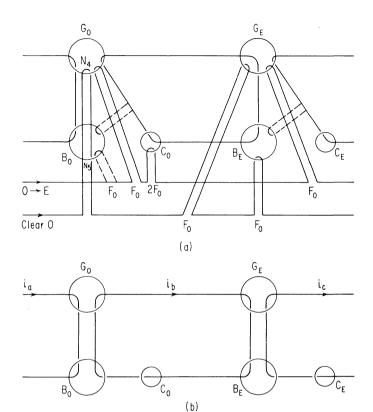

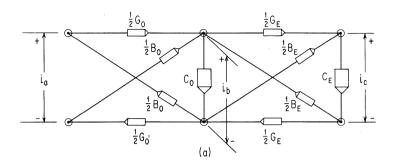

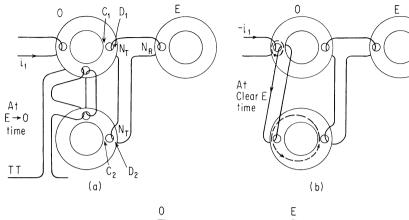

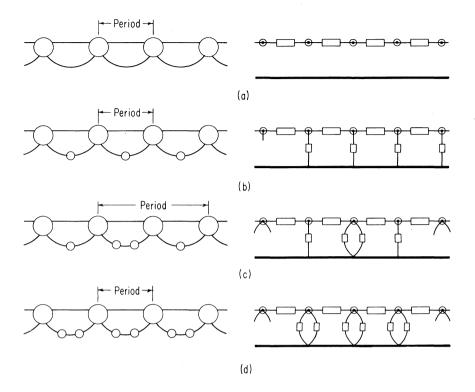

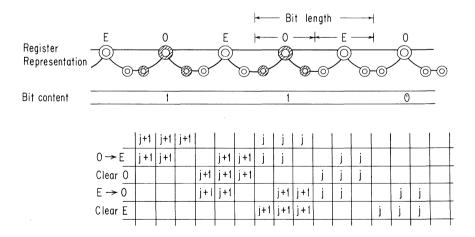

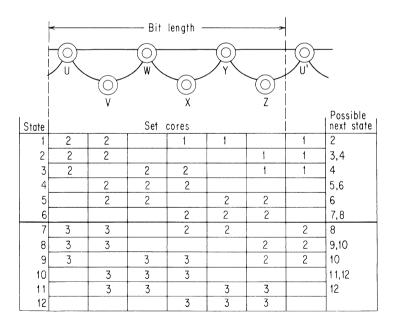

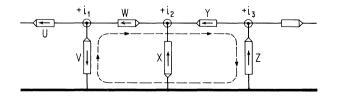

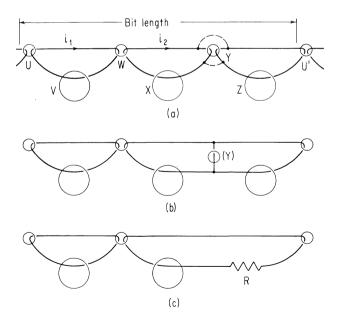

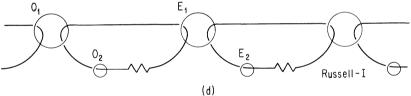

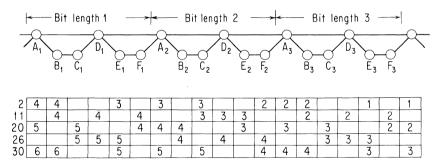

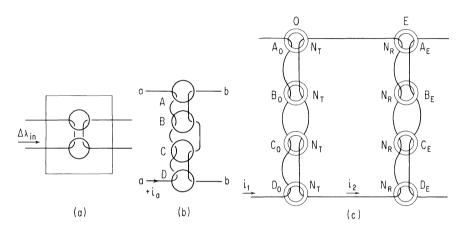

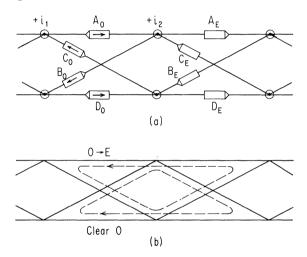

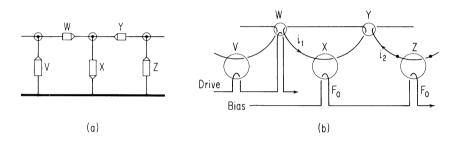

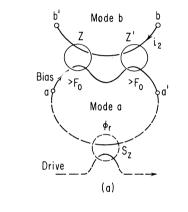

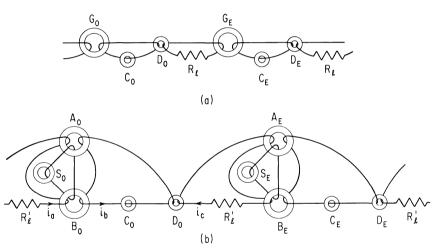

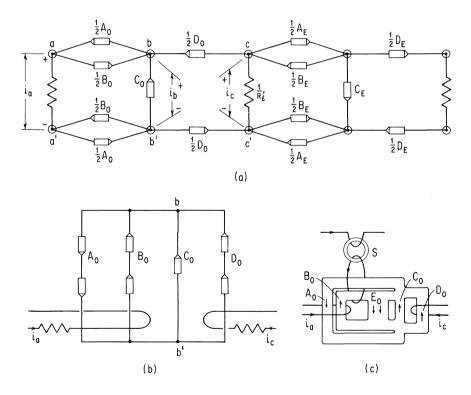

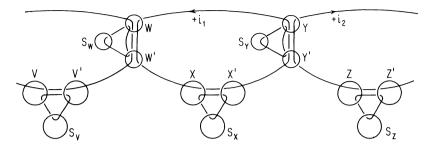

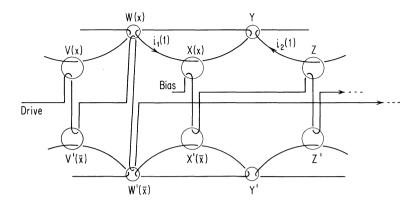

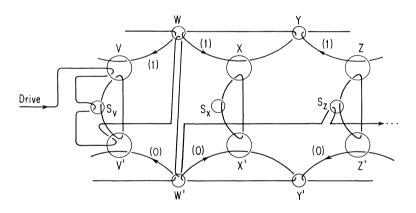

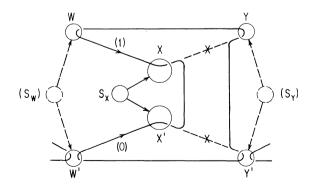

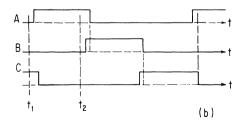

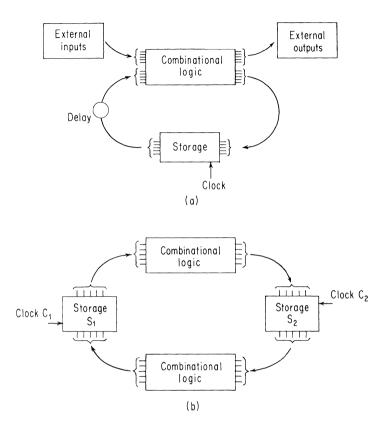

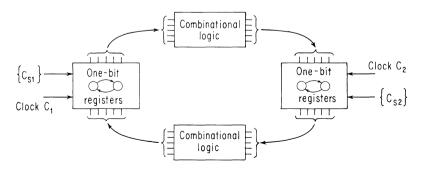

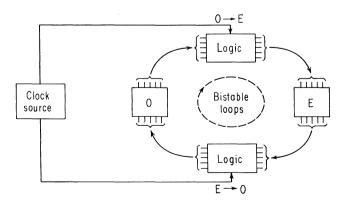

independent of the number of bits N. A common arrangement uses two storage cells per bit and two clock pulses, as shown schematically in Fig. 3-2, where the square boxes represent storage cells and the arrowed lines represent interconnecting circuitry. It is common to refer to the alternate cells as O (for odd) and E(for even). To shift an N-bit pattern that is stored in the O-rank, we activate the coupling circuitry between each O-cell and its right-hand E neighbor, and thereby simultaneously shift the pattern to the E-rank. This is referred to as an  $O \rightarrow E$  shift. Next we activate an  $E \rightarrow O$  shift, and the pattern is transferred back to the O-rank, but shifted one place to the right as required. The *shifting rate*, or *bit rate*, depends on the time it takes to complete this basic two-phase shift cycle.

Fig. 3-2. N-bit register with 2N cores and two clock sources.

An important aspect of binary transfer is the isolation required between adjacent storage cells. In the transfer from Cell  $O_j$  to  $E_j$ , during an  $O \rightarrow E$  transfer, the switching of  $E_j$  must be prevented from affecting the following  $O_{j+1}$  cell, i.e., forward isolation is required, and the switching or readout from  $O_j$  must be prevented from acting on  $E_{j-1}$ , which is acting as a receiver from Cell  $O_{j-1}$ , i.e., back isolation is also necessary. During an  $E \rightarrow O$  transfer, the roles must be reversed, the inactivated paths becoming activated, and vice versa.

Although there are other possible shifting schemes, we concentrate primarily on this simultaneous shifting technique, which is the most common. This results in no particular loss of generality.

## 3-2 Digital Transfer

In the previous section, we represented bistable storage cells symbolically without specifying any particular device technology. Pursuing this symbolic approach, we can derive some important requirements for digital transfer between cells.

#### DIGITAL TRANSFER IN ITERATIVE CORE CIRCUITS

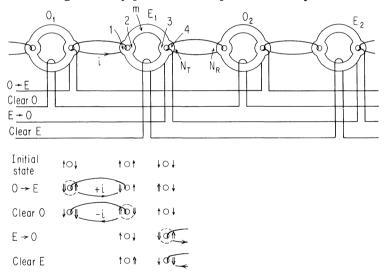

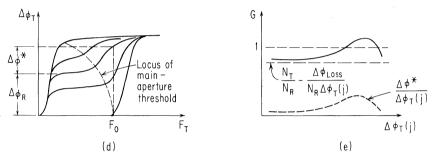

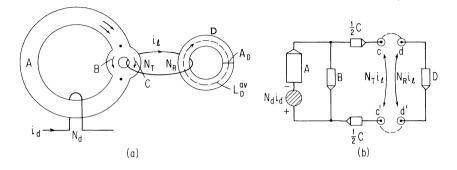

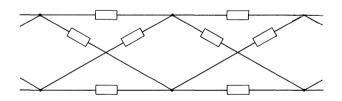

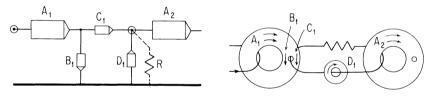

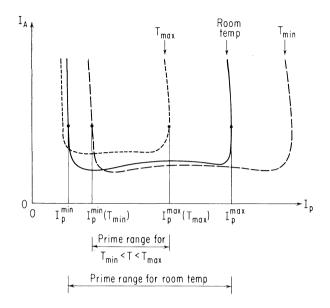

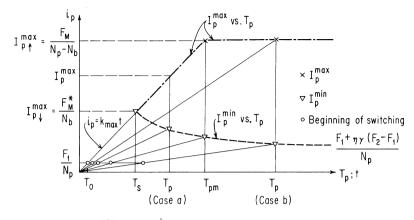

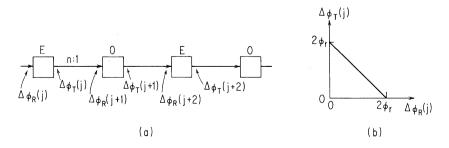

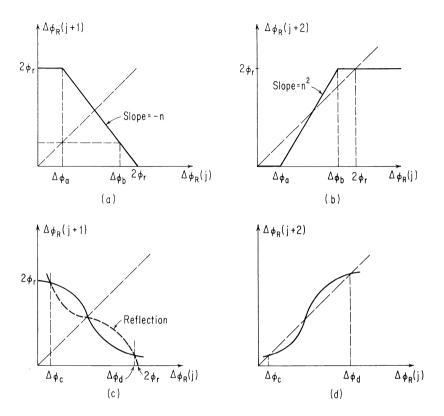

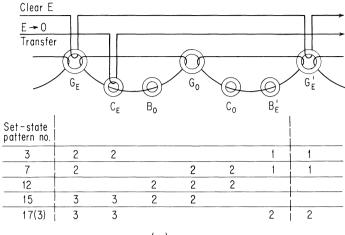

$\Delta\phi$  Gain Requirements. The register circuit of Fig. 3-2 is redrawn along a single row in Fig. 3-3(a), with cells renumbered in sequence. Let us follow just one of the bits of the pattern as it moves along the chain. Suppose that the particular bit of interest is initially stored in Cell j = 1. At the next shift pulse, there is a transfer from Cell j = 1 to Cell j with  $\Delta\phi$  transfer ratio

$$G = \frac{\Delta \phi_j}{\Delta \phi_{j-1}}$$

(3-1)

where  $\Delta \phi_j$  represents the magnitude of flux switched in Cell *j*, and  $\Delta \phi_{j-1}$  is the magnitude of flux simultaneously switched in Cell *j* - 1. We will assume here that the value of  $\Delta \phi$  when the cell is acting as a transmitter is the same as the value of  $\Delta \phi$  switched when the same cell was previously a receiver (though there are important exceptions, as we shall see in later chapters).

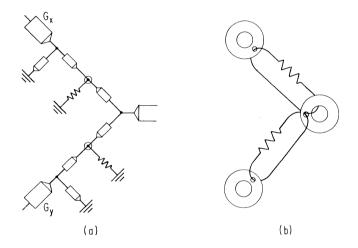

Fig. 3-3. Flux-gain requirements for multistable flux transfer.

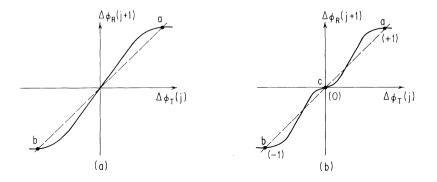

If the transfer ratio were exactly unity in each transfer, independent of the magnitude of  $\Delta\phi$ , then we would have a very useful "analog delay line"; any level of  $\Delta\phi$  injected at one end of the chain would emerge unchanged at the far end at a later time. However, the transfer ratio generally depends on many different circuit parameters, and it is impossible to keep these parameters sufficiently controlled to actually achieve unity transfer ratio over a range of  $\Delta\phi$  levels. Instead, let us consider different ranges of signal level, and ask what form of gain characteristic  $G(\Delta\phi)$  is required to ensure that an initial signal level within any one range should be maintained within that range regardless of the length of the transmission chain. A form of  $G(\Delta\phi)$  characteristic that would satisfy this requirement is indicated in Fig. 3-3(b). In some regions G > 1, in other regions G < 1. At signal levels  $\Delta\phi_1$ ,  $\Delta\phi_3$ , and  $\Delta\phi_5$  represent

stable levels. By this we mean the following: if initially  $\Delta\phi_3 < \Delta\phi < \Delta\phi_4$ , then G < 1, or if initially  $\Delta\phi_2 < \Delta\phi < \Delta\phi_3$ , then G > 1, so that in either case the level will monotonically approach  $\Delta\phi_3$  during subsequent transfers. If the initial signal level is exactly equal to  $\Delta\phi_4$ , then any noise in the system will shift the signal level away from level  $\Delta\phi_4$  toward either level  $\Delta\phi_3$  or  $\Delta\phi_5$ . Thus the levels  $\Delta\phi_2$  and  $\Delta\phi_4$  are unstable points of unity transfer ratio.

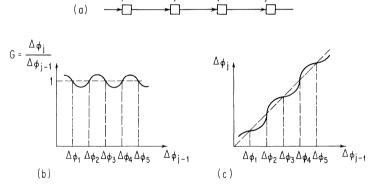

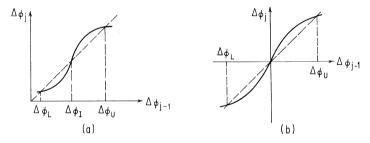

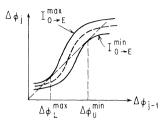

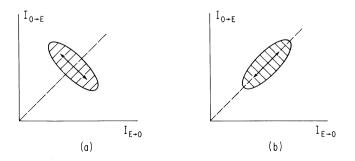

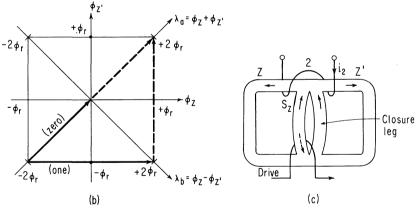

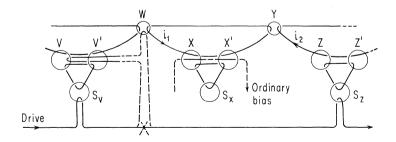

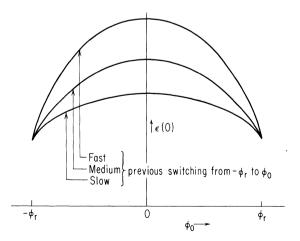

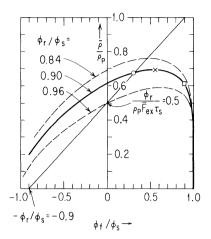

The curve of Fig. 3-3(b) can be translated into the curve of Fig. 3-3(c), known as a  $\Delta\phi$ -transfer curve, where the 45° line is the locus of the stable and unstable unity-gain points. In the case of binary transmission, the transfer curve has the form shown in Fig. 3-4(a). We define the lower stable signal level as the binary zero level, labeled  $\Delta\phi_L$ , and the upper level as the binary one level, labeled  $\Delta\phi_U$ . The intermediate, unstable unity-gain point is labeled  $\Delta\phi_I$ . This type of transfer curve applies to what is generally referred to as a unipolar representation (based on a high magnitude of signal for a one and a low magnitude of signal for a zero). An alternate data representation is shown in Fig. 3-4(b) where the two states have signal levels of equal magnitude but of opposite polarity. This is referred to as a bipolar data representation (which is employed in the circuits discussed in Chap. 9).

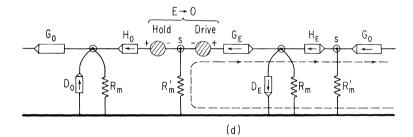

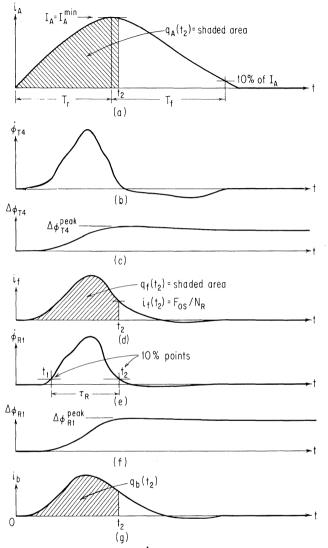

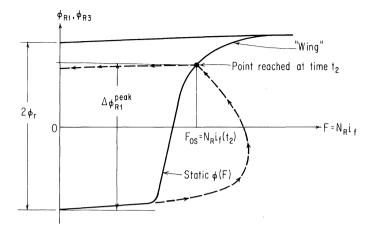

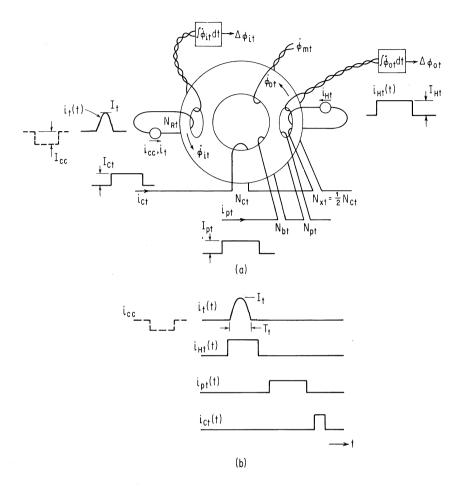

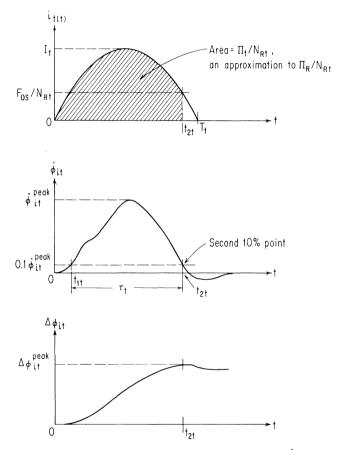

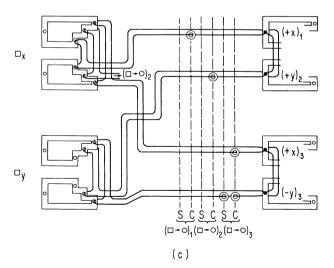

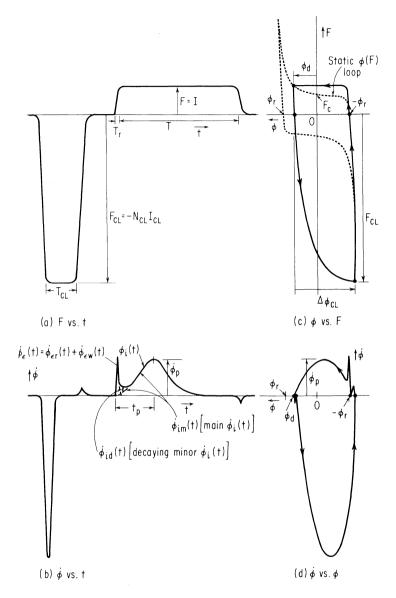

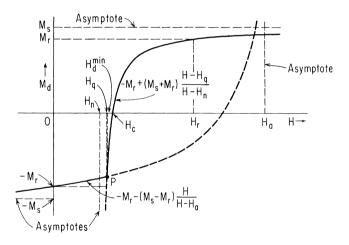

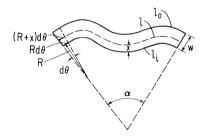

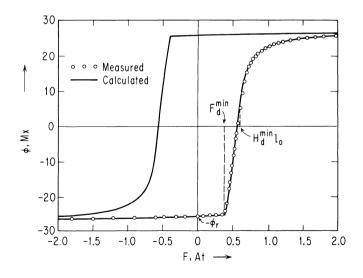

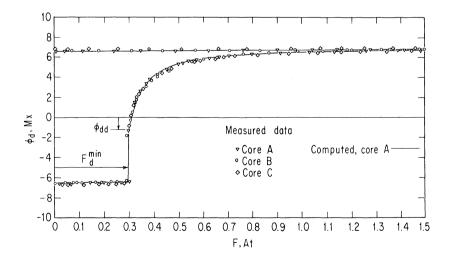

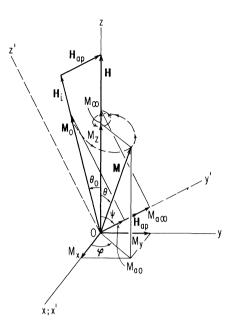

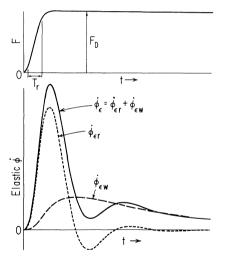

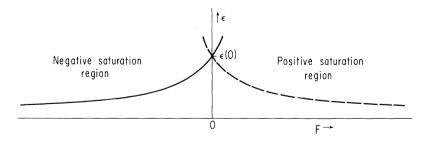

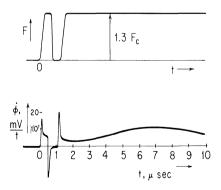

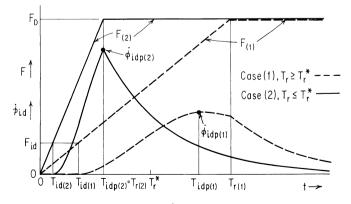

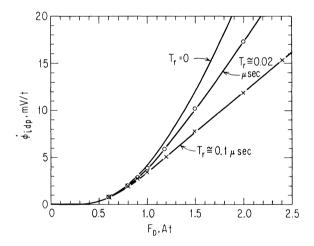

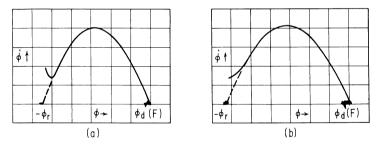

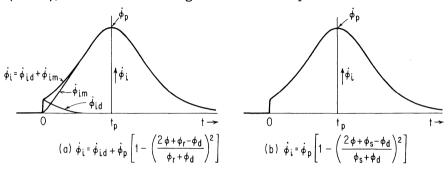

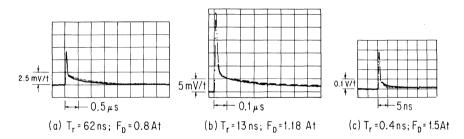

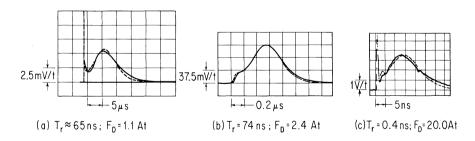

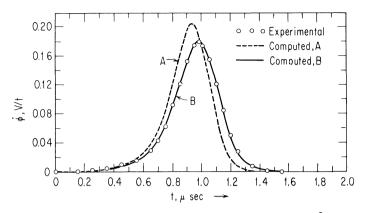

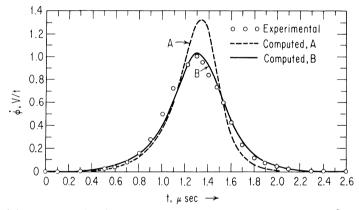

Fig. 3-4. Flux-gain requirements for stable binary transmission: (a) unipolar mode; and (b) bipolar mode.