# Sun-2/50 Field Service Manual

......

Sun Microsystems, Inc. • 2550 Garcia Avenue • Mountain View, CA 94043 • 415-960-1300

### Copyright © 1984 by Sun Microsystems.

This publication is protected by Federal Copyright Law, with all rights reserved. No part of this publication may be reproduced, stored in a retrieval system, translated, transcribed, or transmitted, in any form, or by any means manual, electric, electronic, electro-magnetic, mechanical, chemical, optical, or otherwise, without prior explicit written permission from Sun Microsystems.

## Contents

|                                            | iv         |

|--------------------------------------------|------------|

| Chapter 1 Theory of Operations             | 3          |

| 1.1. Printed Circuit Boards                | 4          |

| 1.2. Monitor                               | 31         |

| 1.3. Power Supply                          | 31         |

| Chapter 2 Diagnostics and Troubleshooting  | 35         |

| 2.1. Overview                              | 35         |

| 2.2. Symptom Analysis                      | 36         |

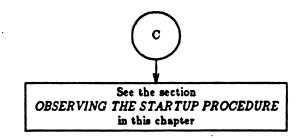

| 2.3. Observing the Startup Procedure       | 37         |

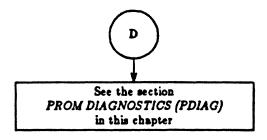

| 2.4. PROM Diagnostics (PDIAG)              | 42         |

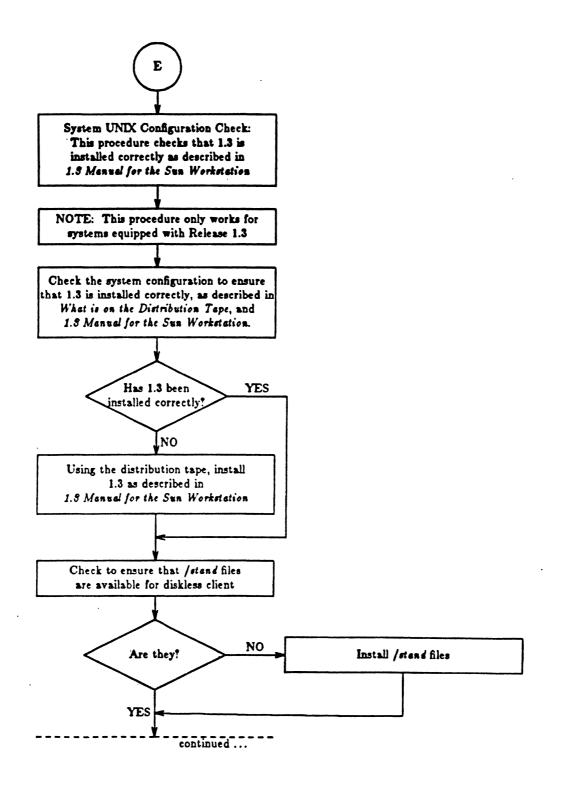

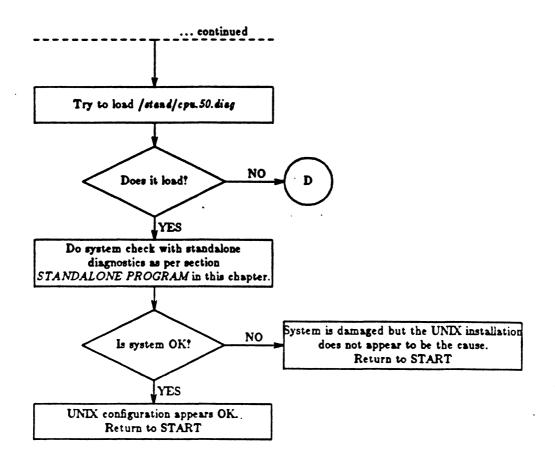

| 2.5. Standalone Programs                   | 51         |

| 2.6. Quick Reference Troubleshooting Guide | 52         |

| Chapter 3 Maintenance                      | 55         |

| 3.1. Printed Circuit Board Removal         | <b>5</b> 6 |

| 3.2. Monitor Removal from Chassis          | 59         |

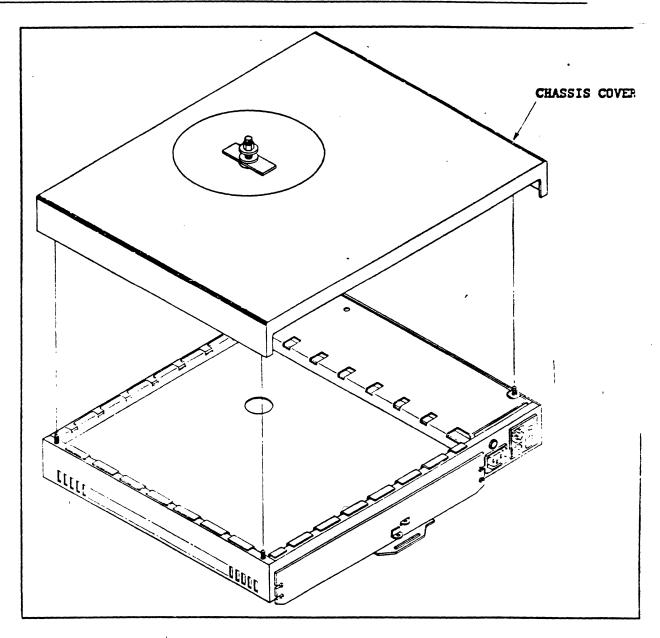

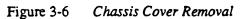

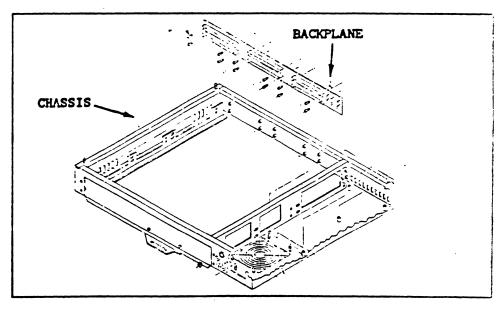

| 3.3. Chassis Cover Removal                 | 61         |

| 3.4. RFI Shield Removal                    | 62         |

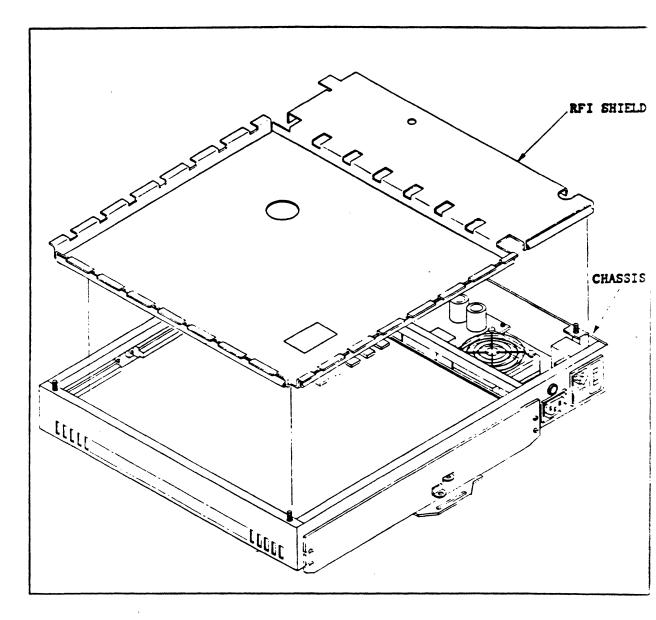

| 3.5. Power Supply Removal                  | 63         |

| 3.6. Cooling Fan Removal                   | 65         |

| 3.7. Backplane Removal                     | 65         |

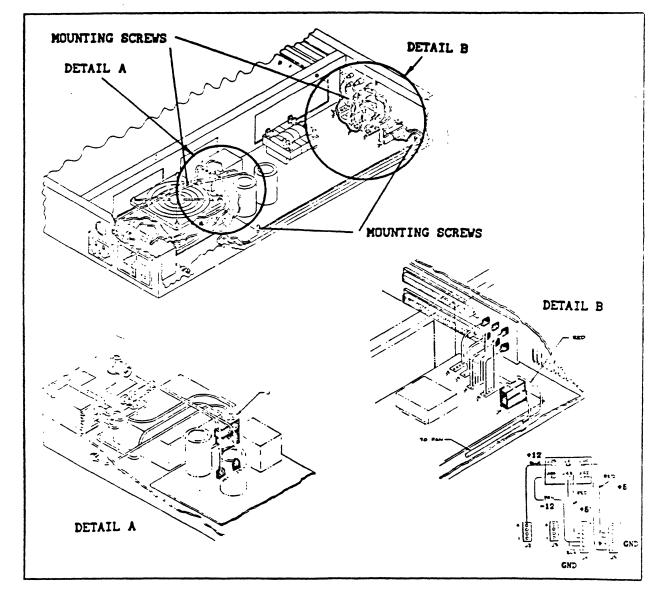

| 3.8. Miscellaneous Parts Removal           | 65         |

.

÷

.

.

\*\*\*\*

| Appendix A Glossary of Sun Terms                   | 77             |

|----------------------------------------------------|----------------|

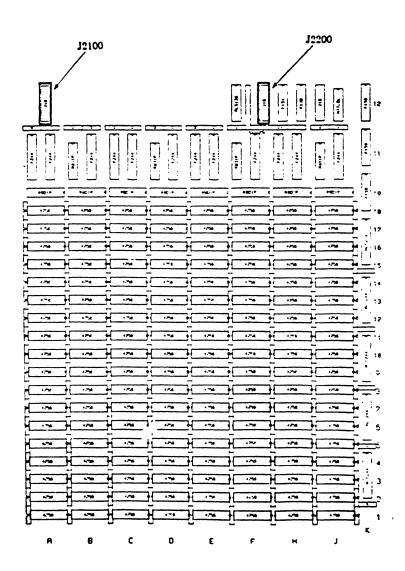

| Appendix B Printed Circuit Board Layouts           | 83             |

| Appendix C Printed Circuit Board Connector Pinouts | 89             |

| Appendix D Select Jumper Options                   | 93             |

| Appendix E Manufacturer's Component Data           | <del>9</del> 9 |

| Appendix F RS-423 P-Diag Jumper Pinout             | 107            |

| Appendix G Ethernet Cable Connections              | 111            |

| Appendix H MUX Box Specification                   | 115            |

| H.1. Installation Requirements                     | 116            |

| H.2. MUX Box (2110) Installation                   | 116            |

| H.3. 2110-B0 Module Installation                   | 117            |

| H.4. 2110-A0/2110-B0 Module Operation              | 117            |

| H.5. Specifications                                | 118            |

| Appendix I Vampire Transceiver Box Installation    | 121            |

| I.1. Tools and Equipment Required                  | 122            |

| I.2. Transceiver Installation                      | 122            |

| Index                                              | 127            |

### Preface

The Sun-2/50 is a microprocessor-based workstation, capable of operating stand-alone or as part of a local area network. Offering 1Mbyte of dynamic memory in its standard configuration, the Sun-2/50 may be expanded to a maximum of 4Mbytes with the addition of one of several memory expansion boards. Memory architecture, based on the concepts of virtual memory, provides access to significantly greater amounts of data storage than is resident on the workstation itself; while integral Ethernet, RS-423 and VME bus interfaces supply data links to a number of systems environments.

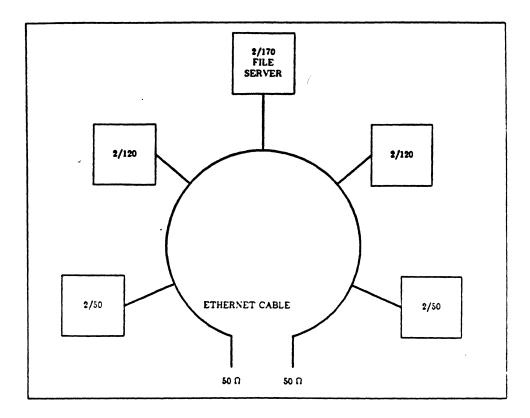

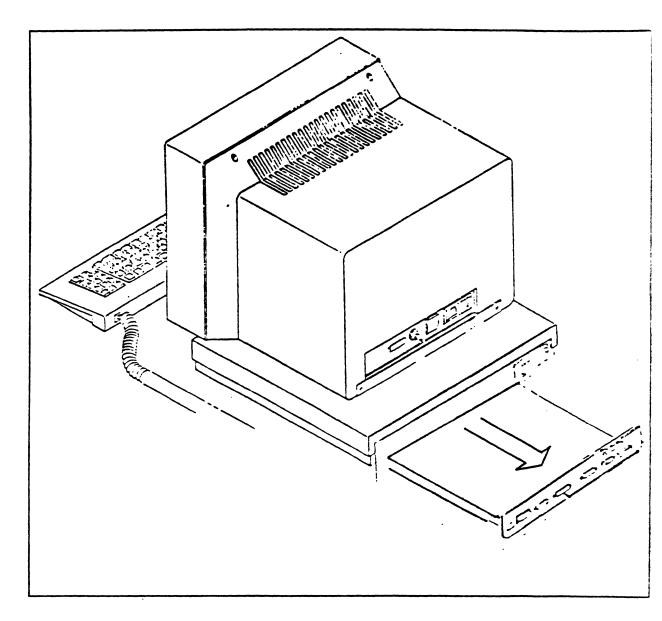

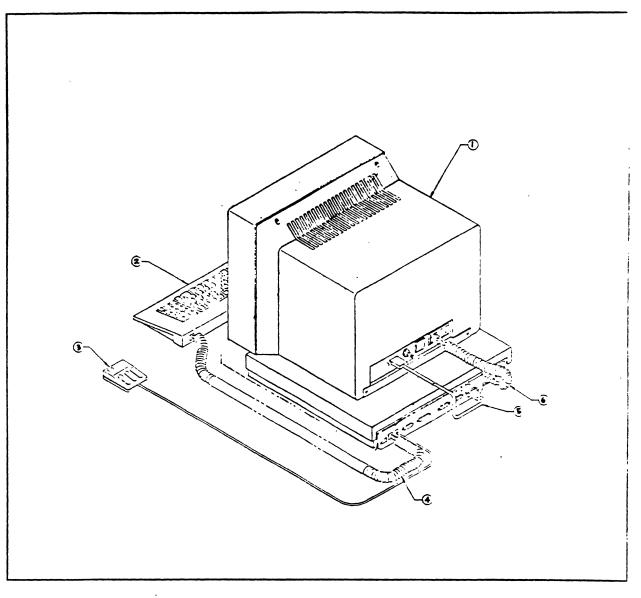

The information presented in this manual is designed to give the reader some insight into the workings of Sun-2/50 logic, provide assistance in troubleshooting problems and, finally, offer step-by-step procedures for the removal and replacement of system components. Figure 1-1 provides an overview of the Sun-2/50 in a typical system environment.

Sun-2/50 System Overview

•

.

| Assumptions About Reader<br>Knowledge | In presenting the information contained in this manual, it is assumed that the reader is familiar with TTL and ECL logic, and with the Motorola MC68010 Microprocessor. The reader should also have a working knowledge of Local Area Networks, Sun-2 virtual memory management architecture and the VME bus specification.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| List of Applicable Documents          | This list provides additional sources of information to be used in conjunction with the Sun-2/50 Service Manual.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                       | <ul> <li>Motorola MC68010 Databook (Motorola P/N ADI 942)</li> <li>Hardware Installation Manual for the<br/>Sun-2/50 Desktop SunStation<br/>(Sun P/N 800-1143-01)</li> <li>VMEbus Specification Manual (VME Manufacturers<br/>Group, Rev. B,Aug. 1982)</li> <li>Moniterm Monitor Service Manual for the<br/>Sun-2 Family of Workstations (Sun P/N<br/>800-1147-01)</li> <li>Philips Electronics Ltd.<br/>Video Display Products<br/>Service/Operator Manual<br/>19" Video Display Unit Model: M19P114A/5102</li> <li>System Managers Manual for the Sun Workstation-<br/>Models 120/170 (Sun P/N 800-1110-01)</li> <li>RS 423 Interface Specification</li> <li>System Release 1.1, Rev. C, release date 3-12-84</li> <li>1.3 Manual for the Sun Workstation (Sun P/N<br/>800-1159-01)</li> </ul> |

.

# Figures

| Figure 0-1  | Sun-2/50 System Overview                  | v          |

|-------------|-------------------------------------------|------------|

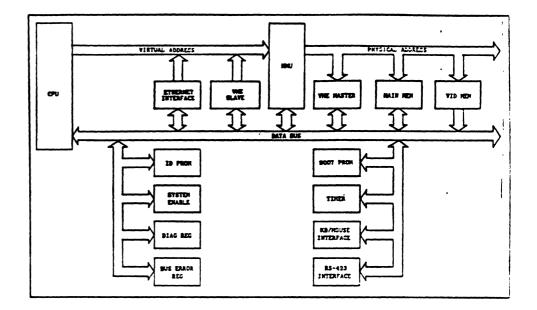

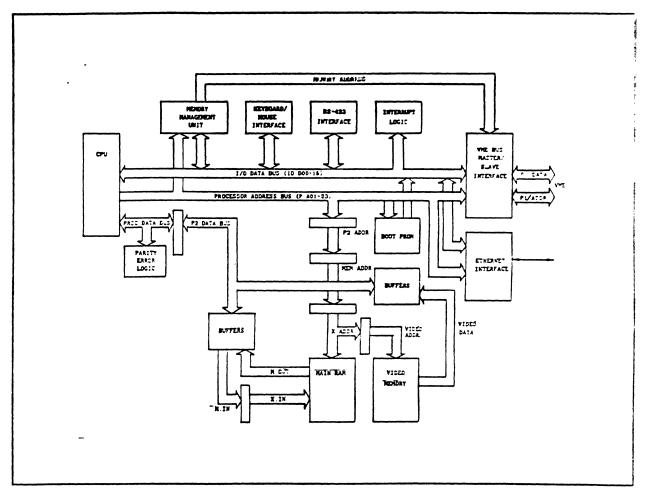

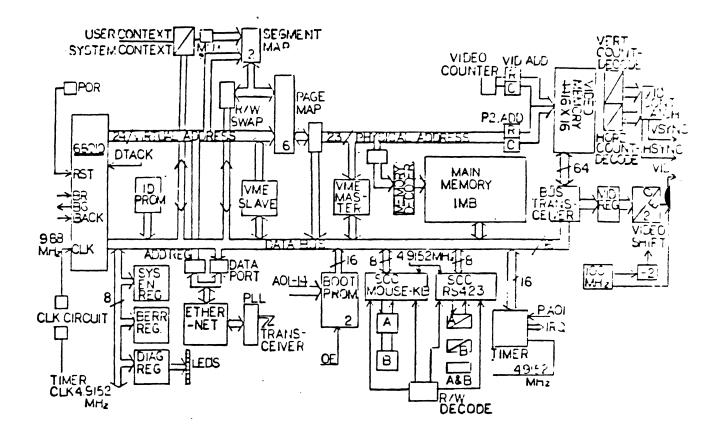

| Figure 1-1  | Sun-2/50 Circuit Overview                 | 5          |

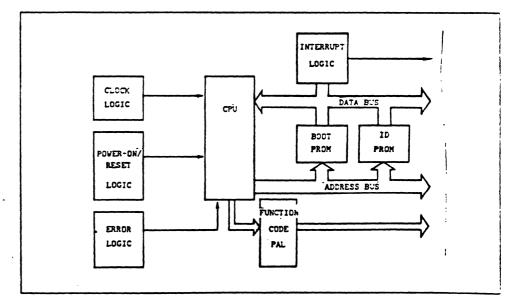

| Figure 1-2  | CPU Logic                                 | 5          |

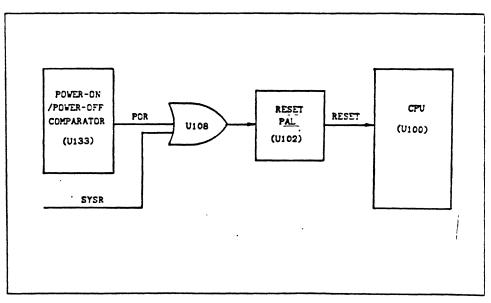

| Figure 1-3  | Power-on/Reset Logic                      | 6          |

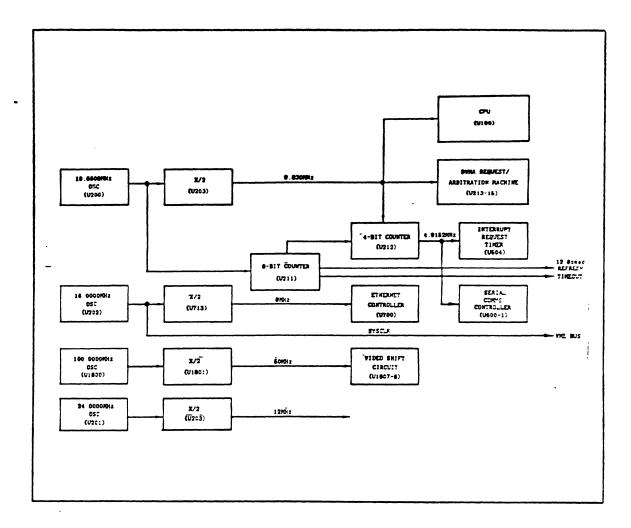

| Figure 1-4  | Clock Circuits                            | 8          |

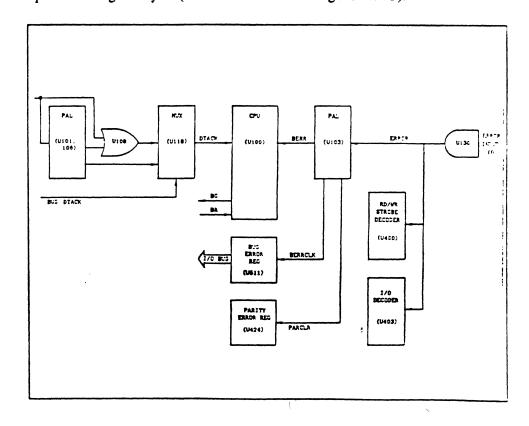

| Figure 1-5  | Data Transfer and Bus Error Logic         | 10         |

| Figure 1-6  | Sun-2/50 Bus Architecture                 | 11         |

| Figure 1-7  | I/O Data Bus                              | 14         |

| Figure 1-8  | Video Logic                               | 15         |

| Figure 1-9  | MMU Logic                                 | 20         |

| Figure 1-10 | Sun-2 Memory Management                   | 21         |

| Figure 1-11 | Memory Address Decode Logic               | 22         |

| Figure 1-12 | DVMA Control Logic                        | 23         |

| Figure 1-13 | DVMA Memory Refresh Logic                 | 24         |

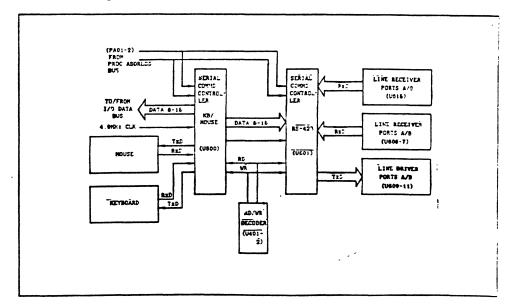

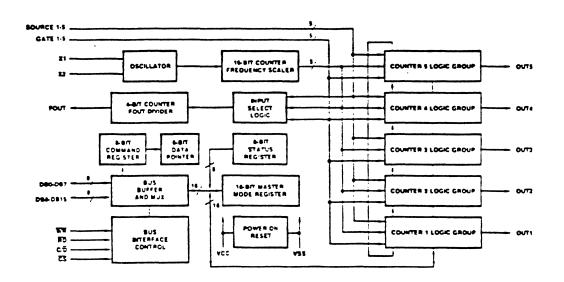

| Figure 1-14 | Serial Communications Logic               | 25         |

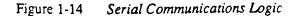

| Figure 1-15 | Ethernet Interface logic                  | 27         |

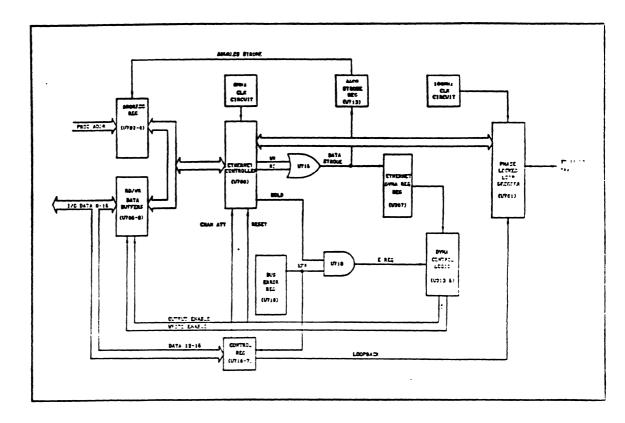

| Figure 1-16 | VME Bus Data Transfer Sequence            | <b>3</b> 0 |

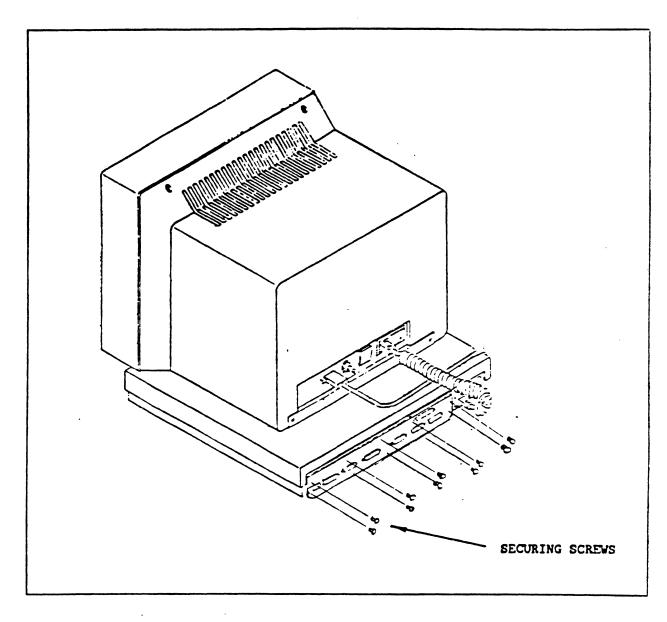

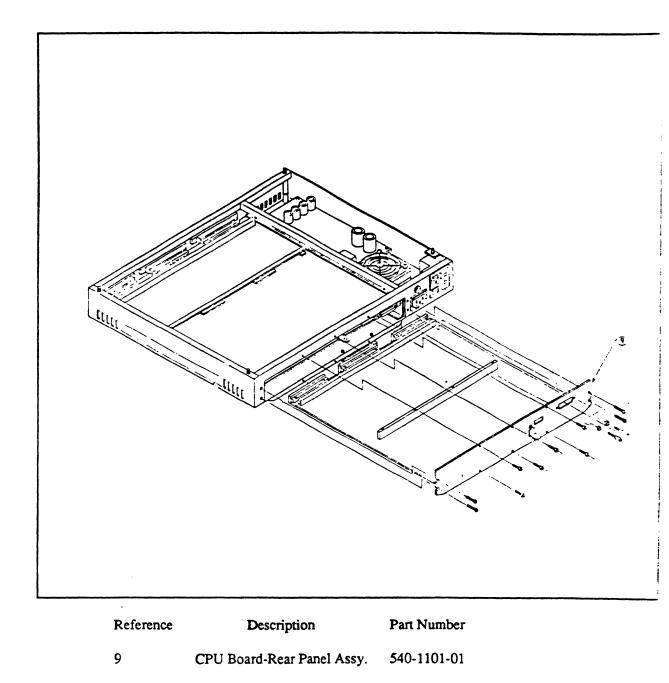

| Figure 3-1  | Rear Panel Securing Screws                | 57         |

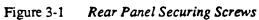

| Figure 3-2  | Releasing Backplane Connectors            | 58         |

| Figure 3-3  | Removing Rear Panel Assembly from Chassis | <b>5</b> 9 |

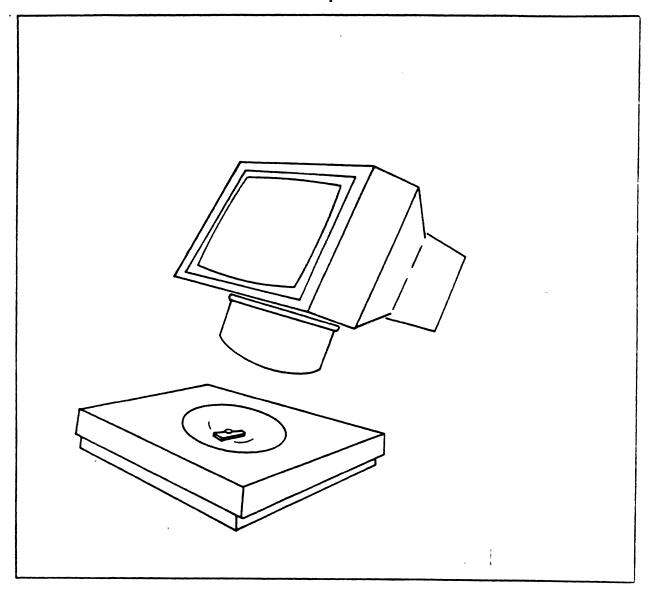

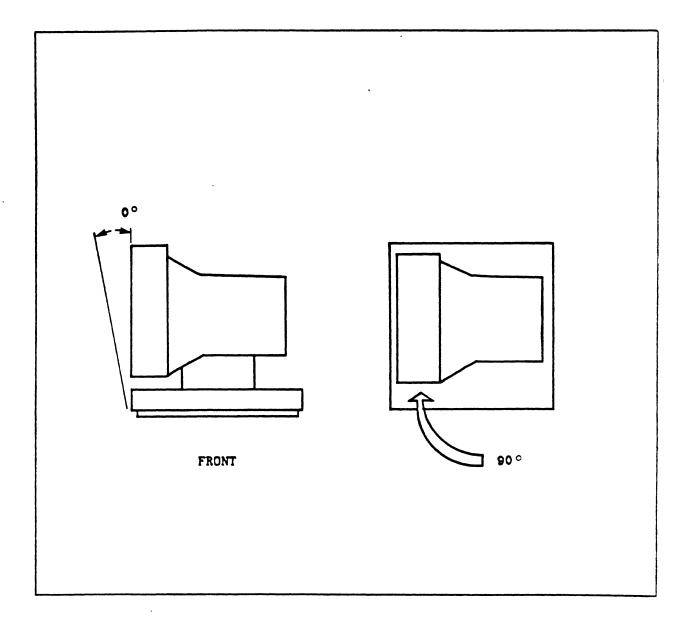

| Figure 3-4  | Monitor Mounting                          | <b>6</b> 0 |

| Figure 3-5  | Positioning Monitor for Removal           | 61         |

•

and the second

•

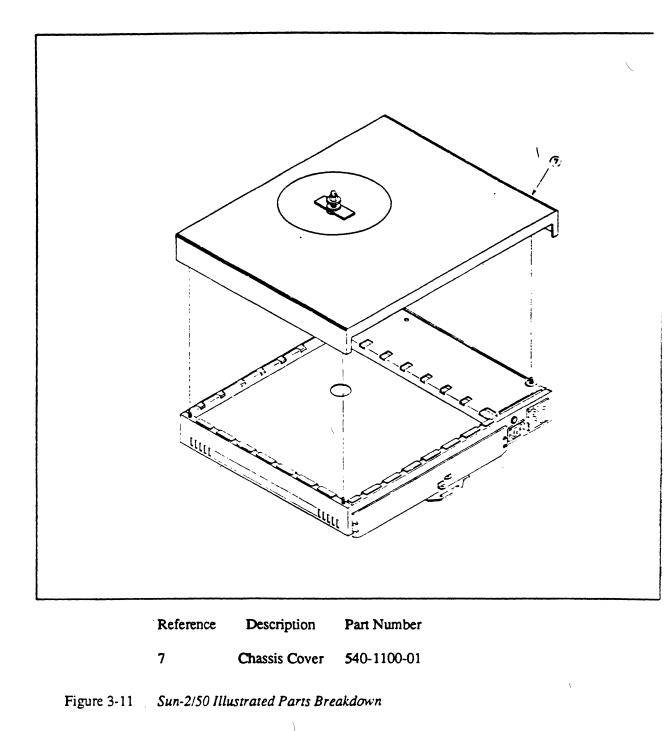

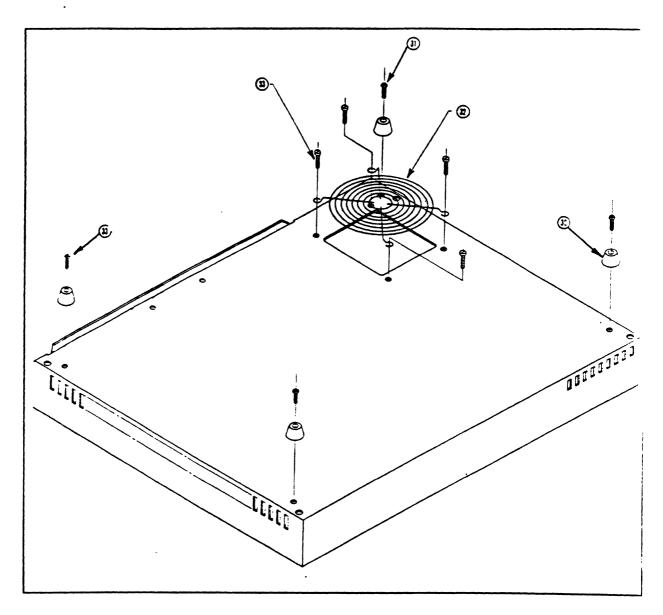

| Figure 3-6  | Chassis Cover Removal                | 62         |

|-------------|--------------------------------------|------------|

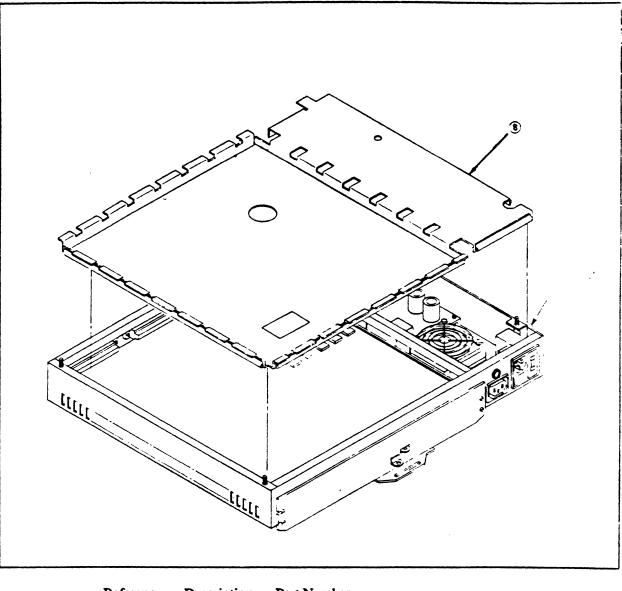

| Figure 3-7  | RFI Shield Removal                   | 63         |

| Figure 3-8  | Power Supply Removal                 | 64         |

| Figure 3-9  | Backplane Removal                    | 65         |

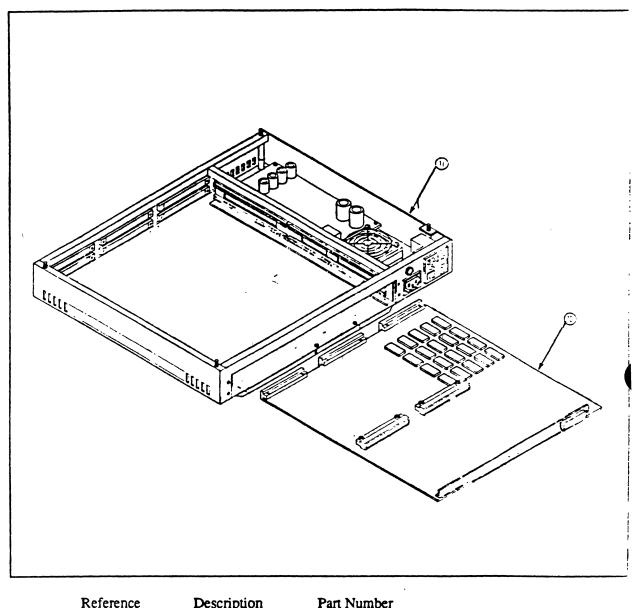

| Figure 3-10 | Sun-2/50 Illustrated Parts Breakdown | <b>6</b> 6 |

| Figure 3-11 | Sun-2/50 Illustrated Parts Breakdown | 67         |

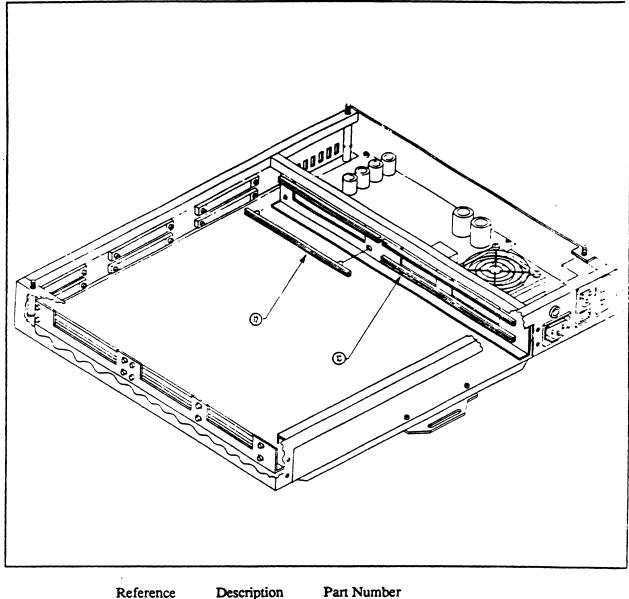

| Figure 3-12 | Sun-2/50 Illustrated Parts Breakdown | 68         |

| Figure 3-13 | Sun-2/50 Illustrated Parts Breakdown | 69         |

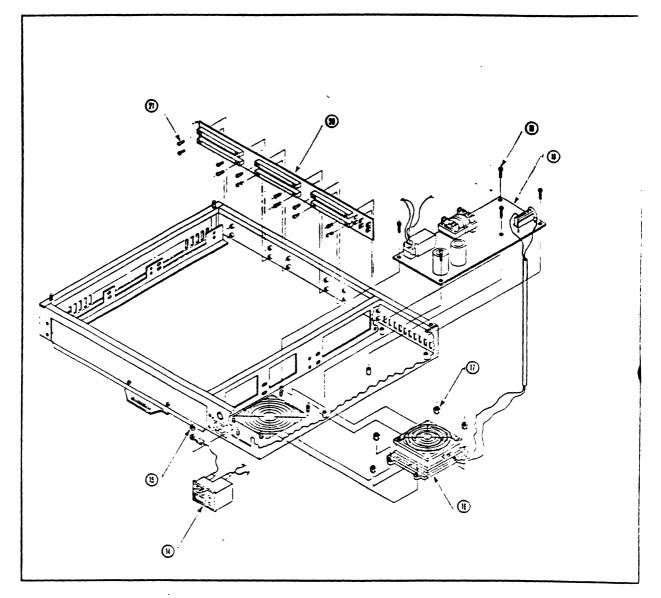

| Figure 3-14 | Sun-2/50 Illustrated Parts Breakdown | 70         |

| Figure 3-15 | Sun-2/50 Illustrated Parts Breakdown | 71         |

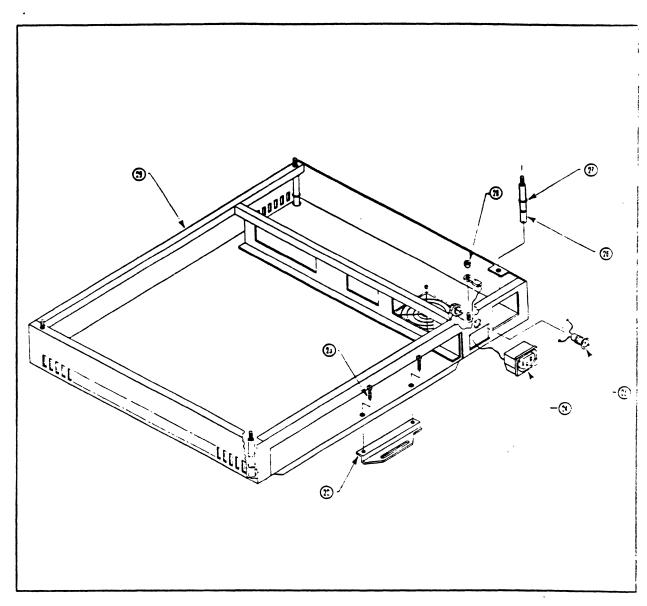

| Figure 3-16 | Sun-2/50 Illustrated Parts Breakdown | 72         |

| Figure 3-17 | Sun-2/50 Illustrated Parts Breakdown | 73         |

| Figure 3-18 | Sun-2/50 Illustrated Parts Breakdown | 74         |

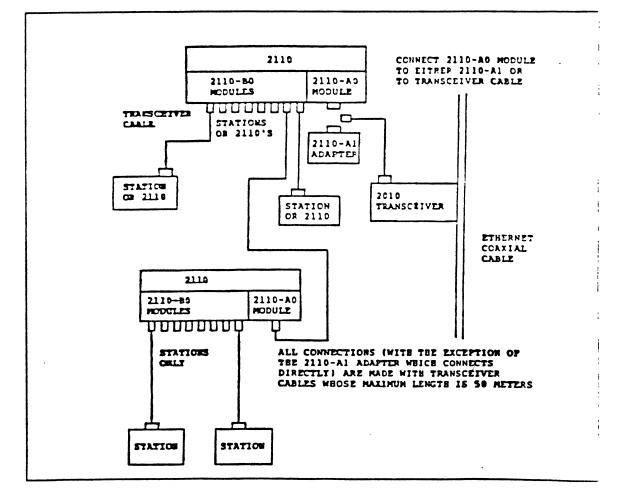

| Figure H-1  | Network Configurations               | 116        |

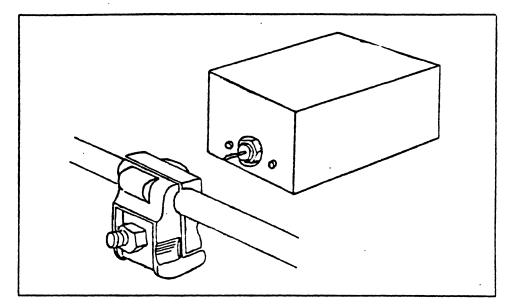

| Figure I-1  | Tap Block                            | 122        |

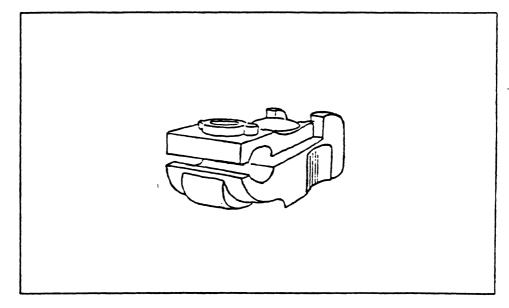

| Figure I-2  | Shim Placement                       | 123        |

| Figure I-3  | Transceiver Installation             | 124        |

| Figure I-4  | TCL Coring Tool Kit                  | 125        |

|             |                                      |            |

.

1

-

.

# Theory of Operations

| Theory of Operations              | 3  |

|-----------------------------------|----|

| 1.1. Printed Circuit Boards       | 4  |

| CPU Logic                         | 4  |

| Microprocessor                    | 4  |

| Power-On/Reset Logic              | 5  |

| Boot PROMs                        | 7  |

| Function Code PAL                 | 7  |

| Clock Circuits                    | 7  |

| Interrupt Logic                   | 8  |

| ID PROM                           | 9  |

| Processor Bus Errors              | 9  |

| Data Transfers                    | 10 |

| Address Error Cycle               | 10 |

| Bus Architecture                  | 11 |

| Processor Data and Address Buses  | 11 |

| I/O Data Bus                      | 12 |

| Memory (P2) Bus                   | 12 |

| Parity Error Logic                | 13 |

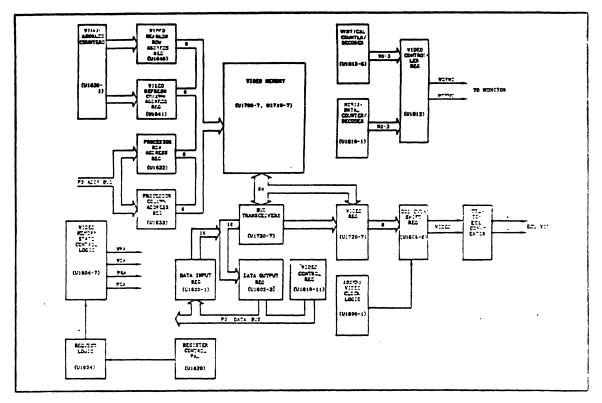

| Video Logic                       | 15 |

| Video Memory and Address Decoding | 15 |

| Video Memory Controller           | 16 |

| Video Sync Control Circuitry      | 16 |

| Video Shift Logic                 | 16 |

|                                   |    |

| Video Interface to the Memory (P2) Bus  | 17 |

|-----------------------------------------|----|

| Video Write Cycles                      | 17 |

| Video Read Cycles                       | 17 |

| Video Refresh Cycle                     | 17 |

| Video to Memory (P2) Bus Data Transfers | 18 |

| Video Interrupts                        | 18 |

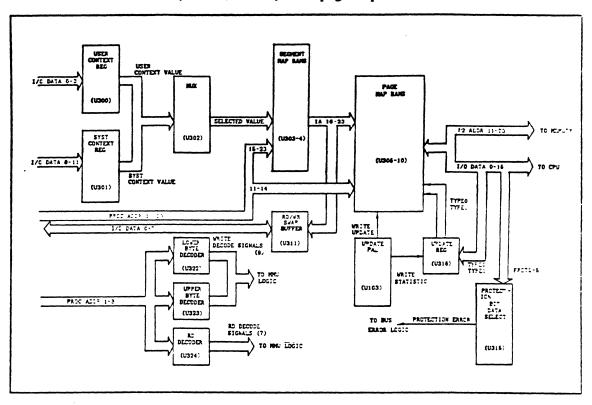

| Memory                                  | 19 |

| Overview of Sun-2 Memory Architecture   | 19 |

| Memory Management Unit (MMU)            | 19 |

| Main Memory                             | 21 |

| Direct Virtual Memory Access (DVMA)     | 22 |

| Interface Logic                         | 25 |

| Serial Communications                   | 25 |

| Ethernet Interface                      | 26 |

| Ethernet DVMA Cycle                     | 27 |

| VME (P1) Bus Interface                  | 28 |

| VME Bus Arbitration and Request Logic   | 28 |

| VME Master Interface                    | 29 |

| VME Slave Interface                     | 29 |

| VME Interrupt Control                   | 30 |

| 1.2. Monitor                            | 31 |

| 1.3. Power Supply                       | 31 |

. .

۹

.

# Theory of Operations

This section offers a brief operational overview of the Sun-2/50 SunStation. For the purpose of this overview, all Sun-2/50 components will be separated into three functional groupings: printed circuit boards (CPU board and optional Memory Expansion board), the monitor and the power supply.

| 1.1. Printed Circuit Boards | A single CPU board contains all of the logic necessary to operate the Sun-2/50 in its standard configuration. Memory capabilities may be enhanced with the addition of the optional Memory Expansion board.                                                                          |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                             | The following logic description applies primarily to the CPU board. Information pertaining to the Memory Expansion board is contained in the section titled "Main Memory". The logic resident on both circuit boards is represented by the functional block diagram in Figure 1-2.   |

|                             | CPU board logic may be separated into the following functional blocks: CPU logic, Video Control circuitry, Memory and Interface logic. Each of these blocks, as well as the interconnecting bus architecture, will be described in the following paragraphs.                         |

| CPU Logic                   | The CPU logic block consists of the microprocessor and the following associated circuitry (refer to Figure 1-3 for a functional block diagram supporting this logic):                                                                                                                |

| X                           | <ul> <li>Power-On/Reset Logic</li> <li>Clock Circuitry</li> <li>Interrupt Logic</li> <li>Boot PROMs</li> <li>ID PROM</li> <li>Function Code PAL</li> <li>Bus and Address Error Logic</li> </ul>                                                                                      |

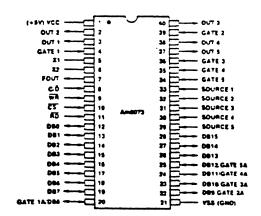

| Microprocessor              | The CPU logic is designed around the Motorola 68010 microprocessor. The 68010 is a 16-bit, virtual memory microprocessor with an asynchronous bus structure supporting 24-bit addresses and 16-bit data words. Refer to Appendix E for pinouts and signal definitions for the 68010. |

•

·

.

. **.**

Power-On/Reset Logic

The power-on/reset logic provide a means of starting a processor and/or system initialization sequence. This sequence is initiated in response to fluctuations in the supply voltage, a reset signal from an external bus, or a halt in a CPU processing cycle.

Microprocessor reset signals are generated by the PAL at U102 as the result of a power-on reset, an external reset, or a watchdog reset (refer to Appendix A). Inputs to the PAL are provided by the power-on reset generator (POR), the VME

bus (SYSR) and the 68010 (HALT).

Initialization and power-on-reset pulses are supplied by a power-on/power-off reset generator. This generator is composed of a dual comparator (U133), reference voltage diode (D101), charge capacitor (K100) and resistor network (R100-107).

The comparator acting as the power-on reset generator compares the voltage from the charge capacitor with the +1.2V reference voltage provided by the diode. The comparator will assert its output until the capacitor voltage reaches +4.5V.

The comparator acting as the power-off reset generator compares the +5.0V supply voltage with the +1.2V reference. The comparator output will be asserted when the +5.0V supply voltage drops below a threshold value of +4.5V.

The comparator outputs are combined to produce a power-on-reset (POR) signal when either comparator output is asserted.

An external reset will be generated when the Sun-2/50 is configured as a "reset slave" and a VME system reset (SYSR) is received. Both POR and SYSR are ORed at U108 and input to the PAL as POR1.

A watchdog reset is generated when the microprocessor stops during a normal cycle and asserts the HALT signal. The PAL will respond by asserting RESET to continue the processing cycle.

Refer to Figure 1-4 for a functional block diagram supporting the Power-On/ Reset logic.

Figure 1-3 Power-on/Reset Logic

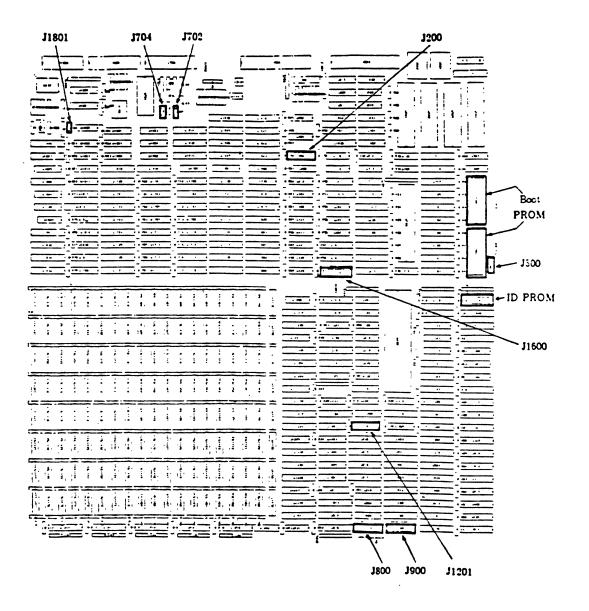

| Boot PROMs        | The boot code used by the CPU during reset, "boot state" and normal code- fetch cycles is stored in two 16,384 word by 8-bit PROMs. These PROMs (U500,U501) are addressed directly with the low-order address bits from the CPU (A01-14). Both PROMs are constantly chip-enabled and their outputs are controlled by an output enable signal (OE.PROM) from the PAL at U101.                                                                                            |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Function Code PAL | The PAL at U101 controls a number of processes which are designated as "spe-<br>cial cycles" (refer to Appendix A). Special cycles are operations in which the<br>68010 function code is neither program nor data. Examples of special cycles are<br>CPU and MMU space cycles and boot PROM read cycles. The PAL receives<br>function code data (P.FC0-2) from the 68010 which indicates the state (user or<br>supervisor) and the cycle type currently being executed. |

| Clock Circuits    | The clock logic provides the timing necessary for internal data processing and for communication with external devices; such as the Ethernet, keyboard, mouse and monitor.                                                                                                                                                                                                                                                                                              |

|                   | All system clocks are derived from four independent oscillators, located on the CPU board. The output of the 19.6608MHz oscillator (U200) is divided by two, producing a 10MHz clock for the CPU (U100) and for the DVMA Request/ Arbitration machine (U213-15). These clocks are further divided to supply 4.9152MHz timing pulses to the Interrupt Request Timer (U504) and to the Serial Communications Controllers (U600/U601).                                     |

|                   | The 16.0000MHz oscillator (U202) is used to produce 8MHz timing pulses for the Ethernet Controller (U700), as well as providing a system clock to the VME bus.                                                                                                                                                                                                                                                                                                          |

|                   | The 100.0000MHz oscillator at U1800 supplies clock pulses to the video shift circuit (U1807-8).                                                                                                                                                                                                                                                                                                                                                                         |

|                   | The output of the 24.0000MHz oscillator (U201) is divided by two to produce a 12MHz clock designed for special applications.                                                                                                                                                                                                                                                                                                                                            |

|                   | Refer to Figure 1-5 for a functional block diagram representing the Clock logic.                                                                                                                                                                                                                                                                                                                                                                                        |

,

nterrupt Logic

The Sun-2/50 interrupt logic provides a means of prioritizing requests for processor attention from both internal and external logic groups.

The interrupt logic consists of a timer at U504 and an interrupt PROM at U105. The timer provides five 16-bit counters for the main logic board and is driven by a 4.9152MHz clock pulse derived from the 19.6608MHz oscillator at U200. Processor address bit A01 selects the count source and the read and write strobes are supplied by the read/write decoders at U401 and U402 respectively. The timer outputs a level 7 interrupt request (IRQ7) and four level 5 interrupt requests (IRQ5).

The interrupt PROM receives inputs from the timer (IRQ5, IRQ7), from the bus error logic (EN.INT1-3), from the video controller logic (V.IRQ-), from the ethernet controller (E.IRQ) and from the Serial Communications Controllers (IRQ6-).

The interrupt PROM outputs three interrupt control signals to the microprocessor (IPLO-2-), which contain the encoded priority level of the device requesting the interrupt. Level 7 is the highest priority interrupt and cannot be masked. Interrupt levels are defined as follows:

| Level   | Meaning                           |

|---------|-----------------------------------|

| 7       | NMI (Non Maskable Interrupt)      |

| 6       | Serial Communications Controllers |

| 5       | Interrupt Timer                   |

| 4       | Video                             |

| 3       | Ethemet                           |

| 1, 2, 3 | INT                               |

The ID PROM (U510) contains basic information on the type and configuration of the Sun-2/50 in which it is installed. This information includes the serial number of the CPU board, the machine Ethernet address and the specific implementation of Sun-2 architecture used. Refer to Appendix A for a listing of the ID PROM contents.

If the original CPU board is removed and a replacement board installed, the ID PROM from the original board must be reinstalled on the new board.

A bus error (BERR) signal to the microprocessor indicates that a problem exists with the data transfer currently being executed. A bus error may be caused by page or protection errors in the Memory Management Unit (refer to Appendix A), parity errors, VMEbus errors, or a timeout.

The eight signals used to generate a bus error are ANDed together at U130. The output of this register (ERROR), when asserted, provides disable lines for the read/write strobe decoder (U400) and for the I/O decoder (U403). ERROR is also presented to the PAL at U103, which then generates the signals BERR, BERRCLK and PARCLK.

BERR is the processor bus error signal. BERRCLK latches the error condition into the bus error register at U511. PARCLR clears the parity error registers at U424, in the event that they were set. Refer to Figure 1-6 for a functional block diagram illustrating the bus error logic.

50 of 31 October 1984

ID PROM

Processor Bus Errors

Data Transfers The CPU uses a number of handshake signals to generate the timing required by the devices it is accessing. Upon completion of any data transfer cycle, a data transfer acknowledge signal (DTACK) is presented to the CPU by an eight-toone multiplexer at U118. Inputs to the multiplexer are provided by PALs at U101 and U106.

When the CPU receives DTACK during a read cycle, the data is latched one clock cycle later and the bus cycle is terminated. When DTACK is received during a write cycle, the write strobes are deasserted and the bus cycle is terminated.

Devices requesting the bus from the CPU assert the signal Bus Request (BG). The CPU relinguishes the bus with the signal Bus Grant (BG). Refer to Figure 1-6 for a functional block diagram of the data transfer logic and to Appendix E for CPU signal definitions.

# Address Error CycleAn address error cycle is handled by the CPU much like an internally generated<br/>bus error. The address strobe (AS) is asserted and a normal cycle is executed, but<br/>no data is transferred because neither of the data strobes (UDS,LDS) are asserted.<br/>Note that the statistic bits in the Memory Management Unit (MMU) are still<br/>updated during this cycle (see the section describing the MMU).

### Figure 1-5 Data Transfer and Bus Error Logic

### Bus Architecture

Sun-2/50 bus architecture supports a number of serial interfaces, as well as direct virtual memory access (DVMA) of the VMEbus by either the CPU or the Ethernet controller. The internal buses include the processor data and address buses, the memory data and address buses, and the I/O data bus. The VME bus is described in the Interface Logic section. Refer to Figure 1-7 for an overview of the Sun-2/50 bus architecture.

Figure 1-6 Sun-2/50 Bus Architecture

Processor Data and Address Buses The 68010 utilizes a 23-bit address bus (P.A01-23) to provide addresses to the Memory Management Unit (MMU), the boot PROMs, the VME bus interface and to the Ethernet interface. Addresses transmitted to main, video and expansion memory are sent via the P2 bus.

The processor data bus (P.D00-15) is connected to the I/O data bus (IO.D00-15) through a pair of bidirectional transceivers at U110 and U111. All on-board data transfers, with the exception of information sent to the parity error logic, are carried out on the I/O data bus.

Data transmitted between the CPU board and the optional memory expansion board is seen as P.D00-15 by the CPU and as P2.D00-15 by the memory.

| I/O Data Bus    | The I/O data bus (IO.D00-15) provides a data path between the CPU and the MMU, the VME bus data port and all input/output devices. The I/O devices serviced by this bus include the boot PROMs (U500,U501), the Ethernet control logic (U700,U716,U717), the interrupt timer (U504) as well as the keyboard/mouse and RS-423 interfaces (U600 and U601 respectively). Refer to Figure 1-8 for a functional block diagram of the I/O data bus. |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | Individual I/O devices are selected by a comparator at U403. The comparator, in conjunction with the AND gate at U433, produces the chip enable signal "CE.IO-". This signal is presented to the bus decoder (U400) and to the read/write decoders (U401,U402) which then decode mapped address lines to select one of eight possible devices.                                                                                                |

|                 | Processor data is placed on the I/O data bus via the transceivers at U110 and U111. These transceivers receive read/write strobes from the PAL at U102.                                                                                                                                                                                                                                                                                       |

|                 | The I/O data bus is driven by the processor data bus on all processor-write and DVMA read-cycles. The processor data bus is driven by the I/O data bus during all DVMA-write and processor-read cycles generated by the I/O devices, the MMU and the VME bus.                                                                                                                                                                                 |

| Memory (P2) Bus | The P2 bus allows addresses and data to be transferred between the CPU and the main memory, video memory and the optional expansion memory. The P2 bus consists of address lines (P2.A00-23), bidirectional data lines (P2.D00-15) and miscellaneous control signals. The memory control signals include the row address strobes (RAS, RAS0, RAS1), the column address strobe (CAS), the read strobe (RD) and the write strobes (WEL, WEU).   |

|                 | RAS is asserted when the processor address strobe and clock are both active.<br>This is the case when the processor has reached a specified state. Once RAS has<br>been asserted, it is latched until a later specified state or until the address strobe is<br>deasserted.                                                                                                                                                                   |

|                 | CAS is asserted at a specified processor state on non-special cycles only. During<br>a special cycle (refer to Appendix A), CAS is inhibited by the signal SPECIAL.<br>The column address is inhibited because, during memory management updates, it<br>is not guarenteed to be stable and could result in invalid memory decoding.                                                                                                           |

|                 | The write strobes (WEL, WEU) are the product of the memory write signal (P2.WR-) from the decoder at U400, and the upper and lower data strobes (LDS, UDS). The write strobes are asserted with a specified processor state and while the data strobe (DS-) is active. The write strobes are turned off when LDS and UDS are deasserted.                                                                                                      |

|                 | P2 bus access is controlled by the decoder at U400. A read or write reference to<br>the P2 bus is generated when the following conditions are met: the page type<br>field is 0 or 1 (refer to the description of the MMU logic), the data strobe is<br>asserted, the specified processor state is asserted and no bus error conditions<br>exist.                                                                                              |

|                 | During a memory bus read-modify-write cycle, the processor address strobe, as well as the row and column address strobes, are asserted for the entire cycle.                                                                                                                                                                                                                                                                                  |

|                 | <b>4</b>                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Both RAS and CAS are asserted before the page map type field is decoded by          |

|-------------------------------------------------------------------------------------|

| U400 and before the protection field is evaluated. As a result, CAS will indicate a |

| valid address, but not necessarily a valid reference. The read/ write strobes       |

| (RD,WEL,WEU) qualify the reference.                                                 |

Parity Error Logic

The parity error logic generates and checks parity during read/write cycles to main or expansion memory. This logic is not used during any other bus cycle and is not used during read/write cycles to the video memory.

Odd parity is generated, during memory write cycles, by the parity generators at U420 and U421. Inputs to these generators are supplied by the processor data bus (P.D00-15) and by the system enable register at U512 (EN PARGEN).

Parity is monitored during read operations by the parity checkers at U422 and U423. A parity error (even parity) results in the assertion of the EVEN output from one or both of the checkers. These signals are clocked into a pair of parity error flipflops (U424) during the memory read cycle, which in turn generate the parity error signals PARERRU- and PARERRL-.

The parity error signals are ORed at U130 with other error conditions to produce ERROR, which is used by the PAL at U103 to assert a bus error state (BERR) to the processor.

Parity errors, unlike other bus errors, cannot abort the current CPU cycle. Because a parity error can only be detected at the end of the read cycle, its existence is not recognized by the processor in time to abort the cycle. The parity error logic provides a means of retaining the error state until it can be recognized by the processor.

In order to ackowledge a bus error (caused by a pending parity error), the CPU must execute a non-special cycle. During this cycle, the PAL at U103 will assert the signal BERRCLK, which clocks the parity error state into the parity error register at U511. PARCLR is also asserted by the PAL to clear the parity error flipflops at U424.

•

Figure 1-7 I/O Data Bus

14

.

### Video Logic

The video logic consists of 128K bytes of memory, the memory controller, the video sync control circuitry, address decode logic, memory (P2) bus interface logic and the video shifter. Figure 1-9 provides a functional block diagram illustrating the video logic.

Figure 1-8 Video Logic

Video Memory and Address Decoding

Video memory (U1700-1707, U1710-1717) is located on the CPU board and is configured as 16K words of 64 bits each. The memory is dual ported to allow access by both the processor and the video refresh logic. Processor update cycles read 16 bits at a time, and write either 8 or 16 bits. Video refresh cycles read 64 bits at a time.

Processor cycle addresses are transmitted via the P2 bus, with the incoming row and column addresses stored in registers at U1632 and U1633 respectively. The video cycle addresses are generated by address counters at U1630 and U1631, and input to a pair of registers at U1640 and U1641. During video refresh, the address counters are incremented every 640nsec with an output enable signal from the decoder at U1728. The refresh counters are reset with the signal V RESET, generated by the video controller register at U1812.

Data is transmitted between the video memory and the P2 bus by the bidirectional bus transceivers at U1730-1737. Outgoing data, to the video shift logic, is latched by registers U1720-1727.

| Vidco Memory Controller      | The video memory controller supplies timing pulses to the memory and its asso-<br>ciated logic. The memory controller is a state machine consisting of two PROMs<br>(U1604, U1605) and a pair of registers (U1606, U1607). The state machine has a<br>total of 16 states (STATE 0-15), which are continuously executed in sequence.<br>Each state has a duration of 40nsec, making the entire 16-state sequence 640nsec<br>long. Timing for this control logic is provided by clock pulses derived from the<br>100MHz oscillator at U1800.                                               |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                              | The memory controller is capable of executing three types of cycles: idle, processor update and video refresh (refer to Appendix A). Idle and processor update cycles are executed in the first eight states; the refresh cycle is executed in the last eight. If no memory requests are pending, the memory controller will execute idle cycles. During these cycles no memory control signals are asserted.                                                                                                                                                                            |

|                              | A synchronous request (V SREQ), output from the request flipflops at U1624, causes the memory controller to execute a processor update cycle. During this cycle, the controller outputs the enable signals PRA and PCA to the row and column address registers (U1632, U1633). These signals ensure that both address registers are enabled in time for the video row and column address strobes (V.RAS, V.CAS).                                                                                                                                                                         |

| Video Sync Control Circuitry | The video sync control circuitry is composed of the horizontal and vertical state machines (U1810-1811 and U1813-1815 respectively) and the video controller latch (U1812). This logic generates horizontal and vertical sync signals for use by the video monitor.                                                                                                                                                                                                                                                                                                                      |

|                              | The horizontal counter at U1810 is incremented every 640nsec, on the falling<br>edge of the memory controller signal V.HCLK. Counter outputs are presented to<br>the horizontal decode PROM at U1811, along with VBLANK from the vertical<br>state machine. The decode PROM generates the control signals horizontal clear<br>(V.HCLR), horizontal sync (V.HSYNC) and display enable (V.DISPEN).<br>V.HCLR provides a reset signal to the counter at U1810. V.HSYNC is used to<br>clock the vertical state machine. V.DISPEN is sent to the video shift logic.                           |

|                              | The vertical counter (U1813, U1814) is incremented on the falling edge of hor-<br>izontal sync (V.HSYNC). Counter outputs are presented to the vertical decode<br>PROM at U1815, which decodes the counter states to produce the signals V.Vo-<br>3. These signals are latched by the video controller latch (U1812) and output as<br>vertical sync (V.SYNC), video clear (V.CLR), vertical blank (V.VBLANK) and<br>video reset (V.RESET).                                                                                                                                               |

| Video Shift Logic            | The video shift logic is composed of a pair of 50MHz shift registers (U1805, U1806), a TTL-to-ECL converter (U1807) and a 100Mhz shift register (U1809).                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                              | Video data (V.D00-07) is output from the video memory, via registers at U1720-<br>1727, and loaded into the shift registers at U1805 and U1806. These registers<br>shift out the even (U1805) and odd (U1806) bits, outputting them as V.VID0 and<br>V.VID1 respectively. Each pair of even and odd bits, together with 10nsec and<br>20nsec clock pulses (derived from the 100MHz oscillator at U1800), is loaded<br>into the TTL-to-ECL converter at U1807. This converter outputs both true and<br>inverted ECL data to the shift register at U1809. The shifted differential outputs |

(VIDEO+, VIDEO-) are terminated with 390ohm resistors at R1800 and R1801.

The video interface to the memory bus consists of data input/output registers, the Video Interface to the Memory video control registers and associated logic. Data transmitted over the P2 bus to (P2) Bus the video logic is latched by the data input registers at U1600 and U1601. Video data sent to the P2 bus is latched by data output registers U1602 and U1603. The data input strobe (V.REQ) and the data output register enable line (V.RD-) are generated by the Control PAL at U1620. The output register clock (V.ACK) and the input register enable signal (V.WU-) are produced by the video memory controller and the RAS decoder PAL (U1616), respectively. The video logic responds to three types of memory accesses: direct reads, direct writes and copy writes. Direct reads and writes are selected via the bus select decoder at U1621. The decoder uses the four most significant P2 bus address bits (P2.A20-23) to generate the video bus select signal V.BSEL. V.BSEL is input to the control PAL at U1620, which then generates a video request signal (V.REQ). A copy write is executed when two conditions are satisfied: the copy comparator at U1623 successfully matches P2 address bits A.17-22 with video base address bits V.BASE1-6, and the control PAL (U1620) is in copy mode. Following a successful address match, the copy comparator asserts the select signal V.CSEL. This signal is input to the control PAL, along with P2 address bit A17, to generate read/write strobes (V.WLC,V.WUC) for the control registers at U1610 and U1611. Data is written to the video memory when the external write strobes (LDS,UDS) Video Write Cycles are asserted by the request latch at U1615. These signals are input to the RAS decoder PAL at U1616. The decoder PAL generates enable signals (V.WU, V.WL) for the bus transceivers (U1730-1737) and data input registers (U1600-1601), as well as row address strobes (RAS0-3) for the memory. Refer to Figure 1-9 for a block diagram supporting this logic. P2 bus data (P2.D00-15) is received by the data input registers and is driven, via the bus transceivers, to the video memory. A read cycle is executed if no write strobes (LDS,UDS) are asserted. The request Video Read Cycles latch (U1615) outputs bank select signals 1 and 2 (V.BS1,2), which are decoded by the PAL at U1616 to address a word in memory. The video data is transmitted from memory to the bus transceivers at U1730-1737. The transceiver output (V.B00-15) is strobed into the data output registers (U1602,1603), and onto the P2 bus, by V.ACK from the memory controller (refer to Figure 1-9). A video refresh cycle is performed during the last eight states of every memory Video Refresh Cycle controller execution sequence in order to refresh the data stored in the dynamic RAM. During this cycle, the signals video row address (VRA-) and video column address (VCA-), from the memory controller, provide output enables for the video address registers at U1640 and U1641 respectively. With the assertion of these signals, the address registers latch values from the address counters

(U1630,1631) and transmit them to memory. All write data is stored in a set of registers, allowing the processor to write to Video to Memory (P2) Bus Data memory without waiting for a port to become available. The write cycle is Transfers automatically completed when the register data is strobed into memory. A second write cycle can only be initiated after the first write operation has been completed. The signal P2.WAIT, output by the latch at U1816, inhibits subsequent writes until the current write operation is completed. P2. WAIT is also used during the unbuffered read cycle to inhibit the processor read-data request until the data is available. This is also the case when a read request is pending while a write cycle is still in progress. The video read/write handshake is implemented by the register control PAL at U1620. The PAL receives bus select signals V.BSEL and V.CSEL, from the bus access decoder (U1621) and copy comparator (U1623) respectively. These signals are used to assert the video request line V.REO, which clocks addresses and control information into the processor address registers (U1632, U1633), and into the request latch (U1615). V.REQ is also input to the sync request registers at U1624 to produce the video state request signal V.SREO. The state request signal is, in turn, presented to the memory controller logic, where it determines what cycle (processor or idle) will be performed. Video interrupts are generated by the flipflop at U1803. The flipflop is clocked on Video Interrupts the leading edge of V.VBLANK, from the vertical state machine. The outputs are asserted whenever the interrupt enable signal (V.INTEN), from the video control register, is active. The interrupt signals V.INTREQ and V.IRQ are output to the video control register and the processor respectively.

| Memory                                   | <ul> <li>Sun-2/50 memory is composed of the following logic:</li> <li>Memory Management Unit</li> <li>Direct Virtual Memory Access Logic</li> <li>Physical Memory (Main and Expansion)</li> <li>Address Decoding</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Overview of Sun-2 Memory<br>Architecture | Sun-2/50 memory architecture is based on the concept of virtual memory, in which the physical memory resident on the PCBs (1-4MB) represents only a small amount of the memory space addressable by the CPU. The balance of the maximum virtual memory space is located on a secondary storage device (e.g. a large capacity disk drive) located elsewhere on the network.                                                                                                                                                                                                                                                                                                                                                                                                |

|                                          | When the CPU attempts to access a virtual memory address location that is not<br>currently residing in physical memory, the access is temporarily suspended until<br>the data is fetched from the secondary storage device. When the physical<br>memory is updated, the suspended access is completed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                          | Addressable memory is arranged in 2K byte pages, with 16 pages comprising a 32K byte segment. Eight contexts may be mapped concurrently, each context having a maximum virtual address space of 16M bytes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

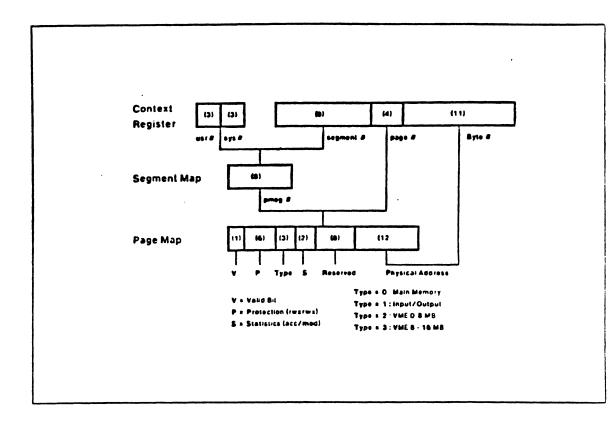

| Memory Management Unit<br>(MMU)          | The MMU consists of a user context register (U300), a system context register (U301), a user/system context multiplexor (U302), the segment map RAMs (U303, U304), the page map RAMs (U305-310) and associated logic. Refer to Figure 1-10 for a functional block diagram supporting this logic and to Appendix A for definitions of MMU terms.                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                          | The MMU is accessed by the lower and upper byte decoders (U322 and U323 respectively) and by the read decoder (U324). All three decoders use the processor address bits P.A01-3 to generate read and write decode signals for the MMU logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                          | During an address translation cycle, the function code from the CPU is used to select either the user or the supervisor context. The context value, output from either the user or supervisor context registers (U300 and U301 respectively), is presented to the multiplexor at U302. The multiplexor outputs, together with processor address lines P.A15-23, are input to the segment map RAMs at U303 and U304. The segment map RAMs use these inputs to produce a page map entry group, which in conjunction with address lines P.A11-14, is used to index the page map RAMs (U305-310). The page map RAMs generate an output composed of mapped address lines and a number of status bits (refer to Figure 1-10) which provides addresses to the CPU and to memory. |

|                                          | The validity of the protection field (PROT 0-5) is checked by the multiplexor at U315. If the protection bits are not set in accordance with the state of read/write line and the processor function codes, the output PROTERR (protection error) is asserted. This signal is presented to the bus error register at U130.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                          | The accessed and modified bits (refer to Figure 1-11) are updated on all nonspe-<br>cial cycles. The update is initiated when the current type field is input to the<br>update register at U316. The update PAL at U103 asserts WR.UPDATE, which<br>supplies a write enable signal to the page map RAM at U307, as well as                                                                                                                                                                                                                                                                                                                                                                                                                                                |

WR.STAT, which output enables the update register. The update register then writes the new data (TYPE0, TYPE1) to the page map RAM.

Figure 1-9 MMU Logic

#### Figure 1-10 Sun-2 Memory Management

Main Memory

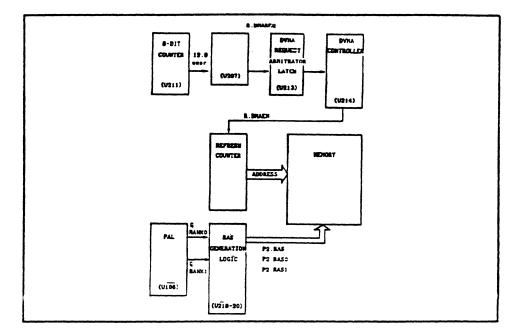

This circuit description is applicable to both the main memory and to the optional expansion memory. Main memory is located on the CPU board and provides the system with 1Mbyte of dynamic RAM. The expansion memory is located on the Memory Expansion board and supplies up to 4Mbytes of additional dynamic RAM storage.

Both main and expansion memory are organized as eight banks of eighteen chips each, for a total of 144 chips. Each bank is capable of storing a 16-bit data word along with two parity bits. The dynamic RAM may be either 64K or 256K bits per chip, providing memory capacity ranging from 1 to 4Mbytes.

The memory is arbitrarily divided into 1Mbyte sections: The first megabyte is always enabled, the second megabyte is enabled when pins 1 and 2, on select jumper J1201, are shunted. The third and fourth megabytes are selected as a pair, when pins 3 and 4 of select jumper J1201 are shunted. Refer to Appendix B for the location of the select jumper.

Address decoding for main and expansion memory is virtually identical: The memory select decoder at U1200 uses the three most significant bits from the P2 bus (P2.A20-22), as well as the configuration of select jumper J1201, to determine if the section being addressed is enabled. If the selected section is enabled, the decoder will output a memory select signal (M.SEL) to the CAS decoder at U1201, and to the read/write decoder at U1202. The read/write decoder will then enable the read/write buffers (U1210-1214) via either M.RD or M.WR, allowing

data to be transferred to and from memory over the P2 bus.

Note that the row address strobe (RAS) is not enabled during the bank select operation. Because of the pipelined RAS-CAS access, the address bits used to select which bank of memory is accessed are only available in time for the column address strobe (CAS).

Each bank of RAM receives an eight-bit address (A0-7) and the control signals RAS, CAS, WEL and WEU. The address is output from the read/write buffers (U1210-1214) and driven to the RAM inputs by line drivers (U1319,1339,1359 and 1379) through 330hm series terminators (U1318, 1338,1358 and 1378).

CAS signals for each bank (M.CAS0-7) are driven directly to the RAM by the CAS decoder at U1201. RAS signals (P2.RAS,0,1) from the RAS generation logic, and the upper and lower byte write strobes (WEL,WEU) from the read/write decoderat U400, are driven to the RAM via a bank of line drivers (U1220,1222,1224 and 1226). Refer to Figure 1-12 for a functional block diagram supporting this logic.

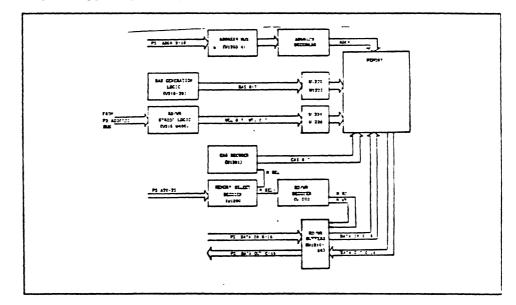

Direct Virtual Memory Access (DVMA) Direct virtual memory access allows other devices to read from and write to the Sun-2/50 memory without interrupting the current CPU process. The DVMA controller logic obtains the processor bus from the CPU and performs the read/write cycle for the requesting device. The DVMA logic accepts requests from the memory refresh logic, the Ethernet controller and the VME bus.

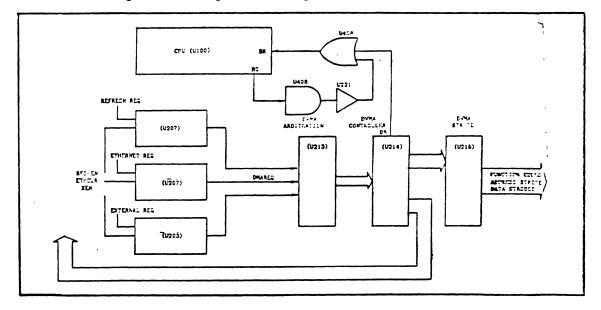

The DVMA control logic is composed of the request flipflops (U207, 203), the request arbitrator latch (U213), the controller PAL (U214) and the strobe PAL (U215).

The request flipflops receive clock pulses from the memory refresh logic (R.REQ), the Ethernet control circuitry (E.DS) and the VME bus slave interface

(X.DMA). When one of the clock pulses is asserted, the flipflops generate the appropriate DMA request and present it to the DVMA request arbitrator latch at U213. The latched request signal is input to the DVMA controller PAL (U214), which prioritizes the request and issues a bus request signal (BR) to the CPU. The CPU responds with a bus grant signal (BG) and the deassertion of the processor address strobe (P.AS). The controller PAL then sends DMA enable signals to the requesting device and to the strobe PAL at U215. The strobe PAL provides the function code for the processor, as well as address and data strobes for the requesting device. Refer to Figure 1-13 for a functional block diagram of the DVMA control logic.

Memory refresh cycles are generated every 12.8usec by the 8-bit counter at U211. The counter output provides a clock for the request flipflop at U207, which issues a refresh DMA request signal (R.DMAREQ) to the associated DVMA control logic. The control logic outputs a DMA enable signal (R.DMAEN) to the refresh counter at U210, causing a "row address" refresh address to be presented to the dynamic RAMs. The PAL at U106 insures that both banks of memory are enabled during the refresh cycle by asserting the signals BANK0 and BANK1 to the RAS generation logic (U218-20). The RAS logic transmits the signals RAS, RAS0 and RAS1 to the RAM. Refer to Figure 1-14 for a functional block diagram illustrating the refresh logic.

Figure 1-12 DVMA Control Logic

Figure 1-13 DVMA Memory Refresh Logic

4

Interface Logic

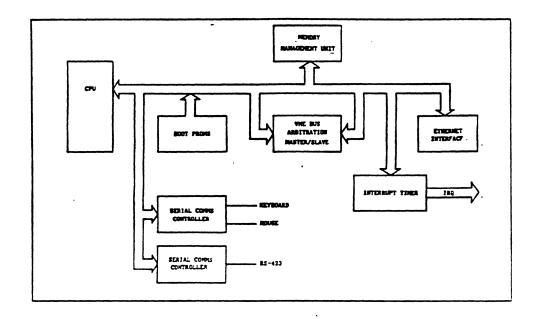

Serial Communications

The interface logic consists of the serial ports for keyboard, mouse and RS-423 communication, as well as the Ethernet and VME bus interfaces.

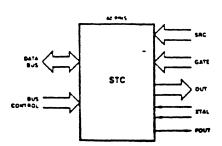

Serial communications between the Sun-2/50 and the keyboard, mouse and RS-423 interface is provided by a pair of Z8530 Serial Communication Controllers (SCCs). The SCC at U600 controls the keyboard and mouse, while the SCC at U601 supports the RS-423 interface.

Timing for both SCCs is provided by a 4.9152MHz clock, derived from the 19.6608MHz oscillator at U200. Chip select lines for the SCCs are supplied by processor address lines P.A01 and P.A02. Read/write control signals are provided by the read/write decoders at U401 and U402. Channels A and B, of the SCC at U600, are assigned to the keyboard and mouse respectively. Channels A and B, of the SCC at U601, correspond to ports A and B of the RS-423 interface.

Data being sent off-board is received by the SCCs over the I/O data bus as IO.D08-15. This data is converted from parallel to serial and transmitted to the selected device via dedicated RXD and TXD lines. For incoming serial data, the process is reversed.

Incoming RS-423 data is driven onto the board by the line receivers at U606 and U607. Outgoing data is driven onto the RS-423 interface by line drivers at U609 and U611. The line receiver at U615 is shared between channels A and B in order to support synchronous SCC applications.

Refer to Figure 1-15 for a functional block diagram supporting the serial communications logic.

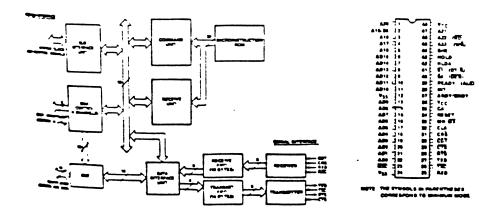

### Ethernet Interface

The Ethernet interface consists of the Ethernet controller (U700), a phase lock loop decoder (U701), the control registers (U716-7) and associated logic. Refer to Figure 1-16 for a functional block diagram supporting the Ethernet interface logic.

Ethemet control is provided by an Intel 82586 Local Area Network Coprocessor. This device implements the Carrier-Sense-Multiple-Access-with-Collision-Detection method of link management (refer to Appendix A), which allows multiple workstations to access the local area network (LAN) at will.

The phase lock loop decoder at U701 acts as an Ethernet encoder/decoder circuit. This decoder connects the Sun-2/50 directly to an external Ethernet transceiver. Outgoing TTL-level data is encoded as transceiver-level code and placed on the Ethernet. Incoming Ethernet data is decoded into TTL-level data and clock signals. The decoding method employs a phase-locked loop approach with 10 samples per bit cell. Sample rate timing is provided by an external crystal (X700) and its associated tank circuit, which provide a 100MHz clock to the decoder's internal oscillator. Either Ethernet level 1 or level 2 interface characteristics may be supported via the select jumper at J704. Refer to Appendix B for the select jumper location.

The Ethernet control registers (U716, U717) manage the overall operation of the Ethernet interface. Inputs to these registers include an error signal from the bus error register (U719) and four bits from the I/O data Bus. The control registers generate interrupt, DVMA request, loopback and reset signals for the Ethernet interface logic.

Figure 1-15 Ethernet Interface logic

Ethemet DVMA Cycle

An Ethernet memory access is initiated by the assertion of a read (RD) or write (WR) signal by the Ethernet controller (U700). These signals are ORed at U718 to produce an Ethernet data strobe (DS), which is used to clock the DVMA request flipflop at U207. The flipflop outputs the request signal E.DMAREQ to the DVMA control logic. The control logic also receives the Ethernet request signal E.REQ. This signal is the result of ANDing HOLD, from the Ethernet controller and E.ERR, from the bus error register. With these signals asserted, the DVMA arbitrator (U213) will continuously request the bus from the CPU until the Ethernet controller deasserts HOLD.

The Ethernet data strobe (DS) is also used, via the register at U713, to produce an address strobe. The address strobe (AS) latches the 24-bit Ethernet address (P.A01-23) into the address registers at U702-4 when the enable signal E.DMAEN is asserted by the DVMA control logic.

During an Ethernet write to memory, the DVMA control logic will provide an output enable signal (E.OE) to the write data buffers at U707 and U708. Data, from the Ethernet controller (U700) is input to the buffers and driven onto the I/O data bus as IO.D00-15.

During an Ethernet read from memory, data is latched into the read buffers at U705 and U706 by the write enable signal E.WE. The buffers are output enabled, driving I/O bus data to the Ethernet controller inputs, by the Ethernet read line (E.RD) issued from the DVMA control logic.

The Ethernet read and write buffers are byte swapped between the I/O data bus and the Ethernet data bus: I/O bus data bits 0-7 correspond to Ethernet bus data bits 8-15 and vice versa.

Ethernet bus errors are flagged by the bus error register at U719. In the event of a bus error, this register transmits the error signal E.ERR to the Ethernet control registers (U716-7) and to the DVMA request register (U207). The E.ERR signal inhibits any future DVMA requests from being sent to the DVMA control logic. DVMA requests are inhibited until the bus error register is cleared by a reset signal (RESET) from the Ethernet control registers.

VME (P1) Bus InterfaceThe VME bus interface provides the Sun-2/50 with bidirectional data access to<br/>any device attached to the VME bus. As the bus master, the CPU may access any<br/>of the slaves on the bus. As a bus slave, the Sun-2/50 may be accessed by other<br/>VME bus masters. Refer to Figure 1-17 for an illustration of the VME bus data<br/>transfer sequence.

The VME bus interface logic is composed of the arbitration and request circuitry, the VME master interface and the VME slave interface.

VME bus utilities are implemented using four control lines: system clock (SYSCLK), AC fail (ACFAIL), system reset (SYSR) and system fail (SYSF).

SYSCLK is derived from the 16MHz oscillator at U202. This signal is driven onto the VME bus by a high-current driver at U817. This clock signal has no phase relationship to other VME bus signals and may be disconnected by removing the shunt from pins 15 and 16 of select jumper J900. Refer to Appendix B for the location of the select jumper.

ACFAIL is derived from the power-on/reset signal POR and is driven onto the VME bus by the driver at U818.

System reset (SYSR) is driven onto the bus by the driver at U818 and is asserted whenever processor reset (P.RESET) is active. When configured as a bus master, the Sun-2/50 issues a reset signal to the VME bus with RESOUT. RESOUT is asserted as the result of a power-on reset, a processor reset or a watchdog reset. As a bus slave, the Sun-2/50 receives a reset signal (RESIN) from the VME bus.

VME Bus Arbitration and Request Logic The arbitration and request logic consists of two PALs (U811, U814) and a pair of registers (U812, U813). Bus request levels are monitored and requests arbitrated using a level daisy chain (refer to Appendix A). A CPU bus request (in order to perform a read/write cycle, or to ackowledge an interrupt) is initiated with the assertion of a bus select signal (BSEL) to the PAL at U811. If the arbitor does not have control of the bus, it will request mastership by asserting the VME bus request signal BREQ and implement a normal bus arbitration sequence. If the arbitor currently controls the bus, it will keep control until another bus master requests it.

VME Master Interface

Once the arbitration logic has obtained bus mastership, the VME master interface allows the CPU board to access any slaves on the VME bus. The master interface is composed of address/address modifier latches (U940-03), a bank of address drivers (U900-03), write data registers (U910-11), write data drivers (U912-13), read data buffers (U908-09) and a control line driver (U817).

The VME slave device being addressed will respond to the data transfer with either an acknowledge signal (DTACK) or a bus error flag (BERR). These signals are latched at U815 and input to the PAL at U816, where they are transmitted to the CPU.

The VME master interface utilizes its backoff/rerun capability in response to VME bus deadlocks and VME accesses that take longer than 2-3usec. A VME bus deadlock results when the CPU attempts to access the VME bus while another bus master is concurrently trying to access the CPU as a slave device. Because the VME bus has no rerun capability, it requests that the CPU resolve the deadlock.

When a VME access is not completed within the specified time limit, or the bus is deadlocked, the state of the VME interface is frozen and a CPU rerun cycle is initiated. During the rerun cycle, the processor may relinguish the bus to the Ethernet interface or to the refresh logic, allowing those devices to execute their functions. The rerun cycle is then ended and the processor continues with the VME access. Rerun cycles are transparent to the VME bus and may also be performed while the CPU is waiting for bus mastership.

Conditions requiring a rerun cycle are recognized by the PAL at U810, which issues a bus rerun signal (B RERUN). This signal is input to the PAL at U102, which generates bus error (BERR) and halt (P.HALT) signals for the processor.

Rerun operations are monitored by a counter at U809. When the count reaches 128, a TIMEOUT signal is asserted to the bus error register (U130).

The VME slave interface allows the CPU board to be accessed by other VME bus masters. A number of conditions must be met before the slave interface is enabled: The address comparator at U930 must successfully match the 4-bit VME bus address (P1.A20-23) to four bits from the switch-selectable base address (X.A0-3) The VME address modifiers must be specified and set. The VME interrupt acknowledge signal (P1.IACK) must be deasserted. The CPU board cannot currently be the bus master, and both the VME address (X.AS) and data (X.UDS,X.LDS) must be asserted. When all of the preceding conditions are met, the signal X.DMA is asserted by the comparator, indicating that a VME slave interface is pending.

When another bus master requests access to the CPU board, the DVMA control logic treats the access as an external DVMA request. When the DVMA control logic receives X.DMA, it initiates an on-board fetch cycle using the external DVMA address held in the registers at U904-06.

During a VME bus write cycle, VME data is placed onto the I/O data bus via the data buffers at U908 and U909. During a VME bus read cycle, data from memory is latched in registers at U910 and U911 and driven onto the VME bus

VME Slave Interface

by data buffers at U912 and U913. The data transfer handshake is completed on the trailing edge of the enable signal (X.DMAEN) from the DVMA control logic. The handshake register at U931 will then assert either an acknowledge signal (X.DTACK) or, in the event of a bus error, the error signal X.BERR. The transfer signal X.DMA, from the comparator at U930, remains asserted until the VME bus master deasserts the data strobes. The handshake register (U931) is cleared on the falling edge of X.DMA.

#### VME Interrupt Control

There are seven VME bus interrupt lines, designated P1.IRQ1-7. All seven lines pass through a select jumper at J800 (refer to Appendix B), allowing any combination of interrupt levels to be selected. The selected interrupt lines are input to the priority decoder at U800, which prioritizes the interrupt requests and outputs the encoded interrupt lines B.IPLO-2. These lines are combined with on-board interrupt requests at the inputs of PROM U105, which produces the processor interrupt signals IPLO-2.

Upon receiving an interrupt request, the CPU generates the appropriate function code for the PAL at U101 and transmits the interrupt level being acknowledged on address lines A01-3. The multiplexor at U802 monitors A01-3 and the interrupt lines IRQ1-7, to determine if the pending interrupt is from an external source.

Figure 1-16 VME Bus Data Transfer Sequence

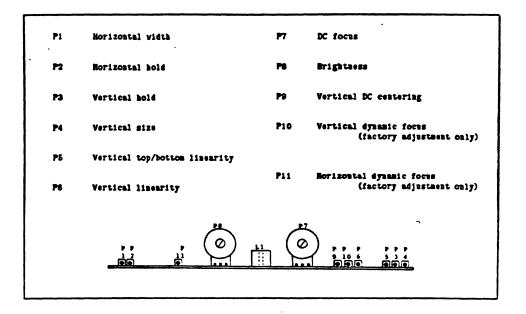

| ther<br>inpu<br>• H<br>• V<br>• E                                  | e Sun-2/50 is configured with either a Phillips or a Moniterm monitor. While<br>re are minor differences between the two, both monitors receive the following<br>uts:<br>Horizontal Sync (HSYNC)<br>/ertical Sync (VSYNC)<br>SCL Video (VIDEO+,-)<br>20/240 AC                                                                                                        |

|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The                                                                | video monitors share the following operational characteristics:                                                                                                                                                                                                                                                                                                       |

| isplay-<br>lock-<br>al Cycle-<br>Cycle-<br>al Retrace-<br>Retrace- | 900 horizontal lines with 1152 pixels per line (Version A)<br>1024 horizontal lines with 1024 pixels per line (Version B)<br>10nsec from 100MHz oscillator<br>16.00usec 62.5KHz<br>15000usec 66.67Hz<br>4.48usec<br>600usec                                                                                                                                           |

| Tro<br>ced                                                         | nitor adjustment procedures are provided in Chapter 2, Diagnostics and<br>publeshooting. Comprehensive hardware descriptions and maintenance pro-<br>ures are to be found in the monitors' respective service manuals (refer to the<br>of applicable documents).                                                                                                      |

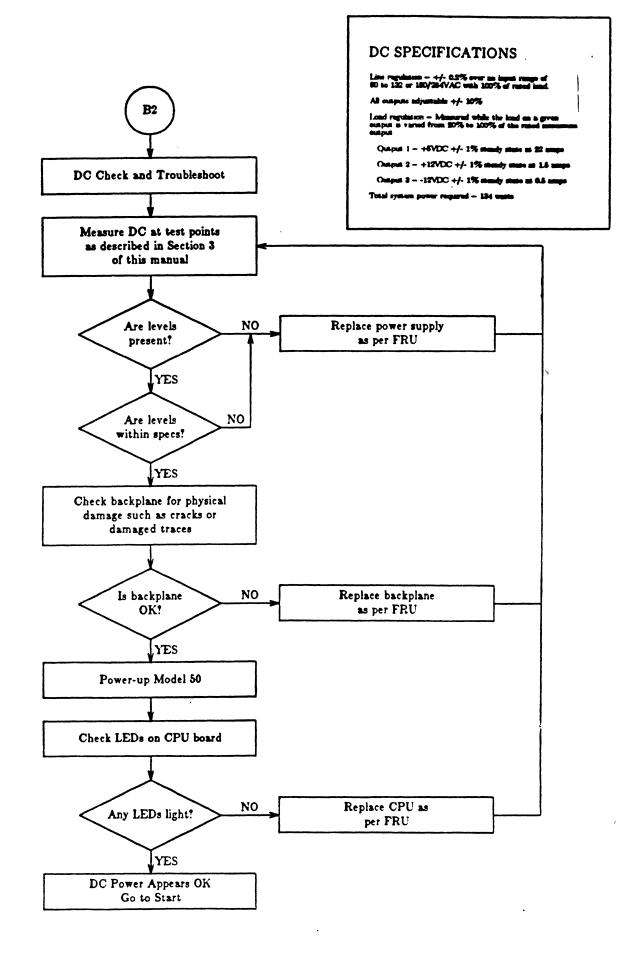

| the<br>+12<br>pov                                                  | wer for the Sun-2/50 is provided by a single-board power supply, located in<br>workstation chassis. The supply generates three regulated voltages, +5VDC,<br>2VDC and -12VDC, which are available at the system backplane. Refer to the<br>wer supply removal procedure in chapter 3 for a wiring diagram showing the<br>upply outputs and their respective voltages. |

| The                                                                | e power supply operating specifications are as follows:                                                                                                                                                                                                                                                                                                               |

| AC Inputs-                                                         | 115/230VAC, 47-70Hz field selectable (Nominal)<br>90-132/180-264VAC (Operating Range)                                                                                                                                                                                                                                                                                 |

| DC Outputs-                                                        | Output 1, +5VDC +/-1% steady state at 22 amps<br>Output 2, +12VDC +/-1% steady state at 1.5 amps<br>Output 3, -12VDC +/-1% steady state at 0.5 amps                                                                                                                                                                                                                   |

|                                                                    | ther<br>inpu<br>• H<br>• N<br>• E<br>• 1<br>The<br>isplay-<br>lock-<br>al Cycle-<br>Cycle-<br>al Retrace-<br>Retrace-<br>Mo<br>Tro<br>ced<br>list<br>Pov<br>the<br>+12<br>pov<br>sup<br>The<br>AC Inputs-                                                                                                                                                             |

# Diagnostics and Troubleshooting

| Diagn | ostics and Troubleshooting      | 35 |

|-------|---------------------------------|----|

| 2.1.  | Overview                        | 35 |

| 2.2.  | Symptom Analysis                | 36 |

|       | Local Problems                  | 36 |

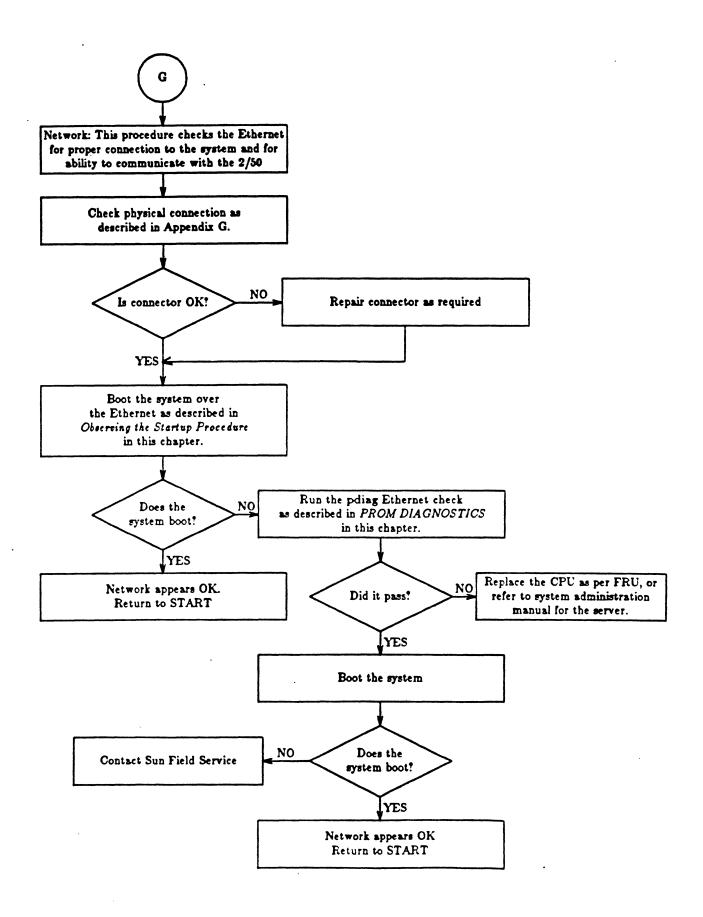

|       | Ethernet Problems               | 37 |

|       | File Server Problems            | 37 |

| 2.3.  | Observing the Startup Procedure | 37 |

|       | Startup Tests                   | 38 |

|       | Boot Device                     | 39 |

|       | UNIX Kemel                      | 40 |

| 2.4.  | PROM Diagnostics (PDIAG)        | 42 |

| •     | Installing PROMs                | 42 |

|       | Using the Diagnostics           | 43 |

|       | Automatic Tests                 | 43 |

|       | Menu Mode                       | 45 |

|       | Test Descriptions               | 46 |

|       | Context Tests                   | 46 |

|       | Startup Tests                   | 47 |

|       | Segment Tests                   | 47 |

|       | Page Tests                      | 47 |

|       | Memory Tests                    | 48 |

|       | Parity Tests                    | 48 |

|       | Video Menu Tests                | 50 |

2

| 50 |

|----|

| 51 |

| 51 |

| 51 |

| 52 |

|    |

|    |

,

.

2

### **Diagnostics and Troubleshooting**

#### 2.1. Overview

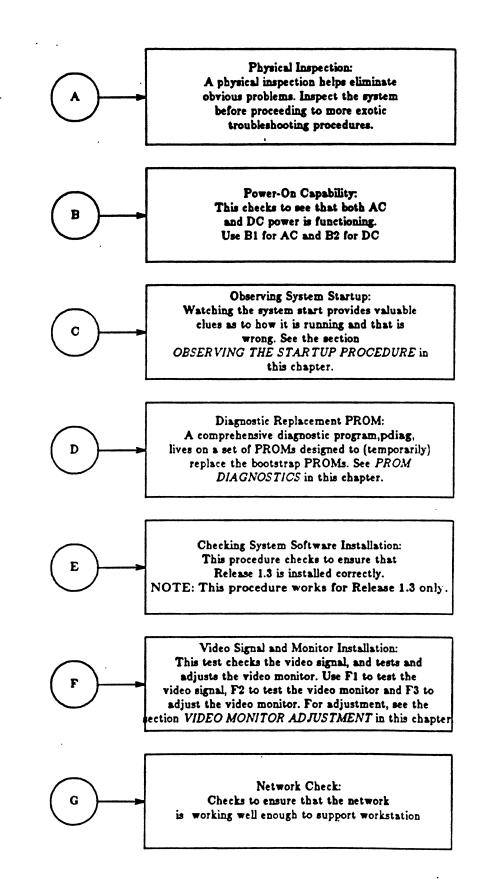

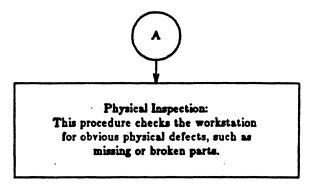

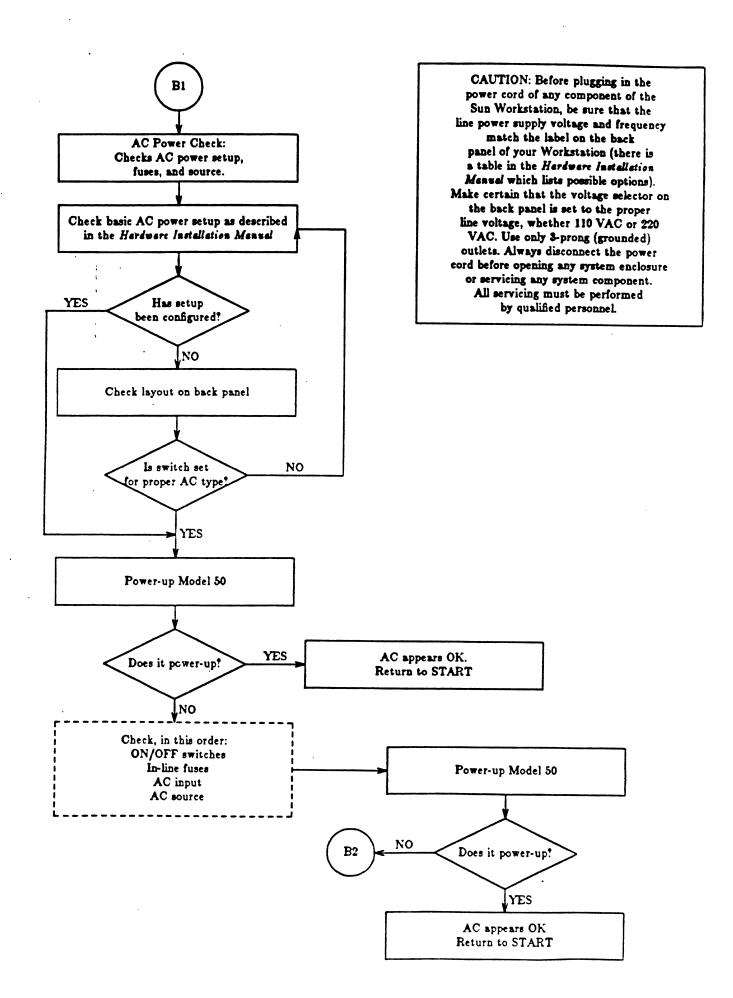

This chapter describes how to diagnose and repair problems on your Sun 2/50 workstation. It provides help for many levels of problems, ranging from simple items like checking power cords and switches, through complicated procedures like running standalone programs and PROM-based diagnostic programs.

This chapter is divided into five sections, each of which provides a different method of solving the problem. The choice of which to use depends on the nature of the problem, your experience, and the resources available.

The sections are:

- A symptom/action table this provides a list of possible problems followed by instructions describing what to do about them.