.

PB2500-9001-011

•

.

.

.

1855 Barber Lane Milpitas, CA 95035, USA

.

#### WARNING

This equipment generates, uses, and can radiate radio frequency energy and if not installed and used in accordance with the instructions in this manual may cause interference to radio communications. It has been tested and found to comply with the limits for a Class A computing device pursuant to Subpart J or Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment. Operation of this equipment in a residential area is likely to cause interference in which the user at his own expense will be required to take whatever measures may be required to correct the interference.

This digital apparatus does not exceed the Class A limits for radio noise emissions from a digital apparatus as set out in the Radio Interference Regulations of the Canadian Department of Communications.

Le present appareil numerique n'est pas de bruits radioelectriques depassant les limtes applicables aux appareils numeriques de Class A, prescrites dans le reglement sur le brouillage radioelectrique edicte par le Ministere des Communicatios du Canada.

#### **PROPRIETARY STATEMENT**

System Industries has prepared this manual for use by System Industries personnel, licensees, and customers. The information contained herein is the property of System Industries and shall neither be reproduced in whole nor in part without prior written approval from System Industries.

System Industries reserves the right to make changes, without notice to the specifications and materials contained herein, and shall not be responsible for any damages (including consequential) caused by reliance on the material as presented, including, but not limited to, typographical, arithmetic, and listing errors.

The following are trademarks of Digital Equipment Corporation:

BA23, BA123, DATATRIEVE, DEC, DECnet, DECservice, DECSYSTEM- 20, DECtape, DECUS, DECwriter, DIBOL-83, DSM-11, FMS, HSC50, FORTRAN IV, HSC70, IAS, Internet, LA, Letterprinter 100, Letterwriter 100, MASSBUS, MicroPDP-11/23, MicroPDP-11/73, MicroPower/Pascal, Micro/RSTS, MICRO/RSX, MicroVAX I, MicroVAX II, MicroVMS, OMNIBUS, Packetnet, PDP, PDT, Professional, Q-bus, QBUS, RA, Rainbow, ReGIS, RSTS, RSX, RT, SBI, SDI, UDA50, UNIBUS, ULTRIX, VAX, VAXELN, VMS, and VT.

UNIX is a trademark of AT & T Bell Laboratories

PB2500-9001

# O

#### **REVISION RECORD**

| REVISION<br>NUMBER | DATE     | DESCRIPTION                                                                                                                                                                   | EO<br>NUMBER |

|--------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 01                 | 03/11/88 | Initial Release                                                                                                                                                               | 4949         |

| В                  | 03/31/88 | Included CPA Rework to Sections 4, 6, and 9                                                                                                                                   | 5010         |

| С                  | 08/30/88 | Technical Corrections                                                                                                                                                         | 5316         |

| D                  | 01/01/89 | Technical Corrections                                                                                                                                                         | 5672         |

| E                  | 04/19/89 | Added CLUSTOR 1 and 2                                                                                                                                                         | 5888         |

| 006                | 09/26/89 | Incorporated Theta Cabinet Information<br>Incorporate New Revision-Renumbering System                                                                                         | 6190         |

| 007                | 01/22/90 | Added Megaram, SI92, SI95, and Write-back<br>Information                                                                                                                      | 6302         |

| 008                | 04/20/90 | Added SCSI Computer Interface Board Option                                                                                                                                    | 6425         |

| 009                | 10/01/90 | Deleted CLUSTOR 2. Add SI817 and SI506<br>Technical Corrections                                                                                                               | 6640         |

| 010                | 07/12/91 | Added BI Bus CPA boards (MSCP), Qbus CPA/M<br>board, 510M Drive Support, New Transition<br>Panels and Cables.<br>Deleted CLUSTOR 1 and CMI Support.<br>Technical Corrections. | 6893         |

| 011                | 09/26/91 | Technical Corrections,<br>510M Drive Changed to 510, Enhancements,<br>Additional Information on DCP Auto-Tuning                                                               | 6924         |

$\mathbf{\cap}$

Section

| 1  |

|----|

| 1  |

| 20 |

|    |

### TABLE OF CONTENTS

| 1. | INTE | RODUCTION 1-1                         |

|----|------|---------------------------------------|

|    | 1.1  | Manual Audience                       |

|    | 1.2  | Related Publications 1-2              |

|    | 1.3  | Manual Conventions 1-3                |

|    | 1.4  | Terms List 1-4                        |

|    | 1.5  | Materials Needed 1-7                  |

| 2. | CLU  | STOR SUBSYSTEM 2-1                    |

|    | 2.1  | Features                              |

|    | 2.2  | Options 2-4                           |

|    | 2.3  | Subsystem Components 2-5              |

|    |      | CLUSTOR Chassis 2-5                   |

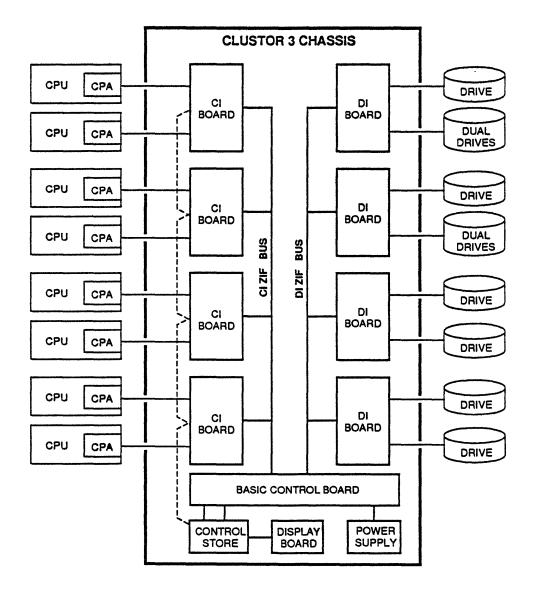

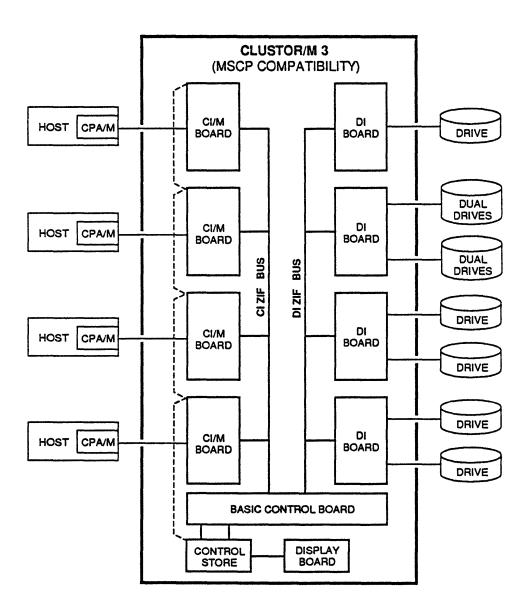

|    |      | CLUSTOR 3 and CLUSTOR/M 3 2-6         |

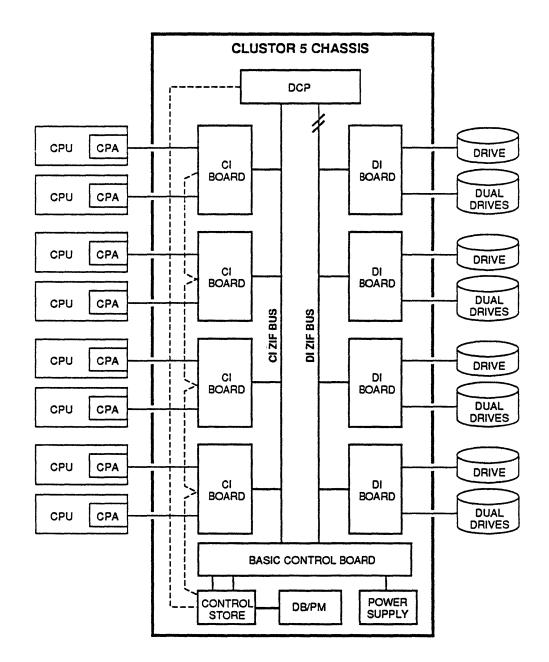

|    |      | CLUSTOR 5 and CLUSTOR/M 5 2-6         |

|    | 2.4  | CLUSTOR (M) Subsystem Boards 2-7      |

|    |      | Basic Control Board 2-7               |

|    |      | Display Board 2-9                     |

|    |      | Control Store Board 2-11              |

|    |      | Computer Interface Board2-13          |

|    |      | Drive Interface Board 2-14            |

|    |      | Disk Cache Processor Board 2-16       |

|    | 2.5  | Computer Port Adapters                |

|    | 2.6  | Disk Drives                           |

|    | 2.7  | Cabling                               |

|    |      | Internal Cabling 2-21                 |

|    |      | External Cabling2-21                  |

|    |      | Disk Drive Cabling                    |

|    |      | Computer Interface Board Cabling 2-22 |

|    |      | Long Line Adapter Cabling 2-22        |

|    |      | Cabinets                              |

| 3. | CON  | FIGURATIONS 3-1                       |

|    | 3.1  | Configuration Requirements            |

|    | 3.2  | Configuration Examples                |

|    |      | CLUSTOR 3 and 5                       |

|    |      | CLUSTOR 5                             |

|    |      | CLUSTOR/M 3 and 5                     |

|    |      | CLUSTOR/M 5                           |

|    |      | Multiport CPU 3-9                     |

|    |      | Dual-Channel Drive                    |

|    | 3.3  | CLUSTOR Board Configuration Settings  |

|    |      | Disk Cache Processor Board            |

|    |      | Computer Port Adapters                |

|    |      | Drives                                |

# Page

ę.

### TABLE OF CONTENTS

### Section

| 4. | PRE | INSTALLATION                              | . 4-1 |

|----|-----|-------------------------------------------|-------|

|    | 4.1 | Environmental and Physical Specifications | 4-1   |

|    | 4.2 | Power Requirements                        | 4-3   |

|    |     | AC Power                                  |       |

|    |     | AC Neutral                                |       |

|    |     | AC Earth Ground                           |       |

|    | 4.3 | Unpacking                                 |       |

|    | 4.4 | Site Preparation                          | 4-4   |

| 5. | INS | TALLATION                                 | . 5-1 |

|    | 5.1 | General Precautions                       | 5-1   |

|    | 5.2 | Cabinet Installation                      | 5-1   |

|    | 5.3 | Subsystem Installation                    | 5-4   |

|    |     | Inspection and Preliminary Checks         |       |

|    | 5.4 | External Cabling                          | 5-5   |

|    | 5.5 | Computer Port Adapter Installation        |       |

|    | 5.6 | Operating System Installation             | 5-5   |

|    | 5.7 | Option and Upgrade Installation           | 5-5   |

|    |     | Long Line Adapter (RM-compatible only)    | 5-5   |

|    |     | CI/M (SCSI CI) Adapter                    | 5-6   |

|    |     | Dual Channel Disk Drive                   | 5-7   |

|    |     | CLUSTOR 3 to 5 Upgrade Installation       | 5-9   |

| 6. | MAI | NTENANCE                                  | . 6-1 |

|    | 6.1 | Subsystem Maintenance                     | 6-1   |

|    |     | Resident Diagnostics                      |       |

|    |     | Disk Cache Processor Tuning               |       |

|    | 6.2 | Component Removal and Replacement         |       |

|    |     | Chassis Components                        |       |

|    |     | Power Supply Replacement                  |       |

|    |     | Fan Replacement                           |       |

|    | 6.3 | CLUSTOR (M) Boards                        |       |

|    |     | CI, DI, and DCP Board Removal             |       |

|    |     | CI, DI, and DCP Board Replacement         |       |

|    |     | CS Board Removal and Replacement          |       |

|    |     | DB and DB/PM Removal and Replacement      |       |

|    |     | BCB Removal and Replacement               |       |

|    |     | Computer Port Adapters                    |       |

| 7. | SUB | SYSTEM VERIFICATION AND TROUBLESHOOTING   | . 7-1 |

|    | 7.1 | Subsystem Verification                    | 7-1   |

|    | 7.2 | Subsystem Troubleshooting                 |       |

|    |     | Controller Faults                         |       |

# Page

•.

C

### TABLE OF CONTENTS

| Page |

|------|

|------|

|    |      | Disk Cache Processor Faults                |

|----|------|--------------------------------------------|

|    |      | Using the Disk Cache Processor Monitor     |

|    | 7.3  | VMS Error Log Entries                      |

|    |      | Q-Bus Error Log Entries 7-15               |

|    |      | eaSIshadow Error Log Entries               |

| 8. | ILLU | JSTRATED PARTS LIST 8-1                    |

| 9. | REA  | DY REFERENCE                               |

|    | 9.1  | Configuration Requirements                 |

|    | 9.2  | Disk Drive Support References              |

|    |      | Display Board                              |

|    |      | Control Store Board                        |

|    |      | Basic Control Board                        |

|    |      | Computer Interface Board (RM-emulation)    |

|    |      | Computer Interface Board (MSCP-emulation)  |

|    |      | Modes of Operation                         |

|    |      | Disk Interface Board                       |

|    |      | Disk Cache Processor Board                 |

| А. | DISI | K DRIVE SETTINGS A-1                       |

|    | A.1  | SI56 Disk Drive A-1                        |

|    | A.2  | SI57 Disk Drive A-3                        |

|    | A.3  | 9733 Disk Drive A-5                        |

|    | A.4  | SI83 Disk Drive A-5                        |

|    | A.5  | SI85 Disk Drive A-5                        |

|    | A.6  | 9751 Disk Drive A-6                        |

|    | A.7  | 9761 Disk Drive A-8                        |

|    | A.8  | SI93 Disk Drive A-9                        |

|    | A.9  | SI95 Disk Drive A-10                       |

|    | A.10 | SI92 Disk Drive A-13                       |

|    | A.11 | SI506 Disk Drive A-16                      |

|    | A.12 | SI817 Disk Drive A-17                      |

|    | A.13 | SI510M Disk Drive A-21                     |

| в. | SBI  | CPA INSTALLATION B-1                       |

|    | B.1  | SBI CPA Location                           |

|    | B.2  | Preliminary Inspection                     |

|    |      | Preliminary Checkout                       |

|    | B.3  | SBI CPA Configuration                      |

|    |      | Transfer and Bus Request Switches          |

|    |      | Internal Registers Transfer Request Switch |

|    |      | RM Emulation Jumpers                       |

|    |      | Last Drive Switches                        |

|    |      |                                            |

Page

### TABLE OF CONTENTS

### Section

|    |              | Extended Register Option                      | B-7  |

|----|--------------|-----------------------------------------------|------|

|    |              | Transfer Request Jumper (SBI Backplane)       |      |

|    |              | Reinstall the CPA Boards                      |      |

|    | B.4          | SBI Terminator Installation                   |      |

|    | B.5          | Power Supply Installation                     |      |

|    | B.6          | SBI CPA Card Cage Installation.               |      |

|    | B.7          | CPA and Power Cabling.                        |      |

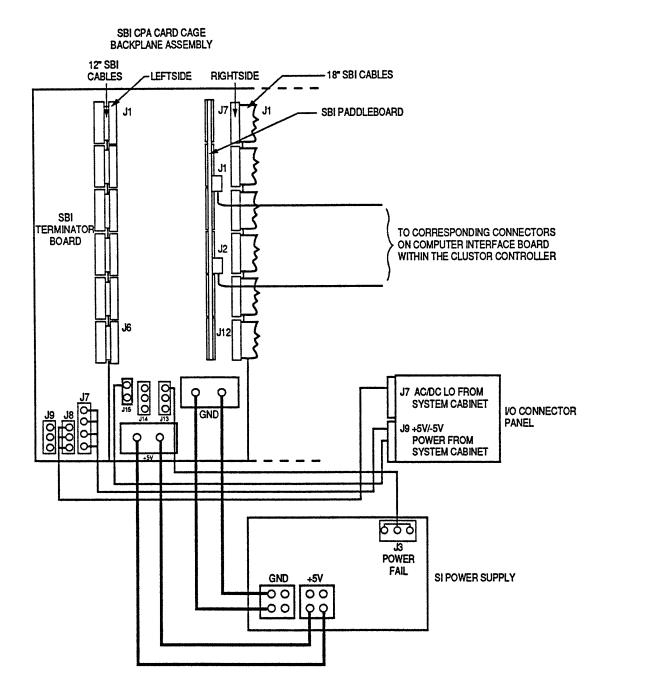

|    | B.8          | Controller to CPA Cabling                     |      |

|    | B.9          | Power Requirements                            |      |

|    | 2.0          | Power Supply Check                            |      |

|    |              | Power Fail Circuit                            |      |

|    |              | System Power-Up and Checkout                  |      |

|    | B.10         | Software Installation                         |      |

|    | B.10<br>B.11 | Installation in a VAX 8600 or 8650            |      |

|    | D.11         | General Information                           |      |

|    |              | Preliminary Checkout                          |      |

|    |              | Expansion Cabinet Installation                |      |

|    |              |                                               |      |

|    |              | Installation in One SI SBI Expansion Cabinet. |      |

|    |              | Installation in Two SI SBI Expansion Cabinets | D-21 |

| С. | <b>GBU</b>   | S CPA INSTALLATION                            | C-1  |

|    | C.1          | Preinstallation Inspection                    | C-1  |

|    | C.2          | CPA Board Configuration                       |      |

|    |              | Control Status Register (CSR) Address         |      |

|    |              | Interrupt Vector                              |      |

|    |              | Transfer Mode                                 |      |

|    |              | Interrupt Levels                              |      |

|    | C.3          | Installation Materials                        |      |

|    | C.4          | Installation in a BA23                        |      |

|    | C.5          | Installation in a BA123                       |      |

|    | C.6          | MicroVAX III Installation                     |      |

|    | 0.0          | Power-Down the Cabinet                        |      |

|    |              | Cabinet Rear Panel Removal                    |      |

|    |              | Open the Front Door                           |      |

|    | C.7          | BA213 Chassis                                 |      |

|    | 0.7          | Card Cage                                     |      |

|    |              | Cable Connection                              |      |

|    |              |                                               | 0 10 |

| D. | UNIE         | BUS CPA INSTALLATION                          | D-1  |

|    | D.1          | Preliminary Steps                             | D-1  |

|    | D.2          | Switch and Jumper Settings                    |      |

|    |              | Control Status Register Address               |      |

|    |              | Interrupt Vector                              |      |

|    |              | Throttle Count                                |      |

|    |              |                                               | -    |

C

### TABLE OF CONTENTS

# Section

E.

F.

|             | CPA Jumpers                                                                                                                                                                                                                                                                                                           | D-4                                                                                                             |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

|             | Bus Request Jumper                                                                                                                                                                                                                                                                                                    | D-4                                                                                                             |

|             | Bus Grant Jumpers                                                                                                                                                                                                                                                                                                     |                                                                                                                 |

|             | Nonprocessor Grant (NPG) Jumper                                                                                                                                                                                                                                                                                       |                                                                                                                 |

| D.3         | Control to CPA Cabling                                                                                                                                                                                                                                                                                                |                                                                                                                 |

| D.4         | Physical Installation                                                                                                                                                                                                                                                                                                 |                                                                                                                 |

| D.5         | Power Requirements                                                                                                                                                                                                                                                                                                    |                                                                                                                 |

|             | CPA Power Fail Circuitry                                                                                                                                                                                                                                                                                              |                                                                                                                 |

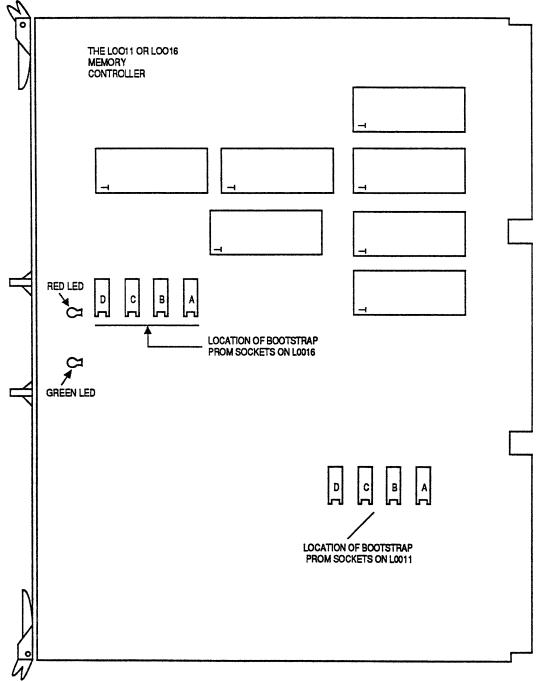

|             | Boot PROM Installation                                                                                                                                                                                                                                                                                                | D-7                                                                                                             |

| BI B        | US CPA INSTALLATION                                                                                                                                                                                                                                                                                                   | E-1                                                                                                             |

| E.1         | BI Bus CPA Jumpers and Node IDs                                                                                                                                                                                                                                                                                       | E-1                                                                                                             |

| E.2         | BI Bus CPA (Initiator) ID Selection                                                                                                                                                                                                                                                                                   | E-2                                                                                                             |

| E.3         | LED Indicators                                                                                                                                                                                                                                                                                                        | E-4                                                                                                             |

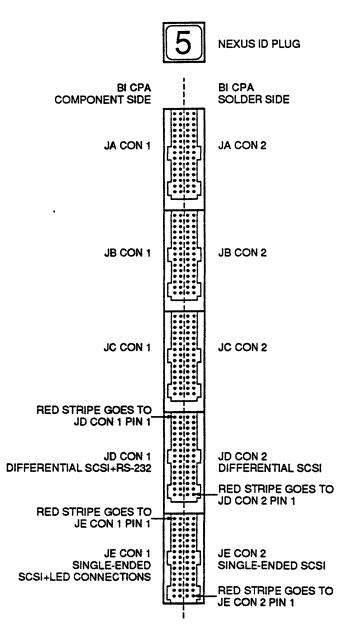

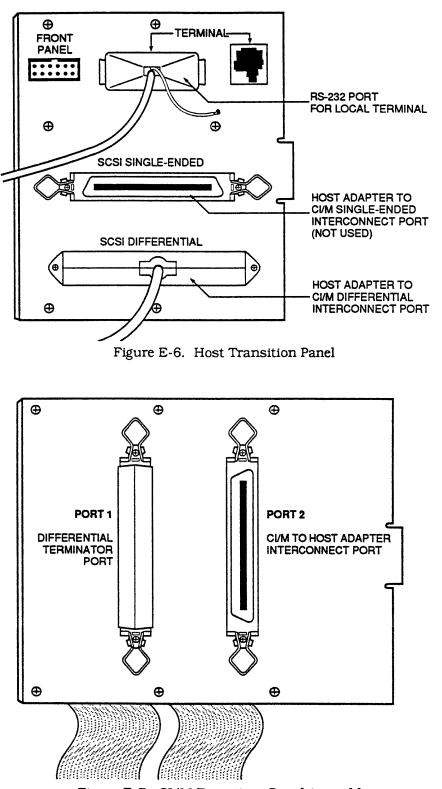

| E.4         | SCSI Bus Cabling and Termination                                                                                                                                                                                                                                                                                      | E-6                                                                                                             |

|             | BI Bus Cabling                                                                                                                                                                                                                                                                                                        |                                                                                                                 |

| E.5         | Differential SCSI Channel                                                                                                                                                                                                                                                                                             | E-8                                                                                                             |

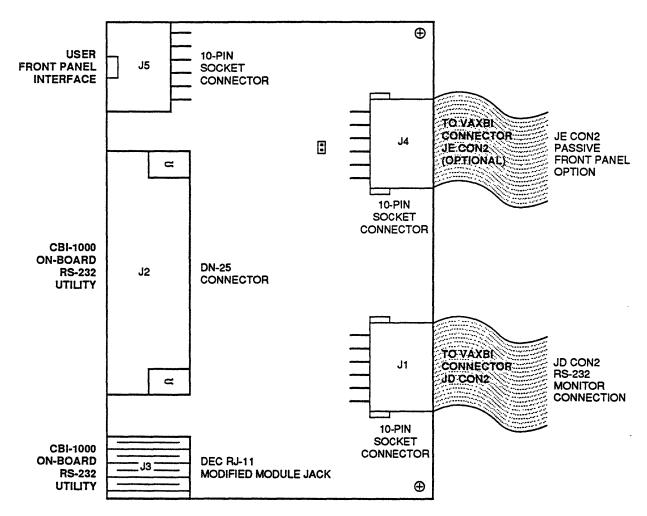

| E.6         | RS-232 Utility for BI Bus CPA                                                                                                                                                                                                                                                                                         | E-11                                                                                                            |

|             | Disk Options                                                                                                                                                                                                                                                                                                          | E-12                                                                                                            |

| <b>Q</b> BU | S CPA/M INSTALLATION                                                                                                                                                                                                                                                                                                  | F-1                                                                                                             |

| F.1         | VMS Considerations                                                                                                                                                                                                                                                                                                    | F-1                                                                                                             |

|             | Qbus CPA/M CSR Address                                                                                                                                                                                                                                                                                                | F-1                                                                                                             |

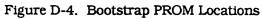

| F.2         | Jumper Settings                                                                                                                                                                                                                                                                                                       | F-2                                                                                                             |

|             | CSR Address Selection                                                                                                                                                                                                                                                                                                 | F-2                                                                                                             |

|             | Interrupt Level Selection                                                                                                                                                                                                                                                                                             |                                                                                                                 |

|             | Block Mode DMA                                                                                                                                                                                                                                                                                                        | F-5                                                                                                             |

|             | Adaptive DMA                                                                                                                                                                                                                                                                                                          | F-5                                                                                                             |

|             | DMA Dwell Time                                                                                                                                                                                                                                                                                                        | F-5                                                                                                             |

|             |                                                                                                                                                                                                                                                                                                                       |                                                                                                                 |

|             | SCSI Host Adapter (Initiator) ID Selection                                                                                                                                                                                                                                                                            | F-6                                                                                                             |

|             | SCSI Host Adapter (Initiator) ID Selection<br>Single-Ended or Differential Mode Selection                                                                                                                                                                                                                             | F-6<br>F-6                                                                                                      |

|             | SCSI Host Adapter (Initiator) ID Selection<br>Single-Ended or Differential Mode Selection<br>SCSI Terminator Power Option                                                                                                                                                                                             | F-6<br>F-6<br>F-7                                                                                               |

|             | SCSI Host Adapter (Initiator) ID Selection<br>Single-Ended or Differential Mode Selection<br>SCSI Terminator Power Option<br>Sync/Async Mode Selection                                                                                                                                                                | F-6<br>F-6<br>F-7<br>F-8                                                                                        |

| F.3         | SCSI Host Adapter (Initiator) ID Selection<br>Single-Ended or Differential Mode Selection<br>SCSI Terminator Power Option<br>Sync/Async Mode Selection<br>Mounting Slot Selection                                                                                                                                     | F-6<br>F-6<br>F-7<br>F-8<br>F-10                                                                                |

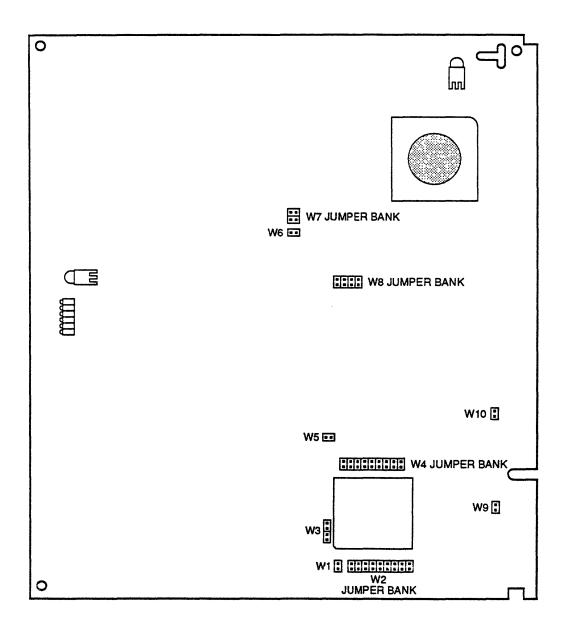

| F.4         | SCSI Host Adapter (Initiator) ID Selection<br>Single-Ended or Differential Mode Selection<br>SCSI Terminator Power Option<br>Sync/Async Mode Selection<br>Mounting Slot Selection<br>LED Indicators                                                                                                                   | F-6<br>F-6<br>F-7<br>F-7<br>F-8<br>F-10<br>F-11                                                                 |

|             | SCSI Host Adapter (Initiator) ID Selection<br>Single-Ended or Differential Mode Selection<br>SCSI Terminator Power Option<br>Sync/Async Mode Selection<br>Mounting Slot Selection<br>LED Indicators<br>SCSI Bus Cabling and Termination                                                                               | F-6<br>F-6<br>F-7<br>F-7<br>F-8<br>F-10<br>F-11<br>F-11                                                         |

| F.4         | SCSI Host Adapter (Initiator) ID Selection<br>Single-Ended or Differential Mode Selection<br>SCSI Terminator Power Option<br>Sync/Async Mode Selection<br>Mounting Slot Selection<br>LED Indicators<br>SCSI Bus Cabling and Termination<br>Single-Ended SCSI Channel                                                  | F-6<br>F-7<br>F-7<br>F-7<br>F-8<br>F-10<br>F-11<br>F-11<br>F-11                                                 |

| F.4<br>F.5  | SCSI Host Adapter (Initiator) ID Selection<br>Single-Ended or Differential Mode Selection<br>SCSI Terminator Power Option<br>Sync/Async Mode Selection<br>Mounting Slot Selection<br>LED Indicators<br>SCSI Bus Cabling and Termination<br>Single-Ended SCSI Channel<br>Differential SCSI Channel                     | F-6<br>F-7<br>F-7<br>F-7<br>F-8<br>F-10<br>F-10<br>F-11<br>F-11<br>F-11<br>F-11<br>F-11<br>F-12                 |

| F.4         | SCSI Host Adapter (Initiator) ID Selection<br>Single-Ended or Differential Mode Selection<br>SCSI Terminator Power Option<br>Sync/Async Mode Selection<br>Mounting Slot Selection<br>LED Indicators<br>SCSI Bus Cabling and Termination<br>Single-Ended SCSI Channel<br>Differential SCSI Channel<br>On-Board Utility | F-6<br>F-6<br>F-7<br>F-7<br>F-8<br>F-10<br>F-10<br>F-11<br>F-11<br>F-11<br>F-11<br>F-12<br>F-12                 |

| F.4<br>F.5  | SCSI Host Adapter (Initiator) ID Selection<br>Single-Ended or Differential Mode Selection<br>SCSI Terminator Power Option<br>Sync/Async Mode Selection<br>Mounting Slot Selection<br>LED Indicators<br>SCSI Bus Cabling and Termination<br>Single-Ended SCSI Channel<br>Differential SCSI Channel                     | F-6<br>F-6<br>F-7<br>F-7<br>F-8<br>F-10<br>F-10<br>F-11<br>F-11<br>F-11<br>F-11<br>F-12<br>F-12<br>F-12<br>F-13 |

# Page

*...*

### TABLE OF CONTENTS

### Section

| G. | RM I | REGISTER SETS                                                                                | . G-1        |

|----|------|----------------------------------------------------------------------------------------------|--------------|

|    | G.1  | SBI CPA Register Groups                                                                      | G-1          |

|    | G.2  | Internal Registers                                                                           | G-3          |

|    |      | Configuration and Status Register (MBACSR)                                                   | G-3          |

|    |      | Controller Register (MBACR)                                                                  | G-5          |

|    |      | Status Register (MBASR)                                                                      | G-6          |

|    |      | Virtual Address Register (MBAVAR)                                                            | G-10         |

|    |      | Byte Count Register (MBABCR)                                                                 |              |

|    |      | Diagnostic Register (MBADR)                                                                  | G-11         |

|    |      | Selected MAP Register (MBASMR)                                                               |              |

|    |      | Command Address Register (MBACAR)                                                            | G-13         |

|    |      | MAP Registers                                                                                | G-14         |

|    |      | UNIBUS and Qbus CPA Registers; SBI External (Drive)                                          |              |

|    |      | Registers (RM03/RM05)                                                                        | . G-15       |

|    |      | Control and Status 1 Register (RMCS1) (776700)                                               |              |

|    |      | (offset 400)                                                                                 |              |

|    |      | Word Count Register (RMWC) 776702                                                            |              |

|    |      | UNIBUS Address Register (RMBA) 776704                                                        | . G-18       |

|    |      | Desired Sector/Track Address Register (RMDA)                                                 | ~            |

|    |      | 776706 (offset 414)                                                                          |              |

|    |      | Control/Status Register 2 (RMCS2) 776710                                                     | . G-20       |

|    |      | Drive Status Register (RMDS) 776612                                                          | <b>~</b> ••• |

|    |      | (SBI offset 404)                                                                             |              |

|    |      | Error Register 1 (RMER1) 776714 (SBI offset 408)<br>Attention Summary Register (RMAS) 776716 | G-20         |

|    |      | (SBI offset 410)                                                                             | C-28         |

|    |      | Look-Ahead Register (RMLA) 776720 (SBI offset 41C)                                           |              |

|    |      | Data Buffer Register (RMDB) 776722                                                           |              |

|    |      | Maintenance Register #1 (RMMR1) 776724                                                       | . 0-25       |

|    |      | (SBI offset 40C)                                                                             | G-29         |

|    |      | Drive Type Register (RMDT) 776726 (SBI offset 418)                                           |              |

|    |      | Serial Number Register (RMSN) 776730                                                         |              |

|    |      | (SBI offset 420)                                                                             | G-30         |

|    |      | Offset Register (RMOF) 776732 (SBI offset 424)                                               |              |

|    |      | Desired Cylinder Register (RMDC) 776734                                                      |              |

|    |      | (SBI offset 428)                                                                             | G-32         |

|    |      | Holding Register (RMHR) 776736 (SBI offset 42C)                                              |              |

|    |      | Maintenance Register #2 (RMMR2) 776740                                                       |              |

|    |      | (SBI offset 430)                                                                             | G-33         |

|    |      | Error Register #2 (RMER2) 776742 (SBI offset 434)                                            |              |

|    |      | ECC Position Register (RMEC1) 776744                                                         |              |

|    |      | (SBI offset 438)                                                                             | G-34         |

|    |      | ECC Pattern Register (RMEC2) 776746                                                          |              |

|    |      | (SBI offset 43C)                                                                             | G-35         |

|    |      | Bus Address Extension Register (RMBAE) 776750                                                | G-35         |

# Page

ر ب ب  $\mathbf{C}$

### Section

### TABLE OF CONTENTS

| G.3 | Register Summaries G-36                                                                        |  |

|-----|------------------------------------------------------------------------------------------------|--|

|     | Configuration and Status Register (MBACSR)                                                     |  |

|     | Controller Register (MBACR) G-36                                                               |  |

|     | Status Register (MBASR)                                                                        |  |

|     | Virtual Address Register (MBAVAR)                                                              |  |

|     | Byte Count Register (MBABCR) G-37                                                              |  |

|     | Diagnostic Register (MBADR)                                                                    |  |

|     | Selected MAP Register (MBASMR) G-37                                                            |  |

|     | Command Address Register (MBACAR)                                                              |  |

|     | MAP Registers G-38                                                                             |  |

|     | Control/Status 1 Register (RMCS1) (776700)                                                     |  |

|     | (offset 400) G-38                                                                              |  |

|     | Word Count Register (RMWC) 776702                                                              |  |

|     | (not used on SBI) G-38                                                                         |  |

|     | UNIBUS Address Register (RMBA) 776704                                                          |  |

|     | (not used on SBI) G-38                                                                         |  |

|     | Desired Sector/Track Address Register (RMDA)                                                   |  |

|     | 776706 (offset 414) G-38                                                                       |  |

|     | Control/Status Register 2 (RMCS2) 776710                                                       |  |

|     | (not used on SBI)                                                                              |  |

|     | Drive Status Register (RMDS) 776612 (SBI offset 404) G-39                                      |  |

|     | Error Register 1 (RMER1) 776714 (SBI offset 408) G-39                                          |  |

|     | Attention Summary Register (RMAS) 776716                                                       |  |

|     | (SBI offset 410)                                                                               |  |

|     | Look-Ahead Register (RMLA) 776720 (SBI offset 41C) G-39                                        |  |

|     | Data Buffer Register (RMDB) 776722 (not used on SBI) G-39                                      |  |

|     | Maintenance Register #1 (RMMR1) 776724                                                         |  |

|     | (SBI offset 40C)                                                                               |  |

|     | Drive Type Register (RMDT) 776726 (SBI offset 418) G-39                                        |  |

|     | Serial Number Register (RMSN) 776730<br>(SBI offset 420) G-40                                  |  |

|     |                                                                                                |  |

|     | Offset Register (RMOF) 776732 (SBI offset 424) G-40<br>Desired Cylinder Register (RMDC) 776734 |  |

|     | (SBI offset 428) G-40                                                                          |  |

|     | Holding Register (RMHR) 776736 (SBI offset 42C)                                                |  |

|     | Maintenance Register #2 (RMMR2) 776740                                                         |  |

|     | (SBI offset 430) G-40                                                                          |  |

|     | Error Register #2 (RMER2) 776742 (SBI offset 434)                                              |  |

|     | ECC Position Register (RMEC1) 776744                                                           |  |

|     | (SBI offset 438) G-40                                                                          |  |

|     | ECC Pattern Register (RMEC2) 776746 (SBI offset 43C) G-41                                      |  |

|     | Bus Address Extension Register (RMBAE) 776750                                                  |  |

|     | (not used on SBI)                                                                              |  |

|     |                                                                                                |  |

### LIST OF ILLUSTRATIONS

# Figure

$\bigcirc$

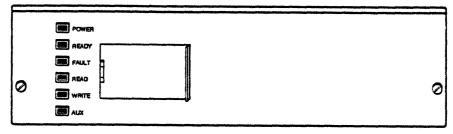

| Figure 2-1. CLUSTOR 3(M) Front Panel                                    | 2-2  |

|-------------------------------------------------------------------------|------|

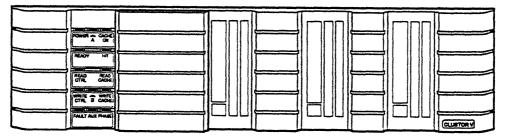

| Figure 2-2. CLUSTOR 5(M) Front Panel                                    | 2-2  |

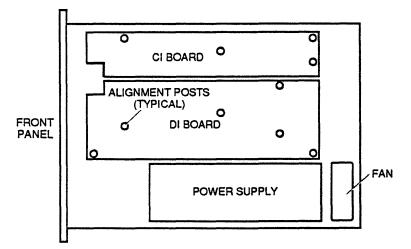

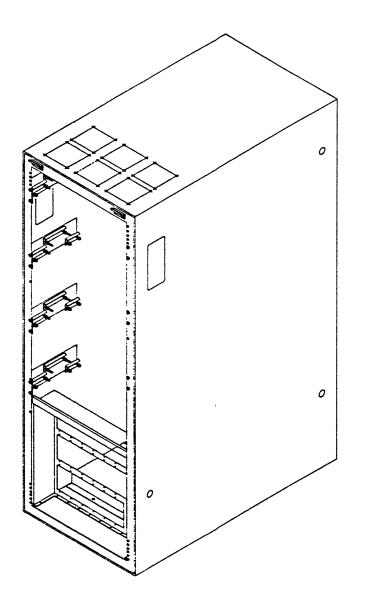

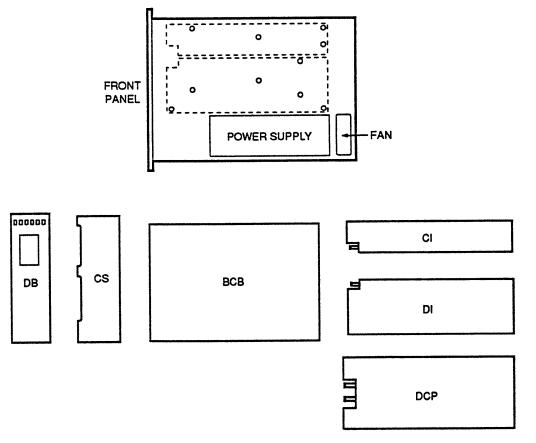

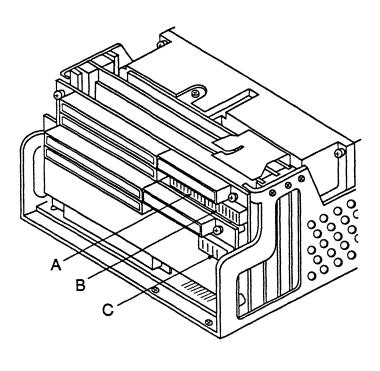

| Figure 2-3. CLUSTOR (M) Chassis Components                              |      |

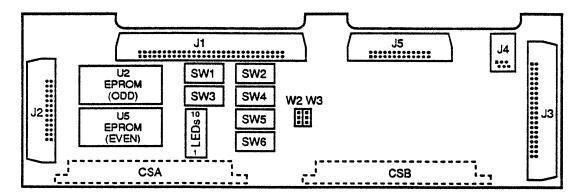

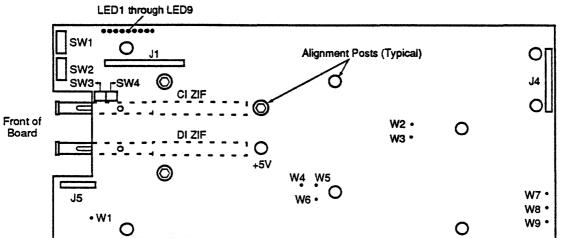

| Figure 2-4. Basic Control Board, Top View                               | 2-7  |

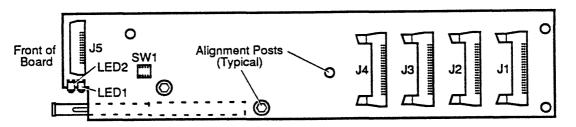

| Figure 2-5. Basic Control Board, Bottom View                            |      |

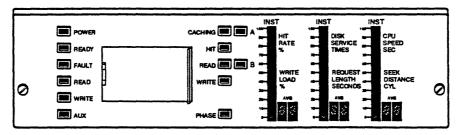

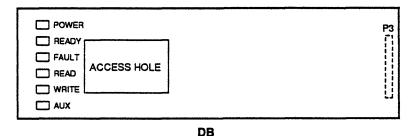

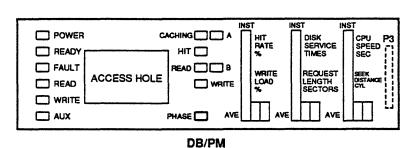

| Figure 2-6. Display and Display/Performance Monitor Panels              | 2-9  |

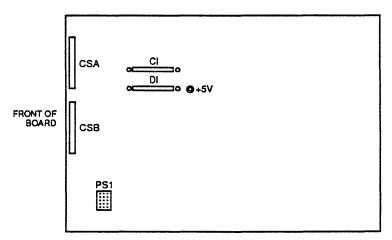

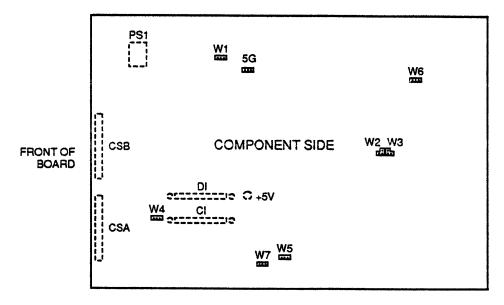

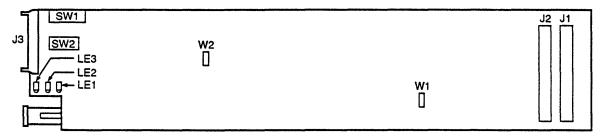

| Figure 2-7. Control Store Board.                                        |      |

| Figure 2-8. SI Computer Interface Board                                 |      |

| Figure 2-9. MSCP Computer Interface Board                               |      |

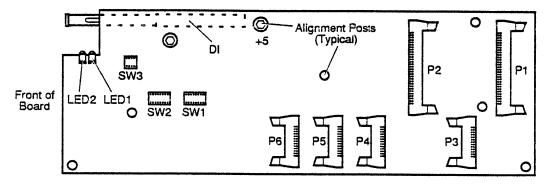

| Figure 2-10. Drive Interface Board                                      |      |

| Figure 2-11. Disk Cache Processor Board                                 | 2-16 |

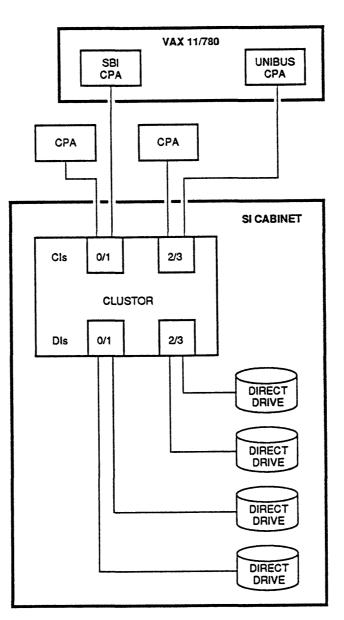

| Figure 3-1. CLUSTOR 3 Subsystem (Maximum) Configuration (RM-compatible) |      |

| Figure 3-2. CLUSTOR 5 Subsystem (Maximum) Configuration (RM-compatible) | 3-5  |

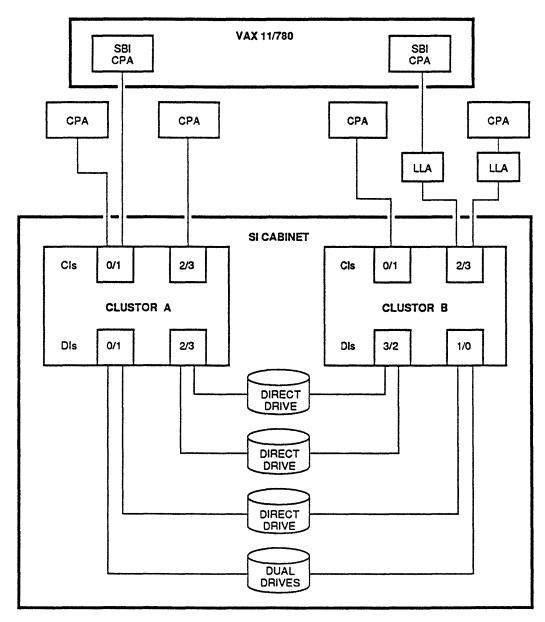

| Figure 3-3. CLUSTOR/M 3 Subsystem (Maximum) Configuration               |      |

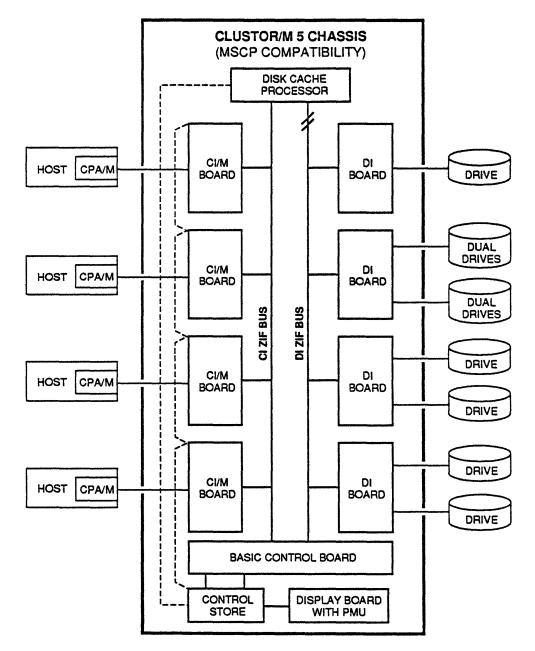

| Figure 3-4. CLUSTOR/M 5 Subsystem (Maximum) Configuration               | 3-8  |

| Figure 3-5. Multiport CPU                                               | 3-9  |

| Figure 3-6. Dual Channel Disk Drive Configuration                       |      |

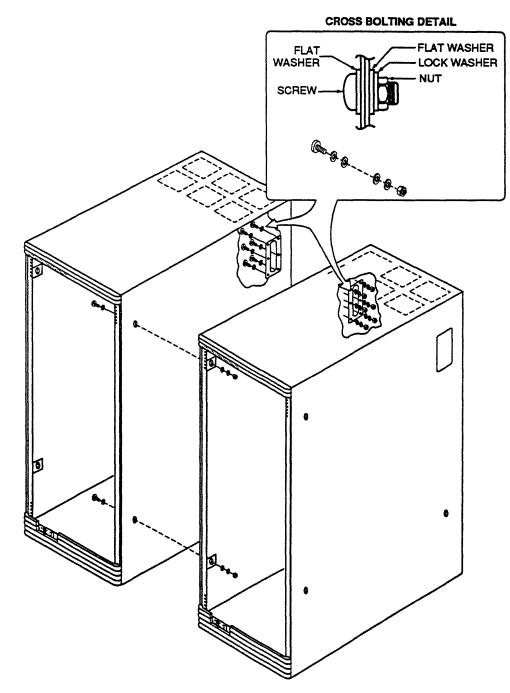

| Figure 5-1. Dual-Bay Cabinet Assembly                                   |      |

| Figure 5-2. Rear View of Cabinet                                        |      |

| Figure 8-1. CLUSTOR Controller Field Replaceable Units                  |      |

| Figure A-1. SI95 Switch Locations for Top I/O Board                     |      |

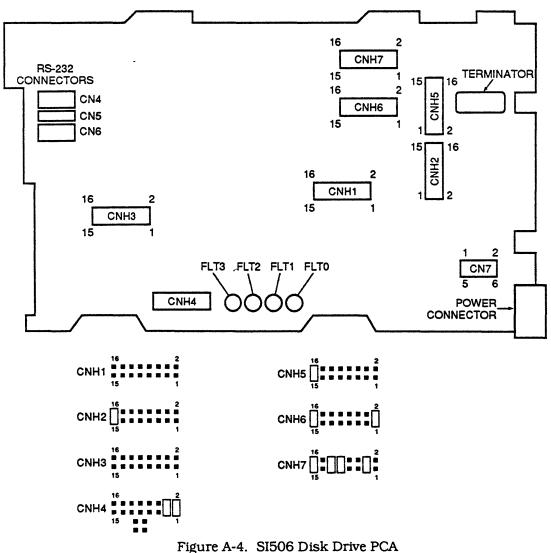

| Figure A-2. SI92 Switch Locations for Top I/O Board                     |      |

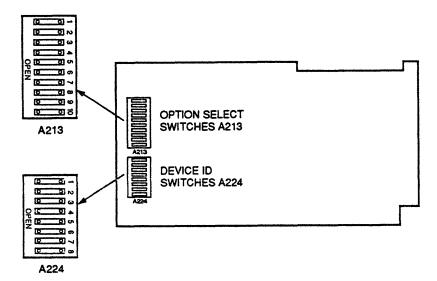

| Figure A-3. SI92 Switch Locations for Sync Board                        |      |

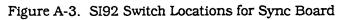

| Figure A-4. SI506 Disk Drive PCA.                                       |      |

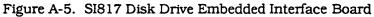

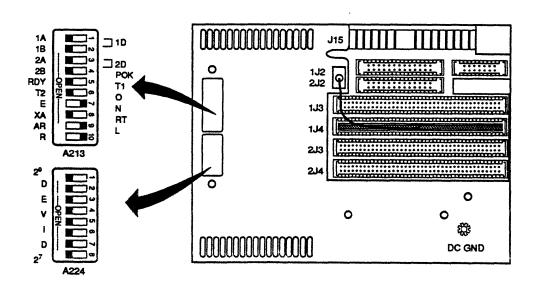

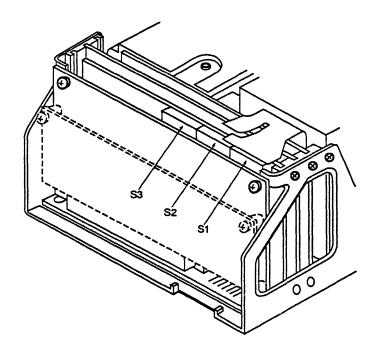

| Figure A-5. SI817 Disk Drive Embedded Interface Board                   |      |

| Figure A-6. SI817 Disk Drive Rear Panel                                 | A-20 |

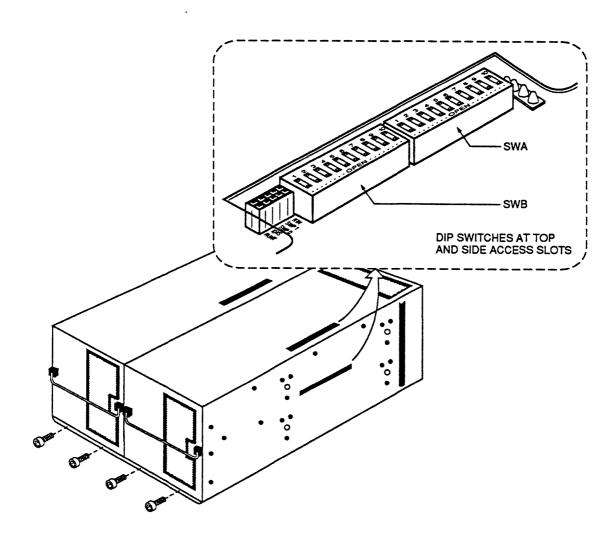

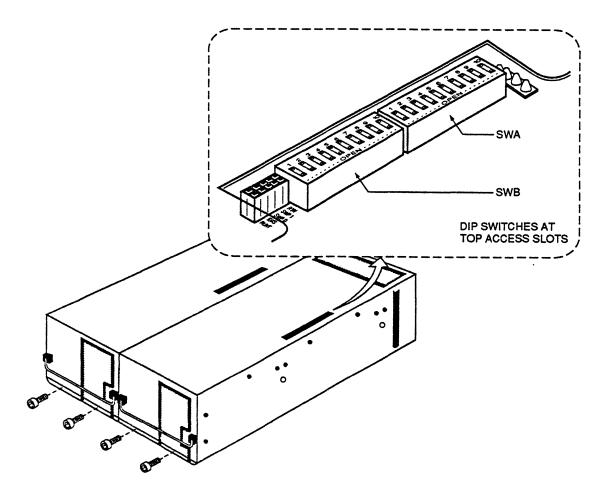

| Figure A-7. SI510M DIP Switch Settings                                  | A-21 |

| Figure A-8. SI510M I/O Switch Settings                                  |      |

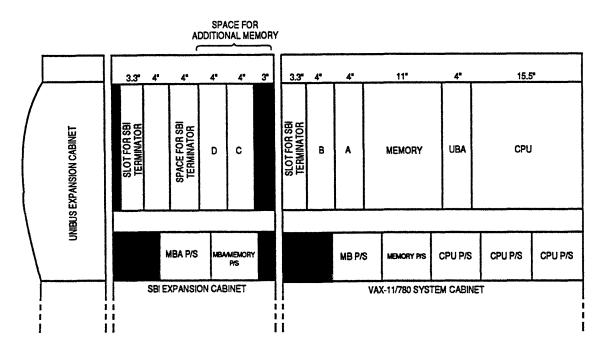

| Figure B-1. MBA Device Locations in the VAX-11/780 Cabinets Rear View   | B-2  |

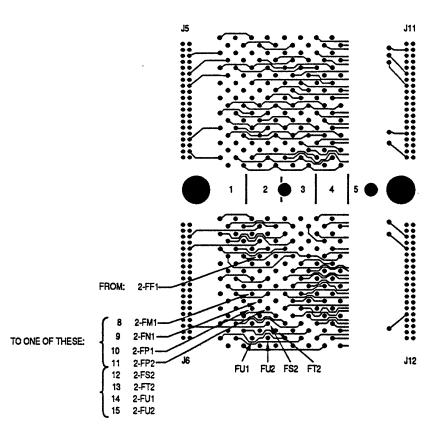

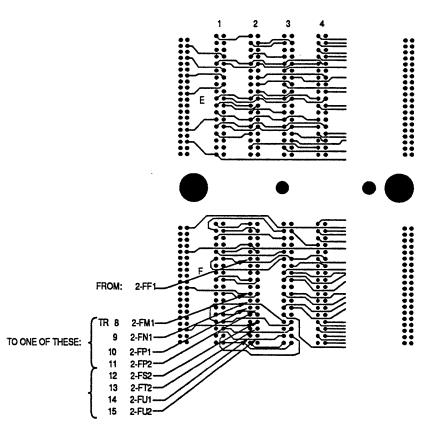

| Figure B-2. SBI Interface Board                                         | B-4  |

| Figure B-3. Internal Registers Board                                    | B-5  |

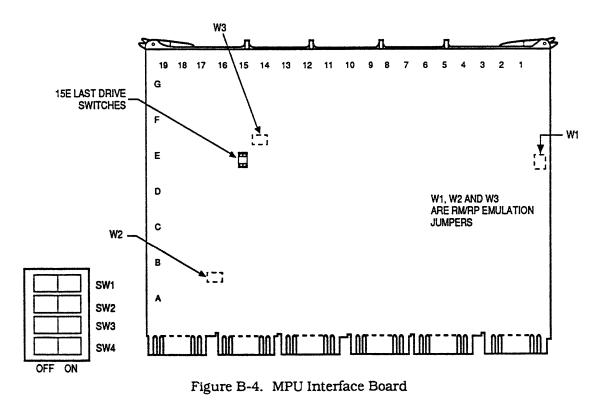

| Figure B-4. MPU Interface Board                                         |      |

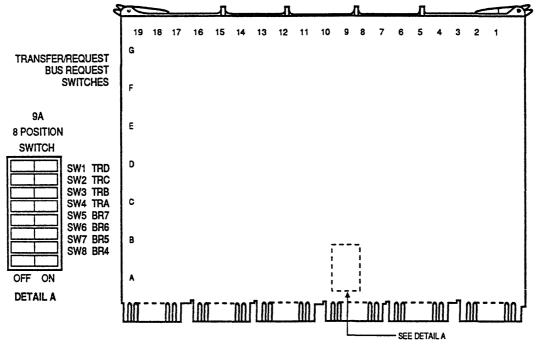

| Figure B-5. SBI Backplane (old style)                                   |      |

| Figure B-6. SBI Backplane (new style)                                   |      |

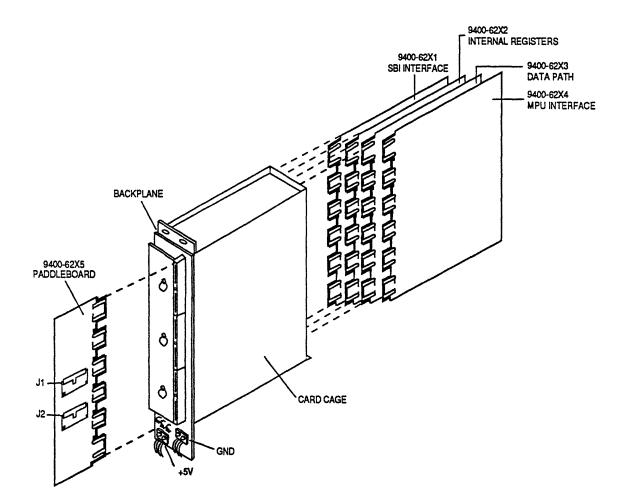

| Figure B-7. SBI Card Cage and Backplane Assembly                        |      |

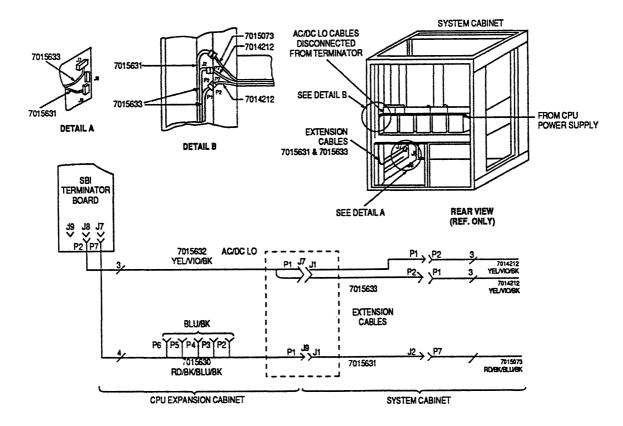

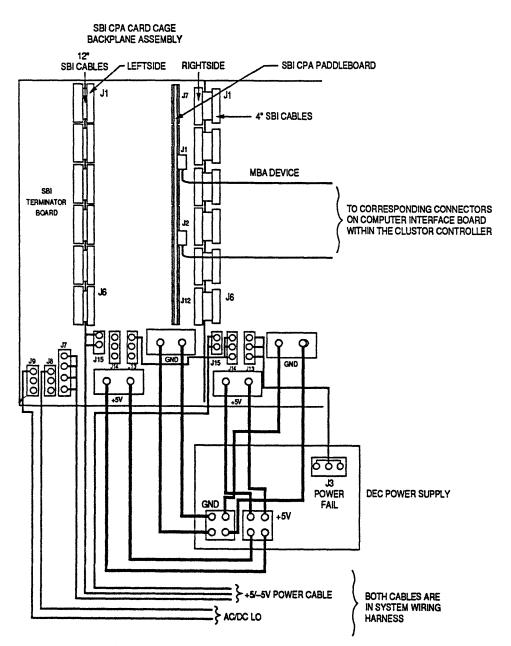

| Figure B-8. SBI Cabling (Expansion Cabinet)                             |      |

| Figure B-9. SBI Cabling (System Cabinet)                                |      |

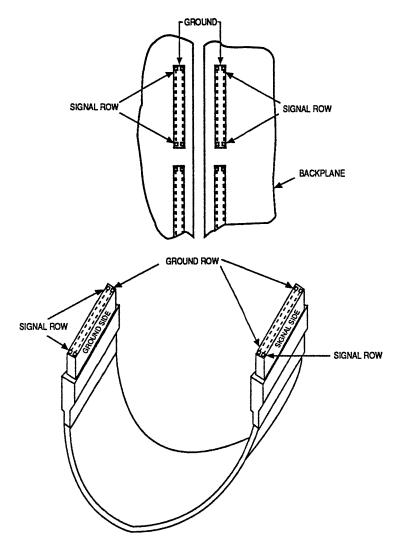

| Figure B-10. SBI Signal Cable Orientation                               | B-15 |

| Figure B-11. Terminator Power Cables Installation                       |      |

| Figure B-12. 780 FCC/750 non-FCC MASSBUS Cable                          |      |

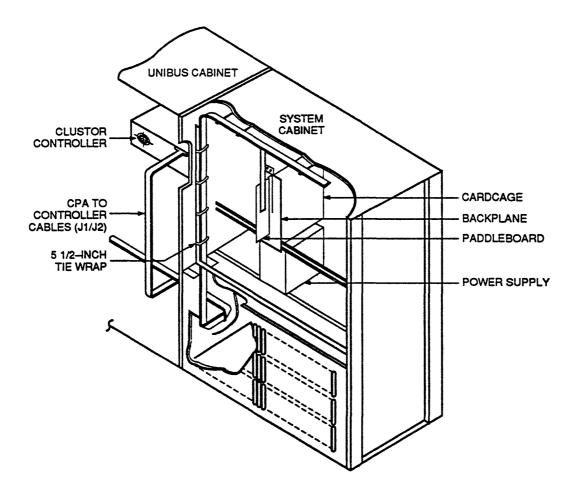

| Figure B-13. Typical System Cabinet Installation                        |      |

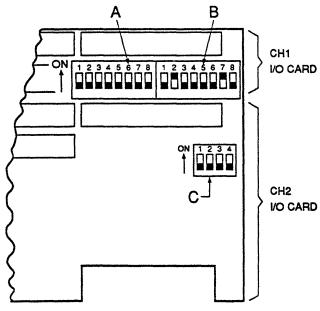

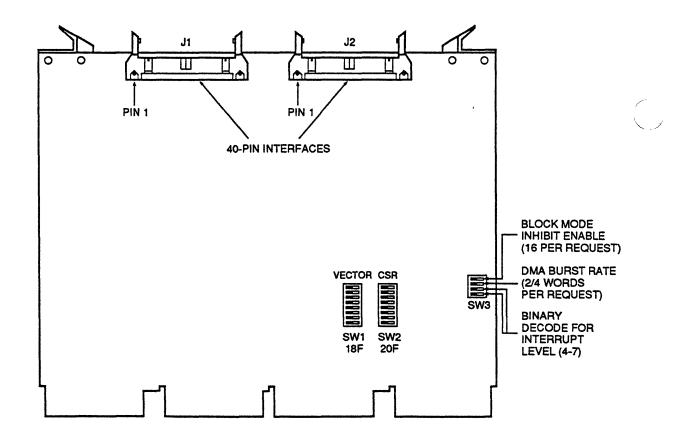

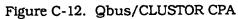

| Figure C-1. Switch Locations and Functions                              |      |

| Figure C-2. BA23 IOCP                                                   |      |

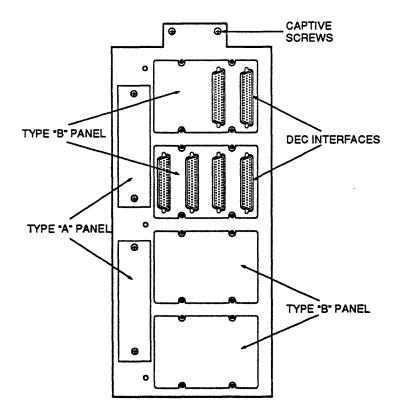

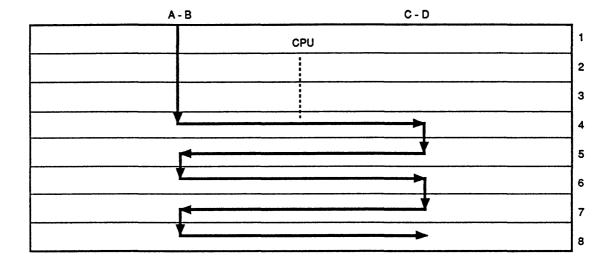

| Figure C-3. BA23 Bus Continuity                                         | C-7  |

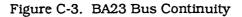

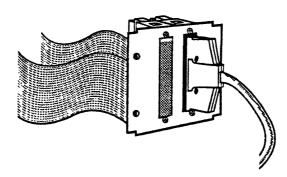

| Figure C-4. BA23 Adapter Plate And Connector Assembly                   |      |

| Figure C-5. BA123 IOCP.                                                 |      |

| Figure C-6. BA123 Bus Continuity                                        |      |

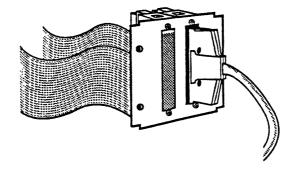

| Figure C-7. BA213 Adapter Plate and Connector Assembly                  | C-11 |

| G                                                                       |      |

### LIST OF ILLUSTRATIONS

# Figure

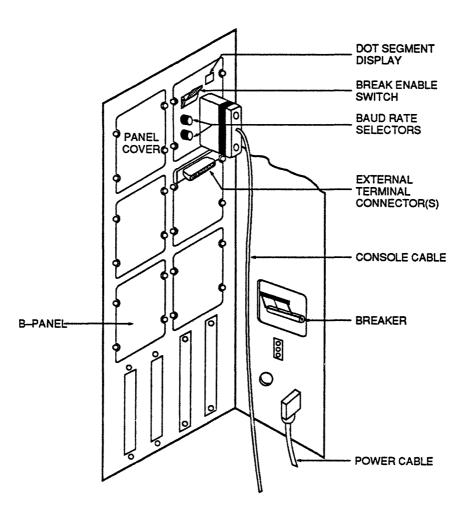

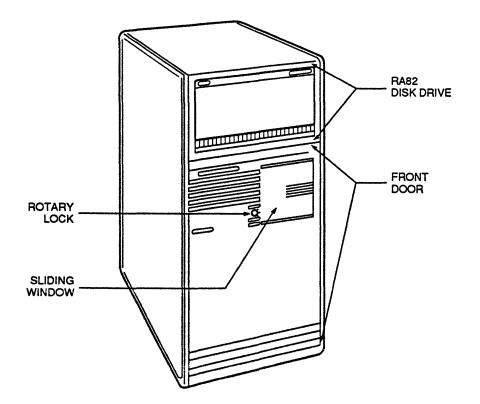

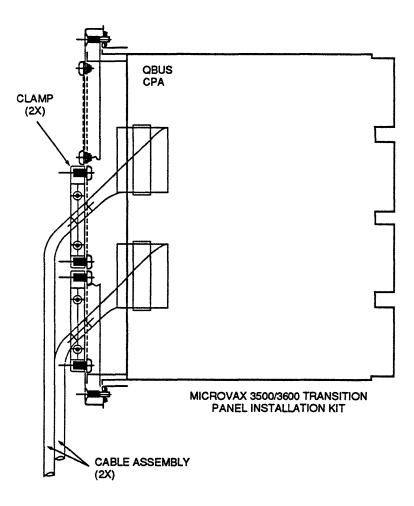

| Figure C-8. | MicroVAX III Cabinet                        | C-12  |

|-------------|---------------------------------------------|-------|

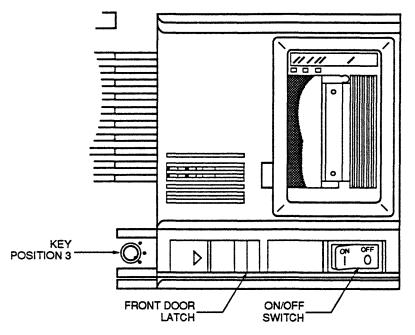

| Figure C-9. | Window and Control Locations                | C-13  |

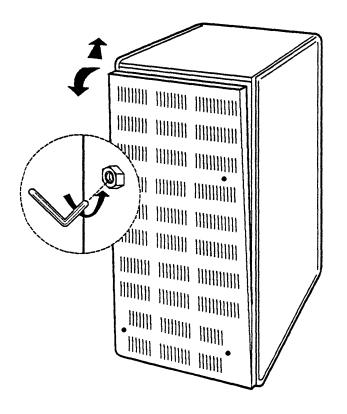

| Figure C-10 | . Cabinet Rear Panel Removal                | C-14  |

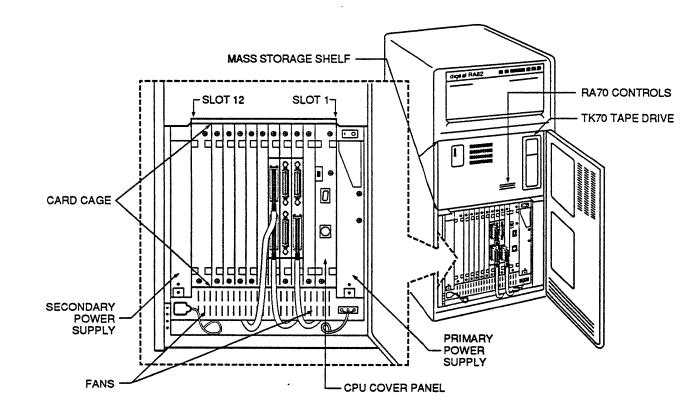

| Figure C-11 | . BA213 Chassis                             | C-15  |

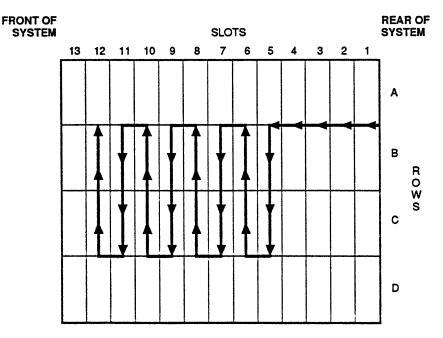

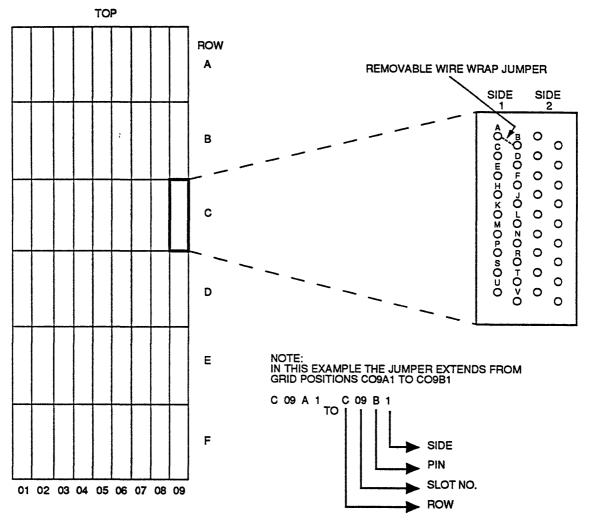

| Figure C-12 | Card Cage                                   | C-16  |

| Figure C-13 | . Qbus/CLUSTOR CPA                          | C-17  |

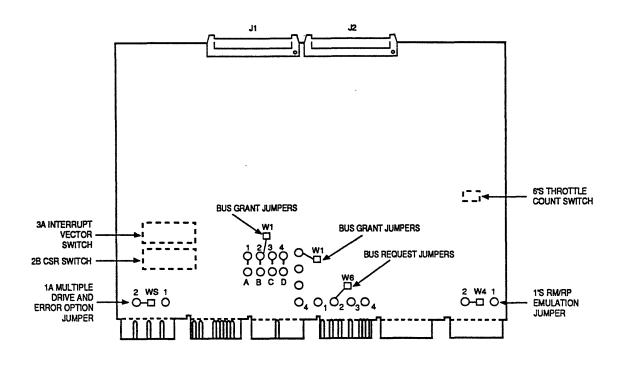

| Figure D-1. | UNIBUS CPA Board                            | . D-2 |

| Figure D-2. | SPC Backplane, Rear View                    | . D-6 |

| Figure D-3. | UNIBUS Adapter Plate and Connector Assembly | . D-7 |

| Figure D-4. | Bootstrap PROM Locations                    | . D-8 |

|             | BI Bus CPA Jumper Block Diagram             |       |

| Figure E-2. | BI Bus CPA LEDs, Front View                 | . E-5 |

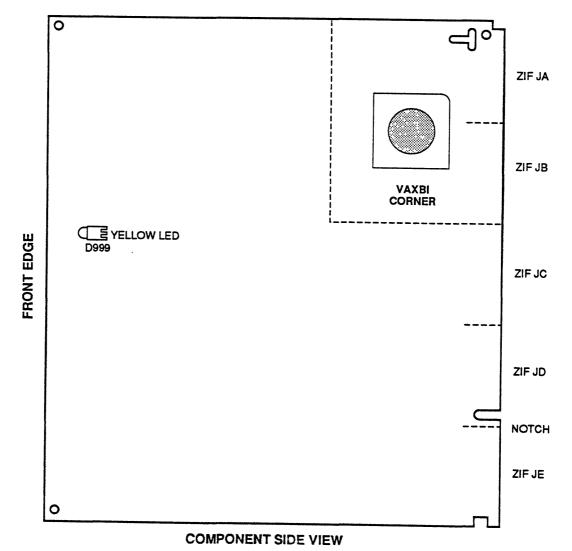

| Figure E-3. | BI Bus CPA ZIF Connectors                   | . E-6 |

| Figure E-4. | BI Bus Backplane Connector                  | . E-7 |

| Figure E-5. | Back Panel Adapter Kit                      | . E-9 |

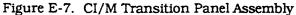

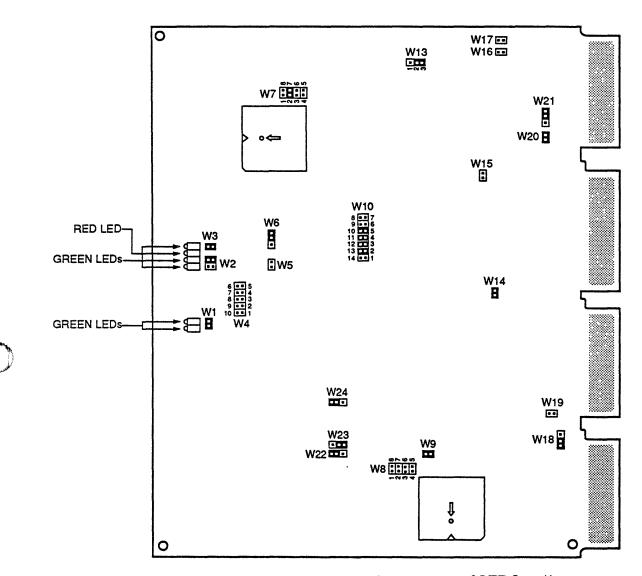

| Figure E-6. | Host Transition Panel                       | E-10  |

|             |                                             | E-10  |

|             | MSCP Qbus CPA/M Jumper and LED Locations    | F-3   |

| Figure F-2. | Qbus CPA/M LEDs, Front View                 | F-11  |

|             |                                             |       |

### LIST OF TABLES

### Table

$\mathbf{O}$

| Table 1-1.       CLUSTOR User Guide Sections       1-1                               |

|--------------------------------------------------------------------------------------|

| Table 1-2. Related Publications    1-2                                               |

| Table 2-1. Computer Operating Systems Supported                                      |

| Table 2-2. Disk Drive Size and Mounting Type    2-19                                 |

| Table 2-3.         Supported Disk Drive Capacities         2-20                      |

| Table 3-1. Actual Disk Drive Sector Counts         3-14                              |

| Table 4-1.       CLUSTOR (M) Subsystem Physical Specifications       4-2             |

| Table 7-1. CS Board LED Bank Indications    7-2                                      |

| Table 7-2. CS Board LED Error Codes    7-2                                           |

| Table 7-2.       CS Board LED Error Codes (Continued)       7-3                      |

| Table 7-3. DCP LED Indications    7-3                                                |

| Table 7-4. DCP Error Codes    7-5                                                    |

| Table 7-5.    68000 Status Register Bits                                             |

| Table 7-6. DCP Status Register Bits    7-8                                           |

| Table 7-7. DCP Control Register Bits    7-9                                          |

| Table 7-8. DCP Commands    7-14                                                      |

| Table 8-1.       CLUSTOR (M) Subsystem Field Replaceable Units       8-2             |

| Table 8-1.       CLUSTOR (M) Subsystem Field Replaceable Units (Continued)       8-3 |

| Table 9-1. Computer Operating Systems Supported                                      |

| Table 9-2. Disk Drive Size and Mounting Methods                                      |

| Table 9-3.         Supported Disk Drive Capacities         9-4                       |

| Table 9-4. Disk Drive Sector Counts (Physical)         9-5                           |

| Table 9-5.    CS Board LED Bank Indications    9-5                                   |

| Table 9-6.       CS Board Jumpers: RS232 Communication Port Signal Pins              |

| Table 9-7. BCB Jumpers   9-6                                                         |

| Table 9-8. CI Port Address Values (RM-emulation)       9-7                           |

| Table 9-9. CI/M Switch Settings   9-7                                                |

| Table 9-10. CI Port Address Values (MSCP-emulation)    9-8                           |

| Table 9-11. Multiple Target Mode Switch Settings                                     |

| Table 9-12.         Single Target with Multiple LUN Switch Settings         9-9      |

| Table 9-13. DI Port Address Values    9-10                                           |

| Table 9-14. DI Board Drive Model Switch Settings    9-11                             |

| Table 9-15. DCP Switch Settings   9-12                                               |

| Table 9-16. DCP Minimum Request Size Settings    9-12                                |

| Table 9-17. DCP Maximum Request Size Settings                                        |

| Table 9-18. DCP Jumpers   9-13                                                       |

| Table 9-19. DCP LED Indications   9-13                                               |

| Table A-1.       SI56 and SI57 General Jumper Settings (Old - Pre-Fab #8)       A-2  |

| Table A-2.    SI56 Sector Jumper Settings.                                           |

| Table A-3.    SI57 Sector Jumper Settings.                                           |

| Table A-4.       SI57 (New - Fab #8) General Jumper Settings         A-4             |

| Table A-5.   9733 Switch Settings                                                    |

| Table A-6.    9733 Sector Switch Settings                                            |

| Table A-7. SI83 and SI85 Switch 1 and 2 Settings       A-6                           |

| Table A-8. SI83 and SI85 Sector Switch Settings       A-6                            |

| Table A-9.    9751 Address Switch Settings.                                          |

| Table A-10.       9751 Logic Board Sector Count Settings         A-7                 |

| Table A-11.       9751 Logic Board I/O Modification Settings         A-7             |

### LIST OF TABLES

### Table

## Page

| Table A-12. 9761 Sector Count and Unit Address Settings                  |

|--------------------------------------------------------------------------|

| Table A-13. SI93 Switch Settings.       A-9                              |

| Table A-14. SI95 Switch and Jumper Settings (Type 3 Control Board)       |

| Table A-15.     SI-Sync Board Switch and Jumper Settings     A-12        |

| Table A-16. SI92 Switch and Jumper Settings (Type 3 Control Board)       |

| Table A-16.     SI92 Switch and Jumper Settings (Continued)     A-14     |

| Table A-17. Sync Board Switch and Jumper Settings       A-15             |

| Table A-18. SI506 Disk Drive Jumper Settings       A-17                  |

| Table A-19. SI817 Disk Drive Interface Board Jumper Settings             |

| Table A-20.       SI817 Disk Drive Interface Board Switch Positions      |

| Table A-21. SI817 Disk Drive Rear Panel Switches (A213)       A-20       |

| Table A-22.    SI510M I/O Board Switch Settings    A-23                  |

| Table A-22. SI510M I/O Board Switch Settings (Continued)       A-24      |

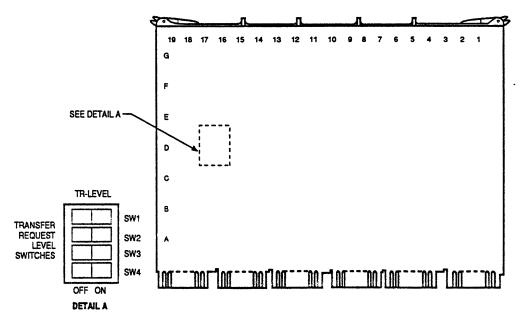

| Table B-1. Transfer Request/Bus Request Switch Settings    B-4           |

| Table B-2. Transfer Request Level Switch Settings    B-5                 |

| Table B-3. RM Emulation Jumpers (MPU Interface Board)       B-6          |

| Table B-4. Last Drive Switch Settings    B-7                             |

| Table B-5. Extended Register Option Jumper Setting                       |

| Table B-6. TR Jumper Locations                                           |

| Table C-1. Control Status Register Address Switch Settings               |

| Table C-2. Interrupt Vector Switch Settings                              |

| Table C-3. Transfer Mode Switch Settings (SW3)                           |

| Table C-4. Interrupt Level Switch Settings    C-5                        |

| Table D-1. CSR Address Switch Settings    D-3                            |

| Table D-2. Interrupt Vector Switch Settings                              |

| Table D-3. Throttle Count Switch Settings                                |

| Table D-4. Bus Request Connections on the UNIBUS CPA Board               |

| Table D-5. Bus Grant Jumper Settings for the UNIBUS CPA Board            |

| Table E-1. CPA For BI Bus Node ID Settings                               |

| Table E-2. CPA for BI Bus SCSI ID Settings    E-2                        |

| Table E-3. BI Bus CPA LED Indications    E-4                             |

| Table F-1. Qbus CPA/M CSR Addresses    F-4                               |

| Table F-2. Qbus CPA/M Jumper Settings    F-9                             |

| Table F-2. Qbus CPA/M Jumper Settings (continued)    F-10                |

| Table G-1. Internal Registers    G-1                                     |

| Table G-2. Base Addresses    G-2                                         |

| Table G-3. External (Drive) Register Address Calculation (Hex)       G-2 |

| Table G-4. Function Code Control Bits    G-17                            |

| Table G-5. Drive Type Code    G-30                                       |

|                                                                          |

.

### 1 INTRODUCTION

*CLUSTOR User Guide* explains how to install, operate, and maintain System Industries CLUSTOR Mass Storage Subsystem. It contains nine chapters and seven appendixes, listed in Table 1-1.

| SECTION                                                  | DESCRIPTION                                                                                           |

|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| Section 1:<br>Introduction                               | Contains the manual audience, related publications, conventions, terms list, and materials needed     |

| Section 2:<br>CLUSTOR Subsystem                          | Describes subsystem features and options, components, indicators, and CLUSTOR subsystem controls      |

| Section 3:<br>Configuration                              | Lists the configuration considerations, configuration examples, and necessary settings                |

| Section 4:<br>Preinstallation                            | Discusses technical specifications, site concerns, and initial unpacking                              |

| Section 5:<br>Installation                               | Explains subsystem, options, and upgrade installation                                                 |

| Section 6:<br>Maintenance                                | Includes subsystem maintenance routines, removal and replacement procedures                           |

| Section 7:<br>System Verification<br>and Troubleshooting | Discusses subsystem verification and approaches for troubleshooting                                   |

| Section 8:<br>Illustrated Parts List                     | Lists Field Replaceable Units within the CLUSTOR<br>Controller                                        |

| Section 9:<br>Ready Reference                            | Provides a quick reference for configuration requirements and board settings used during installation |

| Appendix A:<br>Disk Drive Settings                       | Gives settings for disk drives used with the CLUSTOR Controller                                       |

| Appendix B:<br>SBI CPA Installation                      | Gives installation procedures for SBI CPA                                                             |

| Appendix C:<br>Qbus CPA Installation                     | Provides the installation procedures for Qbus CPA                                                     |

| Appendix D:<br>UNIBUS Installation                       | Gives installation procedures and register information for UNIBUS CPA                                 |

| Appendix E:<br>BI Bus CPA<br>Installation                | Provides installation information for BI Bus CPA                                                      |

| Appendix F:<br>Qbus CPA/M<br>Installation                | Provides installation information for Qbus CPA/M<br>(MSCP).                                           |

| Appendix G<br>RM Register Sets                           | Lists the RM-compatible register sets for SBI, UNIBUS, and QBus CPA                                   |

Table 1-1. CLUSTOR User Guide Sections

#### 1.1 Manual Audience

*CLUSTOR User Guide* is intended for System Industries customer service engineers, system users, and self-maintenance customers. Familiarity with VMS and UNIX operating systems, along with understanding the fundamentals of DEC networks, computers, and disk drive operations, is required.

#### **1.2 Related Publications**

Additional information on the CLUSTOR Subsystems and its related configurations is provided in the publications listed in Table 1-2.

| PUBLICATION<br>NUMBER | TITLE                                            |

|-----------------------|--------------------------------------------------|

| PB5000-9211           | ULTRIX USER GUIDE                                |

| PB8700-9200           | 5.25-INCH DISK DRIVE INSTALLATION GUIDE          |

| PB6005-9100           | 8-INCH QUICK RELEASE CHASSIS USER GUIDE          |

| PB6005-9210           | 5.25-INCH QUICK RELEASE CHASSIS USER GUIDE       |

| PB9900-9036           | VAX 11-780/750/730 V4.4 — 4.7 SBI/CMI USER GUIDE |

| PB9900-9047           | VAX 11-780/750/730 V4.4 — 4.7 UNIBUS USER GUIDE  |

| PB9900-9070           | VAX/VMS V5.X SOFTWARE MODIFICATION GUIDE         |

| PB9900-9310           | UNIX BSD 4.3 UTILITY GUIDE                       |

| PB9900-9992           | 8600/8650 SBI FIELD SERVICE INSTALLATION         |

| PB9901-9041           | FCC DISK DRIVE USER GUIDE                        |

| PB9901-9061           | SI93 DISK DRIVE USER GUIDE                       |

| PB9904-9013           | SILINK USER GUIDE                                |

| PB9904-9014           | SIDOS PROGRAM USER GUIDE                         |

| PB9951-9041           | SI FCC-COMPLIANT 60-INCH CABINET USER GUIDE      |

| PB6500-9001           | THETA SERIES CABINET USER GUIDE                  |

| PB2500-9100           | eaSIshadow USER GUIDE                            |

| PB2950-9001           | SI500C SERIES DISK DRIVE USER GUIDE              |

| PB2920-9001           | SI506 DISK DRIVE USER GUIDE                      |

| PB3270-9001           | SI817 CHASSIS SUBSYSTEM USER GUIDE               |

Table 1-2. Related Publications

#### **1.3 Manual Conventions**

Refer to the following documentation conventions as a guide to using this manual.

• Typed computer entry is shown in **boldface**. Type all boldface characters exactly as they appear. For example:

Type: SHOW DEV

- Screen messages are displayed in a different typestyle, as follows: Printer attached to terminal? (Y/N) [N]:

- Key names are in **boldface** and shown in angle brackets. For example:

<RETURN> <TAB> <CTRL> c

• Interactive sequences that include computer input and output are shown as follows:

Printer attached to terminal? (Y/N) [N]: Y Initializing...

• Variable typed entries, or text you must replace, are shown in *italics*. In the following example

Type: COPY Mxxu:\*.\* xxxxxx::\*/LOG <RETURN>

xx and xxxxxx are italicized and replaced with the actual device type and name.

• Three types of notes are used in this manual: a standard NOTE, a CAUTION note, and a WARNING note.

#### NOTE

The standard NOTE highlights important or additional information.

#### CAUTION

The CAUTION note is used for situations that are potentially dangerous or destructive to data.

#### WARNING

A WARNING note is required if system failure or bodily injury could be involved.

### 1.4 Terms List

The terms list provides definitions and usage information for System Industries and industry-standard terms and acronyms used in this manual.

| BBF         | Bad Block Forwarding — an SI disk sector formatting process<br>that removes a defective sector from service, and replaces it<br>with a designated reserved sector. |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BCB         | Basic Control Board — contains the main microprocessor for the CLUSTOR Controller.                                                                                 |

| CI          | Computer Interface — a board in the CLUSTOR Controller.                                                                                                            |

| CI/M        | Computer Interface — a board in the CLUSTOR/M Controller.                                                                                                          |

| CI-LLA      | Computer Interface Long Line Adapter — a computer interface board requiring LLA cabling to support two CPAs.                                                       |

| CLUSTOR     | An SI mass storage subsystem that interfaces up to 16 disk drives and up to eight DEC computers.                                                                   |

| CLUSTOR/M   | New CLUSTOR controller configuration that includes at least one MSCP-compatible Computer Interface Board.                                                          |

| CLUSTOR (M) | This indicates that <i>both or either</i> CLUSTOR (RM-compatible) and CLUSTOR/M (MSCP-compatible) are involved.                                                    |

| СМІ         | Computer Memory Interconnect — a DEC system bus interface.                                                                                                         |

| СРА         | Computer Port Adapter — the computer interface for the CLUSTOR Controller.                                                                                         |

| CPA/M       | Computer Port Adapter (MSCP) — the computer interface for the CLUSTOR/M Controller.                                                                                |

| CPU         | Central Processing Unit — a computer.                                                                                                                              |

| CRC         | Cyclic Redundancy Check — verifies header fields.                                                                                                                  |

| CS          | Control Store — a board in the CLUSTOR Controller.                                                                                                                 |

| DB          | Display Board — contains front panel indicators for the CLUSTOR/M Controller.                                                                                      |

| DB/PM       | Display Board Performance Monitor — provides extra indicators needed to monitor the DCP function.                                                                  |

| DCP         | Disk Cache Processor.                                                                                                                                              |

.

Ð

| DEC                                                   | Digital Equipment Corporation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DI                                                    | Drive Interface — a board in the CLUSTOR/M Controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DIP                                                   | Dual In-line Package — a bank of switches.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DMA                                                   | Direct memory access — a method of data transfer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DQBI                                                  | CPA for Qbus system with CLUSTOR (RM).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DQBI/M                                                | CPA for Qbus system with CLUSTOR/M (MSCP).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DSBI                                                  | CPA for SBI system with CLUSTOR (RM).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DBBI/M                                                | CPA for BI Bus system with CLUSTOR/M (MSCP).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DUBI                                                  | CPA for UNIBUS system with CLUSTOR (RM).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Direct Format                                         | A disk drive format arrangement where one physical drive<br>emulates one logical drive with a defined drive geometry that<br>uses the large capacity of SI disk drives.                                                                                                                                                                                                                                                                                                                                                                                                                |

| Dual Channel Disk<br>Drives                           | An SI option where a dual channel disk drive is accessed<br>by two subsystems. This CLUSTOR/M configuration allows<br>multiple computers to communicate with the same disk drive.                                                                                                                                                                                                                                                                                                                                                                                                      |

| Dual Disk Format                                      | A disk drive format where two physically daisy-chained disk<br>drives emulate one logical drive with a defined geometry that                                                                                                                                                                                                                                                                                                                                                                                                                                                           |