## The 8500 Series Technical Catalog

|                                                             | age      |

|-------------------------------------------------------------|----------|

| Maintrames                                                  | 0        |

| 8500 MDL Modular Family                                     | . 2      |

| 8550 Microcomputer Development Lab                          |          |

| 8540 Integration Unit                                       | . υ      |

| Integration Tools                                           | . 0      |

| Emulators & Probes                                          | 12       |

| General                                                     | 12       |

| Specific                                                    | 1.3      |

| 8080A/8085A                                                 |          |

| Z80A                                                        |          |

| 6800/02/08                                                  | 17       |

| 6809                                                        |          |

| 3870/72/74/76/F8*                                           |          |

| 1802*                                                       |          |

| 8048/35/39/39-6/49/41A/21/22/8748/8749                      | 22       |

| 6500/1*                                                     | 24       |

| Z8001/Z8002                                                 | 25       |

| TMS9900/SBP9900*                                            |          |

| 68000                                                       |          |

| 8086/8088                                                   |          |

| Real-Time Prototype Analyer (RTPA)                          | . 30     |

| Trigger Trace Analyzer (TTA)                                | 31       |

| Memory Allocation Controller (MAC)                          | 33       |

| Software Tools                                              | 0.4      |

| Assemblers                                                  |          |

| Library Generator                                           | 34       |

| Linker                                                      | 34       |

| Pascal Compilers                                            | 33<br>36 |

| Tektronix Pascal Compiler Major Extensions                  | 30<br>26 |

| MDL/µ Compilers* Advanced CRT-oriented Editor               | ას       |

| Software Support Services                                   |          |

| Peripherals                                                 |          |

| CT 8500 Terminal                                            | 30       |

| 4643 Printer                                                | 00<br>40 |

| PROM Programmer                                             | 41       |

| Accessories                                                 |          |

| Flexible Discs                                              | 41       |

| Interconnecting Cables                                      |          |

| HSI Cables                                                  |          |

| RS-232                                                      | 41       |

| Null Modem                                                  |          |

|                                                             |          |

| Microcomputer Development Lab Workshops                     |          |

| The Development System in the Microcomputer Design Workshop |          |

| Software Design & Debugging Workshop                        | 41       |

| *8550 support only                                          |          |

## **Mainframes**

8500 MDL Modular Family 8550 Microcomputer Development Lab 8560 Multi-User Software Development Unit 8540 Integration Unit

## 8500 Series Modular MDL Family

### Three Basic Design Environments

Microcomputer design is currently performed in three basic work environments. These are the single-user environment, the multiple-user environment, and the host computer environment. The Tektronix 8500 Series of Microcomputer Development Labs offers a full complement of development tools for all three microcomputer design environments. In each case, the most advanced technology available has been incorporated into an 8500 Series microcomputer development system that gives maximum performance in its intended setting. In this manner, Tektronix provides unmatched support for both microcomputer software development and hardware/ software integration, no matter where it occurs.

### The 8550 MDL for the single user environment

The 8550 MDL is a selfcontained microcomputer development lab that gives complete support to one user at a time. Important features of the 8550 MDL include a flexible filing system that easily adapts to any type of software project, high level language and assembly support with symbolic debugging for both 8-bit and 16-bit chips, real-time emulation to install developed software in the prototype hardware, and a powerful set of real-time debugging tools, including the Trigger Trace Analyzer for 8-bit and 16-bit designs, and the Real-Time Prototype Analyzer for 8-bit designs.

### The 8560 MDL for the multi-user environment

The 8560 MDL is a full microcomputer software development lab that supports up to eight separate workstations. It's done through the 8560's powerful TNIX\* operating system, a derivation of Bell Lab's UNIX\*\*Operating System Version 7 that has been tailored specifically for team-oriented microcomputer development work. It includes a fast, flexible filing system for effective data base management, advanced command capability for streamlining software development tasks, and several optional utility packages such as text processing. The 8560 uses a powerful 16-bit CPU to control system resources. Software work stations consist of CRT terminals; and the 8540 Integration Unit, which has full emulation and debugging capability, or the 8550 can be used for hardware/software integration.

## The 8540 Integration Unit for the host computer environment

In the host computer environment, a general purpose computer is used to support microcomputerbased design projects. The host computer's timesharing capability allows a number of designers at CRT terminals to simultaneously use the computer's facilities. Each designer has access to microcomputer development tools such as editors, assemblers, and compilers. The 8540 Integration Unit extends the host computer's microcomputer development support to include the task of hardware/ software integration. While the 8560 or other host computer supports the software development task, the 8540 is used to integrate, test and debug the prototype hardware. The 8540 uses Real-Time Emulation, a fast and efficient integration technique that uses an emulator processor identical in function to the one targeted for the prototype. For added real-time debugging, a 62channel Trigger Trace Analyzer is available as an option.

<sup>\*</sup>TNIX is a trademark of Tektronix

\*\*UNIX is a trademark of Bell Laboratories

## 8550 Microcomputer Development Lab

The 8550 MDL is a completely self-contained microcomputer development system that gives full support to both software development and hardware/software integration. For software development, the 8550 provides a wide range of sophisticated tools for fast, effective code generation. These include many 8-bit and 16-bit assemblers that support symbolic debugging. produce relocatable code and have powerful macro capabilities. High level language support includes Pascal compilers, and MDL/ $\mu$ compilers, Tektronix enhanced form of BASIC with many microcomputeroriented extensions. Also included are both a line-oriented editor and an Advanced CRT-oriented Editor.

All software tools and files are managed by a highly flexible filing system that allows nesting to any level a project requires. Included are a linker and library generator to assist in modular code development. The 8550's two 1Mbyte floppy discs provide more than adequate

mass storage.

For hardware/software integration, the 8550 offers debugging tools that cover the full range of 8500 Series support, both 8-bit and 16-bit. All use Real-Time Emulation, a superior debugging technique that permits code execution in realtime, with no waits or stretched clock pulses added. Symbolic debugging allow easily identified labels to be substituted for numerical addresses. Real-time debugging is available through the Realtime Prototype Analyzer (8-bit chips), and Trigger Trace Analyzer (16-bit and 8-bit chips) with stateof-the-art triggering capability.

**Program Entry and Editing**

Program entry and editing is accomplished via the standard line-oriented editor or the optional Advanced CRT-oriented Editor, so both line and screen-oriented editing are allowed.

Assembly and HLL Support

The 8550's assembler packages provide full code development support for a wide range of 8-bit and 16-bit chips. Powerful macros allow the designer to access frequently used sets of code by name reference. The linker, working with the

relocating features of the assembler, links and locates multiple code segments into a complete executable program. Additionally, a conditional assembly feature allows the designer to customize the final program by testing conditions to determine which of certain code seaments are to be assembled into the final program. Extensive English language diagnostics provide easy-to-understand error messages and locate the line in which the error has occurred. When assembly is completed, the assembled code is stored on disc in a binary format file.

For selected chips, high level language support is available to increase your development power. One language offered is  $MDL/\mu$ , a BASIC-like language created specifically for microcomputer design. Another is Pascal, with its structured approach that readily adapts to microcomputer software development. For both languages, Tektronix has added a full complement of extensions that allow code manipulation at the microprocessor level, including access to interrupt vectors, individual memory locations and I/O ports.

**Program Development and Data File Management**

The 8550's DOS/50 operating system helps the designer manage all phases of program development and debugging. DOS/50 supervises general I/O, file creation and maintenance, program assembly and compilation, program execution, monitoring and debugging. Data management is simplified through a versatile file management system, which allows the user to specify one main system directory, one root directory for each disc, and any number of sub-directories under the root directory. Data files may be created and entered directly into the root directory. As files are accumulated, the user may organize them into specific groups, each under its own specific directory. This allows the user to logically organize his files according to specific project needs.

**Advanced Debugging Tools**

The 8550 MDL also offers complete in-circuit emulation and hardware testing capabilities. With the appropriate prototype control probe for the target microprocessor, the user can transfer control from the 8550 to the prototype one block at a time, debugging at every stage. The Real-Time Prototype Analyzer option provides an invaluable tool for verifying and correcting execution of the program in real time. Its hardware trace function captures bus information from the program as it executes. This information can then be displayed in a trace format, or used to trigger a break in execution, time a program segment, or signal an external device such as a logic analyzer.

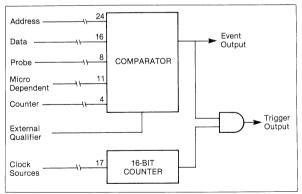

For 16-bit and 8-bit designs, the Trigger Trace Analyzer uses a high speed trace buffer capable of working with bus cycle speeds up to 8 MHz. The buffer is 62 bits wide to capture 16 data bits, 24 address bits, 14 emulator-dependent bits, and 8-bits from external hardware. Up to four independent events can be combined in both logical and sequential combinations to form a breakpoint or data storage trigger. The events themselves can be defined from a combination of bus data, pass delay counters, and an external qualifier. Each event can also initiate its own external output to trigger other instruments such as oscilloscopes and logic analyzers.

The Trigger Trace Analyzer allows a powerful and diverse set of debugging operations. For instance, the real-time length of an interrupt service routine can be measured while simultaneously counting the number of assertions from a second interrupt source. Or the maximum depth of a stack during program execution can be determined. To optimize code performance, the read or writes within any given address range can be isolated and counted, thus identifying heavily used areas to be recoded in assembly language.

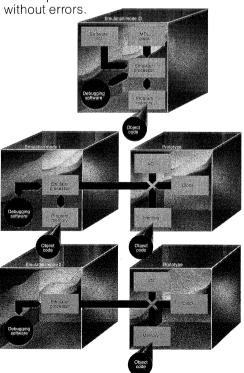

### Real Time Emulation — Three Emulation Modes

After an error-free assembly listing has been obtained, the resulting object code may be executed in system emulation mode 0 on the optional emulator processor. The emulator processor is identical in function to the microprocessor that will finally be installed in the user's prototype. Execution is performed under control of the debug system; during execution, program steps can be traced, software breakpoints can be set, and memory can be examined and changed as required. Should an error be discovered, that portion of the program can be corrected at the source level using the text editor. It can then be reassembled and executed again. This procedure continues until the program is correct.

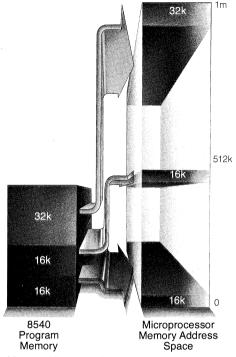

After the software has been debugged, it may be exercised on the prototype circuitry in the partial emulation mode (mode 1). During partial emulation, control may be released from the 8550 to the prototype in stages. The development software runs using 8550 memory space and prototype I/O and clock. The 8550 memory mapping feature allows code to be gradually mapped over to the prototype's memory in manageable blocks. Throughout partial emulation, the user has access to prototype circuitry through the debugging system, which enables him, as before, to trace, set breakpoints, examine and change memory and register contents.

In full emulation (mode 2) the program is run on the prototype, but program execution is still under the complete control of the debug system. All I/O and timing functions are directed to the prototype; all memory has been mapped over to the prototype; and only the prototype control probe is still in place, emulating the target microprocessor. Although the prototype is effectively free-standing, the user may still direct program activity from the 8550.

#### 8550 Parts and Functions

Fig. 1

#### 8550 CHARACTERISTICS

### 8301 MICROPROCESSOR DEVELOPMENT UNIT

Physical

| Height     | 11 in  | (280 mm) |

|------------|--------|----------|

| Width      | 17 in  | (430 mm) |

| Length     | 23 in  | (585 mm) |

| Net Weight | 60 lbs | (27 kg)  |

#### **ENVIRONMENTAL**

Operating

Temperature 32°F to 122°F (0°C to

50°C)

Humidity 90% @ 86°F to 140°F

(30°C to 60°C)

Altitude

Operating 0 to 15,000 ft

(4,500 m)

Storage 0 to 50,000 ft

(15,000 m)

#### POWER REQUIREMENTS

115 V ac (90 V ac-132 V ac) @ 48 to 66 Hz.

230 V ac (180 V ac-250 V) @ 48 to 66 Hz.

Outputs

5.2 V dc + 1%/-2% @ 35.0A + 12 V dc + 0/-5% @ 1.7A -12 V dc + 0/-5% @ 1.7A

#### 8501 DATA MANAGEMENT UNIT

Physical

Height 10.5 in (267 mm)

Width 16.8 in (424 mm)

Length 23.5 in (597 mm)

Net Weight 55 lb (25 kg)

#### **ENVIRONMENTAL**

Operating

Temperature 50°F to 104°F

(10°C to 40°C)

Humidity 20% to 80% relative

noncondensing

Altitude

Operating 0 to 8,000 ft (2500 m)

Derate max operating temp. by 1°C for each 300 m above 2400 m.

Storage 0 to 50,000 ft

(15,000 m)

#### POWER REQUIREMENTS

115 V ac (90-127 V RMS) @ 50 Hz  $\pm$ 1% or 60 Hz  $\pm$ 1%. 230 V ac (180-250 V RMS) @ 50 Hz  $\pm$ 1% or 60 Hz  $\pm$ 1%.

Outputs

24 V dc ±5% @ 2A 12 V dc ±3% @ 4A -12 V dc ±5% @ 540 mA 5 V dc ±5% @ 20 A 15 V dc ±10% @ 20 mA

Output Ripple

24 V dc 100 mV (p-p) ±12 V dc 120 mV (p-p) 15 V dc 50 mV (p-p) 15 V-dc 100 mV (p-p)

Overload Protection

Automatic current limit foldback.

#### FLEX DISC CHARACTERISTICS

Encoding — IBM compatible single or double density. Format must qualify as follows: MFM sectors — 256 bytes. FM sectors — 128 bytes.

Diskette Type — Single or double sided, soft sectored.

Capacity ---

Double sided, double density 1,021,696 bytes.

Single sided, double density 509,184 bytes.

Single sided, single density 256,256 bytes.

### 8560 Multi-User Software Development Unit

The Tektronix 8560 is a multiuser development system that, when used in conjunction with an 8540 Integration Unit, covers the entire microcomputer design process, from software development through hardware/software integration. At the same time, it allows maximum design flexibility by supporting a broad range of chips at both the 8-bit and 16-bit levels. The 8560's multi-user capability offers numerous advantages to the design team, such as lower cost per user, shared software and hardware resources, unified project management and enhanced security.

The heart of the 8560 is a minicomputer running under TNIX,\* a derivation of UNIX\*\* the powerful Operating System designed by Bell Laboratories. The CPU is an LSI 11/23 that operates in conjunction with two I/O processors for high performance throughput. A separate board is included to control two spooling line printers. System memory is 128K bytes (expandable to 256K bytes), and mass storage includes a 1 Mbyte floppy disc and a 35.6 Mbyte (formatted) Winchester hard disc. The I/O processors support baud rates up to 9600 bps, providing wide flexibility when interfacing with various terminals.

Software work stations each consist of a standard RS-232C CRT terminal, with the Tektronix CT8500 being recommended. In this manner, the system's software development capability can be expanded by simply adding terminals. Integration stations each consist of a Tektronix 8540 Integration Unit, which has built-in high-speed serial communications compatibility with the 8560 or an 8550 MDL.

For added flexibility, the 8560 can be configured with the 8540's and 8550's in several different communications modes. The 8540 can be connected in-line with a terminal to a single 8560 port, or without a terminal to a separate port. In either configuration, a user can control any 8540 in the system including several units at the same time. In addition, it is possible to use many of the 8560's powerful command resources when debugging with the 8540. This includes the ability to use the 8560's hardware and software for I/O simulation in the early states of debugging.

The 8560 will support up to two line printers, with the Tektronix 4643 being recommended. The line printers will both operate in the spooling mode, so as not to tie up the users' terminals while printing.

TNIX Operating System

Running under the TNIX operating system, the 8560 can include a wide variety of software design tools offered by Tektronix. These include macro assemblers and compilers\*\*\* for both 8-bit and 16-bit chips; loader/linkers to combine object files into executable object code; and several types of editors, including an advanced screenoriented version. There is also a text processing package that can be a valuable aid to software documentation, and a number of utility packages to expand system capabilities in various ways.

The 8560's TNIX operating system was derived directly from Bell Laboratories' UNIX Operating System, an operating system that has gained widespread acceptance throughout the computer world. TNIX takes all the proven advantages of UNIX and applies them directly to the specific tasks required during microcomputer design.

TNIX includes a hierarchical filing system that greatly enhances the ease and speed of filing operations. It is organized with a "root" directory on top and descending levels of priority underneath. Each level may contain either files or directories that point to more files on a lower level.

TNIX also provides a sophisticated system of read/write protection that guards user material but retains the inter-file access needed to enhance productivity. Each user can specify read, write, or execute protection on any of three levels: user, user's group or public. This way, files can first be completely protected while under initial development, then released to those working on related sections of the program, and finally released to the entire project after debugging is completed. To enhance communication between users, TNIX includes a system of electronic mail that lets team members send messages to one another. It also allows direct communication between two users at separate terminals, plus the ability to broadcast a single message to all terminals. These various communications modes can be a valuable asset to both team members and team management.

Powerful command structures simplify software development and integration

TNIX uses an extremely flexible command structure, one that permits effective programming at the expert level as well as the beginner level. In all cases, TNIX commands let the user concentrate on software design instead of system manipulation. One simple, but very powerful TNIX command operation is pipelining. It permits the output of one command to act as the input to another. At an even higher level of refinement, TNIX permits the construction of intelligent command files that can be called by the user and executed as a single unit.

Other TNIX command features include full read-ahead which lets the user type in commands as fast as possible, without waiting for previous commands to finish. Another time saver is job prioritization, which lets the user concurrently run several jobs which may be at different levels of priority. For instance, a compilation could be detached and run in the background while the user went on to start editing a new source file. This feature saves time while making more intelligent use of the system's resources.

To optimize the user interface, TNIX includes a special amenity called GUIDE, which combines the best features of both menu-driven and command-driven systems. GUIDE lets the user select any system operation from a menu display. and then automatically completes the operation. At any time, the user can exit from GUIDE and escape back to TNIX and its user-driven command format. This way, the user can employ the menu as a learning tool, but is able to depart to the regular TNIX command format for more sophisticated operation.

<sup>\*</sup>TNIX is a trademark of Tektronix

\*\*UNIX is a trademark of Bell Laboratories

\*\*\*Ayailable 2nd quarter, 1982

Automatic module combination cuts complexity

During debugging, software modules that exhibit defects must have corrections entered into their original source code files. Before debugging can resume, all files affected by the changed source modules must be recompiled or reassembled into new, updated object code modules. Otherwise, new and old versions of the interdependent object modules will be mixed.

To streamline debugging, TNIX includes a special feature called 'make" which uses a control file to oversee the modular combination process and ensure that all modules are of the most recent version when combined for execution. "Make" can cut recompiling or reassembling time to an absolute minimum by performing these operations only on files that actually require it.

Advanced software development tools

The 8560 MDL system offers a large selection of software development tools that can be run under TNIX. These include a variety of 8-bit and 16-bit assemblers with features such as macro capability, conditional assembly and relocatable code. Also 16-bit compilers with features like structured constants, bit manipulation and re-entrant code.

Other specialized tools include a loader/linker, and a library generatory. Also two types of editors, including an advanced CRT-oriented editor that allows fast, efficient text manipulation at both the line and character level.

In addition, there are a number of 8560 system utility packages available that offer advanced support to microcomputer design projects. Among these is a text processing package that can be a valuable aid when documenting software, and native programming package for developing your own 8560 software.

Hardware/Software Integration

To handle hardware/software integration tasks, the 8560 is optimized to use the Tektronix 8540 Integration Unit as peripheral work station. Once code targeted for the prototype has been assembled or compiled and linked into executable object modules, it is loaded into the 8540's program memory via a high-speed interface. The code can now be gradually introduced to the

hardware using Real-Time Emulation, a powerful debugging method that employs a processor identical in function to the one targeted for the prototype.

Data captured by the 8540 during debugging and testing can be displayed on the console terminal, the line printer, or routed to the 8560 for further processing.

Real-Time Emulation takes place in three progressive modes, all under the control of the 8540's debug software. During the first mode, all code is executed out of the 8540's program memory, with I/O simulated by software insertions that use 8560 peripherals or files for input and output. In this manner, prototype software debugging can begin even before the hardware becomes available. During the second mode, I/O and clock functions are transferred from the 8540 to the prototype, and code can be mapped over to the prototype memory in manageable blocks as it is debugged. A control probe now connects the emulator processor to the vacant processor socket on the prototype board. During the final mode, all code is installed in the

prototype memory, as well as clock and I/O functions. Through the control probe, the 8540 can now exercise prototype hardware in the same manner that it will function when standing alone.

During all three modes of emulation, the 8540's powerful debug software can be applied. Breakpoints can be set using mnemonic symbols for key program locations. The status of processor registers can be examined on a cycle-bycycle basis. All registers and memory locations can be examined and modified. And for detailed analysis of real-time execution on the prototype bus and selected hardware points, an optional Trigger Trace Analyzer is available with four powerful trigger channels that allow highly selective data acquisition.

For added power during debugging, the 8540's resident command set is also included as part of the TNIX command set. This allows the full range of TNIX command manipulation features to be applied to 8540-based operations. It is even possible to intermix conventional TNIX and 8540 commands in a single command structure.

## 8560 Physical, Environmental and Electrical Characteristics PHYSICAL CHARACTERISTICS

| Height<br>H1<br>H2 | 10.5 inches<br>11.1 inches | (267 mm)<br>(282 mm) |

|--------------------|----------------------------|----------------------|

| Width              | 16.8 inches                | (428 mm)             |

| Length             |                            |                      |

| L1                 | 23.3 inches                | (593 mm)             |

| L2                 | 25.4 inches                | (646 mm)             |

| Weight             | 72.5 lbs.                  | (33 kg)              |

#### **ENVIRONMENTAL CHARACTERISTICS**

| 1) Atmospheric Ambient temperature Relative humidity | Operating<br>10 to 40°C<br>20 to 80%<br>(non-condensing) | Storage -10 to 65°C 10 to 80% (non-condensing) |

|------------------------------------------------------|----------------------------------------------------------|------------------------------------------------|

| Temp. rate of change                                 | 1°C/5 minutes max                                        | 24°C/hour max                                  |

| 2) Altitude Operating                                | 0 to 8,000 feet (2 500<br>by 1°C for each 300 r          | m). Derate max temp<br>n above 2 400 m.        |

| 3) Storage<br>Static Discharge                       | 0 to 40,000 ft (12 200                                   | m).                                            |

| Operating                                            | 0 to 12.5 KV without e                                   | ffect on equipment                             |

#### **ELECTRICAL CHARACTERISTICS**

0 to 12.5 KV without hard failures.

operation.

Power Requirements 115 V Nominal (90-132 VRMS)

430 Watts Max.

or 230 V Nominal (180-250 VRMS) Line Frequence Range: 48-66 Hz Power Consumption

## 8540 Integration Unit

The Tektronix 8540 Integration Unit is used with a 8560 Multi-user Software Development Unit or a General Host Computer, to integrate, test and debug microprocessor based software. The 8540 supports the hardware and software integration phase of a microprocessor/microcomputer based design. The Tektronix 8560 or other host computer supports the software development task.

**Application**

8540 support is employed when the software has been developed to the object code level and is ready to be tested with the hardware. The object code binary program is downloaded to the 8540 and stored in its resident program memory or, if available, in the prototype's own memory. If the prototype hardware is not available. the software can be executed on the 8540 emulator processor using Mode 0 emulation.

A wide variety of emulators are available for in-circuit testing and debugging. For in-circuit testing, the emulator probe replaces the microprocessor chip in the prototype. In emulation mode 1 or mode 2, the software can interact directly with the prototype hardware.

The designer controls and monitors the testing process via a CRT Terminal like the Tektronix CT8500.

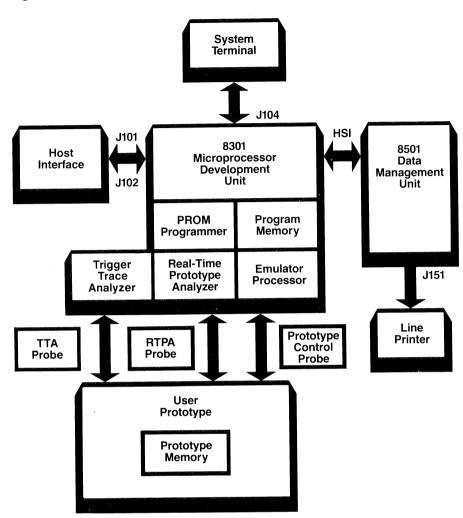

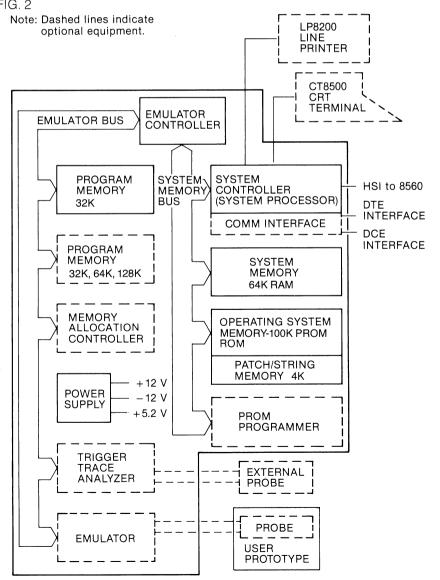

**Block Diagram**

As shown in figure 2, a block diagram of the 8540, the complete operating system is contained in 125K byte PROM/ROM memory. The operating system is loaded from PROM and executed in the 64K-byte system memory. User symbol table information is also stored in system memory.

Part of the 8540 memory system also contains a non-volatile EEPROM buffer to store command strings and firmware update information. Complex and repeated command sequences can be permanently stored and then recalled by employing one user-definable string name. The EEPROM is also used to store update information for firmware maintenance.

The 8540 also includes 32K bytes of static program memory for use by the emulator processor. The static program memory can be expanded to 256K bytes and with the optional Memory Allocation Controller, segments of this memory can be mapped anywhere in the emulator processor's address range.

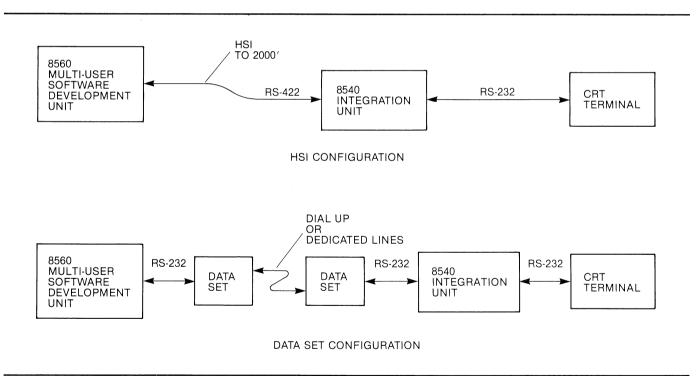

8540 System Configuration Local Interface Configuration. The 8540 Integration Unit connects to the 8560 Multi-user Software Development Unit via a high speed serial interface. Interconnecting cable lengths of up to 2,000 feet can be accommodated without performance degradation. A specialized

interface protocol is used between the 8540 and the 8560 to eliminate any errors that might occur in the transmission process.

Remote Interface Configuration. For remote configurations (greater than 2,000 feet), the 8540 can be connected to the 8560 via RS-232 compatible data sets. Typical intermediate range data sets can be used over dedicated lines for distances of approximately 8 kilometers (5 miles) at data rates up to 9600 baud. For longer distances, data sets can also be used in conjunction with dial-up phone lines.

#### 8540 Block Diagram

FIG. 2

**Operating Modes**

The Tektronix CT8500 CRT Terminal (or a user supplied RS-232 terminal) is the user's interface with the 8540/8560 system. 8540 & 8560 commands that are entered from the terminal are routed first to the 8560. The 8560 processes each command line and routes 8540 commands to the appropriate 8540. This allows commands to be intermixed on a single line and also gives the user the ability to control any 8540 (or several 8540s) in the system. (The 8540 can be configured to operate through a separate 8560 port with no terminal attached.) A local mode is also available so user can communicate directly with the 8540.

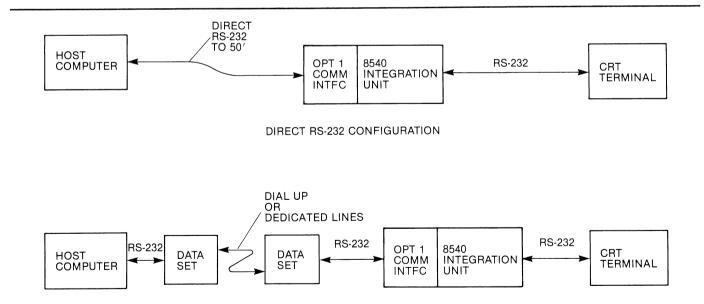

8540 (With Option 1 Comm Interface) Host Computer Configuration

The 8540 Integration Unit is interfaced to a host computer via an RS-232 serial port. Data bytes are ASCII encoded and transmitted asynchronously at speeds up to 9600 baud between the 8540 and the host computer. For local interface configurations (up to 50 feet), the 8540 can be hardwired directly

to the host computer using a standard RS-232 cable. For remote configurations (more than 50 feet) the 8540 interfaces to the host computer via a data set arrangement. Data sets can connect over moderate distances using dedicated lines or virtually unlimited distances with conventional phone lines.

The 8540 can communicate with a host computer in several modes including:

Local Mode. In this mode the terminal communicates directly with the 8540 operating system to control the emulation and debugging process.

Terminal Transparent Mode. In this mode the terminal communicates with a host computer using standard protocol; keyboard data is transmitted to the host and host data is displayed on the terminal's display screen.

Formatted Upload/Download. In this mode microprocessor object code is transferred between the host computer and the 8540 program (emulation) memory. Binary data is encoded into Extended TEKHEX format and transmitted in

message blocks. Checksum information is also included in the message blocks to allow detection of communication errors.

Details of TEKHEX encoding and protocol are included in the 8540 System Users Manual.

**Emulation Support**

When a program is ready for testing, the object module is downloaded from the host computer (or 8560) into 8540 emulator memory. When a symbol table is included with the object module, it is also downloaded and stored in a separate portion of system memory. Program symbols can then be used to reference memory locations instead of the absolute addresses.

The object code is now executed by the emulator processor under control of the 8540 debugging system. Trace displays to the screen (or line printer) show all pertinent information including instruction mnemonics, processor status and any program symbols. The user can set breakpoints to stop in critical sections or use the trace display to show selected instructions or address ranges.

DATA SET CONFIGURATION

There are three progressive emulation modes available in the 8540. In the first (mode 0) the 8540 supplies all memory, clock, and interface signals to the emulator processor. No prototype hardware is required. In the second (mode 1) the clock and interface signals are provided by the prototype hardware. The emulator processor connects to the prototype microprocessor socket via the prototype control probe. The program under test still resides in the 8540 but as debugging progresses, it can be gradually transferred (mapped) over to the prototype's memory. In the third (mode 2) all of the program is transferred to prototype memory. The 8540 still maintains control of program execution through the debugging system. For more specific emulator support information, refer to the appropriate data sheet for each (supported) emulator.

#### **Diagnostics**

The 8540 has a complete diagnostic subsystem. On each power-up cycle, diagnostic firmware checks all available 8540 memory and verifies that all boards are functional.

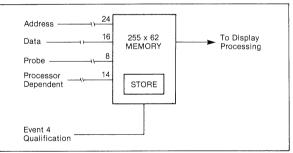

### Trigger Trace Analyzer (Optional)

The Trigger Trace Analyzer (TTA), optional equipment for the 8540 is a powerful debugging tool. It monitors program flow in real time and allows sophisticated control and analysis of the emulator processor. The TTA stores program information in a high-speed 255event buffer. Each event contains 62-bits of information: up to 24-bits of address, 16-bits of data, up to 14-bits of processor information, and 8-bits of external probe information. TTA information is displayed on the terminal in processor specific mnemonics along with all pertinent register and flag information.

#### **PROM Programmer (Optional)**

The PROM Programmer, optional equipment for the 8540 is a general purpose controller unit with plug-in adapter modules. Each module supports a group of similar programmable devices. Functions include: READ, WRITE and COMPARE.

#### 8540 General Specifications

Operating System (Software): DOS/50 derivative (contained in 8k PROM/ROM's) i.e., 96k bytes, command interpreter and kernel 20k bytes diagnostics: 4k bytes patch and command storage (EEPROM)

#### Card Slot Usage Standard Boards:

system controller emulator controller system memory (64k RAM) program memory (32k RAM) system memory (224k PROM/ ROM capacity)

#### **Empty Board Slots:**

system side = 1 slot program side = 11 slots

**Electrical Characteristics** Nominal Operating Voltage: 115 Vac and 230 Vac at 60 Hz

Power Requirements: 700 W max Line Voltage Ranges: 90 to 132 Vac

and 180 to 250 Vac

Line Frequency Range: 48 to 66 Hz

#### I/O Ports

I/O Ports: J100 (8560 Interface) J101 (remote DTE male); J102 (remote DCE female) J103 (Line Printer, Aux); J104 (Terminal)

#### I/O Port Data Rates:

J100 (HSI) = 153.6k baudJ101, J102, J103, J104 = 110/extCLK, 150, 300, 600, 1200, 2400, 4800. 9600 baud

#### Reliability

MTBF: 6700 hr (calculated) MTTR Board: 0.5 hr. MTTR Component: 1.5 hr.

Standards Compliance: UL1244; CSA Bulletin 556B; IEC 348

#### **Environmental Characteristics** Temperature Range

Operating: 0°C to 50°C (32°F to

Storage: 55°C to 75°C (67°F to 167°F)

#### Altitude Range

Operating: Sea level to 4500 m (15.000 ft)

Storage: Sea level to 15,000 m (50,000 ft)

Humidity: 0 to 90% noncondensing (0 to 50°C)

#### Physical Characteristics

#### Cabinet Dimensions:

Height = 280 mm (11 in)Width = 430 mm (17 in)Depth =  $585 \, \text{mm} (23 \, \text{in})$

Cabinet Weight: 26 kg (57.5 lb) Shipping Weight: 35 kg (77.5 lb)\*

Cabinet Color: 3 tone; ivory/gray, smoke tan, earth brown

\*Standard configuration only, no options.

#### **RS-232 Communications** Interface (Option 1)

Interface signals are routed to and from the 8540 system controller board via rear panel connectors J101 (male) and J102 (female). Table 2 lists the J101/J102 pin numbers and corresponding signal names and descriptions. Baud rate on transmitted data and received data is selectable from 110 to 9600 baud. All signals are RS-232-C compatible.

Table 2. Interface signals (Option 1, Comm Interface)

| Signal<br>Name | Circuit | J101<br>DTE       | J102<br>DCE       | Pin |

|----------------|---------|-------------------|-------------------|-----|

| GND            | AA      | Protective ground | Protective ground | 1   |

| Tx             | ВА      | Ŏut               | Ĭn                | 2ª  |

| Rx             | BB      | In                | Out               | 3ª  |

| RTS            | ČA      | Out <sup>b</sup>  | Inc               | 4   |

| CTS            | CB      | Ind               | Oute              | 5   |

| DSR            | ČČ      | In <sup>f</sup>   | Out               | 6   |

| GND            | AB      | Signal<br>ground  | Signal<br>ground  | 7   |

| DCD            | CF      | Ĭnª               | Öut               | 8   |

| DTR            | CD      | Out               | In <sup>h</sup>   | 20  |

Selectable, 110-9600 baud

DTE 1, DTE 2 modes; goes high when data to send

DCE mode; must be high before 8540 accepts data

DTE 1 mode; must be high before 8540 sends data

DCE mode; goes low when 8540 sends data

DTE 2 mode; must be high before 8540 sends data

DTE 1, DTE 2 mode; must be high before 8540 accepts data

DCE mode; must be high before 8540 sends data

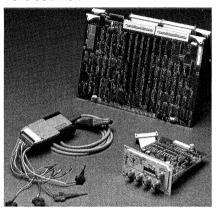

# Integration Tools Emulators & Probes RTPA TTA MAC Board

#### Emulator Processor and Prototype Control Probe Support Packages

The 8500 Microprocessor Development Lab family support a wide variety of different microprocessors and microcomputers.

#### **Emulators**

Emulator packages may be ordered as systems options. These options provide the capabilities necessary to fully emulate the target microprocessor in a user's proto-

type system.

The emulator processor, which resides on a plug-in circuit module along with controlling logic circuitry, enables the user to execute and debug the program on a microprocessor identical to the one which will be used in the prototype, while giving him access up to 256K bytes of Microprocessor Lab program memory.

Software execution is performed under control of DOS-50 in the 8550 system, and under control of TNIX in the 8560 system. During software development, DOS-50 allows the creation of a tree-like file structure with subdirectories to whatever nesting level a project requires. When converting source code to object code, it provides complete supervision of assembly or compilation procedures. During hardware/software integration, DOS-50 handles prototype execution monitoring and debugging operations. It also takes care of general I/O, intersystem communication and PROM programming.

TNIX, the operating system used in the 8560 system uses timesharing to apportion system resources among up to eight workstations plus system utilities. A hierarchial-type filing system is used that groups files and directories logically. Each file carries a date/time attribute to help confirm that the proper version is being accessed. A security system allows password protection, multiple-user file access, and work copies according to current project needs.

#### **Probes**

The prototype control probe connects the emulator processor card to the prototype microprocessor, and allows a designer to transfer program control in three stages from the 8550 or 8560/8540 MDL to the prototype.

All emulation operations are controlled by the powerful Microprocessor Lab system software. The user is able to monitor program execution, set software breakpoints, examine and change memory and register contents. Debug trace information is displayed in a format unique to the microprocessor, with instruction fetches disassembled into mnemonics for easy interpretation.

#### **Three Emulation Modes**

Once an object code file has been created, the program may be exercised in system mode 0. During execution, program steps can be traced, hardware breakpoints can be set, and memory can be examined and changed as reguired. Should an error be discovered, that portion of the program can be corrected at the source level using the text editor. Object code can then be reassembled and reexecuted. This procedure continues until the developmental software program is complete and can be executed without errors.

After the developmental software has been debugged, it may be exercised on the prototype circuitry (mode 1). During partial emulation, control may be released in stages to the prototype. Developmental software is sequenced using the emulator memory space and the prototype I/O and clock. The memory mapping feature allows code to be gradually mapped over to the prototype's memory in blocks. Throughout partial emulation, the program designer has access to prototype circuitry. This access enables the examination and changing of memory and register contents, hardware tracing, and setting of breakpoints.

In full emulation, mode 2, the developmental software program is run on the prototype, but program execution is still under the complete control of the 8550 MDL or 8540 system. All I/O and timing functions are directed by the prototype and all memory has been mapped over to it. The Prototype Control Probe is connected and still emulating the prototype microprocessor. Although the prototype is effectively free-standing, the designer may still direct program activity from the console terminal.

## 8080A and 8085A Emulator Processors and Prototype Control Probes

8080/8080A and 8085/8085A refer to microprocessors manufactured by Intel Corporation. Tektronix, Inc. does not guarantee that other vendors' versions of the 8080/8085 will be compatible with the Tektronix Microprocessor Labs.

### 8080A Emulator Support Package Characteristics

#### PHYSICAL CHARACTERISTICS

Length: 6-foot cable from the Emulator Processor to the interface assembly. 1.5-foot cable from the interface assembly to the 40-pin plug.

Configuration, 6-foot cable: Two 40-conductor groundplane ribbon cables with chassis groundplane and signal paths.

Configuration, 1.5-foot cable: Two twisted pair of 40-conductor cables.

Termination, 6-foot cable: The interface assembly contains resistive termination and receivers for data, address and control from the Emulator Processor module. (The 1.5-foot cable is not terminated.)

#### AC CHARACTERISTICS

**Emulation Clock**

Mode 1 or Mode 2 (user's clock) with 8085A prototype control probe.

Mode 0 (system clock)

Mode 1 or Mode 6.25 MHz max; crystal, RC timing network or TTL input to X1.

6.25 MHz ± 0.01%.

### 8085A Emulator Support Package Characteristics

#### PHYSICAL CHARACTERISTICS

Length: 6-foot cable from the Emulator Processor to the interface assembly. 1-foot cable from the interface assembly to the 40-pin plug.

Configuration, 6-foot cable: Two 40-conductor ribbon cables with chassis groundplane and signal paths.

Configuration, 1-foot cable: Two twisted pair of 40-conductor cables.

Termination, 6-foot cable: The interface assembly contains receivers for data, address and control from the Emulator Processor module. (The 1-foot cable is not terminated.)

## TIMING CHARACTERISTICS Representative 8080A Emulator 8080A Microprocessor Timing Differences

|                                |                                                                      | Proc | essor           | Emu  | latora |      |

|--------------------------------|----------------------------------------------------------------------|------|-----------------|------|--------|------|

| Symbol                         | Parameter                                                            | Min. | Max.            | Min. | Max.   | Unit |

| tCY                            | Clock Period                                                         | .48  | 2.0             | .48  | 2.0    | μs   |

| <sup>t</sup> r, <sup>t</sup> f | CLK Rise and Fall Time                                               | 0    | 50              | 0    | 50     | ns   |

| $^{t}DA$                       | Address Output Delay from $\phi$ 2                                   |      | 200             |      | 185    | ns   |

| <sup>t</sup> DD                | Data Output Delay<br>from φ2                                         |      | 220             |      | 220    |      |

| <sup>t</sup> DC                | Signal Output Delay from $\phi$ 1 or $\phi$ 2 (SYNC, WR, WAIT, HLDA) |      | 128             |      | 165    | ns   |

| <sup>t</sup> DF                | DBIN Delay from $\phi$ 2                                             | 25   | 140             | 40   | 180    | ns   |

| <sup>t</sup> DI                | Delay for Input Bus to Enter<br>Input Mode                           |      | <sup>t</sup> DF | 48   | 205    | ns   |

| <sup>t</sup> DS1               | Data Setup Time during $\phi$ 1 and DBIN                             | 30   |                 | 69   |        | ns   |

| <sup>t</sup> DS2               | Data Setup Time to $\phi2$<br>During DBIN                            | 150  |                 | 189  |        | ns   |

| <sup>t</sup> DH                | Data Hold Time from $\phi2$ during DBIN                              | b    |                 | b    |        | ns   |

| <sup>t</sup> IE                | INTE Output Delay from $\phi$ 2                                      |      | 200             |      | 255    | ns   |

| RS                             | READY Setup Time during $\phi$ 2                                     | 120  |                 | 130  |        | ns   |

| <sup>t</sup> HS                | HOLD Setup Time to $\phi2$                                           | 140  |                 | 180  |        | ns   |

| tIS                            | INT Setup Time during $\phi$ 2 (during $\phi$ (1) in Halt Mode)      | 120  |                 | 190  |        | ns   |

| tΗ                             | Hold Time from $\phi$ 2 (READY, INT, HOLD)                           | 0    |                 | c ·  |        |      |

| <sup>t</sup> FD                | Delay to Float during Hold (Address and Data Bus)                    |      | 120             |      | d      | ns   |

| <sup>t</sup> AW                | Address Stable Prior to WR                                           | е    |                 | f    |        | ns   |

| $^{t}DW$                       | Output Data Stable Prior to WR                                       | g    |                 | h    |        | ns   |

| tWD                            | Output Data Stable from WR                                           | i    |                 | j    |        | ns   |

| tWA                            | Address Stable from WR                                               | i    |                 | j    |        | ns   |

| <sup>t</sup> HF                | HLDA to Float Delay                                                  | k    |                 | d    |        | ns   |

| <sup>t</sup> WF                | WR to Float Delay                                                    | 1    |                 | d    |        | ns   |

| <sup>t</sup> AH                | Address Hold Time after DBIN                                         | -20  |                 | -50  |        | ns   |

- a. All emulator delays are given with reference to  $\phi 1$  and  $\phi 2$  as applied to the emulator CPU. The delay from the prototype  $\phi 1$  and  $\phi 2$  to the CPU  $\phi 1$  and  $\phi 2$  is 98 ns (maximum) and 34 ns (minimum).

- b. Data input should be enabled with DBIN status. No bus conflict can then occur and data hold time is assured. †DH = 50 ns or †DF whichever is less.

- c. READY = -10 ns minimum

- INT = -30 ns minimum

- HOLD = -15 ns minimum

- d. Emulator address and data bus float is based upon (HLDA x DBIN). Maximum float delay is 220 ns after the rising edge of φ1 for non-DBIN cycles and 210 ns after the rising edge of φ2 for DBIN cycles.

- e.  ${}^{t}AW = {}^{2t}CY {}^{t}D3 {}^{t}r\phi2 140 \text{ ns}$

- f.  ${}^{t}AW = 2{}^{t}CY {}^{t}D3 {}^{t}r\phi 2 130 \text{ ns}$

- g.  $^{t}DW = {^{t}CY} {^{t}D3} {^{t}r}\phi = 170 \text{ ns}$

- h.  $^{t}DW = {^{t}CY} {^{t}r}\phi 2 175 \text{ ns}$

- i. If not HLDA,  ${}^{t}WD = {}^{t}WA = {}^{t}D3 + {}^{t}r\phi2 + 10 \text{ ns}$

- if HLDA, tWD = tWA = tWF if HLDA, see noted

- j. If not HLDA,  ${}^{t}WD = {}^{t}Wa = {}^{t}CY {}^{t}r\phi = 20 \text{ ns}$  if H

- k.  ${}^{t}HF = {}^{t}D3 + {}^{t}r\phi\$ 50 \text{ ns}$ l.  ${}^{t}WF = {}^{t}D3 + {}^{t}r\phi2 - 10 \text{ ns}$

#### Timing Assumptions

- CPU timing reference Intel Component Data Catalog (1979)

- 2. All emulator timing is relative to clock at emulator CPU. See Note<sup>a</sup> for CLK delays for prototype.

- Emulator delays are calculated from maximum values in the second edition of The TTL Data Book for Design Engineers, published by Texas Instruments, and minimum delays equal to 20 percent of maximum.

## TIMING CHARACTERISTICS Representative 8085 Emulator 8085 Microprocessor Timing Differences

| Symbol            | Parameter                                              |      |      |                  | latora |      |

|-------------------|--------------------------------------------------------|------|------|------------------|--------|------|

|                   | Farameter                                              | Min. | Max. | Min.             | Max.   | Unit |

| tr, tt            | CLK Rise and Fall Time                                 |      | 30   |                  | 30ª    | ns   |

| <sup>t</sup> XKR  | X1 Rise to CLK Rise                                    | 30   | 120  | 82               | 191    | ns   |

| <sup>t</sup> XKF  | X1Rise to CLK Fall                                     | 30   | 150  | 82               | 221    | ns   |

| <sup>t</sup> AC   | A8-15 Valid to Leading<br>Edge of Control <sup>a</sup> | 270  |      | 255              |        | ns   |

| <sup>t</sup> ACL  | A0-7 Valid to Leading<br>Edge of Control               | 240  |      | 225              |        | ns   |

| <sup>t</sup> AD   | Valid Address to Valid Data In                         |      | 575  |                  | 540    | ns   |

| <sup>t</sup> AFR  | Address Float after Leading<br>Edge of READ INTA       |      | 0    | -85 <sup>b</sup> |        | ns   |

| <sup>t</sup> AL   | Address Valid before Trailing<br>Edge of ALE           | 115  |      | 100              |        | ns   |

| <sup>t</sup> ALL  | A0-A7 Valid before Trailing<br>Edge of ALE             | 90   |      | 75               |        | ns   |

| <sup>t</sup> ARY  | READY Valid from Address Valid                         |      | 220  |                  | 190    | ns   |

| <sup>t</sup> CA   | Address (A8-A15) Valid after Control                   | 120  |      | 135              |        | ns   |

| <sup>t</sup> CL   | Trailing Edge of Control to<br>Leading EDGE of ALE     | 50   |      | 40               |        | ns   |

| <sup>t</sup> DW   | Data Valid to Trailing Edge of WRITE                   | 420  |      | 405              |        |      |

| <sup>t</sup> HABE | HLDA to BUS ENABLE                                     |      | 210  |                  | 55°    | ns   |

| †HABF             | Bus Float after HLDA                                   |      | 210  |                  | 55     | ns   |

| †HACK             | HLDA Valid to Trailing Edge of CLK                     | 110  |      | 80               |        | ns   |

| †HDH              | HOLD Hold Time                                         | 0    |      | -30              |        | ns   |

| <sup>t</sup> HDS  | HOLD Setup Time to Trailing<br>Edge of CLK             | 170  |      | 190              |        |      |

| HNI               | INTR Hold Time                                         | 0    |      | d                |        | ns   |

| tINS              | INSTR, RST, and TRAP Setup time to Falling Edge of CLK | 160  |      | d                |        | ns   |

| <sup>t</sup> LA   | Address Hold Time after ALE                            | 100  |      | 85               |        | ns   |

| <sup>t</sup> LC   | Trailing Edge of ALE to<br>Leading Edge of Control     | 130  |      | 115              |        | ns   |

| <sup>t</sup> LCK  | ALE Low During CLK High                                | 100  |      | 85               |        | ns   |

| <sup>t</sup> LDR  | ALE to Valid Data During Read                          |      | 460  |                  | 445    | ns   |

| <sup>t</sup> LDW  | ALE to Valid Data During Write                         |      | 200  |                  | 185    | ns   |

| <sup>t</sup> LRY  | ALE to READY Stable                                    |      | 110  |                  | 95     | ns   |

| <sup>t</sup> RAE  | Trailing Edge of READ to<br>Re-enabling of Address     | 150  |      | 135              |        | ns   |

| <sup>t</sup> RD   | READ (or INTA) to Valid Data                           |      | 300  |                  | 265    | ns   |

| <sup>t</sup> RDH  | Data Hold Time after READ INTA                         | 0    |      | -35              |        | ns   |

| <sup>t</sup> RYH  | READY Hold Time                                        | 0    |      | -20              |        | ns   |

| <sup>t</sup> RYS  | READY Setup Time to Leading<br>Edge of CLK             | 110  |      | 130              |        | ns   |

| tWD               | Data Valid after Trailing<br>Edge of WRITE             | 100  |      | 85               |        | ns   |

| tWDL              | Leading Edge of WRITE to Data<br>Valid                 |      | 40   |                  | 25     | ns   |

<sup>&</sup>lt;sup>a</sup>The 8085A probe cable uses an FET oscillator buffer in the probe tip. For a crystal applied to X1 and X2 the delay to the CPU is a maximum of 18 ns from the clock phase appearing at X2. For an external clock input at X2, the clock presented to the CPU will be inverted (as output at X2) and typically delayed 40 ns.

<sup>d</sup>Maximum input delays.

INTR RST TRAP (20 ns) (15 ns) (60 ns)

bAddress float will occur for a maximum of 45 ns after ALE drops low.

<sup>°</sup>Although bus drivers to prototype will be turned on, CPU drive to drivers will be tri-stated for a maximum of 210 ns.

## **Z80A Emulator Processor and Prototype Control Probe**

Z80A is a trademark of Zilog Corp. Tektronix, Inc. does not guarantee that other vendors' versions will be compatible with Tektronix 8550 MDL or 8540.

Z80A Emulator Support Package Characteristics

#### PHYSICAL CHARACTERISTICS

Length: 1.8 meter (6 feet) of cable from the Emulator Processor to the interface assembly; 305 millimeter (one foot) of cable from the interface assembly to the 40-pin plug.

Configuration, 1.8 meter cable: Two 40-conductor ribbon cables with chassis ground plane and signal paths.

Configuration, 305 millimeter cable: Two 40-conductor twisted pair cables.

Termination, 1.8 meter cable: The interface assembly contains receivers for data, address, and control from the Z80A emulator processor module. The 305 millimeter cable is not terminated.

## TIMING CHARACTERISTICS Representative Z80A Emulator Z80A Microprocessor Timing Differences

|                                       |                                                            | Proc | essor | Emu  | lator |      |

|---------------------------------------|------------------------------------------------------------|------|-------|------|-------|------|

| Symbol                                | Parameter                                                  | Min. | Max.  | Min. | Max.  | Unit |

| tC                                    | Clock Period                                               | .25  | [1]   | .25  | [1]   | ns   |

| ${}^{t}W\phi_{H}$                     | Clock Pulse Width, Clock High                              | 110  | *a    | 110  | *a    | ns   |

| ${}^{t}W\phi_L$                       | Clock Pulse Width, Clock Low                               | 110  | 2000  | 110  | 2000  | ns   |

| <sup>t</sup> r, f                     | Clock Rise and Fall Time                                   |      | 30    | *b   | 30    | ns   |

| <sup>t</sup> D <sub>AD</sub>          | Address Output Delay                                       |      | 110   |      | 130   | ns   |

| tF <sub>AD</sub>                      | Delay to Float                                             |      |       |      | 85*c  | ns   |

| <sup>t</sup> D <sub>D</sub>           | Data Output Delay                                          |      | 150   |      | 170   | ns   |

| <sup>t</sup> F <sub>D</sub>           | Delay to Float During Write Cycle                          |      | 90    |      | 90*f  | ns   |

| $^{t}S\phi_{\mathtt{D}}$              | Data Setup Time to Rising Edge<br>of Clock During M1 Cycle | 50   |       | 30   |       | ns   |

| ${}^{t}S\phi_{\mathtt{D}}$            | Data Setup Time to Falling Edge of Clock During M2 to M5   | 60   |       | 40   |       | ns   |

| $^{	extsf{t}}DL\phi_{MR}$             | MREQ Delay from Falling Edge of Clock, MREQ Low            | 20   | 85    | 40   | 105   | ns   |

| $^{	extsf{t}}DH\phi_{	extsf{MR}}$     | MREQ Delay From Rising Edge of Clock, MREQ High            |      | 85    |      | 105   | ns   |

| $^{t}DH\phi_{MR}$                     | MREQ Delay from Falling Edge of Clock, MREQ High           |      | 85    |      | 105   | ns   |

| $^{	extsf{t}}$ DL $\phi_{	extsf{IR}}$ | IORQ Delay from Rising Edge of Clock, IORQ Low             |      | 75    |      | 95    | ns   |

| $^{	extsf{t}}DL\phi_{IR}$             | IORQ Delay from Falling Edge<br>of Clock, IORQ Low         |      | 85    |      | 105*c | l ns |

| $^{t}DH\phi_{IR}$                     | IORQ Delay from Rising Edge of Clock, IORQ High            |      | 85    |      | 105   | ns   |

| $^{	extsf{t}}DH\phi_{	extsf{IR}}$     | IORQ Delay from Falling Edge<br>of Clock, IORQ High        |      | 85    |      | 105   | ns   |

| $^{	extsf{t}}DL\phi_{	extsf{RD}}$     | RD Delay from Rising Edge<br>of Clock RD Low               |      | 85    |      | 105   | ns   |

| $^{	extsf{t}}DL\phi_{	extsf{RD}}$     | RD Delay from Falling Edge of Clock, RD High               |      | 95    |      | 115   | ns   |

| $^{	extsf{t}}DH\phi_{	extsf{RD}}$     | RD Delay from Rising Edge<br>of Clock, RD High             |      | 85    |      | 105   | ns   |

| $^{	extsf{t}}DH\phi_{	extsf{RD}}$     | RD Delay from Falling Edge<br>of Clock, RD High            |      | 85    |      | 105   | ns   |

| $^{	extsf{t}}$ DL $\phi_{	extsf{WR}}$ | WR Delay from Rising Edge of<br>Clock, WR Low              |      | 65    |      | 85    | ns   |

| $^{	extsf{t}}$ DL $\phi_{	extsf{WR}}$ | WR Delay from Falling Edge of<br>Clock, WR Low             |      | 80    |      | 100   | ns   |

| $^{	extsf{t}}DH\phi_{WR}$             | WR Delay from Falling Edge of<br>Clock, WR High            |      | 80    |      | 100   | ns   |

| $^{t}DL_{M1}$                         | M1 Delay from Rising Edge of Clock, M1 Low                 |      | 100   |      | 120   | ns   |

| <sup>t</sup> DH <sub>M1</sub>         | M1 Delay from Rising Edge of Clock, M1 High                |      | 100   |      | 120   | ns   |

| $^{t}DL_{RF}$                         | RFSH Delay from Rising Edge of Clock, RFSH Low             |      | 130   |      | 150   | ns   |

| <sup>t</sup> DH <sub>RF</sub>         | RFSH Delay from Rising Edge of Clock, RFSH High            |      | 120   | ¢    | 140   | ns   |

| ${}^{t}S_{WT}$                        | WAIT Setup Time from Falling<br>Edge of Clock              | 70   |       | 100  |       | ns   |

| $^{t}D_{HT}$                          | HALT Delay Time from Falling<br>Edge of Clock              |      | 300   | 0    | 320   | ns   |

| ${}^{t}S_{IT}$                        | INT Setup Time to Rising Edge of Clock                     | 80   |       | 110  |       | ns   |

|                                       |                                                            |      |       |      |       |      |

#### Z80A TIMING CHARACTERISTICS (cont.)

| <sup>t</sup> S <sub>BQ</sub>  | BUSRQ Setup Time to Rising<br>Edge of Clock        | 50   | 70*e  |     | ns   |

|-------------------------------|----------------------------------------------------|------|-------|-----|------|

| $^{t}DL_{BA}$                 | BUSAK Delay from Rising Edge of Clock, BUSAK Low   | . 10 | 00    | 130 | , ns |

| <sup>t</sup> DH <sub>ba</sub> | BUSAK Delay from Falling Edge of Clock, BUSAK High | 10   | 00    | 130 | ns   |

| <sup>t</sup> S <sub>RS</sub>  | RESET Setup Time to Rising<br>Edge of Clock        | 60   | 80*e  |     | ns   |

| <sup>t</sup> F <sub>c</sub>   | Delay to/from Float (MREQ,<br>IORQ, RD, and WR)    | 8    | 30    | 150 | ns   |

| <sup>t</sup> mr               | M1 Stable Prior to IORQ<br>(Interrupt Ack.)        | [2]  | [2]*d |     | ns   |

$\begin{array}{l} \text{[1] } t(c) = t(w(\phi H)) + t(w(\phi L)) + t(r) + r(f) \\ \text{[2] } t(mr) = 2^* \, t(c) + t(w(\phi H)) + t(f) - 65 \end{array}$

Notes \*a. Although static by design, testing guarantees t(w(%H)) of 200  $\mu$ s max.

<sup>\*</sup>b. Clock delay from prototype to emulator CPU is 15 ns maximum.

<sup>\*</sup>c. delay measured from BUSAK aserted at CPU.

$<sup>^{\</sup>star}$ d. IORQ can be delayed a maximum of 153 ns during INTA cycles while the Debug TRACE MODE is active.

<sup>\*</sup>e. timing reference to CPU clock — to reference to prototype, subtract propagation delay through buffers

<sup>\*</sup>f. Data will go to an indeterminate state, but will not tri-state unless BUSREQ is asserted. Timing Assumptions:

<sup>\*</sup> CPU timing reference: Mostek Microcomputer Z80 Data Book; Mostek Corporation, (1978).

## 6800/6802/6808 Emulator Processor and **Prototype Control Probe**

6800, 6802 and 6808 are registered trademarks of Motorola Corporation. Tektronix, Inc. does not guarantee that other vendors' versions will be compatible with Tektronix 8550 MDL

#### 6800/6802 / 6808 Emulator Support Package Characteristics

#### PHYSICAL CHARACTERISTICS

Length: 6 feet of cable from the Emulator Processor to the interface assembly. 1 foot of cable from the interface assembly to the 40-pin plug.

#### Cable configuration

6 foot: 240 conductor ribbon cables with chassis groundplane and signal paths.

1 foot: 2 twisted pair conductor cables made up of signal ground pairs.

#### TIMING CHARACTERISTICS Representative 6800 Emulator — 6802 Microprocessor **Timing Differences**

|                  |                                          | Proc | essor | Emu  | lator-a |         |

|------------------|------------------------------------------|------|-------|------|---------|---------|

| Symbol           | Parameter                                | Min. | Max.  | Min. | Max.    | Unit    |

| tcyc             | Cycle Time                               | 1    | 10    | 1    | 10      | $\mu$ s |

| <sup>t</sup> AD  | Address Delay                            |      | 270   |      | b       | ns      |

| <sup>t</sup> acc | Peripheral Read Access Time              |      | 530   |      | 464     | ns      |

| <sup>t</sup> DSR | Data Setup Time (Read)                   | 100  |       | 182  |         | ns      |

| tΗ               | Input Data Hold Time                     | 10   |       | 26   |         | ns      |

| <sup>t</sup> H   | Output Data Hold Time                    | 30   |       | -25  |         | ns      |

| <sup>t</sup> AH  | Address Hold Time<br>(Address, R/W, VMA) | 20   |       | С    |         | ns      |

| <sup>t</sup> DDW | Data Delay Time (Write)                  |      | 225   |      | d       | ns      |

| <sup>t</sup> PCS | Processor Control Setup Time             | 200  |       | е    |         | ns      |

| <sup>t</sup> PCr | Processor Control Rise and               |      | 100   |      |         | ns      |

| <sup>t</sup> PCf | Fall Time                                |      |       |      |         |         |

<sup>\*</sup>All emulator delays are given with reference to the E signal as presented to the user. The delay from the user clock to the E signal is 93 ns maximum and 19 ns minimum.

$^{\circ}$ Address = -5 ns minimum R/W = 0 ns minimum

VMA = -6 ns minimum

eNMI = 279 ns minimum IRQ = 284 ns minimum RESET = 284 ns minimum

Timing Assumptions. CPU timing reference. The Complete Microcomputer Data Library; published by Motorola Corporation, 1979.

#### Representative 6800 Emulator — 6800 Microprocessor Timing Differences

|                                      |                                                   | Processor      |      | Emu            | lator-a          |                |

|--------------------------------------|---------------------------------------------------|----------------|------|----------------|------------------|----------------|

| Symbol                               | Parameter                                         | Min.           | Max. | Min.d          | Max.d            | Unit           |

| tcyc                                 | Cycle Time                                        | 1              | 10   | 1              | 10               | μs             |

| $^{PW}\phiH$                         | Clock Pulse Width                                 | 400            | 9500 | 400            | 9500             | ns             |

| <sup>t</sup> AD                      | Address Delay                                     |                | 270  |                | е                | ns             |

| <sup>t</sup> acc                     | Peripheral Read Access Time                       |                | 530  |                | 425              | ns             |

| <sup>t</sup> DSR                     | Data Setup Time (Read)                            | 100            |      | 140            |                  | ns             |

| <sup>t</sup> HD                      | Address Hold Time<br>(address)<br>(R/W)<br>(VMA)  | 30<br>30<br>30 |      | 40<br>45<br>40 |                  | ns<br>ns<br>ns |

| <sup>t</sup> EH                      | Enable High Time for<br>DBE Input                 | 450            |      | _              |                  | ns             |

| <sup>t</sup> DDW                     | Data Delay Time (WRITE)                           |                | 225  |                | 482 <sup>f</sup> | ns             |

| <sup>t</sup> PCS                     | Processor Control Setup Time                      | 200            |      | b              |                  | ns             |

| <sup>t</sup> PCr<br><sup>t</sup> PCf | Processor Control Rise and Fall Time              |                | 100  |                |                  | ns             |

| ⁺BA                                  | Bus Available Delay                               |                | 250  |                | 305              | ns             |

| tTSD                                 | Three-State Delay                                 |                | 270  | · o            | С                | ns             |

| <sup>t</sup> DBE                     | Data Bus Enable Down Time During $\phi$ 1 Up Time | 150            |      |                |                  | ns             |

| †DBEr                                | Data Bus Enable Rise and                          |                | 25   |                |                  | ns             |

| <sup>t</sup> DBEf                    | Fall Time                                         |                |      |                |                  |                |

<sup>&</sup>lt;sup>b</sup>Address = 328 ns maximum R/W = 354 ns maximum

VMA = 321 ns maximum

<sup>«</sup>Valid data on a write is based on the failing edge of E rather than on the rising edge. Data is valid from the emulator 500 ns (maximum) after the falling edge of E

## 6809 Emulator Processor and 6809 Prototype Control Probe

6809 is a registered trademark of Motorola Corporation. Tektronix, Inc. does not guarantee that other vendors' versions will be compatible with Tektronix 8550 MDL or 8540

#### 6809 Emulator Support Package Characteristics

#### PHYSICAL CHARACTERISTICS

Length: 6 feet of cable from the Emulator Processor to the interface assembly. 1 foot of cable from the interface assembly to the 40-pin plug.

#### Cable configuration

6 foot: Two 40-conductor ribbon cables with chassis ground plane and signal paths.

1 foot: Two 22-conductor teflon cables with alternating grounds.

#### Termination

6 foot: The interface assembly contains receivers for data, address, and control from the 6809 emulator processor module.

1 foot: The probe assembly contains an oscillator circuit to drive and buffer the 6809 clock input pins. Input lines are not terminated. All output or bidirectional lines are series terminated with 100 ohms.

## TIMING CHARACTERISTICS Representative 6809 Microprocessor — 6809 Emulator (Combined with 6809 Prototype Control Probe) Timing Differences

|                                  |                               | Proc | essor | Emu  | ılator |      |

|----------------------------------|-------------------------------|------|-------|------|--------|------|

| Symbol                           | Parameter                     | Min. | Max.  | Min. | Max.   | Unit |

| <sup>t</sup> CYC                 | Cycle time                    | 0.5  | 10    | 0.5  | 10     | μs   |

| <sup>t</sup> UT                  | Total up time                 | 480  |       | 480  |        | ns   |

| <sup>t</sup> ACC                 | Peripheral read access time   | 320  |       | 278  |        | ns   |

| <sup>t</sup> DSR                 | Data setup time (read)        | 40   |       | 80   |        | ns   |

| <sup>t</sup> DHR                 | Input data hold time          | 10   |       | -6   |        | ns   |

| $^{t}DHW$                        | Output data hold time         | 30   |       | 18   |        | ns   |

| <sup>t</sup> AH                  | Address hold time             | 20   |       | 8    |        | ns   |

| <sup>t</sup> AD                  | Address delay time            |      | 110   |      | 122    | ns   |

| <sup>t</sup> DDW                 | Data delay time (write)       |      | 145   |      | 157    | ns   |

| <sup>t</sup> AVS                 | E(low) to Q(high) time        |      | 125   |      | 125    | ns   |

| <sup>t</sup> AQ                  | Address valid to Q(high)      |      | 15    | 3    |        | ns   |

| <sup>t</sup> PWEL                | Processor clock low           | 210  |       | 210  |        | ns   |

| <sup>t</sup> PWEH                | Processor clock high          | 220  |       | 220  |        | ns   |

| <sup>t</sup> PCSM                | MRDY (H) setup time           | 125  |       | 169  |        | ns   |

| <sup>t</sup> PCS                 | Interrupts setup timeª        | 110  |       | 154  |        | ns   |

| †PCSH                            | HALT (L) setup time           | 110  |       | 154  |        | ns   |

| <sup>t</sup> PCSR                | RESET (L) setup time          | 110  |       | 180  |        | ns   |

| †PCSD                            | DMA/BREQ (L) setup time       | 125  |       | 169  |        | ns   |

| <sup>t</sup> RC                  | Crystal oscillator start time | 100  |       | b    |        | ns   |

| tEr, tEf                         | E rise and fall time          | 5    | 20    | С    | С      | ns   |

| <sup>t</sup> PCr,                | Processor control rise and    |      | 100   |      | d      | ns   |

| <sup>t</sup> pcf                 | fall time                     |      |       |      |        |      |

| <sup>t</sup> QR, <sup>t</sup> Qf | Q rise and fall time          | 5    | 20    | C    | С      | ns   |

| *PWQH                            | Q clock high time             | 220  |       | 220  |        | ns   |

#### Notes:

aNMI (L) setup time to E(rising) is 56 ns

bOscillator must be operating before the emulator can run

<sup>°</sup>Outputs are driven by 74LS244's, series terminated with 100-ohm resistors

dRise and fall times are TTL compatible

## 3870/72/74/76/F8 Emulator Processor and Prototype Control Probes 3870, 3872, 3874 and 3876 are registered trademarks of Mostek. F8 is a registered trademark

#### 3870/72/74/76/F8 Emulator Support Package Characteristics

#### PHYSICAL CHARACTERISTICS

Length: 6-foot cable from the Emulator Processor to the interface assembly. 1-foot cable from the interface assembly to the 40-pin plug.

#### Configuration

6-foot cable: Two 40-conductor ribbon cables with chassis groundplane and signal paths.

1.5-foot cable: Two twisted pair of 40-conductor cables.

Termination, 6-foot cable: The interface assembly contains receivers for data, address and control from the 3870, 3872, 3874, 3876, and F8 Emulator Processor module. (The 1-foot cable is not terminated.)

#### TIMING CHARACTERISTICS Representative 3870, 3872, F8 Emulator 3870, 3872 Microcomputer **Timina Differences**

|                    |                                           |        | Proc              | essor       | Εmι                       | ulator           |       |

|--------------------|-------------------------------------------|--------|-------------------|-------------|---------------------------|------------------|-------|

| Symbol             | Parameter                                 |        | Min.              | Max.        | Min.                      | Max.             | Units |

|                    |                                           | 0/3872 |                   |             |                           |                  |       |

| to(INT)            | Time Base Period, internal oscillator     |        | 250               | 1000        | 250ª                      | 1000             | ns    |

| to(EX)             | Time Base Period, all external modes      |        | 250               | 1000        | 250                       | 1000             | ns    |

| tEX(H)             | External Clock Pulse Width<br>High        |        | 90                | 700         | 40ª                       |                  | ns    |