UNIVERSITY OF MANCHESTER DEPARTMENT OF COMPUTER SCIENCE

MU5 BASIC PROGRAMMING MANUAL

This document is an edited recreation of a copy of the MU5 Basic Programming Manual dating from 1975, parts of which date back to 1972 (at least). The original manuscript appears to be lost and the editor's copy, like those held in the special collections of the University of Manchester library, is in rather poor condition. The original was produced on a manual typewriter, and whereas this version was created using Latex and xfig, it has been designed to appear similar to the original. Some typographical and grammatical errors in the original have been corrected and some of the layout has been altered to improve self-consistency. A copy of a later (1978) edition of the Manual also exists, in a different typeface. The 1978 edition contains some corrections and updates but also includes some new errors. This reconstruction draws on both versions in an attempt to produce a more accurate description of MU5 as seen by its programmers. Any remaining errors are the fault of the editor.

Editor's notes and other additional material are shown in blue. Publication of this document is by kind permission of the University of Manchester School of Computer Science.

Thanks are due to Rob Jarratt for his careful proof reading but mainly for having inspired this reconstruction through his work on creating a software emulator for  $MU5^{1}$ .

> Roland Ibbett June 2017

Roland Ibbett is an Emeritus Professor of Computer Science, University of Edinburgh and formerly Reader in Computer Science at the University of Manchester. In 1979 he was co-author, with the late Professor Derrick Morris, of the "The MU5 Computer System", published by The Macmillan Press.

<sup>&</sup>lt;sup>1</sup>https://robs-old-computers.com/projects/mu5/

# **CONTENTS**

| CHAPTER 1    | Introduction                                  |

|--------------|-----------------------------------------------|

| CHAPTER 2    | Operand Accessing                             |

| CHAPTER 3    | B-Arithmetic                                  |

| CHAPTER 4    | Accumulator Arithmetic                        |

| CHAPTER 5    | Structure Accessing and Store to Store Orders |

| CHAPTER 6    | Organisational Orders                         |

| CHAPTER 7    | The Interrupt System                          |

| CHAPTER 8    | The V Store                                   |

| CHAPTER 9    | The Vx Store                                  |

| CHAPTER 10   | The Basic Programming Language - XPL          |

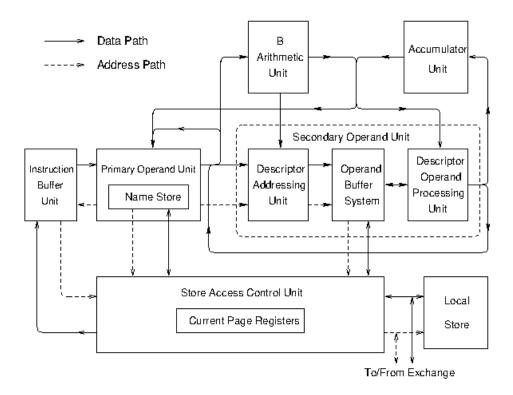

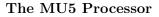

| APPENDIX I   | MU5 Hardware Block Diagrams                   |

| APPENDIX II  | The Engineers' Version of the Order Code      |

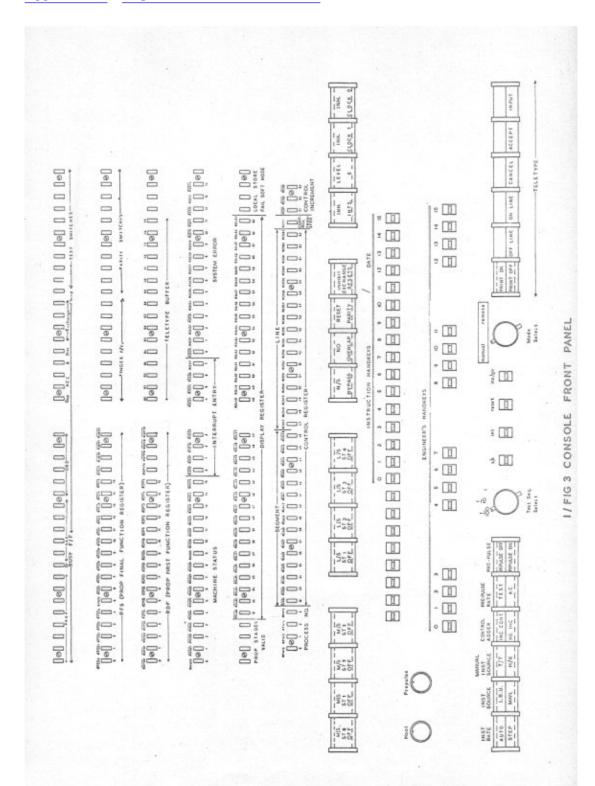

| APPENDIX III | Engineers' Console Front Panel                |

|              |                                               |

# Chapter 1

# 1.1 <u>Introduction</u>

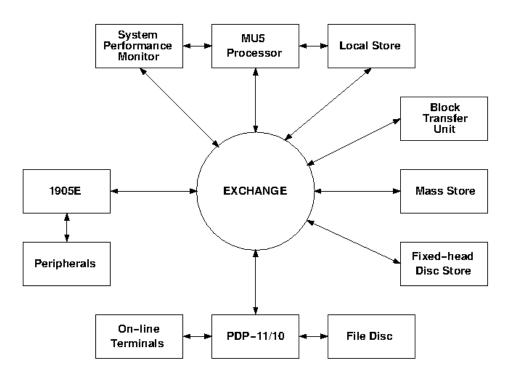

The organisation of the machine  $^2$  is reflected in its order code which is essentially of the form:-

F N

where F defines the function and N the operand. There are four classes of orders:-

Computational orders B-orders Structure accessing and store-to-store orders Organisational orders

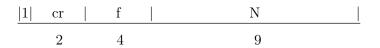

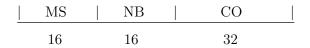

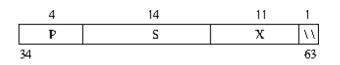

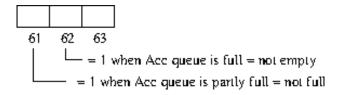

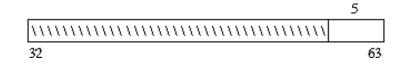

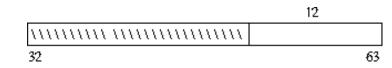

In the computational orders, which are distinguished by a 1 in digit 0, the instruction is divided thus:-

The cr bits define one of four types of arithmetic:-

signed fixed-point unsigned fixed-point decimal floating point

In MU5 the signed fixed-point operations use a 32-bit register X, while the unsigned fixed-point, floating-point and decimal operations share a common 64-bit register A. However, the structure of the instruction code allows for four separate registers. The f bits define the operation to be performed and N defines the operand. Computational orders are of the single address type (e.g. A = operand, A + operand).

<sup>&</sup>lt;sup>2</sup>see: APPENDIX I. For more information go to

http://www.cs.manchester.ac.uk/about-us/history/mu5/

http://ethw.org/The\_University\_of\_Manchester\_MU5\_Computer\_System

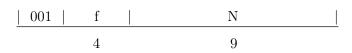

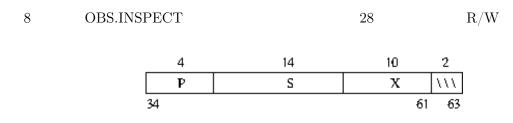

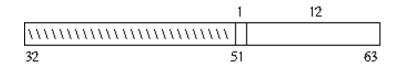

The B-orders operate on the modifier register B. They have the form:-

The functions provided correspond to those which operate on X but the division orders are not implemented in MU5.

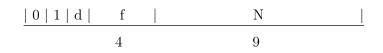

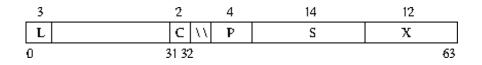

In the structure addressing and store-to-store orders, it is convenient to think of the instruction being divided in the same way:-

However, the two values of d give a total of 32 possible functions; some of these are used for manipulating registers in the secondary operand unit, which is closely associated with all store-to-store operations.

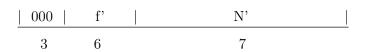

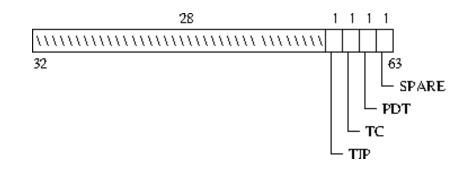

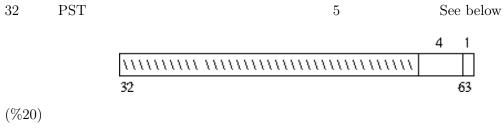

In the organisational orders, the instruction is divided thus:-

The cr bits are zero and the 6 f' bits define both the organisational register and the operation to be performed. The organisational orders are mainly concerned with control transfers and the manipulation of organisational registers.

An operand is specified by N (or N') and is independent of the function. An operand may be a literal, a 'named operand' (more simply, a 'name'), or a secondary operand; various internal registers (X, B, etc.) may also be addressed as operands.

# 1.2 Summary of the Order Code

This section summarises the overall pattern of the order code<sup>3</sup>. The detail is given in later sections as shown below. Some functions in MU5 differ from the general form overleaf, which should be taken only as a statement of the general characteristics.

| References                                    | Chapter     |

|-----------------------------------------------|-------------|

| Computational Orders                          | 3, 4        |

| B register                                    | 3           |

| Accumulators                                  | 4           |

| Structure Accessing and Store to Store Orders | 5           |

| Organisational Orders                         | 6           |

|                                               |             |

| Operand Accessing                             | 2           |

| Literals                                      | 2.3         |

| Variables                                     | 2.4         |

| Internal Register Operands                    | 2.5         |

| Stacked Operands                              | 2.6         |

| Privileged Operands                           | 2.7         |

| Secondary Operands                            | 2.8         |

| Descriptor Types 0 - 3                        | 2.10 - 2.13 |

|                                               |             |

| Internal Registers                            |             |

| B, BOD                                        | 3           |

| AEX                                           | 4           |

| MS                                            | 6.2         |

| NB, XNB, SF, (SN)                             | 2.2         |

| CO                                            | 6.3         |

| D                                             | 2.2         |

| XD, DOD, DT, XDT                              | 5           |

| BN                                            | 6.5         |

| Z                                             | 2.5         |

|                                               |             |

<sup>3</sup>Appendix II shows the version of the order code used by the design engineers.

#### Computational and Store-to-Store Orders

| f  | STS   | S/D   | В      | XS        | AU          | ADC      | AFL       |

|----|-------|-------|--------|-----------|-------------|----------|-----------|

| 0  | XDO = | DO =  | =      | X =       | AOD =       | DUMMY    | = (32)    |

| 1  | XD =  | D =   | = (-1) | DUMMY     | DUMMY       | AEX =    | = (64)    |

| 2  | STACK | D *=  | *=     | X *=      | AOD *=      | AEX *=   | *=        |

| 3  | XD => | D =>  | ⇒      | X =>      | AOD =>      | AEX =>   | ⇒         |

| 4  | XDB = | DB =  | +      | +         | A +         | DUMMY    | +         |

| 5  | ХСНК  | MDR   | —      | —         | Α—          | DUMMY    |           |

| 6  | SMOD  | MOD   | *      | *         | *           | DUMMY    | *         |

| 7  | XMOD  | RMOD  | 1      | 1         | DUMMY       | DUMMY    | 1         |

| 8  | SLGC  | BLGC  | ≢      | ₹         | A ≇         | DUMMY    | A≢        |

| 9  | SMVB  | BMVB  | v      | v         | ΑV          | DUMMY    | ΑV        |

| 10 | DUMMY | BMVE  | t      | † ARITH   | A† LOG      | A †      | A† CTRC   |

| 11 | SMVF  | SMVF  | å      | å         | A &         | DUMMY    | A &       |

| 12 | TALU  | DUMMY | Θ      | Θ         | $A \ominus$ | AOD COMP | Θ         |

| 13 | DUMMY | BSCN  | COMP   | COMP      | A COMP      | COMP     | COMP      |

| 14 | SCMP  | BCMP  | CINC   | AEX=CONVX | DUMMY       | UNPACK   | AEX=CONVA |

| 15 | SUB1  | SUB2  | Ø      | Ø         | DUMMY       | DUMMY    | Ø         |

| 3  | 4 | 3 | 6 |

|----|---|---|---|

| cr | f | k | n |

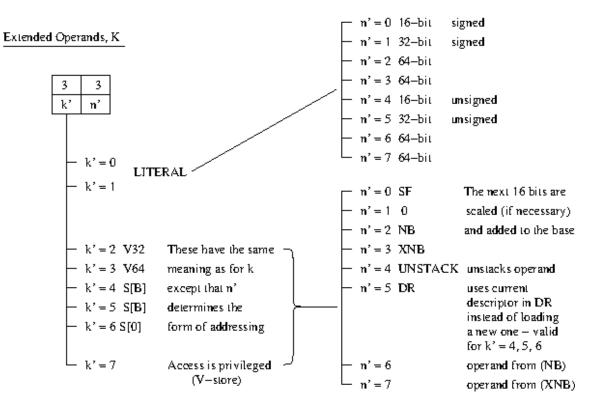

| k1 = 0 or $k = 0 - LITERAL$ | n is 6-bit signed literal                         |

|-----------------------------|---------------------------------------------------|

| k = 1 - JR                  | n defines internal register, P.T.O. $\rightarrow$ |

| k = 2 - V32                 | Operand is accessed directly at                   |

| k = 3 - V64                 | (NB) + unsigned n; n is scaled for V32            |

| k = 4 - S[B]                | Operand is accessed via a                         |

| k = 5 - S[B]                | descriptor at (NB) + n, using                     |

| k = 6 - S[0]                | B or O as an index                                |

| k1 = 1 or k = 7             | K (Extended Operand) P.T.O>                       |

|                             |                                                   |

| 3 | 6 | 1  | 6 |

|---|---|----|---|

| 0 | ſ | k1 | n |

#### Organisational Orders

|   | 0  | ->                           | EXIT          | DUMMY                                            | DUMMY     |

|---|----|------------------------------|---------------|--------------------------------------------------|-----------|

| [ | 4  | JUMP                         | RETURN        | DUMMY                                            | DUMMY     |

|   | 8  | XC0                          | XC1           | XC2                                              | XC3       |

| [ | 12 | XC4                          | XC5           | XC6                                              | STACKLINK |

|   | 16 | MS =                         | DL =          | SPM                                              | SET LINK  |

| [ | 20 | XNB =                        | SN =          | XNB +                                            | XNB =>    |

|   | 24 | SF =                         | SF +          | SF = NB +                                        | SF =>     |

| [ | 28 | NB =                         | NB = SF +     | NB +                                             | NB =>     |

|   | 32 | = 0                          | ≠ 0           | 20                                               | < 0       |

|   | 36 | $\leq 0$                     | > 0           | OVERFLOW                                         | Bn        |

| l | 40 | = 0                          | ≠0            | 0_<                                              | < 0       |

| ι | 44 | $\leq 0$                     | > 0           | OVERFLOW                                         | Bn        |

|   | 48 | 0                            | Bn & X        | Bn & X                                           | х         |

|   | 52 | Bn & $\overline{\mathbf{X}}$ | Bn            | Bn ≠ X                                           | Bn V X    |

|   | 56 | Bn & X                       | $Bn \equiv X$ | Bn                                               | Bn V X    |

|   | 60 | x                            | Bn V X        | $\overline{\operatorname{Bn}} \vee \overline{X}$ | 1         |

Denote test result by T (= 0 for NO, = 1 for YES) The operand specifies the way in which BN is set

| BN = 0   | BN & T   | BN /& T    | BN = T   |

|----------|----------|------------|----------|

| BN &/ T  | DUMMY    | BN≢ T      | BN V T   |

| BN /&/ T | BN≡ T    | BN /       | BN / V T |

| BN =/ T  | BN V / T | BN / V / T | BN = 1   |

#### Internal Register Operands

. .

### The n bits define the internal register to be used.

|   | ← 16→← 16→← 16→← 16→ |    |    |         |  |  |  |

|---|----------------------|----|----|---------|--|--|--|

| 0 | MS                   | NB | C  | 0       |  |  |  |

| 1 |                      |    | ١X | 4B<br>B |  |  |  |

| 2 |                      |    | SN | NB      |  |  |  |

| 3 |                      |    | SN | SF      |  |  |  |

| 4 |                      |    | B  | N       |  |  |  |

| 5 |                      |    |    |         |  |  |  |

| 6 |                      |    |    |         |  |  |  |

| 7 |                      |    |    |         |  |  |  |

| 16 | D |     |  |  |

|----|---|-----|--|--|

| 17 | x | XD  |  |  |

| 18 |   | DT  |  |  |

| 19 |   | XDT |  |  |

| 20 |   | DOD |  |  |

| 21 |   |     |  |  |

| 22 |   |     |  |  |

| 23 |   |     |  |  |

|    |     |     |    | <b>~</b> ─── 64 ─── <del>&gt;</del> |

|----|-----|-----|----|-------------------------------------|

| 32 |     | В   | 48 | AEX                                 |

| 33 |     | BOD | 49 |                                     |

| 34 |     | Z   | 50 |                                     |

| 35 |     |     | 51 |                                     |

| 36 | BOD | В   | 52 |                                     |

| 37 |     |     | 53 |                                     |

| 38 |     |     | 54 |                                     |

| 39 |     |     | 55 |                                     |

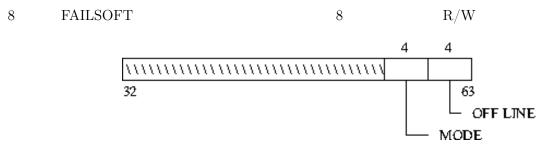

8

# **Descriptor Formats**

Type 0 - General Vector

Type 1 - General String

| τ | SIZE |               | BOUND/LENGTH    | ORIGIN (IN BYTES) |

|---|------|---------------|-----------------|-------------------|

| 2 | 3    | 3             | 24              | 32                |

|   |      | Size – 8 bits | Spare<br>: only |                   |

Type 2 - Address Vector

Format identical with Type 0

Type 3 - Miscellaneous Sub-types

### 2.1 <u>Introduction</u>

The operands for all orders are transferred from source to destination via a highway which is 64 bits wide. For a fetch order, the operand part of the order defines how the highway is loaded and the function part defines the destination (and the operation to be performed at the destination). For a store order, the function part defines how the highway is loaded and the operand part defines the destination.

The function part of an order is described in Chapters 3 - 6; this chapter describes the operand part. With a few exceptions, which will be mentioned when they arise, any function part may be combined with any operand part, so that the two parts may conveniently be described separately.

Operands may be of various sizes up to a maximum of 64 bits. If the operand is less than 64 bits long, then it is loaded on to (or taken from) the least significant end of the highway. On a fetch order, the remaining bits of the highway are set to zero (except for literal operands - see Section 2.3). On a store order, the remaining bits are truncated; for secondary operands only, the truncated bits are checked for zeros.

In addition to various sizes of operand, there are various kinds of operand:-

- literals A literal is specified directly as part of the order, e.g. 'X + 1' would add 1 to the (original) fixed-point accumulator.

- variables A variable is the value in a store location whose address is specified by a base register and the displacement from the base.

- internal the value in most of the internal registers (B, NB, etc.) can be specified registers as an operand, e.g. 'X = NB' loads the value in NB into the fixed-point accumulator.

- stacked Operands can be sent to and from a hardware implemented stack operands working on a last-in first-out basis, e.g. 'A\* STACK' multiplies the floating-point accumulator by the top operand on the stack and removes the operand from the stack.

privileged These can only be accessed in Executive mode; they are described in operands Chapter 8.

secondary A special mechanism is provided for accessing secondary operands, i.e. operands contained in some data structure. The operand part of the order specifies a data descriptor and a modifier. The data descriptor is a 64-bit animal specified as a variable or stacked operand and is combined with the modifier in D to produce the size and address of the secondary operand. For example, consider the orders 'B = 3, D = FRED, A + D[B]' where FRED is a descriptor at address (NB = 5). The action would be to load 3 into the modifier register B, then send the descriptor at address NB + 5 to DR, modify by the value in B (i.e. 3) to give the size and address of the secondary operand and finally add this operand to the floating-point accumulator.

# 2.2 Internal Registers Relevant to Operand Accessing

Section 1.2 contains a complete list of the internal registers with references to their descriptions. In this section, only those registers relevant to operand accessing are described.

#### The Name Segment Number SN

The name segment number SN is 16 bits long. The two most significant bits are permanently zero, and the remaining 14 bits define the segment currently being used for names in a program. Any segment  $(0, 1, 2, ... 2\uparrow 14 - 1)$  may be used for this purpose; it is conventional to use segment 0 whenever possible. The value contained in SN may only be altered by calling an executive procedure.

#### The Name Base Register NB

The name base register NB is 16 bits long. The most significant 15 bits hold the address of any 64-bit word in the name segment SN; the least significant bit is permanently zero. When NB is the base register for an operand access, then it is added to the displacement (the name) to give the address of the operand within the segment SN. If the addition overflows out of the segment, there will be an interrupt.

NB is designed to be the base register for local names in a procedure; its value will usually only be changed on entry and exit.

Orders which alter NB are described in Sections 6.2 and 6.3

$$\frac{| 64-\text{bit word address } |0|}{15}$$

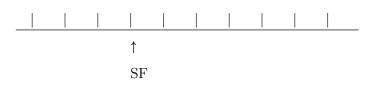

#### The Stack Front Register SF

The format of the stack front register SF is identical with that of NB. SF can be used as a base register in the same way as NB. However, the space in <u>front</u> of SF (i.e. at addresses > SF) must not be accessed in this way; interrupt routines use the area in front of SF as working space, so these locations are liable to change at any time.

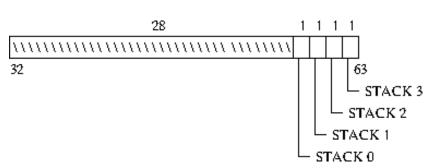

The stack is designed both to provide temporary working space within a procedure (e.g. for evaluating arithmetic expressions) and also the space required for procedure calls (see Section 6.4). Certain orders, e.g. STACK B, cause an operand to be stacked -SF is advanced by 2 (32-bit) words and the operand is stored at the 64-bit word specified by the new value of SF. These operands may be unstacked by specifying the STACK as the operand part of an order, e.g. 'A = STACK' - the 64-bit word at SF is loaded on to the highway and SF is decreased by 2. Note that all unstacked operands are assumed to be 64 bits long.

Orders that alter SF are described in Sections 3.2, 4.4, 6.2 and 6.3.

#### The Extra Name Base XNB

The extra name base register, XNB, is 32 bits long. Bits 2-30 hold the address of a 64-bit word anywhere in the virtual memory; bits 0, 1 and 31 are permanently zero. XNB is used as a base register in the same way as NB and SF, except that the operand is in the segment defined by the top half of XNB (instead of SN). Note that the addition of the name must not overflow out of this segment, or there will be an interrupt. XNB is designed to be a base register for non-local names used in a procedure, and will often change its value in a procedure. In many programs, the top half of XNB will be zero (like SN).

Orders that alter XNB are described in Section 6.2.

| 00 | segment | 64-bit word address | 0 |

|----|---------|---------------------|---|

| 2  | 14      | 15                  | 1 |

#### The Data Descriptor Register D

The data descriptor register, D, is 64 bits long and is used to hold the descriptors required for accessing data structures. The operand part of an order which accesses a data structure specifies a descriptor and a modifier. The descriptor is loaded into D and then combined with the modifier to define the size and address of the particular structure element required.

Details of the descriptor types and the mechanisms for accessing secondary operands are given in Sections 2.8 and 2.10 - 2.13.

D also plays a major part in the operation of the store-to-store orders. D manipulation orders are described, with the store-to-store orders, in Chapter 5.

# 2.3 Literal Operands

A literal operand appears directly as part of the order; if a literal is specified as the operand part of a store order, there will be an interrupt.

There are several alternatives:-

. . .

| (a) | 6-bit  | signed   |

|-----|--------|----------|

| (b) | 16-bit | unsigned |

| (c) | 16-bit | signed   |

| (d) | 32-bit | unsigned |

| (e) | 32-bit | signed   |

| (f) | 64-bit |          |

|     |        |          |

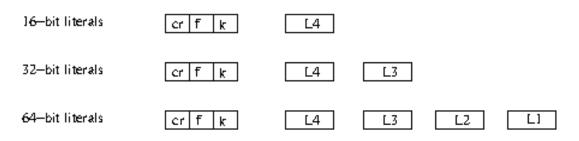

The literals are copied to the least significant end of the highway. The remaining bits of the highway are set to zeros for unsigned literals and to copies of the sign bit for signed literals. The precise format of orders containing literals is unexpected. Let L1 denote 16 bits loaded on to highway bits 0-15. Let L2 denote 16 bits loaded on to highway bits 16-31. Let L3 denote 16 bits loaded on to highway bits 32-47. Let L4 denote 16 bits loaded on to highway bits 48-63. Then the orders appear as follows:-

# 2.4 Variable Operands

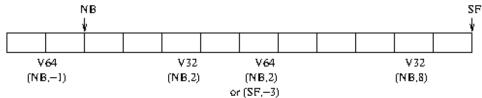

There are two kinds of variable, V32 and V64, of sizes 32 bits and 64 bits respectively. The operand part of the order specifies the kind of order and also defines its name and base. NB, XNB, SF or O may be used as its base (it is convenient to consider O to be a base register which always contains 0). The name is the distance of the variable from the base counting in units equal to the variable size. Some examples are shown below - the diagram represents a section of the virtual store marked out in 32-bit words:-

V64 name are in the range $-2\uparrow15 \leq name < 2\uparrow15$ V32 names are in the range $0 \leq name < 2\uparrow16$

To calculate the address of the operand, the name is scaled (if necessary) and added to the base. If this addition overflows out of the base segment, there will be an interrupt. If NB, SF or O is used as the base, then the variable is taken from the name segment (SN); if XNB is used as the base, then the most significant half of XNB defines the segment. In short instructions the 6-bit displacement, n, is always unsigned, i.e.  $0 \le n < 64$ .

<u>N.B.</u> If XNB points to a segment which is not the name segment, operands relative to XNB may not be used with the following functions, XNB =>, NB =>, SF =>, SETLINK.

Note that the organisational commands, input/output and CTL use words in the name segment. Thus when running under the operating system, 32-bit words:-

0 - 15 should not be used when writing in XPL

0 - 96 should not be used when using the Autocode machine.

### 2.5 Internal Register Operands

Any internal register may be specified as the operand for a fetch order; a store order may write to most internal registers, except those within the primary operand unit, i.e. MS, NB, CO, XNB, SN, SF, BN. A table listing all the registers or combinations of registers that can be accessed in this way is given in Section 1.2; note that only complete lines may be accessed, for example, SF cannot be read by itself but only in combination with SN.

Internal register operands may only be used with computational and store-tostore orders, not with organisational orders.

The Internal Register Z is a dummy operand which is written to as a means of suppressing overlap until the order is complete.

### 2.6 Stacked Operands

When the operand part of the order specifies STACK, the 64-bit word at SF is loaded on to the highway and then SF is decreased by 2. Note that all operands coming from STACK are 64 bits long; this does not mean that only 64-bit operands may be sent to the stack - shorter operands will be extended by zeros on the way.

[A store order specifying STACK will store the operand at SF and <u>decrease</u> SF by 2. This is not a sensible order but it is allowed.]

#### 2.7 Privileged Operands

Privileged operands are used by the Executive to hold system control information. They can only be accessed in Executive mode and are of no interest to the ordinary programmer. Access can be made in two ways. In the first case, a base register and a name are specified as for a variable operand; the size is always 64 bits and the address is calculated exactly as for a V64 variable. However, access is made not to the virtual store of the program but to the local V-store (i.e. the address is interpreted as a local V-store address). In the second case, the operand part of the order is STACK; this action is exactly the same as for other stacked operands but SF is now interpreted as a 64-bit word address in the local V-store. (The local V-store is described in Chapter 8.)

### 2.8 Secondary Operands

For a secondary operand, the operand part of the order specifies a 64-bit descriptor and a modifier. Normally, the descriptor specifies the type and origin (i.e. the starting address) of the data structure containing the secondary operand and the modifier defines which particular operand is required. For example, if A is a descriptor specifying a vector of 32-bit elements, then the orders 'B = 25; X = A[B]' would load the 25th element (counting from zero) of A into the fixed-point accumulator.

Descriptors can define vectors or strings of elements of various sizes; miscellaneous special types are also provided. The different types of descriptor are defined in Sections 2.10 - 2.13.

A descriptor may be specified in the same way as a variable or stacked operand; it is always 64 bits long and is loaded into the D register. Alternatively, the operand part of the order may specify that the descriptor is already in D; this avoids unnecessary loading into D if the same descriptor is used for consecutive secondary operands.

The modifier used is normally B or O (i.e. no modifier). However there are special functions (see Chapter 5) which allow any operand to be used as a modifier and also cause a special type of modification. All modifiers are interpreted as signed 32-bit integers.

When access is made via certain types of descriptor (e.g. vectors) it is possible to check automatically that the modifier (if any) lies in the range  $0 \le \text{modifier} < \text{bound}$ . The bound is held in bits 8-31 of the descriptor.

<u>N.B.</u> A secondary operand may not be used in conjunction with the following functions: D =>, XD =>, XNB =>, NB =>, SF =>, SETLINK.

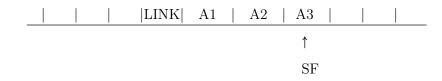

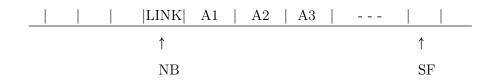

# 2.9 Length of the Orders

An order may be 16, 32, 48 or 80 bits long. It will be 16 bits long when:-

- (a) Operand is 6-bit literal or internal register

- (b) Operand is variable or secondary; base register is NB and 0 ≤ name ≤ 63;

function part is computational or store-to-store

- (c) Operand is variable, privileged or secondary from STACK

An order will be 48 bits long if the operand is a 32-bit literal and will be 80 bits long if the operand is a 64-bit literal. In all other cases an order will be 32 bits long.

# 2.10 Type 0 - Vector Descriptors

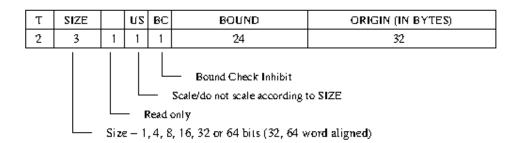

Type 0 descriptors are used for vectors of elements of size 1, 4, 8, 16, 32 or 64 bits. The descriptor defines the origin of the vector, the element size and an upper bound for the modifier (i.e. the number of elements in the vector). The format is :-

|                | T SIZE ROUSBC BOUND ORIGIN IN BYTES                                          |  |  |  |  |  |

|----------------|------------------------------------------------------------------------------|--|--|--|--|--|

|                | 2 3 1 1 1 24 32                                                              |  |  |  |  |  |

| $\mathrm{T}=0$ | Defines type 0.                                                              |  |  |  |  |  |

| SIZE           | Defines the element size as 1, 4, 8, 16, 32 or 64 bits. (Coded as follows:-  |  |  |  |  |  |

|                | 000 = 1  bit;  010 = 4  bits;  011 = 8  bits;  100 = 16  bits;               |  |  |  |  |  |

|                | 101 = 32 bits; $110 = 64$ bits.)                                             |  |  |  |  |  |

| RO             | If $RO = 1$ , descriptor is read only and any attempt to use it for writing  |  |  |  |  |  |

|                | will cause an interrupt.                                                     |  |  |  |  |  |

| US             | If $US = 0$ , then the modifier is scaled before being added to the origin   |  |  |  |  |  |

|                | - for 1-bit elements the modifier is shifted down 3 bits, for 4-bit elements |  |  |  |  |  |

|                | down 1 bit, for 8-bit elements none, for 16-bit elements up 1 bit, for       |  |  |  |  |  |

|                | 32-bit elements up two bits, for 64-bit elements up 3 bits.                  |  |  |  |  |  |

|                | If $US = 1$ , the modifier is not scaled.                                    |  |  |  |  |  |

| BC             | If $BC = 1$ , then there is no bound check.                                  |  |  |  |  |  |

| BOUND          | An upper bound for the modifier. If the bound check bit BCH in DOD           |  |  |  |  |  |

|                | (see Chapter 5) is set to 0 and $BC = 0$ , then the modifier (if any) must   |  |  |  |  |  |

|                | lie in the range $0 \leq$ modifier $<$ BOUND, otherwise there will be an     |  |  |  |  |  |

|                | interrupt (see Section 5.2).                                                 |  |  |  |  |  |

- ORIGIN The origin defines the base address of the vector; it is always a 32-bit byte address. For 16-bit vectors, the least significant bit of the modified address is ignored, so that all elements start at a 16-bit word boundary. For 32 and 64-bit vectors, the two least significant bits are ignored, so elements start on a 32-bit word boundary. Note that vectors of 1-bit and 4-bit elements must start on a byte boundary.

- Action: When an access is made, the modifier (if any) is scaled (according to SIZE and US) and added to the origin to give the address of the required element. Provided there is no bound check fail, the element is accessed. On a fetch order, it is loaded on to the highway (operands < 64 bits long are loaded at the least significant end and the remaining bits are zeroed). On a store order, the highway is stored at the element; there will be an interrupt of any non-zero bit is truncated (see Section 5.2).</p>

### 2.11 Type 1 - String Descriptors

Type 1 descriptors are used for 8-bit elements. The descriptor defines the origin and length of the string. The format is:-

| $ \mathbf{T} $ | SIZE |   |   |   | LENGTH | ORIGIN IN BYTES |  |

|----------------|------|---|---|---|--------|-----------------|--|

| 2              | 3    | 1 | 1 | 1 | 24     | 32              |  |

T = 1 Defines type 1.

SIZE Must define the element size as 8 bits (011), else an interrupt will occur.

LENGTH Defines the number of elements in the addressed string.

ORIGIN Defines a base address, as in type 0.

Action: The modifier (if any) is added to the origin to give the address of the start of the string. LENGTH defines the length of the string, i.e. the number of elements in the string. There is no bound checking.

The final operand is a string of 8-bit elements. In store-to-store orders the whole string will be used as the operand (see Chapter 5). In computational orders, the operand can be at most 64 bits long; if the string is less than 64 bits, then it is zero filled for fetch, truncated with zero-checking for store; if the string is longer than 64 bits, just the first 64 bits of the string are loaded on to or stored from the highway.

# 2.12 Type 2 - Descriptor Descriptors

Type 2 descriptors are identical with type 0 descriptors (except that T = 2 instead of 0). [It's not clear whether type 2 included the RO bit.]

| T  S | SIZE | $ \mathrm{RO} $ | $ \mathrm{US} $ | BC | BOUND | ORIGIN IN BYTES |  |

|------|------|-----------------|-----------------|----|-------|-----------------|--|

| 2    | 3    | 1               | 1               | 1  | 24    | 32              |  |

It is conventional to use type 2 descriptors to address vectors containing descriptors; type 0 is used for vectors containing data.

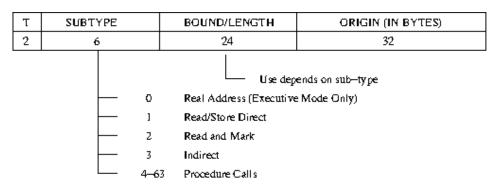

### 2.13 Type 3 - Miscellaneous Descriptors

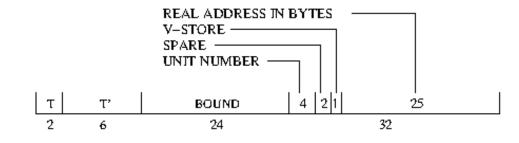

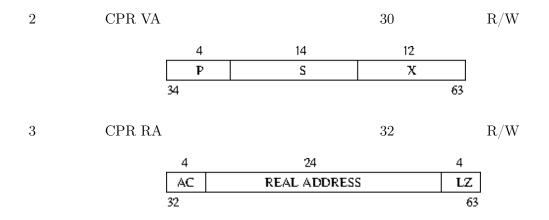

#### Type 3.0 Real Address

T, T' = 3, 0 define type 3.0

BOUND Upper bound for modifier as in type 0.

ORIGIN Contains the real store address (the physical address, not the virtual store address) of a 64-bit operand. The three least significant bits are ignored<sup>a</sup>.

Action: The operand is accessed in the same way as a type 0 64-bit element. The modifier is always scaled and bound checked if bit BCHI in DOD is set to 0. Type 3.0 descriptors may only be used in Executive mode.

#### Type 3.1 Read/Store Direct

| T | T | BOUND | ORIGIN IN BYTES |  |

|---|---|-------|-----------------|--|

| 2 | 6 | 24    | 32              |  |

T, T' = 3, 1 defines type 3.1

BOUND Upper bound for modifier as in type 0.

ORIGIN Defines a 64-bit word address; the three least significant bits are ignored.

<sup>&</sup>lt;sup>a</sup>The V-Store bit should really have been labelled Vx-Store. The V-Store and Vx-Store (Chapters 8 & 9) are (almost) completely separate and are separately addressed.

Action: Access is made in exactly the same way as for a type 0 64-bit element (assuming US = BC = 0, so that the modifier is scaled and bound-checked if bit BCHI in DOD is set to 0. Note that the word lies on a 64-bit word boundary.

The accessing mechanism for this descriptor bypasses all operand buffers and always accesses the real store corresponding to the defined virtual address. This type of access is needed in some executive procedures.

Type 3.2 Read and Mark

| T | T | BOUND | ORIGIN IN BYTES |

|---|---|-------|-----------------|

| 2 | 6 | 24    | 32              |

T, T' = 3, 2 define type 3.2

BOUND Upper bound for modifier as in type 0.

ORIGIN Defines a 64-bit word address;

the three least significant bits are ignored.

Action: Access is made in exactly the same way as for type 3.1 descriptors, bypassing the operand buffers. In addition, for a fetch order, the value of the 64-bit word in the store is finally set to zero.

### Type 3.3 Indirect

| T | Τ' | Х  | ORIGIN IN BYTES |

|---|----|----|-----------------|

| 2 | 6  | 24 | 32              |

T, T' = 3, 3 define type 3.3

X Unused

ORIGIN Defines a 32-bit word address; the three least significant bits are ignored.

Action: The 64-bit element at the origin address is loaded into D and then interpreted according to its type. The new descriptor may be indirect, in which case the whole process is repeated. If a modifier is specified, modification takes place at the final (not indirect) stage.

#### Type 3.4 - 3.7 Procedure Call

| $\mid$ T $\mid$ SIZE $\mid$ T' $\mid$ | Х  | ORIGIN IN BYTES |

|---------------------------------------|----|-----------------|

| 2  3  3                               | 24 | 32              |

T, SIZE, T' = 3, 5, 4 - 7 define the procedure call type.

X Upper bound for procedure call vector which must have 32-bit elements.

ORIGIN Contains the address of the procedure call vector. The two least significant bits of the origin field are ignored.

Action: When an attempt is made to access the operand, the hardware forces a procedure call<sup>a</sup> to the address held in the first 32-bit word of the vector, with the return link including the 'D set' bit pointing to the instruction attempting to make the access. The origin is not modified (even if a modifier is specified by the operand part of the order).

One example of the use of the procedure call descriptor is an implementation of an Algol parameter call by name. If the corresponding actual parameter is a simple variable, then the parameter descriptor can be a normal type 0 descriptor. But if the actual parameter is an expression, then the descriptor will be a procedure call to code which evaluates the expression. The value will be stored in some suitable store location and D replaced by a type 0 descriptor pointing to it; finally, the 'D set' bit in the stored link (c.f. Section 6.2) is set and an EXIT obeyed. The order causing the procedure call will be re-obeyed - the 'D set' bit prevents reloading of D and defines that the current value of D describes the required operand. (The 'D set' bit is automatically reset to 0.)

Note that a procedure call descriptor may be modified; the modification will take place when the order is re-obeyed after exit from the procedure.

<sup>&</sup>lt;sup>a</sup>This involves executing two hard-wired instructions held in the Instruction Buffer Unit:-STACKLINK JUMP D[0].

3.1

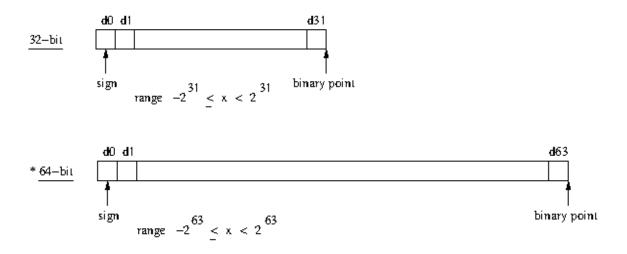

There is a separate 32-bit B-arithmetic unit which operates on the modifier register B. Although B is used mainly for modification, it is also used for some of the simpler integer arithmetic, for example, i = i + 1.

The bits in B are numbered from 0 on the left hand (most significant end).

| <b>d</b> 0 | d1 | <b>d</b> 2 | <b>d</b> 30 | <b>d</b> 31 |

|------------|----|------------|-------------|-------------|

|            |    |            |             |             |

The operand connection to the B-arithmetic unit is from the least significant 32 bits of the highway (bits 32-63).

The B-arithmetic unit performs signed 2's complement arithmetic. Thus B may take values in the range  $-2\uparrow31$  to  $2\uparrow31$  - 1. If, after any arithmetic operation, the true result is outside this range, the overflow bit is set. The overflow bit and a bit which is used to inhibit the interrupt resulting from overflow are digits 5 and 0 of BOD. Thus digit 5 of BOD is set to a one if overflow occurs and the interrupt will be inhibited if digit 0 is also set to one. All other digits of BOD are not significant.

# 3.2 <u>The B-Instructions</u>

The order code provides for 16 B-functions. Only 14 of these are implemented on MU5 and the rest are dummy instructions. The instructions are:-

LOAD (=)

Load B from the least significant 32 bits of the highway.

### LOAD & DECREMENT (=')

Load B from the least significant 32 bits of the highway then subtract 1. If an overflow occurs, digit 5 of BOD is set.

### STACK & LOAD (\*=)

The stack front register (SF) is first advanced by 2. The contents of B are placed on the highway as for a store order (see below). This is then sent to the 64-bit word whose address is specified by the new value of SF. Finally, the operand is loaded into B as in the load order (see above).

STORE (=>)

The content of B is placed on the least significant 32 bits (bits 32-63) of the highway and zeros are placed on the most significant 32 bits (0-31). The operand specifies the destination of this information.

ADD (+)

The operand is added to B, leaving the result in B. If an overflow occurs, then digit 5 of BOD is set.

SUBTRACT (-)

The operand is subtracted from B, leaving the result in B. If an overflow occurs, then digit 5 of BOD is set.

# MULTIPLY (\*)

B is multiplied by the operand to produce a 32-bit result which is the least significant 32 bits of the true 64-bit signed answer. If the true product has more than 32 significant bits, then B contains the least significant 32 bits of the true answer and digit 5 of BOD is set.

DIVIDE (/) A dummy instruction

### NON-EQUIVALENCE(≢)

B and the operand are non-equivalenced to produce a result in B.

OR(V)

B and the operand are or'ed to produce a result in B.

### AND (&)

B and the operand are and'ed to produce a result in B.

#### SHIFT $(\uparrow)$

B will be shifted arithmetically (left) by the number of places specified by the signed integer in digits 57-63 of the operand. If overflow occurs, digit 5 of BOD is set.

### COMPARE (COMP)

The operand is subtracted from B. Bits T1 and T2 of the test register are set from the result of the subtraction (see Section 6.4). A true result is always generated and no overflow may occur. The overflow bit in BOD is copied to bit T0 of the test register<sup>*a*</sup>. The contents of B are not altered.

#### REVERSE SUBTRACT $(\ominus)$

B is subtracted from the operand leaving the result in B. If an overflow occurs, then digit 5 of BOD is set.

#### COMPARE & INCREMENT (CINC)

A compare operation is performed (see above) then B is incremented by 1. If B overflow occurs as a result of being incremented, then digit 5 of BOD is set after the compare operation has been completed.

REVERSE DIVIDE  $(\emptyset)$  A dummy instruction.

<sup>a</sup>This should have said "... no overflow interrupt may occur, i.e. if the result overflows, bit T0 in the test register is set instead of digit 5 in BOD."

### Chapter 4 <u>Accumulator Arithmetic</u>

#### 4.1 The Accumulator and its Associated Registers

The function code contains a set of 16 functions for each of the following kinds of arithmetic:-

fixed point signed fixed point unsigned floating point decimal

In MU5 there are two associated registers:-

X, which is used by the signed fixed point orders,

and

A, which is used by the unsigned fixed point, floating point and decimal orders.

Each accumulator register is conceptually 64 bits long but digits 0-31 of X will not exist on MU5. There are two other visible 64-bit registers in the arithmetic unit, namely AOD and AEX. The bits of AOD are concerned mainly with interrupts whereas AEX (the accumulator extension register) serves to hold the least significant part of double length results. Because the accumulator 'A' is shared, the load and store functions would be the same in the fixed point unsigned, decimal and floating point instruction sets. Therefore, the load and store functions in the fixed point unsigned set are made to operate on AOD and those in the decimal set on AEX.

It is convenient to consider the operand for each function to be the 64-bit accumulator input buffer AIB. Thus the operation of the accumulator functions will be described by reference to the registers:-

# A, X, AOD, AEX, AIB

25

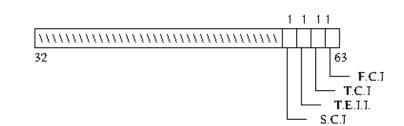

$\underline{\operatorname{digit}}$

| 51 | Operand size $(0/1 \text{ meaning } 32/64 \text{ bits})$ |

|----|----------------------------------------------------------|

| 52 | Inhibit floating point overflow interrupt                |

| 53 | Inhibit floating point underflow interrupt               |

| 54 | Inhibit fixed point overflow interrupt                   |

| 55 | Inhibit decimal overflow interrupt                       |

| 56 | Inhibit zero divide interrupt                            |

| 57 | Floating point overflow indicator                        |

| 58 | Floating point underflow indicator                       |

| 59 | Fixed point overflow indicator                           |

| 60 | Decimal overflow indicator                               |

| 61 | Zero divide indicator                                    |

| 62 | Inhibit rounding                                         |

| 63 | Double length $\pm$                                      |

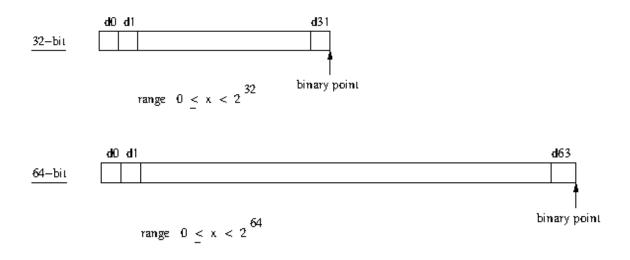

### 4.3 Formats for Arithmetic Data

The formats marked with an asterisk are software concepts only and have no significance in the hardware.

### (a) Fixed-point signed

Data is signed binary, held in 2's complement form. For multiplication and division, the binary point is at the least significant end, i.e. data is interpreted as an integer.

### (b) Fixed-point unsigned

Data is unsigned binary. For multiplication and division, the binary point is at the least significant end, i.e. data is interpreted as an integer.

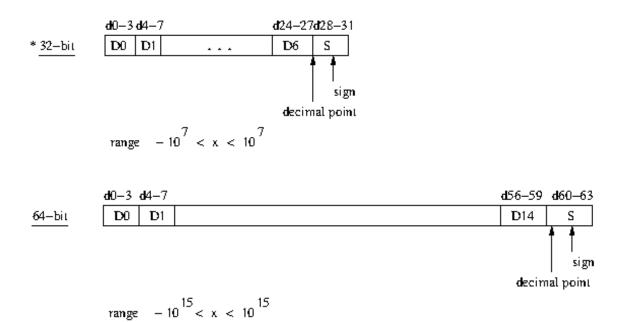

(c) Decimal

Data is in sign-modulus form. The modulus consists of 7 or 15 decimal digits occupying 4 bits each and the sign occupies 4 bits at the least significant end. Each decimal digit is coded in binary ( $0 \equiv 0000$ ,  $1 \equiv 0001 \dots 9 \equiv 1001$ ); the sign code 1101 means -ve, all other combinations mean +ve (1111 is preferred). For multiplication and division, the decimal point is at the least significant end, i.e. data is interpreted as an integer.

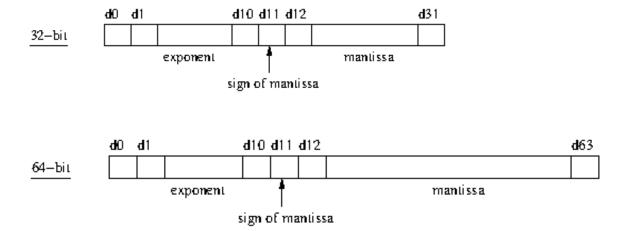

(d) Floating-point

Da ta is stored as a 2's complement mantissa m with an 11-bit exponent e stored at the most significant end. The most significant bit of m gives the sign of m and the interpretation of m assumes a binary point after the sign digit. The exponent has the base 16 and is interpreted as an unsigned 11-bit integer plus 1024, i.e.

| 00000000000  | -> -1024 |

|--------------|----------|

| 00000000001  | -> -1023 |

|              |          |

|              |          |

| 10000000000  | -> 0     |

|              |          |

|              |          |

| 111111111111 | -> 1023  |

This code has been chosen so that floating-point zero has all bits = 0.

4.4. The Signed Fixed Point Accumulator Orders

The arithmetic functions in this set assume X and the operand to be signed integers.

LOAD (=)

Copy digits 32-63 from AIB to X.

LOAD DOUBLE (=') Dummy instruction.

# STACK & LOAD (\*=)

Stack X in digits 32-63 of the next free 64-bit word on the stack, making digits 0-31 in this word zero. Then operate as for LOAD.

### STORE (=>)

Copy X to digits 32-63 of the highway and zeros to digits 0-31 of the highway.

ADD (+)

Digits 32-63 of AIB are added to X and the result is returned to X. If the addition overflows, digit 59 of AOD is set. In this case the result in X will be the least significant 32 bits of a 32-bit answer.

SUBTRACT (-)

Digits 32-63 of AIB are subtracted from X and the result is returned to X. If the result overflows, digit 59 of AOD is set.

# MULTIPLY (\*)

X is multiplied by digits 32-63 of AIB to form a signed single length result in X. If the result overflows, digit 59 of AOD is set and the result is the least significant bits of the 64-bit answer.

DIVIDE (/)

X is divided by digits 32-63 of AIB to form a quotient in X, which will be rounded down. If the divisor is zero, then digit 61 of AOD is set and X will be unaltered.

# NON-EQUIVALENCE( $\neq$ )

The logical non-equivalence of digits 32-63 of AIB with X replaces X.

OR(V)

The logical or of digits 32-63 of AIB with X replaces X.

SHIFT  $(\uparrow)$

X will be shifted arithmetically (left) by the number of places specified by the signed integer in digits 58-63 of AIB. Digit 59 of AOD will be set if the result overflows.

AND (&)

The logical and of digits 32-63 of AIB with X replaces X.

### REVERSE SUBTRACT $(\Theta)$

X is subtracted from digits 32-63 of AIB and the result is stored in X. If overflow occurs, digit 59 of AOD is set.

### COMPARE (COMP)

The operand in digits 32-63 of AIB is subtracted from X. Both are treated as signed integers. Bits T1 and T2 of the test register are set from the result of the subtraction. Note that a true result is generated and no overflow may occur. Bit 59 V bit 61 of AOD is copied to bit T0 of the test register<sup>*a*</sup>. The content of X is not altered.

### CONVERT (CONV)

The only conversion function implemented in the 'X' set is the conversion from integer to floating. The standardised floating result is left in AEX.

# REVERSE DIVIDE ( $\oslash$ )

Except that digits 32-63 of AIB are divided by X, this function operates as for DIVIDE.

<sup>&</sup>lt;sup>a</sup>This should have said "... no overflow interrupt may occur, i.e. if bit 59 or 61 would have been set, the logical OR of the inputs to these bits is formed in the hardware and used to set T0."

# 4.5. The Unsigned Fixed Point Accumulator Orders

The arithmetic functions in this set assume the least significant 32 bits of A and the operand in digits 32-63 of AIB to be 32-bit unsigned integers. They return a 64-bit signed result to A. If the most significant 32 bits of A or AIB are initially non-zero, they are set to zero prior to arithmetic.

LOAD (=)

Copy digits 51-63 from AIB to AOD.

Note: floating point LOAD DOUBLE is the correct order to use in conjunction with unsigned arithmetic.

LOAD DOUBLE (=') Dummy instruction.

STACK & LOAD (\*=)

AOD is stacked and loaded

STORE (=>)

Copy digits 51-63 of AOD to the highway, setting the other digits of the highway to zero.

ADD (+)

Digits 32-63 of AIB are added to digits 32-63 of A and the result is stored in digits 0-63 of A.

# SUBTRACT (-)

Digits 32-63 of AIB are subtracted from digits 32-63 of A and the result is stored in digits 0-63 of A.

### MULTIPLY (\*)

Digits 32-63 of A are multiplied by digits 32-63 of AIB to form a 64-bit product which is stored in A.

DIVIDE (/) Dummy instruction.

#### NON-EQUIVALENCE(*≢*)

Digits 32-63 of A are non-equivalenced with digits 32-63 of AIB and the result is stored in digits 32-63 of A. Digits 0-31 are set to zero.

| OR (V)                      |                                                                               |  |  |

|-----------------------------|-------------------------------------------------------------------------------|--|--|

|                             | Digits 32-63 of A are or'ed with digits 32-63 of AIB and the result is stored |  |  |

|                             | in digits 32-63 of A. Digits 0-31 are set to zero.                            |  |  |

| SHIFT $(\uparrow)$          |                                                                               |  |  |

|                             | A is shifted logically (left) by the number of places specified by the signed |  |  |

|                             | integer in digits 57-63 of AIB. This order operates on all 64 bits of A.      |  |  |

| AND (&)                     |                                                                               |  |  |

|                             | Digits 32-63 of A are and'ed with digits 32-63 of AIB and the result is       |  |  |

|                             | stored in digits 32-to 63 of A. Digits 0-31 are set to zero.                  |  |  |

| REVERSE SUBTRACT $(\Theta)$ |                                                                               |  |  |

|                             | Digits 32-63 of A are subtracted from digits 32-63 of AIB and the result is   |  |  |

|                             | stored in digits 0-to 63 of A.                                                |  |  |

```

COMPARE (COMP)

```

As for COMP in the signed fixed point set, except that the comparison applies to digits 32-63 of A and is on an unsigned basis. T0 of the test register is set to zero.

REVERSE DIVIDE  $(\emptyset)$  Dummy instruction.

4.6. <u>The Decimal Mode Accumulator Orders</u>

LOAD (=)

Dummy instruction.

LOAD DOUBLE (=')

Load AEX from AIB.

STACK & LOAD (\*=)

Stack and load AEX.

STORE (=>)

Store AEX.

| ADD $(+)$    | Dummy instruction. |

|--------------|--------------------|

| SUBTRACT (-) | Dummy instruction. |

| MULTIPLY (*)              | Dummy instruction. |

|---------------------------|--------------------|

| DIVIDE (/)                | Dummy instruction. |

| NON-EQUIVALENCE( $\neq$ ) | Dummy instruction. |

| OR (V)                    | Dummy instruction. |

SHIFT  $(\uparrow)$

Digits 59-63 of AIB are interpreted as a signed binary integer which specifies the number of decimal places by which A is to be shifted (left). The shift is logical over digits 0 to 59. Digits 60-63 are unaltered. If a left shift overflows, digit 60 of AOD is set.

AND (&) Dummy instruction.

#### COMPARE AOD

Digits 51-63 of AIB are and ed with digits 51-63 of AOD. The overflow digit of the test register will be set to 0/1 depending upon the result being non-zero/zero.

# COMPARE (COMP)

A is interpreted as a decimal number according to the formats in Section 4.3. Bit T2 of the test register is set as the sign (bits 60-63) of A. The logical & of A and AIB is formed and bit T1 of the test register is set according as the result is = or  $\neq$  to zero. Bit T0 of the test register is set to bit 60 of AOD (decimal overflow)<sup>*a*</sup>.

#### UNPACK

This instruction sets AEX (32-59) = AIB (32-59) and AEX (60-63) = AIB (60-63) V A (0-3). AEX (0-31) are unaltered. It also shifts digits 0-59 of A four places left. Digits 56-59 of A are set zero and digits 60-63 are unaltered.

REVERSE DIVIDE  $(\emptyset)$  Dummy instruction.

<sup>&</sup>lt;sup>a</sup>As in the case of other COMP orders, an overflow is recorded in test bit T0 rather than in AOD.

# 4.7. The Floating Point Accumulator Orders

For some of the floating-point arithmetic instructions, A and AEX are regarded as a double-length result register, A holding the most significant half and AEX the least significant half. Both will have the format shown in Section 4.3.

In all instructions AIB will form the 64-bit operand if digit 51 of AOD is one. If AOD is zero, digits 32-63 of AIB will form the most significant part of the 64-bit operand of which the other half is zero.

The operation of the floating-point instructions is dependent upon the setting of digits 62 and 63 of AOD. Digit 62 is the inhibit rounding digit. Rounding is performed by forcing 1 into digit 63 of A if the mantissa of AEX is non-zero. Digit 63 is set to select the special double-length versions of add, subtract and reverse subtract and is ignored by all other operations.

### LOAD SINGLE (=)

First, digit 51 of AOD is set to zero, then digits 32-63 of AIB are copied to digits 0-31 of A. Digits 32-63 of A are cleared.

# LOAD DOUBLE (=')

First, digit 51 of AOD is set to a one, then AIB is copied to A.

#### STACK & LOAD (\*=)

A (or digits 0-31 of A) is stacked, then A is loaded as in = / ='if digit 51 of AOD is 0/1. Digit 51 of AOD is unaltered.

# STORE (=>)

A (or digits 0-31 of A, as for X) is stored depending on whether digit 51 of AOD is 1 or 0.

ADD (+)

The operand from AIB is added to A. First the exponents of A and AIB are compared and the exponent field of A is replaced with the larger. The mantissa associated with the smaller exponent is then shifted right by the number of hexadecimal places given by the exponent difference. Also the digits that are shifted out are placed in the mantissa field of AEX, the rest of AEX being cleared. The mantissa field of A is set to the sum of the mantissa fields of A and AIB (one of which may have been shifted). The normalisation shifts that follow apply across the mantissa fields of both A and AEX, with a maximum shift of 13 hexadecimal places. If both mantissa fields are zero, a standard floating point zero is generated (Section 4.3). The exponent of A and AEX are both set to the exponent of the double-length result and rounding is performed as described above. When digit 63 of AOD is set and A and AEX contain a double-length number smaller than AIB, a correct unrounded double-length result will be formed. If either of the above cause exponent overflow/underflow, digit 57/58 of AOD will be set.

SUBTRACT (-)

The operand from the highway is subtracted from A. The operation proceeds in the same general way as ADD. However, if the number to be subtracted is smaller, it is negated and then the add operation is performed.

MULTIPLY (\*)

A is multiplied by the operand to give a double length result in A and AEX. This result is standardised and AEX exponent is set as above. Rounding will occur if digit 62 of AOD is not set. On exponent overflow/underflow, digit 57/58 of AOD is set

DIVIDE (/)

A is divided by the operand to give a single-length standardised (possibly rounded) result in A. If the divisor is zero, digit 61 of AOD is set or if exponent overflow or underflow occurs, digit 57/58 of AOD is set.

#### NON EQUIVALENCE $(\neq)$

The result of combining A with AIB with logical  $\neq$  is returned to A.

OR(V)

The result of combining A with AIB with logical V is returned to A.

#### SHIFT $(\uparrow A)$

A is shifted circularly (left) by the number of places specified by digits 58-63 of AIB.

AND (&)

The result of combining A with AIB with logical & is returned to A.

#### REVERSE SUBTRACT( $\ominus$ )

This is the same as SUBTRACT, except that A is subtracted from the operand.

#### COMPARE (COMP)

A is compared with the operand in AIB and the test register is set. Both are assumed to be floating-point numbers. T0 of the test register is set if any of bits 57, 58, 61 are (i.e. would have been) set.

#### CONVERT (CONV)

The only conversion function provided in the floating-point set is one that converts the integer part of A to a signed fixed-point number, leaving the result in AEX. If the result is too big, digit 58 of AOD is set.

# REVERSE DIVIDE ( $\oslash$ )

This is the same as DIVIDE, except that the operand is divided by A.

### 5.1 <u>Introduction</u>

This chapter defines the registers D, XD and DOD (Section 5.2) and describes the orders associated with the secondary operand unit. The orders fall into three classes:-

| (a) Register manipulation | (Section $5.3$ ) |

|---------------------------|------------------|

| (a) Structure access      | (Section $5.4$ ) |

| (a) Store to Store        | (Section $5.5$ ) |

The register manipulation orders are concerned with loading and storing the registers D and XD. The structure access orders are concerned with modifying descriptors and accessing elements of data structures. The store to store orders enable operations to be carried out on strings of bytes of any length, e.g. moving one string to another or comparing strings. The registers D and XD are used to hold the descriptors of the strings.

The STACK order is described in Section 5.3, chiefly because it isn't described anywhere else.

This chapter assumes the reader is familiar with the different types of descriptor defined in Sections 2.10 - 2.13.

# 5.2. Internal Registers in the Secondary Operand Unit (SEOP)

The two main registers in the SEOP are D and XD. They are both 64 bits long and are used to hold descriptors, so they have type, bound and origin fields as shown below:-

|    | d0   |             |              | d63 |

|----|------|-------------|--------------|-----|

| D  | TYPE | BOUND (DB)  | ORIGIN (DO)  |     |

|    | 8    | 24          | 32           |     |

| XD | TYPE | BOUND (XDB) | ORIGIN (XDO) |     |

|    | 8    | 24          | 32           |     |

The following notation is used for the various parts of D, XD:-

| DO  | the origin field of D  | (d32-63) |

|-----|------------------------|----------|

| XDO | the origin field of XD | (d32-63) |

| DB  | the bound field of D   | (d8-31)  |

| XDB | the bound field of XD  | (d8-31)  |

| DT  | the top half of D      | (d0-31)  |

| XDT | the top half of XD     | (d0-31)  |

The only other register in SEOP that can be used by the programmer is DOD; DOD, D, XD, DT AND XDT may all be read from or written to as internal register operands. DOD is a 32-bit register that contains the interrupt and interrupt inhibit bits for SEOP as follows:-

| d31 | XCH  | XCHK digit                                           |

|-----|------|------------------------------------------------------|

| d30 | ITS  | Illegal Type/Size                                    |

| d29 | EMS  | Executive mode Subtype used in non-executive mode    |

| d28 | SSS  | Short Source String in store to store order          |

| d27 | NZT  | Non-Zero Truncation when storing secondary operand   |

| d26 | BCH  | Bound Check Fail during secondary operand access     |

| d25 | SSSI | SSS Interrupt Inhibit                                |

| d24 | NZTI | NZT Interrupt Inhibit                                |

| d23 | BCHI | BCH Interrupt Inhibit                                |

| d22 |      | Read only interrupt, attempt to write using type $0$ |

|     |      | descriptor with read only bit set.                   |

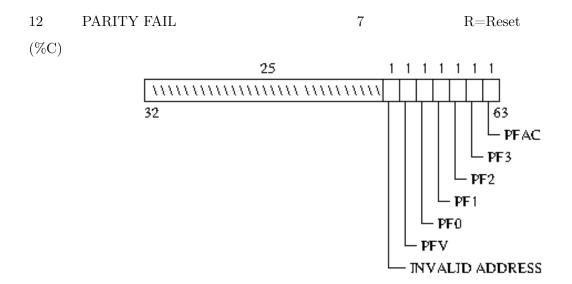

ITS and EMS will always cause an interrupt. SSS, NZT or BCH will cause an interrupt unless SSSI, NZTI or BCHI respectively, are set.

# 5.3. D and XD Manipulation Orders and STACK

| STACK | Stack the operand (advance SF by 2, then store operand at new SF). |

|-------|--------------------------------------------------------------------|

| DO =  | Load the origin of D from bits 32-63 of the operand.               |

|       | Bits 0-31 of D are unaltered.                                      |

| D =   | Load D from bits 0-63 of the operand.                              |

| D *=  | Stack D (advance SF by 2, then store operand at new SF).           |

|       | Then load D from bits 0-63 of the operand.                         |

| D =>  | Store D in bits 0-63 of the operand.                               |

| DB =  | Load the bound of D (bits $(8-31)$ from bits 40-63 of the operand. |

|       | The rest of D is unaltered.                                        |

| XDO = |                                                                    |

| XD =  | As for DO =, D =, D =>, DB = but operate                           |

| XD=>  | on XD instead of D.                                                |

| XDB = |                                                                    |

|       |                                                                    |

<u>Note</u>: Some of these orders may be used with secondary operands. For S[B] and S[0] operands, the effect is as follows:-

(a) DO =, D =, DB =

D will first be loaded with the S operand descriptor; then the secondary operand will be accessed and will replace the whole or part of the new value of D.

(b) D \*=

The original contents of D will be stacked before the S descriptor is loaded into D.

(c) XDO = , XD = , XDB =Work as expected.

The orders  $D \Rightarrow AD \Rightarrow AD \Rightarrow BC and XD \Rightarrow BC and AD A AND AD AND A$

## 5.4. <u>Structure Access Orders</u>

[None of these orders may be used with secondary operands<sup>4</sup>.]

- MOD Uses bits 32-63 of the operand as a signed integer modifier for the descriptor in D. The modifier is added to the origin field (after scaling if US = 0 in type 0 or 2 descriptors) and subtracted from the bound field. A bound check interrupt will occur unless  $0 \le \text{modifier} < \text{bound}$  (assuming bound checking is not inhibited). The bound check applies to descriptors of types 0, 1, 2, 3.0, 3.1 and 3.2. For type 3.3, the indirectly addressed descriptor is loaded into D before the modification takes place. Similarly for type 3.4 3.31, the procedure is called first.

- XMOD Exactly the same as MOD except that it works on XD instead of D. (Types 3.3, 3.4 - 3.31 are illegal.)

- SMOD As for MOD, but DB is unaltered and there is no bound check.

- MDR Equivalent to MOD followed by a D = D[0].

- RMOD Bits 0-31 of the operand are loaded into bits 0-31 of D.Bits 32-63 of the operand are added to bits 32-63 of D.

- XCHK If  $0 \le$  operand bits 32-63 < XDB, then bit 31 of DOD is set to 1, otherwise it is set to 0.

<sup>&</sup>lt;sup>4</sup> It might have been helpful for there have been a reminder here that 1-bit and 4-bit vectors must start on a byte boundary, meaning that if MOD, etc. are used with these vectors, they can only take operands that are multiples of 8.

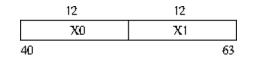

SUB1 A complicated order that works as follows:-

XD must be a vector descriptor (type 0 or 2) addressing 32-bit elements.

SUB2 Omits the first two steps of SUB1:-

B - XD[0] B \* XD[1] DB = XD[2] MOD B XMOD 3

Use of structure access orders

MOD (and XMOD) can be used for constructing substrings of larger strings, e.g. 'D = S; MOD I; DB = L' creates a descriptor for the string of length L starting at the Ith byte of the string S. MOD can also be used to step through a vector, since 'D = V; MOD 1' creates a descriptor to a vector consisting of all but the first element of V.

MDR can be used for moving through a list structure or for creating arrays via an Iliffe vector.

RMOD is used for 'reverse modification'. This is useful when used in combination with the 'dope vector' orders SUB1 and SUB2 described below. It can also be used to make data structures relocatable.

XCHK is a special order that is used to check for overlapping strings. The only dangerous case is when the start of the destination string (for a move or logical store to store order) lies within the source string. So the idea is to put the source string descriptor in XD and then use XCHK with operand = destination origin - source origin. The SUB1 and SUB2 orders are used for accessing arrays via dope vectors. For a general array:-

we want to access X[i1, i2, . . . in]. The address can be expressed in the form:-

$$X0 + (i1 - l1)*m1 + (i2 - l2)*m2 + ... + (in - ln)*mn$$

where m1, m2, . . mn are suitable multipliers; in addition we must have  $l1 \le i1 \le u1$ ,  $l2 \le i2 \le u2$ , ..  $ln \le in \le un$ . When the array is declared, a dope vector is created that contains a triple of 32-bit elements for each dimension of the array; a triple consists of the lower bound l, the multiplier m and a checking value c. For the array X above, the dope vector will look like:-

| 11 m1 c1 12 m2 c2 In mn |

|-------------------------|

|-------------------------|

A descriptor X' is created which points to this vector. To access the element, the appropriate sequence is:-

|         | B = i1          | 1st subscript                                                |

|---------|-----------------|--------------------------------------------------------------|

|         | SUB1 X'         | Load XD with dope vector descriptor and clear D.             |

|         |                 | Subtract 11 from B, multiply by m1, check result is in range |

|         |                 | $0 \le B \le c1$ and add to DO.                              |

|         |                 | (Hence $DO = (i1 - l1)^*m1$ and $l1 \le i1 \le u1$ ).        |

|         | B = i2          | 2nd subscript                                                |

|         | SUB2            | $DO + (i2 - l2)*m2 \qquad l2 \le i2 \le u2$                  |

|         |                 |                                                              |

|         |                 |                                                              |

|         | B = in          | nth subscript                                                |

|         | SUB2            | $DO + (in - ln)^*mn$ $ln \le in \le un$                      |

| There a | are now two way | rs of accessing the element itself:-                         |

|         | RMOD X          | or $B = DO$                                                  |

[The checking values c are clearly (u1 - l1 + 1)\*m1.]

$\mathbf{A} = \mathbf{D}[\mathbf{0}]$

A = X[B]

## 5.5. <u>Store to Store Orders</u>

The store to store orders fall into three main classes: string-string, byte-string and table-string orders; there is also one special table look-up order. The string-string orders operate on a source string and a destination string; operations are provided that move (i.e. copy), compare and logically combine the strings. The byte-string orders use a byte and a destination string; they are the same as string-string orders in which the source string consists of the specified byte repeated as often as necessary. The tablestring orders make it possible to translate the characters of a string into a different code specified in a table or to check a string to see if it contains any of the characters specified in a table. The table look-up order scans the table for a particular element.

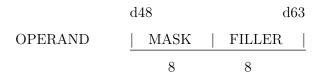

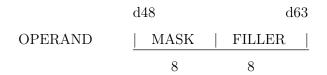

## The MASK

For all the store to store orders except table look-up (TALU), bits 48-55 of the operand are an eight-bit MASK. In each byte processed by the order, bits corresponding to 1's in the mask are ignored; when any byte is used in an operation, the corresponding bits are taken to be zeros, and if a byte is put into store, the corresponding bits in the store are unaltered. For example, if MASK = 11000011, then a move order will only change bits 2-6 of the bytes in the destination string.

# String-String Orders

For all string-string orders, XD contains the source string descriptor and D the destination string descriptor. The descriptors must have type 0, 1 or 2 and element size 8 bits, otherwise there will be an ITS interrupt. The operand defines the MASK (see above) and a FILLER. The FILLER is not in fact used for all the orders.

SMVBMoves one byte from source to destination. If the source string is a null<br/>string, move FILLER to destination. If DB = 0 there will be a BCH<br/>interrupt. Updates DO, DB, XDO, XDB. $[(\underline{if} DB = 0 \quad \underline{then} \text{ BCH interrupt}$ <br/>if  $XDB = 0 \quad \underline{then} \text{ (FILLER => D[0]; MOD 1)}$ <br/> $\underline{else} (XDO[0] => D[0]; XMOD 1)]$

- \*SMVE Moves source to destination. If source is shorter than destination there will be an SSS interrupt; but note that this will simply terminate the operation if the inhibit bit SSSI is set. Updates DO, DB, XDO, XDB. [Li: <u>if</u> DB  $\neq$  0 <u>then</u> (<u>if</u> XDB = 0 <u>then</u> SSS interrupt <u>else</u> (XD[0] => D[0]; MOD 1; XMOD 1); -> L1)]

- SMVF Moves source to destination. If the source runs out, then uses FILLER for remainder of destination. Updates DO, DB, XDO, XDB. [L1: <u>if</u> DB  $\neq$  0 <u>then</u> (SMVB OPERAND; -> L1)]

<sup>\*</sup> See note below under Table-String Orders

- SCMP Compares source and destination strings looking for inequality in two corresponding bytes. If source runs out, FILLER is used. The test register is set = 0 if no inequality is found, > 0 if source byte >destination byte, < 0 if source byte < destination byte; for comparison purposes, the bytes are treated as unsigned integers. DO, DB, XDO, XDB are updated. [L1:  $\underline{\text{if }} DB = 0 \underline{\text{then}} (T = '='; \rightarrow L4);$ if XDB = 0 then (if FILLER  $\neq D[0]$  then -> L2 else (MOD 1; -> L1)) else if  $XD[0] \neq D[0]$  then -> L3 else (MOD 1; XMOD 1;  $\rightarrow$  L1); L2: if FILLER < D[0] then T = '<' else T = '>'; -> L4; L3: if XD[0] < D[0] then T = '<' else T = '>' ; L4: 1

- SLGC Source and destination are logically combined and the result stored in destination. The logical operation is the same for each bit of each byte and is defined by bits 44-47 of the operand.

#### d44 d45 d46 d47

| L | 0 | L1 | L2 | L3 |

|---|---|----|----|----|

|---|---|----|----|----|

The result of the operation is defined by the table below:-

| source bit      | 0  | 0  | 1  | 1  |

|-----------------|----|----|----|----|

| destination bit | 0  | 1  | 0  | 1  |

| result bit      | LO | L1 | L2 | L3 |

If the source string runs out, there will be an SSS interrupt.

[L1: <u>if</u> DB  $\neq$  0 <u>then</u> <u>if</u> XDB = 0 <u>then</u> SSS interrupt; (XD[0] lgc D[0] => D[0]; MOD 1; XMOD 1; -> L1)]

# Byte-String Orders

The byte-string orders are the same as the string-string orders except that the source consists of copies of the BYTE specified in operand bits 56-63. The MASK appears as usual in operand bits 48-55. D contains the destination string descriptor which must have type 0, 1 or 2 and element size 8 bits, otherwise there will be an ITS interrupt; XD is not used.

BMVB Moves one byte to destination.

BMVE Moves BYTEs to destination until full.

BSCN Scans destination looking for a byte = BYTE. The test register is set = 0 if an equality is found, < 0 otherwise. DO and DB are updated. [L1: <u>if</u> DB = 0 <u>then</u> (T = '<'; -> L2); <u>if</u> BYTE = D[0] <u>then</u> (T = '='; -> L2) <u>else</u> (MOD1; -> L1); L2: ]

- BCMP Scans destination looking for a byte  $\neq$  BYTE. The test register is set as for SCMP.

- BLGC Combines BYTE with destination string using logical operation defined by operand bits 44-47 as for SLGC. Result is stored in destination.

## Table-String Orders

For both the table-string orders, XD contains a string descriptor which must have type 0, 1 or 2 and element size 8 bits. D may contain any descriptor. The operand contains no information other than the MASK, specified as usual in bits 48-55.

- \*TRNS Each byte of the XD string is processed in turn. First, it is used as a modifier for the descriptor in D to access a secondary operand. Then the least significant 8 bits of the secondary operand replace the original byte. There may be a BCH interrupt during the D access. D will usually contain a byte vector descriptor.

[L1: <u>if XDB ≠ 0 then</u> (D[XD[0]] => XD[0]; XMOD 1; -> L1)]

- \*TCHK Each byte of the XD string is accessed as above and used as a modifier for the descriptor in D. If the least significant bit of the secondary operand is a 1, then the operation is terminated with BN = 0. If no 1 is found for the whole of the XD string, then BN = 1. D will usually contain a bit vector descriptor.

[L1:  $\underline{\text{if }} \text{ XDB} = 0 \underline{\text{ then }} \text{ BN} = 1 \underline{\text{ else }}$

(if l.s. bit of D[XD[0]] = 0 then (XMOD 1; -> L1) else BN = 0)]

\* TRNS, TCHK, SMVE These orders are not commissioned<sup>a</sup>. If an attempt is made to execute any of them the effect will be that of a DUMMY order, except that an interrupt may occur if the wrong type, size or length has been specified as described above and TCHK will set the Test Register in an unspecified manner.

$<sup>^{</sup>a}$  i.e. in the particular MU5 processor built at the University of Manchester to execute this order code.

TALU This order enables a fast scan to be made for an element equal to the operand. D contains a descriptor that defines the table - origin in DO, length in DB. The length is expressed in byte units. The descriptor must have type 0 or 2 and element size 32 bits. XDO contains a MASK that is used in exactly the same way as the mask in the other store to store orders; bits corresponding to 1's in the MASK are ignored. The least significant 32 bits of the operand are compared with each element of the table in turn for equality (under control of MASK). If no equality is found, then the operation terminates with the test register set > 0 and the descriptor in D updated (DB = 0, DO points after the end of table). If inequality is found, then the test register is set = 0 and the descriptor in D will point to the element found, with the bound field updated. [L1: if DB = 0 then T = '>' else (if operand  $\neq$  D[0] then (MOD 1; -> L1) else T = '=')]

N.B. TALU takes operands directly from store.

# Chapter 6 Organisational Orders

# 6.1 <u>Introduction</u>

The format for the organisational orders is shown below.

$$\frac{\mid \mathrm{cr}=0 \mid \mathrm{f'} \mid \qquad \mathrm{N'} \mid}{3 \quad 6 \qquad 7}$$

The cr bits are zero and the f' bits define the function to be performed. N' defines the operand for the order as described in Chapter 2; the only kind of operand that cannot be addressed is an internal register.

The organisational orders fall into the following groups:-

- (a) Register operations orders manipulating NB, XNB, SF, MS.

- (b) Control transfers and procedure call orders.

- (c) Conditional control transfers.

- (d) Boolean orders operating on the 1-bit Boolean register BN.

- (e) Special orders.

#### NB, SF and XNB Orders

The registers NB, SF and XNB are defined in Section 2.2 and may be regarded as unsigned registers. In the following orders, it should be remembered that the least significant digit of each register is permanently zero, so that the least significant bit of the operand will have no effect.

| NB =  | Load NB from bits 48-63 of the operand.  |

|-------|------------------------------------------|

| SF =  | Load SF from bits 48-63 of the operand.  |

| XNB = | Load XNB from bits 48-63 of the operand. |

- NB + Add operand bits 48-63 to NB; interrupt on segment overflow.

- SF + As for NB +, but add to SF.

- XNB + Add operand bits 48-63 to the least significant 16 bits of XNB; interrupt on segment overflow (carry into top half of XNB is not allowed).

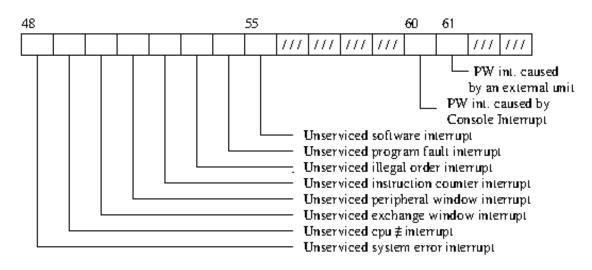

- SF = NB + Add NB to operand bits 48-63 and store result in SF; interrupt on segment overflow.