# Library Development Guide

October 1, 1989

## P/N: 900-00690 Rev. A

Valid Logic Systems, Incorporated 2820 Orchard Parkway San Jose, California 95134 (408) 432–9400 Telex 371 9004 FAX (408) 432–9430

#### Copyright © 1989 Valid Logic Systems, Incorporated

This document contains confidential proprietary information which is not to be disclosed to unauthorized persons without the prior written consent of an officer of Valid Logic Systems, Incorporated.

The copyright notice appearing above is included to provide statutory protection in the event of unauthorized or unintentional public disclosure.

While every attempt has been made to keep the information in this document as accurate and as current as possible, Valid makes no warranty, expressed or implied, with regard to the information contained herein, including, but not limited to, the implied warranties of merchantability and fitness for any particular application. Valid further assumes no responsibility for any errors that may appear within this document or for any damages, direct or indirect, that may result from using this document.

ValidGED, ValidPACKAGER, ValidCOMPILER, ValidSIM, ValidTIME, and Transcribe are trademarks of Valid Logic Systems, Inc.

UNIX is a trademark of AT&T Bell Laboratories.

VAX, DECstation, VMS, and ULTRIX are trademarks of Digital Equipment Corporation. Sun Workstation and Sun Microsystems are registered trademarks of Sun Microsystems, Inc.

10/1/89

## MANUAL REVISION HISTORY

| Rev | Date    | Software Release    | Reason for Change |

|-----|---------|---------------------|-------------------|

| A   | 10-1-89 | Library Release 9.0 | Initial release.  |

|     |         |                     |                   |

|     |         |                     |                   |

|     |         |                     |                   |

|     |         |                     |                   |

|     |         |                     |                   |

|     |         |                     |                   |

|     |         |                     |                   |

|     |         |                     |                   |

|     |         |                     |                   |

|     |         |                     |                   |

## Preface

The Library Development Guide describes creating and maintaining libraries. This guide is intended for use by the System Librarian and/or Library Developer. The Library Developer is responsible for maintaining and modifying all libraries and creating new libraries. Valid recommends that the Library Developer have the following qualifications:

- Knowledge of a system text editor

- Understanding of SCALD language concepts

- Operating knowledge of any Valid application necessary to create required component models and the ability to interpret the application results:

GED ValidPACKAGER ValidCOMPILER ValidSIM ValidTIME Transcribe Valid recommends that you give some consideration to library development decisions that are pertinent to your site requirements. Some of the issues you should resolve:

- Are you developing mil-spec or standard components?

- What body standards should you follow?

- What are the minimum test procedures for a completed component?

- What is the minimum size for a body or the text included with a body?

- Are you using ANSI or commercial components?

- What tools are you currently using? What tools will you be using in the future: Timing Verifier, Simulator? Should you save time by creating models now for tools you might use in the future?

- Will users be developing their own components or will the Librarian be the only developer? Will the Librarian test user-developed components?

The standards used in this manual are for commercial components. If you are building ANSI library components, you should follow the standards designed for ANSI components.

Several Valid manuals are helpful during the library development process. Valid recommends that the Library Developer have access to the following documentation:

- Library Development Guide

- Library Reference Manual

- ValidCOMPILER Reference Manual

- ValidPACKAGER Reference Manual

- ValidSIM Reference Manual

- ValidTIME Reference Manual

- SCALD Language Reference Manual

- Tutorial I: Logic Design

- Tutorial II: Using your Validation Designer

The Library Development Manual covers the following topics:

- Section 1: Library conventions and syntax issues; library organization; library maintenance.

- Section 2: Creating library components.

- Section 3: Creating the physical model.

- Section 4: Creating the simulation model.

- Section 5: Creating the timing model.

- Section 6: Creating support components.

- Section 7: Testing a new library.

- Appendix A: Text file method of creating a library drawing.

- Appendix B: Changes in the library drawing method.

# **Table of Contents**

| Library Fundamentals                                                                                                                                                                                                       | 1–1                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| The Library Development Process                                                                                                                                                                                            | 1–2                                                     |

| Library Conventions and Syntax                                                                                                                                                                                             | 1-3                                                     |

| Conventions                                                                                                                                                                                                                | 1-3                                                     |

| Signal Name Syntax                                                                                                                                                                                                         | 1–3                                                     |

| Library Organization                                                                                                                                                                                                       | 1-5                                                     |

| The Library Directory                                                                                                                                                                                                      | 1–5                                                     |

| Individual Libraries                                                                                                                                                                                                       | 1–7                                                     |

| The Master Library File                                                                                                                                                                                                    | 1–9                                                     |

| Library Components                                                                                                                                                                                                         | 1–11                                                    |

| Component Versions                                                                                                                                                                                                         | 1–14                                                    |

| Library Maintenance                                                                                                                                                                                                        | 1–17                                                    |

| Operating System Considerations                                                                                                                                                                                            | 1–17                                                    |

| Maintaining Libraries on a Foreign Host                                                                                                                                                                                    | 1–19                                                    |

|                                                                                                                                                                                                                            |                                                         |

| Component Creation                                                                                                                                                                                                         | 2–1                                                     |

| -                                                                                                                                                                                                                          |                                                         |

| Basic Procedure (Checklist)                                                                                                                                                                                                | <b>2-1</b><br>2-2<br>2-3                                |

| Basic Procedure (Checklist)                                                                                                                                                                                                | 2–2                                                     |

| Basic Procedure (Checklist)<br>Creating A Library<br>Creating a New Component Drawing                                                                                                                                      | 2–2<br>2–3                                              |

| Basic Procedure (Checklist)<br>Creating A Library<br>Creating a New Component Drawing<br>Editing the .BODY Drawing                                                                                                         | 2–2<br>2–3<br>2–6                                       |

| Basic Procedure (Checklist)<br>Creating A Library<br>Creating a New Component Drawing<br>Editing the .BODY Drawing<br>Moving the Body Name                                                                                 | 2–2<br>2–3<br>2–6<br>2–6                                |

| Basic Procedure (Checklist)<br>Creating A Library<br>Creating a New Component Drawing<br>Editing the .BODY Drawing<br>Moving the Body Name<br>Creating the Body Shape                                                      | 2-2<br>2-3<br>2-6<br>2-6<br>2-8                         |

| Basic Procedure (Checklist)<br>Creating A Library<br>Creating a New Component Drawing<br>Editing the .BODY Drawing<br>Moving the Body Name<br>Creating the Body Shape<br>Drawing Pins                                      | 2-2<br>2-3<br>2-6<br>2-6<br>2-8<br>2-9                  |

| Basic Procedure (Checklist)<br>Creating A Library<br>Creating a New Component Drawing<br>Editing the .BODY Drawing<br>Moving the Body Name<br>Creating the Body Shape<br>Drawing Pins<br>Pass-through Pins                 | 2-2<br>2-3<br>2-6<br>2-6<br>2-8<br>2-9<br>2-11          |

| Basic Procedure (Checklist)<br>Creating A Library<br>Creating a New Component Drawing<br>Editing the .BODY Drawing<br>Moving the Body Name<br>Creating the Body Shape<br>Drawing Pins<br>Pass-through Pins<br>Bubbled Pins | 2-2<br>2-3<br>2-6<br>2-6<br>2-8<br>2-9<br>2-11<br>2-13  |

| Basic Procedure (Checklist)<br>Creating A Library<br>Creating a New Component Drawing<br>Editing the .BODY Drawing<br>Moving the Body Name<br>Creating the Body Shape<br>Drawing Pins<br>Pass-through Pins                 | 2-2<br>2-3<br>2-6<br>2-8<br>2-9<br>2-11<br>2-13<br>2-15 |

| Attaching Properties to the Body                         | 2–21 |

|----------------------------------------------------------|------|

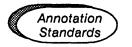

| NEEDS_NO_SIZE Property                                   | 2-23 |

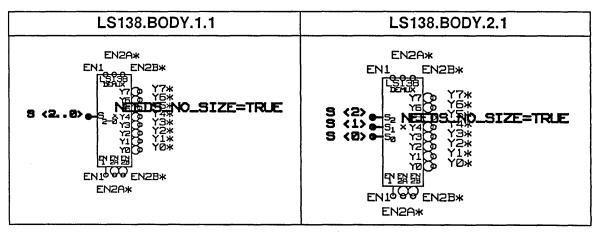

| HAS_FIXED_SIZE Property                                  | 2–24 |

| Invisible Properties                                     | 2–25 |

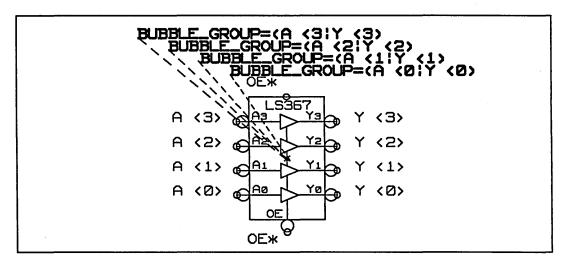

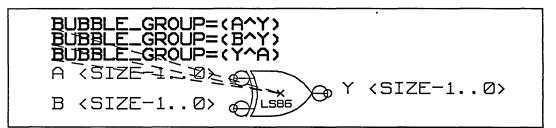

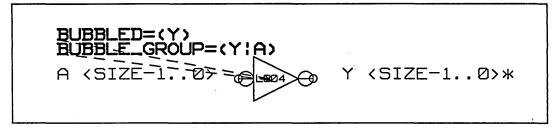

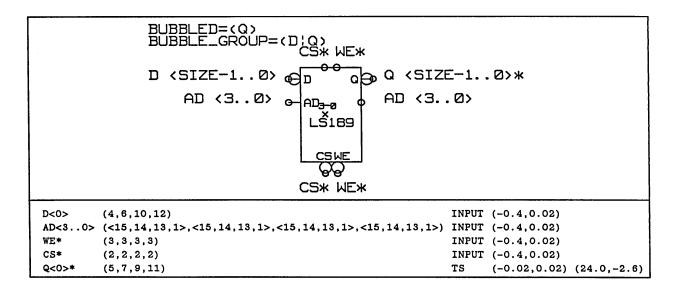

| BUBBLE_GROUP Property                                    | 2–26 |

| BUBBLED Property                                         | 2–29 |

| Completing the Body Drawing                              | 2-31 |

| Building Other Body Versions                             | 2-32 |

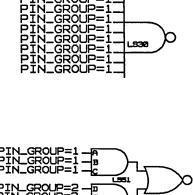

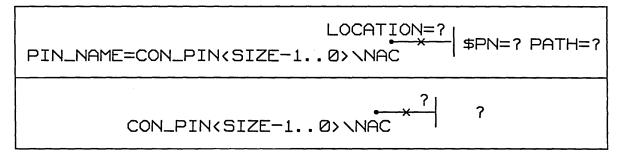

| Vectored Components                                      | 2-32 |

| Sizeable Components                                      | 2–34 |

| Pin Names for Sizeable Components                        | 2–36 |

| Modifying Existing Components                            | 2–38 |

| The Smash Command                                        | 2–38 |

| The Diagram Command                                      | 2-40 |

| Completing a Component                                   | 2–41 |

|                                                          |      |

| The Physical Model                                       | 3-1  |

| Creating the .PART Drawing                               | 3–2  |

| Modifying an Existing .PART Drawing                      | 3–4  |

| Creating the Physical Model: Basic Procedure (Checklist) | 3–5  |

| Creating the Library Drawing                             | 3-6  |

| Adding Body Properties                                   | 3–7  |

| FAMILY Property                                          | 3–8  |

| POWER_PINS Property                                      | 3–9  |

| BODY_TYPE Property                                       | 3-10 |

| COST Property                                            | 3-10 |

| PART_NUMBER Property                                     | 3–10 |

| PHYS_DES-PREFIX Property                                 | 3–10 |

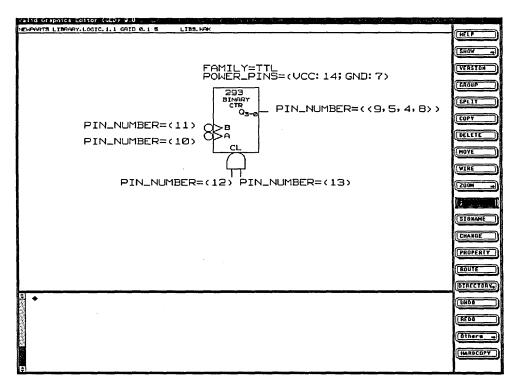

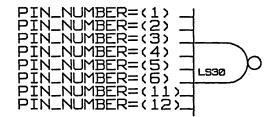

| Adding Pin_Number Properties                             | 3-11 |

| Pin Number Formats                                       | 3-13 |

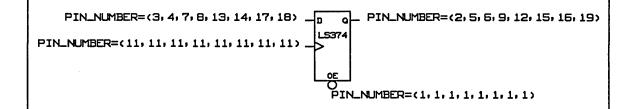

| Single Section Scalar Pins                               | 3–14 |

| Single Section Vector Pins                               | 3–14 |

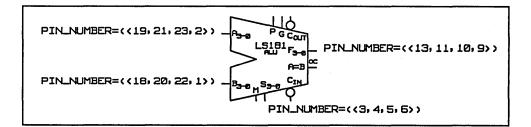

| Multiple Section Scalar Pins                             | 3–16 |

| Multiple Section Common Pins                             | 3-17 |

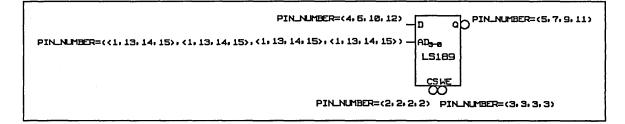

| Multiple Section Common Vector Pins                      | 3–18 |

| Asymmetrical Components                                  | 3–19 |

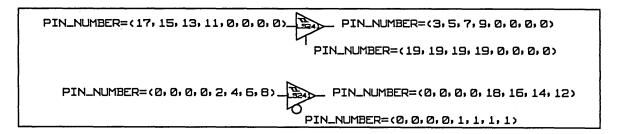

| Compact Pin Number Syntax                                | 3-20 |

| Adding Other Pin Properties           | 3–22 |

|---------------------------------------|------|

| OUTPUT_LOAD Property                  | 3-24 |

| INPUT_LOAD Property                   | 3–24 |

| BIDIRECTIONAL Property                | 3-25 |

| PIN_GROUP Property                    | 3–25 |

| OUTPUT_TYPE Property                  | 3–27 |

| Load Checking Properties              | 3–28 |

| NO_LOAD_CHECK Property                | 3-28 |

| NO_IO_CHECK Property                  | 3–28 |

| ALLOW_CONNECT Property                | 3–28 |

| UNKNOWN_LOADING Property              | 3–28 |

| Completing the Library Drawing        | 3–29 |

| Modifying an Existing Library Drawing | 3-29 |

| Creating the Physical Model File      | 3-30 |

| Archiving Library Drawings            | 3-31 |

|                                       |      |

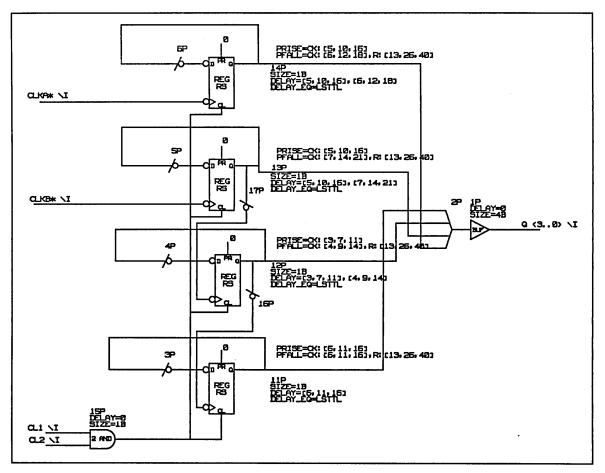

| The Simulation Model                  | 4-1  |

| Defining the Simulation Model         | 4-2  |

| General Design Rules for Models       | 4-2  |

| Delay and Pulse Width Standards       | 4-4  |

| Calculating Delays                    | 4-4  |

| Data-Dependent Delays                 | 4–5  |

| Open Collector Gates                  | 4–5  |

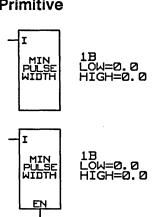

| Pulse Width                           | 4-5  |

| One-Shots                             | 4-6  |

| Creating the Model: Checklist         | 4-7  |

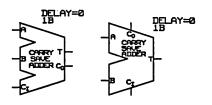

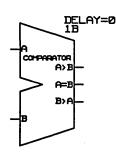

| The Simulator Primitives              | 4–10 |

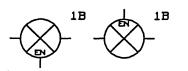

| Bubbled Pins                          | 4-10 |

| Truth Table Abbreviations             | 4-10 |

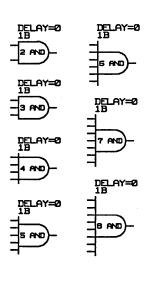

| The Logic Gate Primitives             | 4–11 |

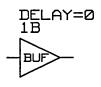

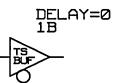

| The Buffer Primitives                 | 4–13 |

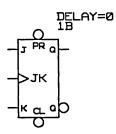

| The JK Primitive                      | 4-15 |

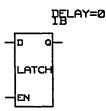

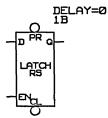

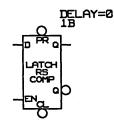

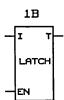

| The Latch Primitives                  | 4–16 |

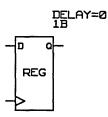

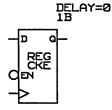

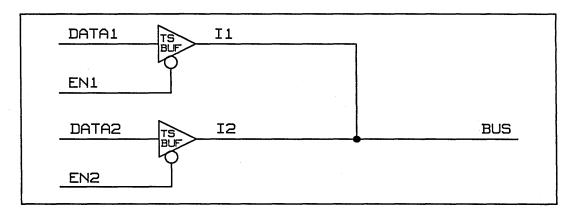

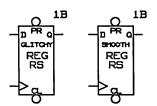

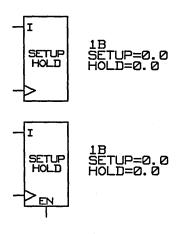

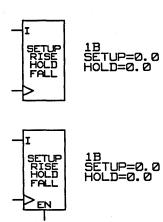

| The Register Primitives               | 4–19 |

|                                       |      |

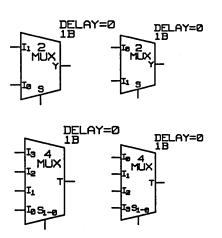

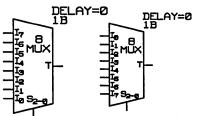

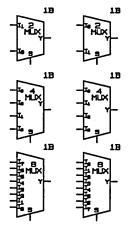

| The Multiplexer Primitives            | 4-24 |

1

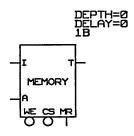

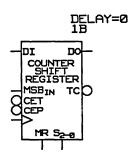

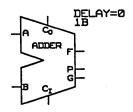

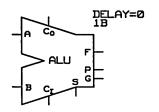

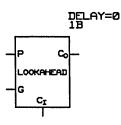

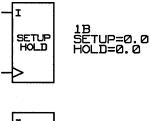

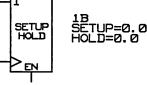

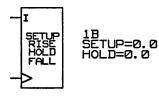

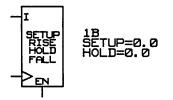

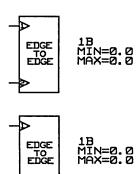

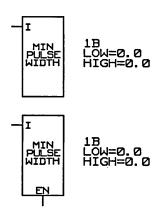

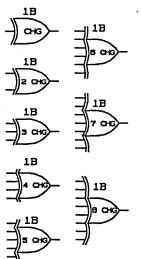

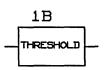

| The MEMORY PrimitiveThe COUNTER/SHIFT REGISTER PrimitiveThe Arithmetic PrimitivesThe Timing Checker PrimitivesOther PrimitivesOther PrimitiveUser-coded PrimitivesSimulation PropertiesBody PropertiesPin PropertiesModifying Simulation Models                                                                                                                        | 4-25<br>4-28<br>4-30<br>4-33<br>4-38<br>4-40<br>4-40<br>4-40<br>4-41<br>4-43<br>4-45<br>4-46    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

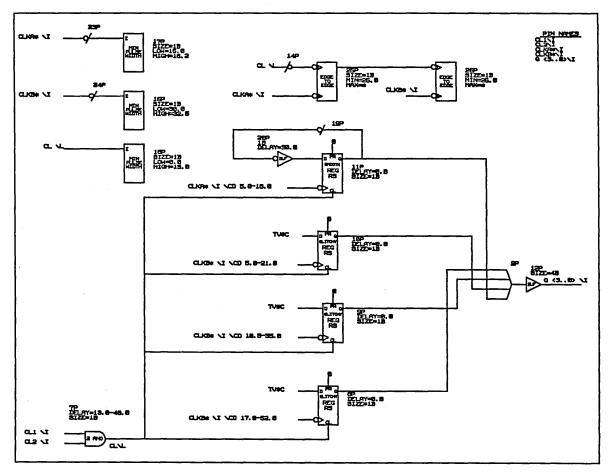

| The Timing Model                                                                                                                                                                                                                                                                                                                                                       | 5-1                                                                                             |

| Defining the Timing Model<br>Creating the Model: Checklist<br>The Timing Primitives<br>Bubbled Pins<br>Truth Table Abbreviations<br>Standard Function Primitives<br>Non-Standard Function Primitives<br>Error-Checking Primitives<br>Timing Properties<br>The DELAY Property<br>The RISE Property<br>The FALL Property<br>The SIZE Property<br>Modifying Timing Models | 5-2<br>5-3<br>5-6<br>5-7<br>5-8<br>5-22<br>5-27<br>5-31<br>5-32<br>5-32<br>5-33<br>5-33<br>5-34 |

| Creating Support Components                                                                                                                                                                                                                                                                                                                                            | 6-1                                                                                             |

| Creating A Connector<br>Creating a Second Version of the Connector<br>The .PART Drawing<br>The Physical Model<br>Creating Additional Physical Models<br>Creating a Connector Break<br>Using the Connector and Connector Break Bodies<br>Simulation and Timing Models                                                                                                   | 6-2<br>6-4<br>6-5<br>6-6<br>6-8<br>6-11<br>6-12<br>6-14                                         |

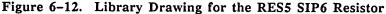

| Creating A Resistor Pack                                       | 6-15       |

|----------------------------------------------------------------|------------|

| The .PART Drawing                                              | 6-16       |

| The Physical Model                                             | 6-16       |

| Physical Part Tables                                           | 6–17       |

| Simulation and Timing Models                                   | 6–17       |

| Creating A Ground                                              | 6–18       |

| The .LOGIC Drawing                                             | 6–18       |

| Simulation and Timing Models                                   | 6–19       |

| Testing the Library                                            | 7–1        |

| Creation Checklist                                             | 7–2        |

| Testing Issues                                                 | 7–7        |

| Text File Method of Adding Physical Information<br>(UNIX Only) | A-1        |

| Using Phys_dat to Add Physical Information                     | A-2        |

| Phys dat Syntax                                                | A-2<br>A-5 |

| Pin Number Formats                                             | A-6        |

| Single Section Scalar Pins                                     | A-6        |

| Single Section Vector Pins                                     | A-7        |

| Multiple Section Scalar Pins                                   | A-7        |

| Multiple Section Common Pins                                   | A-8        |

| Multiple Section Common Vector Pins                            | A-10       |

| Asymmetrical Components                                        | A-11       |

| Changes in the Library Drawing Method                          | B-1        |

|                                                                |            |

| Previous versus Current Method                                 | B-2        |

| Reasons for the Change                                         | B-4        |

| Index                                                          | I–1        |

|                                                                |            |

# Library Fundamentals

T his section discusses:

- Library development process

- Library conventions

- Signal name syntax

- The library directory

- The master library file

- Library components

- Component versions

- Operating system considerations

- Maintaining libraries on foreign hosts

# The Library Development Process

Section 6 discusses creating support components.

There are several steps involved in creating a new library and new components. The section of this manual that contains further information on a procedure is noted beside each step.

| 1 | Build a body drawing. (Section      |                         |

|---|-------------------------------------|-------------------------|

| 2 | Create a physical model. (Section 3 |                         |

| 3 | Create a simulation model (if rec   | quired).<br>(Section 4) |

| 4 | Create a timing model (if require   | ed).<br>(Section 5)     |

| 5 | Test the components.                | (Section 7)             |

| 6 | Update the master library file.     | (Section 1)             |

When designing components, some decisions must be made about how to assign values that are not specified in the data sheets. The librarian must decide what values are to be used and then must maintain consistency for all components in the library. Such decisions should be documented in a file placed in the directory so that other users of the library can read them.

As a general rule, permissions on component models (body drawings, simulation models, and timing models) are set so that only the librarian or root has permission to change the models.

# Library Conventions and Syntax

Conventions

## Signal Name Syntax

Library conventions and syntax affect how model descriptions are entered for all libraries. The Valid libraries conform to the following conventions and syntax.

Conventions govern, to a large extent, the shape of bodies in the libraries and how signals are named. Conventions have far-reaching scope and affect all libraries and all designs made with those libraries. Global conventions must be decided on prior to purchase or installation. Many conventions are determined by corporate policy; others are determined by the user.

Signal names contain information about the signal condensed into a very short space. Library models use signal names to convey information and to correctly model parts. As a consequence, the designer must follow the same syntax used in the libraries.

Valid supports five different signal syntaxes. These are referred to as Library Formats 1 through 5. Only one syntax or library format can be used at a site.

Library Format 1 is the Valid standard library format. A signal name in Format 1 consists of five fields in the following order:

negation name subscript assertion general\_properties

For more information on signal syntax and a description of each Library Format, see the SCALD Language Reference Manual. The five library formats vary in four respects:

- The order of the five fields

- The bit ordering convention (left-to-right or right-to-left)

- The characters used to indicate low and high assertion

- The character or characters used to indicate a bit subrange

It is important to decide on a Library Format before on-site installation. The signal syntax in use at any given site is defined in the *config.dat* file. Table 1-1gives the location of this file on the various platforms.

| Table | 1-1. | Config.dat | File | Locations |

|-------|------|------------|------|-----------|

|-------|------|------------|------|-----------|

| Platform                             | File Location                    |  |

|--------------------------------------|----------------------------------|--|

| DECstation /usr/valid/lib/config.dat |                                  |  |

| PC AT                                | /u0/scald/config.dat             |  |

| SCALDsystem /u0/scald/config.dat     |                                  |  |

| Sun                                  | /usr/valid/lib/config.dat        |  |

| VAX                                  | SCALD\$ROOT:[LANGUAGE]CONFIG.DAT |  |

If the analysis programs are to run on a VAX mainframe, then an identical config.dat file must reside on the host. Signal syntax is often set by predefined company standards. If your company has no standard, we suggest you use the Valid standard library format (Library Format 1). Examples in the documentation assume Library Format 1 unless specified otherwise.

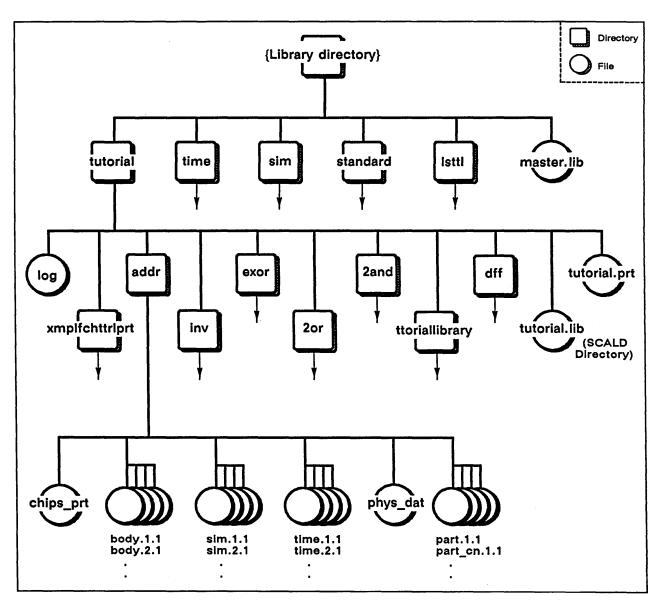

| Library<br>Organization  | A library consists of a main directory with subdirec-<br>tories for each component in the library. All of the<br>Valid-maintained libraries on your system have a<br>similar structure. Any library you create will also<br>have a similar structure. |  |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| The Library<br>Directory | All of the Valid-supplied libraries are installed in a single library directory. Table 1-2 defines the location of this directory on each of the Valid-supported systems.                                                                             |  |

| Table 1–2. Library Directory Locations | Table | 1-2. | Library | Directory | Locations |

|----------------------------------------|-------|------|---------|-----------|-----------|

|----------------------------------------|-------|------|---------|-----------|-----------|

| Directory Location      |

|-------------------------|

| /usr/valid/lib          |

| /u0/lib                 |

| /u0/lib                 |

| /usr/valid/lib          |

| SCALD\$ROOT:[LIBRARIES] |

|                         |

Figure 1–1 shows the structure of a typical Valid-supplied library directory.

Figure 1-1. Contents of a Typical Library Directory

When you list the contents of the library directory, you see the name of each Valid library installed on your system and a few other files and directories. A sample listing of the contents of the library directory is shown in Figure 1-2.

discrete master.lib standard time fast memory sttl tutorial lsttl sim phantom ttl

Figure 1-2. Contents of Sample Library Directory

Individual LibrariesEach individual library is stored in a directory bear-<br/>ing its name. For example, the tutorial library re-<br/>sides in the directory:<br/>/usr/valid/lib/tutorial

/u0/lib/tutorial

VAX: SCALD\$ROOT: [LIBRARIES] TUTORIAL. DIR

In addition to the subdirectories containing the component drawings, a library directory may contain these additional directories and files:

• Two reference drawing directories. The drawing called "EXAMPLE OF EACH ..." includes an example of *every* version of every part in the library. It is primarily for documentation purposes. The drawing is also useful for testing the models for the library since, when used in

SCALDsystem:

These drawing names are abbreviated within the operating system. a compilation, it invokes all versions of all of the parts.

The other reference drawing includes the *first* version of every part in the library. This drawing usually has the same name as the library (for example, the "TUTORIAL LIBRARY" drawing). It can be used for library development.

- A SCALD directory. The extension *.lib* is reserved for library SCALD directories (for example, *lsttl.lib*). This file contains the mapping between GED drawing names and their corresponding operating system directory names.

- A physical information file. The optional .prt file contains physical information about each part in the library. It may be used by the Packager and by the interface programs.

- A log file. Each library has a log file of all updates made to the library since its initial release. The log for Valid libraries is maintained by Valid personnel and is in reverse chronological order.

Figure 1–3 shows a listing of the contents of the tutorial library directory on the UNIX operating system. 2andexortutorial.lib2orinvtutorial.prtaddrlogxmplfchttrlprtdffttoriallibrary

Figure 1-3. Contents of the Tutorial Library (UNIX)

The names of the drawing files are not exactly the same as the GED drawing names because of operating system limitations. The algorithm used to create file names acceptable to the operating system:

- Removes any spaces or special characters

- Shortens the drawing name to a maximum of 14 characters by selectively eliminating characters (beginning with vowels)

- Makes each name unique

The GED name-to-operating system name mapping is done automatically by the SCALD directory file.

The master library file (*master.lib*) resides in the top library directory. It contains the name of each library on your system and the full path to that library. Adding a library entry to the *master.lib* file allows users to access that library.

The GED command **library** looks in the master library file for the full path to the specified library.

## The Master Library File

It is not necessary to update the master.lib file if you only change an existing library. For instance, listing the LSTTL library in the *master.lib* file allows you to enter the command:

library 1sttl

If there is no entry, you would have to enter the entire command line each time:

```

lib /usr/valid/lib/lsttl/lsttl.lib

```

A library can reside anywhere on the system as long as it is listed correctly in *master.lib*. When you have problems accessing a library, check the master library file and see if the library is listed.

The last thing you must do after you create and test a new library is to update the *master.lib* file. Use a text editor to access the file, and add an entry for the new library that lists the abbreviation for the library and the full path to the library.

Figure 1-4 shows a sample *master.lib* file on the Sun or DECstation system. The last entry adds the "userparts" library to the list of libraries that can be accessed on this system.

#### Figure 1-4. Sample Master.lib File

| Library Components | A <i>library component</i> consists of a collection of draw-<br>ings that together define the part. Within GED, each<br>drawing has the same name and a different exten-<br>sion. The drawing names in GED are:                                                                                                                                                                                                                                                          |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| component.BODY     | This drawing defines the shape, pins, and general<br>properties of the library component; it is the sym-<br>bolic representation of the part. When you add a<br>library part to a drawing, the .BODY drawing ap-<br>pears on the screen. The .BODY drawing may repre-<br>sent an actual physical component, or it may repre-<br>sent a block of logic.                                                                                                                   |

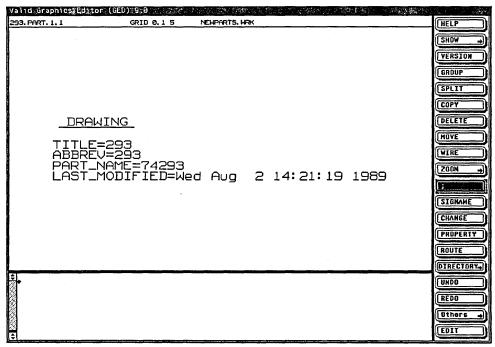

| component.PART     | The .PART drawing tells the Compiler that this com-<br>ponent (body) is a low-level drawing that is added<br>to logic drawings. This drawing contains a<br>DRAWING body and its attached properties that de-<br>fine the physical component name for the Packager.<br>When the Compiler compiles for "logic," it includes<br>the global part information from the .PART drawing<br>for each body on your drawing. This information is<br>then passed on to the Packager. |

| component.SIM      | This drawing defines the simulation model for the library component. When the Compiler compiles for "sim," it includes the corresponding simulation model contained in the .SIM drawing for each body on your drawing. This information is passed to the Logic Simulator.                                                                                                                                                                                                |

| component.TIME     | This drawing defines the timing model for the li-<br>brary part. When the Compiler compiles for<br>"time," it includes the corresponding timing model<br>contained in the TIME drawing for each body on                                                                                                                                                                                                                                                                  |

L

your drawing. This information is passed to the Timing Verifier to check the timing behavior of the entire design.

When you list the contents of a component directory, the drawing files appear as shown in Figure 1-5.

body.1.1 part\_bn.1.1 sim.1.1 time.1.1 body.2.1 part\_cn.1.1 sim\_bn.1.1 time\_cn.1.1 chips\_prt part\_dp.1.1 sim\_dp.1.1 time\_dp.1.1 part.1.1 phys\_dat

Figure 1-5. Contents of Sample Component Directory

#### **Additional Files**

Besides the four component drawings, a library component directory contains these additional files:

- A chips\_prt file. This file contains all the physical information for a component. The chips\_prt file is used by the Compiler and by the section and pinswap commands in GED. (It may also be used by the Packager.) It allows you to preassign pin numbers to a component during schematic creation.

- A *phys\_dat* file. This is an optional file used as input to a special program which can be used to create the *chips\_prt* files. This file appears in some Valid libraries; these libraries may use a different procedure for modify-

If disk space at your site is at a premium, the binary files can be deleted. GED can recreate any drawing from the ASCII version of the files.

There are some exceptions that require a logic drawing in a component directory. ing physical information than do libraries without *phys\_dat* files. See Appendix A for additional information on *phys\_dat* files.

- The binary files (*part\_bn.1.1*, *sim\_bn.1.1*, *time\_bn.1.1*). These files contain the same information as the ASCII version of the drawings, stored in a slightly different format.

- The connectivity files (*part\_cn.1.1, sim\_cn.1.1, time\_cn.1.1*). These files contain the logical net lists for the Packager, Simulator, and Timing Verifier.

- The dependency files (*part\_dp.1.1, sim\_dp.1.1, time\_dp.1.1*). These files list each part used in the drawing and its library directory. This file is used by the GED **update** facility to ensure that the parts in the drawing are current.

Notice that there is no .LOGIC drawing in the component directory. Library components do not normally have logic drawings because components are the lowest-level drawings that are added to logic drawings. In flat designs, logic drawings are made up entirely of library components connected together. In hierarchical designs, logic drawings can be made up of library components and symbols representing other logic drawings connected together.

## **Component Versions**

If a version is not specified, drawing version 1 is used by default.

The version number for a logic drawing should always be "1." The page number for a .BODY drawing should always be "1." Many library parts have more than one body drawing to represent a part. Each of these body drawings is called a *version*. The *version number* is defined by the first digit following the drawing name extension (the third field in the name). The **version** command in GED selects which version of a part is used.

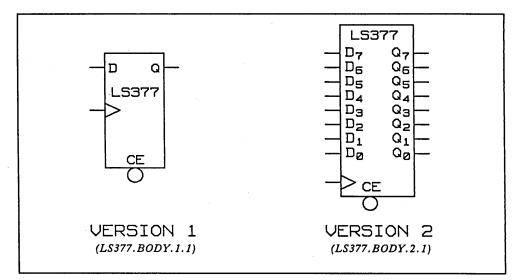

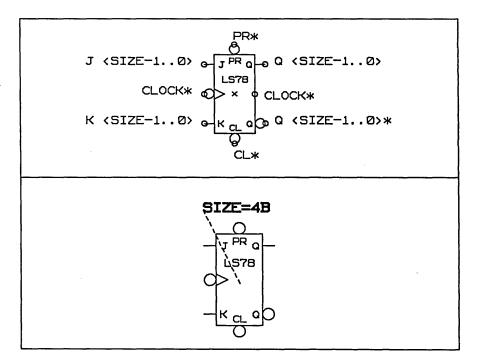

For example, there are two versions of the LS377 part in the LSTTL library: LS377.BODY.1.1 and LS377.BODY.2.1. Figure 1–6 shows the two versions of the LS377 component.

Figure 1-6. LS377 Versions 1 and 2

This is Valid's convention for defining body versions. You are not restricted to these conventions. The Version 1 body drawing usually shows just one representative section of a package. The Version 2 body drawing typically shows all of the sections. (In the case of a simple gate, the second version usually shows the DeMorgan equivalent of the gate.) The Version 1 Drawing

For more information on the SIZE property, see Section 2.

The Version 2 Drawing

See the PIN\_NUMBER portion of Section 3 for more information on asymmetrical components. Because all sections of the LS377 are identical to each other, the Version 1 body can be used to represent:

- One section of a package

- Many sections of one or several LS377 packages

The Version 1 drawing of the LS377 is called a *sizeable* body. The drawing can be used to represent multiple sections by using vectored signal names and attaching the SIZE property to the drawing (after it has been added to a GED logic schematic).

The Version 2 drawing of the LS377 more closely resembles the physical package of an LS377. The LS377 package contains eight identical sections, and the Version 2 drawing shows eight input pins and eight output pins. The Version 2 drawing is used for flat designs.

In most cases, the two body versions must have equivalent pin names. An exception to this rule occurs in parts with asymmetrical sections. In this case the versions of the part that represent the different sections must have no identical pin names, so that the different sections can be distinguished. Additionally, there must be a property attached to each section identifying the section. The Valid convention is to name this property "section" and to give the property a value that identifies the section number of the part to which the body corresponds.

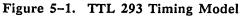

Some simple logic gates have versions (the DeMorgan equivalents) that represent the two different logical functions performed by the gate depending on the polarity of the input signal. An LS08, for example, performs an AND of high-asserted signals or an OR of low-asserted signals. The versions of the LS08 allow the designer to add either form of the gate to a drawing.

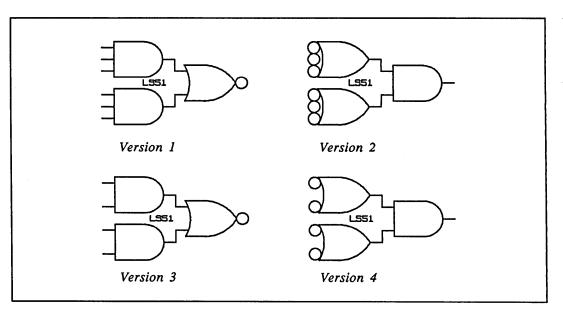

If a part has sections that are not interchangeable (such as the LS51), then there are additional versions that describe the additional sections. Figure 1-7 shows the different sections of the LS51 component.

Figure 1-7. The LS51 Asymmetrical Component

# Library Maintenance

## Operating System Considerations

#### **Disk Space**

Table 1-2 on page 1-5 lists the library directory for each system.

UNIX/ULTRIX:

VMS:

UNIX/ULTRIX:

VMS:

The System Librarian must be very familiar with the SCALD system, the SCALD Language, and logic design. The librarian also needs to be reasonably conversant with the host's operating system and text editor. Maintaining libraries requires considerable caution since an error in a library affects many users and many designs (including completed designs).

There are two important issues to consider for libraries: disk space and file protection.

All libraries are stored in the library directory. There must be enough space in the directory for the libraries plus enough space left over for the users. For Valid-supplied libraries, the library space requirements are indicated in the individual library descriptions.

To determine the amount of space required for a user-created library:

- **1** Change directories to the library in question.

- **2** Determine how much directory space is used:

du -s

DIRECTORY/SIZE/GRAND\_TOTAL [...]

**3** Determine the amount of free space on the disk:

df

SHOW DEVICE DUA0

The amount of disk space required varies depending on the size and complexity of a user's designs.

Protection

UNIX/ULTRIX: VMS:

UNIX/ULTRIX: VMS:

Files: Subdirectories: The disk usage commands show the number of free blocks on /u0 or /usr and DUA0, respectively. Leave enough disk space for users to work with after the libraries are installed. If installing a given library results in fewer than 1000 free blocks, you should either remove some files from /u0, /usr, or DUA0, not install the library, or acquire more disk space.

The libraries and their directories should be writeprotected for everyone except the librarian. The files in the library should be owned by lib or system. Check library ownership by typing:

ls -1

DIRECTORY/OWNER/PROTECTION

If there are any files not owned by lib or system, you can fix this by logging on as root or system, changing your directory to the library in question, and typing:

find . -exec chown lib {} \;

SET DIRECTORY/OWNER=SYSTEM

In VMS, respond to the "Directory" prompt with:

[...]

The *ls* –*l* and *DIRECTORY/OWNER/PROTECTION* commands also show the permissions of all of the subdirectories and files in the library directory.

With UNIX/ULTRIX systems, the correct permissions should be:

-rw-r--r-drwxr-xr-x This protection allows the user (which should be lib) to read and write the files, but allows everyone else only to read the files (UNIX/ULTRIX directories must have execute permission set in order to look inside the directory). If either the "group" or "other" write permissions or both are set (for example, -rw-rw-r-- or -rw-r--rw-), write permission should be removed by logging in as lib (since "lib" owns all the files), changing your directory to the library in question, and typing:

find . -exec chmod go-w {} \\^;

With VMS workstations, the correct permissions should be:

## RWED,RWED,R,R

#### RWED, RWED, RE, RE

With these protections, only the system and owner can read and write files; everyone else only can read the files. If either the "group" or "world" write or delete permissions are set (for example, RWED,RWED,RWE,RW), change the permission by logging in as system and typing:

SET PROTECTION=(G:R,W:G) \*.DIR/LOG

If you work on a foreign host such as a VAX mainframe, keep a copy of the libraries on this machine. Otherwise each user must keep a private version of the libraries, which wastes disk space. These libraries should be kept in a read-only directory.

Files: Subdirectories:

## Maintaining Libraries on a Foreign Host

See the filecopy utility in the System Utilities Reference Manual for details. To copy libraries to or from the foreign host, use the *filecopy* utility. You should run *filecopy* without a *transfer.log* file when copying libraries to ensure that all libraries are on the host. The transfer takes several minutes.

On the VAX mainframe, each library is stored in a directory under [SCALD.LIBRARIES]. Before you transfer the libraries, log in to the VAX and create a directory for each library you want to transfer.

For example, for a library named *biblio*, create the directory [SCALD.LIBRARIES.BIBLIO] on the VAX. The *filecopy.cmd* file would include the following directives:

```

report_files on;

copy_file `biblio.prt';

directory `biblio.lib';

host_kind VMS;

host_destination `/dev/vms/scald/libraries/biblio';

end.

```

Figure 1-8. Sample Filecopy.cmd File

Once the command file is set up, run the filecopy utility to copy all necessary information to the VAX.

# **Component Creation**

This section discusses:

- Creating a library

- Creating a new component drawing

- Creating the body shape

- Drawing pins

- Adding pin names

- Annotating pins

- Attaching properties to the body

- Building other body versions

- Borrowing library parts

# Basic Procedure (Checklist)

Creating a body involves the following steps:

- **1** Create a new library.

- **2** Create the new component drawing.

- **3** Create the body shape.

- 4 Add pins to the body.

- **5** Attach pin names to the pins.

- 6 Annotate the pins (using the GED note command).

- 7 Attach properties to the body.

- 8 Build other body versions.

Each of these steps is detailed in this section.

Throughout these procedures, there are creation standards included for your information. These are the standards used to create all of the Valid libraries; they are the suggested standards for creating your own libraries.

## Creating A Library

The first step in developing a new library is to create a directory for the new library where you can store any parts you create. Since any change made to a Valid library is overwritten when that library is updated, you should also create a library of your own if you must modify an existing library part. Keeping new parts in a special library means your Valid libraries can be updated without losing data.

To create a new library on a UNIX or ULTRIX system, log in as user lib. By default the librarian's working directory is lu0/lib on the SCALDsystem and PC AT or lusr/valid/lib on the DECstation and Sun workstation.

To prevent access to new components until they are ready for distribution, create a permanent test directory under the *lib* directory. Use this directory to and test all new components. Do not enter the test directory name in the master library file. When the components are complete, copy the component directory tree, place the component in the correct library, and enter the new library name in the master library file.

To create new libraries on a VMS system, log in under your own user name. A library can be created under any user account and later moved to the *SCALD\$ROOT*:[*LIBRARIES*] directory (although the file permissions and ownership will have to be changed to user lib). Throughout this manual, a UNIX library named newparts (which is located under user lib) is used as a sample library. Follow these steps to create the *newparts* library: **1** Log in as user lib. 2 From the *lusr/valid/lib* directory, create the new library subdirectory: mkdir newparts **3** Copy the default GED files (\*.cmd and startup.ged) from a user directory into the new directory. **4** Move to the new directory: cd newparts 5 Edit the startup.ged file: vi startup.ged 6 Change the "use" line to read: use newparts.wrk 7 Delete the "masterlibrary" line.

8 Add a library command line for each existing library you might need to create the new library:

```

library lsttl

library ttl

```

- **9** Save the *startup.ged* file and exit the text editor.

- **10** Use the text editor to change the name of your SCALD directory in the .*cmd* files to the new directory name:

directory 'newparts.wrk';

Т

\_\_\_\_\_

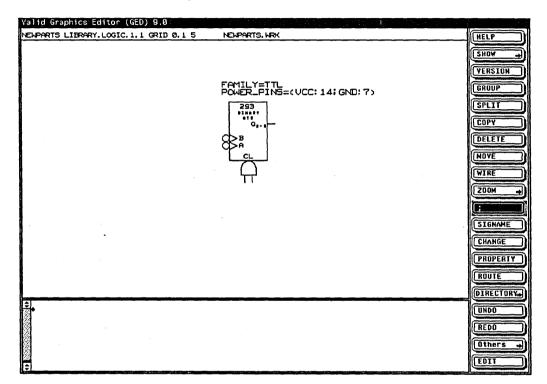

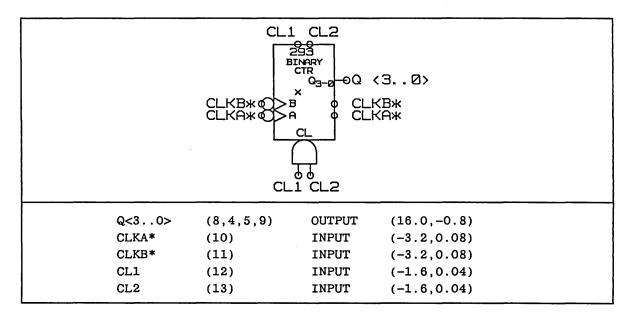

| Creating a New<br>Component<br>Drawing | Because the TTL 293 binary counter component is<br>not included in the Valid library release, it is used as<br>an example throughout this manual to demonstrate<br>the process of adding a new component to your<br>library.                                                                                           |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                        | To create a new component drawing, you must:                                                                                                                                                                                                                                                                           |

|                                        | • Edit the .BODY drawing                                                                                                                                                                                                                                                                                               |

|                                        | • Move the body name away from the origin                                                                                                                                                                                                                                                                              |

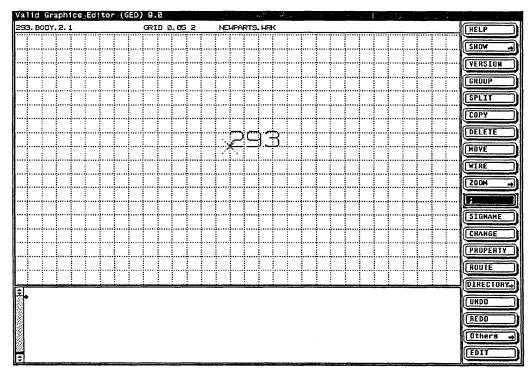

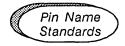

| Editing the .BODY<br>Drawing           | To create a new component called 293, use GED to<br>edit a new drawing called 293.body.2.1. Make sure<br>you add the .body.2.1 extension; if you do not, the<br>default drawing type is .logic and the default version<br>and page number reference is .1.1.                                                           |

|                                        | Version 2 of a body is the "flat" version; that is, it<br>has all pins explicitly marked. Version 1 of a body<br>is <i>vectored</i> , with multiple-bit input and output pins.<br>By building Version 2 first, you can more easily see<br>the relationship between the component logic and<br>the body representation. |

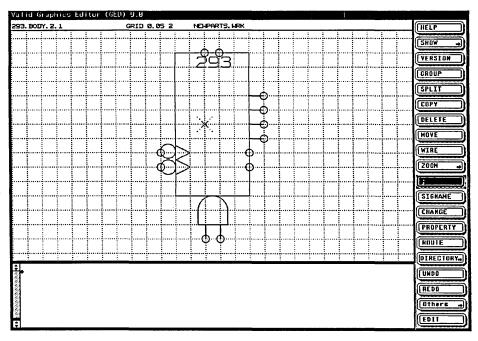

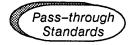

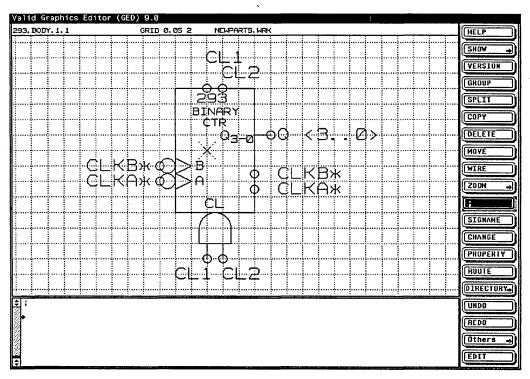

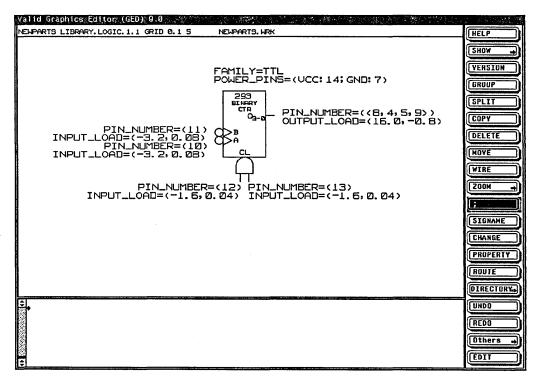

|                                        | When you edit 293.body.2.1, the screen shows a body grid setting, the body name, and a small X (the body origin) in the center of the screen.                                                                                                                                                                          |

|                                        |                                                                                                                                                                                                                                                                                                                        |

Figure 2-1. Editing The TTL Body

- ✓ When you edit a .BODY drawing, the grid is set automatically to 0.05 2. This means there is one-tenth of an inch (0.1 inch) between displayed grid lines. Always use this grid setting when creating the body shape.

- Notes and connections to slanted lines (such as occur on select inputs of multiplexers, for example) can be placed on a grid of 0.01 10 if necessary. Do not use any other grid settings when creating bodies.

### Moving the Body Name

#### Shortening a Body Name

If you change the size of the note, it should still conforms to the suggested Valid standards. The body name, 293, is a note that you can use to label the component body. Be sure to include the component name on the body. The **split** command lets you move the body name note away from the body origin (the small X that appears at 0,0).

To separate the body name and the body origin:

- **1** Select the **split** command from the GED menu.

- **2** Use the right mouse button to select the object to move.

Do not move the body origin; if you do, the editor produces an error message when the body is written and moves the origin back to the center. If your first button click makes the origin move, just click again to select the body name.

- **3** Move the note to the top of the screen and place it down.

- The origin body is used to specify the origin of the body. All body properties are attached to the origin body, and the body should be symmetrical about the origin (the origin should be at the center of the body).

In some cases, you may have a body name that does not easily "fit" into the shape of the body. If you wish to shorten the body name on a drawing, you can use the GED command **change** to shorten the body name note or the **display** command to change the size of the body name note to fit within the body shape.

## Creating the Body Shape

Note that the TTL 293 is not centered horizontally around the origin but that the body falls directly on the major grid intervals. Using GED, you can make a body any size and shape you want: round, oval, trapezoidal, rectangular. For consistency, the body shape should match the body function. Follow the component representation in the appropriate data book or use another Valid library component to model the shape of the body. In order for a body to integrate well with existing libraries, it should be approximately the same size as other library parts. When bodies are made a standard size and labeled in a consistent manner, schematics are easier to draw and maintain.

To create the shape of the TTL 293 body, use the **wire** command to draw a rectangle 10 squares long by 5 squares wide. Center the rectangle around the body origin as much as possible while still keeping the body shap on-grid. The basic shape of the TTL 293 component is shown in Figure 2–2.

| 293 | BOI | Y. 2  | 1 |          | <br> | GRI | DØ.   | 05 2  | 2 | NE       | PAR | TS. N | RK |        |          |   |       |       | ,      |   |          |   |          | HELP      |

|-----|-----|-------|---|----------|------|-----|-------|-------|---|----------|-----|-------|----|--------|----------|---|-------|-------|--------|---|----------|---|----------|-----------|

| 1   |     |       |   |          |      |     |       |       |   |          |     |       |    |        |          |   |       |       |        |   |          |   |          | SHOW .    |

| -   |     | ••••• |   | ••••••   | <br> |     | ••••• |       |   |          |     |       |    | •••••• |          |   |       |       | •••••  |   |          |   |          | VERSION   |

|     |     |       |   |          | <br> |     | ••••• |       |   | 7        | ba  | ন     | _  |        |          |   |       |       | •••••  |   |          |   |          | GROUP     |

| "   |     |       |   |          |      |     | ••••• | ••••• |   | <b>c</b> |     | .ب    |    |        |          |   |       |       |        |   |          |   |          | SPLIT     |

|     |     |       |   |          | <br> |     | ••••  | ••••• |   |          |     |       |    |        |          |   | ••••• |       |        |   | ·····    |   |          | COPY      |

|     |     |       |   |          | <br> |     | ••••• |       |   |          |     |       |    |        | <b> </b> |   |       |       |        |   |          |   |          | DELETE    |

|     |     |       |   |          |      |     | ••••• | ••••• |   | •.       |     |       |    |        |          |   | 1     |       |        |   | 1        |   |          | MOVE      |

|     |     |       |   |          |      |     |       |       |   | ~?       | Κ   |       |    |        |          |   |       |       |        |   |          |   |          | WIRE      |

|     |     |       |   |          |      |     |       |       |   |          |     |       |    | 1      | [<br>    |   |       |       |        |   | <br>     |   |          | Z00M .    |

|     |     |       | - | 1        |      |     |       |       |   |          |     | 1     |    |        | 1        | 1 |       |       |        |   | <u> </u> | [ |          |           |

|     |     |       |   |          |      |     |       |       |   |          |     |       |    | 1      | 1        |   | -     |       |        |   | Î        | 1 |          | SIGNANE   |

|     |     |       |   | -        |      |     |       |       | [ | [<br>    |     |       |    | 1      | Ţ        |   | Ī     |       | [<br>[ |   | Ī        | Ĩ |          | CHANGE    |

|     |     |       |   |          |      |     |       |       |   |          |     |       |    |        |          |   | -     | 1     |        |   | Î        | 1 |          | PROPERTY  |

|     |     |       |   |          |      |     |       |       |   |          |     |       |    |        | 1        | 1 |       | [<br> |        | 1 | Î        | 1 |          | ROUTE     |

| ŧ.  |     |       | · | <u>.</u> | <br> |     |       |       |   |          |     |       |    |        |          |   |       |       |        |   |          |   | <u> </u> | DIRECTORY |

|     |     |       |   |          |      |     |       |       |   |          |     |       |    |        |          |   |       |       |        |   |          |   |          | UNDO      |

|     |     |       |   |          |      |     |       |       |   |          |     |       |    |        |          |   |       |       |        |   |          |   |          | REDO      |

|     |     |       |   |          |      |     |       |       |   |          |     |       |    |        |          |   |       |       |        |   |          |   |          | Uthers    |

Figure 2-2. The TTL 293 Body Shape

- The shape of the body should reflect (wherever possible) the function of the body.

- The size and shape of the body depend on the number of input and output pins required on the body drawing.

- $\nu$  The body should be symmetrical about the body origin.

- Bodies should be made as small as possible but not crowded. Follow the sizes of existing bodies in other libraries. Make flip-flops 0.4 by 0.8 inches. Make gates 0.3 by 0.6 inches.

## **Drawing Pins**

The circle has a 0.1-inch diameter.

You can also use the copy command to create multiple wire stubs.

The following pin conventions are used in all Validsupplied libraries:

- High-asserted pins are shown with a wire stub.

- Low-asserted pins are shown with a circle.

Follow these steps to add pins to the TTL 293 body:

- 1 Use the circle command to add two lowasserted clock pins to the left side of the body. Place the first point of the circle halfway between the first grid interval and the body edge. Place the second point of the circle on the body edge.

- 2 Use the wire command to add four highasserted pins to the right side of the body. Start each wire at the body edge and extend it one grid interval out from the body.

- **3** Use the **arc** and **wire** commands to draw an AND gate at the bottom of the body. Place the first arc point one grid interval below the body and halfway between the second and third vertical grid intersections. Place the second arc point along the same horizontal grid interval and halfway between the third and fourth grid intersections. Place the third grid point at the bottom edge of the body halfway between the first and second grid intersections. Use the **wire** command to complete the gate and to add wire stubs to the bottom of the gate.

#### **Component Creation**

Dots can be open or filled. Use set dots\_open or set dots\_filled to change the default.

The pass-through clock pins are along the right side of the body. The pass-through clear pins are across the top of the body 4 Use the dot command to add a dot at the end of each circle and wire stub. This dot tells GED that this is a pin and that wires can be attached to it and connections made. The dot does not show up on the body when you add the component to a logic drawing in GED.

Remember to add the connection dots to the pass-through clock and clear pins.

**5** Use the wire command and diagonal wires to add the clock wedges to the body.

6 Write the drawing to save it.

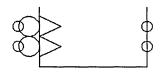

The TTL 293 body now looks like the one in Figure 2-3.

Figure 2-3. The TTL 293 Body and Pins

Pin Standards

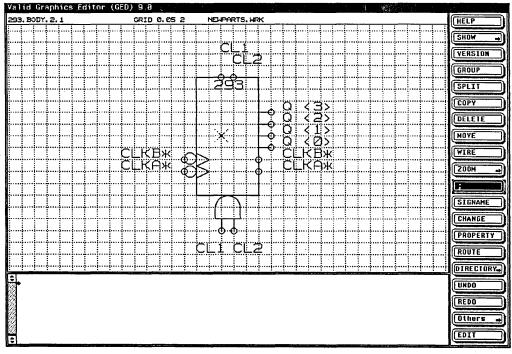

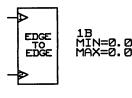

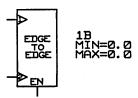

#### Pass-through Pins

Pass-through clock pins

- Place input pins on the left and output pins on the right. Place enable and select pins on the bottom. Place bidirectional pins on either side, usually on the right.

- ✓ Connect all pins to the body with either a 0.1-inch stub (made with a wire), or a bubble (0.1-inch circle), or, if the pin is bubbleable, with both a pin and a bubble (see page 2-15).

- Mark edge-triggered clock pins with a clock wedge 0.1-inch wide and 0.1-inch long. Use the white (center) button to draw the diagonal lines.

- Add pass-through pins wherever possible, especially on clocks, enable, and select lines. Do not add stubs or bubbles to pass-through pins.

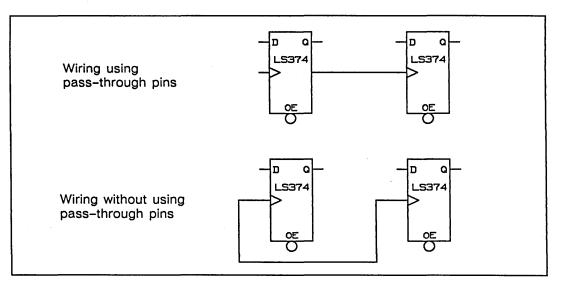

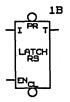

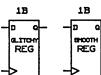

*Pass-through* (or feed-through or bus-through) pins are special "shortcut" pins placed on a body to make it easier to wire a group of bodies together. Many of the components in the Valid libraries are provided with pass-through pins on their clock signals. The pass-through pin is exactly opposite the clock signal. It lets you easily wire the clock signals of several library parts together.

Pass-through pins always appear on the .BODY drawing of the library part, although they are invisible when you add the body to a GED drawing.

For example, if you want to wire the clock signals of two LS374 components together, the pass-through pins allow you to wire in a direct line between components. Without the pass-through pins, the wire would have to jog around the first component to connect to the second component. Figure 2-4 shows two LS374 components wired using the passthrough clock pins and two LS374 components wired without using the pass-through pins.

Figure 2-4. Using Pass-through Pins

- Pass-through pins are always exactly opposite the visible pin to which they are logically connected.

- ✓ The pin names of the visible and the invisible pin must be the same. Identical pin names allow GED to interpret a wire connected to the pass-through pin as also being connected to the clock input pin.

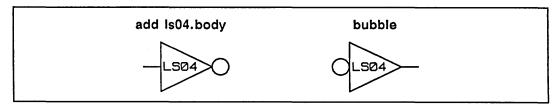

#### **Bubbled Pins**

A bubbleable pin

✓ A pass-through pin never has a bubble, even if the pin it is associated with has a bubble.

GED knows that pins of the same name are the same pin, and if one of them is bubbled, the other must be. This guarantees that correct bubble checking is performed even for passthrough connections.

When defining a pass-through pin, make sure that the pin it is associated with is obvious. In Valid libraries, this is done strictly by its position on the body, not by the use of a note.

The GED **bubble** command replaces the wire stub of a pin on a body with a bubble that represents a lowasserted signal. You must decide which pins can be bubbled.

Since a circle indicates a low-asserted pin and a stub indicates a high-asserted pin, a bubbleable pin has both a stub and a circle. The length of the stub is the diameter of the circle. The connection point (marked by a dot) is at the far end of the stub, where the stub and circle meet.

To use bubbled pins in GED, you must attach the BUBBLED property to the body. For more information on the BUBBLED property, see page 2–29.

## Adding Pin Names

You can use the text justification commands (SET LEFT, SET RIGHT, SET CENTER) to align the pin numbers. The following conventions are used for pin names of parts in the Valid-supplied libraries:

- All pin names are based on the names in the relevant data books.

- On parts having multiple sections, the pin names carry a numerical suffix to distinguish among the sections (the bit subscript).

- Low-asserted pin names end with an asterisk character (\*).

Use the **signame** command to add pin names to the TTL 293 drawing. Add the names as shown in Figure 2-5.

Figure 2-5. The TTL 293 Pin Names

## Adding Properties to Pin Names

Use the **show attachments** command to ensure that all pin names are properly attached.

- The pin names on a body must correspond exactly to those on the logic, timing, and simulation drawings associated with the body.

- ✓ Use the signame command to give the passthrough pin the same name as the parent pin.

- ✓ For gates, letter the input pins as found in the data books, or alphabetically. Letter the output pins as found in the data books, or use Y.

- The pipe character (|) is not allowed in pin names. This is to facilitate the syntax of the BUBBLE\_GROUP property.

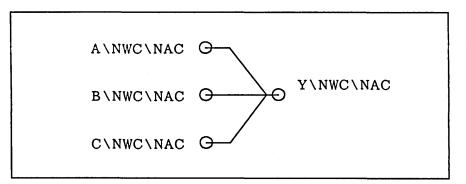

There are two general properties that you can attach to pins when you enter the pin names:

- \NAC

- \NWC

These properties are only used on body drawings. They are not required in the corresponding timing and simulation models or logic drawings.

#### **NAC Property**

The backslash is the general property prefix character.

#### **NWC** Property

NAC stands for "no assertion check." NAC allows a signal of either assertion to be connected to a pin. The Compiler assigns the assertion of the first signal connected to the pin as the pin's assertion. This forces any other signals connected to that pin to have the same assertion as the first signal. The NAC property is used when the assertion level of signals is not important, but all the signals must be compatible.

NWC stands for "no width check." This property is used when the width (in bits) of a pin is not known or when it is desired that signals of any width may be connected to the pin. The Compiler determines the actual bit width from the context in which the NWC property is used.

Figure 2–6 shows a sample merge body that carries both the \NAC and \NWC properties.

#### Figure 2-6. The \NAC and \NWC Properties

## Annotating Bodies

Notes on pins are important since pin names do not appear when bodies are added to logic drawings.

You can use a grid setting of .01 10 if necessary for better placement. Be sure to set the grid spacing back to .05 2 after placing notes. A body should be annotated with:

- The component name

- The pin names

- Any other important information

Annotation makes the function of the body and each pin clear. The notes should be easily readable and should not be crowded. Follow these steps to annotate the TTL 293 body:

- 1 Use the note command and the notes shown in Figure 2-7. Center the notes on the pins *inside* the body and as close to the edge of the body as possible.

- 2 After placing the notes, make them smaller to minimize crowding. Use the **display** command to resize the notes as follows:

display .8: All Q pins The CL pin Pin A Pin B

- display .6: Bit subscripts 0, 1, 2, 3 The words BINARY CTR

- **3** Once the pins are the correct size, use the **move** command to realign the notes.

The TTL 293 body now looks like the one in Figure 2–7.

| Val          | ۱d   | Gra        | ph    | ics   | E     | dit     | or   | -(       | GE                                     | D)       | 9        | 0        |          |       |      |         |      |        | 27       |          |          |     | 1.       | <i>.</i> |            |                                        |     |          | Ċ.       |      |    | 2<br>1. j. | d.       |            | .Sk- | .*:   | 60       | ta/      | ÷., | 1          | ·            | :<br> |    |       |      |     |

|--------------|------|------------|-------|-------|-------|---------|------|----------|----------------------------------------|----------|----------|----------|----------|-------|------|---------|------|--------|----------|----------|----------|-----|----------|----------|------------|----------------------------------------|-----|----------|----------|------|----|------------|----------|------------|------|-------|----------|----------|-----|------------|--------------|-------|----|-------|------|-----|

| 293          | . во | <u>דים</u> | 2. :  | 1     |       |         |      | -        |                                        |          | GRI      | D        | ø.       | Ø     | ; 2  | 2       |      | _      | E        | NP       | ÷Ŗ1      | s.  | WR       | ĸ        |            |                                        |     |          |          |      | _, |            |          |            |      |       | _        |          |     |            |              | _     | 1  | HELP  |      | J   |

| į            |      | ····÷      | ····  |       |       |         | ļ    | <b>.</b> |                                        |          | ••••     | <u> </u> | ÷        | ÷     | •••• | ····    |      |        |          | ÷        |          | +   | ••••     | <b>.</b> | ·+         |                                        |     |          | ÷        | ·    |    | ••••       | ļ        | . <b>!</b> |      | ••••  |          | ļ        | ÷   | <b>.</b>   |              |       |    | SHOW  |      | ลึ  |

|              |      | ····•      |       | ••••  |       |         | ļ    | ļ        |                                        |          |          | Ļ        | ÷        |       | •••• | ļ       |      | ••••   |          |          | ηį.      | ÷   |          |          | ·          |                                        |     |          | ÷        |      | {  | ••••       | ļ        | . <b>.</b> |      |       |          | ļ        | ÷   |            |              | ‡     |    |       | -    | 2   |

| · · · · ·    |      | ····‡      | ····‡ | ••••• |       |         | ļ    | +        | ÷                                      |          | ••••     | <b>!</b> | <b>.</b> | ÷     |      | ····    | ÷    | ••••   | · ·      | <u>-</u> | ř        | ÷   | ·- ,4    | <u>.</u> | · <b>¦</b> | ÷                                      |     |          | ÷        | ÷    |    | ••••       | <b>¦</b> | ÷.         | ÷    | ••••  |          | ļ        | ÷   | - <b>-</b> | -+-          | ‡     | U  | VERST | ON   | J   |

|              | j.   |            | }     |       |       |         | ļ    | į        |                                        |          |          | ÷        | ÷        |       | •••• | ····    |      |        |          |          | <u>}</u> | 2Ę  | -2       | F        | ·          | <b>.</b>                               |     |          | ķ.       |      |    | ••••       | ļ        | ·[         |      | ••••  |          | į        | ÷   |            |              |       | 1  | GROUP |      | ñ   |

|              |      | ····÷      |       |       |       |         | ļ    | ÷        |                                        |          |          | ÷        | ÷        | ÷     | •••• | ····    | ÷    | -      | -        | ģ,       | \$       | ÷   | -        | i        | •          | ÷                                      |     |          | ÷        | ·+·  |    | ••••       | ÷        | - <u> </u> |      | ••••  |          | ļ        | ÷   | ·          | - <b>i</b> - |       |    | COLT  | -    | ñ   |

|              |      |            |       |       |       |         | ŀ    | +        | ÷                                      | ••••     | ••••     | ÷        | ÷        | ÷     |      | ····    | ··   | ••••   | B        | ĪN       |          |     | •••••    |          | •          |                                        |     |          | ÷        | •••• |    | • • • •    | <u> </u> | ·•••       | -+   |       |          | ļ        | ÷   | - <b>-</b> |              |       | Ľ  | SPLIT |      | ĩ   |

|              | ÷    |            | ····• | ••••  |       |         | ŀ    | ÷        | ÷                                      |          | ••••     | ÷        | ÷        | ÷     | •••• | ····    | - f- | ••••   |          | C٦       | Q.P.     |     | ••••     | ŀ        | · • · ·    | ۰'n                                    | Ϋ́  |          | Ż        | Ξ.   | ςİ | ••••       | ÷        | ÷          | ÷    | ••••• |          | <u>.</u> | ÷   | ÷          |              |       | l  | COPY  |      | ]   |

| ·····        |      | ····÷      |       |       | ••••• |         |      | +        | ÷                                      | ••••     | ••••     | ÷…       | ÷        | -     | •••• | <u></u> | ۰ŀ   |        | ••••     | ÷        |          | ۵÷  |          | ⊢        | ÷          | 2                                      | ŝ   |          | à?       | ಶ    | 5  | ••••       | ÷…       | ÷          | -+   |       |          |          | ÷   | ·†··       | -+-          | +     | ſ  | DELET | E    | ົ້າ |

| ·····        |      | ····†      |       |       |       |         | t    |          | ÷                                      |          | ••••     | †•••     | ÷        | -     | •••• | ·       | ··ŀ· |        |          | Ť.       |          | Qż  |          | ⊢        | ę٠         | ** ? 2                                 | Ś   |          | 2.1      | T.   | 5  | ••••       | ÷        | 1          | -+   |       |          |          | ÷   | ÷          | -            |       | ľ  |       |      | 3   |

| •••••        |      |            |       |       | ••••• | •••••   | •••• | ÷        |                                        |          | ••••     | ÷        | ÷        |       | •••• | ÷       | ۰ŀ   |        |          | ×        |          | Q   |          | ⊢        | ÷          | ÷۳                                     | 5   |          | 2 i      | 3    | ŝ  | ••••       | ÷        | ÷          |      | ••••• |          |          | ·÷  | · • • •    | -            |       | ľ  | MOVE  | _    | J   |

| •••••        |      | ····†      |       |       |       |         |      | ÷        | 'n.                                    | $\gamma$ | T.       | Ż١       | Ż        | ic.   | •••• |         | Ľ    |        | ••••     | ÷        |          | Qę  | <b>3</b> | ┝─       | ÷          | ٣ř                                     | Ĩ   | ۳ï       | Ż        | Ř    | ж  | ••••       | ÷        | · [··      | ÷    | ••••  |          |          | ÷   | ·†··       | •            |       | 1  | WIRE  |      | וכ  |

| ·            |      |            |       |       | ••••  | ••••    | ·    |          | ~````````````````````````````````````` | ٣Ì       | _}<br>_} | ĈŻ       | 5        | ĸ     | •••• | ٤       | = 2  | $\geq$ | ŀ٩       | •        | ÷        |     | ••••     | p۰       | ·†···      | ~````````````````````````````````````` | ីរ៉ | Π        | ĈΪ       | Å.   | ж  | ••••       | ţ        | 1          |      | ••••  | ·        | !        | ÷   | 1          | -            |       | 1  | 2000  |      | ลั  |

|              |      | ····†      |       | ••••  |       | İ       | t    | t        | -1                                     |          |          | Ť.       | Ť        | -     | •••• | ¢       | X    | $\geq$ | Ð        | }        | -        | ÷   |          | ₽…       | ÷          | -1                                     |     |          | Ť        | Ť    |    | ••••       | t        | · • •      | 1    | ••••  |          |          | ÷   | ÷.         | 1            | ···†  | Ľ  |       | _    | ್ಷ  |

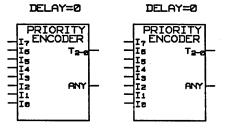

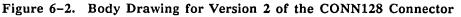

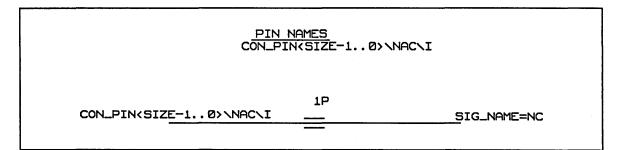

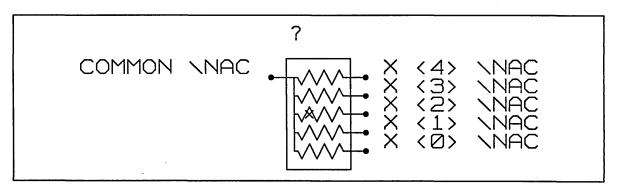

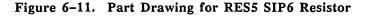

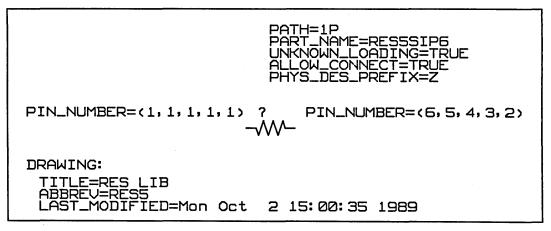

|              |      |            |       | ••••  |       | ····    | 1    | 1        | -                                      |          |          | †…       | Ť        | -     | •••• | †       | ۰ŀ   | ••••   | ••••     | Ċ        | Ė        | ÷   | ••••     | ŀ        | 1          | 1                                      |     |          | ÷        | - t  |    |            | t.       | ÷          |      | ••••  |          |          | 1   | 1          | -            |       |    | :     |      | J   |