|        |                 | COD   | SYM   |                             |                                                                                                                  | SCRIPTIO                |                 | in a furth and an Article State States | T          | APPROVED                                                                                                        | DA              |

|--------|-----------------|-------|-------|-----------------------------|------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------|----------------------------------------|------------|-----------------------------------------------------------------------------------------------------------------|-----------------|

| •      |                 | P     |       |                             | TION RELEA                                                                                                       |                         |                 | 80271                                  |            | here                                                                                                            | 1.7             |

|        | 767             |       |       |                             | ED PER E                                                                                                         |                         |                 |                                        | ť          | 2007                                                                                                            | ₩/"/<br>        |

| _      | <b>98A</b> 0767 |       |       |                             |                                                                                                                  |                         |                 |                                        |            | RO                                                                                                              | 3/22            |

| on sma | <b>8</b>        | 3     | C     | <b>\$91C0445</b><br>WAS 910 | UT 4400587 ANI<br>ON SHEET 4. R<br>COB52 PARA                                                                    | EVISED N                | <b>NOTE SHE</b> | ET 18.91CO                             | 677<br>445 | SOH / m.s.                                                                                                      | 10/<br>/17<br>/ |

|        |                 |       |       |                             | -<br>-<br>-                                                                                                      |                         |                 |                                        |            |                                                                                                                 |                 |

|        |                 |       |       |                             |                                                                                                                  |                         |                 |                                        |            |                                                                                                                 |                 |

|        |                 |       |       |                             | У.                                                                                                               | •                       | . *             |                                        |            |                                                                                                                 |                 |

|        |                 |       |       |                             |                                                                                                                  |                         |                 |                                        |            |                                                                                                                 |                 |

|        |                 |       |       |                             |                                                                                                                  |                         |                 | at 1                                   |            |                                                                                                                 |                 |

|        |                 |       |       |                             |                                                                                                                  |                         |                 |                                        | ,          |                                                                                                                 |                 |

|        |                 |       |       |                             | •<br>•                                                                                                           |                         |                 |                                        |            |                                                                                                                 |                 |

|        |                 |       |       |                             | · •                                                                                                              |                         |                 |                                        |            |                                                                                                                 |                 |

|        |                 |       |       |                             | and the second |                         |                 |                                        |            |                                                                                                                 |                 |

|        |                 |       |       |                             |                                                                                                                  |                         |                 |                                        |            |                                                                                                                 |                 |

|        |                 |       |       |                             |                                                                                                                  |                         |                 |                                        |            |                                                                                                                 |                 |

|        |                 |       |       |                             | · · · · ·                                                                                                        |                         |                 |                                        |            |                                                                                                                 |                 |

|        |                 |       |       |                             |                                                                                                                  |                         | ·               |                                        |            |                                                                                                                 |                 |

|        |                 |       |       |                             |                                                                                                                  |                         |                 |                                        |            |                                                                                                                 |                 |

|        |                 |       |       |                             | 1                                                                                                                |                         |                 |                                        |            |                                                                                                                 |                 |

|        |                 |       |       |                             |                                                                                                                  |                         |                 |                                        |            |                                                                                                                 |                 |

|        |                 |       |       |                             |                                                                                                                  | · .                     | ·               |                                        |            |                                                                                                                 |                 |

| DR     | P.L             | และ   | ,     | 11/15/71                    | 6                                                                                                                |                         |                 |                                        |            | andige methode water in the program water and the solution of                                                   | 98              |

| СН     |                 | AL    |       | 12/2/11                     |                                                                                                                  |                         |                 | <b>nachines</b> //<br>drive / irvine / |            |                                                                                                                 |                 |

| DSC    | GN -            |       |       |                             | ŢĮTLE                                                                                                            |                         |                 |                                        |            | and a state of the second state |                 |

| EN     | GRE             | ffy   | the   | 1/22/11                     |                                                                                                                  | IGI NEER<br><b>0-62</b> | I'NG: DE        | SCRIPTION                              | 1          |                                                                                                                 |                 |

| API    |                 | fre   | the   | 0 11/22/71                  | T UI                                                                                                             | <b>VIVERSAI</b>         | ASYNC           | HRONOUS                                | SERIA      | L CONTRO                                                                                                        | LLER            |

| API    | s part          |       |       | Y CONTAIN                   |                                                                                                                  | ASC)                    | 2<br>2          |                                        |            |                                                                                                                 |                 |

| PRO    | DPRIET          | ARY   | NFOF  |                             | CODE                                                                                                             | SIZE                    | DWG NC          | ).                                     |            | e ante Marcallin avec e ser standigt                                                                            | R.E.            |

|        | T BE DI         | SCLO  | SED   | R USED                      | IDENTINO.                                                                                                        |                         |                 | 98A 0767                               |            |                                                                                                                 | 10              |

| OR     | PRODU<br>SUBJE  | CT, W | ITHO  | UT WRIT-                    | 21101                                                                                                            |                         |                 |                                        | - <u>-</u> |                                                                                                                 | 1               |

| TEN    | PERM            | 15510 | JN FR | OM VOM                      | SCALE                                                                                                            | L                       |                 | • .                                    | SH         | ET   🧳                                                                                                          | 75              |

٠

•

....

· .

INDEX

|                                               |                                                                                                                                                                                      | PAGE                                   |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| SECT                                          | ON I - DESCRIPTION                                                                                                                                                                   |                                        |

| 1.1<br>1.2<br>1.3                             |                                                                                                                                                                                      | 5<br>5<br>12                           |

| SECTI                                         | ON II - INTERFACE AND CONNECTIONS                                                                                                                                                    |                                        |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5               | RS232 Option<br>Current Mode Option<br>Relay Option<br>DTL/TTL<br>Device Address and PIM Drivers                                                                                     | 14<br>14<br>15<br>15<br>19             |

| S <u>ECTI</u>                                 | ON III - PROGRAMMING UASC                                                                                                                                                            |                                        |

| 3.1<br>3.2<br>3.3                             | Instruction Set<br>Explanation of Instruction Set<br>Word/Character Format                                                                                                           | 20<br>21<br>22                         |

| SECTI                                         | ON IV - APPLICATION DATA                                                                                                                                                             |                                        |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7 | General Data<br>Cable Length Versus Rate of Operation<br>Version Selection<br>Assembly of Cable<br>Examples: Usage of RS232<br>Usage of Current Mode Model<br>Usage of Relay Version | 23<br>24<br>24<br>26<br>29<br>32<br>35 |

| SECTI                                         | ON V - TESTING                                                                                                                                                                       |                                        |

| 5.0<br>5.1<br>5.2                             | General<br>Test Routine<br>Test Connector                                                                                                                                            | 38<br>38<br>38                         |

varian data machines (varian subsidiary evarian subsidiary evarian subsidiary evarian subsidiary evarian subsidiary SH 2 OF 53 REV

# INDEX

PAGE

# SECTION VI - THEORY OF OPERATION

| 6.0 | General                        | 40 |

|-----|--------------------------------|----|

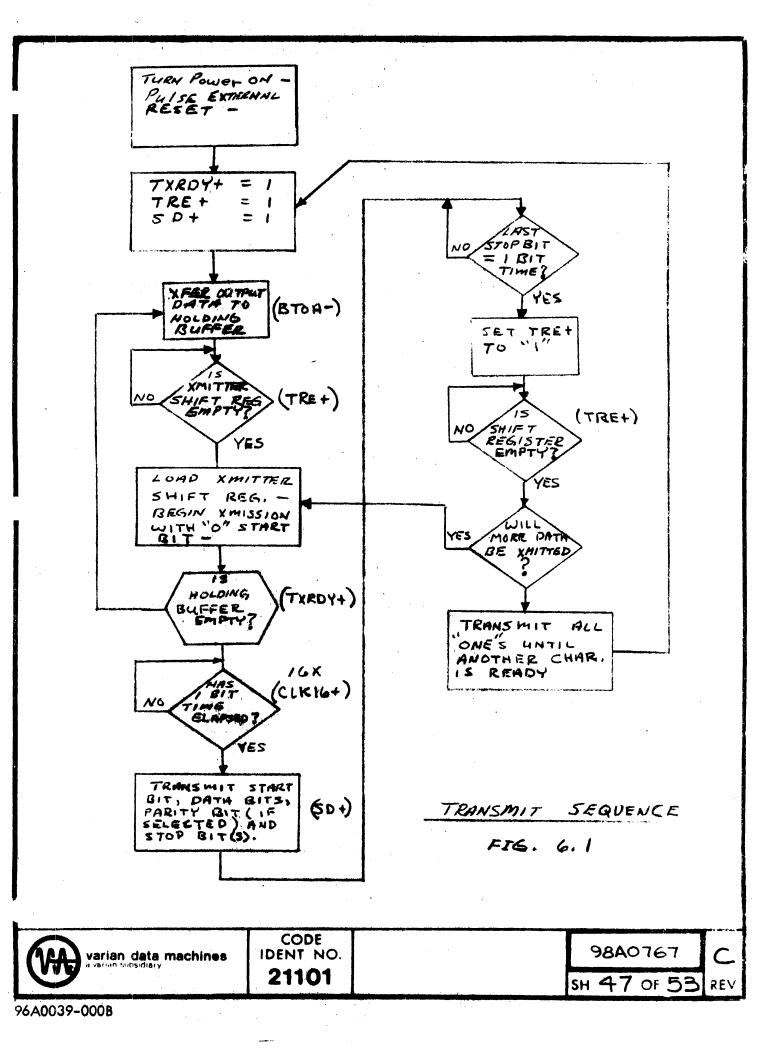

| 6.1 |                                | 40 |

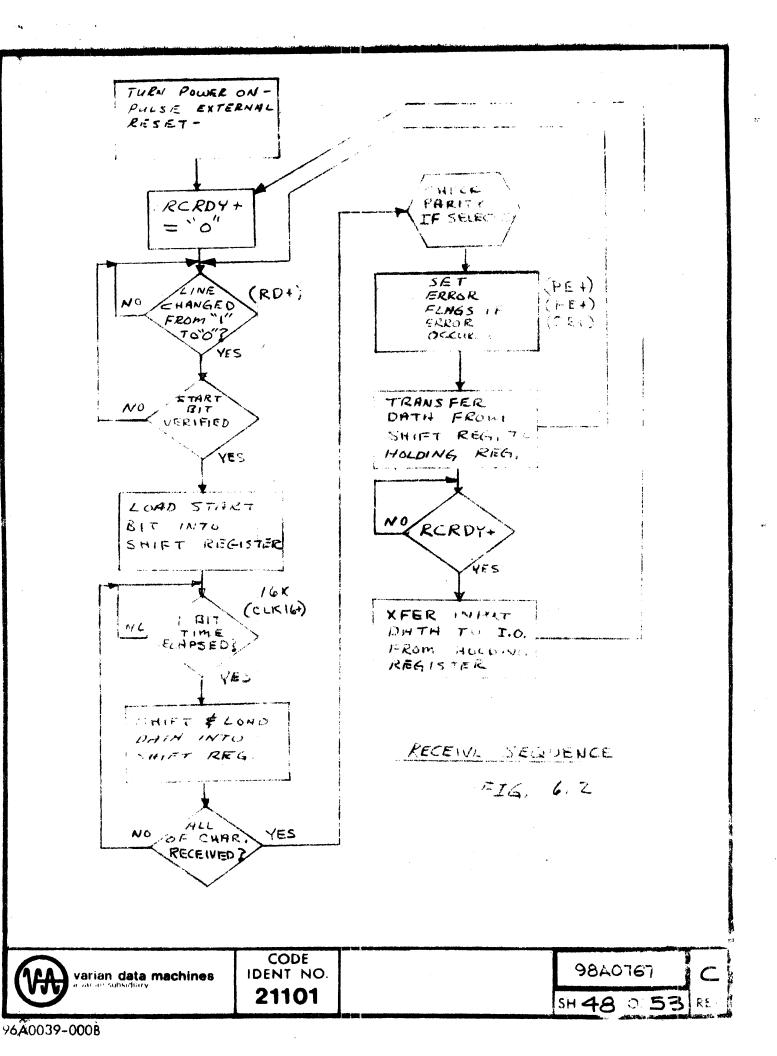

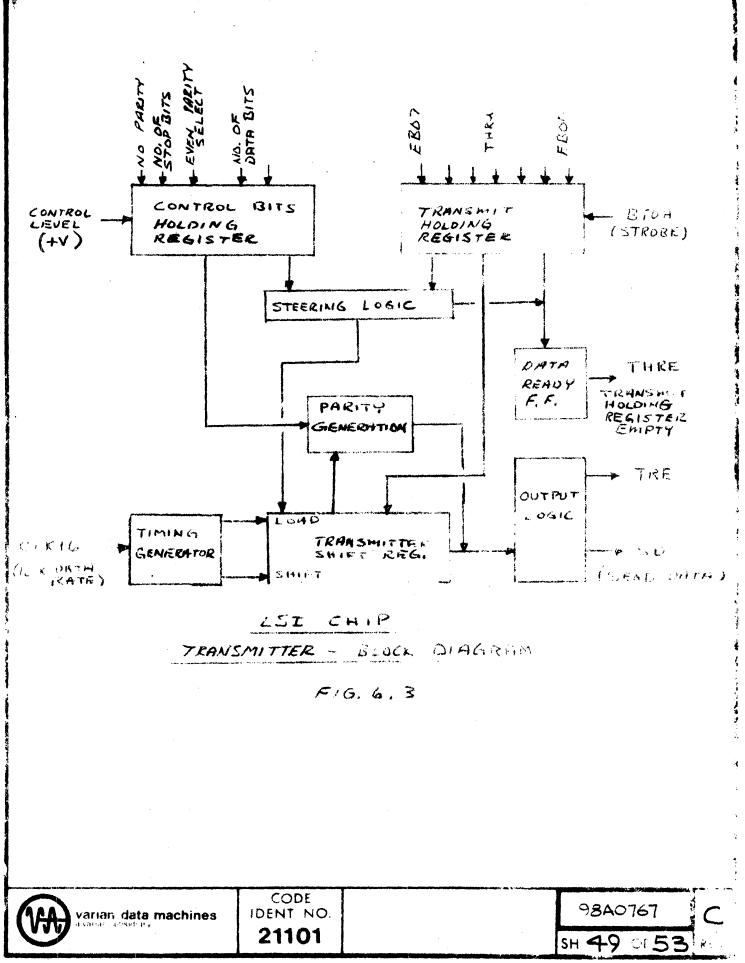

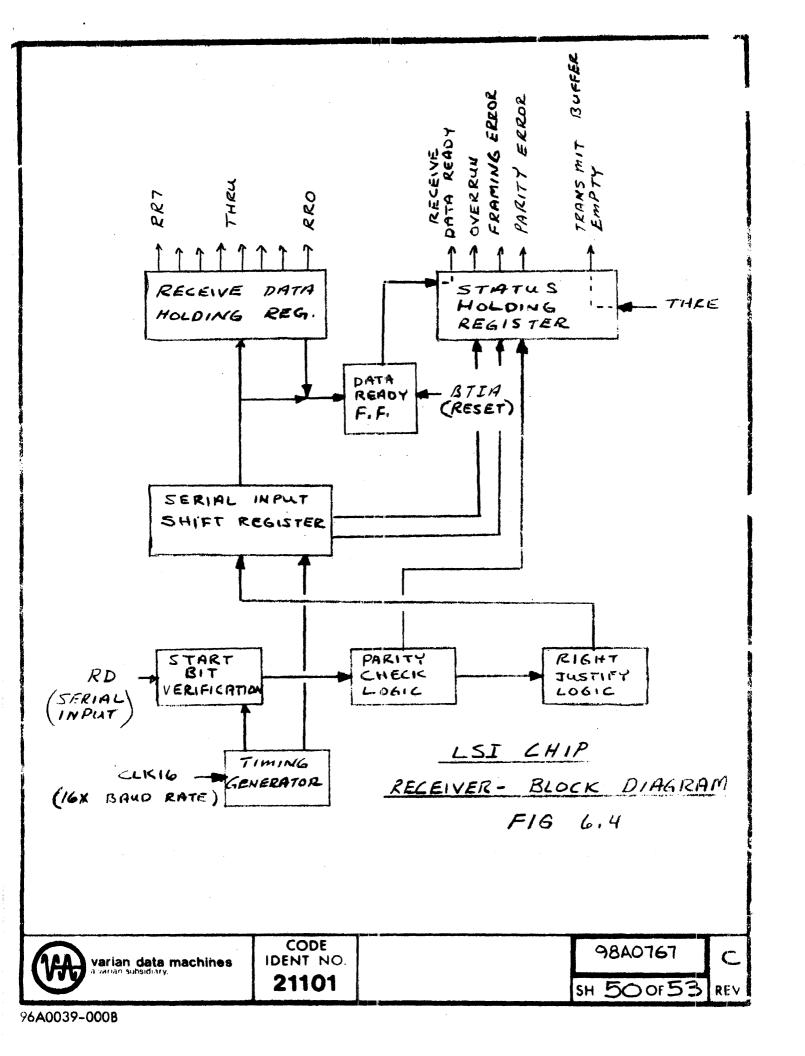

| 6.2 | Transmitter/Receiver Operation | 42 |

| 6.3 | Timing                         | 46 |

|                            |           |                                                                                                                |             | a for the state of |

|----------------------------|-----------|----------------------------------------------------------------------------------------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                            | CODE      | l í                                                                                                            |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| WAA a varian data machines | IDENT NO. |                                                                                                                | 98A0767     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                            | 21101     | la de la companya de |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                            | 21101     | l S                                                                                                            | 5H 2A OF 53 | REV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

. ....

# INDEX

PAGE

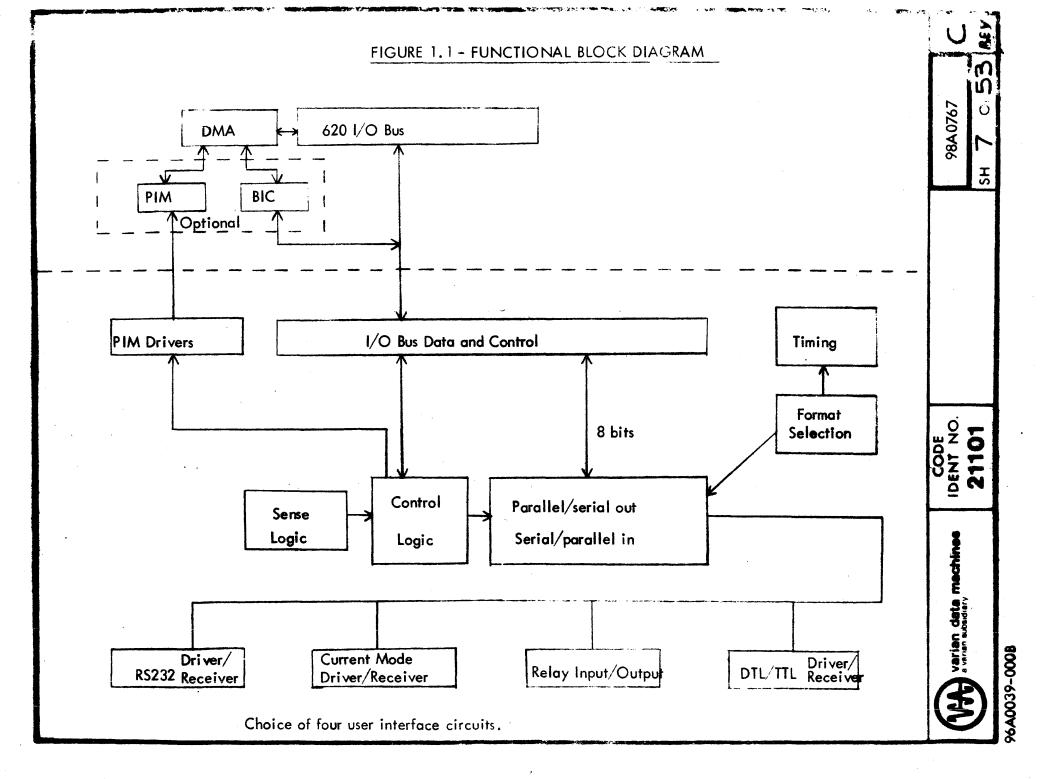

### ILLUSTRATIONS

ł

| Figure 1.1 | Functional Block Diagram            | 7  |

|------------|-------------------------------------|----|

| Figure 1.2 | Baud Rate Selection Chart           | 6  |

| Figure 1.3 | Format Selection Chart              | 9  |

| Figure 1.4 | Asynchronous Format Examples        | 10 |

| Figure 2.1 | PIN Assignment Chart (Input/Output) | 16 |

| Figure 2.2 | Device Address and PIM Connections  | 18 |

| Figure 4.1 | General Specification Chart         | 23 |

| Figure 4.2 | Cable Length Versus Baud Rate       | 24 |

| Figure 6.1 | Transmit Sequence Flow Chart        | 47 |

| Figure 6.2 | Receive Sequence Flow Chart         | 48 |

| Figure 6.3 | Transmitter – Block Diagram         | 49 |

| Figure 6.4 | Receiver – Block Diagram            | 50 |

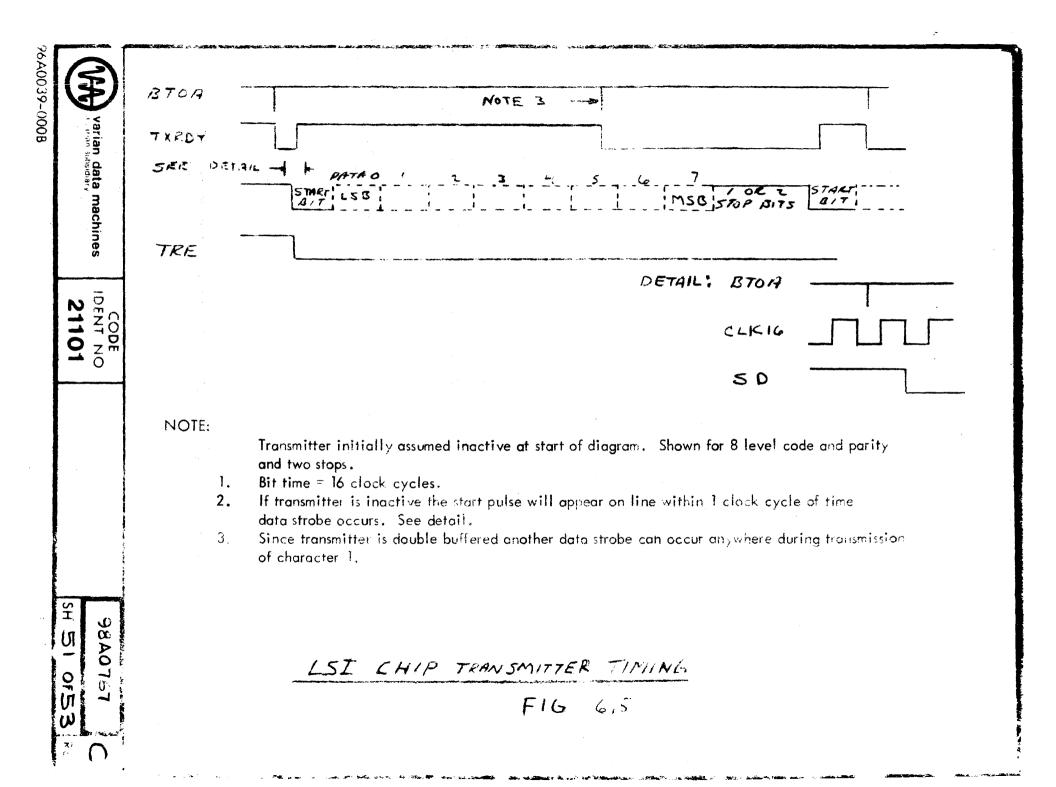

| Figure 6.5 | Transmitter – Timing Diagram        | 51 |

| Figure 6.6 | Receiver - Timing Diagram           | 52 |

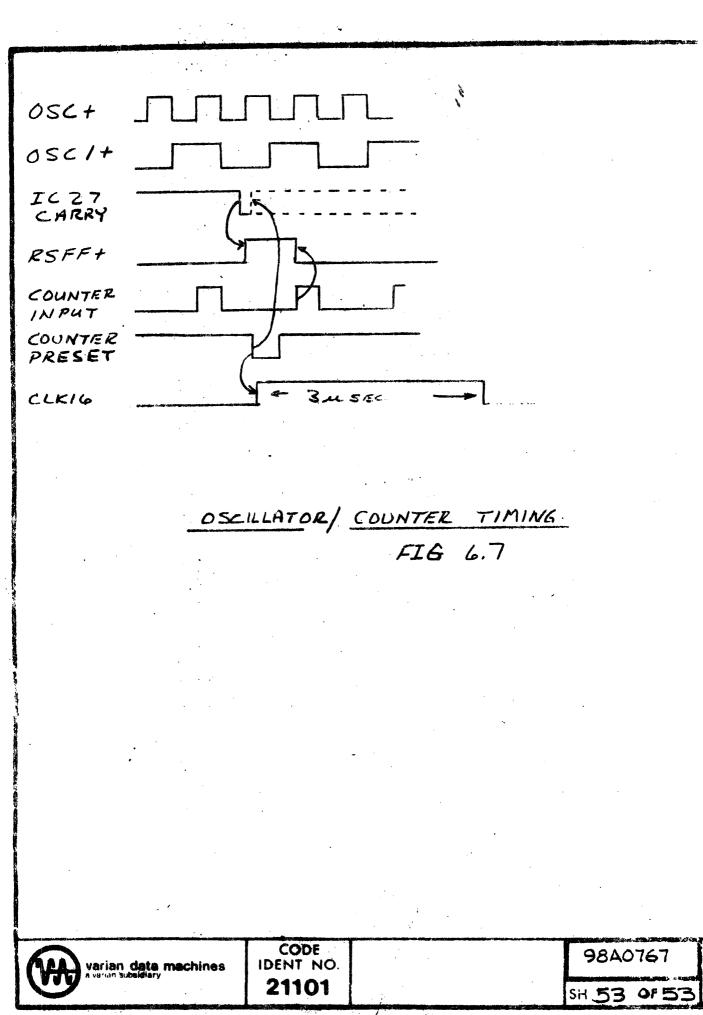

| Figure 6.7 | Oscillator/Counter - Timing Diagram | 53 |

| varian data machines | CODE<br>IDENT NO. | 98, | A070 | 67    | C   |

|----------------------|-------------------|-----|------|-------|-----|

| U                    | 21101             | SH  | 3    | OF 53 | REV |

.....

# ENGINEERING DATA FORM

| OPTION                              | Universal Asynchronous, Serial Controller      |

|-------------------------------------|------------------------------------------------|

| MODEL                               | 620-82 (Formerly E2184)                        |

| NO. OF LOGIC CARDS REQ'D            | 1                                              |

| NO. OF CARD SLOTS REQ'D             | 1                                              |

| LOCATION OF SLOTS (NUMBERING)       | Any I/O slot                                   |

| CONNECTORS REQ'D. (EXCLUDING I/O) , | 2- 44 pin burndy (supplied)                    |

| KEYING                              | NA                                             |

| ST'D. DEVICE ADDRESS                | 02 thru 07 (01 if for TTY) (Can be 00 thru 77) |

| WIRELIST NUMBER                     | PC board                                       |

| MANUAL PUBLICATIONS NUMBER +        | 98A0767                                        |

| PERIPHERAL EQUIPT. REQ'D            | NA                                             |

| MFG'R                               | NA                                             |

| MODEL                               | NA                                             |

| GEN'L. SPECS                        | NA                                             |

| RS232 version requires 100ma o      | t +12V and -12V dc                             |

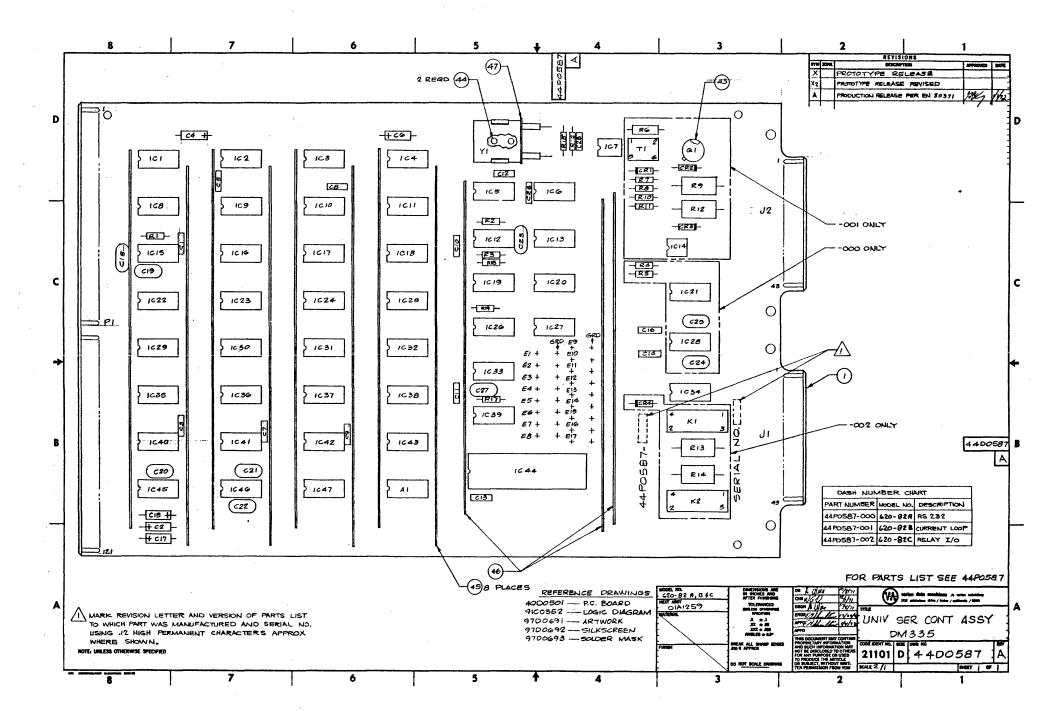

| Reference Documents:                |                                                |

| Top Assembly                        | 01A1259                                        |

| Controller                          | -1410-0507 44D0677                             |

| Test Specification                  | 96iA0768                                       |

| Test Prog. SPS                      | 89A0228                                        |

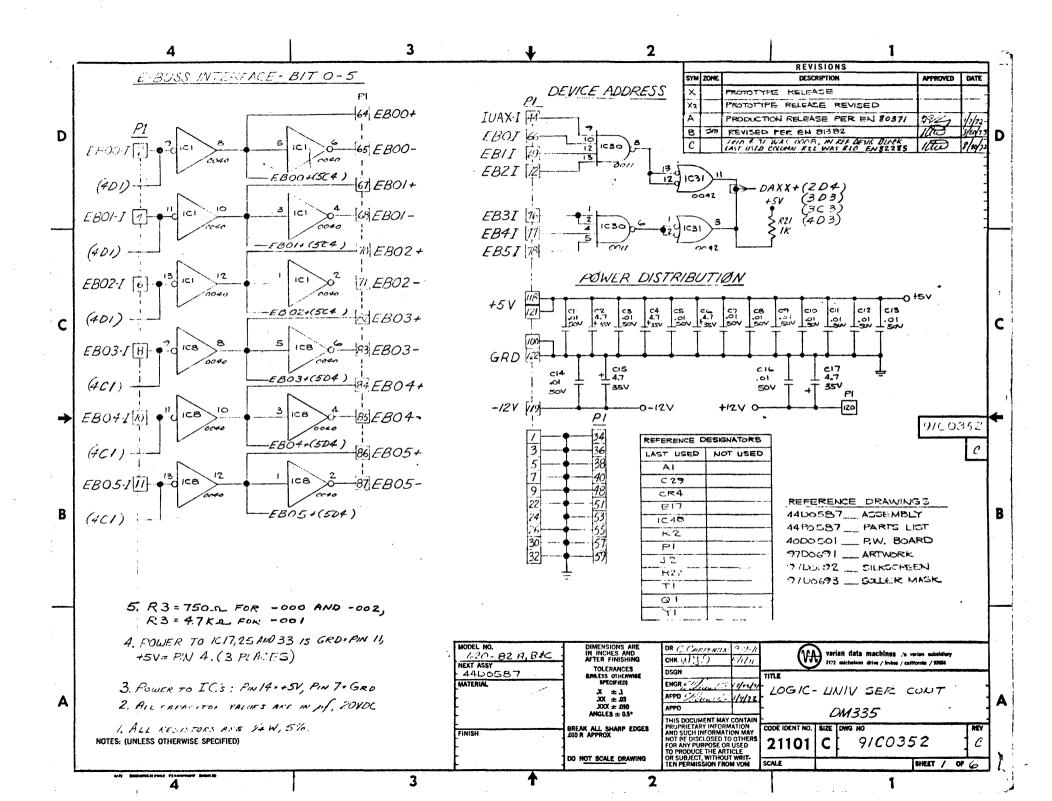

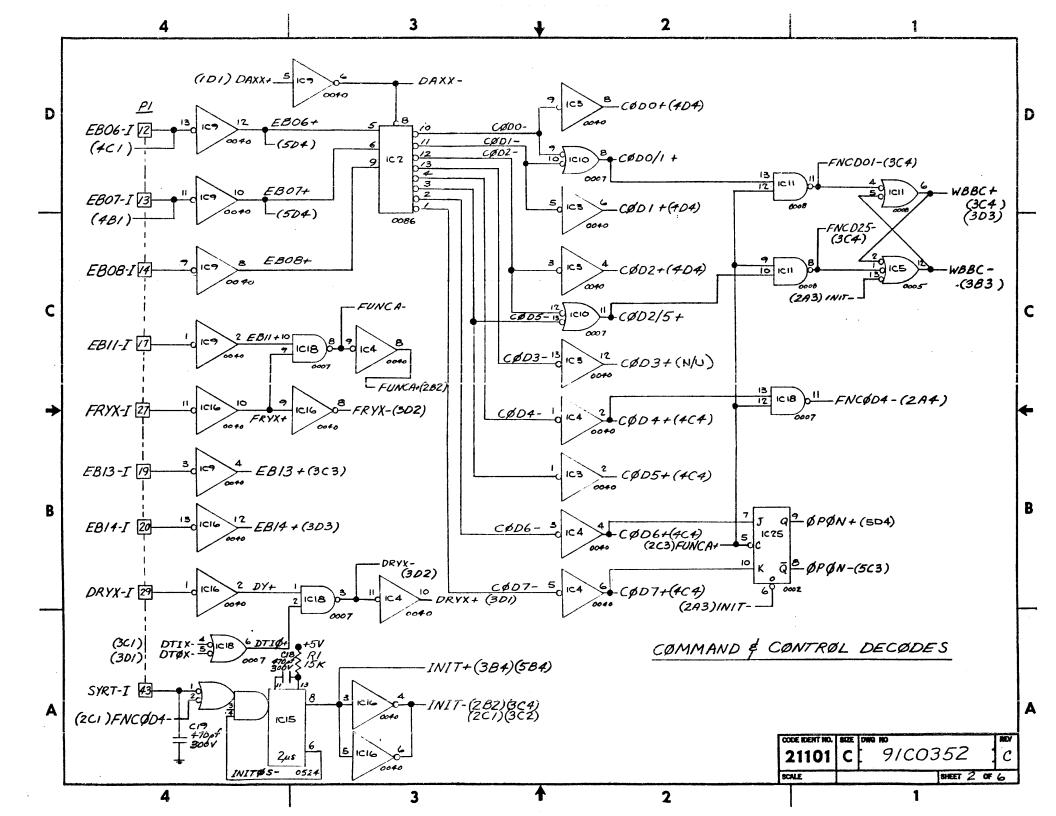

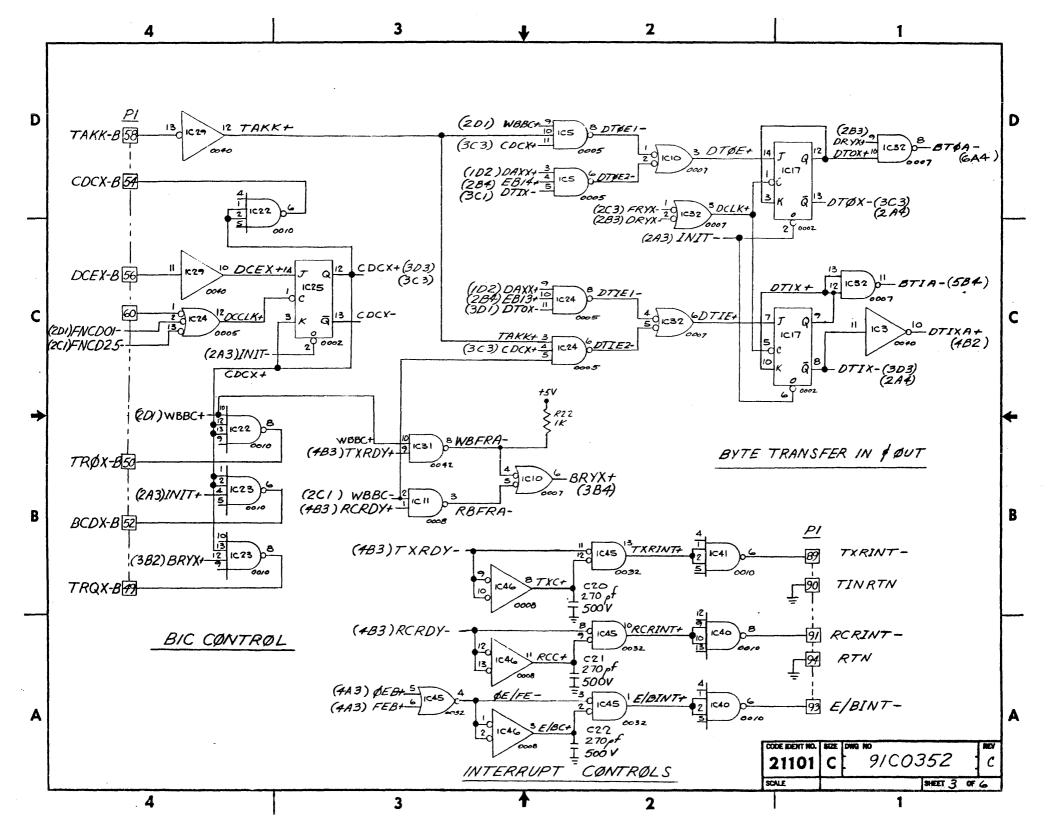

| Logic Diagrams                      | -91-C0352 91C0445                              |

| , Test Routine                      | 32A0107-010                                    |

|                                     |                                                |

|                                     |                                                |

|                                     |                                                |

|                                     |                                                |

|                                     |                                                |

| <b>*</b>                            |                                                |

|                                     |                                                |

| varian data machines<br>a varian subsidiary<br>2722 michelson drive<br>irvine/california/92664 | CODE<br>IDENT. NO |      | 98A0767  | REV<br>C |

|------------------------------------------------------------------------------------------------|-------------------|------|----------|----------|

|                                                                                                | PREPARED BY       | APPR | SHT 4 OF | 58       |

#### SECTION 1 DESCRIPTION

#### 1.1 Introduction

The UASC (Universal Asynchronous Serial Controller) is a versatile character buffered serial controller which can operate in both half or full duplex modes. Four interfaces are available to the user: RS232, Current loop, relay and DTL/TTL. The DTL/TTL interface is always on the controller where as the RS232 or Current Mode or Relay interfaces are selected at time of purchase. The controller is not a data set controller but intended for use on direct connect interfaces.

The controller is capable of operating with one start bit and one or two stop bits, 5,6,7, or 8 bits of data, parity or no parity bit, and odd or even parity. Several operating frequencies from 9600 baud down to 45 baud are possible. All options and operating modes will be set up for the user by VDM, if all requirements are supplied at time of purchase. If the user does not specify the set up for the UASC, the RS232 version will be set up for 1200 baud with no parity, 8 bits of data and one stop bit. Also, the Current Mode version will be set up for 1200 baud with no parity, 8 bits of data and one stop bit. In addition, the relay version will be set up for 110 baud with no parity, 8 bits of data and receive rates will always be equal. The user can easily modify the controller to his data transmission format by placing jumpers on the board as described in section 1.2.2.

#### 1.2 Functional Description

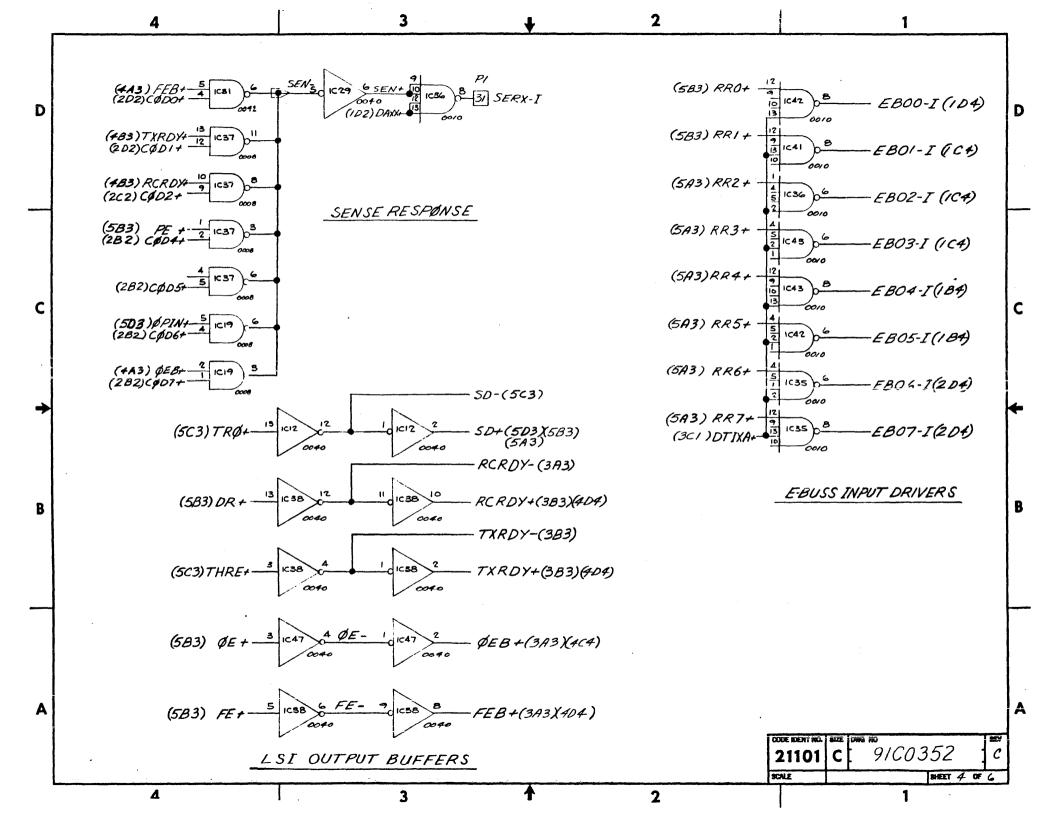

Reference Block Diagram (Figure 1.1).

#### 1.2.1 Timing

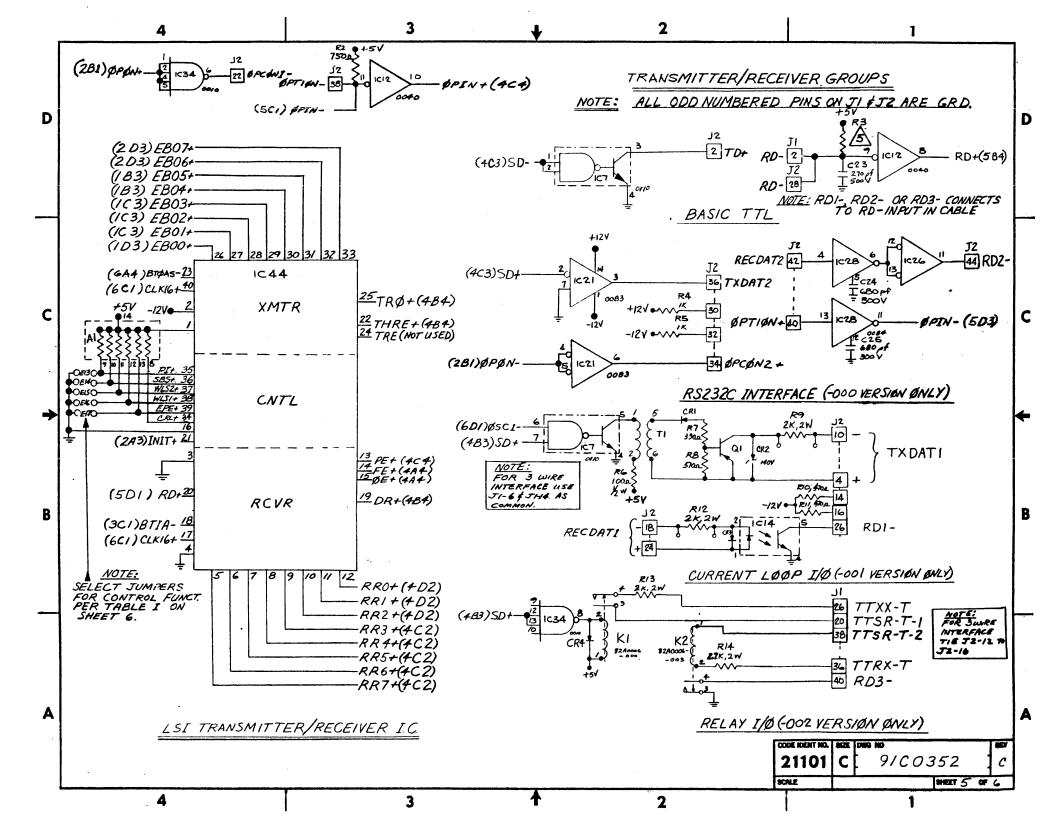

Transmit and Receive clocking to the LSI transmitter/receiver circuit is derived from a 4.608 meg Hz crystal oscillator. A clock rate is derived by setting up the appropriate count in the 12 bit counter. The clock is set up to provide a clock rate 16 times the transmit/receive rate. See Figure 1.2.

| varian deta machines | CODE<br>IDENT NO.<br>21101 | 98А0767 С<br>SH 5 OF <b>53/ жеу</b> |

|----------------------|----------------------------|-------------------------------------|

| 96A0039-000B         |                            |                                     |

1:

| Baud Rate   | Div. By     | E1.        | E2. | E3 | E4 | E5 | E6 | E7 | E8 | E9 | E 10 | E 11 | E12 · |

|-------------|-------------|------------|-----|----|----|----|----|----|----|----|------|------|-------|

| 9600        | 15          |            | x   | x  | x  |    |    |    |    |    |      |      |       |

| 4800        | 30          | x          |     | x  | х  | x  |    |    |    |    |      |      |       |

| 2400        | 60          | x          | X   |    | х  | X  | X  |    |    |    |      | [    |       |

| 2000        | 72          | ×          | х   | x  |    |    |    | x  |    |    |      |      |       |

| 1800        | 80          | x          | х   | x  | х  |    |    | x  |    |    |      |      |       |

| 1200        | 120         | X          | х   | x  |    | x  | X  | X  |    |    |      |      |       |

| <b>6</b> 00 | 240         | X          | Х   | x  | x  |    | X  | X  | X  |    |      |      |       |

| 300         | 480         | X          | х   | x  | x  | x  |    | x  | X  | X  |      |      |       |

| 150         | <b>96</b> 0 | ×          | X   | x  | x  | x  | X  |    | x  | X  | ×    |      | ł     |

| 110         | 1309        |            |     | x  | x  | x  |    |    |    | X  |      | x    |       |

| 75          | 1920        | <b>X</b> . | X   | x  | x  | x  | x  | x  |    | x  | x    | x    |       |

| 45          | 3200        | x          | x   | x  | x  | x  | x  | x  |    |    |      | x    | x     |

|             |             |            |     |    |    |    |    |    |    |    |      |      |       |

### FIGURE 1.2 + BAUD RATE SELECTION CHART

Note that jumper values are selected at one less than the desired divisor value. Other baud rates can be derived by the following formulas

$$D = \underbrace{\frac{CR}{2} \div 16}_{\bullet} \div BR - 1$$

or

(144,00) <u>+</u> BR-1

D = Divisor

CR = Clock or Oscillator Rate

BR = Baud Rate desired

Note: Remainder should not exceed 1% of BR.

Jumpers E1 through E12 are placed on the controller (above the large chip) per the above chart.

| varian data machines | CODE<br>IDENT NO. | 98A0767       | 7 C       |

|----------------------|-------------------|---------------|-----------|

|                      | 21101             | <b>SH 6</b> 0 | F 53- RIV |

3

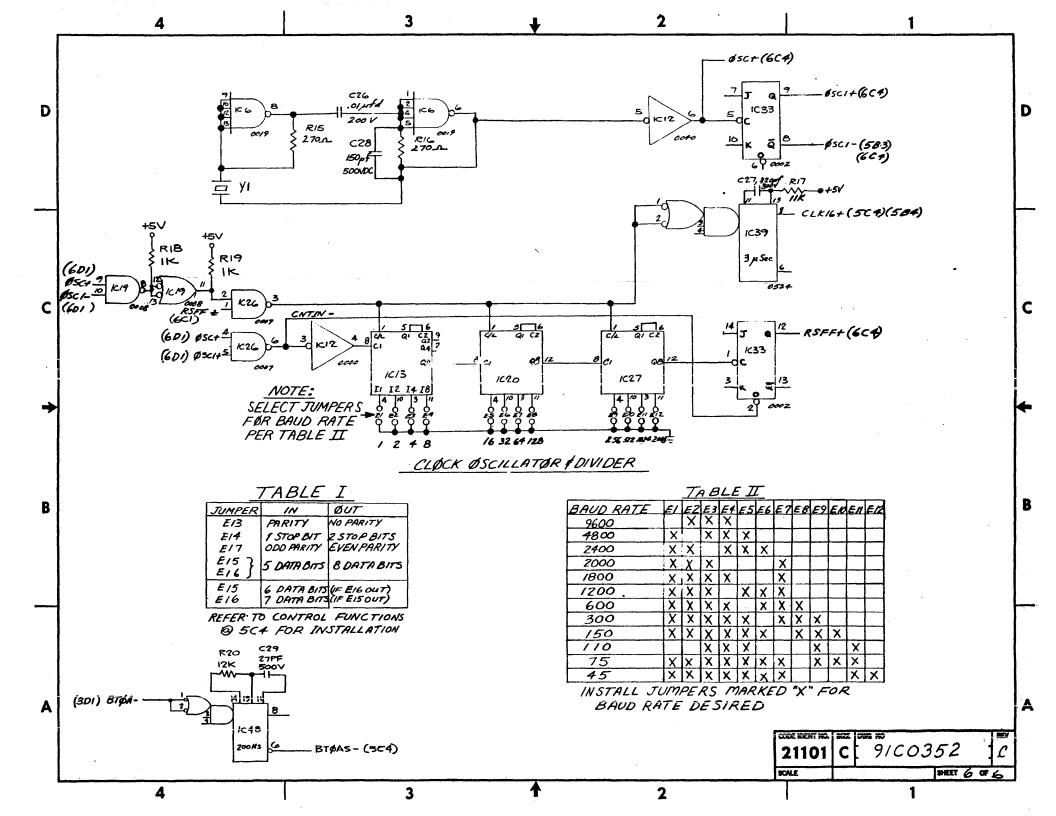

### 1.2.2 Format Selection

Format selection is accomplished prior to initial operation or hookup to the serial device to be controlled. Choice of combinations of five jumpers will provide the following variations: One or two stop bits, 5-6-7 or 8 data bits, odd parity, even parity or no parity. (See Figure 1.3 and 1.4.)

### 1.2.3 620/1/O Bus

The I/O interface is an 8 bit interface to the 620 16 bit I/O. The most significant 8 bits are not used in the 16 bit data word. DMA data transfer in or out of the 620 is possible in conjunction with the BIC option. It should be noted that although this controller has full duplex capability, the BIC can only be connected to the transmit functions or to the receive function (not both at the same time).

#### 1.2.4 Transmit Section

Data is transferred from the 620 1/O to the 8 bit parallel buffer register in the LSI circuit. The 8 bits are then transferred into the serial shift register and shifted out serially with the least significant bit (bit 0) shifted out first. A zero or "space" bit is inserted at the beginning of each serial word. This "Start Bit" preceeds the 5,6,7, or 8 data bits and the parity bit (if selected) and the "Stop Bit"(s). The stop bit(s) is a "1" or "mark" bit.

#### 1.2.5 Receive

Data is received into the serial shift register with Start Bit first followed by 5,6,7, or 8 data bits (least significant bit first), a parity bit (if selected), and 1 or 2 Stop Bits. When the complete character is shifted into the serial register, it is transferred into the parallel buffer register. Immediately after loading the parallel register, the Input Ready Sense line is made "true". Inputting the character will set Input Readv "false". Both Transmit and Receive functions are character buffered and operate independently. The format of the data being received must be the same as that selected for proper operation.

#### 1.2.6 Control Logic

The Control Logic provides direction control for data transfer to and from the I/O bus, BIC connect control, Initialize control, and control of an external line (option enable/ disable).

| varian deta machines | CODE<br>IDENT NO. |        | 98 | A0767 | C   |

|----------------------|-------------------|--------|----|-------|-----|

|                      | 21101             | <br>SH | ß  | OF 55 | REV |

### FIGURE 1.3

### FORMAT SELECTION CHART

Jumpers Added

96A0039-

#### Result

| E13        | Parity Bit Enabled            |

|------------|-------------------------------|

| E14        | One Stop Bit                  |

| E15 and 16 | Five Data Bits per character  |

| E15        | Six Data Bits per character   |

| E 16       | Seven Data Bits per character |

| E 17       | Odd Parity Bit                |

|            |                               |

| Jumpers Omitted | Result                       |

|-----------------|------------------------------|

| E 13            | Parity Bit Disabled          |

| E 14            | Two Stop Bits                |

| E 15 and 16     | Eight DataBits per character |

| E 17            | Even Parity Bit              |

Typical ASCII devices use one start bit, 7 data bits and one parity or 8 data bits, with one or two stop bits.

| varian deta machines | CODE<br>IDENT NO. | 98A 0767   | С   |

|----------------------|-------------------|------------|-----|

|                      | 21101             | SH 9 OF 53 | REV |

### FIGURE 1.4

# ASYNCHRONOUS FORMAT EXAMPLES

|                    |                                      |                                                          | معاور بزوال المبذر استعادتهم والمراد ومراط المعاز بروي | ·····          | -                        |                         |          |

|--------------------|--------------------------------------|----------------------------------------------------------|--------------------------------------------------------|----------------|--------------------------|-------------------------|----------|

|                    |                                      | MSB                                                      |                                                        |                | <b>&gt;</b> L            | SB                      |          |

| 1.                 | Stop Parity<br>Bit Bit               | Bit Bit<br>8 7                                           | Bit Bit 6 5                                            | Bit Bit<br>4 3 | Bit B<br>2               | it Start<br>1 Bit       |          |

|                    | b) Parity                            | Bits S <b>ele</b> cted<br>Bit Selected<br>op Bit Selecte | əd                                                     |                | This is a g<br>CPU to Cl | ood format for<br>PU.   |          |

|                    | ·····                                | MSB                                                      |                                                        |                | > L                      | SB                      |          |

| 2.                 | Stop Stop<br>Bit Bit                 | Bit Bit<br>8 7                                           | Bit Bit<br>6 5                                         | Bit Bit<br>4 3 | Bit B<br>2 1             | it Start<br>Bit         |          |

|                    | b) Parity                            | Bits Selected<br>Bit not Selecte<br>op Bits Selecte      |                                                        |                | Typical fo<br>ASR 33 ar  | r VDM teletype<br>d 35. | <b>e</b> |

|                    |                                      | MSB                                                      |                                                        |                | → LSB                    |                         |          |

| 3.                 | Stop Parity<br>Bit Bit               | Bit Bit<br>7 6                                           | Bit Bit<br>5 4                                         | Bit Bit<br>3 2 | Bit S                    | tart<br>it              |          |

|                    | b) Parity                            | Bits Selected<br>Bit Selected<br>op Bit Selecte          | d                                                      |                |                          |                         |          |

|                    |                                      | MSB-                                                     |                                                        | → LSB          |                          |                         |          |

| 4.                 | 1/2 Stop<br>Bit                      | Stop Bit<br>Bit 5                                        | Bit Bit<br>4 3                                         | Bit Bit<br>2 1 | Start<br>Bit             |                         |          |

|                    | b) Parity                            | a Bits Selected<br>Not Selected<br>top Bits Selec        | ł                                                      |                | Typical Bo               | audot code.             | :        |

|                    |                                      |                                                          |                                                        |                |                          |                         |          |

|                    | 17                                   |                                                          |                                                        |                |                          |                         |          |

|                    |                                      |                                                          |                                                        |                |                          |                         | ļ        |

| variar<br>a varian | n <b>data machines</b><br>subsidiary | CODE<br>IDENT NO.<br>21101                               |                                                        |                |                          | 98A0767                 | С        |

|                    |                                      |                                                          | .4.                                                    |                |                          | H 10 OF 5               | BREV     |

### 1.2.7 Sense Logic

The Sense Logic provides status information to the operating program. Status of Input and Output data registers, three error indications, and an external input line can be monitored.

#### 1.2.8 PIM Drivers

Three PIM Drivers are made available. One line indicates Input Ready. A second line indicates Output Ready. A third indicates either an Input Overflow Error or a Frame Error (Break). An Overflow Error indicates a second character was transferred to the parallel buffer register before the first character was Input. A Frame Error indicates that the first stop bit received was not a "1" bit. The program can detect that a "Break" character was received by verifying that the character received with the Frame Error indication was also an "All Zero" character. Typically, a "Line Break" is more than one consecutive character time. The UASC can receive but cannot transmit a "Line Break".

#### 1.2.9 RS232 Driver/Receivers

The RS232 version fulfills the electrical characteristic requirements of EIA-RS232 B and C. Transmit data, receive data, a control line out and a status line in are implemented with RS232 drivers and receivers.

#### 1.2.10 Current Mode Driver/Receiver

Transmit Data and Receive Data lines only are implemented with this interface. This current loop is capable of operation from 20MA to 60MA at voltages not to exceed 120V across the Transmit Driver. The current loop provides isolation greater than 10 meg ohms at 500Vdc. Detailed specifications are in section 2.2

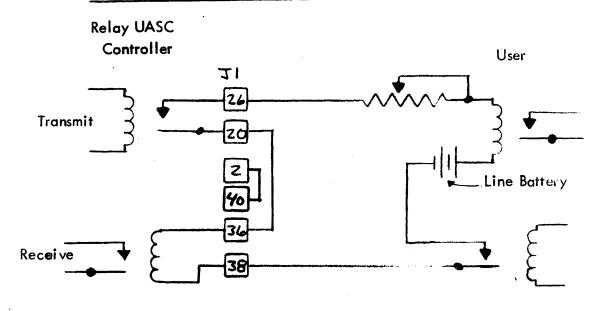

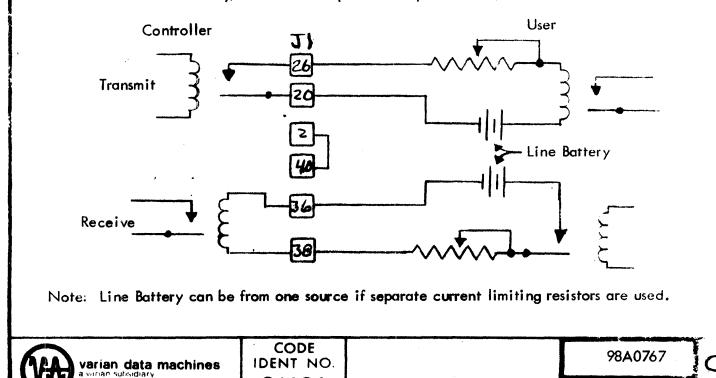

#### 1.2.11 Relay Input/Output

The relay input/output section is mechanized mainly for use as a Teletype Interface. A 2.2K -2 Watt resistor in the Transmit or output circuit and a 2.7K - 2 Watt resistor in the Receive or input circuit are provided as dropping resistors to facilitate connection to the teletype provided line battery source on models 33 and 35. The line battery is a Teletype Option.

The resistors can be bypassed to provide a 20Ma - 12Vdc input/output circuit. Etched pads are made available for this purpose.

| varian data machines | CODE<br>IDENT NO. |       | 98 | BA076 | 67           | C   |

|----------------------|-------------------|-------|----|-------|--------------|-----|

|                      | 21101             | · · · | SH |       | OF <b>53</b> | REV |

The relays are a "Reed" type relay which will function correctly from 0 to 300 baud (150 operations per second max).

### 1.2.12 DTL/TTL Driver/Receiver

The Transmit/Receive Data Lines, as well as the option driver line and option status line, are made available to the user for direct connect to DTL/TTL interfaces. These lines should not exceed 20 feet in cable length. The three previously described interfaces are routed through the DTL/TTL Receivers via the input connectors (J1 and J2).

#### 1.3 Logic Mnemonics List

| 55) A/  |                                       |

|---------|---------------------------------------|

| BRYX    | BIC Data Ready                        |

| BTIA    | Byte Transfer In                      |

| BTOA    | Byte Transfer Out                     |

| CLK 16  | Clock, 16 times data rate             |

| CDCX    | BIC Controlled Device Connect         |

| CODX    | Function Decode - CODO thru COD7      |

| DAXX    | <b>Device</b> Address                 |

| DRYX    | Data Ready , I/O                      |

| DTIX    | Data Transfer In                      |

| DTOX    | Data Transfer Out                     |

| E/B Int | Framing Error or Overrun Error        |

| EBXX    | 620 1/O Data Lines - EB00 thru EB15   |

| EPE     | Even Parity Select                    |

| FE      | Framing Error on line break           |

| FNCODX  | Function Code EXC 0 thru EXC7         |

| FRYX    | Function Ready I/O                    |

| FUNCA   | Function order any EXC command        |

| INIT    | Initialize                            |

| OE      | Overrun Error                         |

| OPIN    | Option Status Line                    |

| OPON    | Optional Control Line Command Storage |

| Øsc     | 4.608 Mhz Oscillator Output           |

| ØSC 1   | 2.304 Mhz Clock Rate                  |

| PE      | Parity Error                          |

| PI      | Parity Enable Line                    |

| RCRDY   | Receive Data Buffer Ready             |

| RCRINT  |                                       |

| RD      | Receive Data Ready Interrupt          |

| RD 1    | Receive Data DTL/TTL Input            |

|         | Receive Data Current Loop Input       |

varian data machinesCODE<br/>IDENT NO.<br/>2110198A0767SH 12 OF 53 REV

96A0039-0008

#### Logic Mnemonics List

- RD2 Receive Data RS232 Input

- RD3 Receive Data Relay Input

- RSFF+ Clock Counter Reset Flip Flop

- RRX Received Data 8 bits parallel 9 thru 7

- SBS Stop Bit Select

- SD Send Data (Transmit)

- SERX Sense Response

- TXRDY Transmit Data Buffer Ready

- TXRINT Transmit Ready Interrupt

- WLS1 Data Bits per Word Select

- WLS2 Data Bits per Word Select

| CODE  |    |  |

|-------|----|--|

| IDENT | NO |  |

| 211   | 01 |  |

|   | 98A0767 |    | 7     | C   |

|---|---------|----|-------|-----|

| I | SH      | 13 | OF 53 | REY |

#### SECTION II INTERFACE AND CONNECTIONS

#### 2.1 **RS232** Option

Conforms to EIA RS232 B and C as applicable.

2.1.2 Logic 0 = +4 to  $+24 \vee$

Logic 1 = 0V to -24V

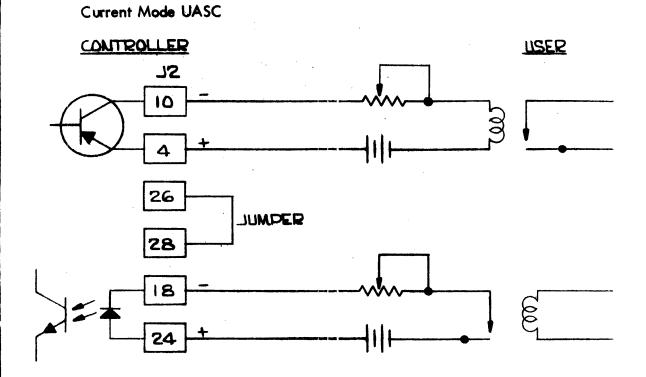

#### 2.2 Current Mode Option

2.2.1 Driver Specification (Note 1)

| Collector Emitter Voltage            | VCEO | 150Vdc Max   |

|--------------------------------------|------|--------------|

| Collector Current - Continuous       |      | 500 MAdc Max |

| Total Dissipation @25 <sup>0</sup> C | Pd   | 1 Watt Max   |

#### 2.2.2 Receiver Specification (Note 1)

Input Forward Voltage Drop V<sub>F</sub> Input Forward Continuous Current I<sub>F</sub> 60MA Max

2.2.3 Isolation

Common Mode Protection500V dcCommon Mode Resistance10 Meg Ohms

2.2.4 Logic 0 = No loop current

Logic 1 = Loop current (20 ma min)

NOTE 1: Current limiting resistors (2.0K - 2W) are mounted in the input and output circuits. Values of these resistors may require change or shorted out. Current ratings above must not be exceeded.

| varian data machines | CODE<br>IDENT NO. | 98A0 76 <b>7</b> | C   |

|----------------------|-------------------|------------------|-----|

|                      | 21101             | SH 14 OF 58      | REV |

2.3 Relay Option

2.3.1 Input (Note 2)

Relay Input Coil Rating

12.5Vdc max.

Relay Input Coil Resistance 1250 ohms

2.3.2 Output (Note 2)

Reed Relay Contact Closure - Form A

2.3.3 Isolation

Common mode resistance 10Meg Ohm @400Vdc

2.3.4 Logic 0 = No current Logic 1 = Current (10 ma min)

Note 2: Current limiting resistors of 2.7K in the input side and 2.0K in the output side may be changed or shorted out. Caution must be used not to exceed 100 Ma through input relay coil.

ACCURATE AND ADDRESS OF

1

1

1

2.4 DTL/TTL (not available when used with RS232)

#### 2.4.1 Input

Both inputs present a 10Ma load at +5Vdc to the user.

#### 2.4.2 Output

Both drivers are capable of sinking 50Ma at +5Vdc.

2.4.3 Logic  $0 = \ge +2.4 \lor dc$

Logic 1 = 0 + .5 Vdc

| varian data machines IDENT | CODE<br>IDENT NO. | 98A0767     | С   |

|----------------------------|-------------------|-------------|-----|

|                            | 21101             | SH 15 OF 53 | REV |

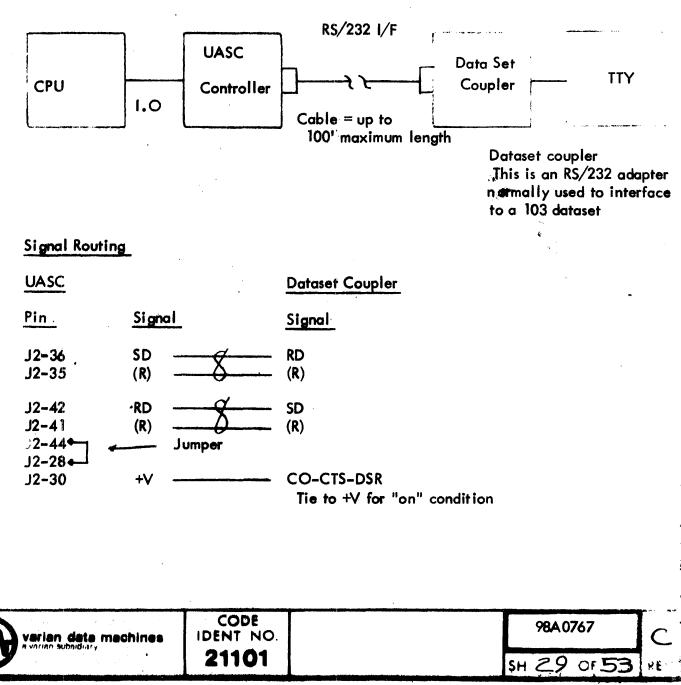

| FIGU                      | FIGURE 2.1           |  |  |  |

|---------------------------|----------------------|--|--|--|

| PIN ASSIGN                | PIN ASSIGNMENT CHART |  |  |  |

|                           |                      |  |  |  |

| RS                        | 232                  |  |  |  |

| FUNCTION                  | PIN LOCATION         |  |  |  |

| Serial Data Transmit      | J2-36                |  |  |  |

| Return                    | J2-35                |  |  |  |

| Serial Data Receive       | J2-42                |  |  |  |

| Return                    | J2-41                |  |  |  |

| Data In (Jumper)          | J2-44 to J2-28       |  |  |  |

| Optional Use Control Line | J2-34                |  |  |  |

| Return                    | J2-33                |  |  |  |

| Optional Use Status Line  | J2-40                |  |  |  |

| Return                    | J2-39                |  |  |  |

|                           |                      |  |  |  |

| * CURRENT MC              | DEVERSION            |  |  |  |

| FUNCTION                  | PIN LOCATION         |  |  |  |

|                           |                      |  |  |  |

| Serial Data Transmit +    | J2-4                 |  |  |  |

| Serial Data Transmit –    | J2-10                |  |  |  |

| Serial Data Receive +     | J2-24                |  |  |  |

| Serial Data Receive –     | J2 <b>-</b> 18       |  |  |  |

\* CAUTION: Excessive reverse current may damage the current mode interface.

J2-26 to J2-28

Data In (Jumper)

98A0767 SH 16 OF 5

FIGURE 2.1 (Cont'd)

1

| RELAY VERS             | SION          |

|------------------------|---------------|

| FUNCTION               | PIN LOCATION  |

| Serial Data Transmit + | J 1≕26        |

| Serial Data Transmit - | J 1–20        |

| Serial Data Receive +  | J 1-36        |

| Serial Data Receive –  | J 1–38        |

| Data In (Jumper)       | J1-40 to J1-2 |

| Data In (Jumper)       | J ]•          |

| * DTL/TTL CO              | ONNECTION      |

|---------------------------|----------------|

| FUNCTION                  | PIN LOCATION   |

| Serial Data Transmit      | J2-2           |

| Return                    | J2 <b>-</b> 1  |

| Serial Data Receive       | J2-28          |

| Return                    | J2-27          |

| Optional Use Control Line | J2-22          |

| Return                    | J <b>2-</b> 21 |

| Optional Use Status Line  | J2-38          |

| Return                    |                |

|                           |                |

\* Note: The above Driver/Receiver cannot be used when the RS232 Driver/Receivers are in place.

|  |  | <b>Var</b><br>a vari |

|--|--|----------------------|

|--|--|----------------------|

| ian deta machines | CODE      |

|-------------------|-----------|

|                   | IDENT NO. |

| uan subsidiary    | 21101     |

98A0767 C

いたい 一番がたい

Ļ

14 × N3

FIGURE 2.2

|      | DEVICE ADDRESS SELECTION |          |                  |     | · · · · · · · · · · · · · |          |                  |

|------|--------------------------|----------|------------------|-----|---------------------------|----------|------------------|

| TEN  | TENS DIGIT               |          |                  |     |                           |          |                  |

| D.A. | :                        | UMPERS   |                  | D.A | JUM                       | PERS     | -                |

| ox   | 76 to 83                 | 77 to 85 | 78 to 87         | X.0 | <b>66</b> to 65           | 69 to 68 | 72 to 71         |

| 1X   | 7 <del>6</del> .to 82    | 77 to 85 | 78 to 87         | X.1 | <b>66 t</b> o 64          | 69 to 68 | 72 to 71         |

| 2X   | 76 to 83                 | 77 to 84 | 78 to 87         | X2  | <b>66</b> to 65           | 69 to 67 | 72 to 71         |

| 3X   | 76 to 82                 | 77 to 84 | 78 to 87         | X.3 | 66 to 64                  | 69 to 67 | 72 to 71         |

| 4X   | 76 to 83                 | 77 to 85 | 78 to 86         | X.4 | 66 to 65                  | 69 to 68 | 72 to 70         |

| 5X   | 76 to 82                 | 77 to 85 | 78 to 86         | X 5 | 66 to 64                  | 69 to 68 | 72 to <b>7</b> 0 |

| 6X   | 76 to 83                 | 77 to 84 | 78 to 86         | X6- | 66 to 65                  | 69 to 67 | 72 to 70         |

| 7X   | 76 to 82                 | 77 to 84 | <b>7</b> 8 to 86 | X7  | 66 to 64                  | 69 to 67 | 72 to 70         |

All pins on this page are on the I/O Back Panel.

| INTERRU                          | RUPT (PIM LINES) Suggeste |                      |  |

|----------------------------------|---------------------------|----------------------|--|

| FUNCTION                         | PIN                       | Order<br>of Priority |  |

| Transmit Data Reg. Ready         | 89                        | #2                   |  |

| Return                           | 90                        |                      |  |

| Rec <b>ei</b> ve Data Reg. Ready | 91                        | ן #                  |  |

| Return                           | 94                        |                      |  |

| Error or Break Interrupt         | 93                        | #3                   |  |

| Return                           | 94                        |                      |  |

|                                  |                           |                      |  |

| varian data machines | CODE<br>IDENT NO. | 98A0767     |       |

|----------------------|-------------------|-------------|-------|

|                      | 21101             | SH 18 CF 53 | K See |

. . . . .

#### 2.5 Device Address and PIM Drivers

The DA for the UASC is wired on I/O back panel. The entire address, both octal digits, must be properly wired for the selected address. DA02 is the first standard address. Add 6 jumpers for the address selected per Figure 2.2.

The PIM drivers are implemented as pulse drivers and can be tied together as an "or" function or can be used on a one for one basis. The program must sense all three functions per interrupt if all are tied together to one PIM input. Reference Figure 2.2 for pin connections.

CODE IDENT NO. 21101

•./

|    | 98A 0767 |             | C   |

|----|----------|-------------|-----|

| S۲ | 119      | <i>े</i> 53 | ×L. |

#### SECTION III PROGRAMMING - UASC

### 3.1 Instruction Set

#### Execute Instructions

| EXC 0 | 1000XX          | Connect BIC (output)  |

|-------|-----------------|-----------------------|

| EXC 1 | 1001XX          | Connect BIC (output)  |

| EXC 2 | 1002XX          | Connect BIC (input)   |

| EXC 3 | 1003XX          | Not used              |

| EXC 4 | 1004XX          | Initialize Controller |

| EXC 5 | 10 <b>55</b> XX | Connect BIC (input)   |

| EXC 6 | 1006XX          | Enable (option)       |

| EXC 7 | 1007XX          | Disable (option)      |

# Sense Instructions

| SEN O | 1010XX          | Frame Error or Break |

|-------|-----------------|----------------------|

| SEN 1 | 1011XX          | Output Ready         |

| SEN 2 | 1012XX          | Input Ready          |

| SEN 3 | 1013XX          | Not used             |

| SEN 4 | 1014XX          | Input Parity Error   |

| SEN 5 | 101 <i>5</i> XX | Not used             |

| SEN 6 | 1016XX          | Sense (option)       |

| SEN 7 | 1017XX          | Input overflow error |

#### Data Transfer Instructions

| OAR | 103 1XX         |

|-----|-----------------|

| OBR | 1032XX          |

| OME | 103 <b>01</b> X |

| INA | 102 IXX         |

| INB | 1022XX          |

| IME | 102 <b>0X</b> X |

| CIA | 102.5XX         |

| CIB | 1026XX          |

| XFER "A" reg to controller    |

|-------------------------------|

| XFER "B" reg to controller    |

| XFER Memory to controller     |

| XFER Data to "A" reg          |

| XFER Data to "B" reg          |

| XFER Data to Memory           |

| XFER Data to cleared "A" reg  |

| XFER Data to cleared "B" reg. |

| Standard Device Address is as follows: |   |    |                                                        |  |  |

|----------------------------------------|---|----|--------------------------------------------------------|--|--|

| lst Unit                               | = | 02 |                                                        |  |  |

| 2nd Unit                               | = | 03 |                                                        |  |  |

| 3rd Unit                               | = | 04 |                                                        |  |  |

| 4th Unit                               | Ħ | 05 |                                                        |  |  |

| 5th Unit                               | = | 06 | DA01 may be used if UASC is used on the first teletype |  |  |

| 6th Unit                               | = | 07 | in a system.                                           |  |  |

CODE varian data machines a varian subsidiary IDENT NO. <u>98A076</u>7 21101 SH 2001 5 7 RE

#### 3.2 Explanation of Instruction Set

#### 3.2.1 EXC Instructions

EXC 0 and EXC 1 are both (either one) used to connect the BIC to output control of the UASC.

EXC 2 and EXC 5 are both (either one) used to connect the BIC to control input of the UASC. The multiple BIC connect instructions are implemented for compatibility of the UASC, Teletype Controller, Paper Tape Controller, etc., instruction sets. The EXC 6 and EXC 7 Instructions are used to turn on optional control line on and off. EXC 4 is used to reset all functions on the UASC.

#### 3.2.2 Sense Instructions

SEN 0, Frame Error or Break, is used to detect that a character received did not have "mark" or "l"stop bits. The program can check the received character to verify that the data was all "zeros". If the data was all zeros and a Frame Error was sensed, a "Line Break" was received. If the data was not all zeros, the error was probably a "hit' on the line or noise.

SEN 1 and SEN 2 indicate the status of the Transmit and Receive buffer registers. SEN 4 indicates, when true, that a parity error has been detected on a character received.

SEN 6 indicates the status of an optional status line. SEN 7 indicates that another character was received before the prior character was removed from the input register.

#### 3.2.2 Data Transfer Instructions

These instructions are self explanatory. See 3.1.

#### 3.2.3 Interrupts

The interrupt functions are implemented on an individual system basis. SEN 1 and SEN 2 are implemented with individual drivers. SEN 0 and SEN 7 are "ORed" together on the same driver. All may be "ORed" together if desired.

CODE IDENT NO. 21101 「おおっておろい」があった。 あったい キー・モード・ビード いっていた あるまたがある うまうしまい しかいえん

3.3 Word/Character Format (UASC to CPU)

Only data is transferred. Parity, if selected, is not transferred as part of data to cr from the CPU.

-5

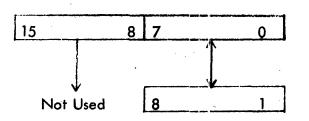

3.3.1 16 Bit Word - 8 Bit Character

Transmitted or received character

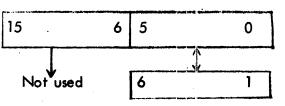

3.3.2 16 Bit Word - 7 Bit Character

Transmitted or received character.

3.3.3

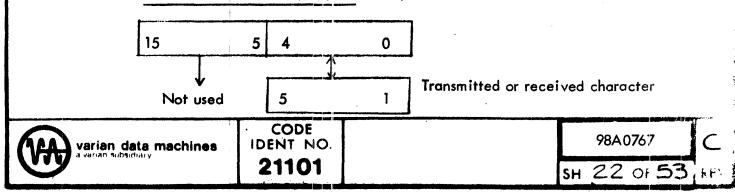

#### 16 Bit Word - 6 Bit Character

Transmitted or received character.

3.3.4 16 Bit Word - 5 Bit Character

#### SECTION IV APPLICATION DATA

### 4.1 General Data

As previously mentioned in Section 1, the controller is available in several versions. The general purpose nature of the controller logic and the three available interface types makes it adaptable for use in many applications where a serial bit/non-modem type interface is required. It is suggested that the user read and study this entire section prior to attempting operation.

The chart below gives the general characteristics of each model along with the cable length/rate restrictions.

|                         | Y                                                                                                                            | FIGURE 4.1                                                                        |                     |                                                                       | and and a subscription of the second                        |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------|-----------------------------------------------------------------------|-------------------------------------------------------------|

| Model                   | Serial Rate, BPS<br>(bits per second)                                                                                        | Character<br>Size                                                                 | Stop Bit            | Cable. and<br>Distance                                                | Miscellaneous                                               |

| R5232                   | 45 to 9600 bps<br>depending upon<br>cable length<br>(See Fig. 4.2)                                                           | 5,6,7, or 8 level<br>(bits). Parity bit<br>(if any) is added<br>to the data bits. | One or<br>Two       | Standard<br>length=20ft.,<br>optionally<br>up to 100ft.               |                                                             |

| Current<br>Mod <b>e</b> | Same as RS232                                                                                                                | Same as RS232                                                                     | Same<br>as<br>RS232 | Standard<br>length=20ft.<br>optionally<br>up to more<br>than one mile | User must<br>provide "line<br>battery" for<br>loop current. |

| Relay                   | 45 to 330 bps.<br>Typically would<br>be 75 or 110 bps.<br>Relays will not<br>operate reliably<br>at higher than<br>300 b ps. | Same as RS232                                                                     | Same<br>as<br>RS232 | Same as<br>current mode                                               | Same as<br>current mode.                                    |

FIGURE 4.1

### 4.2 Cable Length Versus Rate of Operation

As noted in Figure IV, the RS232 model cable length is restricted to 100'. The RS232 interface is not isolated and operates in a voltage mode as set forth in RS232 B and C. Therefore, the maximum cable distance must be observed. RS232 is typically restricted to 50 feet of cable distance, but usually operates well up to 100 feet. The other models operate on a current loop (isolated interface) basis and cables can be much longer. Table below gives some general guidelines. Cables should be twisted pair using 24 gauge (or larger) wire. Note that maximum operating rate of the relay version is 330 bps so Figure 4.2 applies primarily to the Current Mode version.

| Rate in BPS        |

|--------------------|

| 10,000 bps maximum |

| 4,800 bps maximum  |

| 1,800 bps maximum  |

| 900 bps maximum    |

| 300 bps maximum    |

|                    |

#### 4.3 Version Selection

The three versions of the controller will cover a wide field of applications. The version of controller to be used depends primarily on the peripheral device interface. For example, a full-duplex terminal with an RS 232 I.F. (capable of operating with a 103 or 202 modem), but located within 100' of the computer, can usually be driven via the RS 232 version controller by adding a few jumpers at the peripherals (modem) connector. Typically, the modeun control leads are jumpered "on" simulating the presence of the modem. "On" can be maintained by tying +12Vdc thru the IK source to the control lead pins.

In the case where a user needs an isolated interface, he would use the current mode or relay version of the controller.

The data below will assist users in configuring workable systems. Several application cabling examples are shown for each version of the controller following the general discussion of cabling, full/half duplex, 20/60 ma and line battery implementation.

### 4.3.1 Full-Half Duplex Discussion

All models can operate in a true (simultaneous send and receive) full duplex manner or in a send only, receive only, send or receive - half - duplex manner.

If the controller is cabled up in a full duplex (4 wire) manner, it will not see a reflected (echoed) input of what it is sending. If, however, the controller is cabled up in a half-duplex manner (only one pair of wires used), the outputted data on the send circuit will be reflected (echoed) back into the controller's receive section as input. The CPU software must ignore this "echoed" input during output of a message in this case. See cabling examples and discussion of signal routing.

### 4.3.2 20/60 MA Current Made Operation

The Current Mode interface is limited at 20 to 60 MA operation. Two 2K-2 Watt dropping resistors are provided for use with a fixed voltage current source such as a model 33 or 35 teletype. Etched pages are provided for jumpering out the 2K resistors if a variable voltage current source (line battery) is available. The current loop interface provides DC isolation up to 500Vdc. If the user supplies the line battery, this isolation will be maintained. If loop current is derived from the 12V source on the controller board, isolation at the controller end is lost.

### 4.3.3 Relay Current Loop Operation

The relay current loop is limited to 20 to 60 MA operation as well as the discrete current loop. 2K-2 Watt dropping resistors are provided for use with fixed voltage current sources (line battery), such as a model 33 or 35 teletype. Normal relay isolation is obtained with this interface when line battery is supplied by user.

### 4.3.4 One and a Half Stop Bits

Although the user has the ability to select only one or two stop bits, he can operate with a 1-1/2 stop bit format. This is done by simply selecting two stop bits. For a Transmit function, the end result is that the maximum transfer rate is lowered by 1/2 bit time per character. For Received data, the controller ignores the second stop bit completely. Thus, the 1/2 bit time can be handled nicely and without noticable speed reduction.

varian data machines

CODE IDENT NO. 21101 98A0767 SH 25 OF 5

#### 4.3.5 Line Battery Requirements

VDM may provide a controller only or a peripheral device along with the controller. If both the controller and VDM peripheral device is provided, VDM will supply "line battery". If VDM provides the controller only, the user (or peripheral supplier) will normally supply "line battery".

#### 4.3.5.1 What is "Line Battery"?

This is normally a power source (supply) capable of providing enough current for "loop" operation. In the case of a 20ma, full duplex loop application, a power supply capable of supplying 20ma to both loops is required. Voltage for proper operation of the VDM current loop (or relays) can be from 12V to 100V at 60ma maximum. Besides the power supply itself, a means of adjusting (and/or regulating) the amount of current is required. A trimpot or fixed resistor network (per loop supplied) is adequate. One "battery" supply can supply many current loops; Typically, a one amp, 24Vdc supply could handle 20 (20ma-full duplex) controller-peripheral device hookups. VDM suggests usage of a barrier strip approach for a multiple relay type loop installation. See next pages. Use of an isolated "separate" power supply is the preferable method of implementing line battery.

#### 4.4 Assembly of Cable (to peripheral device)

VDM provides a 20' open-ended cable kit with each controller. This cable kit includes a 44 pin Burndy type edge-on connector and hood, extra pins, and two twisted pairs in a jacket. The user makes up his cable to fit the application. See the examples for each type of controller. The cable routes from the top or bottom edge connector labled J1-J2 on the controller, to the peripheral device. (Reference: figure 2.1) The two pairs provided in the 20'cable kit are needed for "send" signals and "receive" signals. The twisted pairs are connected to the 44 pin connector as shown on the following pages. Wires required for operation with the (option) control and status lines are not included.

Users must determine the proper pin numbers at the peripheral device if the peripheral is not supplied by VDM.

P. T. LUNCHARD

12.2.3

3

SH 27 OF 53 REV

4.4.1.2

Line Battery/Device Hookup - Full Duplex

21101

٠٠.

# 4.4.1.3 Line Battery/Device Hookup - Full Duplex

Note: As in 4.4.1.2, line battery can be one source if separate current limiting resistors are used.

| varian data machines | CODE<br>IDENT NO. | 98A0767    | C |

|----------------------|-------------------|------------|---|

|                      | 21101             | SH 28 0F53 |   |

#### 4.5 Examples: Usage of RS232

### 4.5.1 Example #1 - Data Set Coupler

ASR-33 Teletype equipped with a dataset coupler. Hardwire controller to 110bps, 2 stop bits, no parity, 8 bits. Hook-up cable as shown.

96A0039-0008

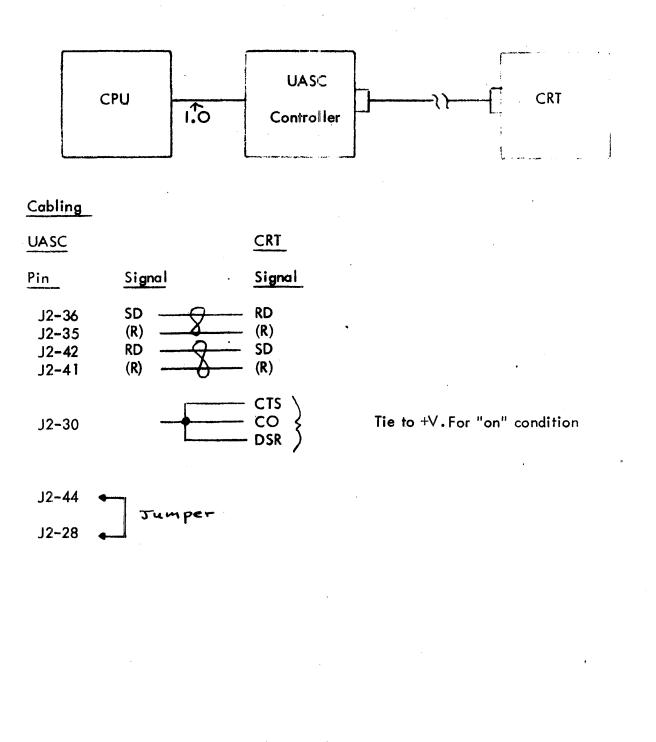

# 4.5.2 Example #2 - CRT Hookup

CRT with RS232 I/F (202 Modem). Hardwirecontroller to rate desired: Probably, 1200, 2400, or 4800 bps, 8 bits, 1 stop bit, parity.

varian data machinesCODE<br/>IDENT NO.<br/>2110198A0767SH 300F.5

RE

96A0039-000B

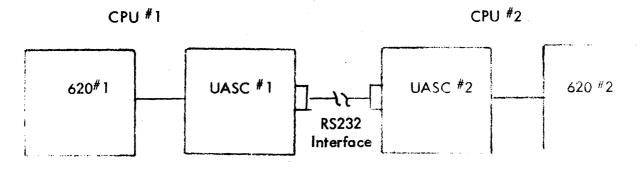

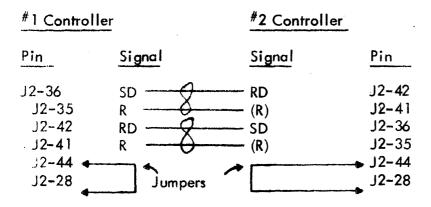

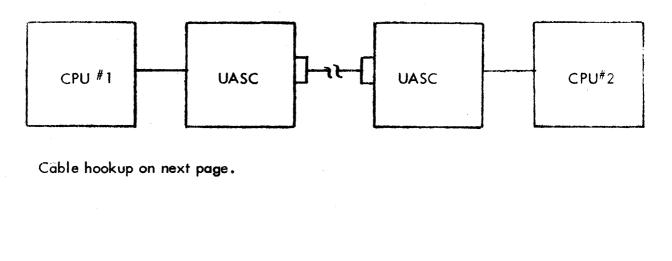

# 4.5.3 Example #3 - 620 CPU to 620 CPU

Hardwire the controller to 2400, 4800, or 9600 bpi. Set character size to 8 bits plus odd or even parity, one stop bit. Hook up the cable as shown.

#### Cabling

There are no control leads to "tie on" in this case.

| J2-34         | OPC | OPS | J2-40 |

|---------------|-----|-----|-------|

| J2-33         | R   | R   | J2-39 |

| J2 <b>-40</b> | OPS | OPC | J2-34 |

| J2-39         | R   | R   | J2-33 |

Optional control capability

This hookup provides an additional control and status line.

#### 4.6 Usage of Current Mode Model

Unit has a solid state discrete current loop interface. It can typically be used to handle devices employing a current interface such as teletypes and/or terminals equipped with a 20/60ma current loop. Either half or full duplex operation is possible. This model has a major advantage over the RS232 interface in that the maximum cable length may be much longer. (See Figure 4.1). It has a major advantage over the relay interface in that the rate can be much higher than with electro-mechanical relays. See controller characteristics table and line battery discussion.

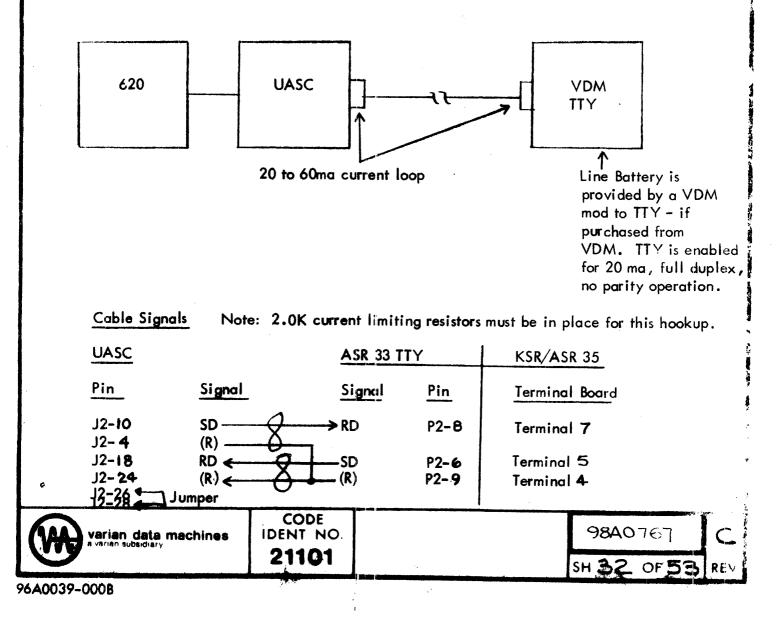

#### 4.6.1 Example #1 - Interface to TTY

VDM modified KSR-ASR 33, 35 teletypes. Prepare the controller for 110 bps, 8 bits, no parity, 2 stop bits. Cable as shown.

Cable may be upito 10,000 feet long.

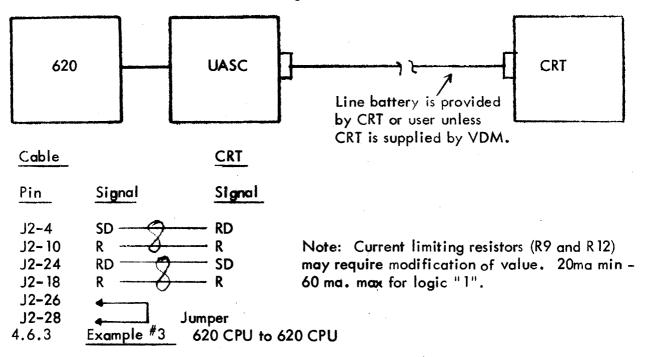

### 4.6.2 Example #2 - CRT Hookup

CRT equipped with "current loop". Hardwire the controller to: bps = 1200, 2400, or 4800 bps, 8 data bits, 7 data plus parity, one stop bit. Hook-up cable as shown. See rate/distance table for maximum length of cable.

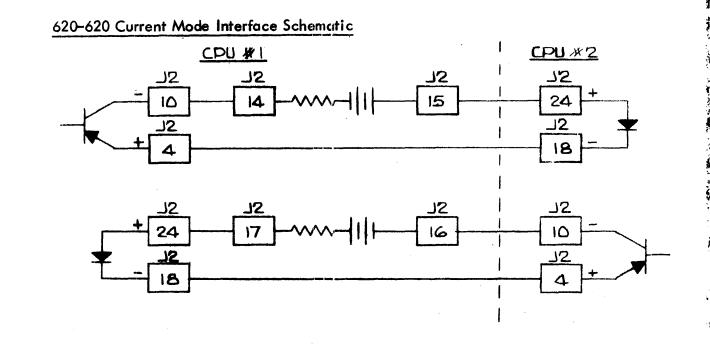

Hardwire controller to: bps = 1200, 2400, 4800, or 9600 bps. Set to 8 bits plus odd or even parity, 1 stop bit. Hook up cable as shown. See rate/distance table for max. length of cable.

ذ

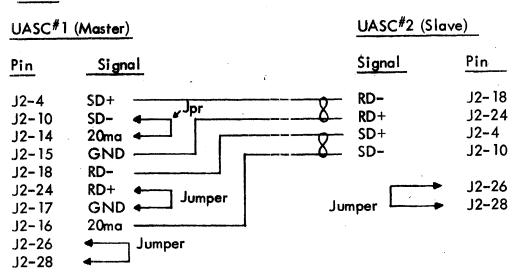

4.6.3 (Cont'd)

Cable

Note: Current limiting resistors R9 and R12 on both ends are shorted out for this application.

96A0039-000B

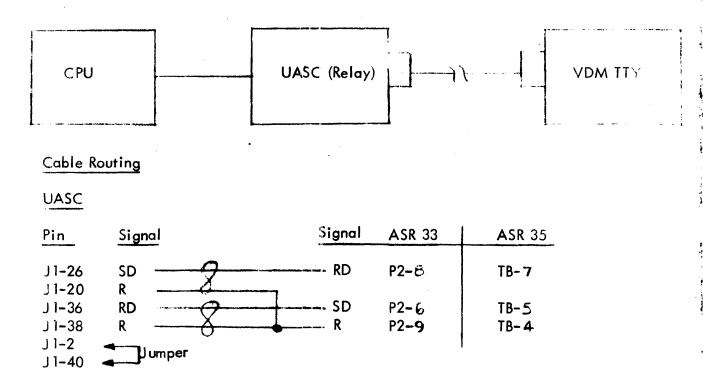

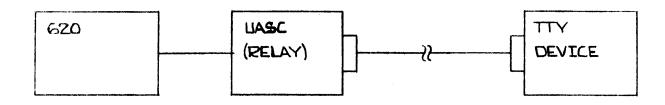

### 4.7 Usage of Relay Version

This model is equipped with a set of electromechanical (reed) relays and is designed for usage with teletype-telegraph (current loop) type equipment. It can handle 5 or 8 level applications such as (5 level) models 28, 32 (8 level) models 33 and 35 teletypes and 83B type polling (5 level) equipment. The relay interface can be hooked up to handle full or half-duplex "loops" as required. In the case of half-duplex operation, the CPU must ignore the "received" input while it is sending. The "received" input (while sending) is an "echo" only.

### 4.7.1 Full Duplex - Cable Routing - Schematic

CODE

IDENT NO. 21101