# Customer Engineering Division

# WANG COMPUTER SYSTEMS 60 & 80

# Volume 1

# **System Introduction**

© Wang Laboratories, Inc., 1977

2ND Edition (Reprint) MAY, 1982

#### NOTICE:

This document is the property of Wang Laboratories, Inc. Information contained herein is considered company proprietary information and its use is restricted solely to the purpose of assisting you in servicing Wang products. Reproduction of all or any part of this document is prohibited without the consent of Wang Laboratories.

LABORATORIES, INC.

ONE INDUSTRIAL AVENUE, LOWELL, MASSACHUSETTS 01851, TEL. (617) 061-4111, TWX 710 343-0760, TELEX 94-7421

November, 1977

#### PREFACE

The WCS 60 and 80 systems represent a significant departure from Wang's pre-1977 product lines. At the heart of a WCS 60/80 system, the 2200VS Central Processor operates on a completely different set of concepts. New terminology introduced in this text during the development of each concept must be understood before details of 2200VS hardware are studied.

Publications for WCS 60/80 Service training/support are grouped into four categories: 1)Pretraining, 2)In-class handouts, 3)a Post-training package, and 4), Miscellaneous 2200VS documentation.

Pretraining documentation is primarily intended for individuals scheduled for formal WCS 60/80 training at the Home Office. Each of the publications in the 'Pre-training package' must be read thoroughly before the prospective trainee attends class.

Pre-Training Publications:

- 1. 2200VS, Volume I System Introductory Manual (CE)

- 2. 2200VS Programmers's Introduction (WL#800-1101PI)

- 3. CDC Microcircuits Manual (OEM)

In-class handouts will be used as training aids for daily classroom and laboratory sessions. The following publications comprise the 'in-class handouts' package, and must be kept in class.

In-Class Handouts:

- 1) CP Hardware Manual (CE)

- 2) IOP Master Processor Manual (CE)

- 3) Parallel Workstation IOP Manual (CE)

- 4) IOP Tester Manual (CE)

i

Hard/Floppy Disk I/O Manual (CE) 5) 2200VS, Volume II - System Installations, Diagnostics, and 6) Troubleshooting (CE)\* 2200VS, Volume III-Preventive Maintenance (CE)\* 7) 2200VS Pre-Instaliation Guide (Site preparation)\* 8) 2200VS Principles of Operation (WL#800-1100PO) 9) 2200VS Assembly Language Manual (WL#800-1200AS) 10) 2200VS System Frogrammer's Guide (WL#800-1103SP) 11) IBM Assembly Language Student Text (IBM #SC20-1646-6) 12) Chaintrain - Logic & Troubleshooting Manual (OEM) 13) Chaintrain - Maintenance Instructions Manual (OEM) 14) Chaintrain - Operation Instructions Manual (OEM) 15) Chaintrain - Principles of Operation Manual (OEM) 16) 17) CDC 75 Meg Disk Manuals (OEM): a) CDC Storage Module Drive BK4XX-BK5XX b) CDC BK4XX-BK5XX Installation & Checkout c) CDC BK4XX-BK5XX Diagrams & Wire Lists 18) CDC 288 Meg Disk Manuals (OEM) a) CDC Storage Module Drive BK6XX-BK7XX b) CDC BK6XX-BK7XX Installation & Checkout 19) CDC Field Test Unit Manual (OEM) 20) Kennedy Mod. 9100 Vacuum Column Tape Transport Manual (OEM) 21) Kennedy Mod. 9219 Formatter Manual (OEM) Schematics for all Wang circuit boards 22)

The Post-training package can be used by those who have already attended a WCS 60/80 seminar. These publications are as follows:

Post-Training Package:

- 1) Model 61V Printer Manual (CE)\*

- 2) Zilog Z-80 Manual (CE/OEM)

- 3) 2200VS Cobol Language Ref. Manual (WL#800-1201CD)

- 4) 2200VS Executive Introduction Menual (WL#800-1105EI)

- 5) 2200VS BASIC Language Ref. Manual (WL#800-XXXX)\*

\*Not published as of November, 1977.

ii

- 6) 2200VS File Management Utilities Manual (WL#800-1300 FM)

- 7) 2200VS RPG II Reference Manual (WL#800-XXXX)\*

- 8) CDC 'Hawk' Training Manual (CE/OEM)

- 9) CDC 'Hawk' Training Manual (CE/OEM)

The final category is rather informal, and consists of certain user manuals, data sheets, product bulletins, competetive profiles, etc. The present list of such publications is as follows:

Miscellaneous Documentation:

- 1) 2200VS Brochure (WL#700-4507)

- 2) 2200VS Product Bulletin No. 155

- 3) 2200VS/WCS 60/WCS 80 Data Sheet (WI.#800-2101, 2201)

- 4) 2200VS Peripherals Data Sheet (WL#800-2102)

- 5) 2200VS Languages Data Sheet (WL#800-2201)

- 6) 2260V Ten-Megabyte Disk Data Sheet (WL#800-XXXX)\*

- 7) 2265V-1 (75-Meg Disk) Data Sheet (WL#800-XXXX)\*

- 8) 2265V-2 (288-Meg Disk) Data Sheet (WL#800-XXXX)\*

- 9) 2231W-1 (120 cps Matrix Printer) Data Sheet (WL#800-XXXX)\*

- 10) 2231W-2 (120 cps Matrix Printer) Data Sheet (WL#800-XXXX)\*

- 11) 2221W (200 cps Matrix Printer) Data Sheet (WL#800-XXXX)\*

- 12) 2261W (240 lpm Matrix Printer) Data Sheet (WL#800-XXXX)\*

- 13) 2263V-1 (400 1pm Train Printer) Data Sheet (WL#800-XXXX)\*

- 14) 2263V-2 (600 lpm Train Printer) Data Sheet (WL#800-XXXX)\*

- 15) 2209V (1600V)I 9-Track Tape) Data Sheet (WL#800-XXXX)\*

- 16) 220V06 Telecommunications Data Sheet (WL#800-XXXX)\*

Presently, requests for 2200VS documentation 'packages' can only be honored for prospective WCS 60/80 students.

The remaining 11 items of this memorandum generally describe the contents of existing and proposed 2200VS user manuals.

\*Not published as of November, 1977.

#### 1. 2200VS PROGRAMMER'S INTRODUCTION (WL #800-1101PI)

This manual was previously known as the "8300 System Introduction". It preserves all of the material from the original System Introduction with the exception of Chapter 1 (general discussion of system features), which moves to the new "EXECUTIVE JNTRO-DUCTION TO THE 2200VS" (see next page). New material was added on Data Management functions (file types and access methods, shared files, etc.). Specifically, the manual covers the following topics:

Introductory Concepts Workstation Characteristics Command Processor System Utilities Procedure Language Data Management Functions

2. 2200VS COBOL REFERENCE MANUAL (WL #800-1201CB)

Reference manual for 2200VS COBOL, with material on multiple indexing, additional workstation support features, shared files, etc.

3. 2200VS PRINCIPLES OF OPERATION (WL #800-1100PO)

General descriptions of machine architecture, machine instruction set, and I/O devices.

4. 2200VS ASSEMBLER LANGUAGE REFERENCE MANUAL (WL #800-1200AS)

Reference text for 2200VS macroassembler.

\*Not published as of November, 1977.

### 5. 2200VS SYSTEM PROGRAMMER'S GUIDE (WL #800-1103SP)

A collection of "all the things you wanted to know about the system but were afraid to ask". Included are descriptions of all super- visor calls (SVC's), system macros, and control blocks.

6. EXECUTIVE INTRODUCTION TO THE 2200VS (WL #800~1105)

A brief, general introduction to major system features intended for the edification of management. This manual will incorporate material from Chapter 1 of the present "8300 System Introduction", as well as the 2200VS Product Bulletin, to provide clear, simplified discussions of concepts such as virtual memory, print spooling, background processing, etc.

7. 2200VS BASIC LANGUAGE REFERENCE MANUAL (WL #800-XXXX)\*

Reference manual documenting the elusive 2200VS version of BASIC.

8. 2200VS FILE MANAGEMENT UTILITIES (WL #800-1300FM)

Documentation of the CONTROL, DATENTRY, and REPORT utilities. Oriented towards non-programmers who wish to use these utilities for data entry and report generation.

9. 2200VS SYSTEM MANAGEMENT GUIDE (WL #800-XXXX)\*

A manual intended for use by system administrators. This manual covers topics of interest to those responsible for system administrative functions, including:

Security (transplanted from "Console Operator's Guide") File Backup Procedures Error Reporting and Generating Formatted Dumps System I/O Error Log System Performance Evaluation (when is more memory needed, or another disk, etc.)

v

## 10. 2200VS SYSTEM OPERATION GUIDE (WL #800-1102SO)

Previously titled "8300 Console Operator's Guide", this manual covers various topics of interest to the system operator, including:

Print Spooling Background Processing Operational Characteristics of all peripherals

11. 2200VS RPG II REFERENCE MANUAL (WL #800-XXXX)\*

Reference Manual for RPG II.

DIRECT ALL COMMENTS ON THIS MANUAL TO THE TECHNICAL WRITING STAFF OF WANG LABS' CUSTOMER ENGINEERING DIVISION.

\*Not published as of November, 1977.

TABLE OF CONTENTS

SECTION 1 SYSTEM OVER JIEW

| 1.1  | INTRODUC PIOR                                                           |            |  |

|------|-------------------------------------------------------------------------|------------|--|

| ι.2  | INTERACTIVE OPERATION                                                   | 1-1<br>1-1 |  |

| 1.3  | THE 'COMMAND PROCESSOR'                                                 |            |  |

| 1.4  | MULTIPLE USERS                                                          | 1-2        |  |

| 1.5  | MULTILINGUAL SYSTEM                                                     | 16<br>17   |  |

| 1.6  | LARGE ON-LINE FILES/FILE MANAGEMENT FACILITIES                          |            |  |

| 1.7  | VIRTUAL MEMORY                                                          | 1-8        |  |

|      | 1.7.1 GENERAL                                                           | 1-9        |  |

|      |                                                                         | 1-9        |  |

| 1.8  | 1.7.2 ADVANTAGES AND DISADVANTAGES OF "VIRTUAL MEMORY"<br>EXPANDABILITY |            |  |

| 1.9  | MAJOR PERFORMANCE FEATURES                                              | 1-15       |  |

|      | 1.2.1 AUTOMATIC PROGRAM SHARING                                         | )-15       |  |

|      | 1.9.2 INDEPENDENT L/O PROCESSORS                                        | 1-15       |  |

|      | 1.9.3 AUTOMATIC DATA COMPACTION                                         | 1-16       |  |

|      | 1.9.4 AUTOMATIC CRINT SPOOLING                                          | 1-16       |  |

|      | 1.9.5 BACKGROUND PROCESSING                                             | 1-17       |  |

| 1.10 | USER CONVENIENCE FEATURES                                               | 1-17       |  |

|      | 1.10.1 DATA ENTRY/FILE MAINTENANCE                                      | 1-18       |  |

|      | 1.10.2 INTERACTIVE TEXT EDITOR                                          | 1-18       |  |

|      | 1.10.3 INTERACTIVE DEBUG FACILITY                                       | 1-19       |  |

| 1.11 | ADDITIONAL SYSTEM UTILITIES                                             | 1-19       |  |

|      | FILE PROTFOTION AND SECURITY                                            | 119        |  |

| 1.13 |                                                                         | 1-22       |  |

| 1.14 | HARDWARE CENERAL                                                        | 1-23       |  |

|      | 1.14.1 THE CENTRAL PROCESSING UNIT (CPU)                                | 1-23       |  |

|      | 1.14.2 I/O PROCESSORS (107'S)                                           | 1-24       |  |

|      | 1.14.3 WORKSTATION                                                      | 1-25       |  |

|      | 1.14.4 DISKS                                                            | 1-26       |  |

|      | 1.14.5 PRINTERS                                                         | 1-27       |  |

|      | 1.14.6 TAPS DRIVE                                                       | 1-30       |  |

|      | 1.14.7 COMUNICATIONS                                                    | 1-34       |  |

|      | THE CONTRACTOR AND                                                      | 1-35       |  |

## SECTION 2 SYSTEM CONCEPTS

| 2200VS - VIRTUAL MEMORY                             | 2-1                                                                                                                                                        |

|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.1.1 A COMPARISON TO EXISTING 2200's               | 2-1                                                                                                                                                        |

| 2.1.2 RELATION OF VIRTUAL MEMORY TO PHYSICAL MEMORY | 2-2                                                                                                                                                        |

| COMPILERS, INTERPRETERS, AND ASSEMBLERS             | 2-14                                                                                                                                                       |

| 2.2.1 COMPILERS                                     | 2-14                                                                                                                                                       |

| 2.2.2 INTERPRETERS                                  | 2-15                                                                                                                                                       |

|                                                     | 2-16                                                                                                                                                       |

| THE 'OPERATING SYSTEM'                              | 2-18                                                                                                                                                       |

|                                                     | 2.1.1 A COMPARISON TO EXISTING 2200's<br>2.1.2 RELATION OF VIRTUAL MEMORY TO PHYSICAL MEMORY<br>COMPILERS, INTERPRETERS, AND ASSEMBLERS<br>2.2.1 COMPILERS |

# SECTION 3 INTRODUCTION TO 2200VS HARDWARE

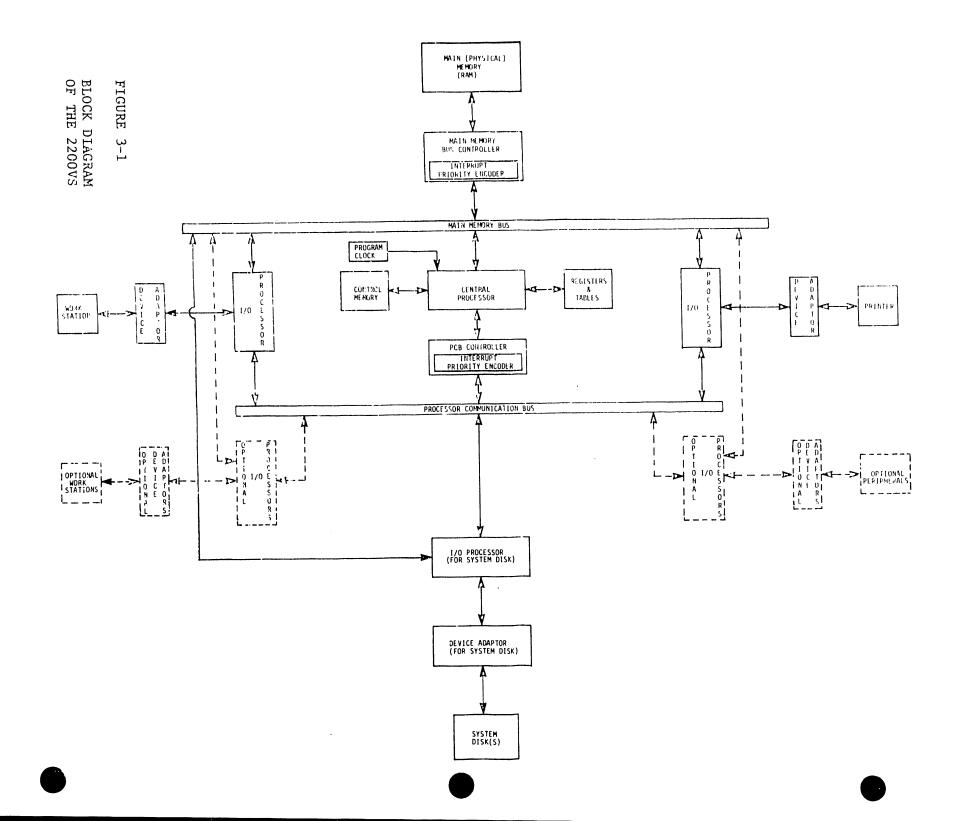

| 3.1 | SYSTEM  | BLOCK OVERVIEW                             | 3-1    |

|-----|---------|--------------------------------------------|--------|

|     |         | GENERAL                                    | 31     |

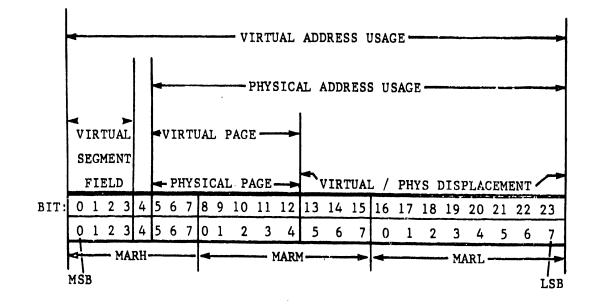

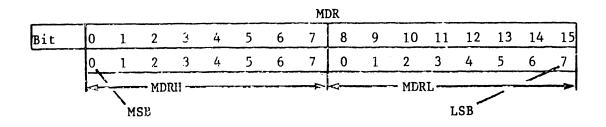

|     |         | DATA ORGANIZATION IN THE 2200VS            | 3/1    |

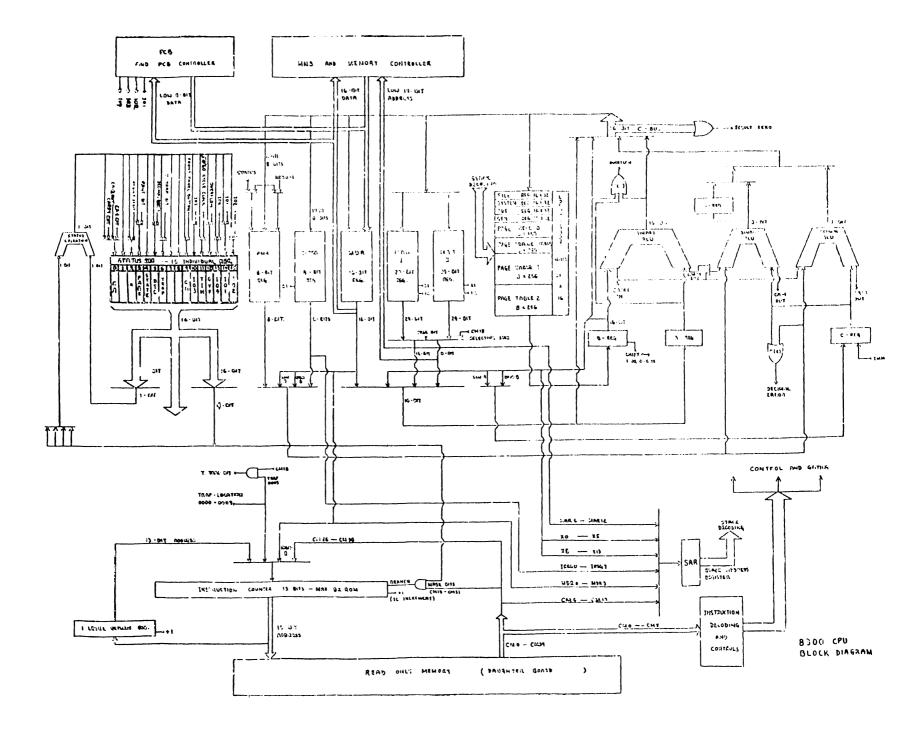

| 3.2 |         | ITRAL PROCESSOR                            | 3-t;   |

|     |         | GENERAL                                    | 36     |

|     |         | CENTRAL PROCESSOR HARDWARE DETAILS         | 3-12   |

|     |         | INSTRUCTION SETS                           | 3-28   |

|     |         | 3.2.3.1 MICROINSTRUCTION FORMAT IN CONTROL | 3-28   |

|     |         | MEMORY                                     |        |

|     |         | 3.2.3.2 MACHINE INSTRUCTION FORMAT         | 333    |

|     | 3.2.4   | INTERUPTS                                  | 3-43   |

|     |         | 3.2.4.1 GENERAL                            | 343    |

|     |         | 3.2.4.2 TYPES OF INTERRUPTS                | 3~43   |

| 3.3 | THE INI | PUT/OUTPUT PROCESSOR (7110 PC)             | 3-46   |

|     |         | THE MICROPROCESSOR (MP)                    | 3-48   |

|     |         | 3.3.1.1 REGISTER STRUCTURE                 | 3-49   |

|     |         | 3.3.1.2 ARITHMETIC LOGICAL UNIT (ALU)      | 3-50   |

|     |         | 3.3.1.3 CONTROL MEMORY (CM)                | 354    |

|     |         | MAIN MEMORY BUS/LOGIC                      | 3~54   |

|     | 3.3.3   | PROCESSOR COMMUNICATION BUS LOGIC (PCB)    | 3 55   |

|     |         | 3.3.3.1 INPUT/OUTPUT INTERRUPTIONS         | 3- 55  |

|     |         | 3.3.3.2 I/O TACK TERMINATION/COMPLETION    | .i −60 |

|     | 3.3.4   | DEVICE ADAPTER (DLI OR DA)                 | 368    |

|     | 3.3.5   | THE TOP MP MICROINSTRUCTION SET            | 369    |

| 3.4 | MAIN M  | EMORY                                      | 3 71   |

| 3.5 | DISK S  | TORAGE PHYSICAL DESCRIPTION                | 3-78   |

|     | 3.5.1   | VOLUME LABEL                               | 378    |

|     | 3.5.2   | VOLUME TABLE OF CONTENTS                   | 3-78   |

|     | 3.5.3   | EXTENTS                                    | 3-79   |

## SECTION 4 WORKSTATION CHARACTERISTICS

| 4.1 | INTRODUCTION |                                      | 41   |

|-----|--------------|--------------------------------------|------|

| 4.2 | THE CR       | r                                    | 4-1  |

|     | 4.2.1        | THE SCREEN AND CURSOR                | 4 -1 |

|     | 4.2.2        | SCREEN FORMATTING                    | 4-1  |

|     | 4.2.3        | FIELDS                               | 4-2  |

|     | 4.2.4        | FIELD ATTRIBUTE CHARACTERS           | 4-3  |

|     | 4.2.5        | TABS                                 | 4-5  |

|     | 4.2.6        | AUDIO INDICATORS                     | 4-5  |

| 4.3 | THE KEY      | Y BOARD                              | 4-6  |

|     | 4.3.1        | CURSOR FOSITIONING KEYS              | 4-6  |

|     | 4.3.2        | DATA ENTRY KEYS                      | 4-9  |

|     | 4.3.3        | SPECIAL KEYS                         | 4-10 |

|     | 4.3.4        | KEYS COMMUNICATING WITH THE COMPUTER | 4-11 |

| APPENDIX A | GLOSSARY                    | A-1  |

|------------|-----------------------------|------|

| APPENDIX B | 2200VS COMMON IC'S          | A-33 |

| APPENDIX C | UPGRADING THE WCS/60        | A-57 |

| APPENDIX D | UPGRADING THE WCS/80        | A-58 |

| APPENDIX E | CONFIGURATIONS              | A-59 |

| APPENDIX F | SPECIFICATIONS              | A-61 |

| APPENDIX G | 2260V FIXED/REMOVABLE DISK  | A-63 |

| APPENDIX H | 2265V-1 REMOVABLE DISK PACK | A-64 |

| APPENDIX I | WORK STATION                | A-65 |

| APPENDIX J | 2261V PRINTER               | A-66 |

# SECTION SYSTEM **OVER**-VIEW

#### SECTION 1

#### SYSTEM OVERVIEW

#### 1.1 INTRODUCTION

The Wang 2200VS, also known as the 8300, is an interactive, multiuser, general-purpose computer.

Initially, the 2200VS will be offered in two packaged systems, the WCS/60 and the WCS/80. A standard WCS/60 System will include the 2200VS computer with 64K of memory, a 308K diskette drive, a 10 megabyte disk drive, one workstation, and a 240 lpm printer. A standard WCS/80 will include a 2200VS computer with 256K of memory, a 308K diskette drive, two 75 megabyte disk drives, a workstation, and a 240-line-per-minute printer. Both systems can be expanded with additional memory, more disks, and more workstations. Both are designed to serve, even in their minimal configurations, as complete commercial data processing systems.

#### 1.2 INTERACTIVE OPERATION

The 2200VS, like all previous 2200 systems, is "interactive", allowing users to communicate directly with the system from workstations. The system requests user-specified data and provides useful information in a series of clear, nontechnical prompts displayed on the workstation screen. Such prompts may ask the user to "fill in the blanks" with requested data, or select a desired item from a number of displayed options.

Many other systems require the use of a complex special language for issuing instructions to the system and controlling system functions. On the 2200VS, no special language is required. All system functions are invoked through a special program called the 'command processor'. The user simply chooses the desired function from a displayed menu, then responds to any subsequent prompts asking information for that function. If the user response is erroneous or insufficient, the system returns an error message which identifies the problem, and, in many cases, suggests a possible solution.

Running a program on any existing 2200 processor is a trivial task: The user simply loads the program, then keys RUN and EXECUTE. On the 2200VS, it is scarcely more complicated. The user simply chooses the RUN PROGRAM function from the Command Processor Menu, then types in the program name, disk library, and volume in which it is located (this is the equivalent of performing a LOAD DC operation on the 2200). When this information is entered, the user keys ENTER to begin program execution.

At any point during the execution of a program, a user can interrupt the program by keying HELP. The HELP key is somewhat analogous to the HALT/STEP key on the 2200: it temporarily halts program execution, without destroying any critical information or closing any files. The program can be resumed from the point of interruption with a CONTINUE command. While a program is interrupted, the user has access to all system functions. He can, for example, examine the status of open files or I/O devices, scratch or rename files, or begin debug processing. Once these functions are completed, normal execution of the interrupted program can be continued.

1.3 THE 'COMMAND PROCESSOR'

All user communication with the 2200VS is carried out by issuing interactive 'commands' which direct the Operating System\* to perform a variety of tasks. Commands, selected from a 'Command Processor Menu', are used to perform such operations as running programs, setting default parameters, scratching and renaming files, initiating debug processing, and examining and modifying various aspects of the system status.

In general, if any program parameter is inadvertently omitted or specified incorrectly, the Command Processor simply repeats the appropriate screen prompt so that the user may enter the correct value.

The Command Processor has two slightly different versions of its menu. The "normal" Command Processor menu is displayed whenever no program is running at a given work station. The user is therefore

provided immediate access to the system upon completion of any program, so that a new program or command can be initiated at once. If a running program is interrupted prior to completion, as the result of a fatal execution error, etc., the Command Processor displays a modified Command Processor Menu, which permits the user to either continue program execution or cancel the program.

A program cannot be continued while a selected 'command' from the modified menu is executing. Nor, can a second program be run at the same work station while the first program is interrupted. In order to run a new program, the current program must be terminated, either through normal completion or cancellation by the user. For this reason, the RUN command does not appear in the modified Command Processor Menu. RUN is replaced by CONTINUE.

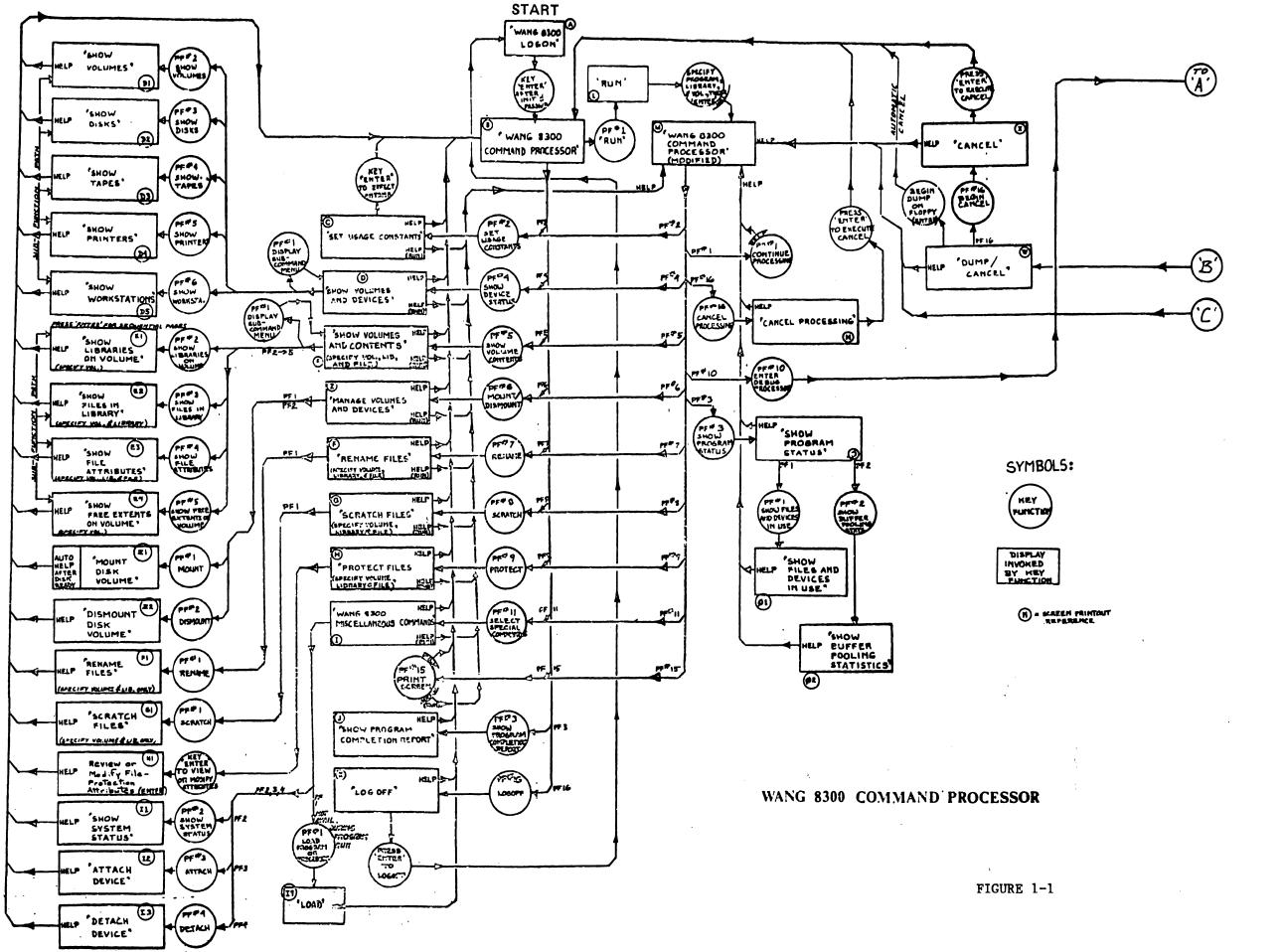

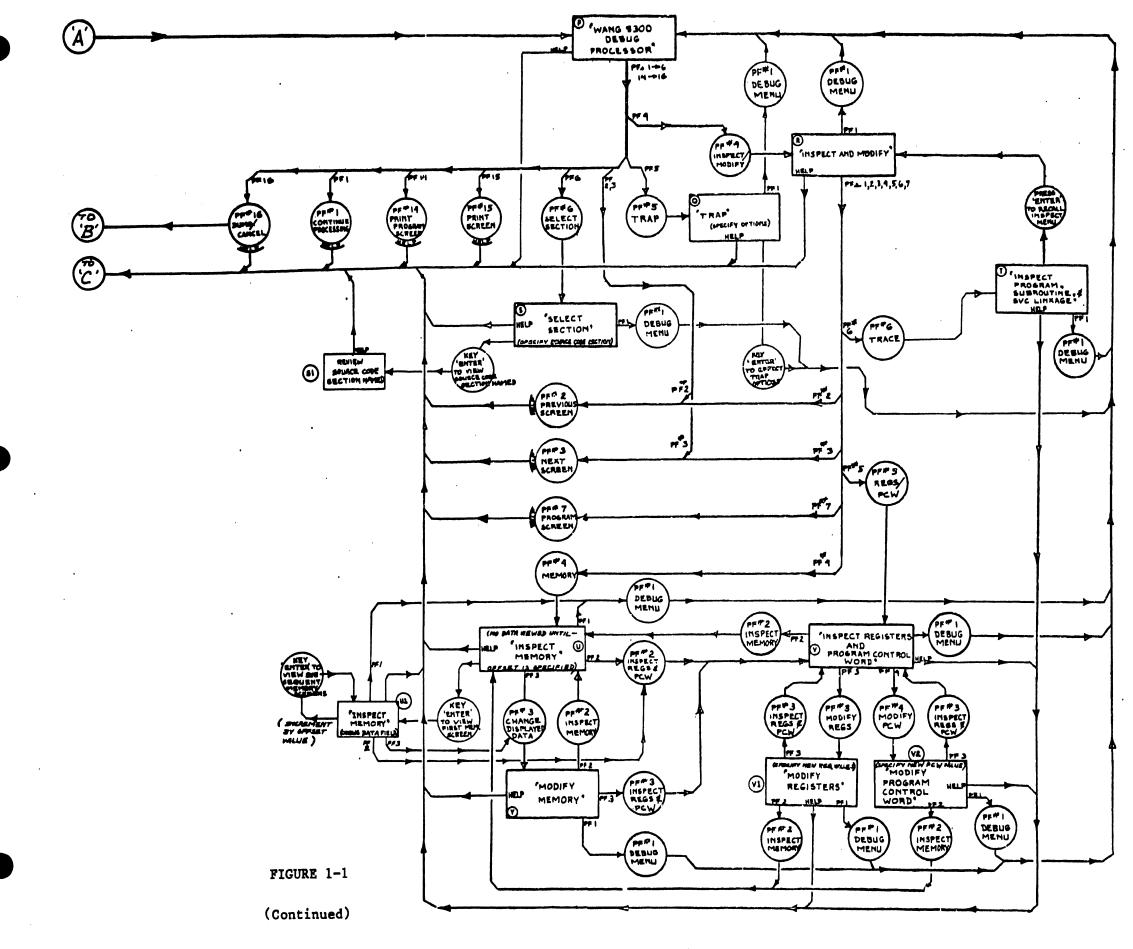

The diagram on the following page is a map of the 2200VS/8300 Command Processor. Each circle on the map indicates that some keyboard function takes place; each rectangle on the map represents a screen that is presented to the user by the Command Processor. The map takes the workstation operator from LOGON, through all primary functions of the Command Processor, including the Debug Processor. Note that certain screens may be invoked by either the Command Processor or the <u>Modified</u> Command Processor. When the HELP key is used during a program run, the <u>Modified</u> Command Processor is invoked, rather than the Command Processor. The Command Processor map should be used in conjunction with the Programmer's Introduction Manual (WL# 800-1101PI-01) when familiarizing oneself with the 8300 workstation.

\*See Section 2; Introductory Concepts.

It is important to understand that, although the system can process two or more tasks concurrently from several work stations, a single work station <u>cannot</u> perform two or more tasks concurrently. Only <u>one</u> program or procedure may be run from each work station at any time.

#### 1.4 MULTIPLE USERS

The 2200VS supports multiple workstations; in a WCS/60 configuration, a maximum of 16 workstations can be supported; in a WCS/80, the maximum is 24. Each workstation can be running its own job concurrently with the others. Since each "job" is actually a separate program, such a system is often referred to as a 'multiprogramming' system. Of course, since there is only one central processor and one memory, it is not possible for two or more programs actually to be executing at exactly the same instant. On the 2200VS, all programs share a common set of resources. Each program (or some portion of it) is kept in its own location(s) in memory. The central processor permits each program to run for a short period of time, then interrupts and permits enother program to run for a similar brief period; this process continues indefinitely, or until all programs terminate. Because the central processor is fast and is managed efficiently, the illusion is created that each user's program is running without interruption, simultaneously with all other programs.

The key to the success of such a scheme is the Operating System software, which must manage the use of common resources such as the central processor, memory, and I/O devices, with maximum efficiency. The 2200VS operating system is designed for such efficiency; it is designed to guarantee that each user will have reasonable response time for his program, and elso ensure that each program runs without interference from others. The process of sharing a single computer among many users is called 'distributed processing'. Each user can proceed exactly as if he had access to his own private system.

The 2200VS Operating System imposes no special restrictions on the types of jobs which can be run concurrently from each workstation. It is not unlikely, for example, that an installation might have two or more workstations running a large data entry application, while other workstations are running an order-entry program, and still other workstations are being used by programmers for program development. Such a system obviously provides great flexibility for the user, who is not forced to purchase several different systems to perform different jobs.

Typically, in a multi-workstation configuration, one workstation is designated as the 'system console'. In addition to running normal programs, the system console provides a second mode of operation in which it can control a number of special system features not accessible from regular workstations, including 'print spooling' and 'background processing', explained in paragraphs 1.8.4 and 1.8.5.

#### 1.5 MULTILINGUAL SYSTEM

Unlike previous 2200 Systems, the 2200VS supports multiple languages. ANSI COBOL and BASIC, as well as Assembler Language is currently available. Also unlike previous systems, 2200VS languages are 'compiled' rather than 'interpreted'.

COBOL, (Common Business Oriented Language), is one f the most popular programming languages in use today for commercial data processing applications. COBOL programs read like ordinary business English, yet the language provides an array of powerful record formatting, data manipulation, and file handling capabilities which are particularly important for data processing applications. In part, also, COBOL's popularity derives from the fact that it is the only major language subject to an industry-wide standard, administered by the American National Standards Institute (ANSI).

For the programmer who wishes to obtain a greater degree of control over the system and write more efficient programs, the 2200VS also provides an Assembler language. Since the instruction set of a

machine defines the complete set of elementary capabilities provided by the machine, Assembler language provides the programmer with access to the machine's total repertoire of functions.

The 2200VS Assembler also allows a programmer to define a routine consisting of a series of instructions, and assign a name to the routine. The name can then be specified (instead of the entire routine) as a single instruction in a program. Such named routines are called "macros," and the names assigned to them are called "macroinstructions." Because the 2200VS Assembler permits the definition of macros, it is also referred to as a 'macroassembler'.

It is important to note that the machine instruction set of the 2200VS contains all instructions available on the IBM 360, along with most available on the 370. Programmers familiar with IBM 360/370 Assember Language should therefore find 2200VS Assembler easy to learn.

The 2200VS Procedure Language allows users to create special text files which perform many of the operations normally executed interactively by the user at a workstation. Some typical procedures would be: running two or more programs sequentially, supplying run-time parameters to a program, and scratching or renaming programs. Procedures can reduce the number of keystrokes and interactions required of a user who is running a program.

'Compilers', 'Interpreters', and 'Assemblers' are discussed more thoroughly in Section 2.

1.6 LARGE ON-LINE FILES/FILE MANAGEMENT FACILITIES

To support applications with large on-line data base requirements, the 2200VS supports extensive on-line data storage capacity. Both the 10-megabyte and 75-megabyte disk units are supported. In a WCS/60 configuration, the maximum disk storage capacity is 150 megabytes; in a WCS/80, the maximum is 600 megabytes.

The 2200VS 'Data Management System' provides a comprehensive disk file access and maintenance capability. Two types of 'files' are supported on the system: 'sequential files', in which records are stored in the order in which they are written; and 'indexed files', in which records are stored in order of their key values. In both types of files, records may be accessed either sequentially or randomly. A third access mode, dynamic access mode, permits a program to switch back and forth between sequential and random access on the same data file.

The indexed file system permits multiple indexes for a single file. This feature enables a record to be accessed on different keys for different purposes. An employee record, for example, may be accessed by employee name for personnel purposes and by employee number for payroll purposes.

A single file can be shared among several different users. Several users may therefore perform updates and/or inquiry operations on a common file concurrently. In data entry applications, for example, all operators can directly update a single master file. The additional steps of creating temporary files for all operators, and then merging them together are therefore eliminated.

The 'Data Management System' is discussed in more detail in Section 2.

1.7 VIRTUAL MEMORY

1.7.1 GENERAL

To understand the need for virtual storage, one must first understand the characteristics and shortcomings of conventional <u>real</u> storage management. When a program is entered into a computer, it must be tailored by the programmer to fit within the confines of that computer's physical (real) memory. Secondly, the memory space taken up by that program must be allocated in one piece. Other data or programs cannot be allocated to the same section of real memory. If a program requires (for example) 50,000 bytes of real storage, but during execution uses only 12,000 bytes actively, the remaining 38,000 bytes of real storage are effectively wasted. If a program is too large to fit into the available memory, it must be broken up into a series of modules, or overlays, each of which is small enough to fit in memory. Similarly, if there is not enough memory to hold all of the data used by a program, special procedures must be written into the program to handle the data in smaller chunks.

To further complicate problems, Operating System routines also take real memory space. Real storage tends to become 'fragmented'; that is, a condition occurs where there are many unused storage locations, but these are spread out all through real memory, and there is no single piece of contiguous storage large enough to meet a current demand for real memory space.

Finally, if a memory upgrade is purchased, programs must be revised, sometimes extensively, to take advantage of the added memory. The net effect of these considerations is that programs must be designed to meet the restrictions imposed by a particular machine, rather than to most efficiently deal with the problems these machines are intended to solve.

To provide efficient management of real storage space, memory allocation responsibilities must be taken away from the user. In the 2200VS, this management function is performed by the Operating System.

The process by which blocks of program address space are placed in ('bound' to) a computer's real storage space for execution is called 'relocation'. The 2200VS uses a 'dynamic relocation' process

as the foundation for its virtual memory system. Indeed, one of the most important features of the 2200VS is its 'virtual memory' system. The term 'virtual memory' more specifically refers to a technique of memory management is which the Operating System uses disk storage as an extension of physical memory, automatically ensuring that only those sections of a program and its associated data which are frequently referred to or 'referenced' during program execution are kept in physical memory; less frequently referenced sections are kept on disk until needed.

## 1.7.2 ADVANTAGES AND DISADVANTAGES OF "VIRTUAL MEMORY"

Virtual memory can best be explained by comparison with many larger computer systems (in the 2200VS's price range) that do not have virtual memory capability. On previous 2200 models, if a programmer wrote a program that exceeded the total available real memory space, he would have had to carefully break the program into a series of modules, or overlays, each of which would have been small enough to fit in real memory. As previously stated, this procedure involves the addition of special software (a 'procedure') to control the overlay process.

On a multiprogramming system, where several users share the same physical memory, this problem becomes even more complex. Each user must know how much of the total memory is available to him. One solution is to divide the total memory into a number of 'partitions' of fixed size, and give each user his own partition. Such systems are called <u>fixed partition</u> systems. They are simple but inefficient, since when a user is not using his entire partition, the unused portion remains vacant, even if a user in another partition requires more memory for his application. A refinement of this technique, called <u>dynamic partitioning</u> makes more efficient use of memory by expanding or contracting the size of each user's partition as his memory requirements increase or decrease (subject, of course, to the requirements of other users). Partitioning systems have commonly been

used on minicomputers (such as certain DEC systems). An alternative to partitioning used on some systems is <u>swapping</u>. In a system that employs swapping, each user has access to all of the available real memory. The system manages this by swapping entire programs in and out of memory from the disk. Each program is brought into memory, permitted to run for a brief interval ('time slice'), and then is swapped out while another program takes its place in memory. One example of a competitive system which utilizes swapping is the IBM System 34.

These systems still share two serious inefficiencies:

- 1. They force the programmer to tailor programs to fit the available memory.

- 2. They require the user to modify his software in order to take advantage of additional memory.

These drawbacks are eliminated with a virtual memory system.

In a virtual memory system, the Operating System (rather than the programmer) automatically performs the function of fitting a program to the available real memory space. The Operating System accomplishes this task by first dividing the available physical memory into a number of fixed-size 'page frames'. On the 2200VS, each page frame is 2K bytes in size; thus a 64K system would be divided into 32 page frames. The program address space is correspondingly divided into a number of pages, also 2K bytes in size. When program execution begins, the Operating System loads the first page of the program into an available page frame (2K block) in physical memory. Other page frames may be loaded with the 'first pages' from other programs. If additional page frames are available, the system loads in as many pages of the programs as there are available page frames in memory.

As program execution proceeds, reference may be made (either through the normal sequence of execution or as the result of a branch) to a section of the program not currently located in physical memory. When such a reference occurs, the system automatically interrupts program execution. It then locates the referenced page in virtual memory (on disk), loads that page into an available page frame in physical memory, and resumes execution of the program. This entire process takes place automatically without the user's intervention or knowledge.

Because the Operating System automatically handles the job of overlaying each program and transferring pages in and out of memory as necessary, the amount of physical memory available does not impose any constraint on the program size. The programmer can write his program to meet the needs of the application most efficiently, without regard for the size of that program or the physical characteristics of the system.

The total amount of virtual memory accessible to each user on the 2200VS is one megabyte. Each user has, in effect, his own one-megabyte computer. So long as his program and its associated variable data do not exceed one million bytes in size, there is no need to break it into overlays. Note that the one megabyte figure for each user's accessible virtual memory space is constant, and is not dependent upon the amount of physical memory available, nor upon the number of users on the system. A 64K system with 16 users provides each user with one megabyte, as does a 512K system with only four users.

Although the <u>amount</u> of memory accessible to each user does not vary with the physical memory size or number of users, the system's <u>response time is affected</u> by these factors. The system guarantees each user one megabyte of virtual memory by keeping all unreferenced program pages on a disk, and storing only as many of these pages in physical memory as there are available page frames. If there are many

users on the system and relatively little physical memory, the total number of pages from each program which can be kept in memory at any time will be small. In this case, the system must spend a good deal of time transferring pages in and out of memory as program execution proceeds. (But even in this situation, a virtual memory system would still offer better performance than either a partitioning or a swapping system.) Since the disk I/O operations involved in page transfers are relatively slow compared to actual execution time once a page is in memory, inadequate memory with too many users can degrade system performance.

Conversely, whenever a memory upgrade is purchased in a <u>virtual</u> memory system, all programs experience an immediate improvement in response time with <u>no</u> changes in the software itself. In other types of systems, such performance improvement <u>may</u> be immediate, or may require software modification. Virtual memory is the <u>only</u> system which guarantees automatic performance improvement without software modification when more memory is added.

In summary, 2200VS vartual memory offers the following advantages:

- Allocation of memory is managed among several users more efficiently than other, less sophisticated memory management techniques.

- Each user is provided with access to a one-million-byte virtual memory (½ Meg program address space, ½ Meg modifiable data space).

- 3. Program size is made independent of memory size. Programs can be designed to meet the needs of the application, not the restrictions of a particular machine. The same programs will run on other 2200VS systems with different memory configurations.

- 4. Memory upgrades will automatically improve performance, without requiring modifications to existing software.

#### 1.8 EXPANDABILITY

The modular design of the 2200VS permits it to be readily expanded with additional physical memory, more disks, and additional workstations and printers. (Expansion can be carried out with no impact on existing software.)

A WCS/60 configuration can be expanded from the minimum 64K of memory to a maximum of 256K, in 64K increments. Disk capacity can be increased from the minimum 10 megabytes to a maximum of 150 megabytes. Up to 16 additional workstations can be added (for a total of 17). High-performance printers are also available.

A WCS/80 configuration can be expanded from the minimum 256K of memory to a maximum of 512K, with disk storage expandable from 150 megabytes up to 600 megabytes. The WCS/80 can support up to 23 workstations.

The user with distributed data processing requirements can therefore, purchase several system configurations of differing size and complexity, and utilize a common set of application software on all systems.

#### 1.9 MAJOR PERFORMANCE FEATURES

In addition to those already mentioned, the 2200VS provides a diversity of features designed to increase total throughput and improve system performance. Among these are: automatic program sharing, independent I/O processors, automatic data compaction, automatic print spooling, and background processing.

#### 1.9.1 AUTOMATIC PROGRAM SHARING

When two or more users are running the same program at the same time, it would be wasteful to keep a separate copy of the program in memory for each user. To avoid such duplication, the system auto-

matically causes several users to share the same copy of a program in memory whenever possible. The amount of memory saved by this feature can be substantial when, for example, a number of users are running a large data entry program, or several programmers are compiling COBOL programs. Program sharing also improves performance for all users by reducing the total number of pages which must be transferred in and out of memory.

#### 1.9.2 INDEPENDENT I/O PROCESSORS

Most conmercial application programs spend a good deal of their time performing I/O operations, such as reading and writing disk files, or sending output to a printer. On the 2200VS, I/O operations are handled by independent I/O processors, which control the transfer of data between memory and the various I/O devices. When a program requests an I/O operation, the central processor notifies the appropriate I/O processor, supplies it with any necessary information, then turns its attention to other processing while the I/O operation is carried out. Because each I/O processor can transfer information directly to or from memory without central processor involvement (i.e., 'Direct Memory Access -DMA'), the central processor is able to perform internal processing and internal processing guarantees that maximum use is made of the central processor, and increases overall system throughput.

#### 1.9.3 AUTOMATIC DATA COMPACTION

To conserve disk storage and hasten data transfer, the system provides an option to compress data records automatically before storing them on disk. In the compaction process, characters which are repeated three or more times in sequence are stored as a single character and a repetition count. Data compaction is performed automatically on all print files, and is performed on a data file if the "compressed records" option is specified when the file is

created. Compressed records are automatically expanded to their original format by the system when they are read back into memory, making the entire compaction process completely transparent to the user's software. Data compaction can reduce the disk storage requirements of many files up to 50% and contributes to improved performance by reducing the total number of characters which must be transferred between disk and memory for each record access.

#### 1.9.4 AUTOMATIC PRINT SPOOLING

Print spooling is a technique by which a job scheduled for printing is temporarily stored in a disk file rather than being sent directly to the printer. The 'Print files' thus created on disk are placed in a print queue under the control of the <u>system console</u>. When a printer becomes available, each job is then printed in the order determined by the print queue. Print spooling has the dual benefit of freeing individual workstations from dependence upon printer availability, and enabling the printers to be efficiently scheduled.

In most installations, printers are a common resource shared by all users. If printers are not used efficiently, system performance can be seriously degraded. For example, a user at one workstation who wishes to print only a few pages could be held up for hours while another user is printing a lengthy report. To avoid this situation, the 2200VS system provides this automatic 'print spooling' feature. Print spooling is one function of the 'Data Management System', which in turn is a subset of the Operating System software.

#### 1.9.5 BACKGROUND PROCESSING

Background processing is the automatic execution of batched lower-priority programs whenever there are no higher-priority programs being handled by the Operating System.

Although the 2200VS is designed primarily for interactive operation, it is possible to run jobs which require large amounts of

processor or I/O time, with a minimum amount of operator interaction, on a 'background' basis. Background jobs are run in a batch from the system conscle, rather than from the individual workstations. All workstations therefore remain available for interactive use even while a background job is running.

#### 1.10 USER CONVENIENCE FEATURES

While they may serve as useful first criteria for evaluating a system, performance and throughput do not tell the whole story. A system must also be designed so that its users can make the most effective use of its facilities, without being forced to undergo a long and arduous learning process. The 2200VS is a user-oriented system which offers a multitude of convenience features that make it easier to use by programmers and non-programmers alike. Among these features are: a versatile data entry, file maintenance, and report generation facility; an interactive text editor for entering and editing source programs; an easy-to-use symbolic debug facility for program debugging; and an assortment of system utility programs, including sort, copy and link routines.

#### 1.10.1 DATA ENTRY/FILE MAINTENANCE

Included in the 2200VS system software is a package of three programs designed to facilitate the creation and maintenance of data file, and the creation of reports based on such files. A setup utility permits the user to define a data file by specifying the types of data in each record of the file, and to design the screen display used to prompt an operator for information to be entered for each record. A data entry program can then be used to solicit operator input by displaying the defined prompts and accepting and validating entered data. A report utility, intended for use by management as well as programmers, provides great flexibility in the design of custom reports which present information from a data file in a useful and coherent format.

#### 1.10.2 INTERACTIVE TEXT EDITOR

Program development is greatly facilitated on the 2200VS by an interactive text editor. With the editor, a programmer can create and modify program files interactively using any one of the supported languages. Entering program text is as easy as typing it into the display, and editing an existing program is equally simple with the many editing functions provided. Interactive program development permits programmers to work with maximum productivity in the development and maintenance of programs.

#### 1.10.3 INTERACTIVE DEBUG FACILITY

In many cases, the process of identifying and correcting bugs in a program is more time-consuming than the writing process itself. To assist the programmer in this task, the 2200VS supports an easy-to-use interactive debug facility.

The 2200VS Debug Processor permits inspection of program code, and permits inspection and modification of data by memory address. In addition, an easy-to-use 'symbolic' debug feature is provided that displays section of source code in a program 'window' on the workstation screen, and permits data values to be examined and modified by symbolic data name rather than by address. The 2200VS Debug Processor also includes facilities for examining and modifying internal registers and the Program Control Word. Breakpoints can be set in a program, and another feature allows the user to manually step through program execution.

#### 1.11 ADDITIONAL SYSTEM UTILITIES

A variety of additional system utility programs are provided to support the general programming task. These include, among others, copy, sort and linker utilities. The versatile copy utility permits the user to copy a single program or data file, an entire library of

such files, or a complete disk volume. For data files, the copy utility provides an option to change the file organization from sequential to indexed or vice-versa. The sort utility provides high-speed sort and merge capabilities for both indexed and sequential files, with either fixed or variable-length records. The linker, finally, is used to link together two or more program modules into a single large program, and optionally to remove the symbolic debug information previously inserted in a program for debugging purposes. Other utilities include a translation utility which translates from EBCDIC to ASCII and vice-versa; a special copy utility which copies and automatically translates 2200 program and data files to 2200VS format (and vice-versa); and a display utility, which can be used to display and/or print printer files.

The following list contains the names and descriptions of all 2200VS system utility programs. A detailed description of each system utility is documented in the <u>2200VS</u> File Management Utilities Manual, WL# 800-1300FM.

- ASSEMBLE Assembles a source program written in 2200VS macroassembler language.

- BASIC Compiles a program written in 2200VS BASIC.

- COBUL Compiles a program written in 2200VS COBOL.

- CONTROL Used to define attributes and validation criteria for a data file.

- COPY Copies files, libraries, or entire volumes from one location to another.

- COPY 2200 Copies and automatically converts files from 2200 standard format to 2200VS format, and vice versa.

DATENTRY - Used to create and update data files.

- DISKINIT Initializes a new disk volume in 2200VS format, with a volume label and Volume Table of Contents.

- DISPLAY Displays the contents of a file on the work station screen.

- DUMP Produces a printed copy of a task dump previously written to diskette with the DUMP AND CANCEL function of the Debug Processor.

- EDITOR Used to enter and edit source program text.

- EZFORMAT Used to create display files for formatting the work station screen.

- LINKER Combines two or more program modules into a single executable program.

- LISTVTOC Produces complete or selective listings of a specified volume's Table of Contents, and examines the VTOC for errors.

PRINT - Prints the contents of a print file.

- REPORT Used to produce customized reports from a data file.

- RPG II Compiles source programs written in 2200VS RPG II.

- SORT Sorts a data file, with an optional capability to merge two or more sorted files.

- TRANSL Automatically translates the contents of a specified file from EBCDIC to ASCII (the code used internally by the 2200VS), or vice versa.

#### 1.12 FILE PROTECTION AND SECURITY

All disk and tape files on the 8300 are classified according to a flexible file protection and security system, tailored at each installation to suit the requirements of the specific applications in use. At each installation, the file protection and security system is under the direct control of the Security System Administrators. The Security System Administrators are specially recognized users who determine the meaning and use of the file protection classes. They are able to access all files on the system, including the System User List and the Special Privilege Program List.

Every program, procedure, and data file on the system can be placed in one of twenty-eight file protection classes. Classes A through Z are used to represent protection classes whose meanings are determined by the Security System Administrators. For example:

Class W - The Workorder File Class P - The Product File Class C - The Customer File Class Q - The Sales Quota File Class R - The Pension Administration File Class M - The Payroll File Class X - Proprietary Programs and Procedures Class D - Confidential Project Documentation Files

Classes "#" and " " (blank) are reserved for specific uses:

Class " " - Unprotected Files Class "#" - Private and Security System Administration Files

The class of unprotected files is specified by setting the file protection class to blank. An unprotected file can be accessed by any user of the system. Class "#", unlike the other file protection classes, is used to define one protection class for each user. When specified, Class "#" identifies those files which can be accessed only by the user who created them (and by the Security System Administrators).

Before any user of the system can access a protected file, he must identify himself using the Logon command. At Logon Time, by lookup in th System User List, the user's Logon-ID and Password are validated, and his "access rights", relative to the defined file protection classes, are determined. The access rights are listed in the System User List (for each file protection class) to specify three different levels of privilege in order of increasing responsibility:

- 1) Execute Only Access (EXEC)

- 2) Execute and Input Access (READ)

- Execute, Input, Update, Rename, Scratch and Debug Access (WRITE)

These access rights are checked whenever a user attempts to execute a program or procedure, whenever he attempts to open an existing file, and whenever he attempts to rename or scratch a file.

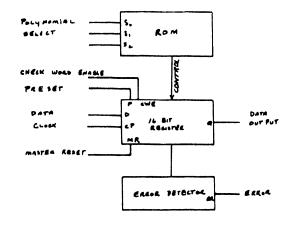

#### 1.13 RELIABILITY

To ensure the integrity of information stored in memory and on external storage devices (disk or tape), the system provides automatic error detection and correction facilities. In physical memory, all single-bit errors are corrected automatically, while multi-bit errors cause an error indication. Similar checks also are performed on information stored on disk or tape.

1.14 HARDWARE - GENERAL

This section describes the Central Processing Unit, I/O Processors, available options, and peripheral devices for the WCS/60 and WCS/80.

1.14.1 THE CENTRAL PROCESSING UNIT (CPU)

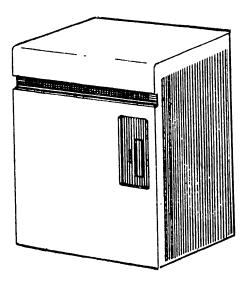

The CPU is the central component of the WCS/60 and WCS/80 systems. It is a compact cabinet which houses the 2200VS computer (including main memory and I/O Processors) and the system diskette drive.

FIGURE 1-2 CENTRAL PROCESSING UNIT (CPU)

THE WCS/60 CPU

The WCS/60 CPU contains the 2200VS computer, the 2270V 308,000-byte diskette drive, and two IOP's:

- 1) A 22V01 Printer/Workstation IOP, which supports one printer and up to three workstations.

- A 22V02 Diskette/10 Megabyte Disk IOP, which supports the 2270V system diskette drive and up to three 2260V 10 Megabyte Fixed/Removable Disk Drives.

Up to four additional IOP's support other peripherals and communications options. Minimum memory for the WCS/60 is 64K bytes. Memory upgrades are available in increments of 64K, to a maximum of 256K bytes.

THE WCS/80 CPU

The WCS/80 CPU contains the 2200VS computer, a 2270V 308,000-byte diskette drive, and three IOP's:

- 1) A 22V01 Printer/Workstation IOP, which supports one printer and up to three 2246P workstations.

- A 22V02 Diskette/10 Megabyte Disk IOP, which supports the 2270V system diskette drive and up to three 2260V 10 megabyte fixed/removable disk drives.

- 3) A 22V04 Removable Disk Pack Disk IOP, which supports a combined total of four 2265V-1 75 megabyte disk drives, and/or 2265V-2 288 megabyte disk drives.

Up to five additional IOP's support other peripherals and communications options.

1.14.2 I/O PROCESSORS (IOP'S)

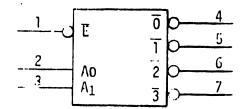

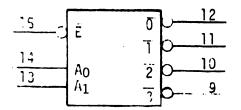

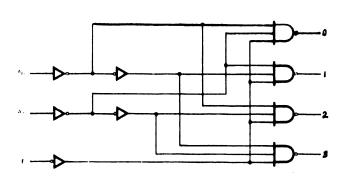

I/O Processors control the operations of peripheral devices. The following IOP's are available:

22V01 Printer/Workstation IOP. Supports one printer up to three workstations.

- 22V02 Diskette/10 Megabyte Disk IOP. Supports one 2270V 308,000 Byte Diskette Drive and up to three 2260V 10 Megabyte Disk Drives.

- 22V04 75 Megabyte Removable Disk Drive IOP. Supports two 2265-1 75 Megabyte Removable Disk Drives. (Used only for WCS/60; only one 22V04 IOP per system is allowed.)

22V05 9 Track Tape Drive IOP. Supports up to four 2209V 9 Track Magnetic Tape Drives.

22V06 Communications IOP. Available in two models to support bisynchronous telecommunications in the following combinations. 22V06-1 - Supports one bisynchronous line. 22V06-2 - Supports two bisynchronous lines.

# 1.14.3 WORKSTATION

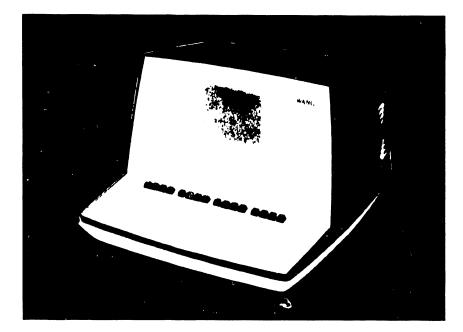

The 2246P workstation is the means by which users communicate with the system.

# FIGURE 1-3 2246P PARALLEL WORK STATION

The workstation consists of a display screen and keyboard. The 12-inch diagonal CRT display screen has a total display capacity of 1920 characters (24 rows, with 80 characters per row). Characters can be displayed in bright or dim intensity, and the screen can be formatted into 'fields'. The keyboard contains the familiar typewriter-like arrangement of alphabetic, numeric, and special character keys. A strip of 16 Program Function keys is placed along the top of the keyboard.

Workstations can be attached locally or remotely. A local workstation may be a maximum distance of 250 ft. from the CPU. A remote workstation may be located anywhere adjacent to a telephone line; it communicates with the CPU via the 22V06 communications IOP. (See the discussion of the communication IOP at the end of this chapter.)

# 1.14.4 DISKS

In addition to the system diskette drive, three hard-disk models are available, ranging in storage capacity from 10 megabytes to 288 megabytes.

#### 2270V SYSTEM DISKETTE DRIVE

The 2270V diskette drive, mounted in the Central Processing Unit, holds a single removable diskette.

Each diskette has a storage capacity of 308,000 bytes. Diskettes can be used to store programs or small, transient data files; they also serve as a convenient means of transferring information between two WCS systems, or between a WCS system and a foreign computer system. In addition, all updates to the WCS/60 and WCS/80 system software made by Wang Laboratories will be provided on a diskette.

FIGURE 1-4 2270V SYSTEM DISKETTE DRIVE

# 2260V TEN-MEGABYTE FIXED/REMOVABLE DISK DRIVE

The 2260V provides an approximate storage capacity of 10 million bytes, equally divided between a fixed and removable platter.

Because the disk unit contains both a fixed platter and a removable cartridge, backup operations can be performed easily. Cartridges containing backup file copies or information which is not currently needed can be stored "off-line" and remounted in the disk unit as required.

FIGURE 1-5 2260V FIXED/REMOVABLE DISK DRIVE 10 megabytes

2265V REMOVABLE DISK PACK DISK DRIVE

The 2265V is a high-performance, high-capacity disk unit which provides fast access to large volumes of information.

FIGURE 1-6 2265V-1, -2 REMOVABLE DISK DRIVE 75 megabytes (2265V-1) 288 megabytes (2265V-2)

The 2265V is available in two models:

1) The 2265V-1, with a storage capacity of 75 million bytes.

2) The 2265V-2, with a storage capacity of 288 million bytes.

Each model holds a single, removable disk pack. In addition to its high speed and large storage capacity, each model of the 2265V also provides extensive automatic error checking and correction facilities to ensure greater reliability.

On the WCS/60, a maximum of two 2265V-1 75 megabyte drives are allowed. The 2265V-2 288 megabyte drive is <u>not</u> supported on the WCS/60.

On the WCS/80, a combined maximum of eight 2265V disk drives are allowed (2265V-1 and/or 2265V-2).

1.14.5 PRINTERS

A variety of different printers are available for the WCS/60 and WCS/80, offering different speeds and print types. There is no restriction on the printer models which may be attached to a particular system.

#### 2221V MATRIX PRINTER

The 2221V is a versatile matrix character printer. Characters are formed using a 9 x 7 dot matrix (for some characters, a larger 9 x 9 matrix is used for better detail).

FIGURE 1-7 2221V MATRIX CHARACTER PRINTER 200 characters per second

The 2221V provides a character set of 96 characters, including upper and lowercase and special characters. Multipart forms with up to four carbons plus an original can be handled. Paper in widths from 3 1/2 inches (8.9 cm) to 14.9 inches (37.2 cm) can be mounted. The printer provides automatic vertical formatting, programmable audio alarm, and an expanded-print capability.

The 2221V prints serially at 200 characters per second. The number of lines per minute actually printed varies, according to the line length, from 65 to about 300 lines per minute.

# 2231V MATRIX PRINTER

The 2231V is an economical matrix printer which offers many of the features of the 2221V, but with a somewhat slower printing speed.

FIGURE 1-8 2231V-1, -2 MATRIX CHARACTER PRINTER 120 characters per second

The 2231V provides a full 96-character set, including upper and lowercase and special characters, using a 7 x 9 dot matrix to form each character. The 2231V is available in two models: the 2231V-1 prints a 112-character line (10 pitch); the 2231V-2 prints a 132-character line (12 pitch). Multipart forms and variable paper widths can be handled, and an audio alarm and expanded print capability are provided (see the 2221V). The 2231V prints serially at a rate of 120 characters per second. The actual printing speed varies, according to the line length, from 45 to about 250 lines per minute.

## 2261V MATRIX LINE PRINTER

The 2261V printer is a high-performance matrix line printer which produces quality output at much higher speed than serial printers.

FIGURE 1-9 2261V MATRIX LINE PRINTER 240 lines per minute

The 2261V produces high-quality output using a 9 x 8 dot matrix to form each character. (An 11 x 8 matrix is used for some characters to obtain better detail.) A complete set of 96 characters, including upper and lowercase and special characters, can be printed.

A switch-selectable pitch features enables you to switch from 10 pitch (132-character line) to 12 pitch (160-character line). Line density is also switch-selectable at either 6 line per inch or 8 lines per inch.

An original and up to four carbon copies can be printed, with paper width varying from 3 1/2 inches (8.9 cm) to 14.9 inches (37.8 cm).

The printer offers a number of other useful features, including automatic formatting, expanded print, and a programmable audio alarm.

The 2261V prints bidirectionally, using four matrix impacter printing heads to achieve a print speed of 240 lines per minute, independent of line length.

2263V LINE PRINTER

The 2263V is a solid-character line printer which produces quality printed output at high speed. The 2263V is available in two models: the 2263V-1, with a printing speed of 400 lines per minute; and the 2263V-2, with a printing speed of 600 lines per minute.

FIGURE 1-10 2263V-1, -2 LINE PRINTER 400 lines per minute (2263V-1) 600 lines per minute (2263V-2)

The 2263V prints one entire line (up to 132 characters) at a time. It can print one original and up to five carbon copies. Paper widths from 3.5 inches (8.9 cm) to 19.5 inches (48.8 cm) can be handled. The printer provides a number of useful features, including an automatic paper puller, static eliminator, and programmable audio alarm. Different typefaces and special character sets (including foreign language character sets) are optionally available.

The 2281V produces typewriter-quality output at 30 characters per second.

FIGURE 1-11 2281V WHEEL PRINTER 30 characters per second

The 2281V is a bidirectional output writer which utilizes a daisy character wheel with an 86-character set (upper/lowercase and special characters). Character wheels are removeable/replaceable for changing character sets.

The 2281V prints either a 132 or 158-character line at 30 characters per second. Among its features are programmable character underscoring, format tabbing, and color print selection.

1.14.6 TAPE DRIVE

## 2209V NINE-TRACK TAPE DRIVE

The 2209V Nine-Track Magnetic Tape drive is particularly useful for transferring information between a WCS/60 or WCS/80 and other computer systems.

FIGURE 1-12 2209V NINE-TRACK MAGNETIC TAPE DRIVE

The 2209V can read from or write to any 1600 bytes-per-inch (bpi) Phase Encoded magnetic tape. It supports both ASCII and EBCDIC character codes.

The Model 2209V operates in the Phase Encoded mode at a density of 1600 bpi. The drive transports tape at a velocity of 75 inches per second during read and write operations, and up to 200 inches per second during rewind. The unit contains a dual-gap read/write head, full width erase head, tape cleaner, and photo electric sensors to detect reflective tape markers and tape breakage. The Model 2209V provides read-after write verification and automatic correction for single track errors, and for multiple track errors which can be reduced to a single track.

# 1.14.7 COMMUNICATIONS

# 22V06 COMMUNICATIONS IOP

The 22V06 Communications IOP is an I/O Processor which supports bisynchronous communication with a variety of line speeds and industry standard protocols. It is available in two models:

- 1) The 22V06-1 supports a single bisynchronous line.

- 2) The 22VJ6-2 supports two bisynchronous lines.

A number of different line speeds are available including 1200, 2400, 4800, and 9600 baud. At least one line can support an automatic calling unit.

A number of industry standard protocols are supported for bisynchronous transmission:

- 1) 2780/3780 emulation.

- 2) 3270 emulation.

- 3) HASP.

On the 22V06-2, each line is independently programmed; thus it is possible to run different protocols on separate lines concurrently from the same IOP.

Remote 2246P workstations can be attached to the system via the 22V06 IOP. Such workstations function as local workstations, enabling users in remote locations to communicate directly with the system and interactively access all system facilities, just as if they were logged on locally.

# Technical Information

| DEVICE                                                          | GENERAL<br>SPECIFICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PERFORMANCE                                                                                                                                                                                                                     | PHYSICAL<br>SPECIFICATIONS                                                                                                                                                                                                                                                                                     | ENVIRONMENTAL<br>REQUIREMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

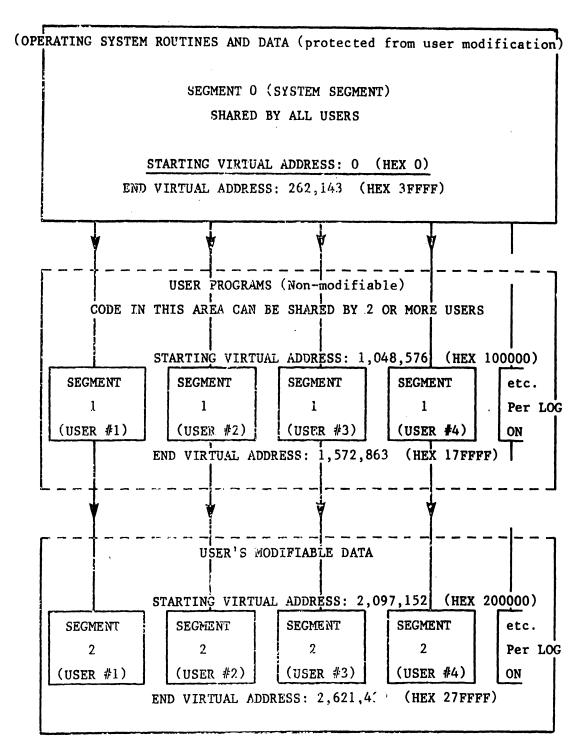

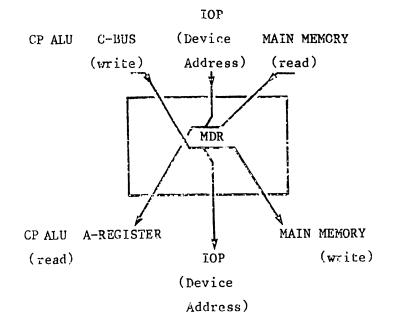

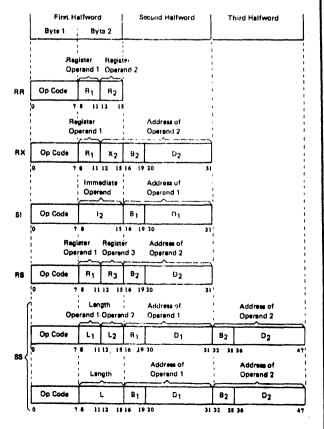

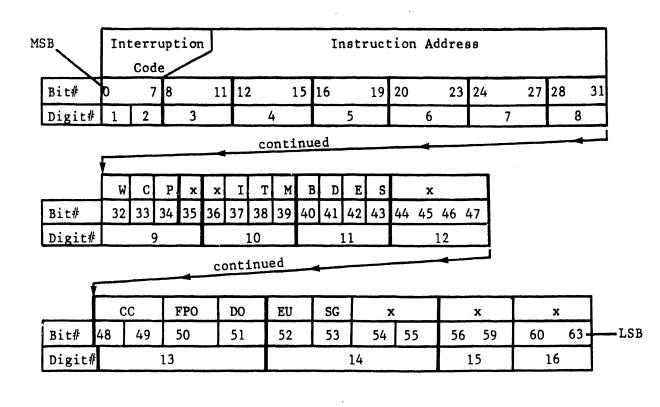

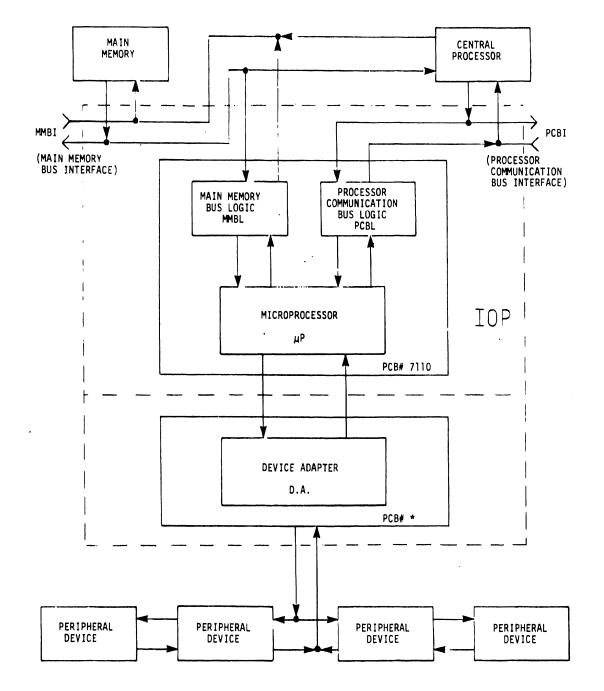

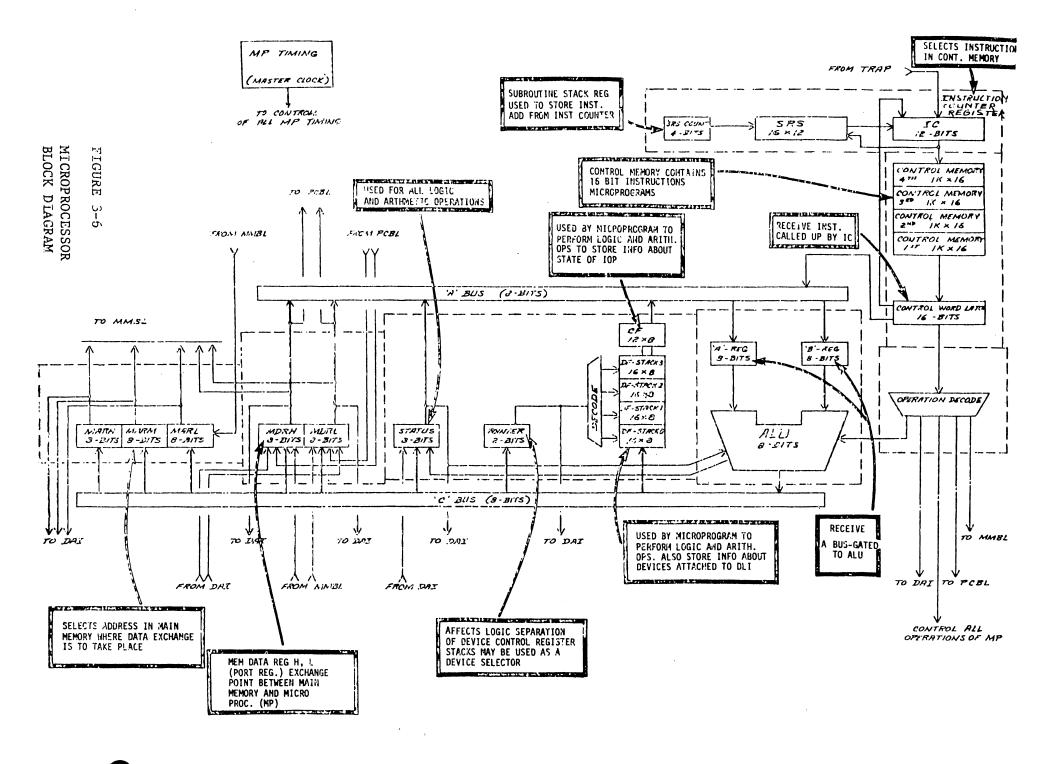

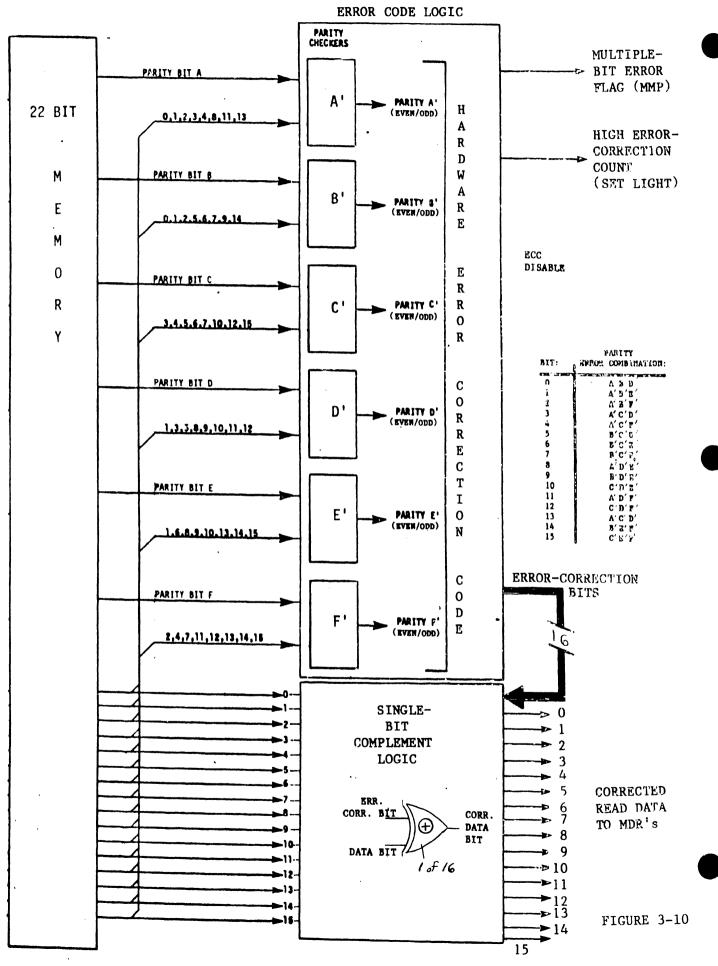

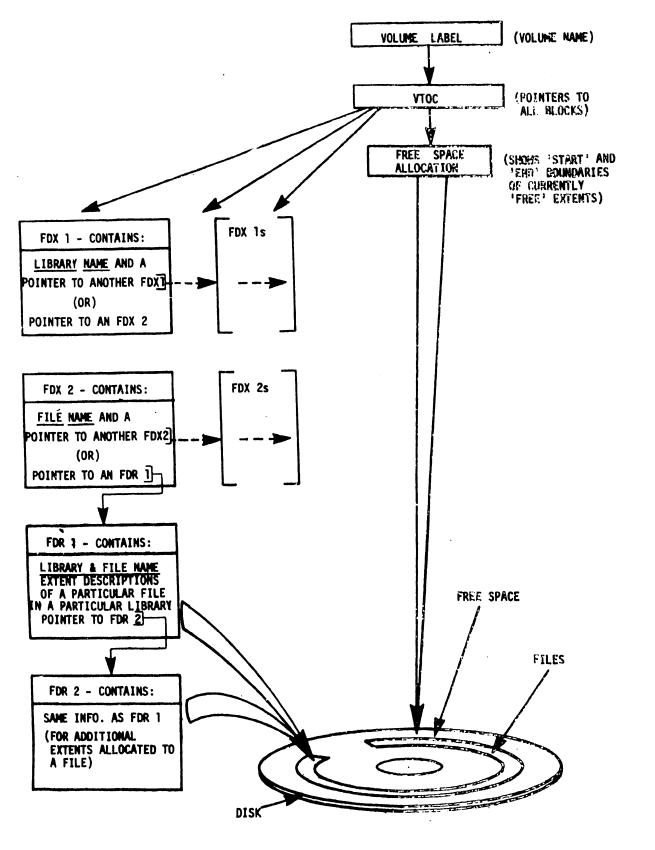

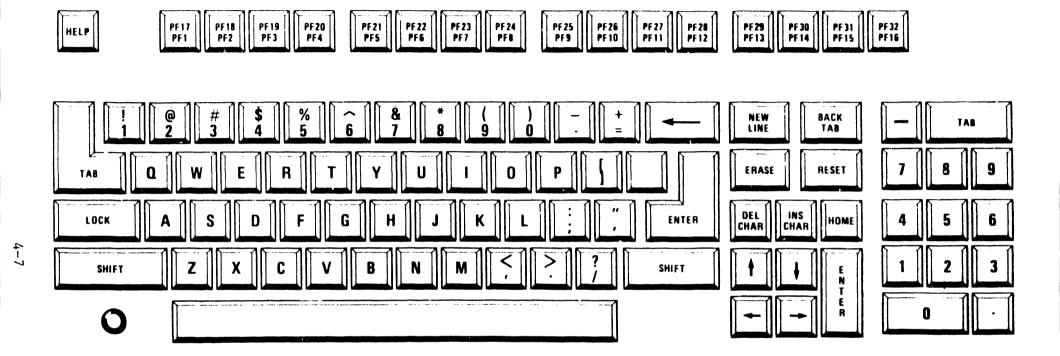

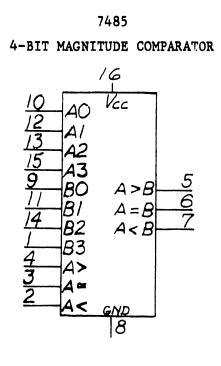

| Model 2248P<br>Parallel Workstation                             | CRT<br>12 inch diagonal display screen<br>24 lines, 80 characters per line<br>Screen can be formatted into<br>discrete fields<br>Manual controls for contrast<br>and brightnois<br>Bright and dim intensity for<br>instant recognition of field<br>modifiability<br>User-programmable blinking<br>cursor for next-character<br>position<br>Anti-glare filter<br>Keyboard<br>Typewriter-like keyboard<br>Cursor positioning keys<br>Character insertion and<br>deletion keys<br>Numeric keypad<br>16 Program Function keys<br>Programmable Audio Alarm | • 2K Random Access Memory                                                                                                                                                                                                       | <ul> <li>Physical Dimensions         Height = 13 in (33 cm)         Width = 19.5 in (49.5 cm)         Depth = 19.5 in (49.5 cm)         Weight         40 ib (18.2 kg)         Heat Dissipation         427 BTU/hr         Cable         500 ft maximum         </li> </ul>                                    | <ul> <li>Power Requirements         <ol> <li>115 or 230 VAC (±10%)</li> <li>50 or 60 Hz (±1 Hz)</li> <li>125 watts</li> </ol> </li> <li>Operating Environment         <ol> <li>50°F to 90°F</li> <li>(10°C to 32°C)</li> <li>35% to 65% relative humidity</li> </ol> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |