CUSTOMER ENGINEERING DIVISION

2200VS/8300

HARD/FLOPPY DISK DEVICE ADAPTER MANUAL

# PRELIMINARY

NOTICE:

This document is the property of Wang Laboratories, Inc. Information contained herein is considered company proprietary information and its use is restricted solely to the purpose of assisting you in servicing Wang products. Reproduction of all or any part of this document is prohibited without the consent of Wang Laboratories.

LABORATORIES, INC.

INDUSTRIAL AVENUE, LOWELL, MASSACHUSETTS 01851, TEL. (617) 851-4111, TWX 710 343-8769, TELEX 94-7421

## PREFACE 8300 BUS STRUCTURE

The 8300 System is a multiple processor system: The Central Processor (CP) is the master processor; the Input/Output Processors (IOPs) receive commands from the CP and control their attached peripheral devices. All processors (CP and IOPs) have the ability to access Main Memory by using the Main Memory bus (MMB). Processor requests for Main Memory operations are handled one at a time based on the high priority requesting processor at the start of each Main Memory cycle. A Main Memory operation consists of a transfer of one or two bytes between Main Memory and a processor.

A second bus, the Processor Communication Bus (PCB), allows the CP to send commands to any particular IOP. The PCB also provides an interrupt capability; after an IOP requests CP service, the CP can grant this pending interrupt request by using the PCB.

An IOP has one or more peripheral devices attached to it. The IOP performs control and data transfer operations involving these attached devices as directed by CP commands. CP commands are issued to a particular peripheral device; the command is performed by the IOP to which that device is attached. In general, an IOP has only one type of device attached to it. (This allows the IOP microprogram to be shared among the attached devices.)

The following conventions are used in this manual and schematics:

- 1. Each term is characterized by its logic active level-i.e. TO1 = Time one active high (+3.8V) TO1 = Time one active low (OV to +.4V)

- 2. All logic device symbols reflect that devices stand-alone function not its function within a particular circuit.

3. Logic '1' = +3.8V = HIGH Logic '0' = 0V + .4V = LOW

,

4. The weight (binary) of bits within registers and busses is bit-0 being the most significant bit. The higher the bit number, the lower its value-i.e.

| (MSB) | RO  | R15  | (LSB) |

|-------|-----|------|-------|

| (MSB) | ICO | IC11 | (LSB) |

- 5a. All signals crossing an interface (DAI, DLL, PCBI) are active high +3.8V.

- 5b. All strobes crossing an interface are active low 0V + .4V.

## NCTE:

These levels are recommended but not the rule. Any differences will be pointed out where they occur.

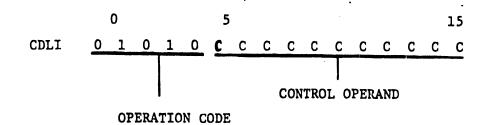

6a. ( )= Finger connections (bottom of board)

6Ъ. (

Connector connections

- TABLE OF CONTENTS -

ICP DEVICE ADAPTER SUB-SYSTEM FOR HEARD / FLOPPY DISK (7111 BOARD) SECTION 0.3 OVERVIEW 0.1 · BLOCK DIAGRAM DEVICE ADAPTER (IA) 1.0 · DESCRIPTION 1.1 ·BLOCK DIAGRAM 1.2 ·MNEMONIC LIST DEVICE ADAPTER INTERFACE (DAI) 1.3. ·DEVICE LEVEL INTERFACE (DLI) 1.4 ·OPERATIONAL SPECIFICATION 1.5 2.0 · HARDWARE OPERATION 2.1 · WRITE CLOCK · DISK CONTEOL 2.2 BIT SERIFILIZATION REGISTER (ECR) 2.4 · BIT COUNTER 2.5 · SECTOR COUNTER ·DIRECT MEMORY ACCESS (DMA) 2.6 · CYCLIC REDUNDANCY CHECK (CRC) 2.7 2.8 · OPERATIONAL STATUS ERROR FLAGS & OPERATION TERMINATION 2.9 ·FLOPPY DISK TIMER · TERMINATOR VOITAGE & PROTECT CIRCUIT 2.10 3.0 ·INSTRUCTION OPERATION 3.1 · GIVE DISK STATUS 3.2 · GIVE OPERATION STATUS 3.3 · GIVE SECTOR 3.4 · SEEK (HARD DISK ONLY) 5.5 · SURFACE OPERATION 3.6 · FORMAT 3.7 ·WRITE 3.8 · READ 3.9 · WRITE / VERIFY

iii

TABLE OF CONTENTS (CONTINUED)

SECTION ·INSTRUCTION OPERATION (CONTINUED) • RESTORE (HARD DISK ONLY) 3.10 3.11 • STEP (FLOPPY) · HEAD CONTROL (FLOPPY) 3.12 · DIRECTION SELECT (FLOPPY) 3.13 · START TIMER (FLOPPY) 3.14 · FILE INOPERABLE RESET (FLOPPY) 3.15 4.0 HARD DISK 5.0 FLOPPY DISK 6.0 TEST PROCEDURES APPENDIX A.1 · SCHEMATIC A.2 · DEVICES USED

iv

#### IOP DEVICE ADAPTER SUB-SYSTEM OVERVIEW

#### DESCRIPTION:

The Device Adapter (DA) is that part of the Input/Output Processor (IOP) that adapts the peculiar requirements of a peripheral device to the requirements of the Microprocessor (MP) within the IOP.

#### GENERAL RELATIONSHIP:

The IC? exchanges information with the CP through main memory via a set of lines called the Main Memory Bus (MMB). The CP and the IOP engage in dialog via a set of lines called the Processor Communication Bus (PCB). The significance of these two sets of lines is qualified by two interfaces: the PCB interface (PCBI) and the MMB interface (MMBI). These two interfaces are integral components of the IOP as are the Device Level Interface (DLI) which qualifies signals between the devices and the IOP, and the Microprocessor (MP) which acts as the controller of these interfaces.

An IOP relieves the CP of the burden of communicating directly with I/O devices and permits data processing to proceed concurrently with I/O operations. An IOP provides the logical capabilities necessary to operate and control an I/O device. The IOP decodes the commands fetched from main memory and interprets them for the particular type of device.

#### Input/Output Devices

Input/Output devices provide external storage and a means of communication between data processing systems or between a system and its environment. Input/Output devices include such equipment as workstations, magnetic tape units, disks, typewriter-keyboard devices, printers, and teleprocessing devices.

1

0.0

#### Input/Output Device Identification

The WANG 8300 system is capable of connecting 8 input/output processors with each processor capable of connecting up to 16 I/O devices. (This configuration may be altered in future models.)

Each device has a one byte (8 bit) device address. All values from 00 to FF are legitimate device addresses. The priority of interrupt service is determined by the physical position of the IOP in the hardware configuration and not by the device address.

An 8-bit device address consists of an IOP portion and a device portion. The bit assignments are IOP dependent. The current IOP supports from four to sixteen devices; the high order four or six bits are therefore the IOP address and the low order two or four bits are the device address.\*

The following block diagram shows the functional relationship of major components within the IOP. The relationship of the IOP (shown inside of box) with Main Memory, CPU and the Peripheral Device(s), is via the MMBI, PCBI and DLI respectively.

The CPU converses with Main Memory via the MMBI as does each IOP. However, the block diagram shows a separate path to clarify the functional data path and control path of the 8300 system.

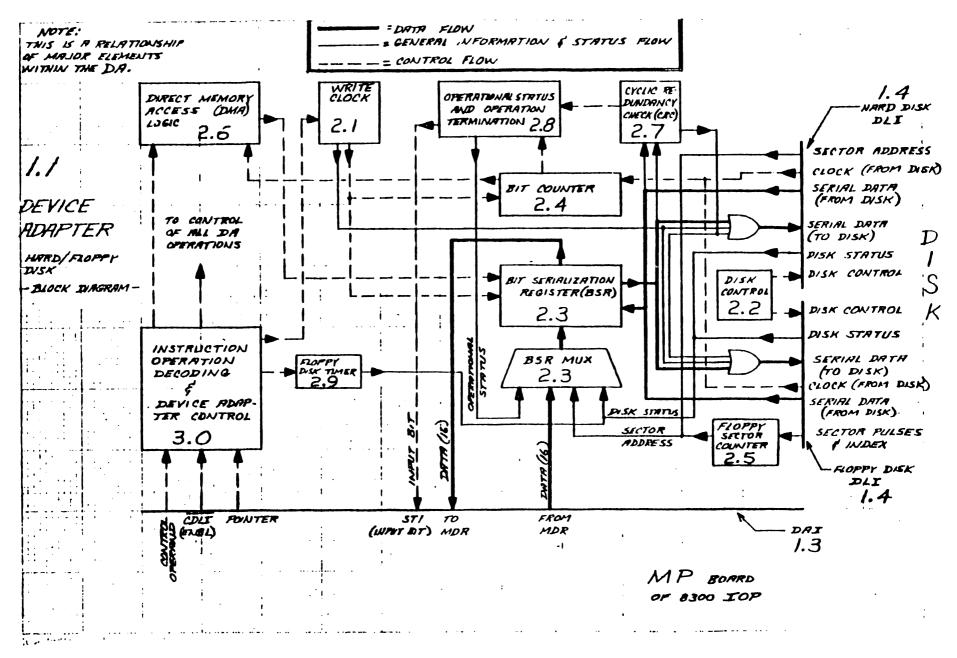

The device adapter (DA) contains hardware required to interface the peripheral device(s) to its controlling microprocessor. The DA resides in the same module as the MP but is part of the peripheral device's hardware. This module is referred to as the IOP and the peripheral device(s) as the IOP device(s).

For further description, operation and eventual hardware breakdown, refer to the section indicated below each title.

\* IIII DDDD = 16 DEVICE IOP IIIIII DD = 4 DEVICE IOP I = IOP ADDRESS D = DEVICE ADDRESS

## - HARD/FLOPPY DISK DEVICE ADAPTER -(210-7/11 PC Bound)

DESCRIPTION:

The Device Adapter converts the peculiar requirements of a particular peripheral device to the requirements of the Microprocessor portion of the 8300 IOP.

The Microprocessor commands the peripheral device, via the Device Adapter, and supplies various status associated with the peripheral and any other special information that might be required by the peripheral.

In the case of the Hard/Floppy Disk Device Adapter, the following tasks are performed by the Device Adapter:

- A. DISK SELECTION i.e., one of four possible disks is selected gaining access to the DLI port and made available for all data transfers and control information both to and from the microprocessor via the DLI and DAI.

- 1. This selection is a direct function of the MP's pointer register.

PT0

PT1

0

0

= SEL 0 (Hard Disk)

0

1

= SEL 1 (Hard Disk)

1

0

= SEL 2 (Hard Disk)

1

1

= FLOPPY DISK SELECT

2. This select shifts the device adapter's internal operation of its clock to accomodate both the hard and floppy disk's different data rates.

4

1.0

B. INSTRUCTION DECODING - i.e., to determine what task is to be performed and the execution of that task satisfying the requirements of the disk and microprocessor/microprogram:

> Format

>  Write

>  Read

>  Write/Verify

>  Various Status Information Transfers and Operations

- C. DIRECT MEMORY ACCESS (DMA) i.e., the DA handles the actual main memory transfer by its hardware rather than the microprocessor by its Control Memory Bus Interface microinstruction (CMBI). This results in a fast memory access required by the disk in order to read or write consecutive bytes.

- There are 256 consecutive data bytes in each sector of the disk.

- 2. The microprocessor, after issuing the appropriate command to the device adapter, waits for the input bit to be set by the device adapter (signalling the end of the operation) before issuing any more commands to the device adapter.

The following block diagram shows the relationship between major elements within the Device Adapter.

For further description of each element, refer to the section indicated in each element block.

· · ·

# DEVICE ADAPTER

.

- DIABLO & SHUGART -

MNEMONIC LIST:

C

| ACC & ACC                            | -   | Allow Cyclic Check                              |

|--------------------------------------|-----|-------------------------------------------------|

| ACK & ACK                            |     | 'A' Clock                                       |

| ADDR ACK                             |     | Address Acknowledge                             |

| ADO                                  | •   | Allow DLI Instruction                           |

| APL                                  | · 🖬 | Allow Parallel Load                             |

| BCK & BCK                            | -   | 'B' Clock                                       |

| BSR                                  | -   | Bit Serialization Register                      |

| CCE                                  | -   | Cycle Check Error                               |

| CDLI                                 | 82  | Control Device Level Interface Microinstruction |

| CIS                                  |     | Controller In Sync                              |

| СР                                   | -   | Central Processor                               |

| CSR                                  | Ľ   | Clear Serialization Register                    |

| DCE                                  |     | Data Compare Error                              |

| DCP                                  | •   | Data Comparison                                 |

| DDS                                  |     | Disk Direction Stored                           |

| DLS                                  |     | Device Level Select                             |

| DOS                                  |     | Data Order Stored                               |

| DSMH                                 |     | Device Strobe MDRH                              |

| DSML                                 |     | Device Strobe MDRL                              |

| DSO & DSO                            |     | Disk Trobe Out                                  |

| DO (MSB) $\leftrightarrow D/S$ (LSB) | -   | Data to MP Board MDRH & MDRL Input Multiplexers |

| EOF                                  |     | End of Format                                   |

| EOR                                  |     | End of Read                                     |

| EOW                                  |     | End of Write                                    |

| FCS                                  | -   | Format Command Stored                           |

| FDP                                  |     | Floppy Disk Pointer                             |

| FIR & FIR                            | -   | File Inoperable Reset                           |

| FMC                                  | -   | Format Command                                  |

| FRN                                  | -   | File Ready                                      |

| HPS                                  |     | Head Position Select                            |

| HR16                                    | Hardware Read 16                      |

|-----------------------------------------|---------------------------------------|

| HTS =                                   | Hardware Transfer Stop                |

| HW16 -                                  | Hardware Write 16                     |

| INC2 -                                  | Second Increment Pulse to MAR         |

| INITE                                   | Latched Initialize                    |

| INIT2                                   | Initialize                            |

| IOP -                                   | Input/Output Processor                |

| ISS                                     | Inhibit Serialization (Reg.) Shift    |

| IWC =                                   | Increment Write Clock                 |

| LAI                                     | Logical Address Interlock             |

| LIS                                     | Load In Status                        |

| LSR                                     | Load Serialization Register           |

| LTZ                                     | Load Track Zero                       |

|                                         | Memory Address Register High          |

|                                         | Memory Address Register Low           |

|                                         | Main Memory                           |

|                                         | Microprocessor                        |

| MXA =                                   | BSR Multiplexer Select 'A'            |

| MXB -                                   |                                       |

| $PTO (MSB) \leftrightarrow PTI (LSB) =$ |                                       |

| RCS & RCS                               |                                       |

|                                         | Read Command                          |

| RDI & RDI                               | Read Data In                          |

| RFD                                     | Resync For Data                       |

| RGA                                     |                                       |

| ROS                                     | Reset Operational Status              |

| RSA                                     |                                       |

| RST                                     |                                       |

| RTS                                     |                                       |

| RVC                                     | •                                     |

| SCA                                     |                                       |

| SCD                                     |                                       |

| SDD & SDD                               |                                       |

| 201                                     |                                       |

| 500                                     |                                       |

| 5 <i>DF</i>                             | <ul> <li>Shift During Read</li> </ul> |

| SDR                                     | Pointer to Drive #0                   |

| JEL V                                   | ••••••                                |

:

| SEL 1                                                                         |     | Pointer to Drive #1            |

|-------------------------------------------------------------------------------|-----|--------------------------------|

| SEL 2                                                                         | -   | Pointer to Drive #2            |

| SHC & SHC                                                                     | -   | Strobe Header Check            |

| SHP & SHP                                                                     | -   | Strobe Head Position (Up/Down) |

| SHW                                                                           | =   | Set Write Request              |

| SIE                                                                           | 82  | Seek Incomplete                |

| SINPT & SINPT                                                                 | -   | Set Input Bit                  |

| SIS                                                                           |     | Step Into Sixteen              |

| SOP                                                                           |     | Surface Operation              |

| SOS                                                                           |     | Step Out of Sixteen            |

| SPP                                                                           | -   | Sector Pulse Present           |

| SRR                                                                           | 100 | Set Read Request               |

| SRT                                                                           | -   | Start Read Termination         |

| SSR                                                                           |     | Shift Serialization Register   |

| STG                                                                           | -   | Shorten The Gap                |

| STP                                                                           | -   | Step-Floppy                    |

| $\overline{S1}$ (MSB) $\leftrightarrow$ $\overline{S5}$ (LSB)                 | -   | Sector Address from Disk       |

| $\overline{\text{TAO}}$ (MSB) $\leftrightarrow$ $\overline{\text{TA8}}$ (LSB) | 86  | Track Address Bits (Cylinder)  |

| TIS                                                                           |     | Time In Sync                   |

| T02, T04, T06                                                                 | æ   | Subcycle Times (MP)            |

| ULH                                                                           | -   | Upper-Lower Head               |

| WCE                                                                           | *   | Write Check/File Inoperative   |

| WDC                                                                           | æ   | Write Data Command             |

| WGT                                                                           | -   | Write Gate Time                |

| WMR                                                                           | 86  | Write Memory Request           |

| WPT                                                                           | m   | Write Protect                  |

| WTG & WTG                                                                     | =   | Write The Gap                  |

1.3

The Device Adapter Interface is that set of interconnecting lines between the Microprocessor and the Device Adapter.

The following is a description of DAI terms and their pin assignments peculiar to the Hard/Floppy Disk Device Adapter sub-system. For a complete list of the DAI terms, see the 8300 MP Manual.

MDRH (MDH0 ↔ MDH7) & MDRL (MDL0 ↔ MDL7) LINES - MP TO DEVICE

These sixteen lines come from the microprocessor and are direct outputs from the MDR (Memory Data Register). Since the microprocessor is utilizing the MDR for its operations, the information across these lines can only be considered valid when the appropriate strobe and command is sent from the controller to the peripheral device. In addition, these lines may also be used to pass commands, (bits within the MDR) to the Device Adapter in conjunction with the microprocessor CDLI command.

DATA (DO-D15) LINES - DEVICE TO MP

These sixteen lines come from the Device Adapter and are utilized to pass data and status back to the microprocessor. These lines are used in conjunction with the SELECT MDR, STROBE MDRH and STROBE MDRL lines. These lines must have the same truth as the bits required in the MDR.

## NOTE: (DO-D7) = MDRH (D8-D15) = MDRL

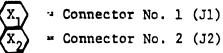

CONTROL OPERAND OF CDLI INSTRUCTIONS (R5-R15)

These eleven lines come from the microprocessor and signal the Device Adapter as to the operation it is requested to perform. The usage of these bits varies from one machine to another and will be specific to the device type to be connected. These lines may be bit significant or binary coded.

If the instruction is transferred to the Device Adapter via the MDR register(s), the control operand of the CDLI instruction will remain undefined.

CDLI LINE (CDLI)

This line, (active low) is valid from TO2 (CLOCK TIME 2) throughout the execution of the microinstruction and is present when the microcode issues a command to the D.A. At this time, the D.A. electronics can interpret its instruction from either the eleven instruction lines or via the output lines from the MDR. The method used for implementation can be made by the hardware designer and the microprogrammer at the time of the design conception.

POINTER LINES (PTO AND PT1)

These two lines come from the microprocessor and indicate to the device electronics the peripheral port which is of interest to the microprocessor.

**T02-T04-T06**

These lines come from the microprocessor and are the timing signals associated with microinstructions coming across the Device Adapter Interface.

SELECT MDR (DLS)

This line is generated by hardware within the Device Adapter. When the D.A. electronics is required to put data or status into the MDR (under command of the microprocessor), this line must be brought low. At some time later, the appropriate MDR segment (either MDRH or MDRL) must be strobed.

## STROBE MDRII (DSMH), MDRL (DSML)

These two lines are under control of the D.A. electronics,

When data or status is loaded into the MDR, and at sometime after the MDR selection, the appropriate MDR strobe will be made.

INPUT RESPONSE (SINPT)

This line is generated within the Device Adapter.

This line is used to set the INPUT bit in the microprocessor, thereby indicating a response from a device operation. The microcode within the microprocessor tests this bit periodically for a device response. The purpose of this bit is to allow for asynchronous operations within the peripheral device to become synchronous with the microprocessor. The minimum pulse width for this signal is 25 nanoseconds.

#### INITIALIZE (INIT2)

This line will be 0 volts during power-up time for 50 microseconds, then changes to +3.8 volts. An active low pulse of 50 microseconds will also be generated via the prime button.

#### HARDWARE WRITE SIXTEEN (HW16)

This line must be held at +3.8V when not in use. When this line is brought to 0 volts, the memory controller takes in the contents of the MDR.

#### HARDWARE READ SIXTEEN HR16)

This line must be held at +3.8V when not in use. When this line is brought to 0 volts, the memory controller loads the data from the main memory into the MDR.

#### HARDWARF STATUS BIT 1 (HSB1)

This line will be 0 volts normally and will go to +3.8V when a memory parity error occurs. This bit will become a status bit in the operational status byte.

HARDWARE STATUS BIT 2 (HSB2)

This line will be 0 volts normally and will go to +3.8V when an illegal address has been sensed by the memory controller. This bit will become a status bit in the operational status byte.

#### HARDWARE TRANSFER STOP (HTS)

This line will be +3.8V normally and will go to 0 volts when either illegal address or parity error is detected. During a direct transfer, a 0 volt on this line will cause an immediate termination of the direct transfer operation.

RESET OPERATIONAL STATUS (ROS)

This line " NoRmally At +3.8V, A & volt level on this line causes hardware status bits 1 and 2 to be reset.

#### MAR INCREMENT (INC2)

This line is normally +3.8V. When this line goes to 0V and then back to +3.8V, the memory address counter is incremented for the second time during the current MEMORY OPERTON.

## SYSTEM INITIALIZE

:

This line is normally +3.8V. When this line goes to OV, it indicates a master reset (power-on) from the system. This line will also go to OV whenever the power supply voltages become out of tolerance. DAT PINI MOSSIGNMENT

| DIRECT MEMORY     | RCCESS                     | NIISCELLANEOUS | SIGNALS        |

|-------------------|----------------------------|----------------|----------------|

| SIGNIAL NINI-1E   | PILI NO.                   | SIGNINL NAME   |                |

| HTS               | I,                         | HARM (115B)    |                |

| H 5.31            | 44<br>54                   | X ·            |                |

| HSB2<br>HW16      | 04<br>14<br>2 <sub>4</sub> |                |                |

| HR16              | 2,                         | MIRRY-         | •              |

|                   | 1911 - 19<br>19            |                |                |

|                   |                            | •              |                |

|                   |                            |                | • • •          |

|                   |                            |                |                |

| MISCELLANCOUS     | SIGNAL 5                   | HAR-           | •              |

| SYSTEM INITIALIZE | PIN NO.<br>13              | N.             | •              |

|                   |                            | · (2,5E')      | ,              |

|                   |                            | TWC2           | N <sub>4</sub> |

|                   |                            |                |                |

|                   |                            | -              |                |

|                   |                            |                |                |

|                   |                            |                |                |

| ·                 |                            |                |                |

|                   |                            |                |                |

|                   |                            |                |                |

|                   | ·                          |                |                |

|                   |                            | -1             |                |

1.3

DAL FILL ASSIGNMARAT

NAME PIN NO. FIN NO. SIGNAL SIGNAL NAME (r:15B) (1:15B) DO MDHO /3 F.3  $S_2$ NIDHI 152  $\mathcal{D}/$ MDH2 142  $\mathcal{R}_{Z}$ DZ MINTS 132 DB  $\mathcal{F}_2$ NUNH MDHF  $\Lambda'_{\underline{r}}$ 12z D4MDH'5 1/2  $M_{2}$ D522 NIDHS 102 ДG MDH7 (ISB)  $\mathcal{P}_{2}$ D7 $\mathcal{K}_{\mathbb{R}}$ Jz  $\mathcal{D}\mathcal{B}$ 3z (MSB) MDLO DЭ 14-ر<del>ی</del> ششر MD11 72 DIO 52 62 5 MD12 .D// ADR 1D13  $5_{2}$  $\mathcal{D}_{Z}$ DIZ 42 MDL4 D13  $C_2$  $S_2$ HDL 5 Ξz D14 Êz D15 (15E) MDIS Az MDLT (LSB)  $/_2$  $\mathcal{R}_{\mathcal{B}}$ DIS (MSE) DSNIH R5 $N_3$ 143 113 **R6** DSMIL 133 **ボ**7 123 43 SINT (32 MA LOW) 178  $K_3$ INIT2 113  $\mathcal{J}_{\mathfrak{Z}}$ ボタ CNPTROL OPERAND RIO H3 RII Fз E,3 RIZ  $\mathcal{D}_{\mathfrak{Z}}$  $B_1 - Z_1$ R13 +5VR  $\mathcal{C}_{\mathcal{F}}$ R4-144 . R14 (158) R15  $\mathcal{Z}_{3}$ 73 - 63 C, - 3, tor 23 P4- 134 MOF (PULL UP TO (+5V WATEN LANGED) 105 43 -5VR 15.1 C. I 103 54 (MSB) +12VR PTO 83 (15B) PTI  $\mathcal{P}_{3}$ TOZ P3 Sa T04 TOG 153

1.3

- DEVICE LEVEL INTERFACE (DLI) -

The Device Level Interface consists of three connectors. Two connectors are used for connection to the first 10 megabyte hard disk. One or two more hard disk(s) can be attached in a daisy chain configuration - i.e., the second hard disk can be attached to the first, and the third hard disk can be attached to the second disk.

- The last hard disk must be terminated. If only one hard disk is used, it must be terminated.

- ' 2. Connectors number one and two are used for the hard disk DLI:

The floppy disk has its own connector on the device adapter. Only one floppy disk can be attached - i.e., no daisy chain configuration of floppy disks is allowed.

The floppy disk DLI, for the most part, is in a parallel configuration with the DLI for the hard disk and uses the terminator block physically mounted on the hard disk. Those signals peculiar to the floppy disk only are terminated within the floppy disk.

, A single or multiple (up to 3 max.) hard disk configuration may appear without a floppy disk, of A FLOPPY WITHOUT HARD DISKS, OR ANY COMBINATION FLOPPY AND HARD DISKS. 2. The connector with no subscript is used for the floppy disk DLI:

X - Connector for the Floppy Disk

The following Device Level Interface description is broken into two parts. The first is the DLI for the Hard Disk(s) and the second is the DLI for the Floppy Disk:

# - SIGNAL DESCRIPTION -(HARD DISK) - LINES TO THE DISK DRIVE -

#### UNIT SELECT LINES (SELO, SEL1, SEL2)

There are three unit select lines going out of the interface port. They are used to select one of the three possible drives in the daisy chain configuration. A value of '0' in one of these lines selects the corresponding unit. The selected drive has access to the interface port and all signals to and from the interface apply to this drive.

#### DISK SELECT (SDP)

This line selects the removable or the fixed cartridge. A '0' selects the removable cartridge; a '1' selects the fixed cartridge.

HEAD SELECT (ULH)

This line selects the upper or lover head of the selected cartridge. A '0' selects the upper surface head; a '1' selects the lower surface head.

#### TRACK ADDRESS (TAO (MSB) + TAB (LSB))

These 9 lines active low (OV, .4V), are used to specify a cylinder address where the heads are to be moved. These lines are strobed with the strobe line and stored in an internal address register (disk drive).

## DISK STROBE OUT (DSO)

This line is used to enable the track address and the restore lines. This line is made '0' when the appropriate signal lines have settled and must be held until at least the leading edge of the address acknowledge signal is detected. RESTORE (RST)

This line is used to position the heads at cylinder 0. After completion of this command the heads are located over cylinder 0, and the seek incomplete condition is reset. This signal is active low (0V, .4V). This line must have settled before the application of  $\overline{DSO}$ .

#### WRITE GATE (WRITE GATE)

This line turns on the write current in the selected head. The signal must be applied at least 2  $\mu$ sec prior to writing the first flux transition, and held for the entire duration of the write operation. This signal is active low (0V, .4V).

#### \*ERASE GATE (ERASE GATE)

This line turns, the erase current in the selected head. There is no built in delay of erase current. This signal is active low (OV, .4V).

#### WRITE DATA AND CLOCK (WRITE DATA)

This line accepts multiplexed data and clock pulses for double frequency or phase encoding type recording. Pulses must have a minimum width of 100 nanoseconds. Leading edges must have a transition time of not more than 50 nanoseconds. Pulses are active low (0V, .4V).

#### READ GATE (READ GATE)

This line enables the read clock and read data output lines. The read gate must be held active during the entire read operation. This signal is active low (0V, .4V).

\*Erase Gate causes a "trim" erase of the data track. The hard disk does not have crasing of the entire track capability. The "trim" erase limits the width of a track by crasing all signals that are wider than the specified track width. (See Diablo Series 40 Maintenance Manual.)

LINES FROM THE DISK DRIVE-

#### FILE READY (FRN)

A '0' on this line indicates that all the following conditions are met (normal operation):

- Power On

- Dust Cover Loaded\*

- Equipment Drawer Closed

- LOAD/RUN Switch In RUN Position

- Start Up Cycle Complete

- Write Check False

- File Select True

#### READY TO SEEK (RTS)

A '0' on this line indicates that the drive is in the file ready condition and is not in the process of executing a seek operation. Following a seek command to a valid address (other than the present address), or a restore command, this line will go to '1' within 1 µsec after detecting the leading edge of the strobe signal. The return of the line to '0' indicates that the seek or restore operation has been completed. This line does not change when the present cylinder is addressed.

#### ADDRESS ACKNOWLEDGE (ADDR ACK)

A '0' on this line indicates that a command to move the heads has been accepted and that execution of the command has started. An address acknowledge is issued 500 nanoseconds after the leading edge of the strobe is detected even if there is no change in the address. This signal is a 1 µsec pulse. The pulse will not be issued if a logical address interlock condition is detected.

\*On the Diablo Series 40 Disk Drive, the removable disk platter need not be installed, just the dust cover, to obtain a file ready condition.

#### LOGICAL ADDRESS INTERLOCK (LAI)

A 'O' on this line indicates that a track address greater than 407 has been received and that the command is not executable. The seek command is suppressed. This line is reset ('1') with the next valid address acknowledge or with the restore command.

SEEK INCOMPLETE (SIE)

A '0' on this line indicates that a malfunction has caused an incomplete seek operation. This value will be maintained until a restore command has been received and executed by the disk drive.

SECTOR MARK (SPP)

A '0' on this line indicates that a sector slot passes by the transducer. This line is pulsed for 40  $\mu$ sec when this condition arises (24 times per revolution).

## SECTOR ADDRESS $(\overline{S1}(MSB) \leftrightarrow \overline{S5}(LS2))$

These 5 lines define the sector address under the read/write heads. The selected address counter is advanced by the leading edge of the sector mark and is reset to zero by the leading edge of sector mark following the index mark. The value of the sector counter is not considered valid for the duration of the sector mark pulse. These lines are active low (OV, .4V).

#### READ CLOCK (READ CLOCK)

This line provides clock pulses which have been separated from the data signals during reading. Pulse width is nominally 100 nanoseconds, with a minimum of 50 nanoseconds and a maximum of 150 nanoseconds. The negative going edge must be used for reference. This pulse is active low (0V, .4V).

## READ DATA (READ DATA)

This line is used for output data signals which have been separated from clock signals during reading. Pulse width is nominally 100 nanoseconds, with a minimum of 50 nanoseconds and a maximum of 150 nanoseconds. The negative going edge of this signal must be used for reference. This pulse is active low (0V, .4V).

## WRITE CHECK (WCE)

A '0' on this line indicates that one or more of the following conditions exist:

- Write current without a true write gave line

- Write and select on both heads

- Erase current without a true erase gate line

- Erase gate line true without erase current

- Significant voltage drop

All external commands are suppressed. This line is reset by either adjusting the voltage or by turning the LOAD/RUN switch to LOAD and back to RUN.

DLI (HARD DISK) - PIN ASSIGNMENT -

| SIGNAL NAME         | PIN NO.                | SIGNAL NAME            | PIN NO.            |

|---------------------|------------------------|------------------------|--------------------|

| SEL O               | 432                    | FRN                    | 43,                |

| SEL /               | 442                    | RTS                    | 38,                |

| SEL 2               | 452                    | ADDR ACK               | 472                |

| SDP                 | 3/2                    | LAI                    | 44,                |

| ULH                 | 272                    | SIE                    | 37,                |

| TAO (MSB)           | 39,                    | SPP                    | 29,                |

| TAI<br>TA2          | 29 <sub>2</sub><br>48, | <u>51</u> (MSB)<br>52  | 45,                |

| TR3<br>TR4          | 47,                    | <u>52</u><br><u>53</u> | 3 <i>2,</i><br>35, |

| 7A5                 | 49,<br>41,             | 54<br>55 (LSB)         | 36,<br>34,         |

| TAG<br>TAT          | 40,<br>46,             | READ CLOCK             | 28,                |

| TAB (LSB)           | 42,                    | READ DATA              | 30,                |

| DSO                 | 362                    | WCE                    | 32,                |

| RST                 | 372                    |                        | /                  |

| WRITE GATE          | 39 <sub>2</sub>        |                        |                    |

| ERASE GATE          | 40 <sub>2</sub>        |                        |                    |

| WRITE DATA          | 27,                    |                        |                    |

| READ GATE           | 31,                    |                        |                    |

| + 5V (FOR TERMINATO | 1 482 E 492            |                        |                    |

|                     | SK DRIVE               | EDOM                   | DISK DRIV          |

NOTE: PINS I TROUGH 25 OF BOTH CONNECTORS (JI 5 J2) ARE CONNECTED TO ± OV. FLOPPY DISK SELECT (FDS)

This signal active low (OV, .4V) selects the floppy disk drive for access to the Device Level Interface port and all signals to and from the interface apply to this drive.

#### DIRECTION SELECT (DDS)

This interface signal defines the direction of motion of the R/W head when the Step line is pulsed. A logical one level defines the direction as out and if a pulse is applied to the Step line the R/W head will move away from the center of the a.sk. Conversely, if this input is a logical zero level is applied the direction of motion is defined as in and if a pulse is applied to the Step line the R/W head will move towards the center of the disk.

#### STEP (STP)

This interface line is a control signal which causes the R/W head to move with the direction of motion defined by the Direction Select line. The access motion is initiated on each logical zero to logical one transition of this signal.

#### HEAD LOAD (HPS)

This interface line performs two functions. One function is to remove the 24 volts from the stepper motor which will allow the motor . to run cooler. This means that in order to step, the Head Load line must be a logical O level. It also is a control signal to an actuator that allows the disk to be moved into contact with the R/W head before a Read/Write operation. A logical one deactivates the head load actuator and causes a bail to lift the pressure pad from the disk, which removes

the load from the disk and R/W head. A logical zero level on this signal activates the head load actuator and allows the pressure pad to bring the disk into contact with the R/W head with the proper contact pressure.

#### FILE INOPERABLE RESET (FIR)

This interface line provides a direct reset on the File Inoperable latch. The inactive level for this signal is a logical one. The File Inoperable condition is reset with a logical zero level applied to this line.

#### NOTE:

Under no circumstances should the drive be operated with this signal at a constant logical zero level since all data safety circuitry will be defeated.

#### WRITE GATE (WRITE GATE)

Write Gate is an interface line which controls the writing of data on the disk. A logical one level on this interface line turns off the current source to the write drivers along with the current sinks for the write current. A logical zero level on this line enables the write current source and current sinks, and disables the stepping circuitry.

#### WRITE DATA (WRITE DATA)

This interface line provides the data to be written on the disk and each transition from the logical one level to logical zero level causes the current through the R/W head to be reversed. Input impedance for Write Data =  $100\Omega$ .

INDEX (INDEX)

This interface signal is provided by the disk drive once each revolution (166.67 ms) to indicate the beginning of the track. Normally,

this signal is a logical one level and makes the transition to the logical zero level for a period of .4 ms once each revolution.

## TRACK OO (LTZ)

·--

The Track 00 interface signal indicates when the R/W head is positioned at track zero (the outer most data track) and the access circuitry is driving current through phase one of the stepping motor (Head Load signal true). This signal is at a logical one level when the R/W head is not at track zero and is at a logical zero level when the R/W head is at track zero.

FILE INOPERABLE (WCE)

File Inoperable is the output of the data safety circuitry and is at a logical zero level when a condition which jeopardizes data integrity has occurred.

| File Inoperable | = (Write Gate | Write I Sense) |

|-----------------|---------------|----------------|

|                 | +(Write Gate  | Write I Sense) |

|                 | +(Write Gate  | Head Load)     |

|                 | +(Write Gate  | Write Data)    |

|                 | +(Write Gate  | Door Closed)   |

#### SECTOR (SECTOR)

This interface signal is provided by the disk drive 32 times each revolution. Normally, this signal is a logical one level and makes the transition to the logical zero level for a period of .4 ms 32 times each revolution (32 sectors).

WRITE PROTECT (WPT)

This interface signal is provided by the disk drive to allow the user an indication when a write protected diskette is installed. The signal is a logical one level when the diskette is not protected and a logical zero when it is protected.

#### SEPARATED DATA (READ DATA)

Separated Data is the interface line over which read data is sent to the using system. The frequency modulated signal written on the disk is demodulated by the drive electronics and the data pulses are sent to the using system over this interface line. Normally, this signal is a logical one level and each data bit recorded on the disk causes a transition to the logical zero level for 200 ns.

#### SEPARATED CLOCK (READ CLOCK)

The Separated Clock interface line provides the using system the clock bits recorded on the disk in frequency modulation recording. The levels and timing are identical to the Separated Data line except that a separated clock pulse occurs each 4µs, instead of in multiples of 4µs.

#### READY (FRN)

This interface signal is provided to indicate to the user that a diskette is installed properly, the door is closed, and that two index or sector pulses have been detected (diskette is turning). This signal is at a logical one level when not ready and is at a logical zero level when ready.

DLI (FLOPPY DISK) - PIN ASSIGNMENT-

| SIGNAL NAME | PIN NO. | SIGNAL NAME | PIN NO. |

|-------------|---------|-------------|---------|

| FDS         | 23      | INDEX       | 15      |

| DDS         | 5       | ITZ         | 25      |

| STP         | З       | WCE         | 29      |

| HPS         | 21      | SECTOR      | 19      |

| FIR         | /       | WPT         | 17      |

| WRITE GATE  | 7       | READ DATA   | 13      |

| WRITE DATA  | 9       | READ CLOCK  | 11      |

|             |         | FRN         | 27      |

TO DISK DRIVE

FROM DISK DRIVE

1.4

NOTE:

EVEN PINS 2 THROUGH 26 ARE CONNECTED TO ± OV.

- OPERATIONAL SPECIFICATION -

This section contains the operational specifications for the three 10 Megabyte Hard Disks and the 3.1 Megabit Floppy Disk controlled by the Device Adapter.

# - HARD DISK - 100 MEGABIT (10 MEGABYTE -)

1.5

#### GENERAL DESCRIPTION:

\* The Diablo Series 40 Disk Drive Model 44 is presently being used. It uses both a fixed disk and a removable top loading disk cartridge, for a capacity of 100 megabits of data at a recording density of 2200 Bits Per Inch (BPI) and an average access time of 38 milliseconds. Each disk has an upper and lower surface of 408 tracks each with a lateral track density of 200 Tracks Per Inch (TPI), giving the disk 408 cylinders of 4 tracks each. There are 24 sectors per track yielding a total of 39,168 sectors, with 256 (8-bit) bytes of usable data per sector.

#### NOTE:

Hard Disk is the general terminology given to a disk system where the Read/Write head(s) do not make physical contact with the recording media. This recording media is of a close tolerance unflexable material.

\*See Diablo Systems Incorporated, Series 40 Disk Drive Maintenance Manual. ('Diablo' is a trademark of Diablo Systems Incorporated.)

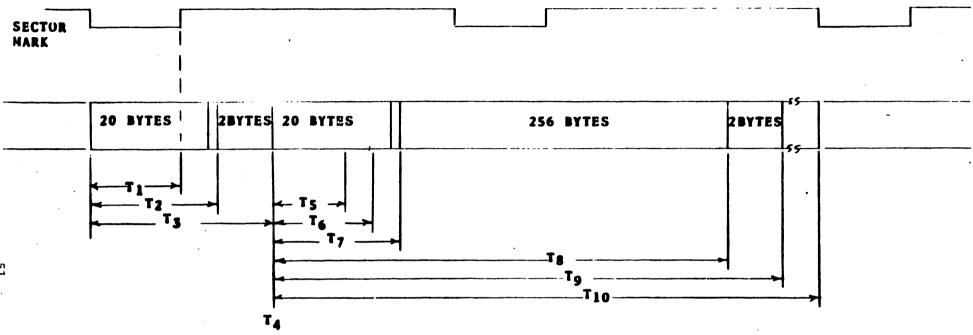

DISK FORMAT

Each track on the disk is divided into 24 sectors of equal length. Each full track rotation is approximately 25 milliseconds for the 2400 RPM drive. The following diagram illustrates the details of the track sector.

|          |        |        |     | ·      |            |     | 1        |

|----------|--------|--------|-----|--------|------------|-----|----------|

| PREAMBLE | SYNC 1 | HEADER | GAP | SYNC 2 | DATA FIELD | CRC | POSTAMBE |

Preamble - This field is created during a format operation. It starts at the leading edge of the sector mark and consists of 20 bytes: the first nineteen bytes are 0 (all clock bits), the first 6 bits of the twentieth byte are 0, the last two bits are 'll'. This field is used to switch the head to read the sync 1 character during write, read, and read/verify operations.

Sync 1 - This field is contained in the preamble. It consists of three bits (011). The interface detects a 011 and prepares to read the header.

Header - This section contains information identifying the sector as cylinder, head, disk, and actual sector address. It is created as a result of the format command. It is read and compared with MDR for write, read, and read/verify operations.

The following diagram describes the 16 bits of the header:

S1 S2 S3 S4 **T1** т2 T3 T4 **T**5 **T6** T7 **T**8 TO D H SO 0 MDRH 7/0 MDRL 7

#### (MEMORY DATA REGISTER)

where Tl to T8 = Low 8 order bits of cylinder address T0 = High order bit of cylinder address D = Disk = 0 - Fixed disk = 1 - Removable disk H = Head = 0 - Bottom head = 1 - Top head S0 to S4 = Sector Address

For the seek command, bits 9 and 10 are used to select the platter (fixed/removable) and the surface (top/bottom) respectively.

Gap - The gap is composed of all clock bits but for the last two bits which are 'll'. This field serves as a preamble to the data field. The gap is used for header comparison time and to allow for switching of the heads in the case of a write command.

Sync 2 - The sync 2 character is the last three bits of the gap (011). These bits are created during a write operation. For read and read/verify operations, these bits designate the start of the data field.

Data Field - This field contains 256 bytes of data.

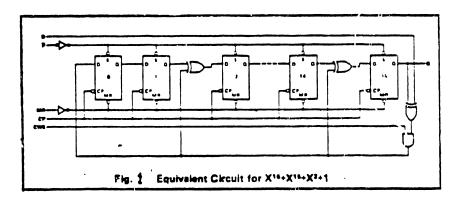

CRC - (Cyclic Redundancy Check) - This check is a 2-byte character created from the sync 2 character and the 256 bytes of the data field.

Postamble - This section is composed of all clock bits.

# DISK SECTOR FORMAT

| FIELD                | 2400 RPM     | APPROXIMATE BYTES |

|----------------------|--------------|-------------------|

| Preamble &<br>Sync 1 | 64 µsec      | 20                |

| Header               | 6.4 ивес     | 2                 |

| Gap And<br>Sync 2    | 32 µвес      | 10                |

| Data Field           | 819.2 µsec   | 256               |

| CRC                  | 6.4 µзес     | 2                 |

| Postamble            | 113.66 µsec  | 35.5              |

| TOTAL                | 1041.66 µsec | 325.5             |

The Preamble and Postamble are necessary to absorb system tolerances.

DISK SELECTION:

The hard disk gains access to the communication lines whenever the pointer register equals (00, 01, 10).

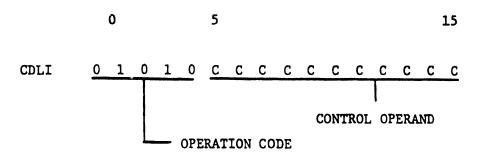

CDLI - CONTROL DEVICE LEVEL INTERFACE

Upon detection of this instruction, the MP sets the INPUT bit=0, alerts the DAI and allows the control operand. MDR (16 bits) and the pointer register (2 bits) are also allowed to the DAI. The \*INPUT status bit is set to '1' by the DAI in response. The status register must not be used as a B-bus operand when waiting for the DAI response (INPUT bit).

FORMAT:

\*The input bit signals the completion of an assigned task by the Device Adapter.

The table below lists the 9 commands as specified by the control operand.

| BIT    |    | OPERATION                  |

|--------|----|----------------------------|

| 8,9    | -  | 01 – Give Disk Status      |

|        | -  | 10 - Give Operation Status |

|        | =  | 11 - Give Sector           |

| 10     | -  | 1 - Seek                   |

| 11     | -  | 1 - Surface Operation      |

| 12, 13 |    | 00 - Format                |

|        |    | 01 - Write                 |

|        | 82 | 10 - Read                  |

|        | -  | 11 - WRICE / Verify        |

| 15     |    | 1 - Restore                |

# GIVE DISK STATUS (CDLI 040)

Upon detection of this command the interface strobes 5 bits of status reflecting the state of the disk into BITS MDL3-MDL7. BITS MDL0-MDL2 are made 1. The status bits should be in MDRL by the start of the next instruction cycle.

| MDRL | Bit |     | Condition                |

|------|-----|-----|--------------------------|

| MDL3 | -   | 0 - | Address interlock        |

| MDL4 | =   | 0 - | File ready               |

| MDL5 |     | 0 - | Ready to seek/read/write |

| MDL6 | =   | 0 - | Seek incomplete          |

| MDL7 | -   | 0 - | Write check              |

Address Interlock - This bit is set to 0 if the seek command cannot be executed due to a track address greater than the number of tracks available. This bit remains 0 until a restore command or a seek command to a valid address has been accepted.

File Ready - This bit is set to 0 if all of the following conditions are met:

- (a) Power on.

- (b) Dust cover loaded.

- (c) Equipment drawer closed.

- (d) LOAD/RUN switch in RUN position.

- (e) Start-up cycle complete.

- (f) Write check. (NOT ACTIVE (HIGH)).

Ready to Seek/Read/Write - This bit is set to 0 if the disk is not in the process of executing a restore command or a seek command to an address other than the one under the heads and if the File Ready bit is 0. The seek incomplete bit has no bearing on this bit.

Seek Incomplete - This bit is set to 0 if a malfunction keeps the seek operation from completing. This bit remains 0 until a restore command has been completed by the disk.

Write Check - This bit is set to 0 if a malfunction occurs which may not be corrected by the microprocessor.

GIVE OPERATION STATUS (CDLI 080)

Upon detection of this command, the interface strobes 8 bits of status reflecting the result of a read, write, wire/verify, or format operations into BITS MDLO-MDL7. The status bits should be in MDRL by the start of the next instruction cycle.

MDRL Bit Condition MDL0 = 1 - File not ready MDL1 = 1 - Parity Error MDL2 = 1 - Illegal address MDL3 = 1 - Data compare error MDL4 = 1 - Header compare error MDL5 = 1 - CRC error MDL6 = 1 - Overrun MDL7 = 1 - Mixed error

File Not Ready - This bit is set to 1 if the disk presents a file not ready condition (write check, etc.).

Parity Error - This bit is set to 1 whenever the interface is in a direct memory access operation and the memory controller reports a parity error.

Illegal Address - This bit is set to 1 whenever the interface is in a direct memory access operation and the memory controller reports an illegal address.

Data Compare Error - This bit is set to 1 if during a read/verify operation the data does not compare equal.

Header Compare Error - This bit is set to 1 whenever the interface finds that the header bytes in MDR are not the same as the header bytes in the sector.

CRC Error - This bit is set to 1 whenever the interface finds that the computed CRC is not the same as the CRC written on the disk.

**Overrun -** This bit is set to 1 if the interface is ready for a memory operation and the last memory operation has not completed.

Mixed Error - This bit is set to 1 if any of the following conditions occur during an operation:

- (a) The interface cannot detect the sync 2 character.

- (b) There is still data to be read or written on the disk and a sector mark has been detected.

- (c) No sector mark detected after a sector's time.

Operation status must be requesced after every surface operation. The microprogram should time the duration of the surface operation since a condition may arise which keeps the input bit from being set.

#### GIVE SECTOR (CDLI 0C0)

\* The complemented value of the sector address lines is strobed into BITS MDL3-MDL7. If the sector is not valid (a sector mark pulse is present), BIT MDL2 is made 0. BITS MDL0 and MDL1 are forced to 1.

SEEK (CDLI 020)

The low order 8 bits of track address are in BITS MDHO-MDH7, the high order track address bit is in BIT MDLO. The interface gates the 9 track address bits to the disk address lines and issues a strobe. If the address is invalid, the address interlock bit will reflect this condition. If the address interlock bit is zero and the disk accepts the command, the address interlock bit is set to 1.

If the command is accepted and the track address is valid, the heads are placed at the selected track.

If the disk is deselected, the platter select and surface select revert to the default values (fixed platter, bottom surface). Because of this, it is necessary to issue a seek command to select the platter and surface prior to a surface operation. After platter and surface selection, a six microsecond delay must be introduced prior to requesting the selected sector counter. Also a 25 microsecond delay must be introduced from the time of seek to the time of a surface operation.

For the above four commands, the interface does not set the input bit to 1.

# FORMAT (CDLI 010)

Upon receipt of this command, the interface awaits the leading edge of the sector mark pulse. Once it has sensed it, the format operation

\*The sector address is active low (OV, .4V). MDL3 is the most significant bit of the sector address.

starts. The interface creates the preamble, writes the sync 1 character and writes the header (from MDR-16 bits). The input bit is set to 1 immediately after the header is written.

# WRITE (CDLI 014)

Upon receipt of this command, the interface awaits the leading edge of the sector mark pulse. Once it has sensed it, the write operation starts. The interface detects the sync 1 character and prepares to read the header. The read header is compared with the header in MDR (16-bits); if the headers do not match, a status bit is set in the operation status and no data transfer takes place. The input bit is set to 1, and the operation is terminated.

If the headers match, the interface writes the gap and the sync 2 character designating the start of the data field. The MAR contains the memory address from which the data is to be transferred. The interface reads two bytes at the time from memory, increments the memory address by 2, writes the two bytes on the disk and computes the CRC. A total of 256 data bytes are transferred from memory, the two CRC bytes are written, the interface sets the input bit to 1, and creates the postamble.

#### READ (CDLI 018)

Upon receipt of this command, the interface awaits the leading edge of the sector mark pulse. Once it has sensed it, the read operation starts. The interface detects the sync 1 character and prepares to read the header. The read header is compared with the header in MDR (16-bits); if the headers do not match, a status bit is set in the operation status and no data transfer takes place. The input bit is set to 1, and the operation is terminated.

If the headers match, the interface detects the gap and the sync 2 character and prepares to read the data. The MAR contains the memory address at which the data is to be transferred. The interface reads two

bytes at the time from the disk, computes the CRC, writes the two bytes into memory and increments the memory address by 2. A total of 256 data bytes are transferred to memory. The computed CRC is compared with the CRC read from the disk; if they do not match, the appropriate bit in the operation status reflect the condition. The interface sets the input bit to 1 indicating operation completion.

The CRC is written and checked by the device adapter. The MP never participates in this activity, however, the MP is notified if a CRC error has occurred.

### WRITE /VERIFY (CDLI 016)

Upon receipt of this command, the interface awaits the leading edge of the sector mark pulse. Once it has sensed it, the operation starts. The interface detects the sync 1 character and prepares to read the header. The read header is compared with the header in MDR (16-bits); if the headers do not match, a status bit is set in the operation status and no data comparison takes place. The input bit is set to 1, and the operation is terminated.

If the headers match, the interface detects the gap and the sync 2 character and prepares to read the data from the disk. The MAR contains the memory address from which the data is to be read. The interface reads 2 bytes from the disk and two bytes from memory at a time, compares them and if they do not match, the data compare error bit in the status register is set to 1. The CRC character is computed. This is done for all of the 256 bytes in the disk. The computed CRC is compared with the CRC read from the disk; if it does not match, the appropriate bit in the operation status reflects the condition. The interface sets the input bit to 1 indicating operation completion.

If there is a sector mark pulse at the time one of the above four commands is issued, the interface sets the input bit to 1 before the next instruction cycle and terminates the operation.

This command causes the heads to be positioned over track 0; once there, the seek incomplete indication is reset.

The input bit is not set to 1 by the interface as a response to this command.

## 8300 HARD DISK TIMING

**10 MEGA BYTE** 2400 RPM

- T3 LAST BIT OF THE TWO BYTE HEADER (22 BYTES) (70.4uS) (CTR-176 FORMAT) (CTR=16 READ/WRITE/READ VERIFY)

- T4 = REFERENCE POINT FOR READ/WRITE/READ VERIFY SEQUENCE, COUNTER NOW LOADED TO 96

- T5 = SWITCH HEADS DURING A WRITE SEQUENCE (6 BYTES) (19.2uS) (CTR=144)

- T6 = STARTING POINT DURING A READ-OR A-READ VERIFY, LOOKING FOR SYNC CHARACTER 011(8 BYTES) (25.6uS) (CTR=160)

- T7 = FINISH WRITING DATA SYNC CHARACTER DURING A WRITE SEQUENCE (10 BYTES) (32uS) (CTR=176)

- T8 = END OF WRITE FOR SYNC TWO AND DATA FIELD (266 BYTES) (851.2uS) (CTR=2224)

- **T9 = END OF CRC (268 BYTES( (857.6uS) (CTR=2240)**

, . . .

T10 = END OF POSTAMBLE (303 BYTES) (969.6uS) (POSTAMBLE=112uS)

- FLOPPY (315 KILOBYTE) -

# GENERAL DESCRIPTION:

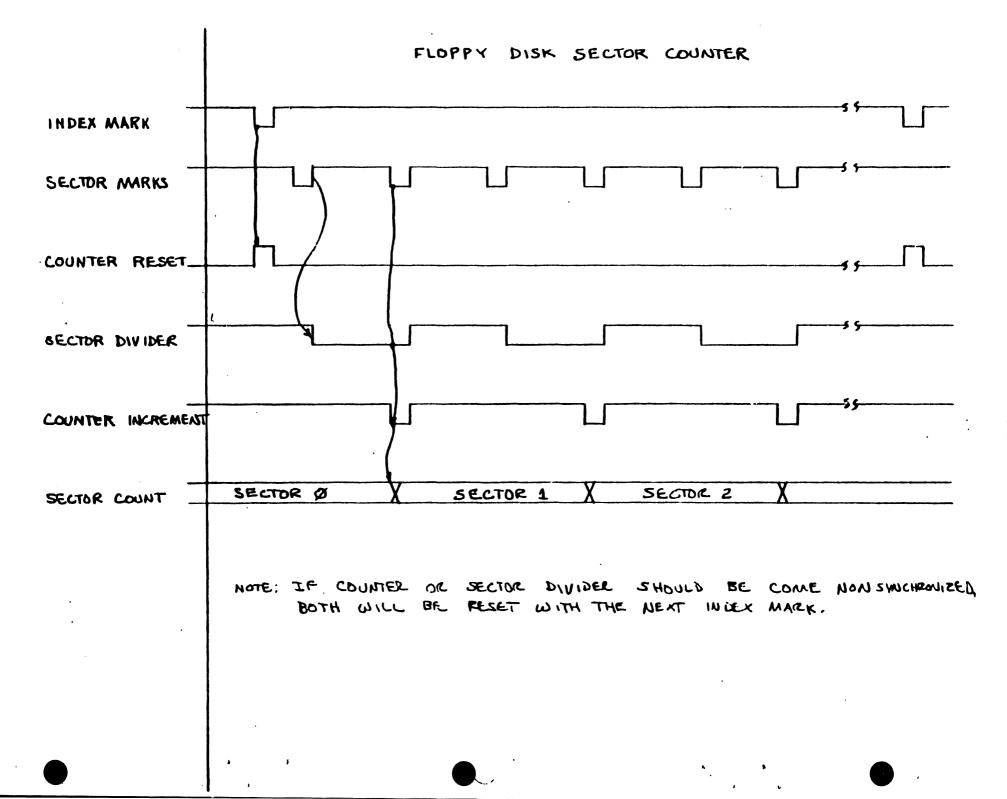

The Shugart Floppy \*Model 901 consists of one diskette, one read/ write head which makes contact with the diskette's surface during step and surface operations, one PCB which provides some elementary functions, and other controlling and controlled mechanisms. Most of the electronics necessary to control the floppy are also used to control the hard disks. There are a few components which are dedicated to the control of the floppy. One is the sector counter which is set to 0 by the leading edge of the index mark and incremented by 1 every time two sector marks have been sensed. Another is the timer which is a 12.6 ms (+10%) one shot that is controlled by a CDLI instruction and monitored through one bit obtained in MDRL after execution of the Give Disk Status CDLI instruction. The timer is used to fulfill three functions: to time the duration of step, to time the head settling time once at the desired track, and to measure the 50 ms interval that must be introduced between head load and valid data. Those components used to control the hard disk are modified (clock frequency changed, counters preset, etc.) to control the floppy.

# NOTE:

Floppy Disk is the general terminology given to a disk system where the Read/Write head(s) makes physical contact with a flexible recording media.

\*See Shugart Associates Diskette Storage Drive Manual SA900/901

(Wang Laboratories Service Bulletin No. 46.2 starting on page 10).

#### DRIVE CHARACTERISTICS

Rotational Speed: 360 RPM 166.72 ms Rotational Period: Average Access Time: 424 ms Average Latency: 83 ms 31250 bytes/sec. Data Transfer Rate: Bit Cell Time: 4 usec Track to Track Access Time: 11 ms Head Settling Time Once at Desired Track: 11 ms One Sector's Time: 5.21 ms Number of Sectors Per Track: 32 Number of Tracks: 77 Sector Mark Duration: 400 µsec + 200 µsec 400 µsec + 200 µsec Index Mark Duration: Direction Select Pulse Duration: l usec min. Time Between Head Load and Valid Data: 50 ms Time Between Head Load and Step: 30 ms

#### DISK FORMAT

Each track on the disk is divided into 32 sectors of equal length. The present specifications require a sector to be 256 data bytes long. In order to allow for this, two sectors must be used, so in effect, each track is divided into 16 sectors each lasting 10.42 ms. The following diagram illustrates the sector organization.

| PREAMBLE | SYNC 1 | HEADER | GAP | SYNC 2 | DATA FIELD | CRC | POSTAMPLE |

|----------|--------|--------|-----|--------|------------|-----|-----------|

|          |        |        |     |        |            |     |           |

Preamble - This field is created during a format operation. It starts at the leading edge of the sector mark and consists of 20 bytes: the first nineteen bytes are 0 (all clock bits), the first 6 bits of the twentieth byte are 0, the last two bits are 'll'. This field is used to switch the head to read the sync 1 character during write, read, and read/verify operations.

Sync 1 - This field is contained in the last byte of the preamble. It consists of three bits (Oll). The interface detects a Oll and prepares to read the header.

Header - This section contains information identifying the sector as cylinder, head, disk, and actual sector address. It is created as a result of the format command. It is read and compared with MDR (16-bit) for write, read, and read/verify operations.

The following diagram describes the 16 bits of the header:

#### Header

| First Byte           |                              |      |    |   |   |   |                        | Second Byte |       |      |      |     |   |   |   |   |

|----------------------|------------------------------|------|----|---|---|---|------------------------|-------------|-------|------|------|-----|---|---|---|---|

| 0                    |                              | MDRH |    |   | 7 |   |                        | 0           |       |      | MI   | ORL |   |   | 7 |   |

| 0                    | 64                           | 32   | 16 | 8 | 4 | 2 | 1                      |             | 0     | 0    | 0    | 0   | 8 | 4 | 2 | 1 |

| Track Address        |                              |      |    |   | • |   |                        | Se          | ctor  | Add  | ress |     |   |   |   |   |

| Valid Binary Values: |                              |      |    |   |   |   | Val                    | Lid 1       | Binar | ry V | alue | s : |   |   |   |   |

| 0000 0000 through    |                              |      |    |   |   |   | 000                    | 0 00        | 000   | thro | ugh  |     |   |   |   |   |

|                      | <b>0100 1100 =</b> 77 Tracks |      |    |   |   |   | 0000 1111 = 16 Sectors |             |       |      | tors |     |   |   |   |   |

Gap - The gap is composed of all clock bits but for the last two bits which are 'll'. This field serves as a preamble to the data field. The gap is used for header comparison time and to allow for switching of the heads in the case of a write command.

Sync 2 - The sync 2 character is the last 3 bits of the gap (011). These bits are created during a write operation. For read and read/ verify operations, these bits designate the start of the data field.

Data Field - This field contains 256 bytes of data.

CRC - (Cyclic Redundancy Check) - This check is a 2-byte character created from the sync 2 character and the 256 bytes of the data field.

Postamble - This section is composed of all clock bits.

The preamble and postamble are necessary to absorb system tolerances.

#### FIELD LENGTH APPROXIMATE BYTES Preamble & Sync 1 640 µsec 20 Header 64 µsec 2 Gap & Sync 2 640 usec · 20 Data Field 8192 µsec 256 CRC 64 µвес 2 Postamble 820 µsec 25 TOTAL 10420 µsec 325

# DISKETTE SECTOR FORMAT

#### **DISK SELECTION:**

The floppy disk gains access to the communication lines whenever the pointer register is ll. It is undesirable to have the select/deselect function become the head load/unload function. The disk select sole function is to qualify the communication lines for floppy operations.

# CDLI - CONTROL DEVICE LEVEL INTERFACE

Upon detection of this instruction, the MP sets the INPUT bit=0, alerts the DAI and allows the control operand. MDR (16 bits) and the pointer register (2 bits) are **giso** allowed to the DAI. The \*INPUT

\*The input bit signals the completion of an assigned task by the Device Adapter.

status bit is set to 'l' by the DAI in response. The status register must not be used as a B-bus operand when waiting for the DAI response (INPUT bit).

FORMAT:

The table below lists the 12 commands as specified by the control operand.

OPERATION

BIT

| 5, 6, 7 = | 001 - Step                  |

|-----------|-----------------------------|

| J, U, 7 - | 001 - Scep                  |

| E         | 111 - Head Control          |

| =         | 011 - Direction Select      |

| =         | 100 - Start Timer           |

|           | 101 - File Inoperable Reset |

| 8,9 =     | 01 - Give Disk Status       |

| =         | 10 - Give Operation Status  |

| -         | 11 - Give Sector            |

| 11 =      | 1 - Surface Operation       |

| 12, 13 =  | 00 - Format                 |

| *         | 01 - Write                  |

| =         | 10 - Read                   |

| -         | 11 - Waite/Verify           |

|           |                             |

GIVE DISK STATUS (CDLI 040)

Upon detection of this command, the interface strobes 5 bits of status reflecting the state of the disk into MDRL. The status should be in MDRL by the start of the next instruction cycle.

MDRL Bit Condition

MDL0 = 0 - Track 0

MDL1 = 0 - Write Protect

MDL2 - Undefined

MDL3 - Undefined

MDL4 = 0 - File Ready

MDL5 = 0 - Timer Not Active

MDL6 - Undefined

MDL7 = 0 - File Inoperable

Track 0 - This bit is 0 whenever the head is positioned at the outermost data track (away from disk registration hub).

Write Protect - This bit is 0 whenever the diskette is write protected. It is a microprogram responsibility to reject any write commands to a diskette that is write protected.

File Ready - This bit is 0 when all of the following conditions are met:

- (a) Power on.

- (b) Diskette properly loaded.

- (c) Door closed.

- (d) Diskette is turning (two sector marks sensed).

The ready indication is provided when two sector marks (or an index mark and a sector mark) are sensed, not necessarily when the drive is up to speed For this reason the program introduces a two second delay at initialize time.

Timer Not Active - This bit goes to 1 as soon as the Start Timer command is issued; it goes to 0 once 12.6 ms  $(\pm 10\%)$  have elapsed from the time the Start Timer command was received.

File Inoperable - This bit is set to 0 whenever the head is improperly energized. When this bit is 0, no surface operations should take place since the data integrity circuitry is not at its optimum. A File Inoperable Reset command must be issued to reset this indicator.

GIVE OPERATION STATUS (CDLI 080)

This command produces the result described in the hard disk specification and must be used as specified there.

GIVE SECTOR (CDLI 0C0)

\* This command works as specified in the hard disk specification. Bit MDL3 always receives a 1.

Surface Commands - Format (CDLI 010), Write (CDLI 014), Read (CDLI 018), /Verify (CDLI 01C). These commands work as specified in the hard disk specification.

STEP (CDLI 100)

This command causes the interface to pulse the step line which in turn causes the floppy to move the head one track in the direction previously selected. For this command to work properly, the head must have been loaded for at least 30 ms. The interface does not require program attention during the time (11 ms) that it takes the step to complete, that is, the floppy may be deselected.

\*The floppy has only 4 sector address lines (MDL4 becomes the most significant bit).

HEAD CONTROL (CDLI 700)

Through this command, the head may be loaded and unloaded. Once the head is loaded, the microprogram must introduce a 50 ms delay before valid data is expected, that is, before a Surface operation is started. Also, the microprogram must delay at least 30 ms from the time the head is loaded to the time of the first step. This delay is part of the 50 ms delay.

Bit MDL4 of MDRL is used to specify load or unload.

MDL4 = 0 - Head Unload. MDL4 = 1 - Head Load.

The other bits in MDRL may be set to any value while issuing this command.

# DIRECTION SELECT (CDLI 300)

This command is used to select the direction in which the heat is to move during the Step command. The direction selected is stored in the interface so it is not necessary to select it every time a stop is to be done. The direction is selected through bit MDL4 of MDRL.

MDL4 = 0 - Direction Out (towards track 0). MDL4 = 1 - Direction In (towards track 76).

The other bits in MDRL may be set to any value. The following sequence is acceptable:

Load MDRL with Direction Bi Direction Select Step Start Timer

The direction may be selected any time after initialize.

#### START TIMER (CDLI 400)

Upon receipt of this command, the interface will fire the /2.4 ms  $(\pm 10\%)$  one shot and set the Timer Not Active bit to 1. Once the /2.6 ms have elapsed, the Timer Not Active bit is set to 0. This is the only command that may be issued independent of the selected device, that is, the pointer register may contain any value and the command will be acknowledged. However, to monitor the timer (through the Give Disk Status CDLI instruction) the pointer register must contain a 'll'. The timer may be started and monitored even if there is no disk connected in the interface port.

#### FILE INOPERABLE RESET (CDLI 500)

This command will cause the File Inoperable bit to be reset without clearing the condition which caused it to be set. This command is necessary because if the condition clears, the File Inoperable bit will not be automatically set to 1.

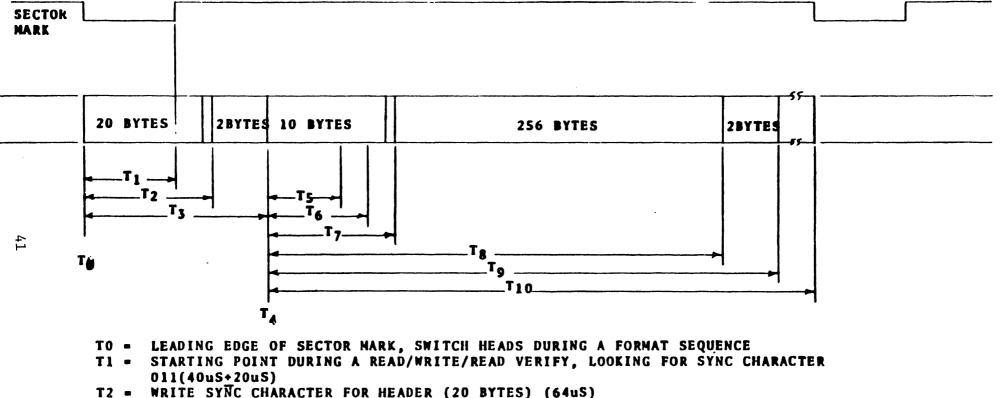

**8300 FLOPPY DISK TIMING**

- TO LEADING EDGE OF THE SECTOR MARK, SWITCH HEADS DURING A FORMAT SEQUENCE

- T1 = STARTING POINT DURING A READ/WRITE/READ VERIFY, LOOKING FOR SYNC CHARACTER 011 (400uS+200uS)

- T2 WRITE SYNC CHARACTER FOR HEADER (20 BYTES) (640uS)

- T3 = LAST BIT OF THE TWO BYTE HEADER (22 BYTES) (704uS) (CTR=176 FORMAT) (CTR=16 READY/WRITE/READ VERIFY)

- **T4 = REFERENCE POINT FOR READ/WRITE/READ VERIFY** SEQUENCES

- TS = SWITCH HEADS DURING A WRITE SEQUENCE (16 BYTES) (512uS) (CTR-144)

- STARTING POINT DURING A READ-OR A- READ VERIFY, LOOKING FOR SYNC CHARACTER 011 T6 = (18 BYTES) (576uS) (CTR=160)

- T7 FINISH WRITING DATA SYNC CHARACTER DURING A WPITE SEQUENCE (20 BYTES) (640uS) (CTR = 176)

- TS = END OF WRITE FOR SYNC TWO AND DATA FIELD (276 BYTES) (8832uS) (CTR=2224)

- T9 = END OF CRC (278 BYTES) (8896uS) (CTR=2240 WRITE) (2224 READ)

- T10- END OF POSTAMBLE (303 BYTES) (9696uS) (POSTAMBLE=800uS)

**\*ALL T. SES SHOWN ARE NOMINAL**

The hardware operation is broken down into major elements of operation - i.e., each element described has, for the most part, an independent circuit operation and provides a distinct operational function.

These major element descriptions are limited to the immediate circuit operation. The relationship of these elements to each other are described in the Instruction Operation Section - 3.0.

The following elements are described:

# ELEMENT

# SECTION

| •   | Write Clock                                               | 2.1  |

|-----|-----------------------------------------------------------|------|

| •   | Disk Control                                              | 2.2  |

| •   | Bit Serialization Register (BSR)                          | 2.3  |

| •   | Bit Counter                                               | 2.4  |

| •   | Sector Counter                                            | 2.5  |

| •   | Direct Memory Access (DMA)                                | 2.6  |

| •   | Cyclic Redundancy Check (CRC)                             | 2.7  |

| • • | Operational Status Error Flags<br>& Operation Termination | 2.8  |

| •   | Floppy Disk Timer                                         | 2.9  |

| •   | Terminator Voltage & Protect Circuit                      | 2.10 |

- WRITE CLOCK -

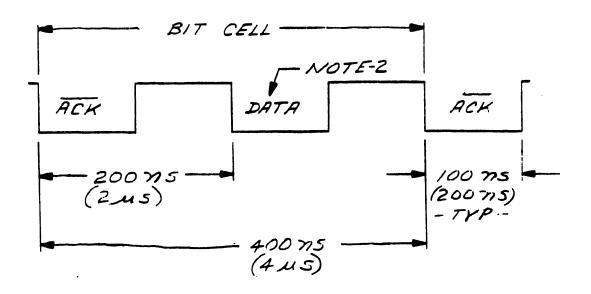

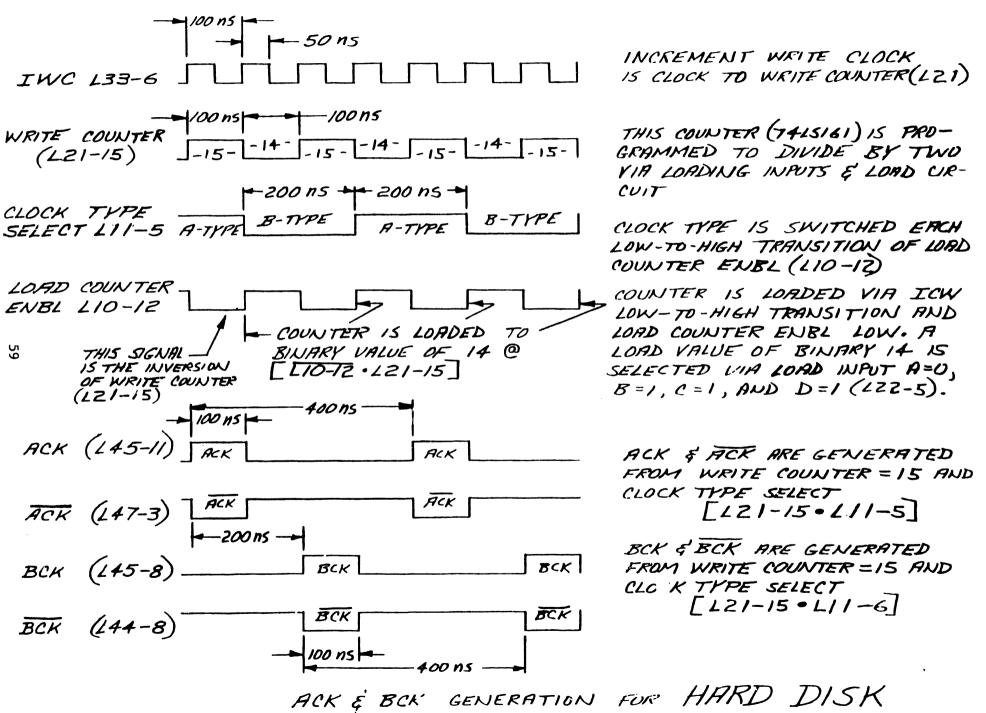

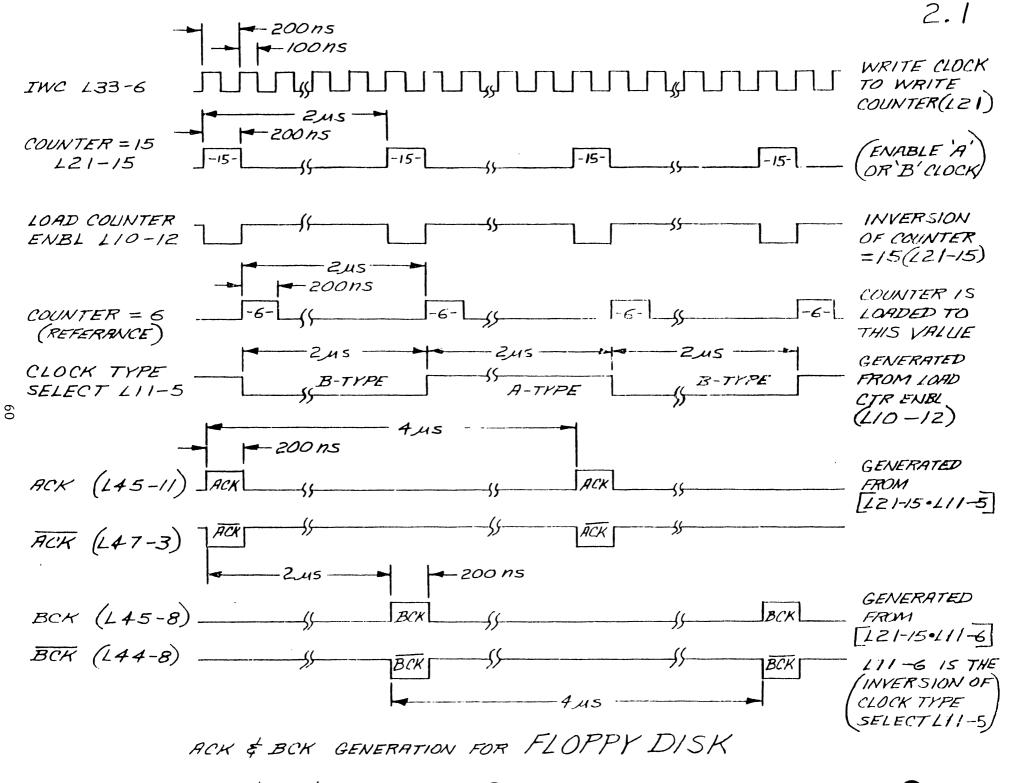

The Write Clock circuit is used to provide all the necessary timing relationships required to write data on the disk drive media - i.e., to generate 'bit-cells' which will contain the data bit, and, to place the data bit within that 'bit-cell'. Two clock components are generated to satisfy this 'bit-cell' arrangement. They are 'A-clocks' (ACK &  $\overline{ACK}$ ), and 'B-clocks' (BCK &  $\overline{BCK}$ ). The 'A-clocks' are used to form the 'bit-cell' and the 'B-clocks' are used to place the data bit in the center of the 'bit-cell'.

Both the hard disk and the floppy disk have this 'bit-cell' arrangement, however, the rotational speed and density of the hard and floppy disks are different. Therefore, the 'bit-cells' and the actual 'A-clocks' and 'B-clocks' are of different duration for each. The write clock network automatically supplies the correct timing for the selected disk drive.

The following schematics, description, and timing diagrams depict the Write Clock operation:

2.1

NOTES:

!. XXX = HARD DISK. (XXX) = FLOPPY DISK. 2. DATA: HIGH = LOGIC O' LOW = LOGIC I' THE DATA IS WRITTEN AT BCK' TIME.

DISK 'BIT-CELL'

#### CIRCUIT OPERATION

The Write Clock network can be broken into two areas. The generation of the Increment Write Clock (IWC), used to step the write counter and to provide the actual pulse width of the 'A-clocks' (ACK & ACK) and the 'B-clocks' (BCK & BCK), and the generation of the 'bit-cell' duration and 'data-bit' placement within the 'bit-cell'.

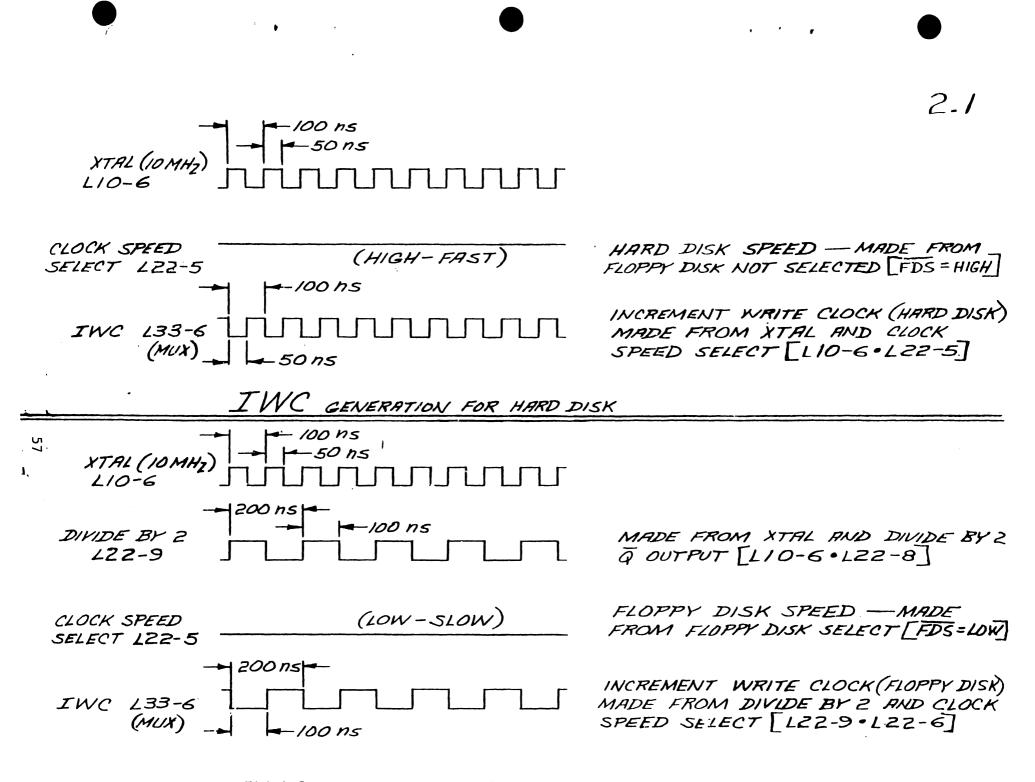

#### INCREMENT WRITE CLOCK (IWC)

A 10 MHz crystal oscillator is the base for all write clock circuitry. The buffered oscillator output (L10-6) is felt at the input of IWC multiplexer (L33-2), and is passed through when the clock speed flop (L22-5) is selected to the hard disk timing (fast, L22-5 = '1'). The speed select flop is set via term FDS at a logic '1' level (floppy disk not selected) and clocked via L10-12 (Write  $\overline{\text{CTR}=15}$ ) on the low to high transition. The write counter is a free running counter clocked by the term IWC (Increment Write Clock). It should be noted that IWC is always active at one of its two speeds.

The output of the IWC multiplexer reflects the inversion of the buffered oscillator (L10-6). This signal has a 100 ns period with a 50% duty cycle. The buffered oscillator output is also felt on the clock input of flop L22-9. The 'Q' output of flop L22-9 (L22-8) is tied to the 'D' input of that flop forming a divide by two counter. When the speed select flop is set to floppy disk timing (L22-5=logic '0') the buffered oscillator output felt on L33-2 is blocked and the divide by two counter felt on L33-5 is gated through the IWC multiplexer via L22-6 felt on L33-4. The output of the IWC multiplexer (L33-6) reflects the inversion of the divide by two flop (L22-9). This signal has a 200 ns period with a 50% duty cycle.