# **VS-85 Computer System**

**Customer Engineering Product Maintenance Manual**

741-1224

#### PREFACE

This document is the Standard Maintenance (STD) Manual for the VS-85 Computer Systems. It is organized in accordance with the approved STD outline established at the Field/Home Office Publications meetings conducted on September 14th and 15th, 1982. The scope of this manual reflects the type of maintenance philosophy selected for this product (swap unit, printed circuit assembly, chip level or any combination thereof).

The purpose of this manual is to provide the Wang-trained Customer Engineer (CE) with instructions to operate, troubleshoot and repair the VS-85 Computer Systems. It will be updated on a regular schedule.

The last page before the back cover is a comment sheet. Please take the time to fill out the comment sheet and return it, via the Home Office mail pouch, addressed to:

Wang Laboratories, Inc. Customer Engineering Technical Documentation M/S 8237 437 South Union Street. Lawrence, Mass. 01843-9984

#### Fourth Edition (August 1984)

This edition of the VS-85 Computer Systems STD manual obsoletes document(s) no. 729-1224-A/A1/A2. The material in this document may only be used for the purpose stated in the Preface. Updates and/or changes to this document will be published as Product Service Notices (PSN's) or subsequent editions.

This document is the property of Wang Laboratories, Inc. All information contained herein is considered company proprietary, and its use is restricted solely for the purpose of assisting the Wang-trained CE in servicing this Wang product. Reproduction of all or any part of this document is prohibited without the prior consent of Wang Laboratories, Inc.

© Copyright WANG Labs., Inc. 1983, 1984

## WARNING

| * |                                                       | * |

|---|-------------------------------------------------------|---|

| * | DO NOT OPEN THE SWITCHING POWER SUPPLY UNDER ANY      | * |

| * | CIRCUMSTANCE. EXTREMELY DANGEROUS VOLTAGE AND         | * |

| * | CURRENT LEVELS (IN EXCFSS OF 300 VOLTS DC AND UN      | * |

| * | LIMITED CURRENT) ARE PRESENT WITHIN THE POWER SUPPLY. | * |

| * |                                                       | * |

| * | DO NOT ATTEMPT TO REPAIR THE SWITCHING POWER          | * |

| * | SUPPLY; IT IS FIELD REPLACEABLE ONLY.                 | * |

| * |                                                       | * |

| * | AFTER POWERING THE UNIT DOWN AND DISCONNECTING THE AC | * |

| * | POWER CONNECTOR FROM THE POWER SOURCE RECEPTACLE,     | * |

| * | ALLOW ONE MINUTE BEFORE REMOVING THE POWER SUPPLY TO  | * |

| * | PROVIDE ADEQUATE TIME FOR ANY RESIDUAL VOLTAGE TO     | * |

| * | DRAIN THROUGH THE BLEEDER RESISTORS.                  | * |

| * |                                                       | * |

۰,

iii

#### WARNING

| *  | ****  | ******   | *******   | **** | ***** | ******** | *** | ****7 | ***** | **** | **:<br>* |

|----|-------|----------|-----------|------|-------|----------|-----|-------|-------|------|----------|

| *  | THIS  | COMPUTER | EQUIPMENT | HAS  | BEEN  | VERIFIED | AS  | FCC   | CLASS | Α.   | *        |

| *  |       |          |           |      |       |          |     |       |       |      | *        |

| ** | ***** |          |           |      |       |          |     |       |       |      |          |

IN ORDER TO MAINTAIN COMPLIANCE WITH FCC CLASS A VERIFICATION, THE FOLLOWING CONDITIONS MUST BE ADHERED TO DURING NORMAL OPERATION OF EQUIPMENT.

- ALL COVERS MUST BE ON SYSTEM AND SECURED IN THE PROPER MANNER.

- ALL INTERNAL CABLES MUST BE ROUTED IN THE ORIGINAL MANNER WITHIN THE CABLE CLAMPS PROVIDED FOR THAT PURPOSE.

- THE MAINTENANCE PANEL DOOR MUST BE KEPT CLOSED.

- ALL EXTERNAL CABLING MUST BE SECURED AND THE PROPER CABLE USED TO ENSURE THAT CABLE SHIELDING IS PROPERLY GROUNDED TO THE CABLE CLAMPS PROVIDED.

- MAKE SURE CONTACT FINGER STRIP CLIP-ON (WLI P/N 654-2139) IS IN PLACE AND UNDAMAGED. (CONTACT FINGER STRIP MAY BE ORDERED AND CUT TO PROPER LENGTH).

- ALL HARDWARE MUST BE PROPERLY SECURED.

The last page before the back cover is a comment sheet. Please take the time to fill out the comment sheet and return it, via the Home Office mail pouch, addressed to:

.

Wang Laboratories, Inc. Customer Engineering Technical Documentation M/S 8237 437 South Union Street. Lawrence, Mass. 01843-9984

729-1224-A

vi

.

#### TABLE OF CONTENTS

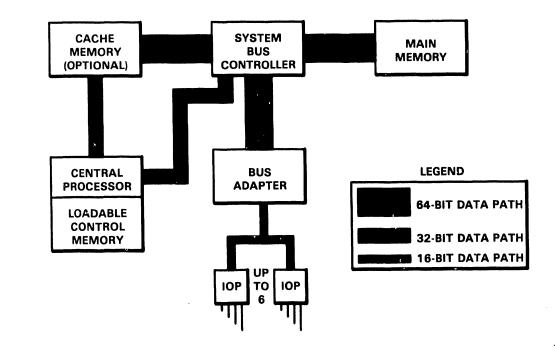

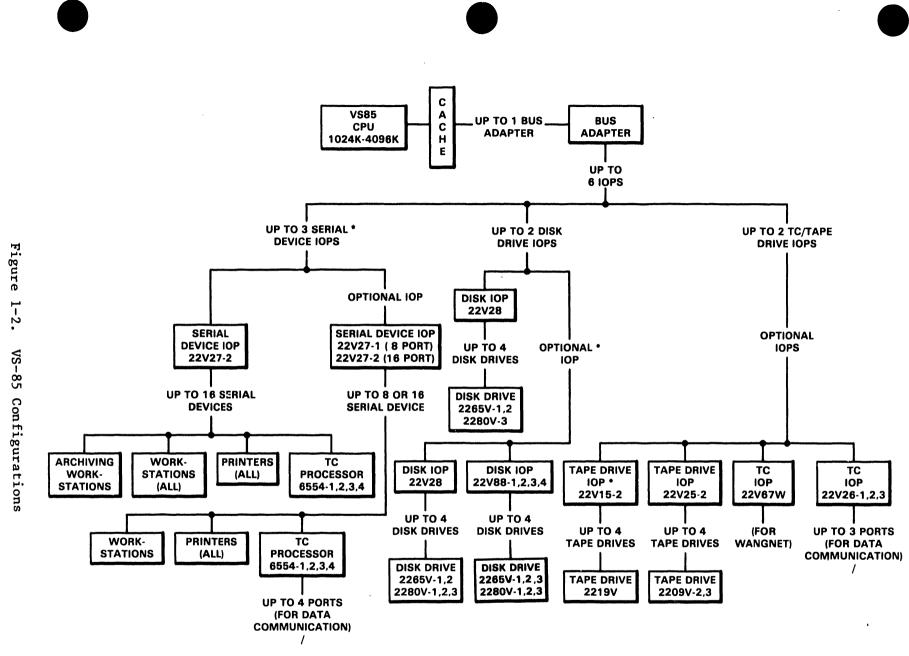

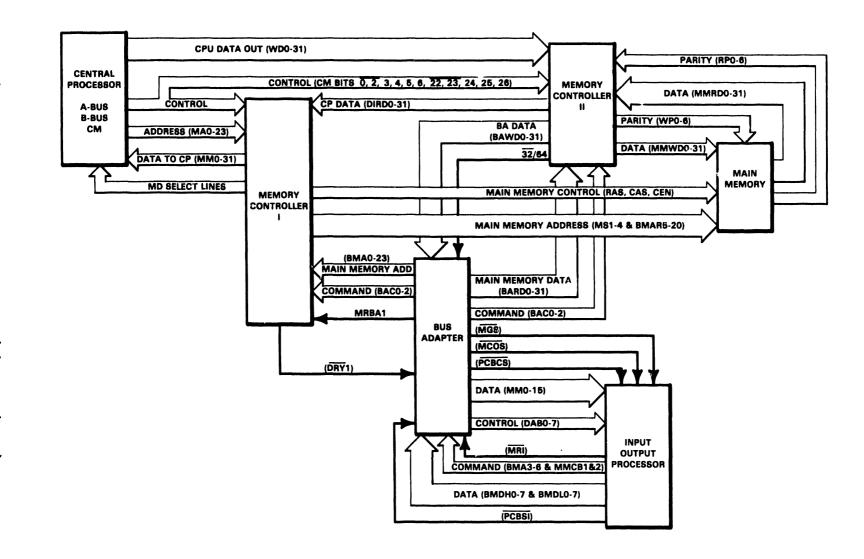

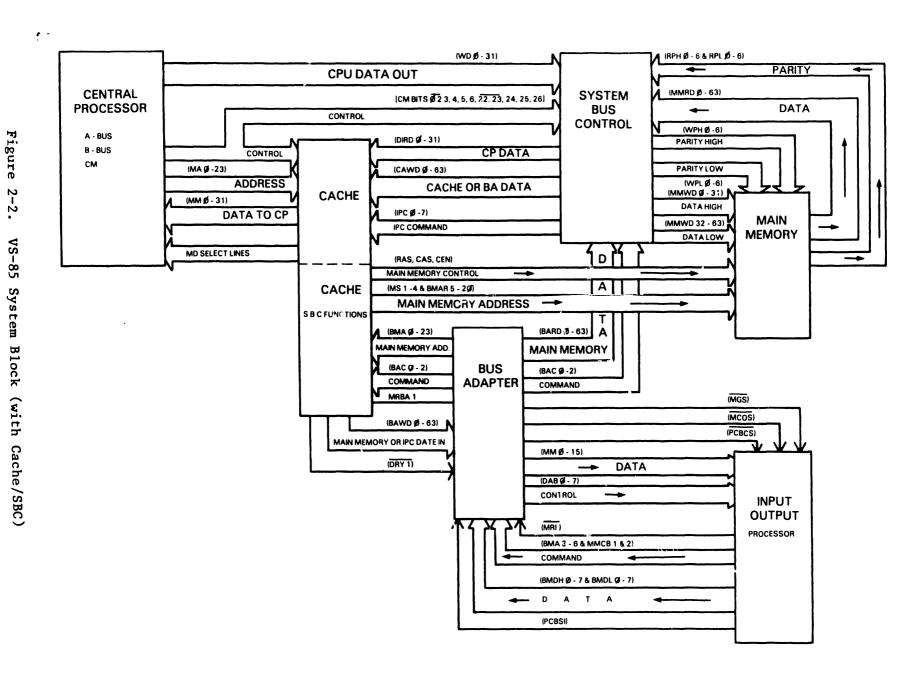

#### CHAPTER 1 INTRODUCTION Page 1.1 1.2 1.3 Related Publications ..... 1-2 1.4 System Description ...... 1-4 1.4.1 Central Processor ..... 1-5 1.4.2 Control Memory ..... 1-6 1.4.3 Memory Controller I (MCI) ..... 1-6 1.4.4 Memory Controller II ..... 1-7 1.4.5 1.4 6 System Bus Controller ..... 1-7 1.4.7 Main Memory ..... 1-7 1.4.8 1.5 1.6 1.7 Display and Maintenance Panels ..... 1-9 1.8 Software Description ..... 1-10 1.9 1.9.1 Operating System 6.10 Description ..... 1-11 1.9.2 User Convenience Features ..... 1-12 1.9.3 1.9.4 Expanded Operating System Features ..... 1-12 1.9.5 Additional System Utilities ..... 1-12 1.9.6 File Protection and Security ..... 1-14 1.9.6.1 File Protection Codes ..... 1-14 1.9.6.2 Special Protection Codes ..... 1-14 1.9.6.3 User Access Rights ..... 1-15 1.10 Error Detection and Correction ..... 1-15 1.11 Configurations ..... 1-16 Model Numbers ...... 1-16 1.11.1 1.11.2 Domestic Upgrade Kits ..... 1-16 1.11.3 International Upgrade Kits ..... 1-16 Associated Peripherals ..... 1-18 1.12 System Specifications ..... 1-18 1.13

#### CHAPTER 2 THEORY OF OPERATION

| 2.1   | Introduction               |

|-------|----------------------------|

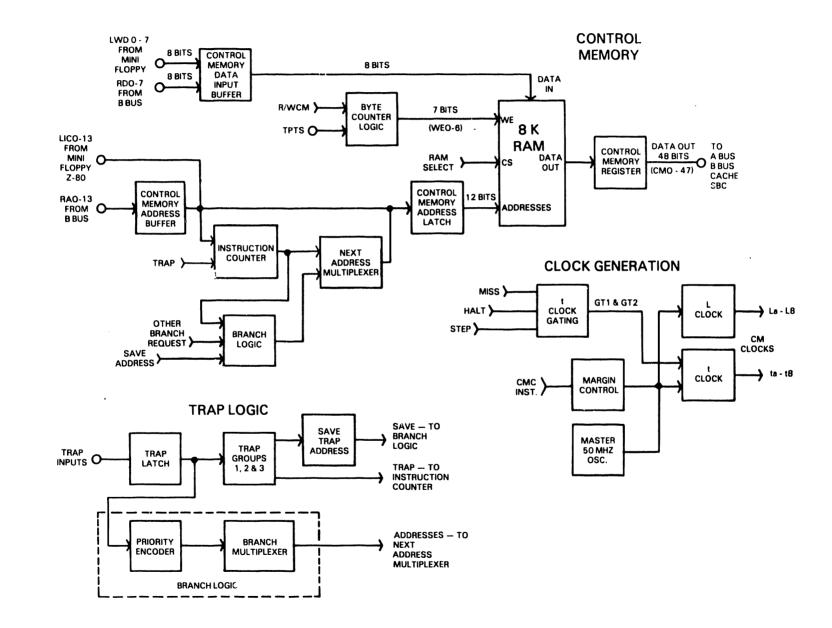

| 2.2   | Control Memory 2-1         |

| 2.2.1 | Writing Control Memory 2-5 |

| 2.2.2 | Reading Control Memory 2-5 |

| 2.2.3 | Traps                      |

| 2.2.4 | Branching                  |

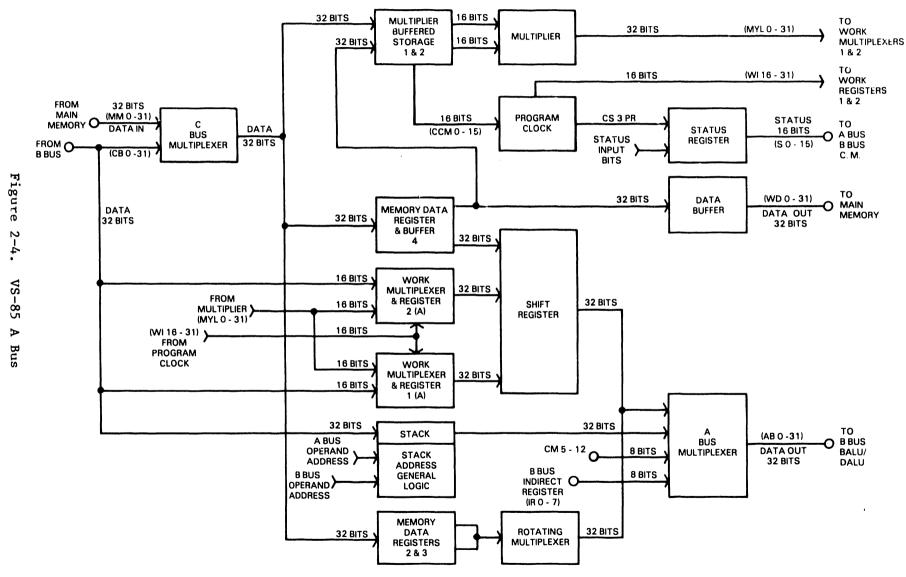

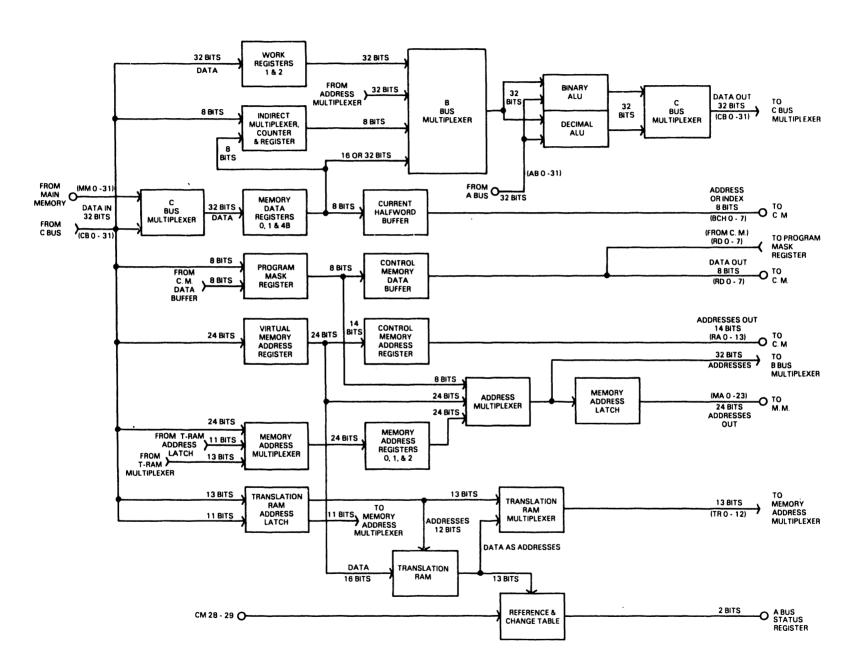

| 2.3         Central Processor         2-7           2.3.1         A Bus         2-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2.2.5      | Clock Generation and Control                            | 2-7  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------------------------------------------|------|

| 2.3.1.1       C Bus Main Memory Multiplexer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2.3        |                                                         |      |

| 2.3.1.1       C Bus Main Memory Multiplexer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2.3.1      | A Bus                                                   | 2-7  |

| Rotating Multiplexer         2-7           2.3.1.3         Memory Data Register 4, Data Buffer, Work<br>Multiplexers/Registers, and Shift Register         2-9           2.3.1.4         Multiplexers/Registers, and Shift Register         2-10           2.3.1.6         A Bus Multiplier         2-10           2.3.1.6         CP Stack         2-10           2.3.1.6         CP Stack         2-10           2.3.1.7         CP Stack         2-11           2.3.1.8         Program Clock         2-11           2.3.2.1         C Bus Main Memory Multiplexer         2-12           2.3.2.2         Memory Drta Registers 0, 1, and 4B, and         2-12           2.3.2.3         Work Registers, Indirect Counter,         2-14           2.3.2.4         B Bus Multiplexer         2-14           2.3.2.5         Binary Arithmetic Logic Unit, Decimal Arithmetic         2-14           2.3.2.6         Program Mask Register and Virtual Memory         2-14           2.3.2.7         Control Memory Address Buffer and         2-15           2.3.2.8         Memory Operation Overview, Memory Address Multiplexer,         2-16           2.3.2.8.1         General Memory Operations Overview         2-16           2.3.2.6         Translation Overview         2-16                                                                                                | 2.3.1.1    |                                                         |      |

| 2.3.1.3       Memory Data Register 4, Data Buffer, Work<br>Multiplexers/Registers, and Shift Register       2-9         2.3.1.4       Multiplier       2-10         2.3.1.5       A Bus Multiplier       2-10         2.3.1.6       CP Stack       2-11         2.3.1.7       CP Status Register       2-11         2.3.1.6       CP Status Register       2-11         2.3.1.7       CP Status Register       2-11         2.3.1.8       Program Clock       2-11         2.3.2.1       C Bus Main Memory Multiplexer       2-12         2.3.2.1       C Bus Main Memory Multiplexer       2-12         2.3.2.2       Memory Drta Registers 0, 1, and 4B, and<br>Current Halfword Buffer       2-12         2.3.2.3       Work Registers, Indirect Counter,<br>and Indirect Register       2-14         2.3.2.4       B Bus Multiplexer       2-14         2.3.2.5       Binary Arithmetic Logic Unit, Decimal Arithmetic<br>Logic Unit, and C Bus Multiplexer       2-14         2.3.2.6       Program Mask Register and Virtual Memory<br>Address Register 0, 1, and 2       2-15         2.3.2.7       Control Memory Address Buffer and<br>Control Memory Address Buffer and<br>Control Memory Operations Overview       2-16         2.3.2.8.1       General Ammory Operations Overview       2-16         3.2.8.2                                                                  | 2.3.1.2    |                                                         |      |

| Multiplexers/Registers, and Shift Register         2-9           2.3.1.4         Multiplier         2-10           2.3.1.5         A Bus Multiplier         2-10           2.3.1.6         CP Stack         2-10           2.3.1.7         CP Stack         2-10           2.3.1.8         Program Clock         2-11           2.3.2.1         C Bus Main Memory Multiplexer         2-12           2.3.2.1         C Bus Main Memory Multiplexer         2-12           2.3.2.3         Work Registers 0, 1, and 4B, and         2-12           2.3.2.3         Work Registers, Indirect Counter,         and Indirect Register         2-14           2.3.2.4         B us Multiplexer         2-14         2.3.2.5           2.3.2.5         Binary Arithmetic Logic Unit, Decimal Arithmetic         2-14           2.3.2.6         Program Mask Register and Virtual Memory         2-15           2.3.2.6         Program Mask Register and Virtual Memory         2-15           2.3.2.7         Control Memory Address Buffer and         2-15           2.3.2.8         Memory Operation Overviews         2-16           2.3.2.8.1         General Memory Operations Overview         2-16           2.3.2.8.2         Read and Write Overview         2-16                                                                                                                    |            | Rotating Multiplexer                                    | 2-7  |

| Multiplexers/Registers, and Shift Register         2-9           2.3.1.4         Multiplier         2-10           2.3.1.5         A Bus Multiplier         2-10           2.3.1.6         CP Stack         2-10           2.3.1.7         CP °tatus Register         2-11           2.3.1.8         Program Clock         2-11           2.3.2.1         C Bus Main Memory Multiplexer         2-12           2.3.2.1         C Bus Main Memory Multiplexer         2-12           2.3.2.2         Memory Data Registers 0, 1, and 4B, and         Current Halfword Buffer           2.3.2.3         Work Registers, Indirect Counter,         2-12           3.2.4         B bus Multiplexer         2-14           2.3.2.5         Binary Arithmetic Logic Unit, Decimal Arithmetic         2-14           2.3.2.6         Program Mask Register and Virtual Memory         2-15           2.3.2.7         Control Memory Address Buffer and         2-15           2.3.2.8         Memory Operation Overview, Memory Address Multiplexer,         2-16           3.2.8.1         General Memory Operations Overview         2-16           2.3.2.8.1         General Memory Operations Overview         2-16           2.3.2.8.3         Translation Overview         2-16 <td< td=""><td>2.3.1.3</td><td>Memory Data Register 4, Data Buffer, Work</td><td></td></td<>               | 2.3.1.3    | Memory Data Register 4, Data Buffer, Work               |      |

| 2.3.1.5       A Bus Multiplier       2-10         2.3.1.6       CP Stack       2-10         2.3.1.7       CP Status Register       2-11         2.3.1.8       Program Clock       2-11         2.3.2       B Bus       2-12         2.3.2       Current Rain Memory Multiplexer       2-12         2.3.2.1       C Bus Main Memory Multiplexer       2-12         2.3.2.2       Memory Drta Registers 0, 1, and 4B, and       2-12         2.3.2.3       Work Registers, Indirect Counter,       and Indirect Register       2-14         2.3.2.4       B Bus Multiplexer       2-14         2.3.2.5       Binary Arithmetic Logic Unit, Decimal Arithmetic       2-14         2.3.2.6       Program Mask Register and Virtual Memory       Address Register       2-15         2.3.2.7       Control Memory Address Buffer and       2-15       2.3.2.7         Control Memory Address Registers 0, 1, and 2       2-16       2.3.2.8.1       General Memory Operation Overview, Memory Address Multiplexer,       and Memory Address Registers 0, 1, and 2       2-16         2.3.2.8.1       General Memory Operations Overview       2-16       2.3.2.8.3       Translation Overview       2-16         2.3.2.8.3       Translation Overview       2-16       2.3.2.8.5       Memo                                                                                                    |            |                                                         | 2-9  |

| 2.3.1.6       CP Stack       2-10         2.3.1.7       CP °tatus Register       2-11         2.3.1.8       Program Clock       2-11         2.3.2       B Bus       2-12         2.3.2.1       C Bus Main Memory Multiplexer       2-12         2.3.2.2       Memory Drta Registers 0, 1, and 4B, and       2-12         2.3.2.3       Work Registers, Indirect Counter,       2-14         2.3.2.4       B Bus Multiplexer       2-14         2.3.2.5       Binary Arithmetic Logic Unit, Decimal Arithmetic       2-14         2.3.2.6       Program Mask Register and Virtual Memory       2-14         2.3.2.7       Control Memory Address Buffer and       2-15         2.3.2.8       Memory Operation Overviews, Memory Address Multiplexer,       2-16         2.3.2.8.1       General Memory Operations Overview       2-16         2.3.2.8.2       Read and Write Overview       2-16         2.3.2.8.4       Ripple Overview       2-16         2.3.2.8.5       Memory Address Registers 0, 1, and 2       2-17         2.3.2.8       Memory Address Registers 0, 1, and 2       2-16         2.3.2.8.5       Memory Address Registers 0, 1, and 2       2-16         2.3.2.8.6       Ripple Overview       2-16                                                                                                                                                              | 2.3.1.4    | Multiplier                                              | 2-10 |

| 2.3.1.7       CP °tatus Register       2-11         2.3.1.8       Program Clock       2-11         2.3.2       B Bus       2-12         2.3.2.1       C Bus Main Memory Multiplexer       2-12         2.3.2.2       Memory Data Registers 0, 1, and 4B, and       2-12         2.3.2.3       Work Registers, Indirect Counter,       2-14         2.3.2.4       B Bus Multiplexer       2-14         2.3.2.5       Binary Arithmetic Logic Unit, Decimal Arithmetic       2-14         2.3.2.6       Program Mask Register and Virtual Memory       2-14         2.3.2.6       Program Mask Register and Virtual Memory       2-15         2.3.2.7       Control Memory Address Buffer and       2-15         2.3.2.8       Memory Operation Overviews, Memory Address Multiplexer,       and Memory Operation Overview         2.3.2.8.1       General Memory Operations Overview       2-16         2.3.2.8.2       Read and Write Overview       2-16         2.3.2.8.3       Translation Overview       2-16         2.3.2.8.4       Riple Overview       2-16         2.3.2.8.5       Memory Address Registers 0, 1, and 2       2-17         2.3.2.8.1       General Memory Address Latch, Translation RAM,       2-16         2.3.2.8.5       Memory A                                                                                                                            | 2.3.1.5    | A Bus Multiplier                                        | 2-10 |

| 2.3.1.8       Program Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2.3.1.6    | CP Stack                                                | 2-10 |

| 2.3.2       B Bus       2-12         2.3.2.1       C Bus Main Memory Multiplexer       2-12         2.3.2.2       Memory Drta Registers 0, 1, and 4B, and       2-12         2.3.2.3       Work Registers, Indirect Counter,       2-12         and Indirect Register       2-14         2.3.2.4       B Bus Multiplexer       2-14         2.3.2.5       Binary Arithmetic Logic Unit, Decimal Arithmetic       2-14         2.3.2.5       Binary Arithmetic Logic Unit, Decimal Arithmetic       2-14         2.3.2.6       Program Mask Register and Virtual Memory       2-14         2.3.2.7       Control Memory Address Buffer and       2-15         2.3.2.8       Memory Operation Overviews, Memory Address Multiplexer,       2-16         2.3.2.8.1       General Memory Operations Overview       2-16         2.3.2.8.2       Read and Write Overview       2-16         2.3.2.8.3       Translation Overview       2-16         2.3.2.8.4       Ripple Overview       2-16         2.3.2.9       Address Registers 0, 1, and 2       2-17         2.3.2.9       Address Registers 0, 1, and 2       2-17         2.3.2.9       Address Registers 0, 1, and 2       2-16         2.3.2.8.5       Memory Address Latch, Translation RAM,       2-                                                                                                                            | 2.3.1.7    | CP <sup>c</sup> tatus Register                          | 2-11 |

| 2.3.2.1       C Bus Main Memory Multiplexer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2.3.1.8    | Program Clock                                           | 2-11 |

| 2.3.2.2       Memory Drta Registers 0, 1, and 4B, and<br>Current Halfword Buffer       2-12         2.3.2.3       Work Registers, Indirect Counter,<br>and Indirect Register       2-14         2.3.2.4       B Bus Multiplexer       2-14         2.3.2.5       Binary Arithmetic Logic Unit, Decimal Arithmetic<br>Logic Unit, and C Bus Multiplexer       2-14         2.3.2.6       Program Mask Register and Virtual Memory<br>Address Register       2-15         2.3.2.7       Control Memory Address Buffer and<br>Control Memory Data Buffer       2-15         2.3.2.8       Memory Operation Overviews, Memory Address Multiplexer,<br>and Memory Address Registers 0, 1, and 2       2-16         2.3.2.8.1       General Memory Operations Overview       2-16         2.3.2.8.2       Read and Write Overview       2-16         2.3.2.8.3       Translation Overview       2-16         2.3.2.8.4       Ripple Overview       2-16         2.3.2.8.5       Memory Address Registers 0, 1, and 2       2-17         2.3.2.9       Address Register and Memory Address Latch       2-18         2.3.2.10       Translation RAM Address Latch, Translation RAM,<br>Reference/Change Table, and Translation RAM,<br>Reference/Change Table, and Translation RAM Multiplexer       2-18         2.4       Main Memory       2-20         2.4.1       Control Signals       2-20 | 2.3.2      | B Bus                                                   | 2-12 |

| Current Halfword Buffer2-122.3.2.3Work Registers, Indirect Counter,<br>and Indirect Register2-142.3.2.4B Bus Multiplexer2-142.3.2.5Binary Arithmetic Logic Unit, Decimal Arithmetic<br>Logic Unit, and C Bus Multiplexer2-142.3.2.6Program Mask Register and Virtual Memory<br>Address Register2-152.3.2.7Control Memory Address Buffer and<br>Control Memory Data Buffer2-162.3.2.8Memory Operation Overviews, Memory Address Multiplexer,<br>and Memory Address Registers 0, 1, and 22-162.3.2.8.1General Memory Operations Overview2-162.3.2.8.2Read and Write Overview2-162.3.2.8.3Translation Overview2-162.3.2.8.4Ripple Overview2-162.3.2.8.5Memory Address Registers 0, 1, and 22-172.3.2.9Address Registers 0, 1, and 22-172.3.2.9Address Registers 0, 1, and 22-172.3.2.9Address Multiplexer and Memory Address Latch2-182.3.2.10Translation RAM Address Latch, Translation RAM,<br>Reference/Change Table, and Translation RAM Multiplexer2-182.4Main Memory2-202.4.1Control Signals2-202.4.2Memory Write and Read2-202.4.4Refresh2-242.5Memory Controller I (MCI)2-242.5.1Main Memory Addresses From BA and CP2-24                                                                                                                                                                                                                                                            | 2.3.2.1    | C Bus Main Memory Multiplexer                           | 2-12 |

| 2.3.2.3Work Registers, Indirect Counter,<br>and Indirect Register2-142.3.2.4B Bus Multiplexer2-142.3.2.5Binary Arithmetic Logic Unit, Decimal Arithmetic<br>Logic Unit, and C Bus Multiplexer2-142.3.2.6Program Mask Register and Virtual Memory<br>Address Register2-152.3.2.7Control Memory Address Buffer and<br>Control Memory Data Buffer2-152.3.2.8Memory Operation Overviews, Memory Address Multiplexer,<br>and Memory Operations Overview2-162.3.2.8.1General Memory Operations Overview2-162.3.2.8.2Read and Write Overview2-162.3.2.8.3Translation Overview2-162.3.2.8.4Ripple Overview2-162.3.2.8.5Memory Address Registers 0, 1, and 22-172.3.2.8.4Ripple Overview2-162.3.2.8.5Memory Address Registers 0, 1, and 22-172.3.2.8.6Memory Address Registers 0, 1, and 22-172.3.2.8.5Memory Address Registers 0, 1, and 22-172.3.2.8.6Memory Address Registers 0, 1, and 22-172.3.2.8.7Memory Address Registers 0, 1, and 22-172.3.2.8.8Memory Address Latch, Translation RAM,<br>Reference/Change Table, and Translation RAM,<br>Reference/Change Table, and Translation RAM<br>Address2-182.4.1Control Signals2-202.4.2Memory Write and Read2-202.4.3Addressing2-232.4.4Refresh2-242.5.1Main Memory Addresses From BA and CP2-24 <td>2.3.2.2</td> <td>Memory Data Registers 0, 1, and 4B, and</td> <td></td>                                                                   | 2.3.2.2    | Memory Data Registers 0, 1, and 4B, and                 |      |

| 2.3.2.3Work Registers, Indirect Counter,<br>and Indirect Register2-142.3.2.4B Bus Multiplexer2-142.3.2.5Binary Arithmetic Logic Unit, Decimal Arithmetic<br>Logic Unit, and C Bus Multiplexer2-142.3.2.6Program Mask Register and Virtual Memory<br>Address Register2-152.3.2.7Control Memory Address Buffer and<br>Control Memory Data Buffer2-152.3.2.8Memory Operation Overviews, Memory Address Multiplexer,<br>and Memory Operations Overview2-162.3.2.8.1General Memory Operations Overview2-162.3.2.8.2Read and Write Overview2-162.3.2.8.3Translation Overview2-162.3.2.8.4Ripple Overview2-162.3.2.8.5Memory Address Registers 0, 1, and 22-172.3.2.8.4Ripple Overview2-162.3.2.8.5Memory Address Registers 0, 1, and 22-172.3.2.8.6Memory Address Registers 0, 1, and 22-172.3.2.8.5Memory Address Registers 0, 1, and 22-172.3.2.8.6Memory Address Registers 0, 1, and 22-172.3.2.8.7Memory Address Registers 0, 1, and 22-172.3.2.8.8Memory Address Latch, Translation RAM,<br>Reference/Change Table, and Translation RAM,<br>                                                                                                                                                                                                                                                                                                                                               |            | Current Halfword Buffer                                 | 2-12 |

| 2.3.2.4B Bus Multiplexer2-142.3.2.5Binary Arithmetic Logic Unit, Decimal Arithmetic<br>Logic Unit, and C Bus Multiplexer2-142.3.2.6Program Mask Register and Virtual Memory<br>Address Register2-152.3.2.7Control Memory Address Buffer and<br>Control Memory Data Buffer2-152.3.2.8Memory Operation Overviews, Memory Address Multiplexer,<br>and Memory Address Registers 0, 1, and 22-162.3.2.8.1General Memory Operations Overview2-162.3.2.8.2Read and Write Overview2-162.3.2.8.3Translation Overview2-162.3.2.8.4Ripple Overview2-162.3.2.8.5Memory Address Registers 0, 1, and 22-172.3.2.9Address Registers 0, 1, and 22-172.3.2.9Address Registers 0, 1, and 22-182.3.2.10Translation RAM Address Latch, Translation RAM,<br>Reference/Change Table, and Translation RAM,<br>Reference/Change Table, and Translation RAM,<br>Reference/Change Table, and Translation RAM<br>Address 2-202-202.4.1Control Signals2-202.4.2Memory Write and Read2-202.4.3Addressing2-202.4.4Refresh2-244.5.1Memory Controller I (MCI)2-242.5.1Main Memory Addresse From BA and CP2-24                                                                                                                                                                                                                                                                                                             | 2.3.2.3    | Work Registers, Indirect Counter,                       |      |

| 2.3.2.4B Bus Multiplexer2-142.3.2.5Binary Arithmetic Logic Unit, Decimal Arithmetic<br>Logic Unit, and C Bus Multiplexer2-142.3.2.6Program Mask Register and Virtual Memory<br>Address Register2-152.3.2.7Control Memory Address Buffer and<br>Control Memory Data Buffer2-152.3.2.8Memory Operation Overviews, Memory Address Multiplexer,<br>and Memory Address Registers 0, 1, and 22-162.3.2.8.1General Memory Operations Overview2-162.3.2.8.2Read and Write Overview2-162.3.2.8.3Translation Overview2-162.3.2.8.4Ripple Overview2-162.3.2.8.5Memory Address Registers 0, 1, and 22-172.3.2.9Address Registers 0, 1, and 22-172.3.2.9Address Registers 0, 1, and 22-182.3.2.10Translation RAM Address Latch, Translation RAM,<br>Reference/Change Table, and Translation RAM,<br>Reference/Change Table, and Translation RAM,<br>Reference/Change Table, and Translation RAM<br>Address 2-202-202.4.1Control Signals2-202.4.2Memory Write and Read2-202.4.3Addressing2-202.4.4Refresh2-244.5.1Memory Controller I (MCI)2-242.5.1Main Memory Addresse From BA and CP2-24                                                                                                                                                                                                                                                                                                             |            | and Indirect Register                                   | 2-14 |

| Logic Unit, and C Bus Multiplexer2-142.3.2.6Program Mask Register and Virtual Memory<br>Address Register2-152.3.2.7Control Memory Address Buffer and<br>Control Memory Data Buffer2-152.3.2.8Memory Operation Overviews, Memory Address Multiplexer,<br>and Memory Address Registers 0, 1, and 22-162.3.2.8.1General Memory Operations Overview2-162.3.2.8.2Read and Write Overview2-162.3.2.8.3Translation Overview2-162.3.2.8.4Ripple Overview2-162.3.2.8.5Memory Address Registers 0, 1, and 22-172.3.2.8.4Ripple Overview2-162.3.2.8.5Memory Address Registers 0, 1, and 22-172.3.2.9Address Registers 0, 1, and 22-172.3.2.9Address Multiplexer and Memory Address Latch2-182.3.2.10Translation RAM Address Latch, Translation RAM,<br>Reference/Change Table, and Translation RAM Multiplexer2-182.4.1Control Signals2-202.4.2Memory Write and Read2-202.4.3Addressing2-202.4.4Refresh2-232.4.4Refresh2-242.5.1Main Memory Addresses From BA and CP2-24                                                                                                                                                                                                                                                                                                                                                                                                                             | 2.3.2.4    |                                                         |      |

| 2.3.2.6Program Mask Register and Virtual Memory<br>Address Register2-152.3.2.7Control Memory Address Buffer and<br>Control Memory Data Buffer2-152.3.2.8Memory Operation Overviews, Memory Address Multiplexer,<br>and Memory Address Registers 0, 1, and 22-162.3.2.8.1General Memory Operations Overview2-162.3.2.8.2Read and Write Overview2-162.3.2.8.3Translation Overview2-162.3.2.8.4Ripple Overview2-162.3.2.8.5Memory Address Registers 0, 1, and 22-172.3.2.8Memory Address Registers 0, 1, and 22-172.3.2.8Memory Address Registers 0, 1, and 22-172.3.2.8.5Memory Address Registers 0, 1, and 22-172.3.2.8.5Memory Address Registers 0, 1, and 22-182.3.2.10Translation RAM Address Latch, Translation RAM,<br>Reference/Change Table, and Translation RAM,<br>Reference/Change Table, and Translation RAM<br>Multiplexer2-182.4Main Memory2-202.4.1Control Signals2-202.4.2Memory Write and Read2-202.4.3Addressing2-232.4.4Refresh2-242.5Memory Controller I (MCI)2-242.5.1Main Memory Addresses From BA and CP2-24                                                                                                                                                                                                                                                                                                                                                         | 2.3.2.5    | Binary Arithmetic Logic Unit, Decimal Arithmetic        |      |

| Address Register2-152.3.2.7Control Memory Address Buffer and<br>Control Memory Data Buffer2-152.3.2.8Memory Operation Overviews, Memory Address Multiplexer,<br>and Memory Address Registers 0, 1, and 22-162.3.2.8.1General Memory Operations Overview2-162.3.2.8.2Read and Write Overview2-162.3.2.8.3Translation Overview2-162.3.2.8.4Ripple Overview2-162.3.2.8.5Memory Address Registers 0, 1, and 22-172.3.2.8.5Memory Address Registers 0, 1, and 22-172.3.2.9Address Multiplexer and Memory Address Latch2-182.3.2.10Translation RAM Address Latch, Translation RAM,<br>Reference/Change Table, and Translation RAM Multiplexer2-182.4Main Memory2-202.4.1Control Signals2-202.4.2Memory Write and Read2-202.4.3Addressing2-202.4.4Refresh2-212.5.1Main Memory Addresses From BA and CP2-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            | Logic Unit, and C Bus Multiplexer                       | 2-14 |

| 2.3.2.7Control Memory Address Buffer and<br>Control Memory Data Buffer2-152.3.2.8Memory Operation Overviews, Memory Address Multiplexer,<br>and Memory Address Registers 0, 1, and 22-162.3.2.8.1General Memory Operations Overview2-162.3.2.8.2Read and Write Overview2-162.3.2.8.3Translation Overview2-162.3.2.8.4Ripple Overview2-162.3.2.8.5Memory Address Registers 0, 1, and 22-162.3.2.8.5Memory Address Registers 0, 1, and 22-172.3.2.9Address Multiplexer and Memory Address Latch2-182.3.2.10Translation RAM Address Latch, Translation RAM,<br>Reference/Change Table, and Translation RAM Multiplexer2-182.4Main Memory2-202.4.1Control Signals2-202.4.2Memory Write and Read2-202.4.4Refresh2-212.4.4Refresh2-242.5Memory Controller I (MCI)2-242.5.1Main Memory Addresses From BA and CP2-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2.3.2.6    | Program Mask Register and Virtual Memory                |      |

| 2.3.2.7Control Memory Address Buffer and<br>Control Memory Data Buffer2-152.3.2.8Memory Operation Overviews, Memory Address Multiplexer,<br>and Memory Address Registers 0, 1, and 22-162.3.2.8.1General Memory Operations Overview2-162.3.2.8.2Read and Write Overview2-162.3.2.8.3Translation Overview2-162.3.2.8.4Ripple Overview2-162.3.2.8.5Memory Address Registers 0, 1, and 22-162.3.2.8.5Memory Address Registers 0, 1, and 22-172.3.2.9Address Multiplexer and Memory Address Latch2-182.3.2.10Translation RAM Address Latch, Translation RAM,<br>Reference/Change Table, and Translation RAM Multiplexer2-182.4Main Memory2-202.4.1Control Signals2-202.4.2Memory Write and Read2-202.4.4Refresh2-212.4.4Refresh2-242.5Memory Controller I (MCI)2-242.5.1Main Memory Addresses From BA and CP2-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            | Address Register                                        | 2-15 |

| 2.3.2.8Memory Operation Overviews, Memory Address Multiplexer,<br>and Memory Address Registers 0, 1, and 22-162.3.2.8.1General Memory Operations Overview2-162.3.2.8.2Read and Write Overview2-162.3.2.8.3Translation Overview2-162.3.2.8.4Ripple Overview2-162.3.2.8.5Memory Address Registers 0, 1, and 22-172.3.2.9Address Multiplexer and Memory Address Latch2-182.3.2.10Translation RAM Address Latch, Translation RAM,<br>Reference/Change Table, and Translation RAM Multiplexer2-182.4Main Memory2-202.4.1Control Signals2-202.4.2Memory Write and Read2-202.4.4Refresh2-232.4.4Refresh2-232.4.4Refresh2-244.5Memory Controller I (MCI)2-244.5.1Main Memory Addresses From BA and CP2-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2.3.2.7    | Control Memory Address Buffer and                       |      |

| and Memory Address Registers 0, 1, and 22-162.3.2.8.1General Memory Operations Overview2-162.3.2.8.2Read and Write Overview2-162.3.2.8.3Translation Overview2-162.3.2.8.4Ripple Overview2-162.3.2.8.5Memory Address Registers 0, 1, and 22-172.3.2.9Address Multiplexer and Memory Address Latch2-182.3.2.10Translation RAM Address Latch, Translation RAM,<br>Reference/Change Table, and Translation RAM Multiplexer2-182.4Main Memory2-202.4.1Control Signals2-202.4.2Memory Write and Read2-202.4.3Addressing2-232.4.4Refresh2-242.5Memory Controller I (MCI)2-242.5.1Main Memory Addresses From BA and CP2-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            | Control Memory Data Buffer                              | 2-15 |

| 2.3.2.8.1General Memory Operations Overview2-162.3.2.8.2Read and Write Overview2-162.3.2.8.3Translation Overview2-162.3.2.8.4Ripple Overview2-162.3.2.8.5Memory Address Registers 0, 1, and 22-172.3.2.9Address Multiplexer and Memory Address Latch2-182.3.2.10Translation RAM Address Latch, Translation RAM,<br>Reference/Change Table, and Translation RAM Multiplexer2-182.4Main Memory2-202.4.1Control Signals2-202.4.2Memory Write and Read2-202.4.3Addressing2-232.4.4Refresh2-242.5Memory Controller I (MCI)2-242.5.1Main Memory Addresses From BA and CP2-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2.3.2.8    | Memory Operation Overviews, Memory Address Multiplexer, |      |

| 2.3.2.8.2Read and Write Overview2-162.3.2.8.3Translation Overview2-162.3.2.8.4Ripple Overview2-162.3.2.8.5Memory Address Registers 0, 1, and 22-172.3.2.9Address Multiplexer and Memory Address Latch2-182.3.2.10Translation RAM Address Latch, Translation RAM,<br>Reference/Change Table, and Translation RAM Multiplexer2-182.3.2.10.1Translation RAM2-182.4Main Memory2-202.4.1Control Signals2-202.4.2Memory Write and Read2-202.4.3Addressing2-232.4.4Refresh2-242.5Memory Controller I (MCI)2-242.5.1Main Memory Addresses From BA and CP2-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            | and Memory Address Registers 0, 1, and 2                | 2-16 |

| 2.3.2.8.3Translation Overview2-162.3.2.8.4Ripple Overview2-162.3.2.8.5Memory Address Registers 0, 1, and 22-172.3.2.9Address Multiplexer and Memory Address Latch2-182.3.2.10Translation RAM Address Latch, Translation RAM,<br>Reference/Change Table, and Translation RAM Multiplexer2-182.3.2.10.1Translation RAM2-182.4Main Memory2-202.4.1Control Signals2-202.4.2Memory Write and Read2-232.4.4Refresh2-232.4.4Refresh2-242.5Memory Controller I (MCI)2-242.5.1Main Memory Addresses From BA and CP2-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |                                                         |      |

| 2.3.2.8.4Ripple Overview2-162.3.2.8.5Memory Address Registers 0, 1, and 22-172.3.2.9Address Multiplexer and Memory Address Latch2-182.3.2.10Translation RAM Address Latch, Translation RAM,<br>Reference/Change Table, and Translation RAM Multiplexer2-182.3.2.10.1Translation RAM2-182.4Main Memory2-202.4.1Control Signals2-202.4.2Memory Write and Read2-202.4.3Addressing2-232.4.4Refresh2-232.5Memory Controller I (MCI)2-242.5.1Main Memory Addresses From BA and CP2-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2.3.2.8.2  |                                                         |      |

| 2.3.2.8.5Memory Address Registers 0, 1, and 22-172.3.2.9Address Multiplexer and Memory Address Latch2-182.3.2.10Translation RAM Address Latch, Translation RAM,<br>Reference/Change Table, and Translation RAM Multiplexer2-182.3.2.10.1Translation RAM2-182.4Main Memory2-202.4.1Control Signals2-202.4.2Memory Write and Read2-202.4.3Addressing2-232.4.4Refresh2-242.5Memory Controller I (MCI)2-242.5.1Main Memory Addresses From BA and CP2-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2.3.2.8.3  |                                                         |      |

| 2.3.2.9Address Multiplexer and Memory Address Latch2-182.3.2.10Translation RAM Address Latch, Translation RAM,<br>Reference/Change Table, and Translation RAM Multiplexer2-182.3.2.10.1Translation RAM2-182.4Main Memory2-202.4.1Control Signals2-202.4.2Memory Write and Read2-202.4.3Addressing2-232.4.4Refresh2-242.5Memory Controller I (MCI)2-242.5.1Main Memory Addresses From BA and CP2-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.3.2.8.4  |                                                         |      |

| 2.3.2.10Translation RAM Address Latch, Translation RAM,<br>Reference/Change Table, and Translation RAM Multiplexer2-182.3.2.10.1Translation RAM2-182.4Main Memory2-202.4.1Control Signals2-202.4.2Memory Write and Read2-202.4.3Addressing2-232.4.4Refresh2-242.5Memory Controller I (MCI)2-242.5.1Main Memory Addresses From BA and CP2-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2.3.2.8.5  |                                                         |      |

| Reference/Change Table, and Translation RAM Multiplexer 2-182.3.2.10.1Translation RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |                                                         | 2-18 |

| 2.3.2.10.1       Translation RAM       2-18         2.4       Main Memory       2-20         2.4.1       Control Signals       2-20         2.4.2       Memory Write and Read       2-20         2.4.3       Addressing       2-23         2.4.4       Refresh       2-24         2.5       Memory Controller I (MCI)       2-24         2.5.1       Main Memory Addresses From BA and CP       2-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2.3.2.10   |                                                         |      |

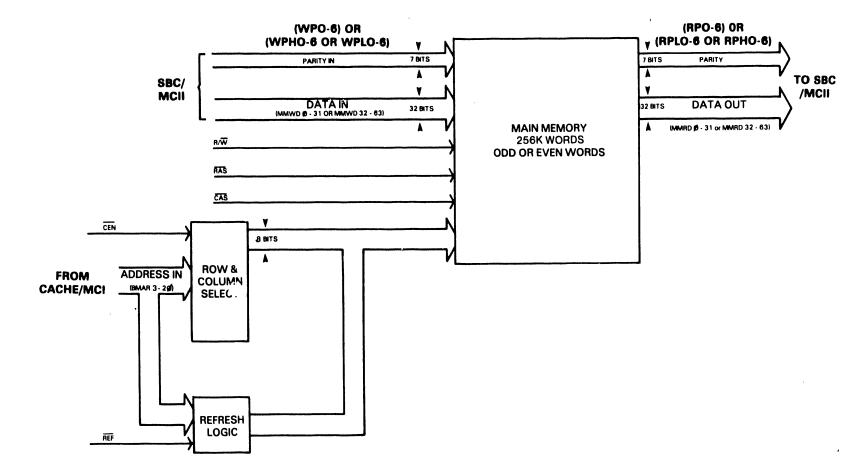

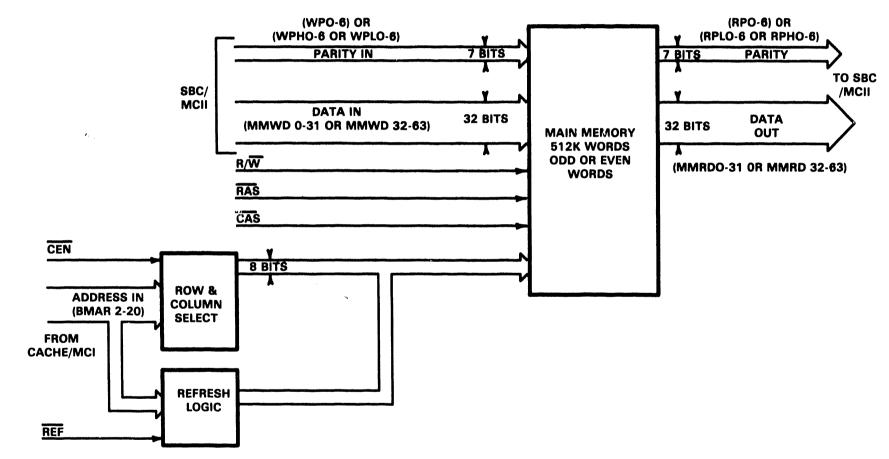

| 2.4       Main Memory       2-20         2.4.1       Control Signals       2-20         2.4.2       Memory Write and Read       2-20         2.4.3       Addressing       2-23         2.4.4       Refresh       2-24         2.5       Memory Controller I (MCI)       2-24         2.5.1       Main Memory Addresses From BA and CP       2-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |                                                         |      |

| 2.4.1       Control Signals       2-20         2.4.2       Memory Write and Read       2-20         2.4.3       Addressing       2-23         2.4.4       Refresh       2-24         2.5       Memory Controller I (MCI)       2-24         2.5.1       Main Memory Addresses From BA and CP       2-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2.3.2.10.1 | Translation RAM                                         | 2-18 |

| 2.4.2       Memory Write and Read       2-20         2.4.3       Addressing       2-23         2.4.4       Refresh       2-24         2.5       Memory Controller I (MCI)       2-24         2.5.1       Main Memory Addresses From BA and CP       2-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |                                                         |      |

| 2.4.3       Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |                                                         |      |

| 2.4.4       Refresh       2-24         2.5       Memory Controller I (MCI)       2-24         2.5.1       Main Memory Addresses From BA and CP       2-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |                                                         |      |

| 2.5Memory Controller I (MCI)2-242.5.1Main Memory Addresses From BA and CP2-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            | 0                                                       |      |

| 2.5.1 Main Memory Addresses From BA and CP 2-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |                                                         |      |

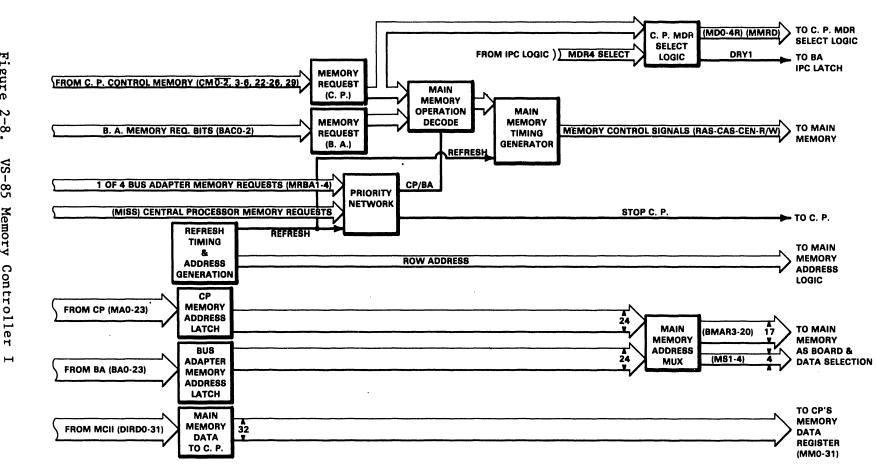

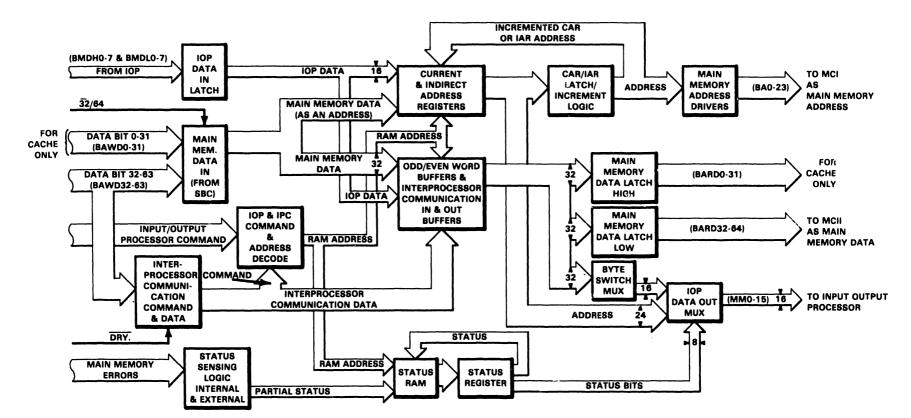

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            | Memory Controller I (MCI)                               | 2-24 |

| 2.5.2 Main Memory Data Direct To CP 2-26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |                                                         |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2.5.2      | Main Memory Data Direct To CP                           | 2-26 |

١

| 2.5.3 | Main Memory Control                         | 2-26 |

|-------|---------------------------------------------|------|

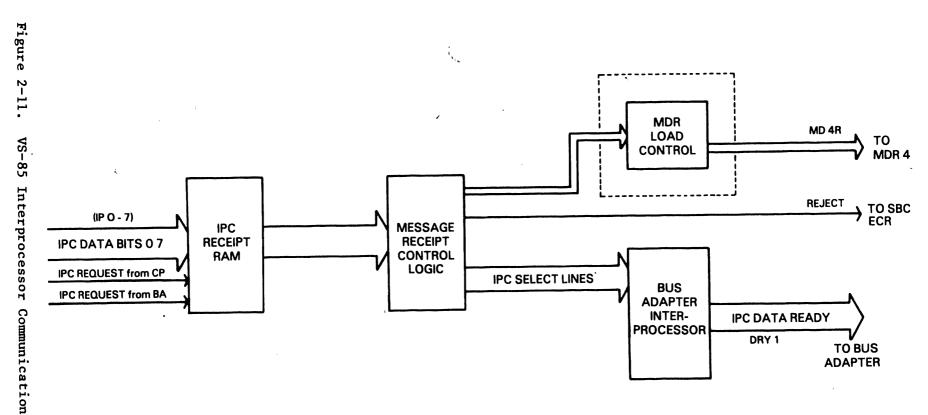

| 2.5.4 | Interprocessor Communications Control       | 2-26 |

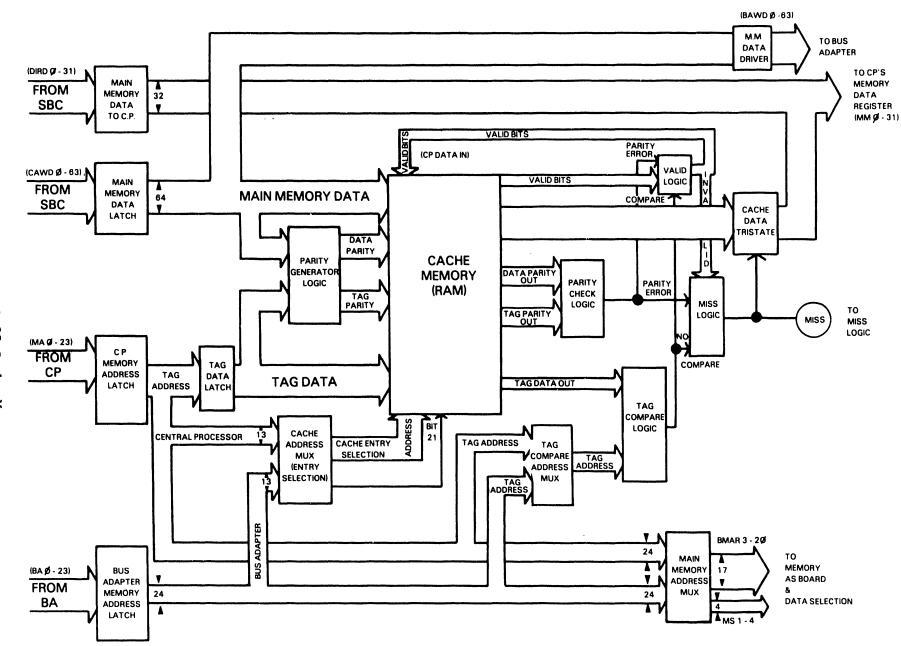

| 2.6   | Cache Memory                                |      |

| 2.6.1 | Configuration                               | 2-28 |

| 2.6.2 | Data Written To Cache                       |      |

| 2.6.3 | Data Read From Cache                        | 2-29 |

| 2.6.4 | Main Memory Addresses From BA and CP        | 2-29 |

| 2.6.5 | Tag Compare (MISS) and Parity               | 2-29 |

| 2.6.6 | Valid and Invalid Cache Locations           | 2-30 |

| 2.6.7 | Main Memory Data Direct To CP               | 2-30 |

| 2.6.8 | Main Memory Control                         | 2-30 |

| 2.6.9 | Interprocessor Communications Control       |      |

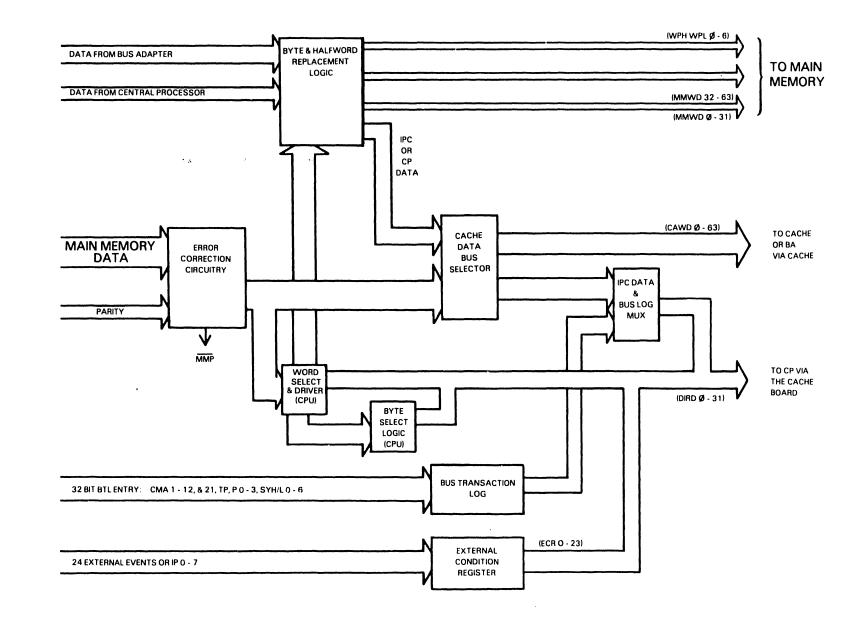

| 2.7   | Memory Controller II (MCII)                 | 2-35 |

| 2.8   | System Bus Controller                       | 2-35 |

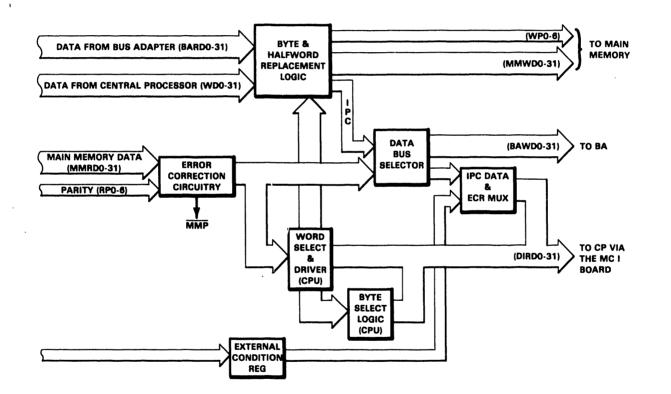

| 2.8.1 | Data Error Correction                       | 2-35 |

| 2.8.2 | Read Data Path                              | 2-37 |

| 2.8.3 | Data To Main Memory                         | 2-37 |

| 2.8.4 | Interprocessor Communications               | 2-38 |

| 2.8.5 | External Condition Register                 | 2-38 |

| 2.8.6 | Bus Transaction Log                         | 2-39 |

| 2.9   | Bus Adapter                                 | 2-39 |

| 2.9.1 | IOP Priority                                | 2-39 |

| 2.9.2 | IOP Instructions                            | 2-41 |

| 2.9.3 | Encoding Of BA Memory Commands              | 2-41 |

| 2.9.4 | Write IOP Data To Main Memory               | 2-41 |

| 2.9.5 | Addresses To Main Memory                    | 2-42 |

| 2.9.6 | Main Memory Data To IOP With Byte Switching | 2-42 |

| 2.9.7 | Interprocessor Communications               | 2-43 |

| 2.9.8 | Status Register                             | 2-43 |

# CHAPTER 3 OPERATION

| 3.1   | General                           |

|-------|-----------------------------------|

| 3.2   | Controls                          |

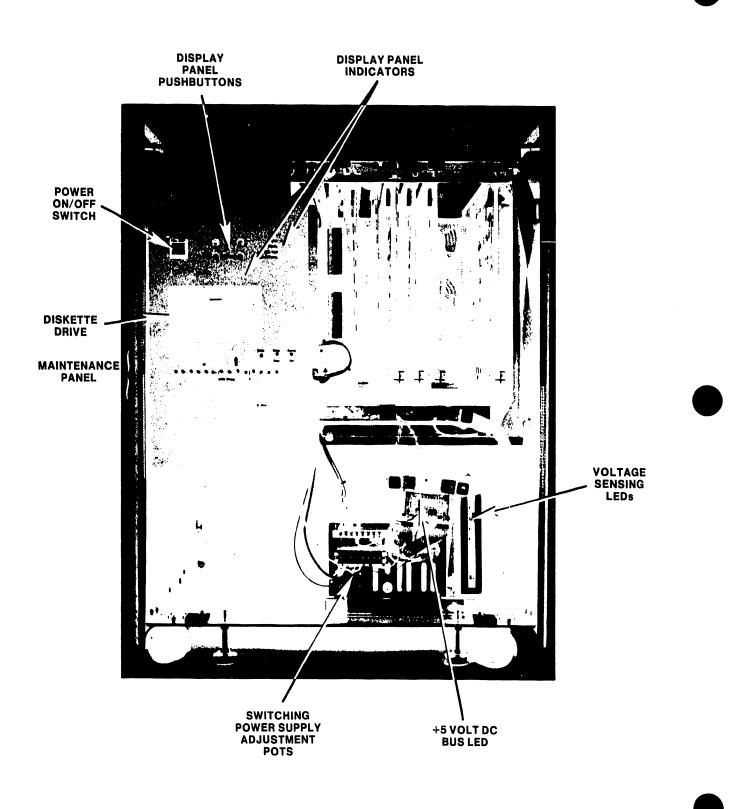

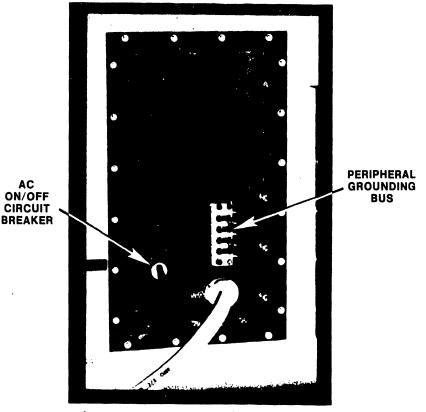

| 3.2.1 | Power Filter Assembly 3-3         |

| 3.2.2 | Display Panel Control Buttons 3-4 |

| 3.2.3 | Boot Pushbutton                   |

| 3.2.4 | Control Mode Pushbutton 3-5       |

| 3.2.5 | Initialize Pushbutton 3-5         |

| 3.2.6 | System Load Pushbutton 3-5        |

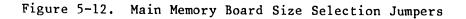

| 3.2.7 | Main Memory Size                  |

| 3.2.8 | Main Memory Size Selection 3-6    |

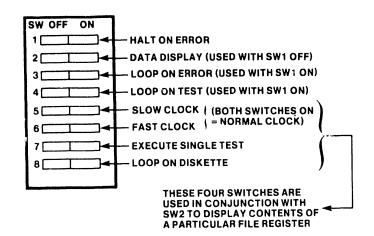

| 3.2.9 | IOP Switches 3-6                  |

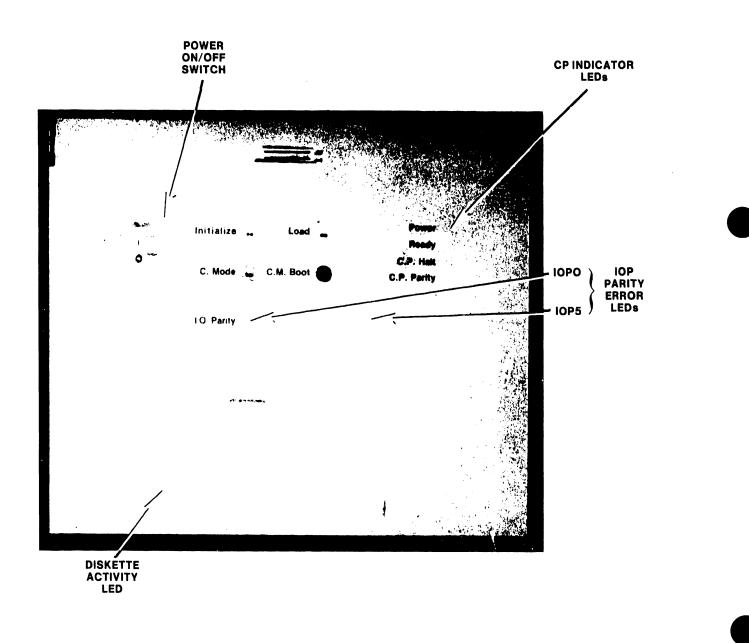

| 3.3   | Indicators                        |

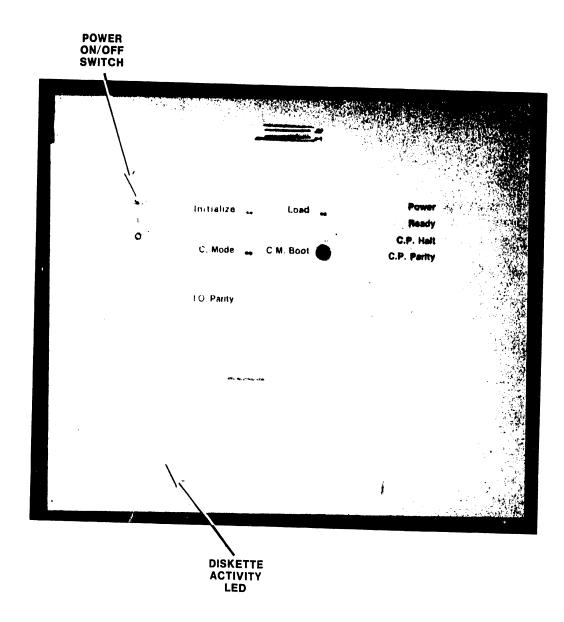

| 3.3.1 | Display Panel                      |

|-------|------------------------------------|

| 3.3.2 | Central Processor Indicators       |

| 3.3.3 | IOP Parity Error Indicators        |

| 3.3.4 | Internal Indicators 3-8            |

| 3.3.5 | ECC Indicator LEDs 3-8             |

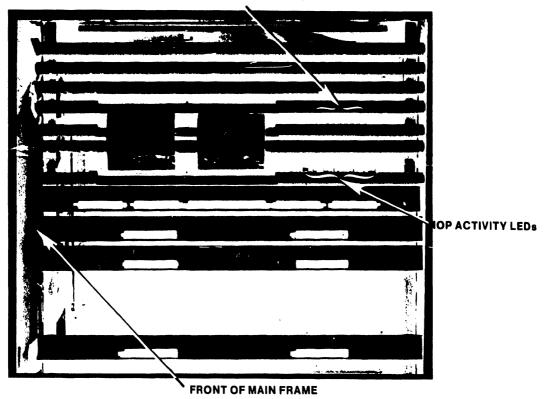

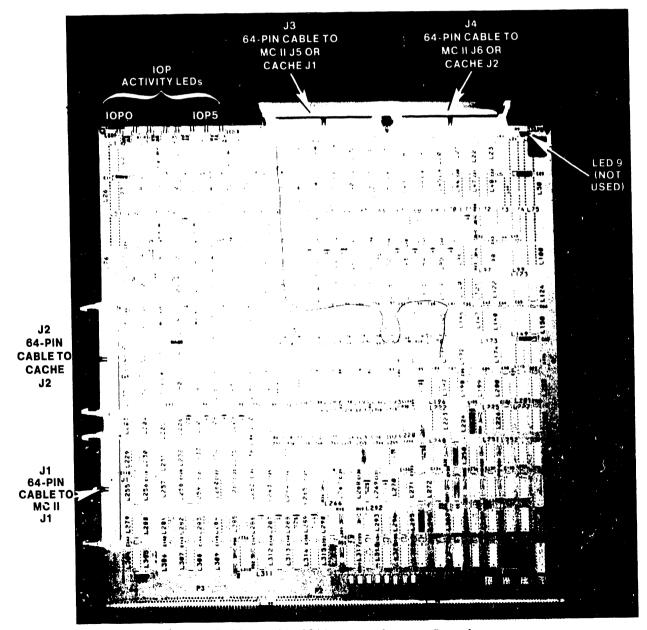

| 3.3.6 | IOP Activity LEDs 3-8              |

| 3.4   | Support Materials 3-9              |

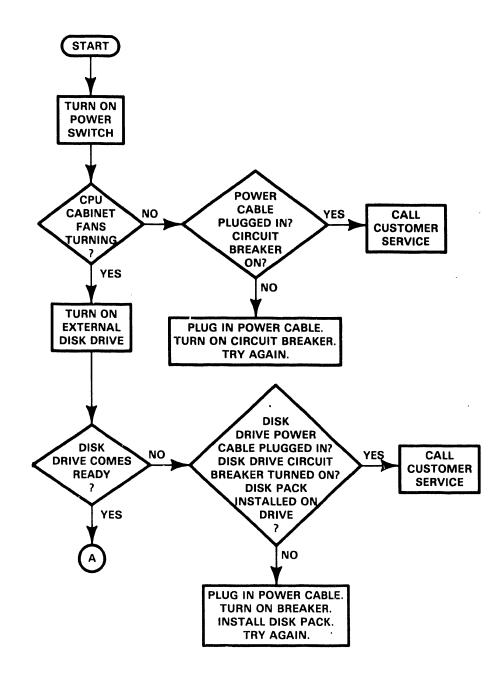

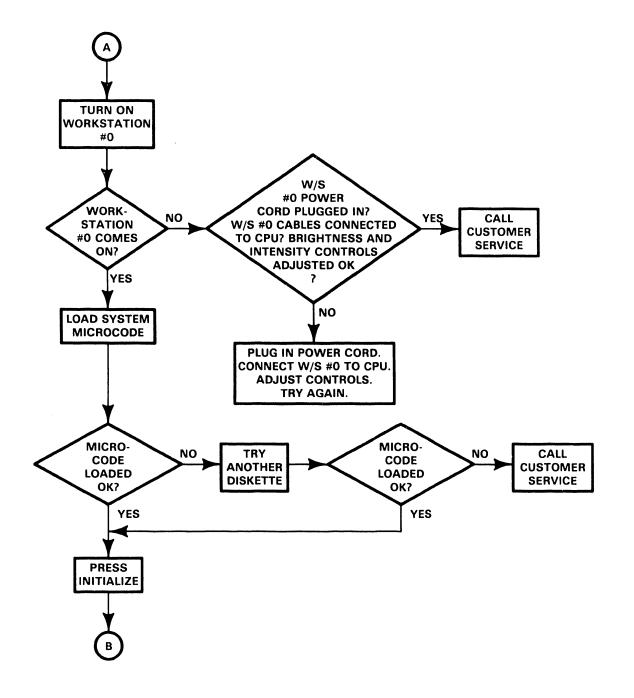

| 3.5   | Daily Turn-On Procedures 3-9       |

| 3.6   | Daily Verification Procedures 3-10 |

| 3.7   | Daily Shut-Down Procedures 3-10    |

| 3.8   | Emergency Shut-Down Procedures     |

| 3.9   | Operator Preventive Maintenance    |

# CHAPTER 4 INSTALLATION

#### Page

| 4.1    | General                              | 4-1  |

|--------|--------------------------------------|------|

| 4.2    | Installation Site Check              | 4-1  |

| 4.3    | Tools and Test Equipment             | 42   |

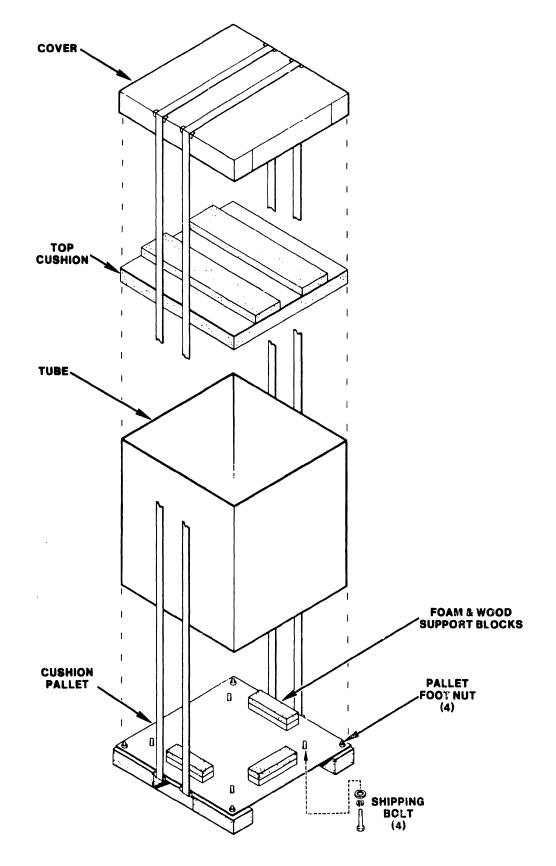

| 4.4    | Unpacking                            |      |

| 4.4.1  | Claims Information                   |      |

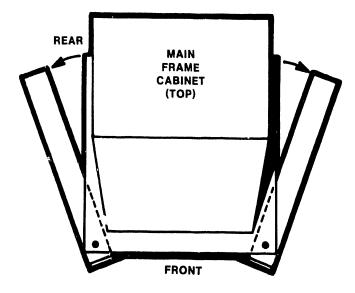

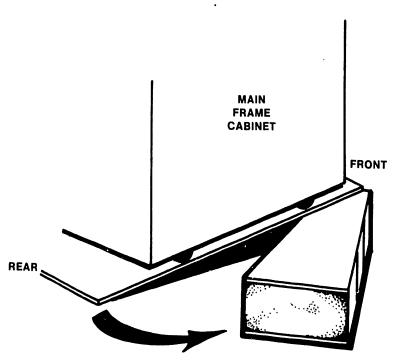

| 4.4.2  | Unpacking The Main Frame             |      |

| 4.4.3  | Unpacking The Peripherals            |      |

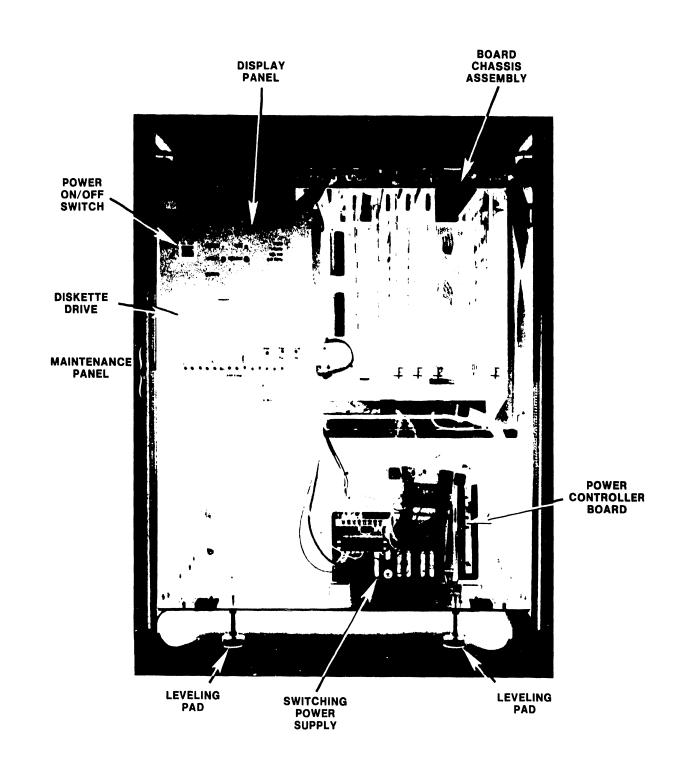

| 4.5    | Main Frame Inspection                | 4-9  |

| 4.5.1  | Peripheral Inspection                | 4-9  |

| 4.6    | Minimum Requirements                 |      |

| 4.6.1  | Hardware                             | 4-10 |

| 4.6.2  | Software                             | 4-10 |

| 4.6.3  | Diagnostics                          | 4-11 |

| 4.7    | Main Frame Power Source Check        | 4-12 |

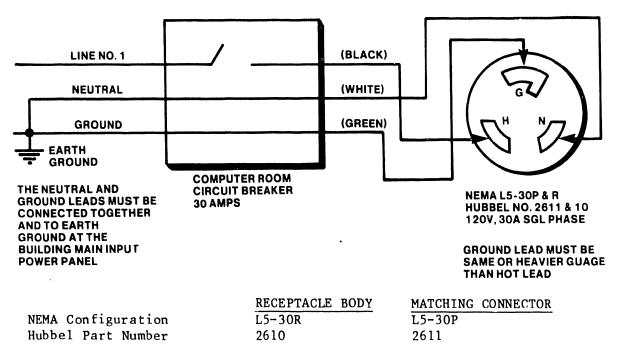

| 4.7.1  | 115VAC Domestic Power Source         | 4-12 |

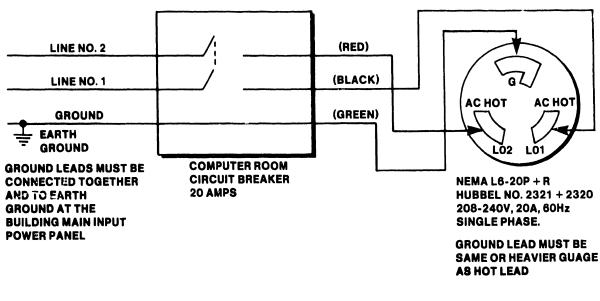

| 4.7.2  | 208-240VAC Domestic Power Source     | 4-13 |

| 4.7.3  | Initial Main Frame Power-Up          | 4-14 |

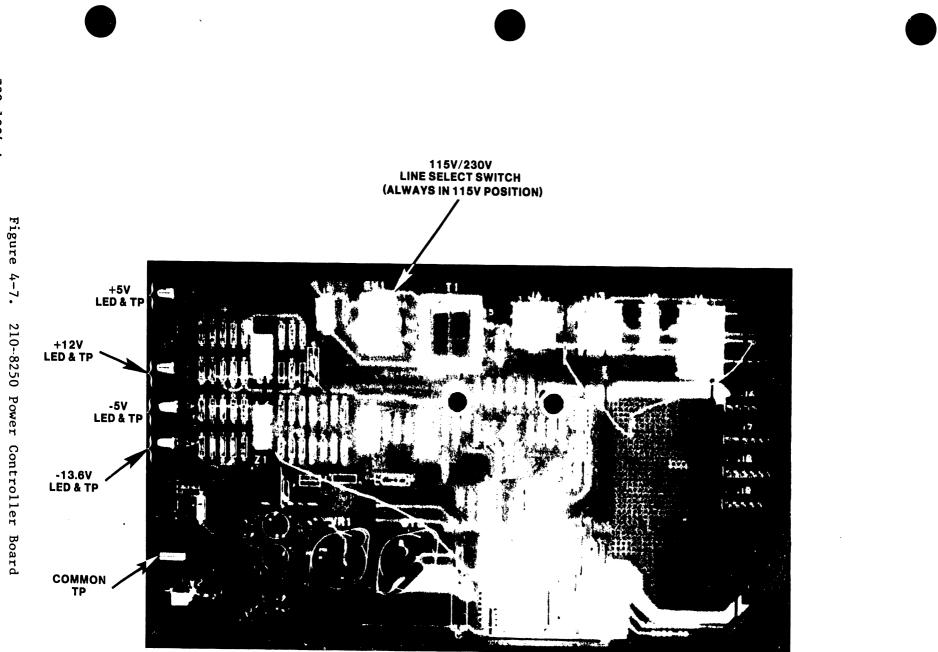

| 4.7.4  | DC Voltage Checks                    | 4-14 |

| 4.8    | Running Diagnostics                  | 4-18 |

| 4.9    | Initial Microcode Loading            | 4-18 |

| 4.10   | System Generation (SYSGEN)           | 4-20 |

| 4.10.1 | Performing A SYSGEN                  | 4-20 |

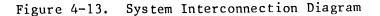

| 4.11   | System Interconnection               |      |

| 4.11.1 | Connector Plate-To-IOP Cabling       | 4-26 |

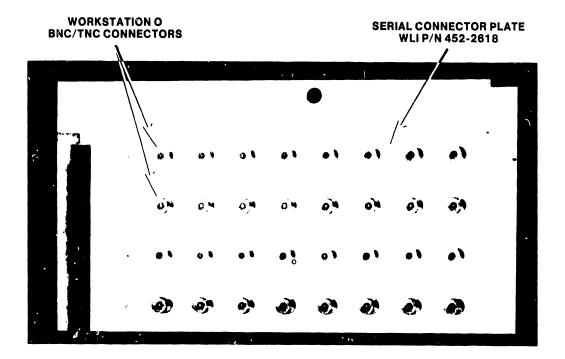

| 4.11.2 | BNC/TNC Connectors                   | 4-26 |

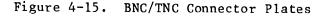

| 4.11.3 | Disk Cable Connectors                | 4-27 |

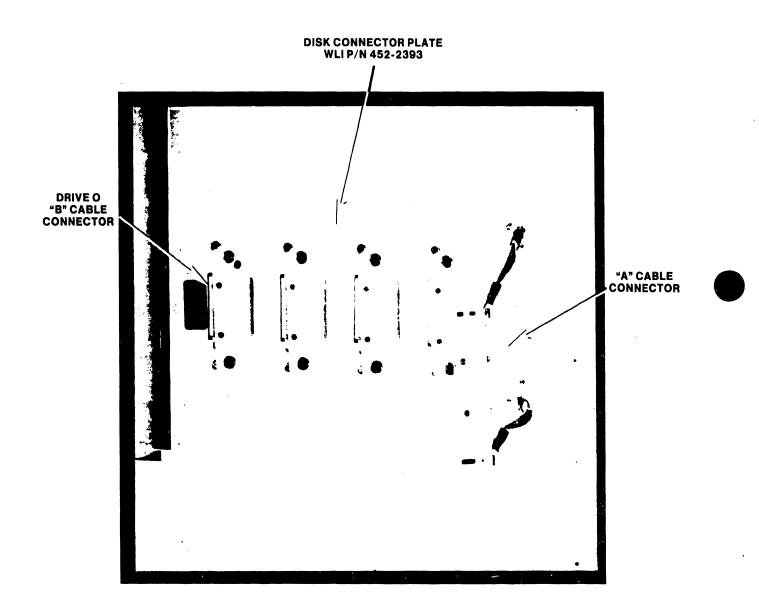

| 4.11.4 | Telecommunication Connectors         | 4-29 |

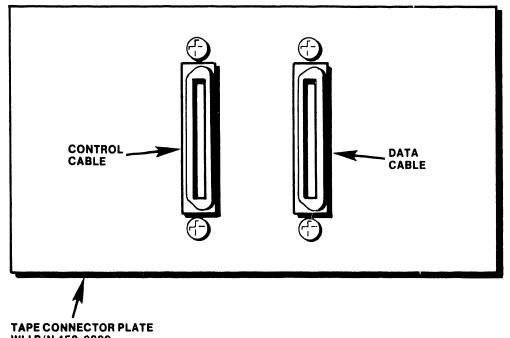

| 4.11.5 | Tape Cable Connectors                | 4-30 |

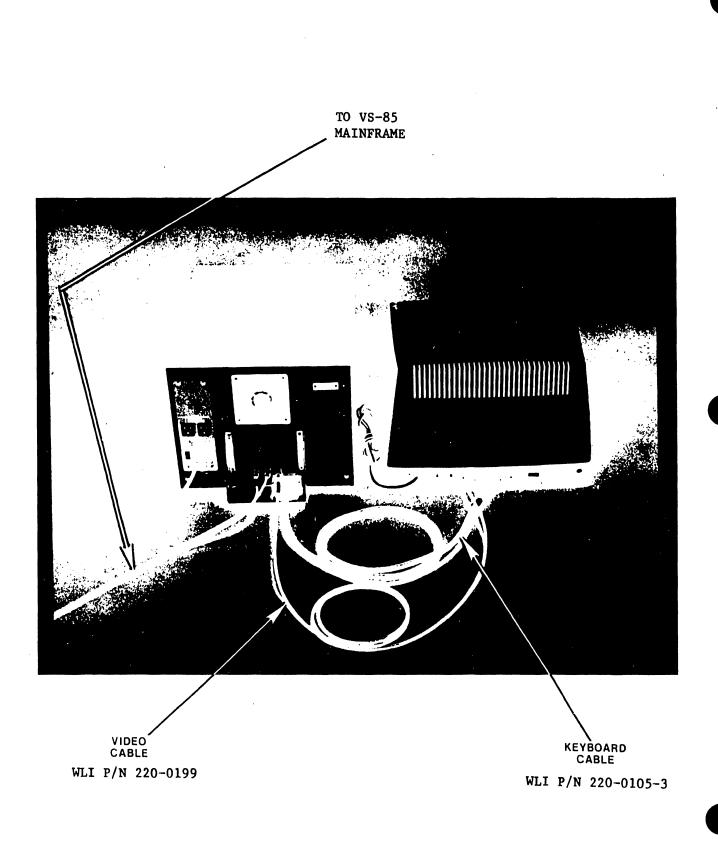

| 4.11.6 | Installing the Archiving Workstation |      |

| 4.12   | System Checkout 4-33                        |

|--------|---------------------------------------------|

| 4.13   | On-Line Checkout 4-33                       |

| 4.13.1 | Disk Drive Checkout 4-33                    |

| 4.13.2 | Printer Checkout 4-34                       |

| 4.13.3 | Tape Drive Checkout 4-35                    |

| 4.13.4 | Workstation Checkout 4-35                   |

| 4.13.5 | Final Checks 4-36                           |

| 4.14   | Close Up Main Frame 4-36                    |

| 4.15   | Daily System Power-Up/Power-Down Procedures |

| 4.16   | System Turnover 4-37                        |

|        |                                             |

# CHAPTER 5 PREVENTIVE AND CORRECTIVE MAINTENANCE

| 5.1       | General                                                 |     |

|-----------|---------------------------------------------------------|-----|

| 5.2       | Preventive Maintenance                                  |     |

| 5.2.1     | Tools                                                   |     |

| 5.2.2     | Test Equipment                                          |     |

| 5.2.3     | Materials                                               |     |

| 5.2.4     | Preventive Maintenence Schedule 5-1                     |     |

| 5.2.5     | Cleaning Mini-Floppy Drive Heads 5-2                    |     |

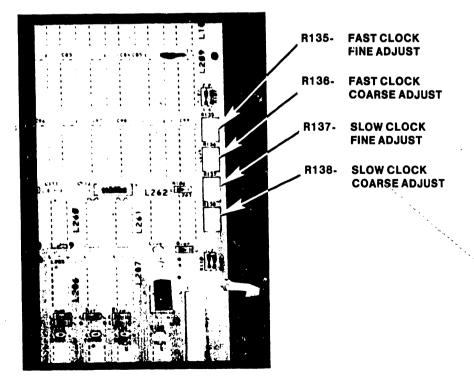

| 5.2.6     | Electrical Adjustments 5-2                              | ,   |

| 5.2.6.1   | Main Frame Voltage Adjustments 5-2                      |     |

| 5.2.7     | Peripheral Preventive Maintenance                       |     |

| 5.3       | Corrective Maintenance 5-3                              | j   |

| 5.3.1     | Tools                                                   | ,   |

| 5.3.2     | Test Equipment                                          | ,   |

| 5.3.3     | Materials                                               | ,   |

| 5.3.4     | Alignments 5-3                                          | 1   |

| 5.3.4.1   | Mini-floppy Drive Data Separator Adjustments 5-3        | ,   |

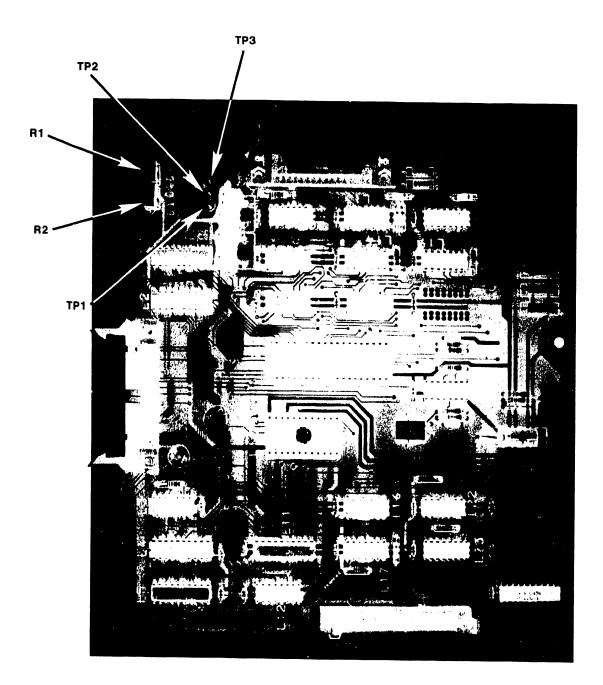

| 5.3.4.2   | Preliminary Mini-floppy Drive Adjustment Procedures 5-3 | 5   |

| 5.3.4.3   | Performing the Adjustment 5-5                           | ,   |

| 5.3.5     | Removal/Replacement 5-9                                 | )   |

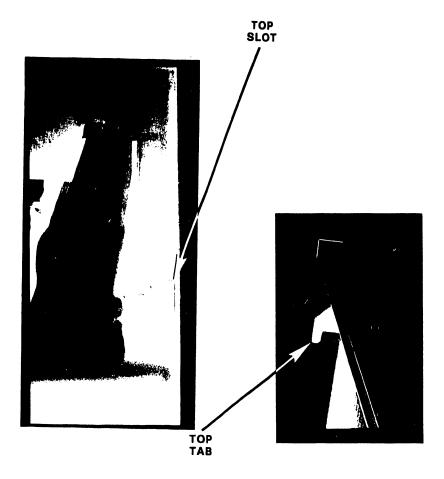

| 5.3.5.1   | Top Cover Removal                                       | 1   |

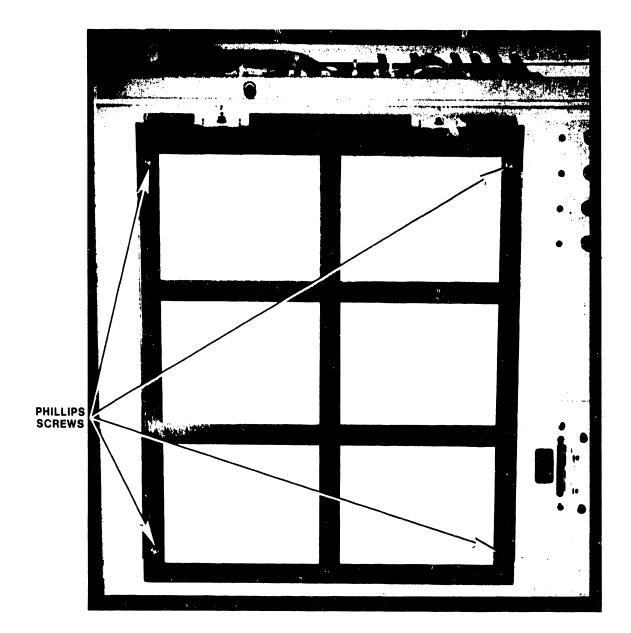

| 5.3.5.2   | Front Cover Removal 5-9                                 | )   |

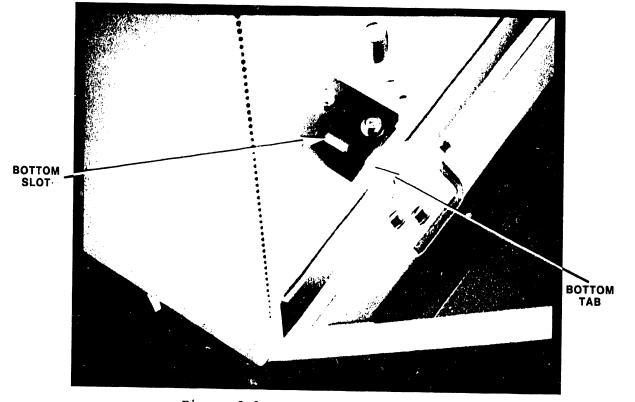

| 5.3.5.3   | CP Circuit Board Removal/Replacement                    | )   |

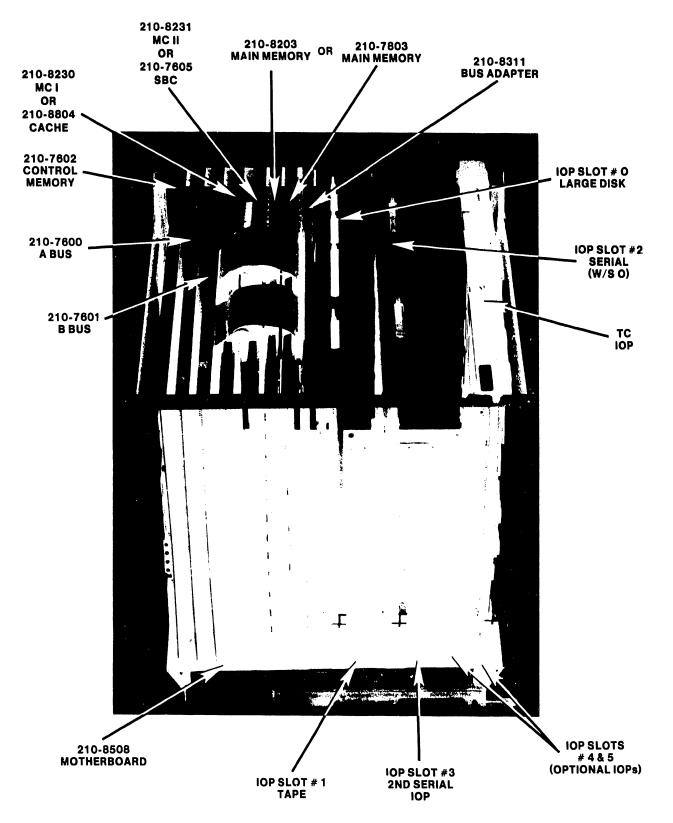

| 5.3.5.3.1 | 210-7602 Control Memory Removal/Replacement 5-9         | )   |

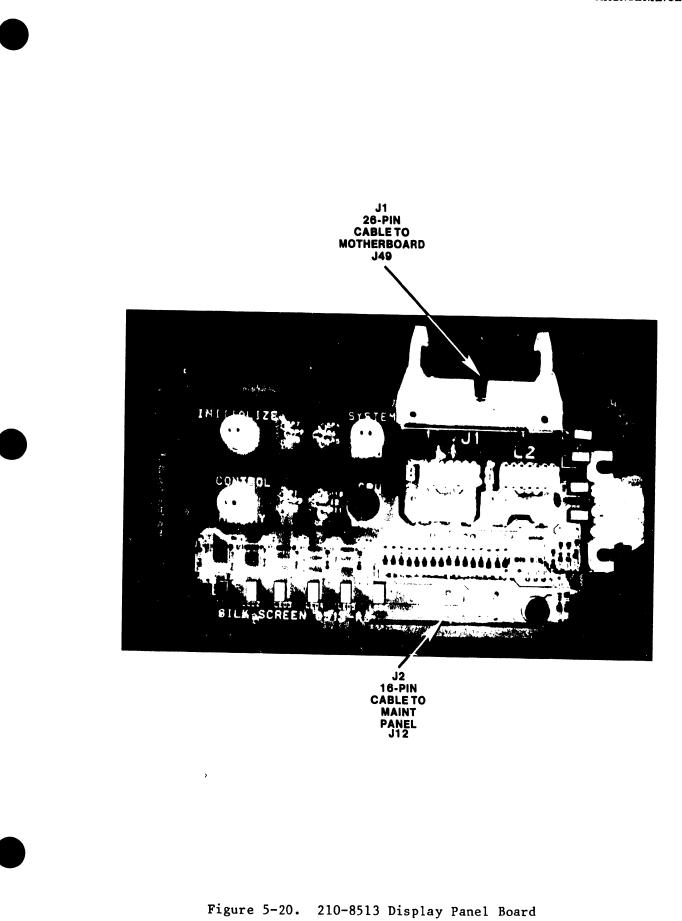

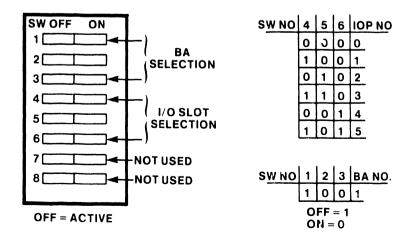

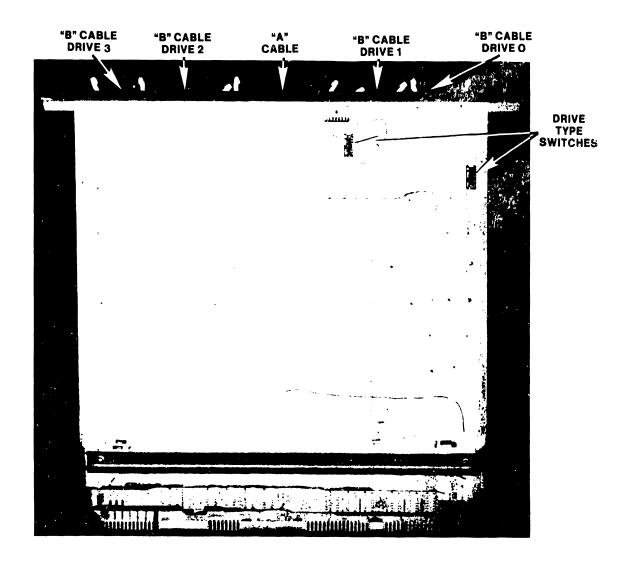

| 5.3.5.3.2 | 210-7600 A Bus Removal/Replacement 5-1                  | .2  |