THIS INFORMATION IS CONFIDENTIAL AND PHOPRILTARY TO WDC AND SHALL NOT BE REPLODUCED OR FURTHER DISCLOSED TO ANYONE OTHER THAN WDC EMPLOYEES WITHOUT WRITTEN AUTHORIZATION FROM WESTERN DIGITAL CORPORATION.

Rev. 11-25-75 Rev. 2-25-74 Ð Rev. 4-10-74  $\mathbb{C}$ Rev. 6-3-74 D Rev. 10-2-74 Ε Roy 11-14-74 Rev. 11-20-74 Rev. 12-11-74 Rev. 12-16-74 Rev. 1-30-75 J Rev. 3-26-75 K Rev. 5-2-75 Rev. 12-15-75

# **PRELIMINARY**

CP1631B

512 X 22 MICROPROGRAM ROM

(MICROM)

# PRELIMINARY

| PREPARED BY |       | WESTERN           | O DIGITAL | TITLE CP1631B                      |     |

|-------------|-------|-------------------|-----------|------------------------------------|-----|

| CHECK BY    | Alto. | WESTERN & DIGITAL |           | 512 X 22 MICROPROGRAM ROM (MICROM) |     |

| APPD R & D  |       | ISSUE DATE        | SHEET     | NUMBER                             | REV |

| APPD ENG    |       |                   | 1 of 14   | 500281                             | М   |

| APPD OP'S   |       |                   | •         |                                    |     |

#### INTRODUCTION

The WDC CP1631B (MICROM) is a 512 word by 22-bit N-channel silicon gate ROM. The ROM coding is programmed on the diffusion mask level (1N). The primary application for the ROM is for microprogram storage in the WDC microprocessor system. It is designed to interface directly with the CP1611B and CP1621B microprocessor chip set. The chip is packaged in a 40-lead plastic cavity dual-in-line package.

#### FEATURES

- . Organization 512 X 22

- . Access Time < 200 nsec

- Bi-Directional, Common Address and Data Bus Directly Compatible With WDC Microprocessor Microinstruction Bus

- Low Power Dissipation Typically 150 mW

- . Four High Voltage Clocks

#### OPERATION

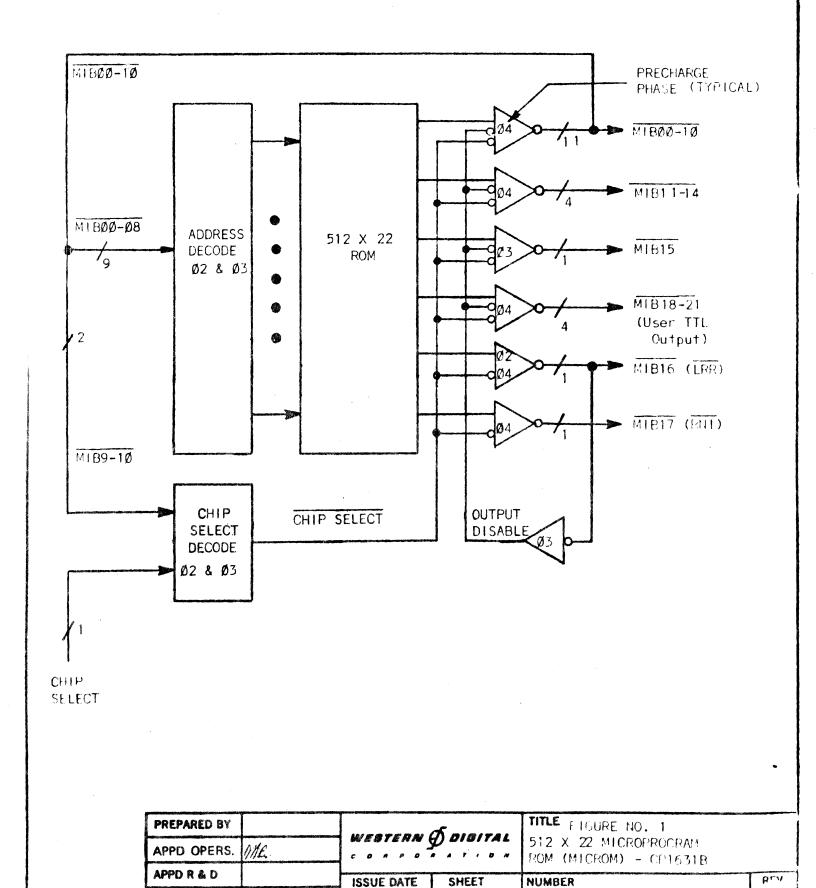

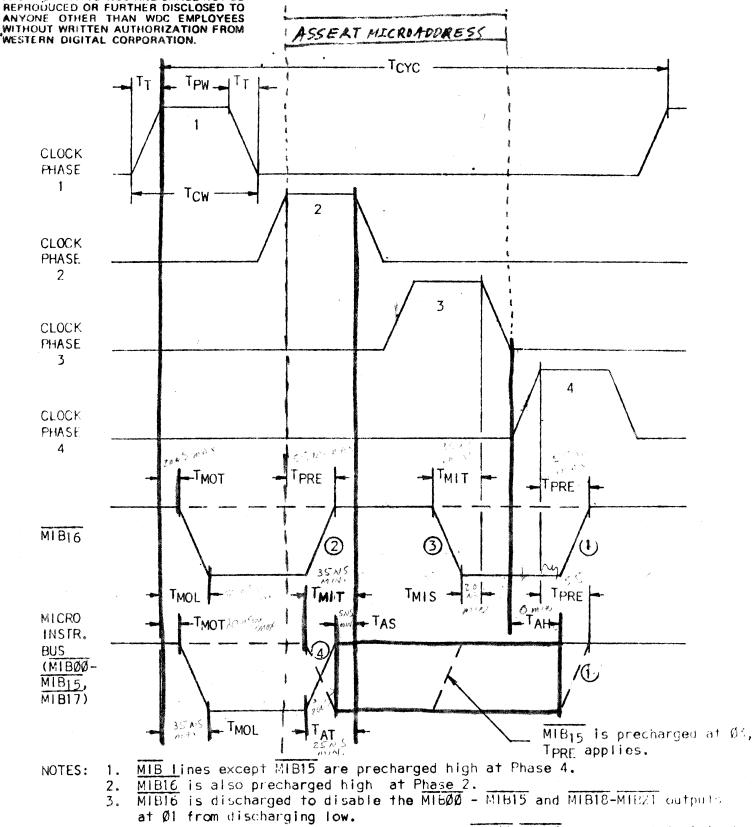

The basic operation of the microinstruction Control ROM (MICROM) is to receive addresses sent on the Microinstruction Bus (MIB) from the location counter of the CP1621B Control Chip, decode the address, access the ROM, and then output a 22-bit wide microinstruction to the Microinstruction Bus. The microinstruction address is transferred to the MICROM during  $\emptyset 2$ . It is decoded during  $\emptyset 3$  and the ROM is accessed during  $\emptyset 4$ . The microinstruction is transferred to the MIB bus at  $\emptyset 1$ . Address and data on the MIB is active low (Logic "1" = Low). The MIB bus is precharged high by all MICROMs on the bus as described by the following definitions of pin functions.

| PREPARED BY |     | WERTERN         | O DIGITAL | TITLE CP1631B                  |     |

|-------------|-----|-----------------|-----------|--------------------------------|-----|

| CHECK BY    | WE. | WEBTERN DOGITAL |           | 512 X 22 MTCROPROGRAM (MTCROM) | ROM |

| APPD R & D  |     | ISSUE DATE      | SHEET     | NUMBER                         | REV |

| APPD ENG    |     |                 | 2         | 500281                         | ١   |

| APPD OP'S   |     |                 |           |                                | М   |

- 1. MIBØØ MIBIØ; The address is transferred into the MICROM on these lines at Ø2 from the CP1621B. They are unconditionally precharged high at Ø4 by all the MICROMs on the MIB. MIBØØ is the least significant address (AØ) and MIBIØ is the most significant address (AIØ). The microinstruction data is placed on these lines at Ø1 by conditional discharge. MIBØØ is the LSB of the microinstruction. Chip selection is performed by MIBØ9, MIBIØ, and Chip Select. These signals are programmable.

- 2. MIB11 MIB14; These lines are microinstruction outputs only. They are unconditionally precharged high at Ø4 and conditionally discharged at Ø1 by the ROM microinstruction data.

- 3. MIB15; This line functions like MIB11 MIB14 except that it is precharged high during Ø3 by the MICROM.

- 4. MIB16; This is a MICROM input and output line. It is unconditionally precharged high at both Ø2 and Ø4. Microinstruction data is transferred out at Ø1 as with the other MICROM outputs. This output will enable the loading of the Return Register (RR) on the Control Chip when it is low at Ø1 (LRR). At Ø3 it performs as an Output Enable for the MICROM. If this line is discharged low by the Control Chip at Ø3 then MICROM lines MIBØØ to MIB15 and MIB18 MIB21 will not be discharged at the next Ø1.

- 5. MIB17; This MICROM output functions like MIB11 to MIB14. It is used on the Control Chip to enable the "Read Next Instruction" translation while over-riding any other translation. Discharging MIB17 to a low at Ø1 activates

| PREPARED BY |      | WESTERN (  | Dogwa | CP1631B                               |     |

|-------------|------|------------|-------|---------------------------------------|-----|

| CHECK BY    | 1/18 | 2 4 4 2    |       | 512 X 22 MICROPROGRAM ROM<br>(MICROM) | 1   |

| APPD R & D  |      | ISSUE DATE | SHEET | NUMBER                                | REV |

| APPD ENG    |      |            | 3     | 500281                                | М   |

| APPD OP'S   |      |            |       |                                       | , , |

the translation.

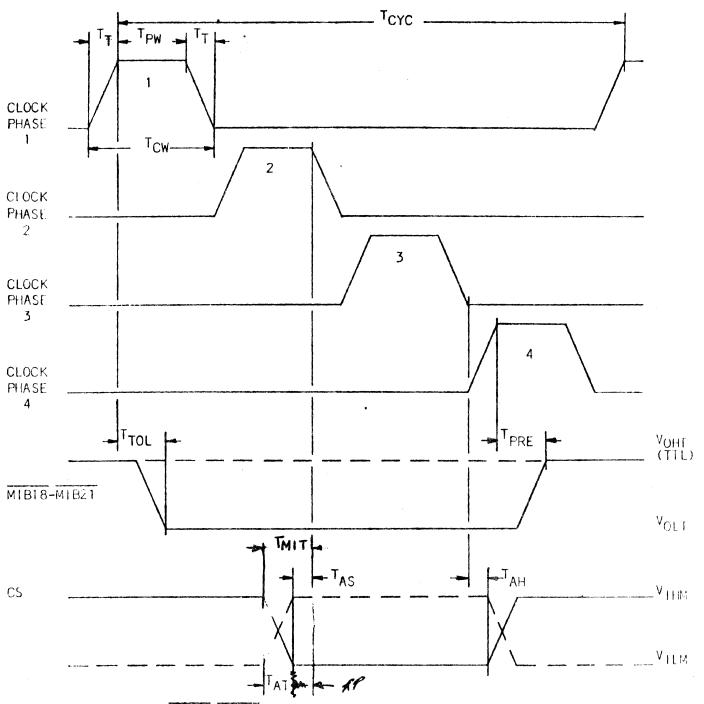

- 6. MIB18 MIB21; These four lines are extra TTL compatible outputs which can be used for external control functions. They are not used by the Control or Data chips. These outputs have wired-OR capability.

- 7. CHIP SELECT (CS); This is an MOS level input that will select (Enable) the MICROM with a high input level. This input is sampled like an address input at Ø2.

NOTE: A transistor programmed in the Memory Matrix will read as a high level on the MicroInstruction Bus when it is accessed.

Chip Select and Output Disable functions are performed by two additional rows in the ROM Matrix and therefore are programmable to affect any or all of the outputs.

NOTE: The MICROM is responsible for precharging the MIB lines unconditionally.

MIBØØ-MIB14 and MIB17-MIB21 are precharged high during Ø4. MIB15 is

precharged high during Ø3 and MIB16 is precharged high during Ø2 and Ø4.

(The MIB lines are precharged also when the chip is disabled.)

| PREPARED BY |       |            | Rowers | TITLE CP1631B         |     |

|-------------|-------|------------|--------|-----------------------|-----|

| CHECK BY    | 17.16 | WESTERN    |        | 512 X 22 MICROPROGRAM |     |

| APPD R & D  |       | ISSUE DATE | SHEET  | ROM (MICROM) NUMBER   | REV |

| APPD ENG    |       |            | 4      | 500281                |     |

| APPD OP'S   |       | 1          |        | 200201                | M   |

APPD ENG

CP1631B - 11K (MICROM)

5

500281

1-1

THIS INFORMATION IS CONFIDENTIAL AND PROPRIETARY TO VICE AND SHALL HOT SE EXPROSUCED OR FUNCTION DISCLOSED TO ANYONE OTHER THAN WOO EMPLOYEES WITHOUT VALITA AUTHORIZATION FROM WESTERN DIGITAL CORPORATION.

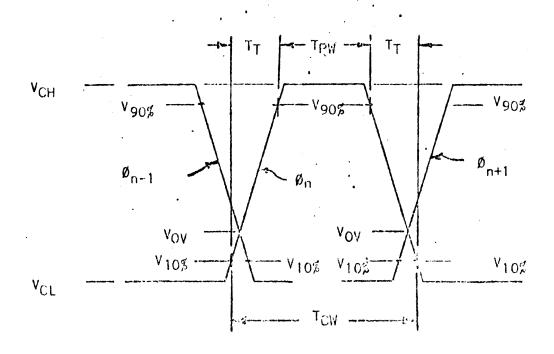

# CLOCK DIAGRAM

# DEFINITION OF 10% AND 90% VOLTAGE POINTS FOR CLOCK, INPUTS AND OUTPUTS

$$V_{90\%} = V_{LOW(max.)} + .9 \left[V_{HIGH(min.)} - V_{LOW(max.)}\right]$$

This definition applies to clock, input and output pins.

| 1 | PREPARED BY<br>APPO OPERS. | n's                                          | recoveres (5) asciral | CP1631B 512 X 22 MICROPROGRAM ROM (MICROM) | 1 , |

|---|----------------------------|----------------------------------------------|-----------------------|--------------------------------------------|-----|

|   | ASSPAD                     | napanan i renam kamanan ulker sinta ulkera a | ROOSE MARKET OF LE    | 100.05 tc<br>500281                        | )   |

PROPRIETARY TO WOC AND SHALL NOT BE

4. Address input transistions occur only on MIBON-MIBIN lines and Chip Select.

5. Switching times are measured at 10% and 90% of specified levels.

| PREPARED BY | WESTERN (  | Knierza | TITLE FIGURE NO. 2    |     |

|-------------|------------|---------|-----------------------|-----|

| APPD OPERS. |            | ATTO    | MICROM TIMING DIAGRAM |     |

| APPD R & D  | ISSUE DATE | SHEET   | NUMBER CP16.41P       | REV |

| APPD ENG    |            | 1       | 500281                | 11  |

PROPRIETARY TO WDC AND SHALL NOT BE REPRODUCED OR FURTHER DISCLOSED TO ANYONE OTHER THAN WDC EMPLOYEES WITHOUT WRITTEN AUTHORIZATION FROM WESTERN DIGITAL CORPORATION.

NOTE: TIL outputs (MIB18-MIB21) are unconditionally driven high at Ø4 and conditionally driven low at Ø1. This conditional low will be valid until the next Ø4.

| PREPARED BY |   | WESTERN (  | To mercar | TITLE FIGURE NO. 3 |     |

|-------------|---|------------|-----------|--------------------|-----|

| APPD OPERS. |   | COMPO      |           | TTL OUTPUT TIMING  |     |

| APPD R & D  | · | ISSUE DATE | SHEET     | CP1631B<br>NUMBER  | REV |

| APPD ENG    |   |            | 8         | 509281             |     |

THIS INFORMATION IS CONFIDENTIAL AND PHOPRIETARY TO WOC AND SHALL NOT BE HEPHODUCED OR FURTHER DISCLOSED TO ANYONE OTHER THAN WOC EMPLOYEES WITHOUT WRITTEN AUTHORIZATION FROM WESTERN DIGITAL CORPORATION.

# ABSOLUTE MAXIMUM RATINGS OVER FREE AIR TEMPERATURE RANGE (Unless Otherwise Noted)\*

| Supply Voltage V <sub>DD</sub> (See NOTE) | -0.5V to 15V   |

|-------------------------------------------|----------------|

| Supply Voltage VCC (see NOTE)             | -0.5V to 15V   |

| Supply Voltage V <sub>BB</sub> (see NOTE) | -10V to 1.0V   |

| All Other Pin Voltages (see NOTE)         | -1.0V to 15V   |

| Clock Voltage (see NOTE)**                | -1.0V to 15V   |

| Operating Free Air Temperature Range      | 0°C to 125°C   |

| Storage Temperature Range                 | -55°C to 125°C |

NOTE: These voltage values are with respect to  $V_{SS}$  Supply Voltage. If  $V_{BB}$  is more positive than any other voltage, then  $I_{BB}$  must be limited to  $I_{Oma}$ .

- \* Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum-rating conditions for extended periods may affect device reliability.

- \*\* The other three clock voltages must be between 0.5V and -0.6V except for switching overlaps. Not more than one clock may be high at any one time.

Applying power to the part may be any sequence of conditions that do not violate the maximum ratings specified on this sheet.

| PREPARED BY |     |            | Пописан     | TITLE CP1631B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |  |

|-------------|-----|------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|

| CHECK BY    | MR. | WESTERN    | - I I I I I | 512 X 22 MICROPROGRAM (MICROM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |  |

| APPD R & D  | **  | ISSUE DATE | SHEET       | NUMBER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | REV |  |

| APPD ENG    |     |            | 9           | 500281                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | м   |  |

| APPO OP'S   |     |            |             | and the second s | 1.3 |  |

PROPRIETARY TO WDC AND SHALL NOT BE REPRODUCED OR FURTHER DISCLOSED TO ANYONE OTHER THAN WDC EMPLOYEES WITHOUT WRITTEN AUTHORIZATION FROM WESTERN DIGITAL CORPORATION.

#### OPERATING CHARACTERISTICS

$T_{CASE}$  =  $\emptyset$ °C to 70°C,  $V_{DD}$  = +12.0V  $\pm$  .6V,  $V_{BB}$  = -3.9  $\pm$  .25V,  $V_{SS}$  =  $\emptyset$ V,  $V_{CC}$  = +5V  $\pm$  .25V

| SYMBOL           | CHARACTERISTIC                                                                         | MIN          | TYP  | MAX          | UNITS | COMMENTS AND CONDITIONS                               |

|------------------|----------------------------------------------------------------------------------------|--------------|------|--------------|-------|-------------------------------------------------------|

| TÉ .             | Leaka <b>ge Curre</b> nt For <b>Any Pin</b><br>Other <b>Than</b> Clock Or <b>Power</b> |              |      | ±10          | μΑ    | V <sub>IN</sub> = 5.25V/ØV                            |

| 1 <sub>BB</sub>  | V <sub>BB</sub> Supply Current                                                         |              |      | -500         | μА    | <b>VBB</b> = -5.25V                                   |

| LC               | Clock Leakage Current                                                                  |              |      | ±100         | μΑ    | V <sub>CLOCK</sub> = 13.7V/ØV                         |

| CCAVE            | Average VCC Operating Current*                                                         |              | 10.0 | 20.0         | mA    | T <sub>CYC</sub> = 300 nsec<br>C <sub>L</sub> = 25 pf |

| IDDAVE           | Average Vpp Operating Current                                                          |              | 10.0 | 20.0         | mA    | T <sub>CYC</sub> = 300 nsec<br>C <sub>L</sub> = 50 pf |

| VIHM             | Input High Voltage (All Inputs)                                                        | 4.0          |      | VCC          | ٧     |                                                       |

| VILM             | Input Low Voltage (All Inputs)                                                         | 0.0.         |      | 0.8          | ٧     |                                                       |

| V <sub>OHM</sub> | Output High Voltage (MOS)                                                              | 4.35         |      | VCC          | ٧     | 1 <sub>0</sub> = -30 μA                               |

| <b>VOHT</b>      | Output High Voltage (TTL)                                                              | 2.4          |      | VCC          | ٧     | l <sub>O</sub> = -50 μA                               |

| VOLM             | Output Low Voltage (MOS)                                                               | VSS          |      | 0.4          | · V   | 10 = 100 μA                                           |

| VOLT             | Output Low Voltage (TTL)                                                               | 0.0          |      | 0.4          | V     | 1 <sub>0</sub> = 1.8 ma                               |

| V <sub>O</sub> V | Overlap Voltage Of Any Two<br>Adjacent Clock Phases                                    | 0.0          |      | 3.0          | ٧     |                                                       |

| V <sub>CH</sub>  | Clock High Voltage (SEE NOTE)                                                          | 11.8<br>12.0 |      | 13.0<br>13.7 | V     | $V_{DD} = 11.4  V_{DD} = 12.6$                        |

| VCL              | Clock Low Voltage (SEE NOTE)                                                           | -0.6         |      | 0.5          | ٧     |                                                       |

NOTE: Linear interpolation applies for  $V_{CH}$  when  $V_{DD}$  is between 11.4V and 12.6V. No overshoot or undershoot allowable.

\*Note: The majority of this current is used to precharge the output capacitance, CL; and therefore, is proportional to the CL precharged by the MICROM and the frequency of discharge.

| CHECK BY  APPD R & D | WESTERN & DIGITAL |             | CP1631B 512 X 22 MICROPROGRAM ROM (MICROM) |      |  |

|----------------------|-------------------|-------------|--------------------------------------------|------|--|

| APPD ENG             | ISSUE DATE        | SHEET<br>10 | NUMBER 500281                              | REV. |  |

| APPD OP'S            |                   | , ,         | 500201                                     |      |  |

### AC CHARACTERISTICS

$T_{CASE}$  =  $\emptyset^{o}C$  to  $70^{o}C$ ,  $V_{DD}$  = +12V ± .6V,  $V_{BB}$  = -3.9V ± .25V,  $V_{SS}$  =  $\emptyset^{o}V$ ,  $V_{CC}$  = +5. $\emptyset^{o}V$  ±0.25V

| SYMBOL.         | CHARACTERISTIC                            | MIN | TYP | MAX        | UNITS | CONDITIONS             |

|-----------------|-------------------------------------------|-----|-----|------------|-------|------------------------|

| 1 <sub>PW</sub> | Clock Width High (All Phases)             | 55  |     | 240        | nsec  |                        |

| ¹c₩             | Clock Width Low (All Phases)              | 75  |     | 300        | nsec  |                        |

| $\tau_{T}$      | Clock Transition Time (All Phases)        | 5   |     |            | nsec  |                        |

| TCYC            | Clock Period (Ali Phases)                 | 300 |     | 1000       | nsec  |                        |

| TMOL            | Output Propagation Delay<br>From Ø1 Clock |     |     | 35         | nsec  | C <sub>L</sub> = 50 pf |

| TPRE            | Time To Precharge Outputs<br>High         |     |     | <b>5</b> 5 | nsec  | C <sub>L</sub> = 25 pf |

| TMIS            | Input Set-Up Time on<br>MIB16 At Phase 3  | 20  |     | ,          | nsec  |                        |

| TTOL            | TTL Out Switching Low                     |     |     | 55         | nsec  | Figure 5               |

| TAS             | Address Set-Up Time                       | 5   |     |            | nsec  |                        |

| TAH             | Address Hold Time                         | Ø   |     |            | nsec  | ·                      |

| TMOT            | Output Transition Start<br>Delay Time     |     |     | 20         | nsec  | C <sub>L</sub> = 50 pf |

| TMIT            | Input Transition Start<br>Set-Up Time     | 35  |     |            | nsec  |                        |

| TAT             | Address Transition Start<br>Set-Up Time   | 25  |     |            | nsec  |                        |

| PREPARED BY CHECK BY |  | WESTERN (  | DIGITAL | CP1631B 512 X 22 MICROPROGRAM ROM (MICROM) |  | MC                                     |

|----------------------|--|------------|---------|--------------------------------------------|--|----------------------------------------|

| APPORAD              |  | ISSUE DATE | SHEET   | NUMBER                                     |  | REV.                                   |

| AMO ENG              |  |            | 11      | - 500281                                   |  | М                                      |

| APPO OF'S            |  |            |         | L                                          |  | ــــــــــــــــــــــــــــــــــــــ |

HIS INFORMATION IS CONFIDENTIAL AND ROPRIETARY TO WDC AND SHALL NOT BE PHODUCED OR FURTHER DISCLOSED TO TYONE OTHER THAN WDC EMPLOYEES ITHOUT WRITTEN AUTHORIZATION FROM ESTERN DIGITAL CORPORATION.

## CAPACITANCE

| SYMBOL           | CHARACTERISTIC                       | MIN | TYP | MAX | UNITS | CONDITIONS                                    |

|------------------|--------------------------------------|-----|-----|-----|-------|-----------------------------------------------|

| Cø1              | Clock Phase 1 Capacitance            |     | 20  | 50  | pf    |                                               |

| C <sub>Ø2</sub>  | Clock Phase 2 Capacitance            | ٠   | 40  | 60  | pf    | V <sub>IN</sub> = ØV,                         |

| CØ3              | Clock Phase 3 Capacitance            |     | 20  | 50  | pf.   | VIN = ØV,<br>V <sub>SS</sub> = ØV,            |

| C <sub>Ø4</sub>  | Clock Phase 4 Capacitance            |     | 50  | 100 | pf    | $v_{DD} = \emptyset v$ ,<br>$v_{BB} = -3.9 V$ |

| $c_D$            | Data Input/Output Pin<br>Capacitance |     | 5.0 | 8.0 | pf    | f = 1 MHz                                     |

| $c_{\mathbb{C}}$ | Clock To Clock Capacitance           |     | 3.0 | 6.0 | pf    |                                               |

| PREPARED BY |       |            | Ø         | TITLE CP1631B                      |     |

|-------------|-------|------------|-----------|------------------------------------|-----|

| CHECK BY    | 11/1/ | WESTERN    | J BIBITAL | 512 X 22 MICROPROGRAM ROM (MICROM) |     |

| APPD R & D  |       | ISSUE DATE | SHEET     | NUMBER                             | REV |

| APPD ENG    |       |            | 12        | 500281                             | М   |

| APPD OP'S   |       |            | 12        | 300261                             |     |

HIS INFORMATION IS CONFIDENTIAL AND HOPRIETARY TO WDC AND SHALL NOT BE FPHODUCED OR FURTHER DISCLOSED TO MYONE OTHER THAN WDC EMPLOYEES VITHOUT WRITTEN AUTHORIZATION FROM JESTERN DIGITAL CORPORATION.

## FIGURE 4

#### PIN ASSIGNMENT CP1631B

|         |        | ,        |             |

|---------|--------|----------|-------------|

| PIN NO. | SIGNAL | PIN' NO. | SIGNAL      |

| 1       | Ø3     | . 21     | Ø2          |

| 2       | VBB    | 22       | VCC         |

| 3       | NC*    | 23       | CHIP SELECT |

| 4       | NC     | 24       | NC          |

| 5       | NC     | 25       | NC          |

| 6       | NC     | 26       | MIBII       |

| 7       | MIB15  | 27       | MIB1Ø       |

| 8       | MIB14  | 28       | MIBØ9       |

| 9 .     | MIB13  | 29       | MIBØ8       |

| 1Ø      | MIB12  | 3Ø       | MIBØ7       |

| 11      | MIB16  | 31       | MIBØ6       |

| 12      | MIB17  | 32       | MIBØ5       |

| 13      | MIB18  | 33       | MIBØ4       |

| 14      | MIB19  | 34       | MIBØ3       |

| 15      | MIB2Ø  | 35       | MIBØ2       |

| 16      | MIB21  | 36       | NC          |

| 17 .    | NC     | 37       | MIBØ1       |

| 18      | NC     | 38       | MIBØØ       |

| 19      | VSS    | 39       | VDD         |

| 2Ø      | Ø4     | 40       | Ø1          |

|         |        |          |             |

\* NOTE: NC means No Connection.

| PREPARED BY |        | WESTERN (  | 5 minisar | CP1631B               |     |

|-------------|--------|------------|-----------|-----------------------|-----|

| CHECK BY    | WILE . |            | DIGITAL   | 512 X 22 MICROPROGRAM |     |

| APPD R & D  |        | ISSUE DATE | SHEET     | ROM (MICROM) NUMBER   | REV |

| APPD ENG    |        |            | 13        | 500281                | M   |

| APPD OP'S   |        |            | _         |                       |     |

# C P 1 6 1 1 B

# NEW REVISIONS

| REVISION                                      | DATE                    | PAGES                 | CHANGES                                                                                                                                                                                                                                                          |

|-----------------------------------------------|-------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| G                                             | 3-25-75                 | 1<br>6                | New Title Page with new revision Old: The address remains on the bus for one complete clock cycle. The data is                                                                                                                                                   |

|                                               |                         |                       | New: The address is valid on the bus during Phases 2, 3, and 4. The data is                                                                                                                                                                                      |

|                                               |                         | 9                     | CE changes to CS                                                                                                                                                                                                                                                 |

|                                               | •                       | 10                    | New Clock Diagram                                                                                                                                                                                                                                                |

|                                               |                         | 11                    | Output delay times measured from 10% voltages of the clocks.                                                                                                                                                                                                     |

|                                               |                         | 12<br>13              | Delete Supply Voltage V <sub>CC</sub> .<br>New                                                                                                                                                                                                                   |

|                                               |                         | 14                    | New                                                                                                                                                                                                                                                              |

|                                               |                         | 15                    | $V_{IN} = \emptyset V$ added, and 12V changed to $\emptyset V$ for $V_{DD}$ .                                                                                                                                                                                    |

|                                               |                         | 17                    | New TTL Output Test Load.                                                                                                                                                                                                                                        |

| (G)                                           | 4-8-75<br>NOIE: Page 15 | 10<br>_becomes_Page_1 | Added "For Clock Inputs and Outputs"                                                                                                                                                                                                                             |

|                                               |                         | •                     |                                                                                                                                                                                                                                                                  |

| <b>H</b>                                      | 5-2-75                  | 10                    | New Revision added to Title Page.  Comment added: "This definition applies                                                                                                                                                                                       |

|                                               |                         | 13                    | to clock, input and output pins."  IL Condition line: $V_{1N}$ - changed to $V_{1N}$ =. $V_{OLM}$ Condition line: I = changed to $I_0$ =.                                                                                                                        |

|                                               |                         | 14                    | $V_{CH}$ and $V_{CL}$ line has same Condition comment.<br>$T_{DOV}$ and $T_{DOT}$ line Condition statements changed to read: Fig. 5.                                                                                                                             |

|                                               |                         | 17                    | Title added: Figure 5, and 50 pf added, from DUT line.                                                                                                                                                                                                           |

| the fair the tips over one say the tips op to | NOTE: All page          | s contain curre       | nt revision letter (H).                                                                                                                                                                                                                                          |

| l                                             | 11-10-75                | 11                    | Redrawn with output delays measured from 90% of clocks, TMOT and TMIT times added                                                                                                                                                                                |

|                                               |                         | 13                    | TA changed to $T_{CASE}$ $V_{BB}$ =-5.0 changed to $V_{BB}$ = -3.9V $I_{L}$ MAX ±5 changed to ±10 $I_{BB}$ MAX 100 changed to -500 $I_{LC}$ MAX ±30 changed to ±100                                                                                              |

|                                               |                         |                       | IDDAVE TYP 10 changed to 20.0 IDDAVE MAX 20 changed to 35.0 VIHM MIN 4.0 changed to 4.25 VCH MIN 11.4 changed to 11.8 VCH MAX 12.6 changed to VDD + 1.1V VCL MIN 0.0 changed to -0.6 VIHT MIN 2.4 changed to 3.0 1.0V Overshoot and Undershoot Allowable changed |

|                                               |                         |                       | to No Overshoot or Undershoot Allowable                                                                                                                                                                                                                          |

# CP1611B

# NEW REVISIONS Contt

| REVISION                                      | DATE       | PAGE | CHANGES                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------------------|------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| •                                             | 11-10-75   | 14   | TA changed to TCASE  VBB = -5.0V changed to VBB = -3.9V  TPW MIN 40 changed to 55  TCW MIN 70 changed to 75  TT MAX dropped  TMIH MIN 0 changed to 5  TMOL MAX 40 changed to 35  TJOL MAX 40 changed to 35  TDIS MIN 0 changed to 15  TDIH MIN 0 changed to 10  TWLS MIN 0 changed to 10  TWLS MIN 0 changed to 10  TMIT and TMOT added  "NOTE: THESE TIMES, ETC." dropped |

| NOTE: All pages (<br>current re<br>Letter (1) |            | 15   | Cg1 TYP 30 changed to 40 Cg1 MAX 50 changed to 60 Cg2 TYP 30 changed to 40 Cg2 MAX 50 changed to 60 Cg3 TYP 30 changed to 40 Cg3 TYP 30 changed to 60 Cg3 MAX 50 changed to 60 Cg4 TYP 30 changed to 40 Cg4 MAX 50 changed to 60 Cg4 MAX 50 changed to 60 CD MAX 8.0 changed to 15.0 VBB = -5V changed to VBB = -3.9V                                                      |

| (1)                                           | 11-14-75   | 11   | Twhen measured from 10% $\emptyset_4$ changed to 10% of $\emptyset_1$                                                                                                                                                                                                                                                                                                      |

| acapted pople                                 | spi 1/6/16 | 12   | V <sub>BB</sub> 0.5V changed to 1.0V<br>Pin Voltages -0.5V changed to -1.0V<br>Clock Voltages -0.5V changed to -1.0V<br>Operating Temp. Range 70°C changed to 125°C<br>(If V <sub>BB</sub> is more, etc.) added to NOTE<br>** -0.5V changed to -0.6V                                                                                                                       |

| David K. M. 16/76                             | and and    | 13   | ILC CONDITION 12.6V changed to 13.7V  V <sub>IHM</sub> MIN 4.25 changed to 4.1  V <sub>CH</sub> MAX V <sub>DD</sub> + 1.1V changed to 13.0 for  V <sub>DD</sub> = 11.4V, 13.7 for V <sub>DD</sub> = 12.6  V <sub>CH</sub> MIN 11.8 changed to 12.0 for V <sub>DD</sub> = 12.7  NOTE added  V <sub>IHT</sub> MIN 3.0 changed to 2.4                                         |

| ()'  \v                                       | <b>()</b>  | 14   | TDOV MAX 75 changed to 70 TDOT MAX 60 changed to 55 TWHS MIN 15 changed to 20 TWLS MIN 10 changed to 20                                                                                                                                                                                                                                                                    |

15