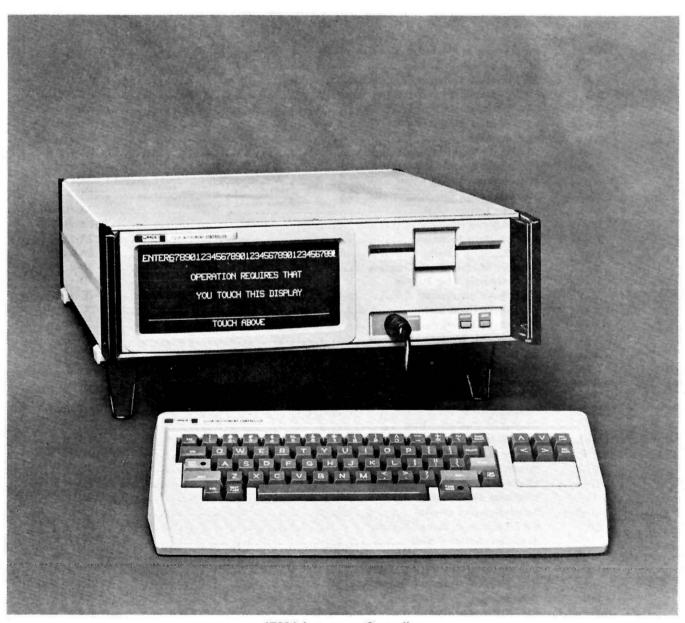

# 1720A Instrument Controller

Service Manual

#### **NOTE**

This manual documents the Model 1720A and its assemblies at the revision levels shown in Section 4A. If your instrument contains assemblies with different revision letters, it will be necessary for you to either update or backdate this manual. Refer to the supplemental change/errata sheet for newer assemblies, or to the backdating sheet in Section 4A for older assemblies.

# 1720A Instrument Controller

Service Manual

#### WARRANTY

Notwithstanding any provision of any agreement the following warranty is exclusive:

The JOHN FLUKE MFG. CO., INC., warrants each instrument controller it manufactures to be free from defects in material and workmanship under normal use and service for the period of 90 days from date of purchase. This warranty extends only to the original purchaser. This warranty shall not apply to fuses, floppy disks or contents thereof, or any product or parts which have been subject to misuse, neglect, accident or abnormal conditions of operations.

In the event of failure of a product covered by this warranty, John Fluke Mfg. Co., Inc. will repair an instrument controller returned to an authorized Service Facility within 90 days of the original purchase; provided the warrantor's examination discloses to its satisfaction that the product was defective. The warrantor may, at its option, replace the product in lieu of repair. With regard to any instrument controller returned within 90 days of the original purchase, said repairs or replacement will be made without charge. If the failure has been caused by misuse, neglect, accident or abnormal conditions of operations, repairs will be billed at a nominal cost. In such case, an estimate will be submitted before work is started if requested.

THE FOREGOING WARRANTY IS IN LIEU OF ALL OTHER WARRANTIES, EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS OR ADEQUACY FOR ANY PARTICULAR PURPOSE OR USE. JOHN FLUKE MFG. CO., INC., SHALL NOT BE LIABLE FOR ANY SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES, WHETHER IN CONTRACT, TORT OR OTHERWISE.

#### If any failure occurs, the following steps should be taken:

- 1. Notify the JOHN FLUKE MFG. CO., INC., or the nearest Service Facility, giving full details of the difficulty, and include the Model number, type number, and the serial number. On receipt of this information, service data or shipping instructions will be forwarded to you.

- 2. On receipt of the shipping instructions, forward the instrument controller transportation prepaid. Repairs will be made at the Service Facility and the instrument controller returned, transportation prepaid.

#### SHIPPING TO MANUFACTURER FOR REPAIR OR ADJUSTMENT

All shipments of JOHN FLUKE MFG. CO., INC., instrument controllers should be made via United Parcel Service or "Best Way" prepaid. The instrument controller should be shipped in the original packing carton. If this original carton is not available a suitable container that is rigid and of adequate size may be used. However, the JOHN FLUKE MFG. CO., INC., does not recommend shipment of instrument controllers in substitute containers. In the event a substitute container must be used, the instrument controller should be wrapped in paper and surrounded with at least four inches of excelsior or other similar shock absorbing material. JOHN FLUKE MFG. CO., INC., shall assume NO risk for intransit shipment damage.

#### **CLAIM FOR DAMAGE IN SHIPMENT TO ORIGINAL PURCHASER**

The instrument controller should be thoroughly inspected immediately upon original delivery to purchaser. All material in the container should be checked against the enclosed packing list. The manufacturer will not be responsible for shortages against the packing sheet unless notified immediately. If the instrument controller is damaged in any way, a claim should be filed with the carrier immediately. (To obtain a quotation to repair shipment damage, contact the nearest Fluke Technical Center.) Final claim and negotiations with the carrier must be completed by the customer.

The JOHN FLUKE MFG. CO., INC. will be happy to answer all application or use questions, which will enhance your use of this instrument. Please address your requests or correspondence to: JOHN FLUKE MFG. CO., INC., P.O. BOX 43210, MOUNTLAKE TERRACE, WASHINGTON 98043, ATTEN: Sales Dept. For European Customers: Fluke (Nederland) B.V., Zevenheuvelenweg 53, Tilburg, The Netherlands.\*

\*For European customers, Air Freight prepaid.

#### 1720A SERVICE POLICY

#### **WARRANTY POLICY**

a. The 1720A Controller is serviced primarily through a module exchange program or by returning the unit to your local service center for repair. Diagnostic software routines have been provided that will allow the user to isolate a fault to the module level. In the event of a failure contact your local service center to arrange for a replacement module.

There is a complete support inventory at each service facility with a 24-hour turnaround time goal on exchange modules.

- b. Upon request, on-site service is available for which a "transport zone fee" is charged. The rates for these charges are available from the local office of John Fluke Mfg. Co., Inc.

- c. An on-site service contract may be purchased within the warranty period to assure minimum down time.

#### **OUT-OF-WARRANTY SERVICE**

- a. The 1720A Controller is serviced primarily through a module exchange program or by returning the unit to your local service center for repair. Diagnostic software routines have been provided that will allow the user to isolate a fault to the module level. In the event of a failure contact your local service center to arrange for a replacement module. Module exchange will be available to the customer on a flat rate exchange basis. There will be a complete support inventory at each service facility with a 24-hour turnaround goal on exchanges.

- b. On-site service is available on a time and materials basis. Additionally a transport zone fee is also chargeable.

- c. An on-site service contract may be purchased to assure minimum down time. Contract support will also assure maximum priority on all service requests. Contracts initiated prior to the expiration of the warranty will not require a reinspection fee.

- d. Units may be returned to any service facility for repair with quotations to the customers for estimated time and material charges.

|  | · |   |

|--|---|---|

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   | · |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

## **Table of Contents**

| SECTION    | •                                                                                                       | TITLE                                                                                                                                                                                                                                                                                  | AGE                                                                                      |

|------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| 1          | INTROD                                                                                                  | DUCTION AND SPECIFICATIONS                                                                                                                                                                                                                                                             | 1-1                                                                                      |

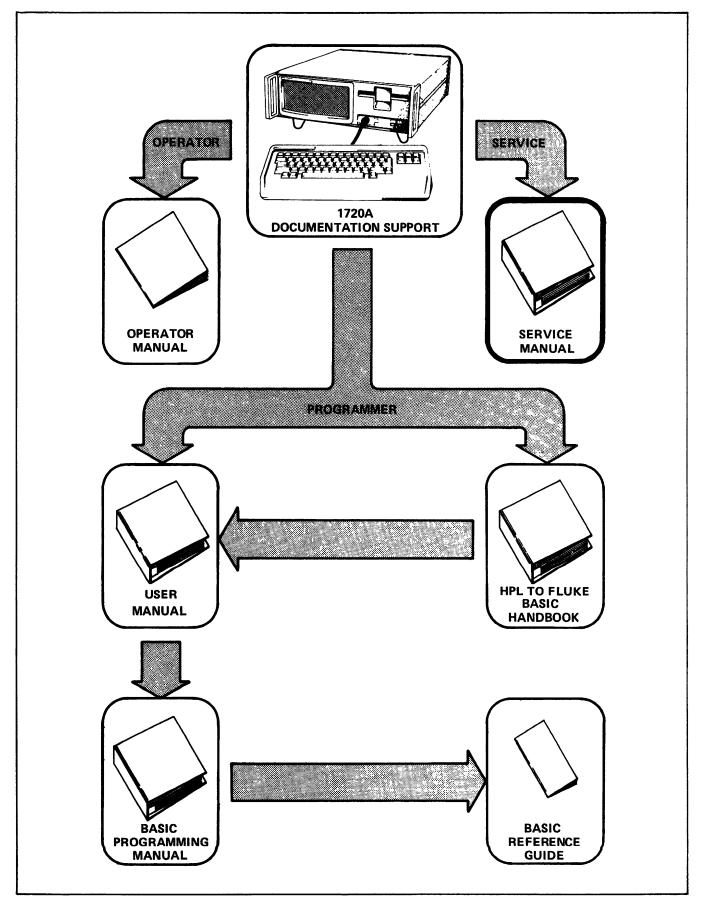

|            | 1-1.<br>1-3.<br>1-5.<br>1-7.<br>1-9.<br>1-11.<br>1-13.<br>1-15.<br>1-17.                                | DESCRIPTION OF THE 1720A DOCUMENTATION 1720A User Manual 1720A Fluke BASIC Programming Manual 1720A BASIC Reference Guide HPL to Fluke BASIC Handbook 1720A Display Worksheet Pads 1720A Operator Manual 1720A Service Manual Introduction To This Manual SPECIFICATIONS               | 1-3<br>1-1<br>1-1<br>1-1<br>1-1<br>1-1<br>1-3                                            |

| 2          | THEOR                                                                                                   | Y OF OPERATION                                                                                                                                                                                                                                                                         |                                                                                          |

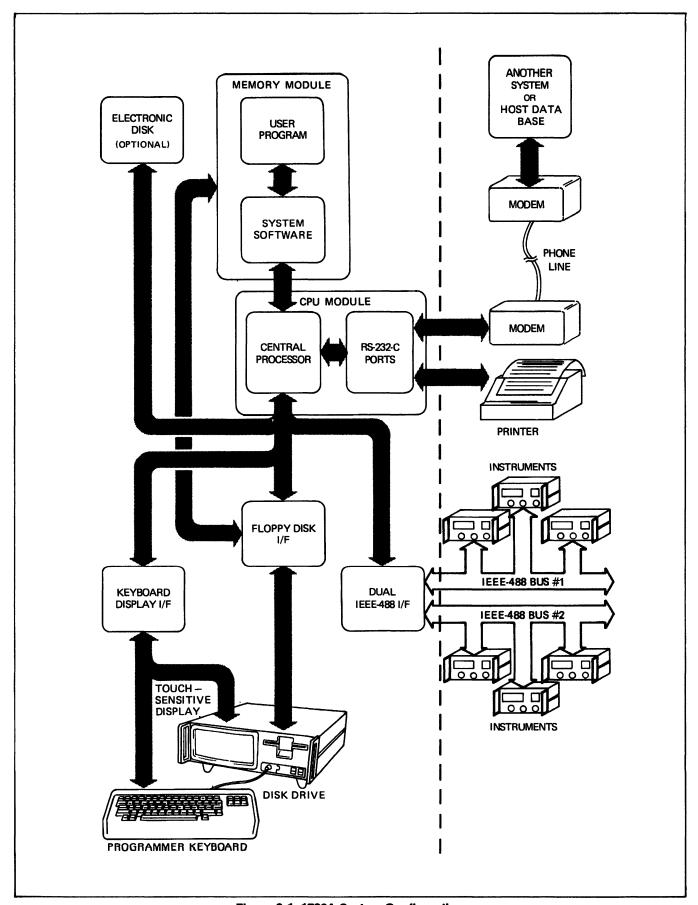

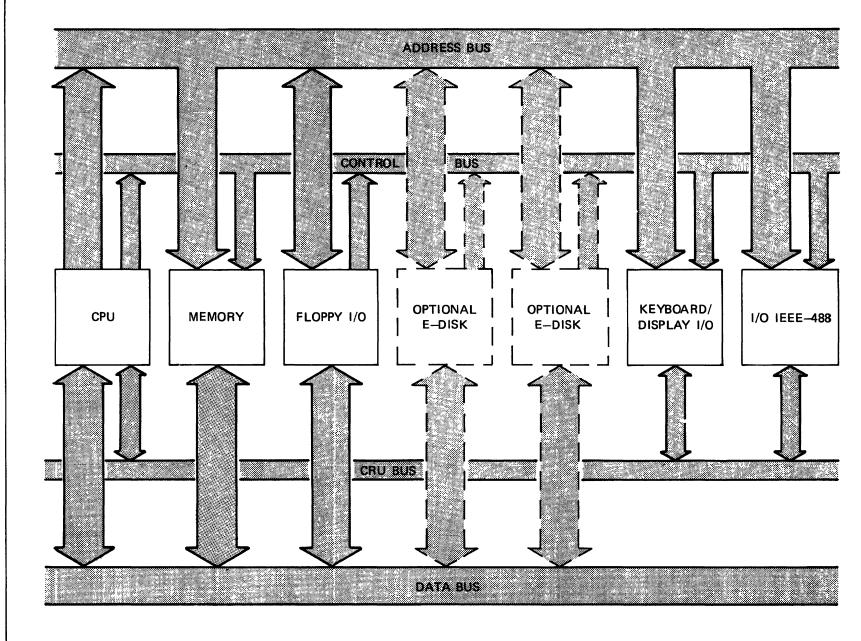

|            | 2-1.<br>2-3.<br>2-8.<br>2-10.<br>2-12.<br>2-14.<br>2-16.<br>2-18.<br>2-20.<br>2-22.<br>2-25.<br>2-27.   | INTRODUCTION  OVERALL FUNCTIONAL DESCRIPTION  System Software  32K Word Main Memory  Control of Peripheral Devices  Data Processing  Serial Data Capability  Floppy Disk Storage  Programmer Keyboard and Touch-Sensitive Display  Bus Structure  Optional Electronic Disk  Interrupts | 2-1<br>2-1<br>2-1<br>2-3<br>2-3<br>2-3<br>2-3<br>2-3<br>2-3<br>2-3<br>2-3<br>2-3         |

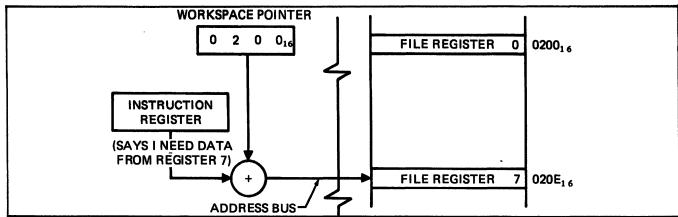

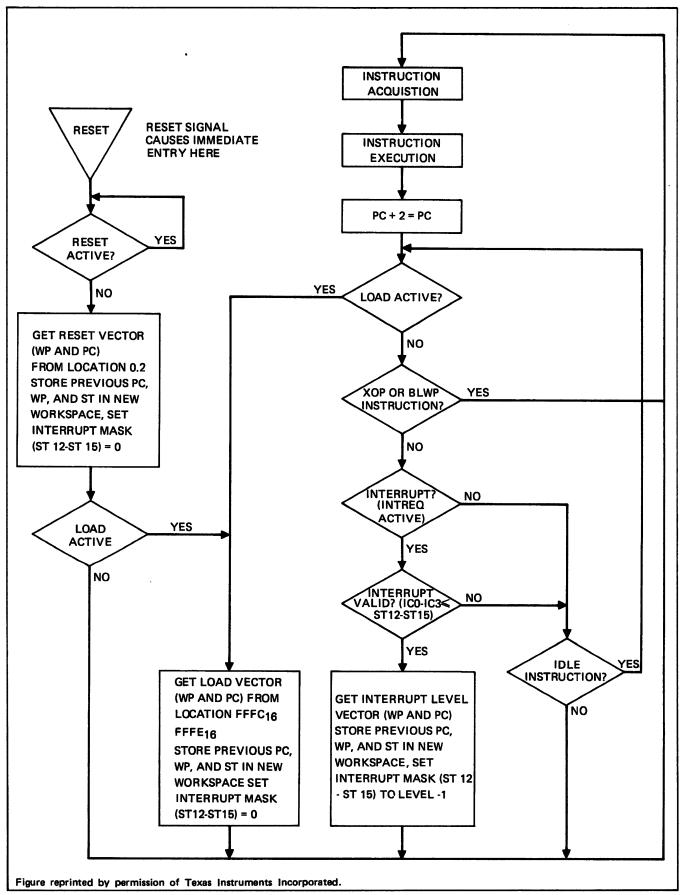

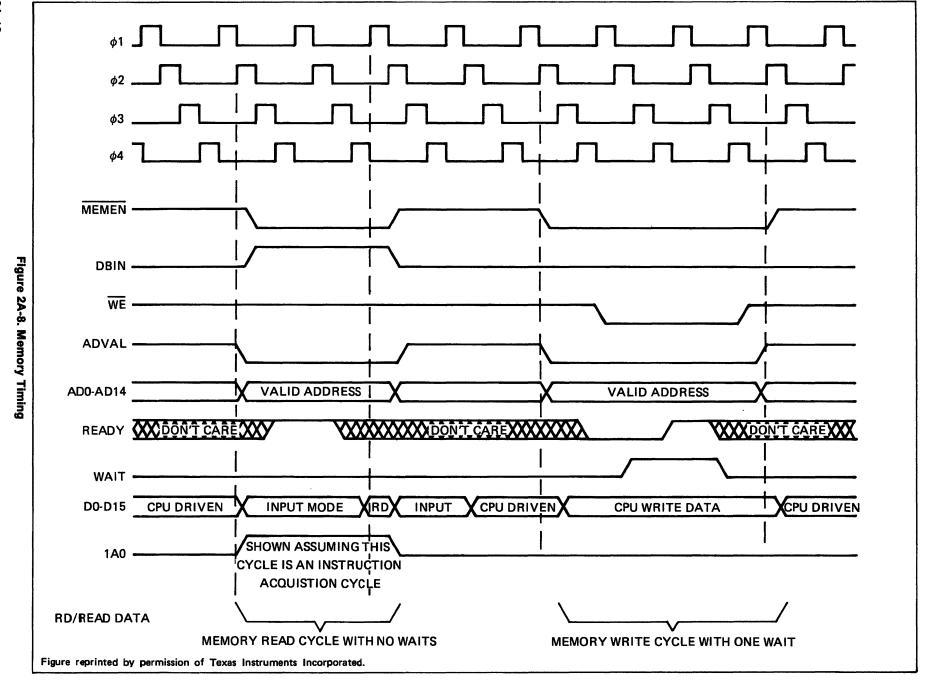

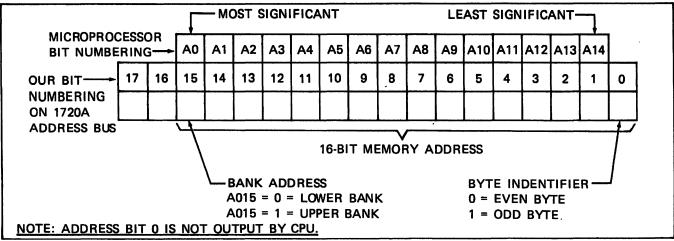

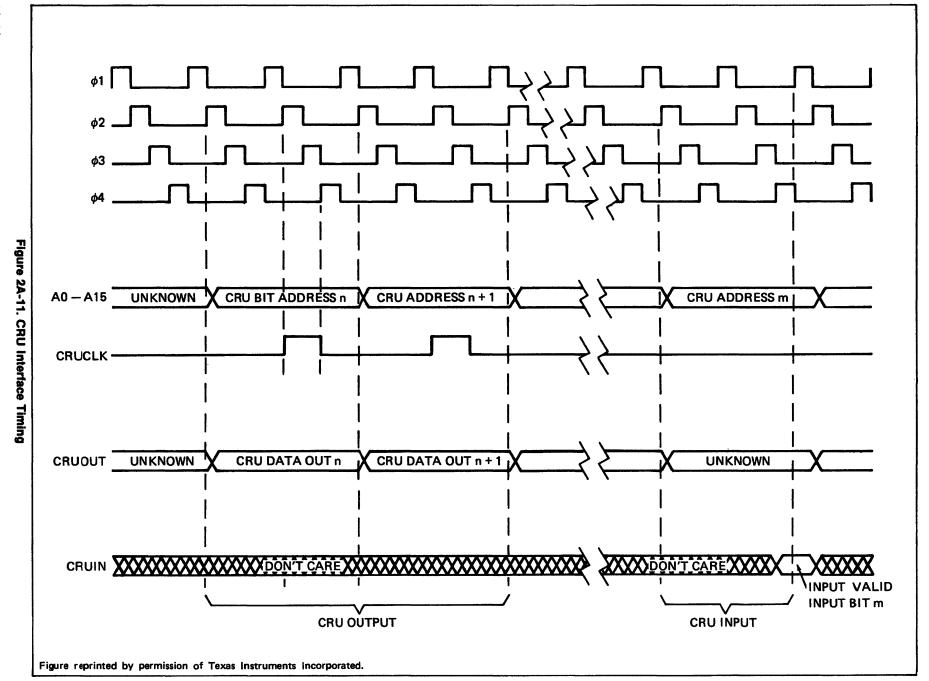

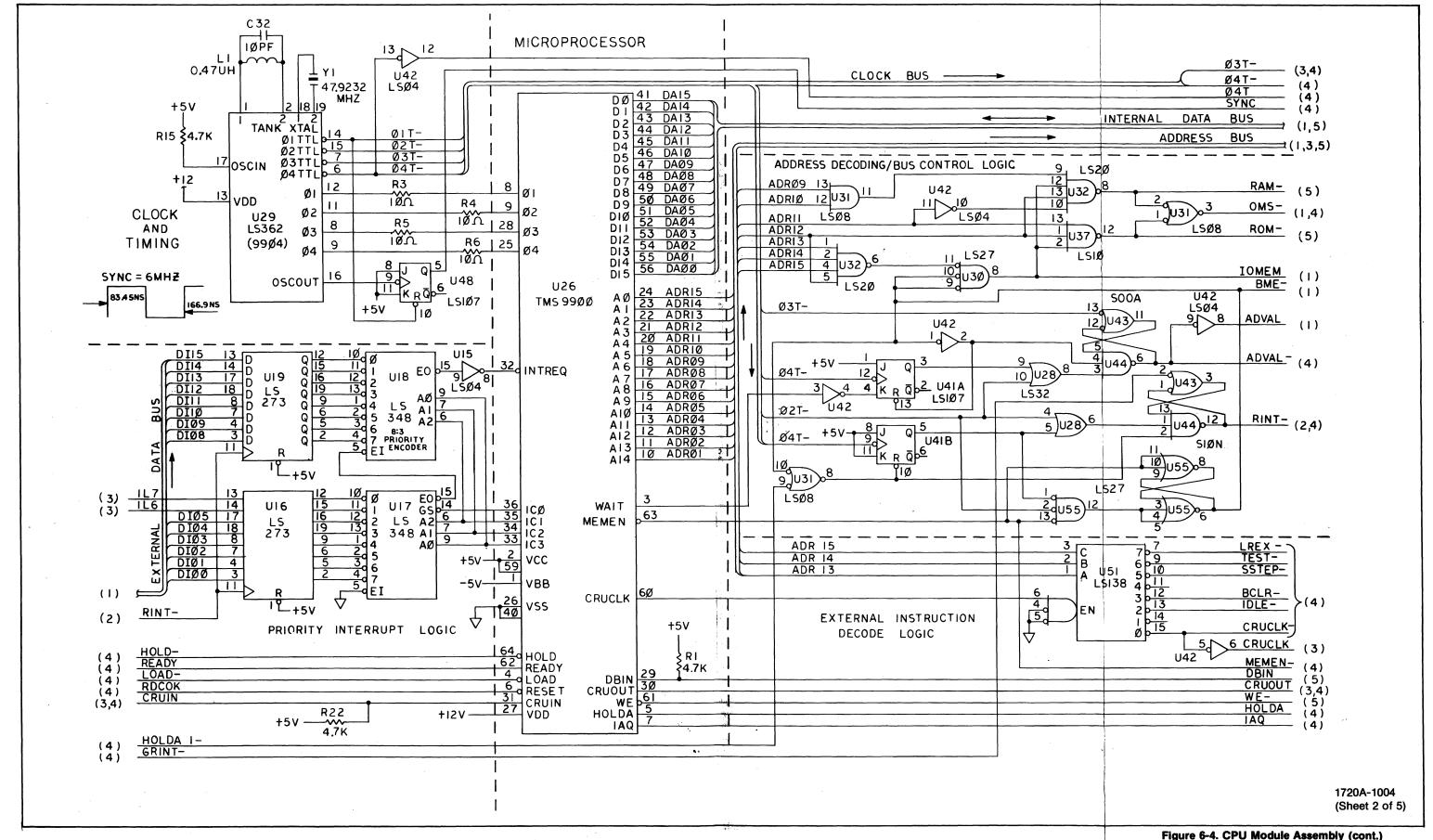

| 2 <b>A</b> | 2A-1.<br>2A-6.<br>2A-7.<br>2A-10.<br>2A-12.<br>2A-14.<br>2A-17.<br>2A-22.<br>2A-24.<br>2A-28.<br>2A-34. | INTRODUCTION DECODING AND EXECUTING INSTRUCTIONS Overview Workspace Registers Internal Registers Workspace Register File Instruction Cycle MEMORY DATA TRANSFERS MEMORY MAPPED I/O OPERATIONS CRU IN/OUT DATA TRANSFERS ELECTRONIC DISK DATA TRANSFERS RESPONSE TO INTERUPTS           | . 2A-1<br>. 2A-1<br>. 2A-3<br>. 2A-4<br>. 2A-4<br>. 2A-4<br>. 2A-5<br>. 2A-12<br>. 2A-12 |

| SECTION |                  | TITLE                                         | PAGE    |

|---------|------------------|-----------------------------------------------|---------|

|         | 2A-36.           | Device Interrupts During RINT                 | . 2A-13 |

|         | 2A-39.           | RESET and LOAD                                |         |

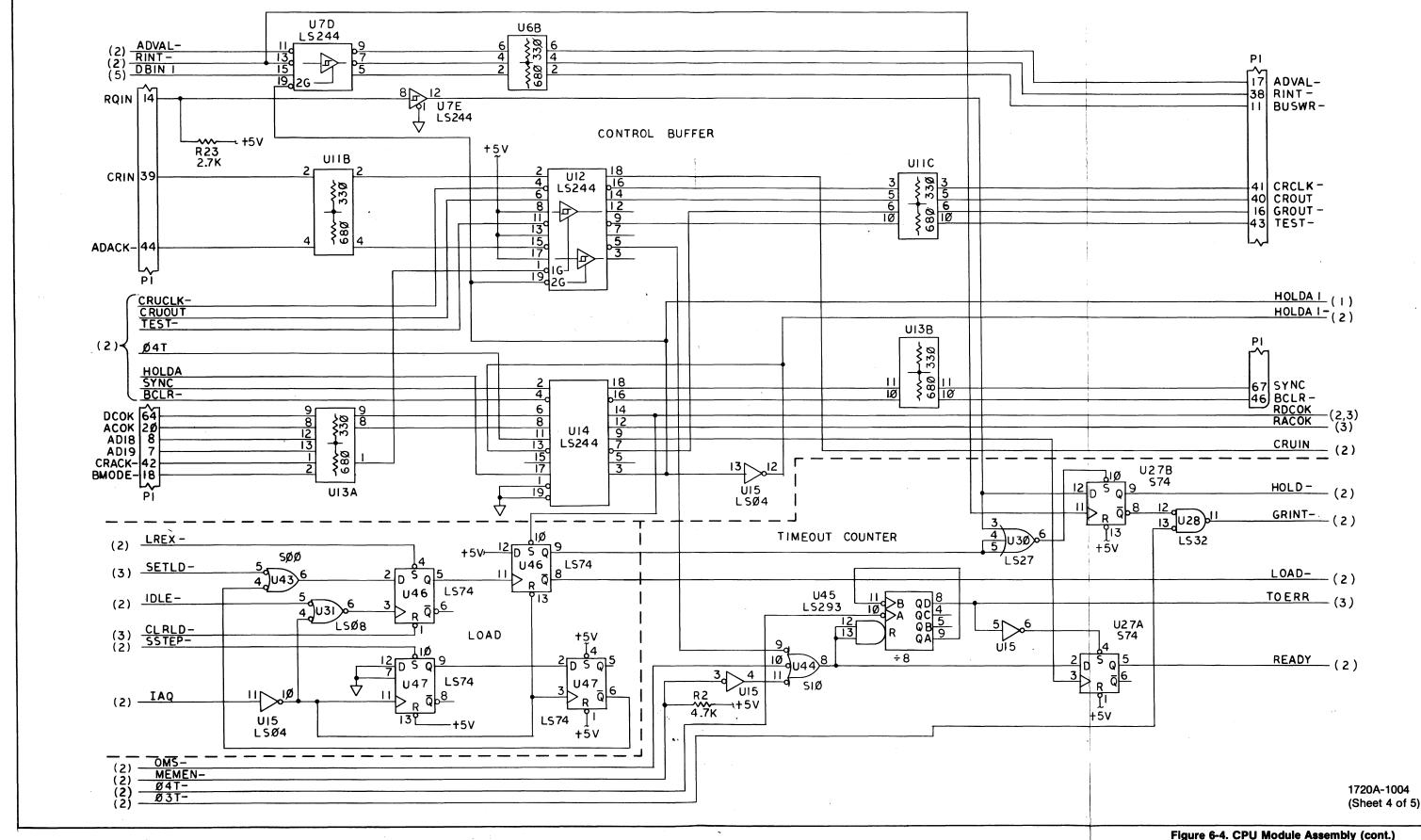

|         | 2A-43.           | RESPONSE TO DMA REQUESTS                      |         |

|         | 2A-46.           | EXTERNAL INSTRUCTION LOGIC                    |         |

|         | 2A-48.           | CPU CLOCK AND SYSTEM SYNC                     |         |

|         | 2A-50.           | TIME-OUT ERROR                                |         |

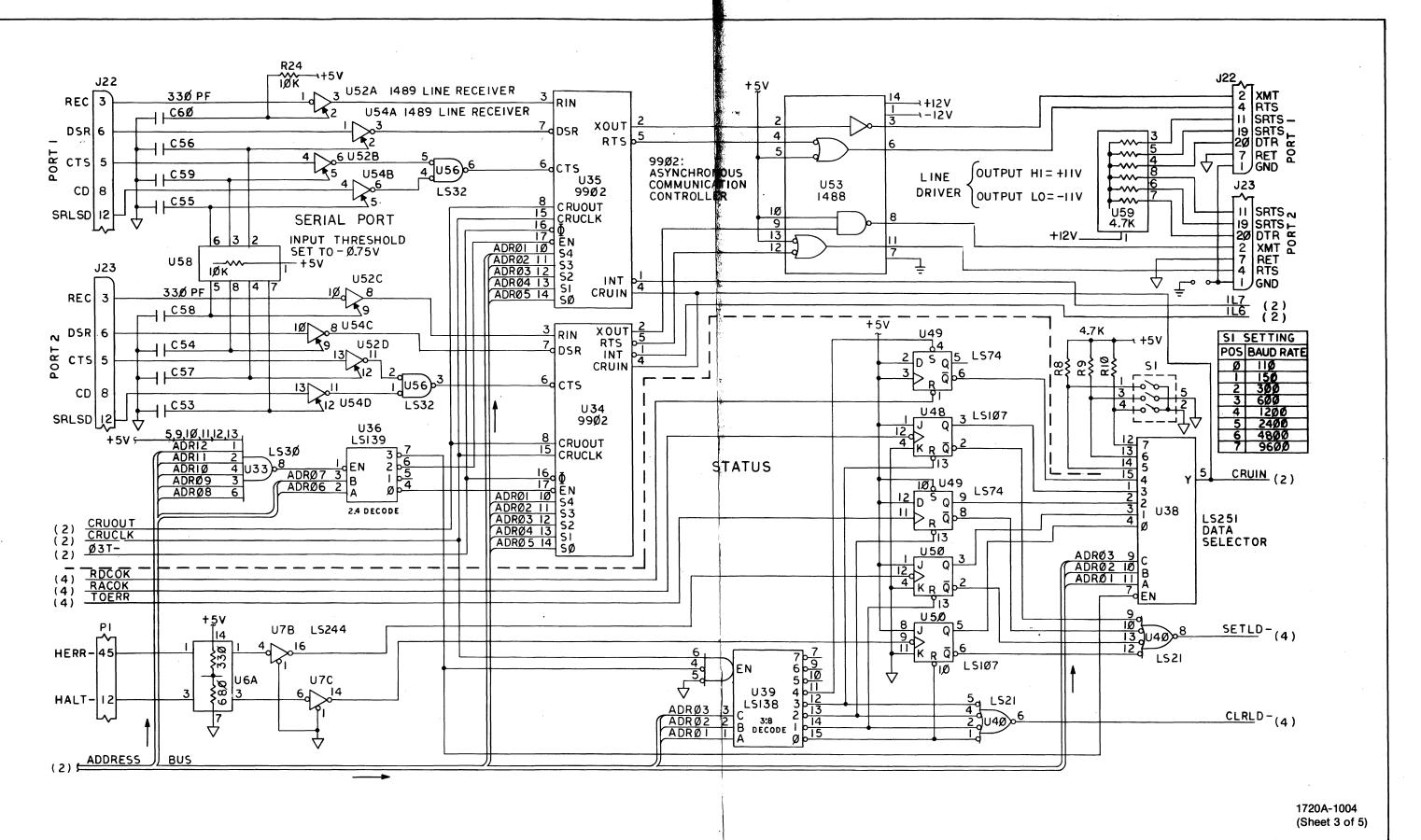

|         | 2A-53.           | RS-232-C SERIAL PORTS                         |         |

|         | 2A-58.           | CPU MODULE STATUS REGISTER                    |         |

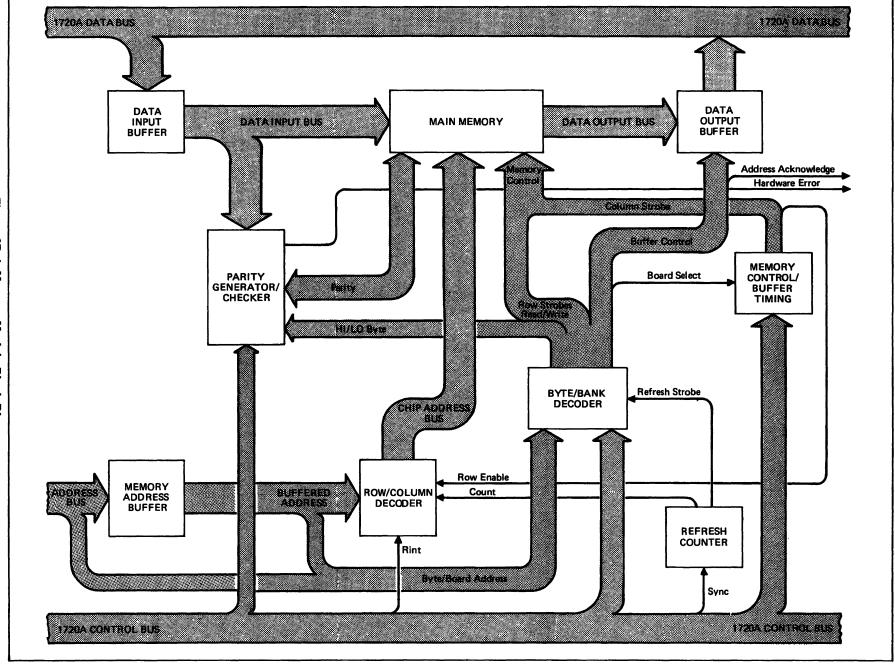

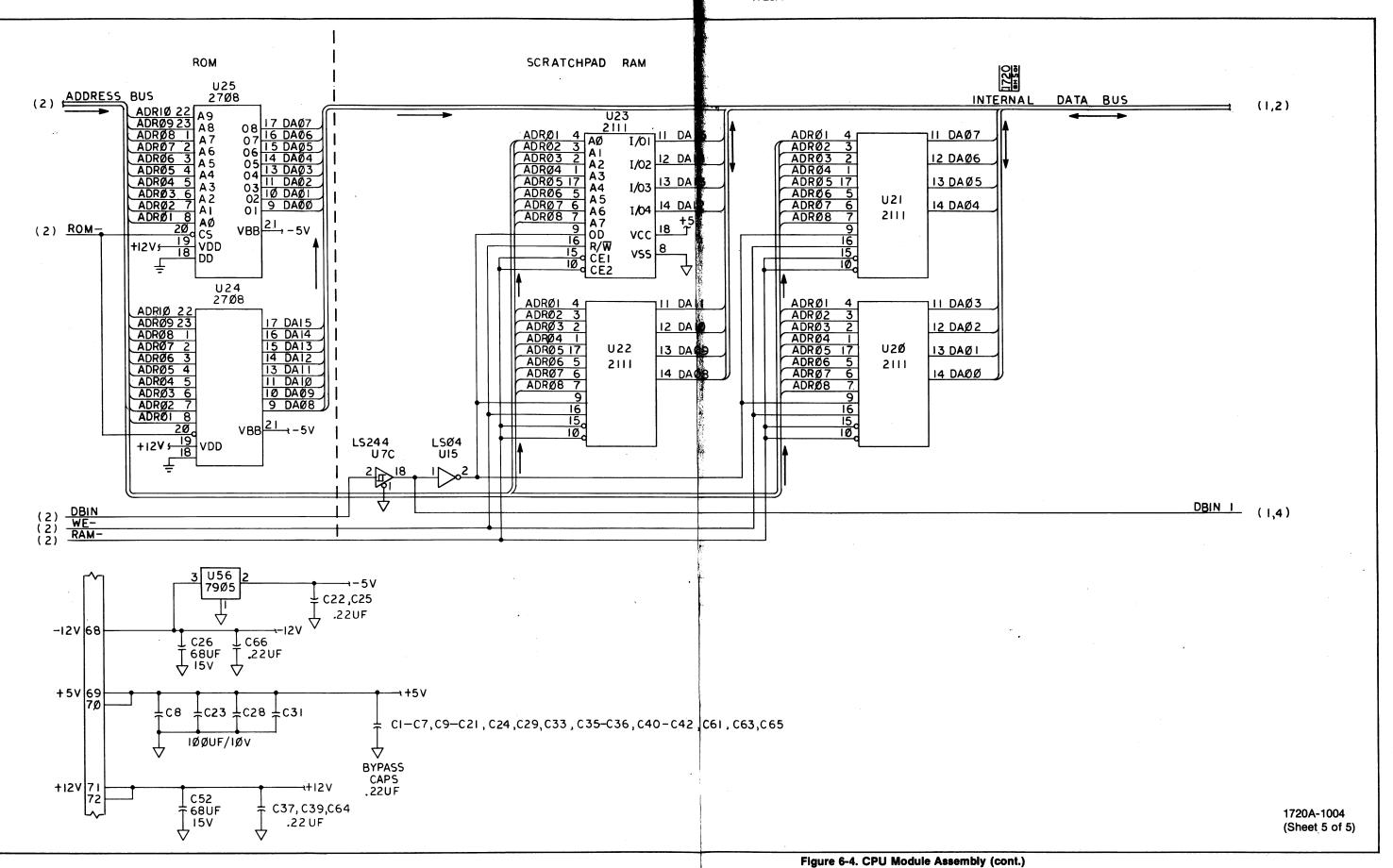

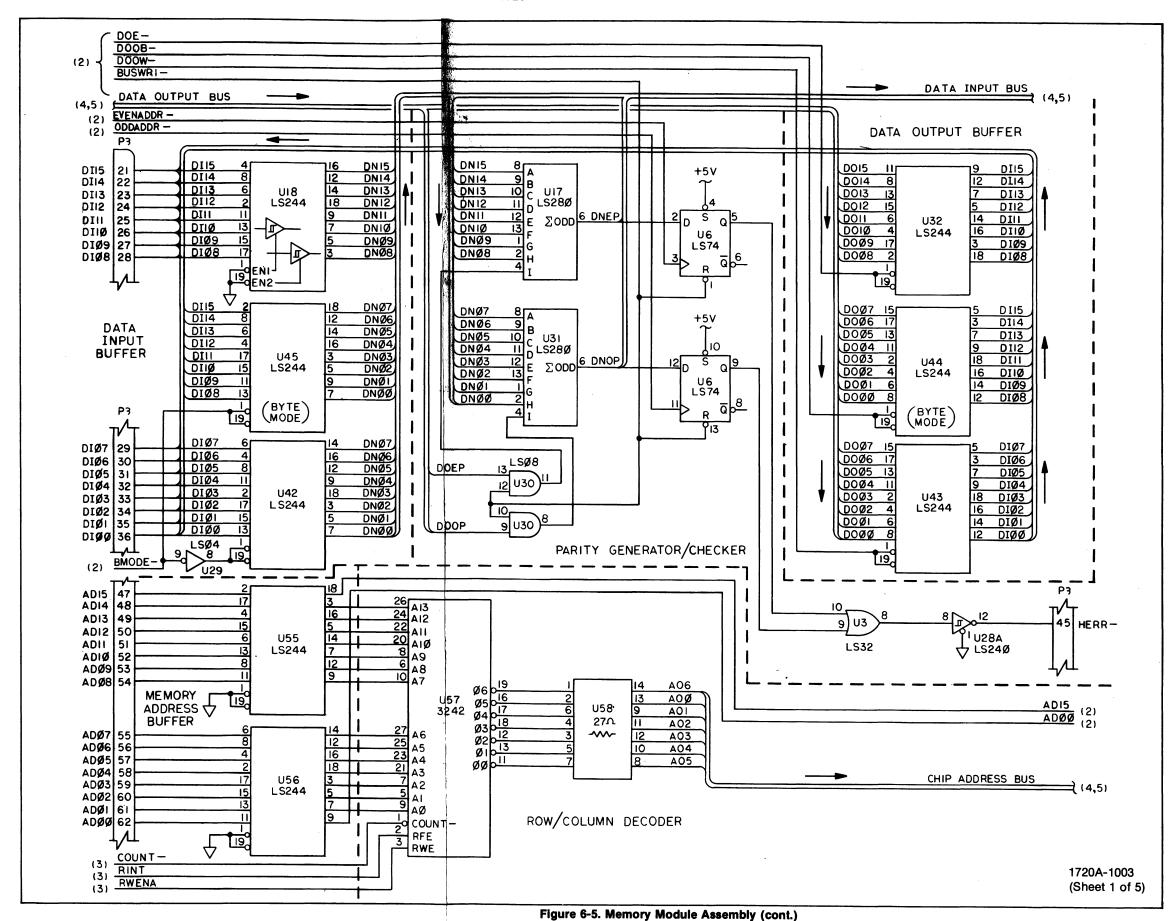

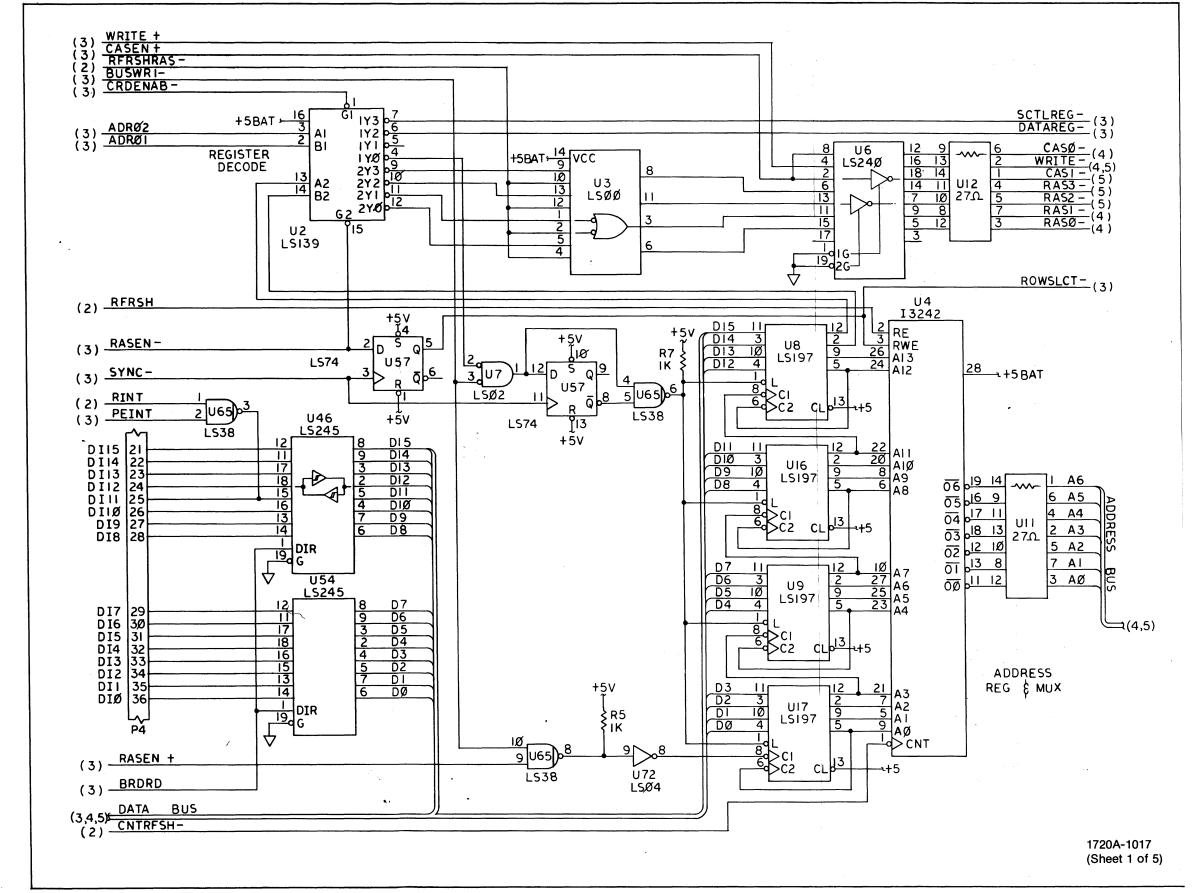

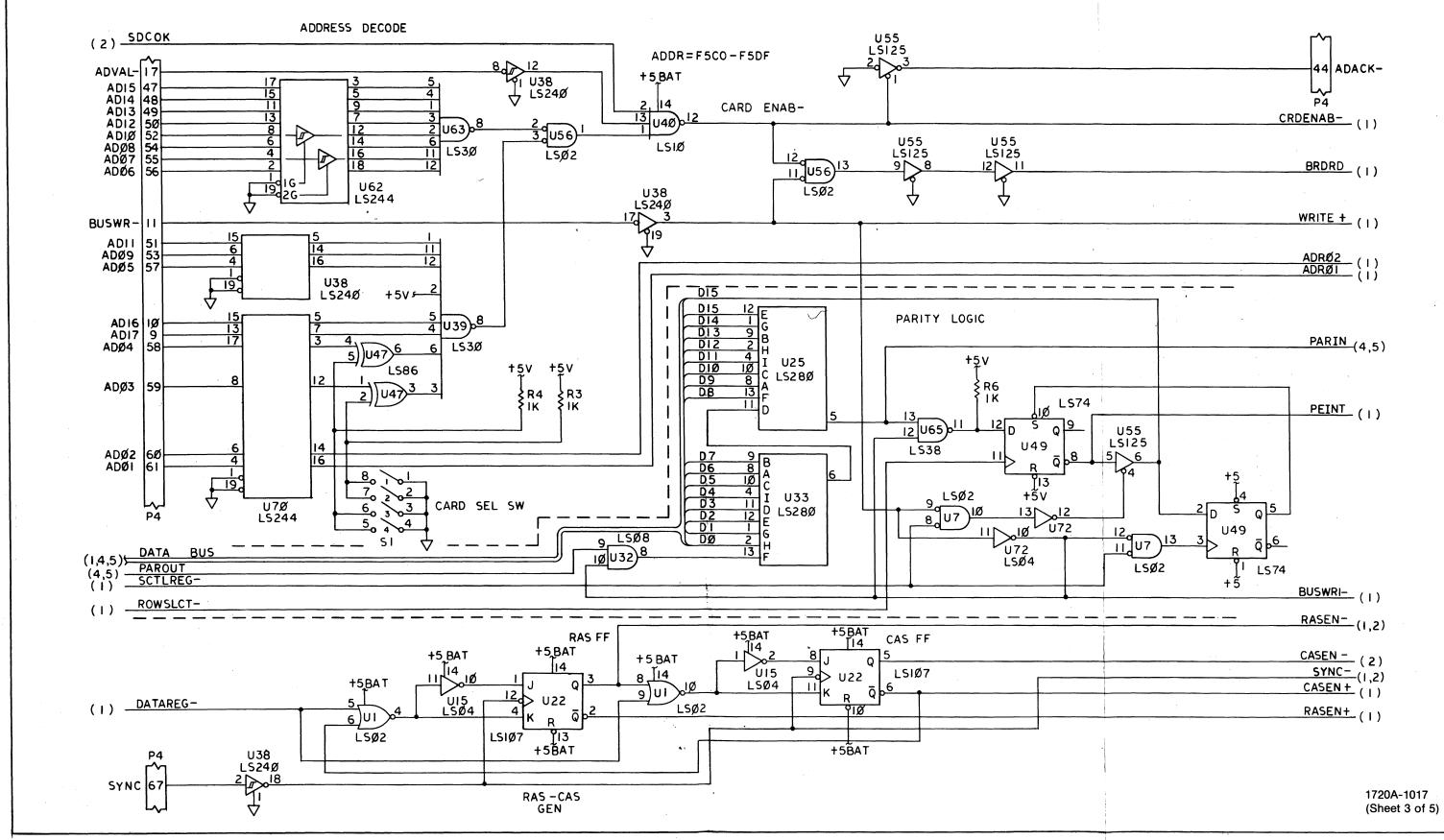

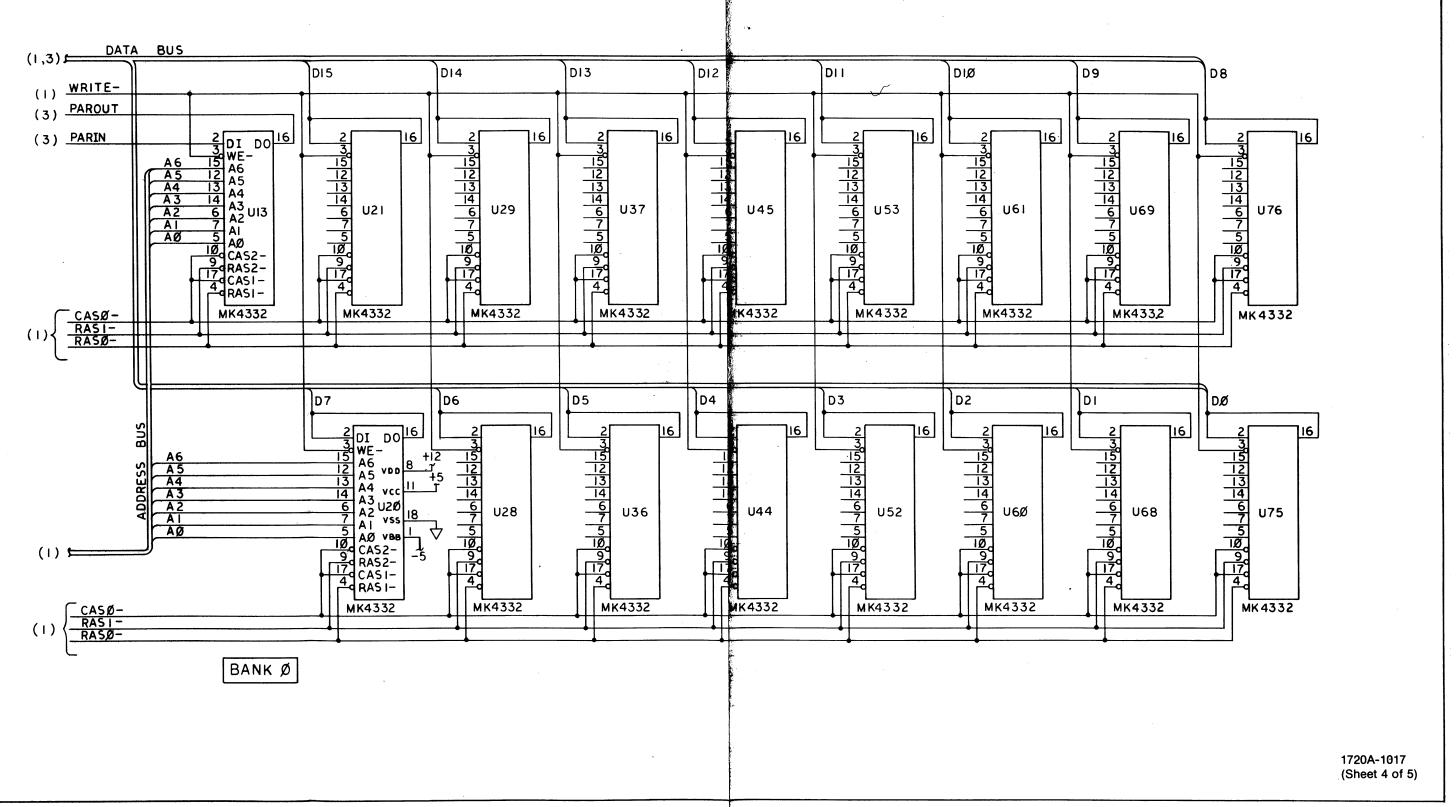

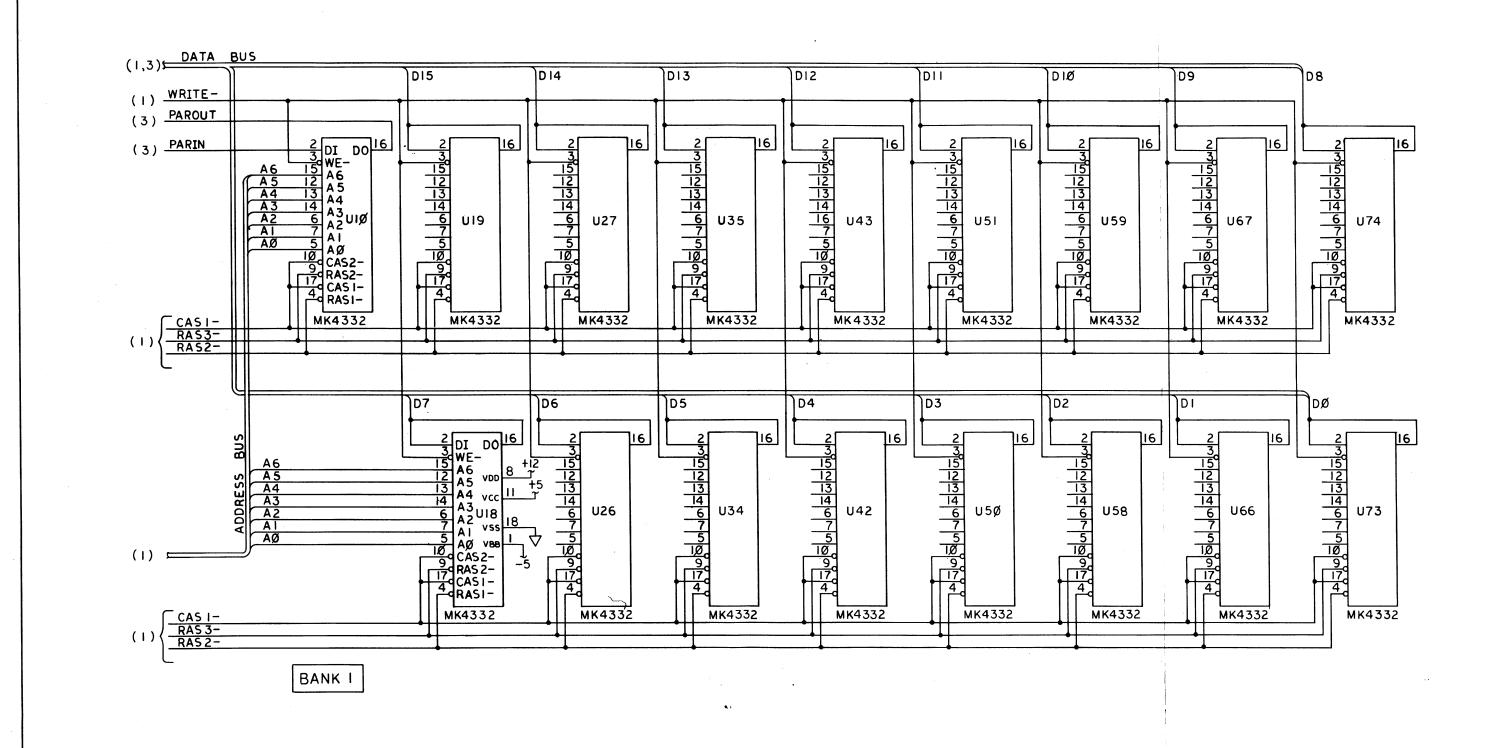

| 2B      | MEMO             | RY MODULE                                     | 2B-1    |

|         |                  | INTRODUCTION                                  |         |

|         | 2B-1.            |                                               |         |

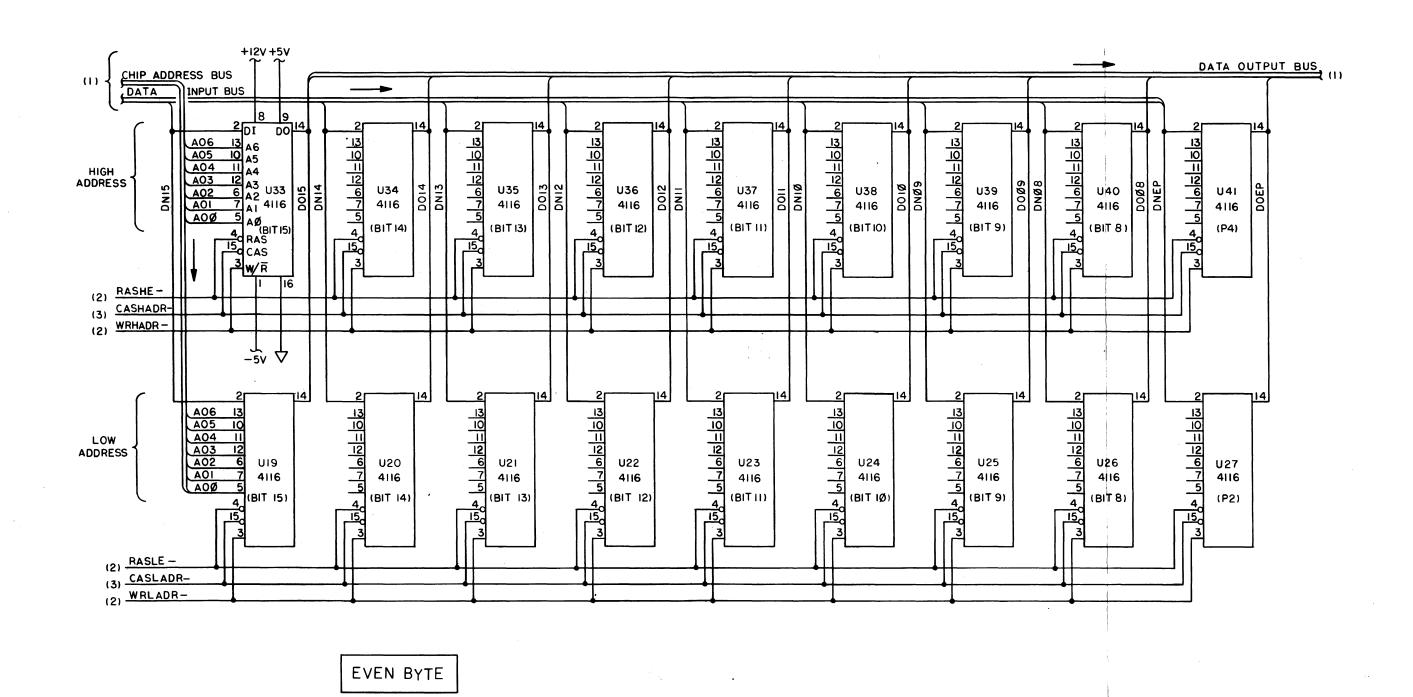

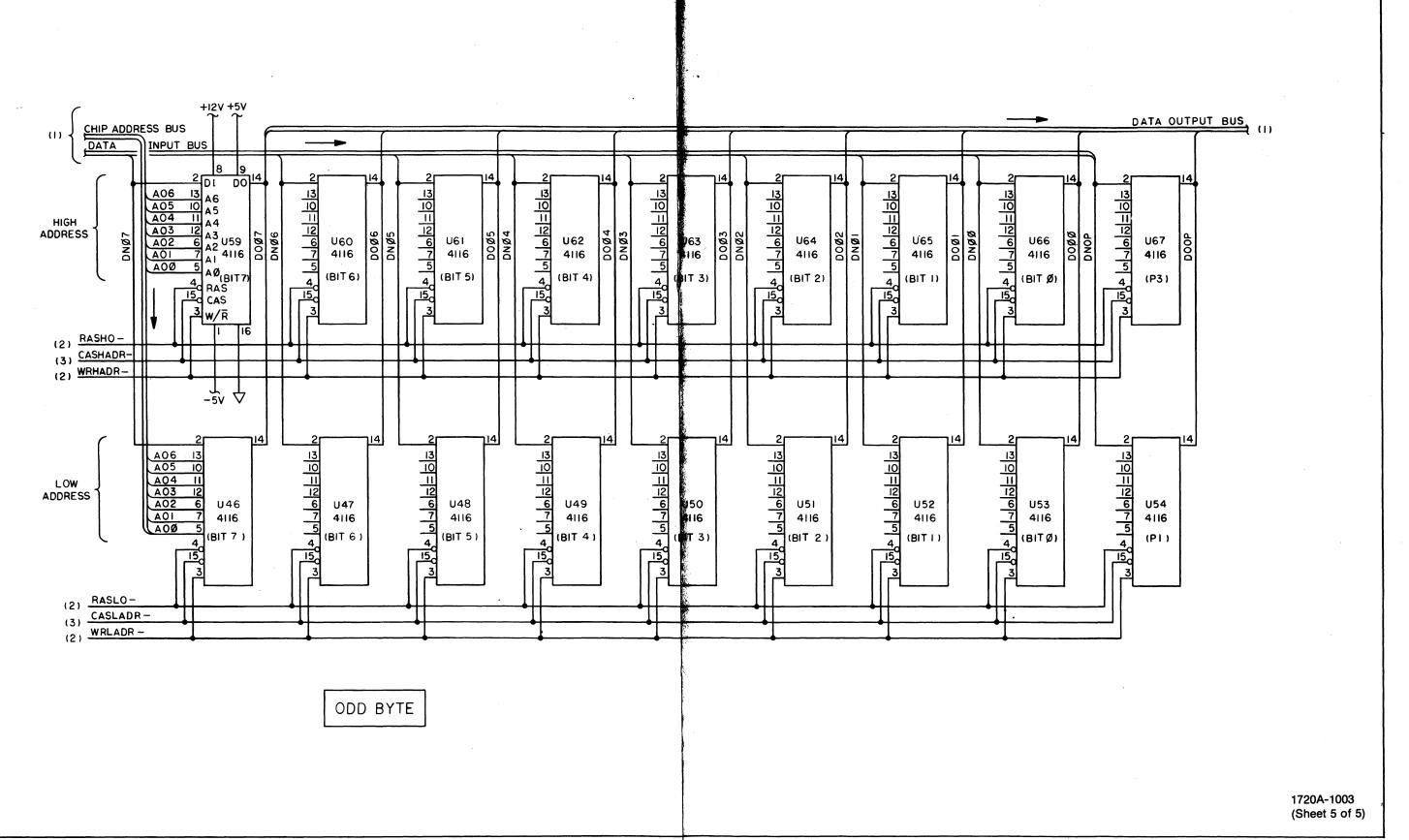

|         | 2B-4.            | MAIN MEMORY                                   |         |

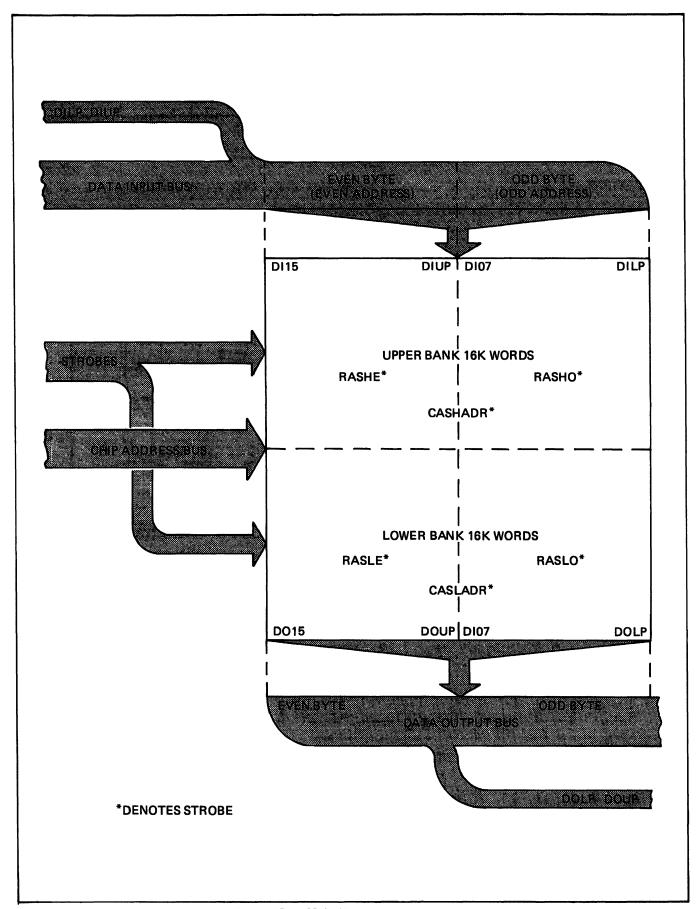

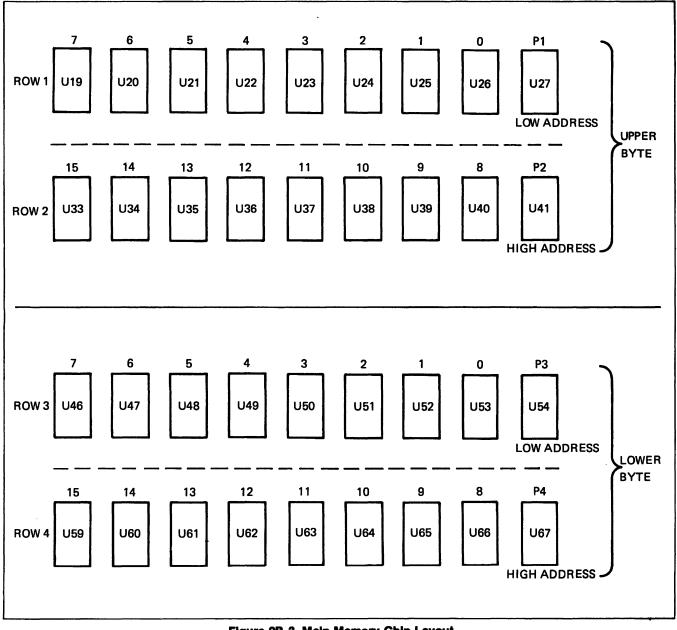

|         | 2B-5.<br>2B-7.   | Dynamic Ram                                   |         |

|         | 2B-7.<br>2B-9.   | Independent Upper and Lower Address Banks     |         |

|         |                  |                                               |         |

|         | 2B-11.           | 7-Bit Chip Address Bus                        |         |

|         | 2B-13.           | Read and Write Operations                     |         |

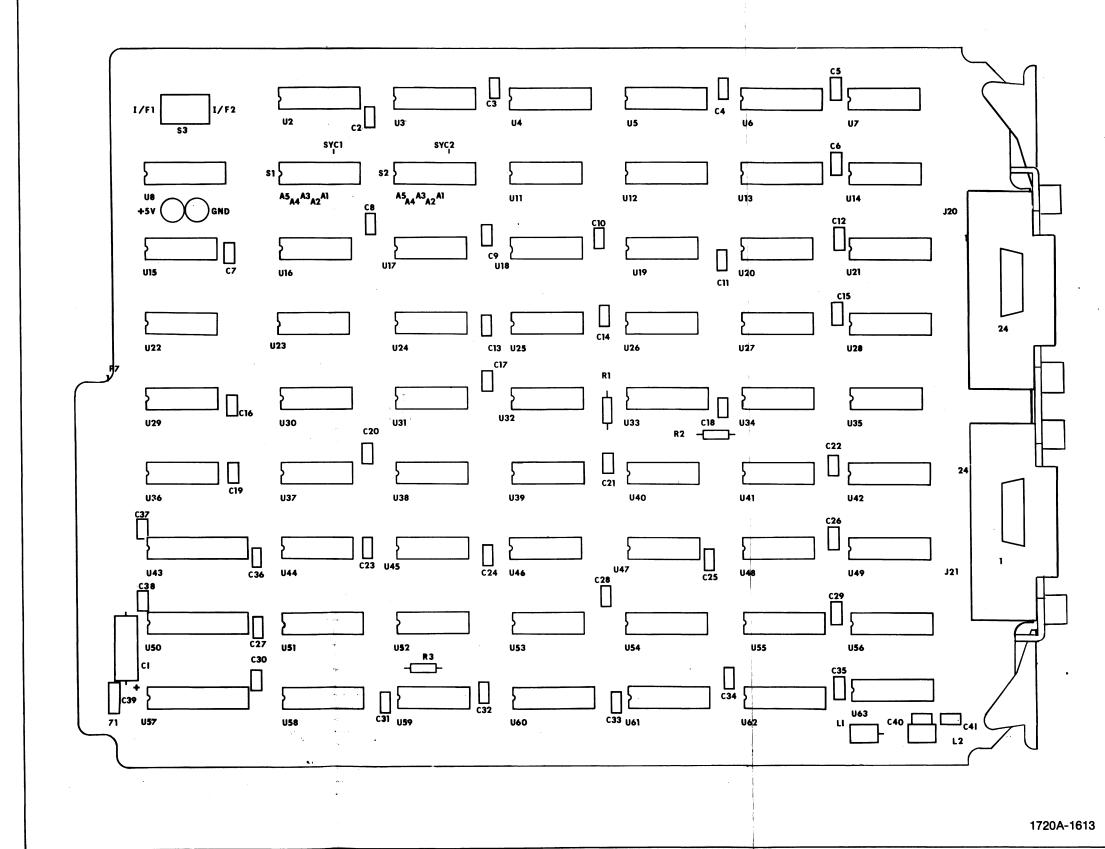

|         | 2B-17.<br>2B-19. | TRI-STATE BUFFERS                             |         |

|         | 2B-19.<br>2B-21. | Memory Address Buffer                         |         |

|         | 2B-21.<br>2B-23. |                                               |         |

|         | 2B-23.<br>2B-26. | Data Input Buffer                             |         |

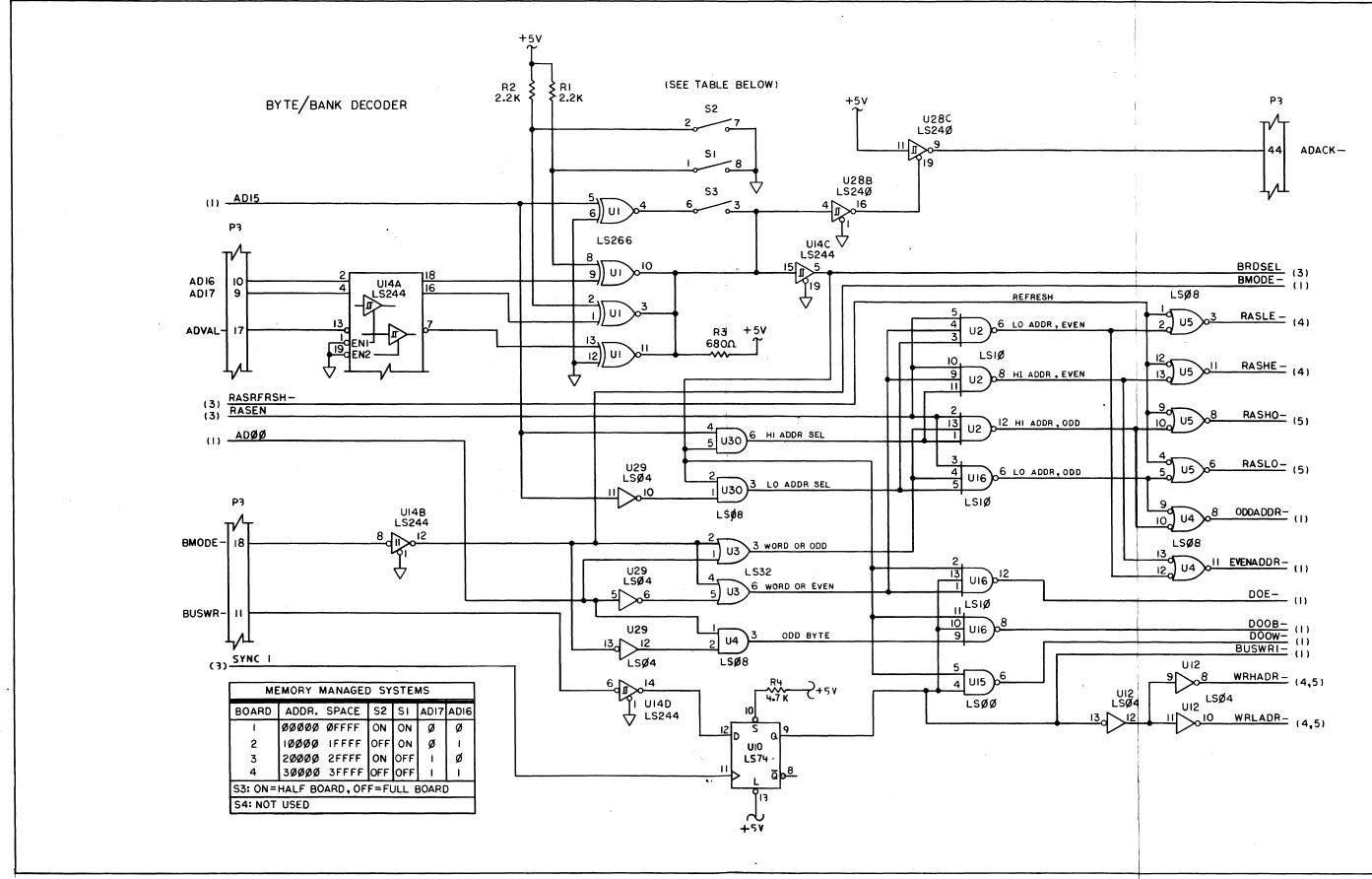

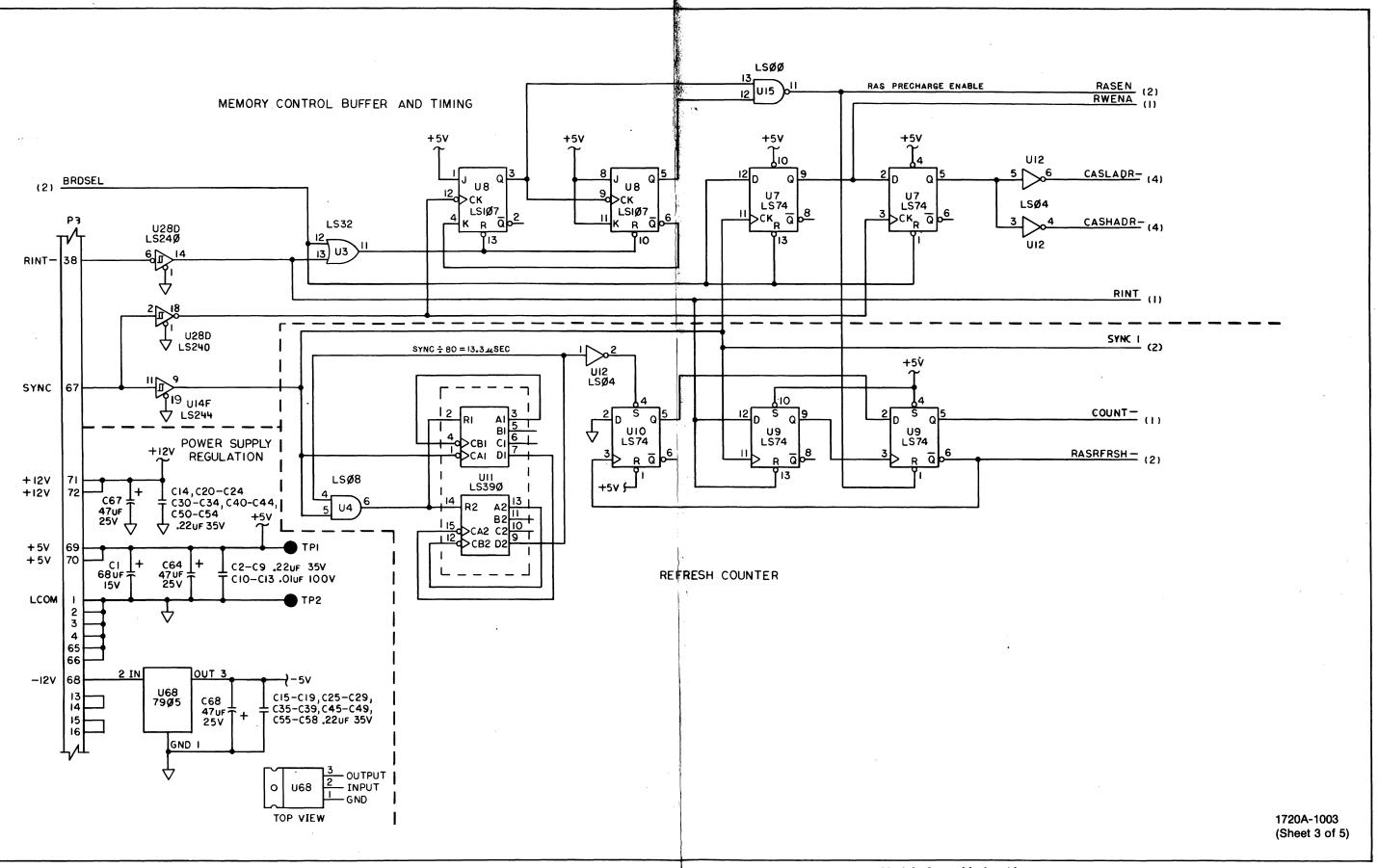

|         | 2B-28.           | ON BOARD STROBE GENERATION                    |         |

|         | 2B-28.<br>2B-30. | Byte/Bank Decoder                             |         |

|         | 2B-30.<br>2B-38. | Memory Control Buffer and Timing              |         |

|         | 2B-36.<br>2B-41. | CHIP ADDRESS MULTIPLEXING                     |         |

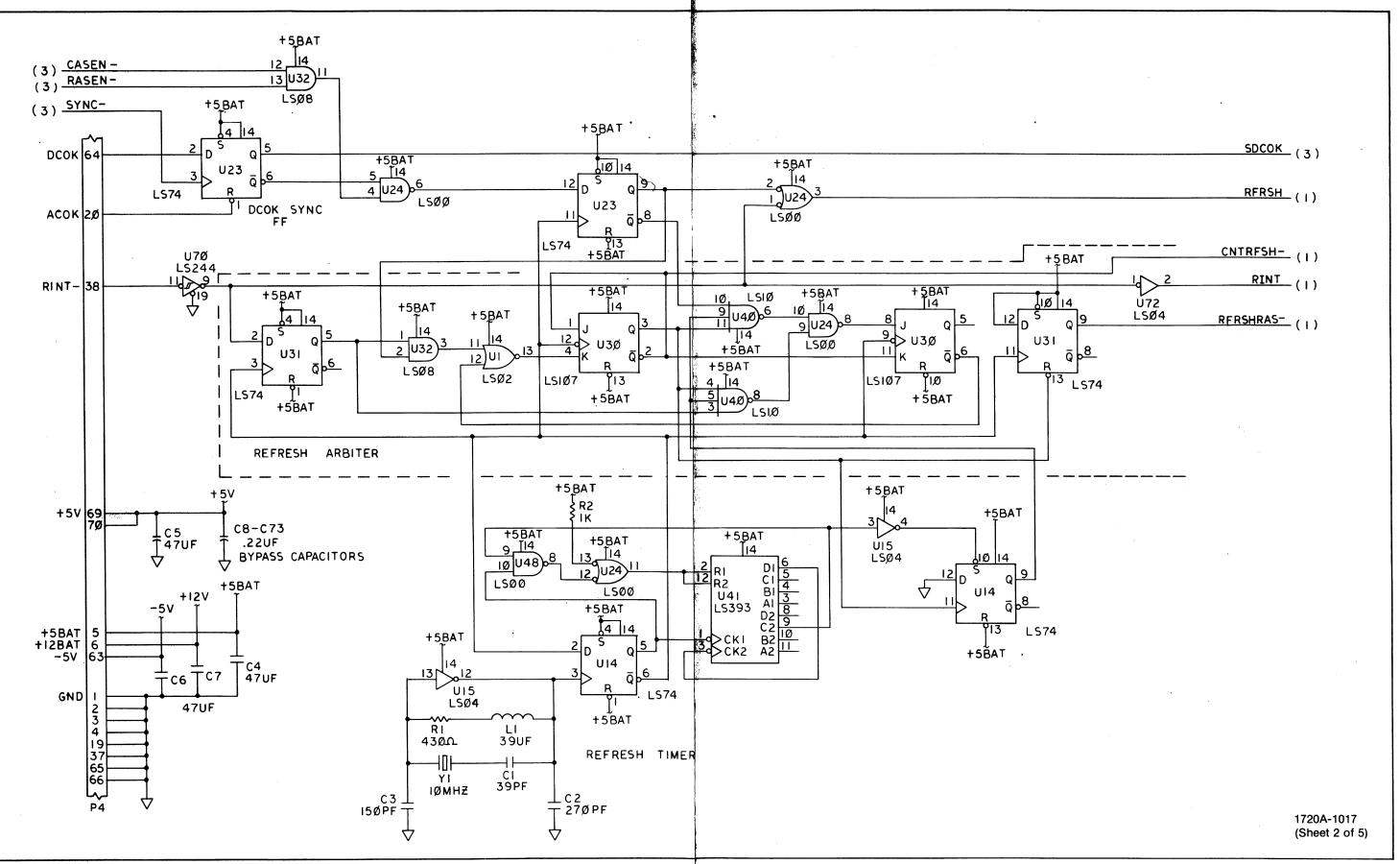

|         | 2B-41.           | TRANSPARENT REFRESH                           |         |

|         | 2B-47.           | Refresh Counter                               |         |

|         | 2B-49.           | Row Column Decoder                            |         |

|         | 2B-52.           | BYTE PARITY                                   |         |

|         | 2B-52.<br>2B-54. | Write Parity Generation                       |         |

|         | 2B-54.           | Read Parity Checking                          |         |

|         | 2B-58.           | SWITCH SELECTABLE BANKS                       |         |

|         |                  | •                                             |         |

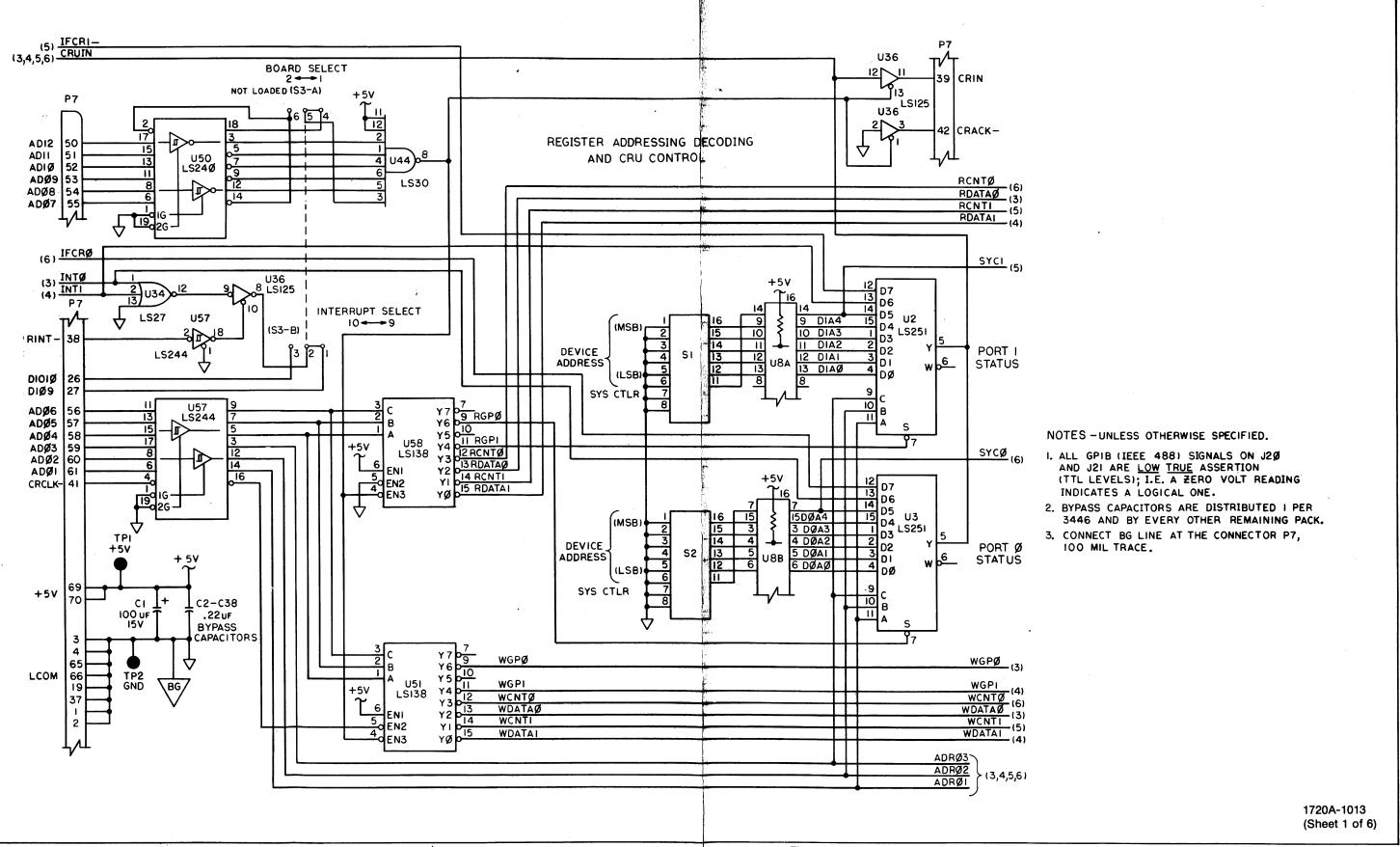

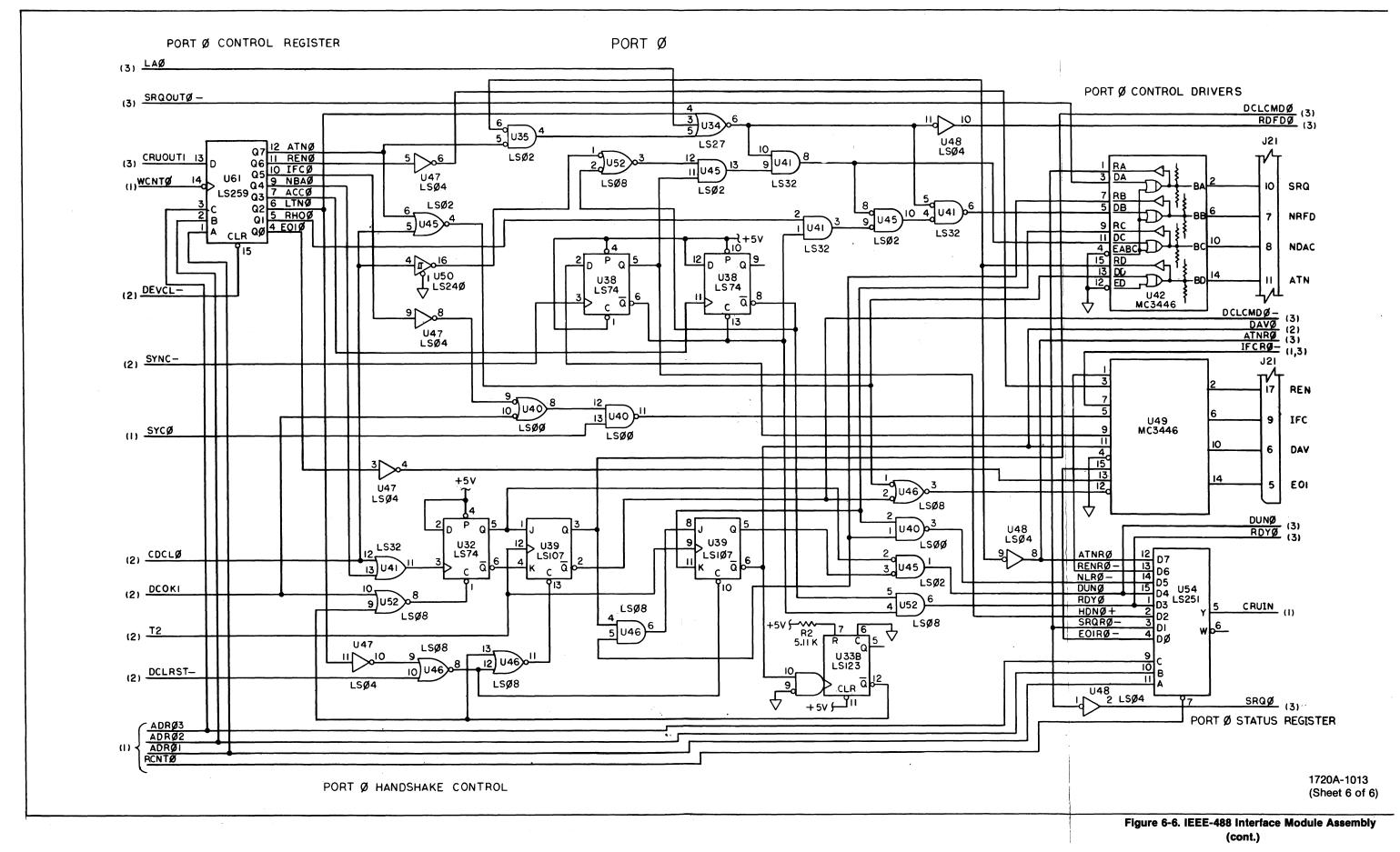

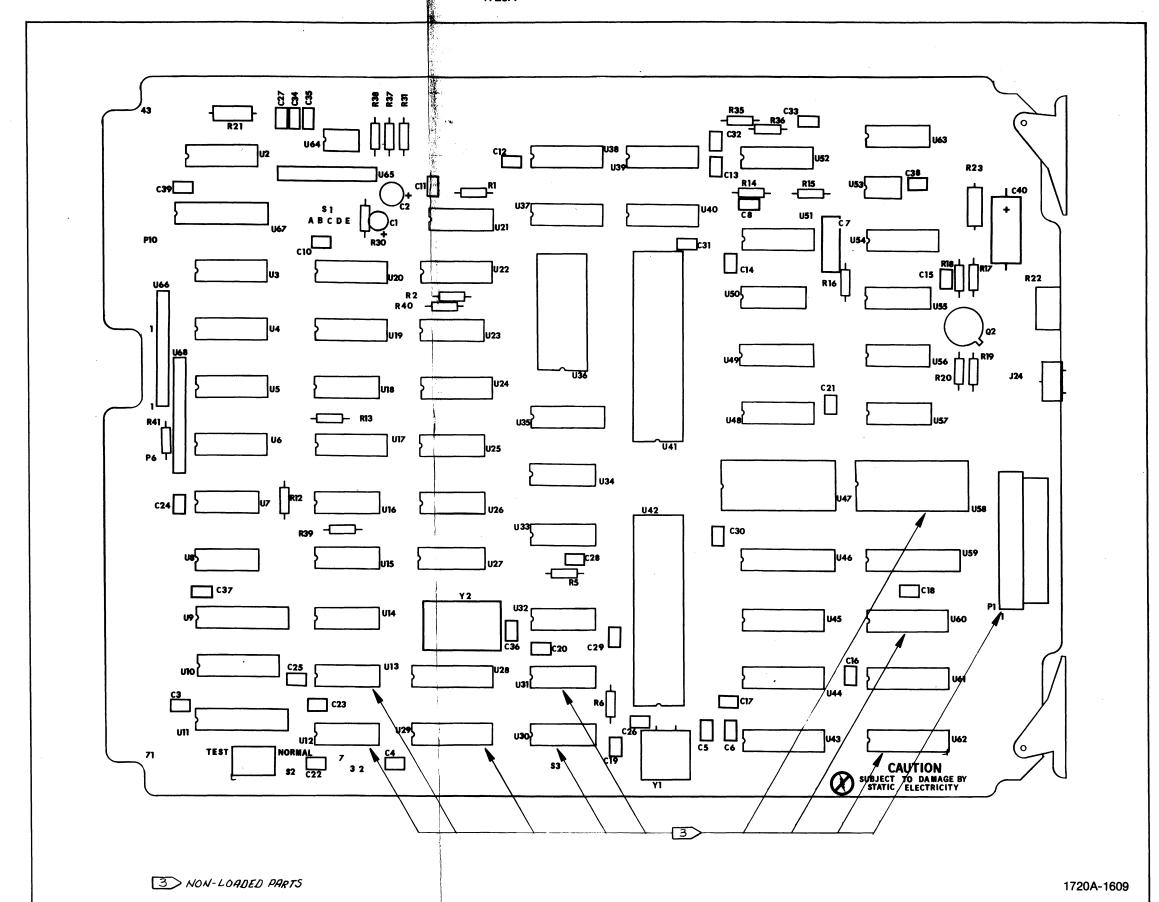

| 2C      | IEEE-4           | 88 INTERFACE MODULE                           | . 2C-1  |

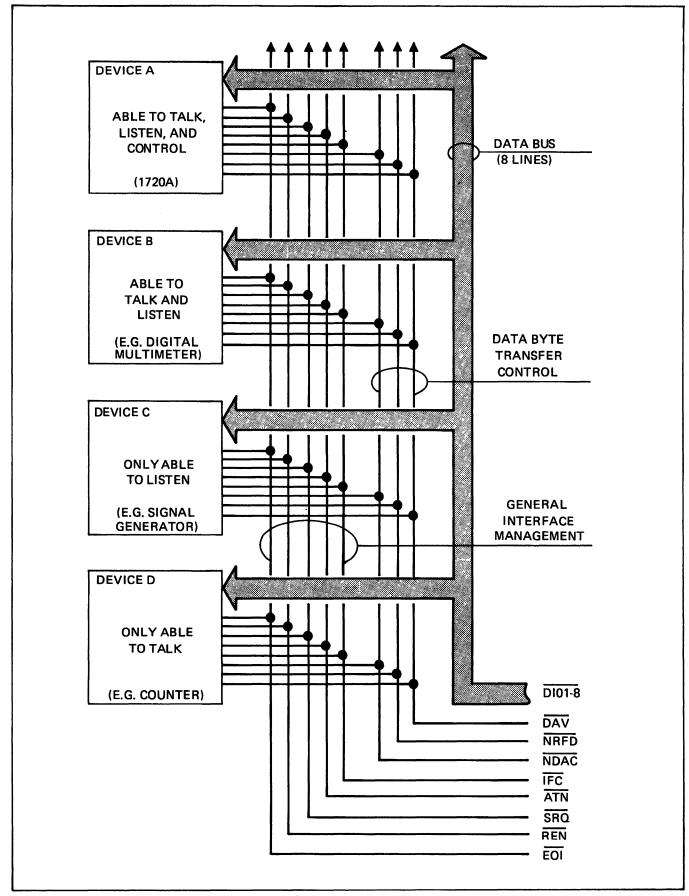

|         | 2C-1.            | INTRODUCTION                                  | . 2C-1  |

|         | 2C-3.            | INTRODUCTION TO THE IEEE-488 BUS              | . 2C-1  |

|         | 2C-5.            | Basic Concepts and Terms                      | . 2C-1  |

|         | 2C-13.           | Bus Operating Modes                           |         |

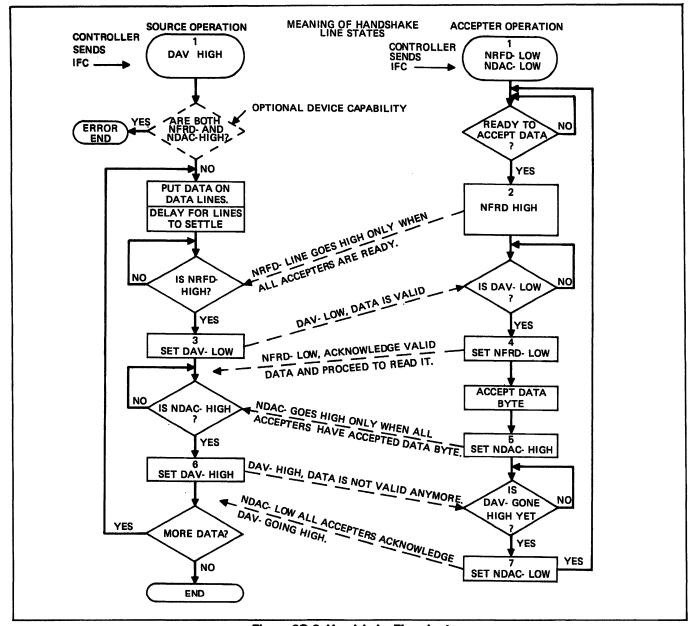

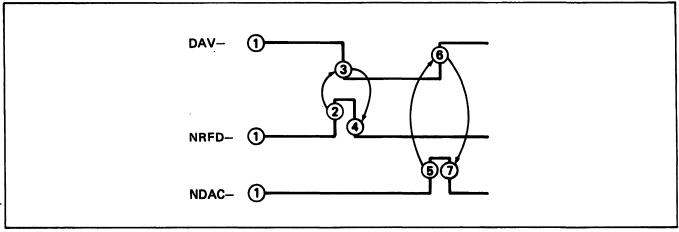

|         | 2C-20.           | Three-Wire Handshake                          | . 2C-2  |

|         | 2C-22.           | Operational Sequences                         |         |

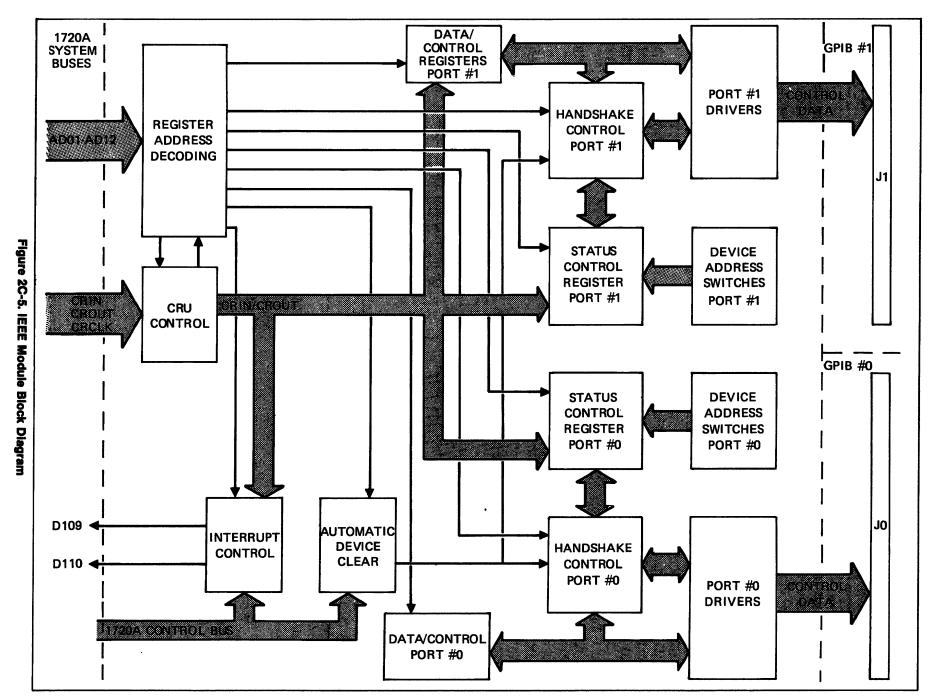

|         | 2C-26.           | IEEE-488 INTERFACE MODULE THEORY OF OPERATION |         |

|         | 2C-27.           | Introduction                                  |         |

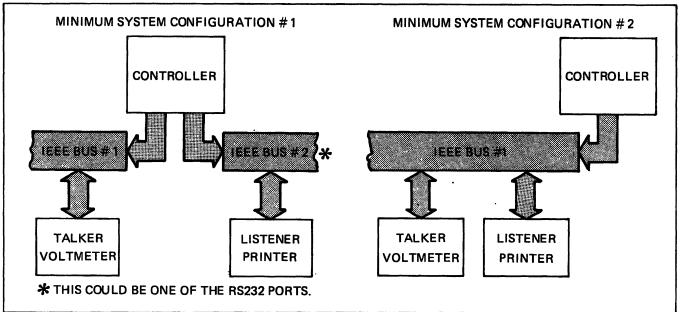

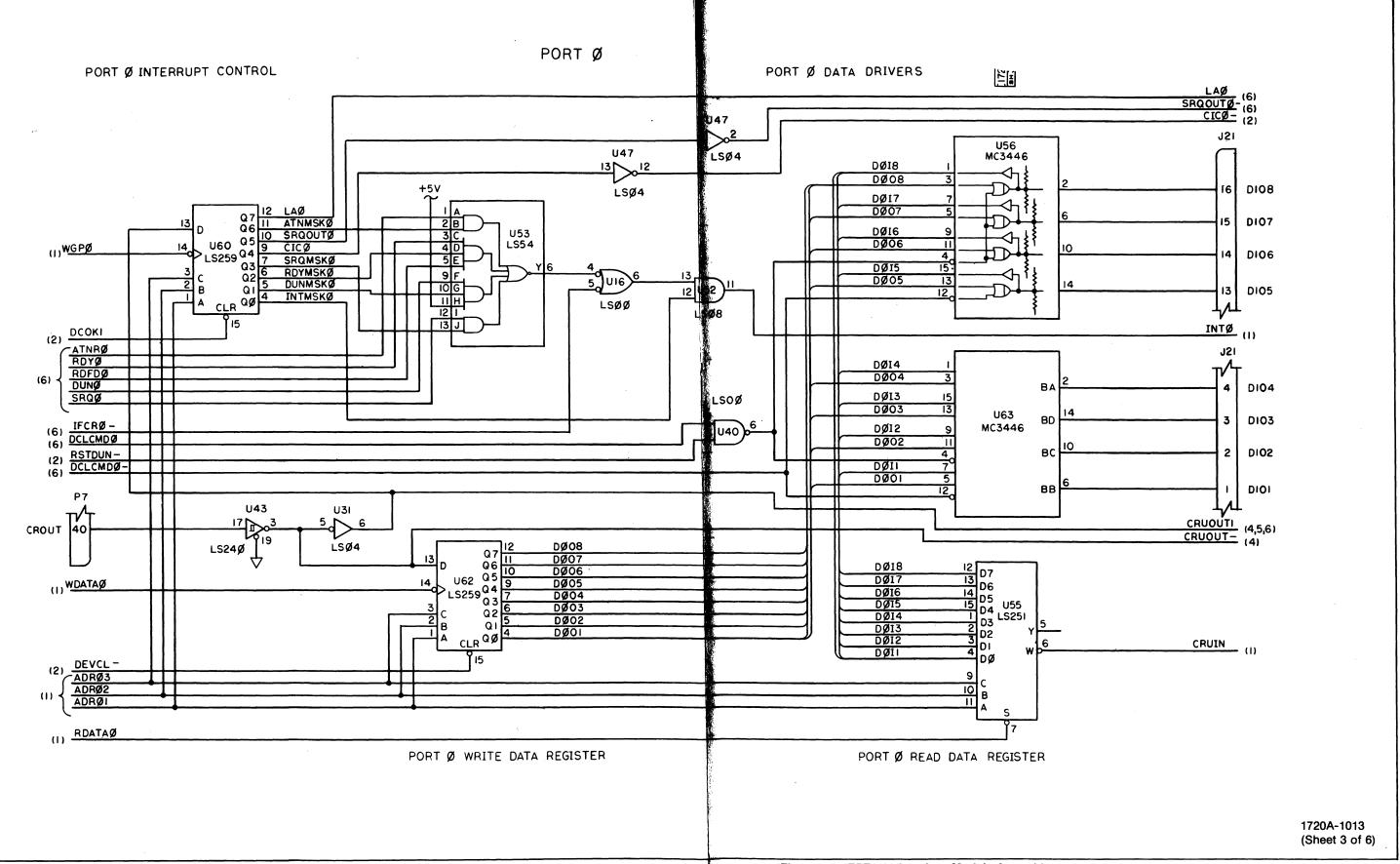

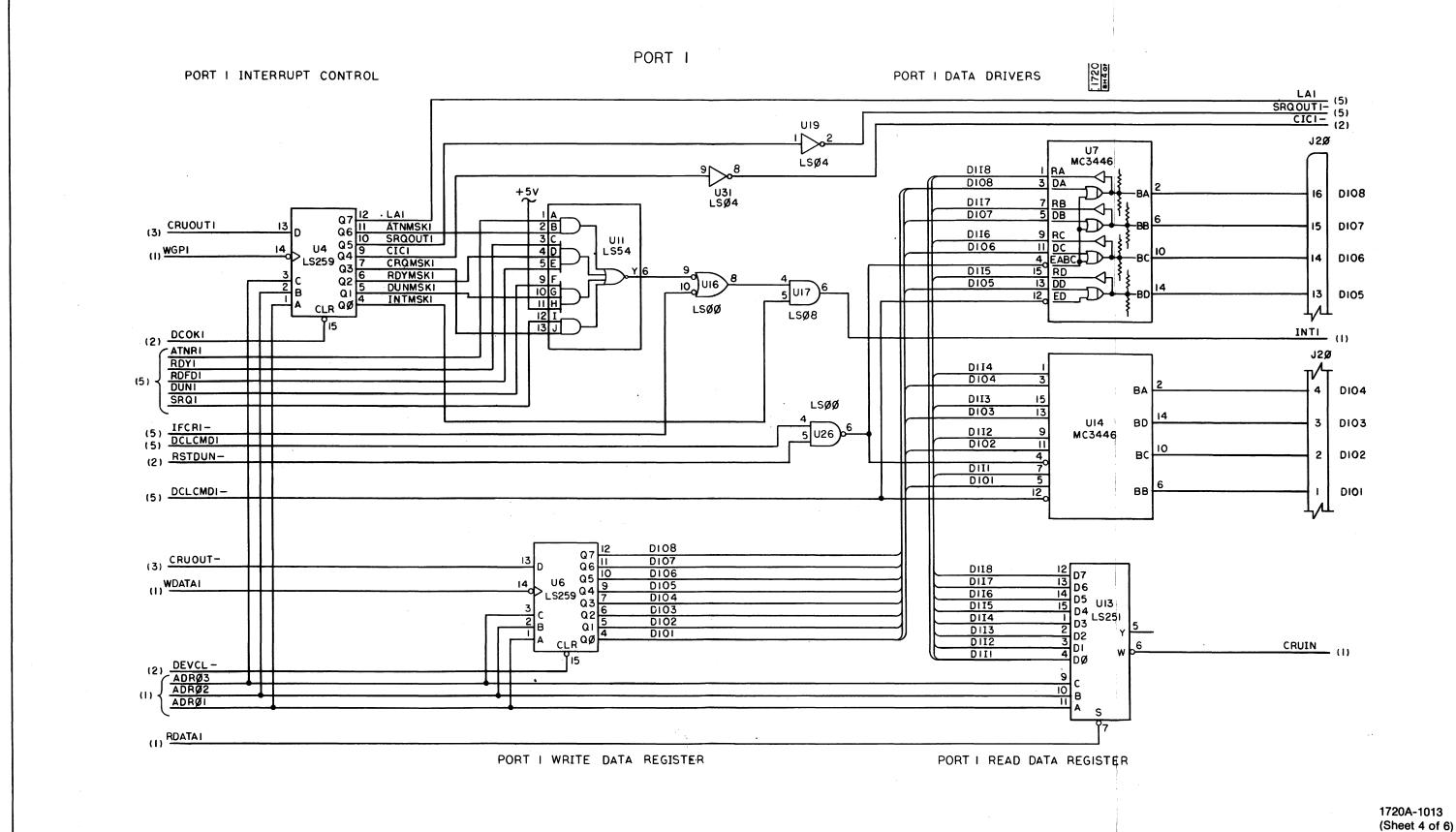

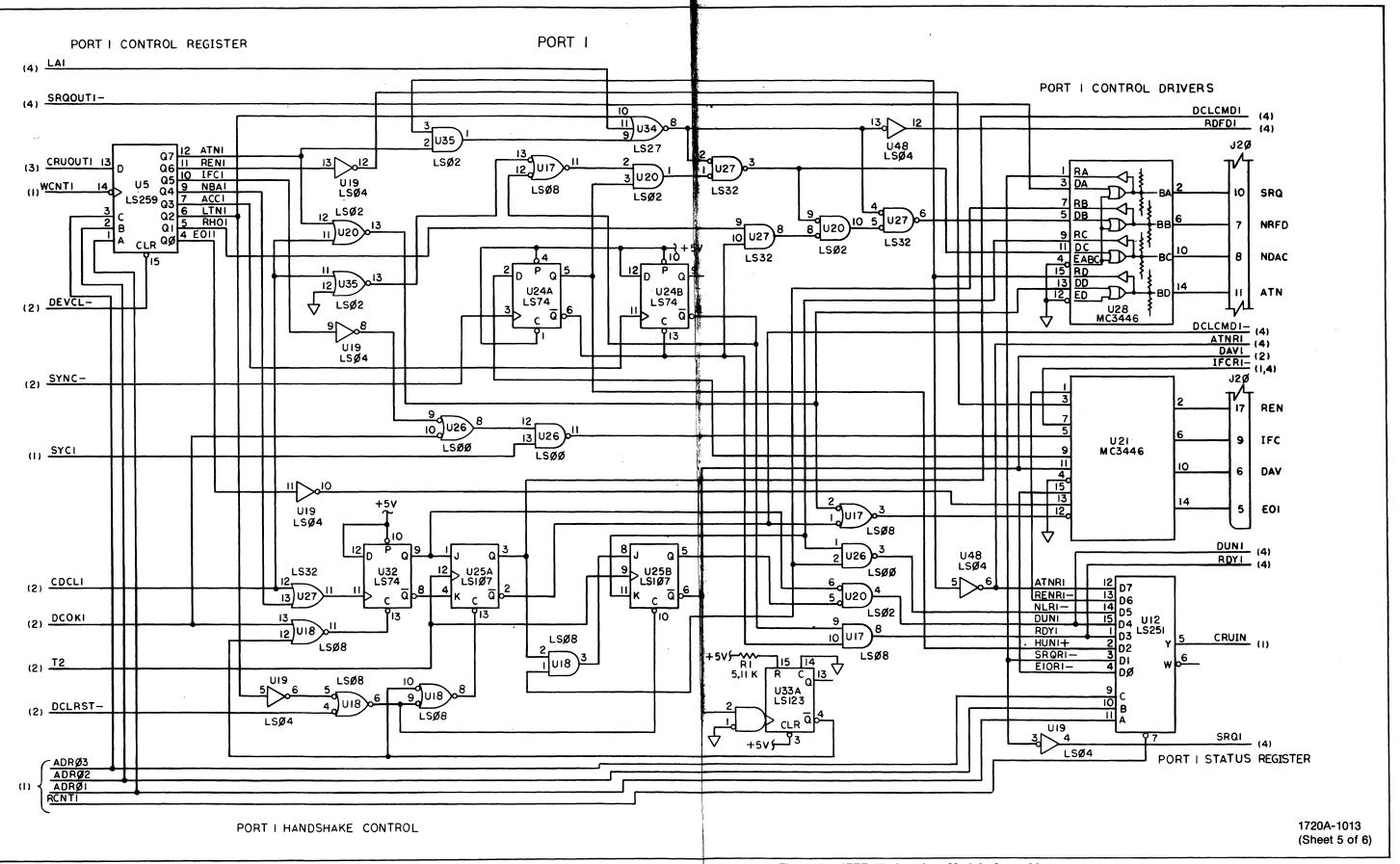

|         | 2C-30.           | Two Independent IEEE-488 Ports                |         |

|         | 2C-37.           | IEEE Bus Read Operation                       |         |

|         | 2C-40.           | IEEE Bus Write Operations                     |         |

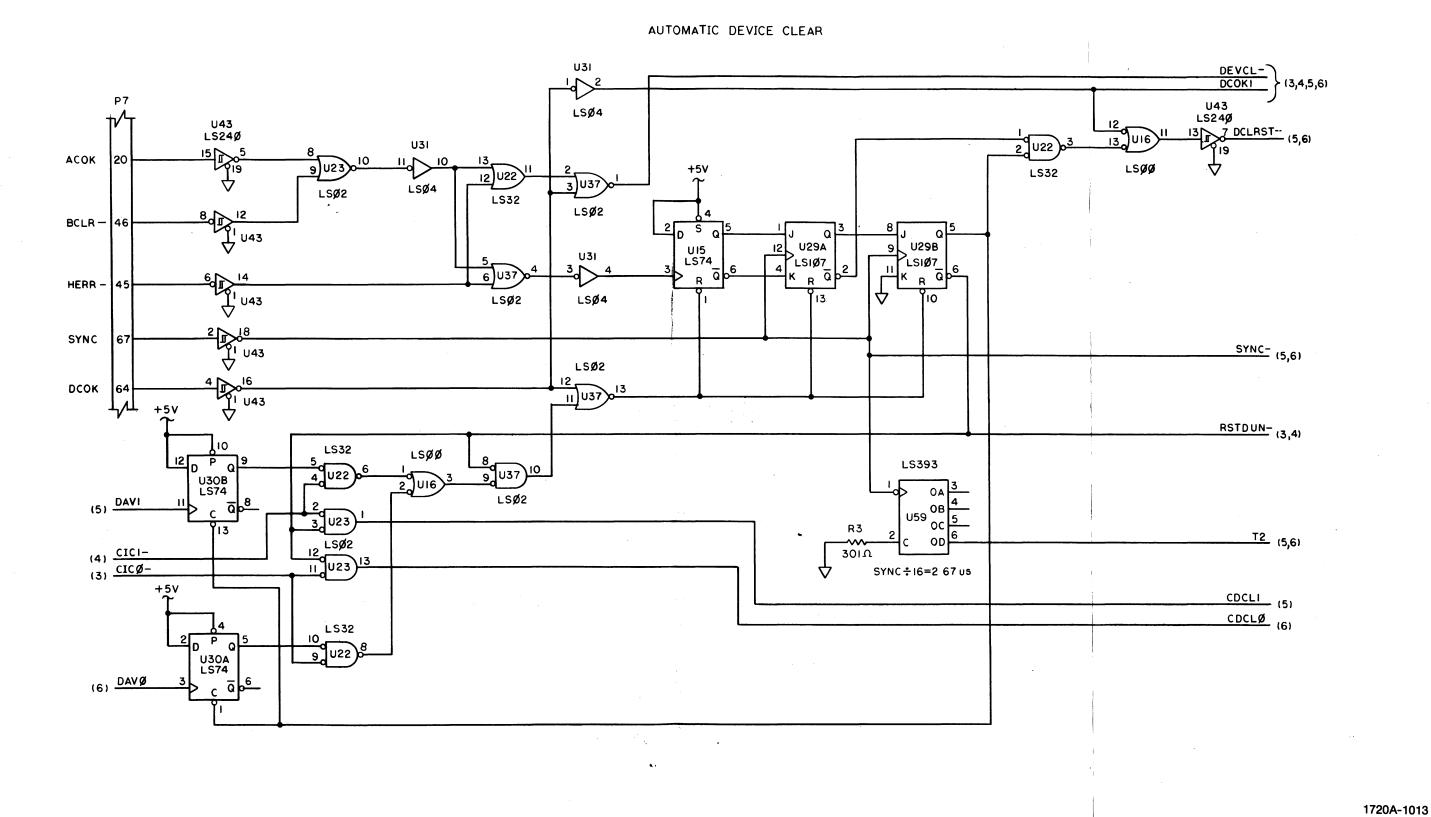

|         | 2C-42.           | Automatic IFC                                 |         |

|         | 2C-44.           | Automatic DCL                                 |         |

|         | 2C-46.           | Five Maskable Interrupts                      |         |

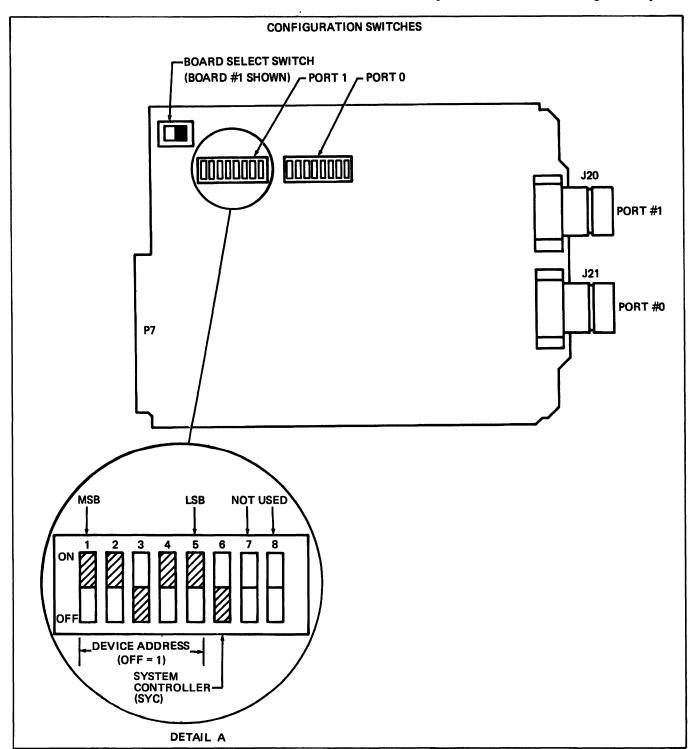

|         | 2C-51.           | Configuration Switches                        |         |

|         | 2C-54.           | Board# Select Switch                          | . 2C-15 |

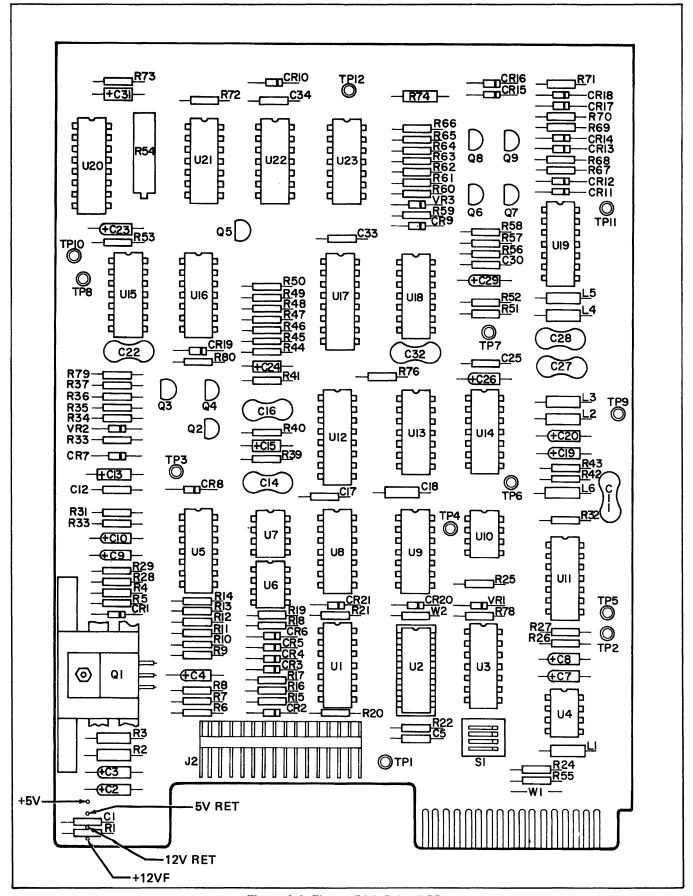

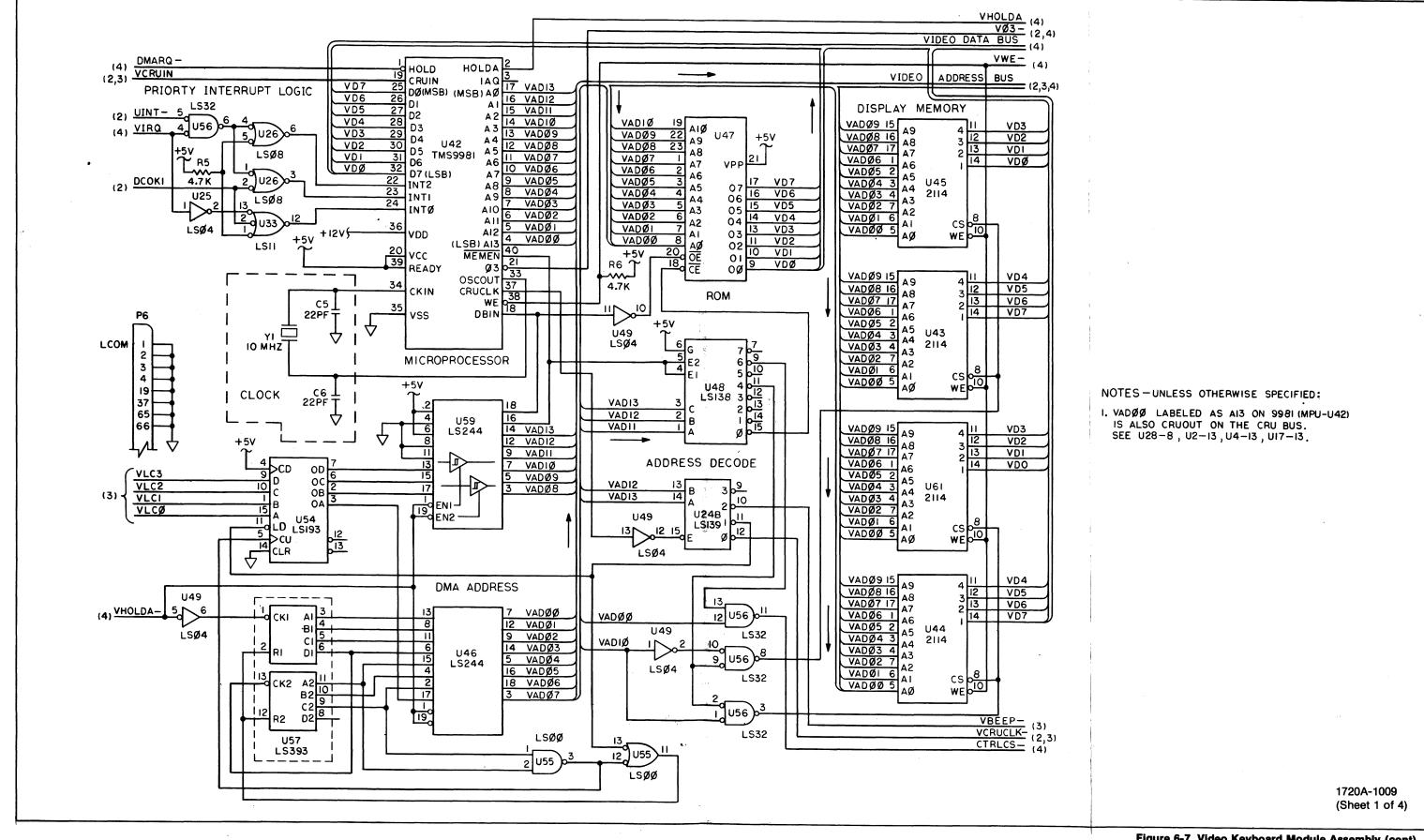

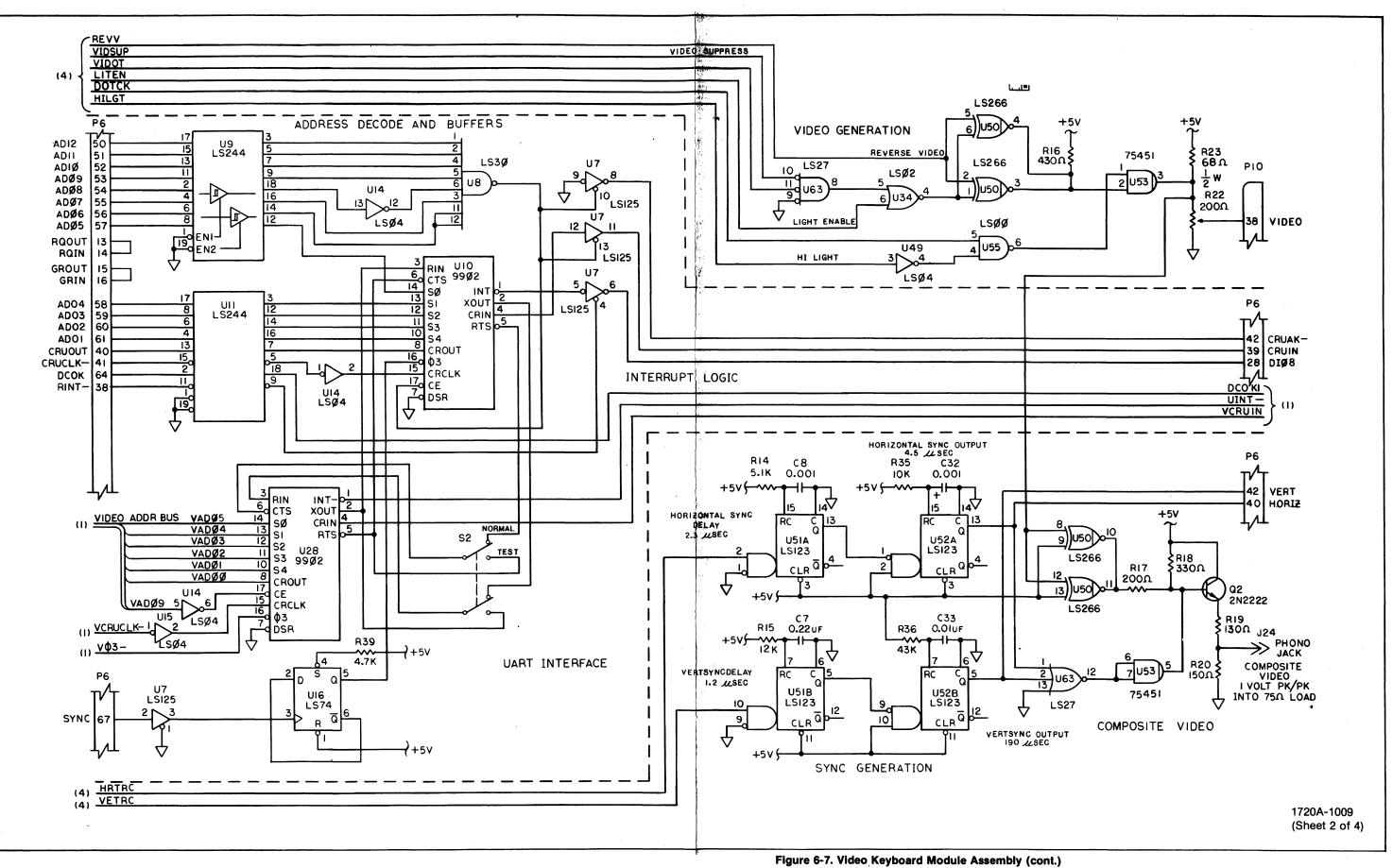

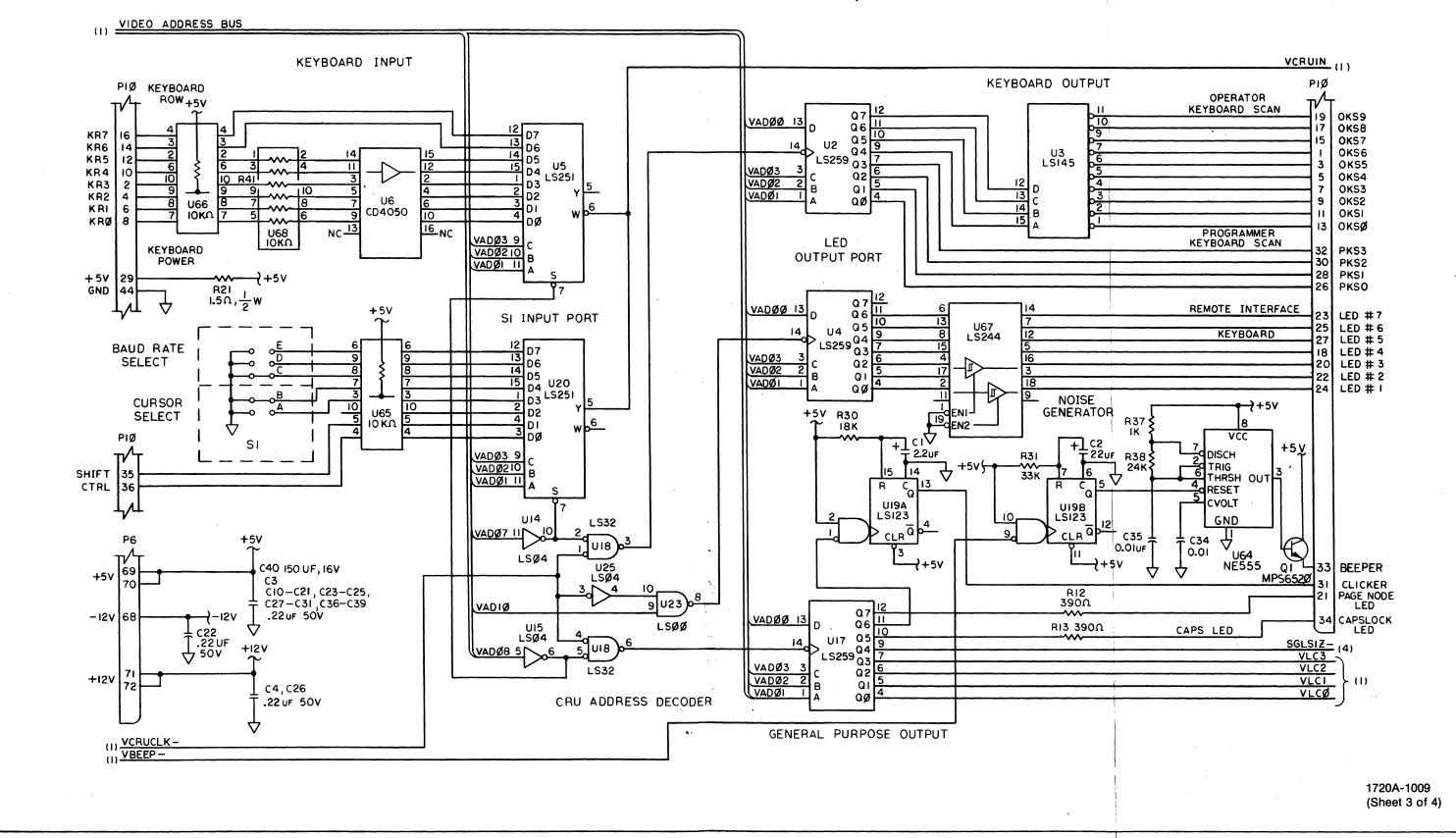

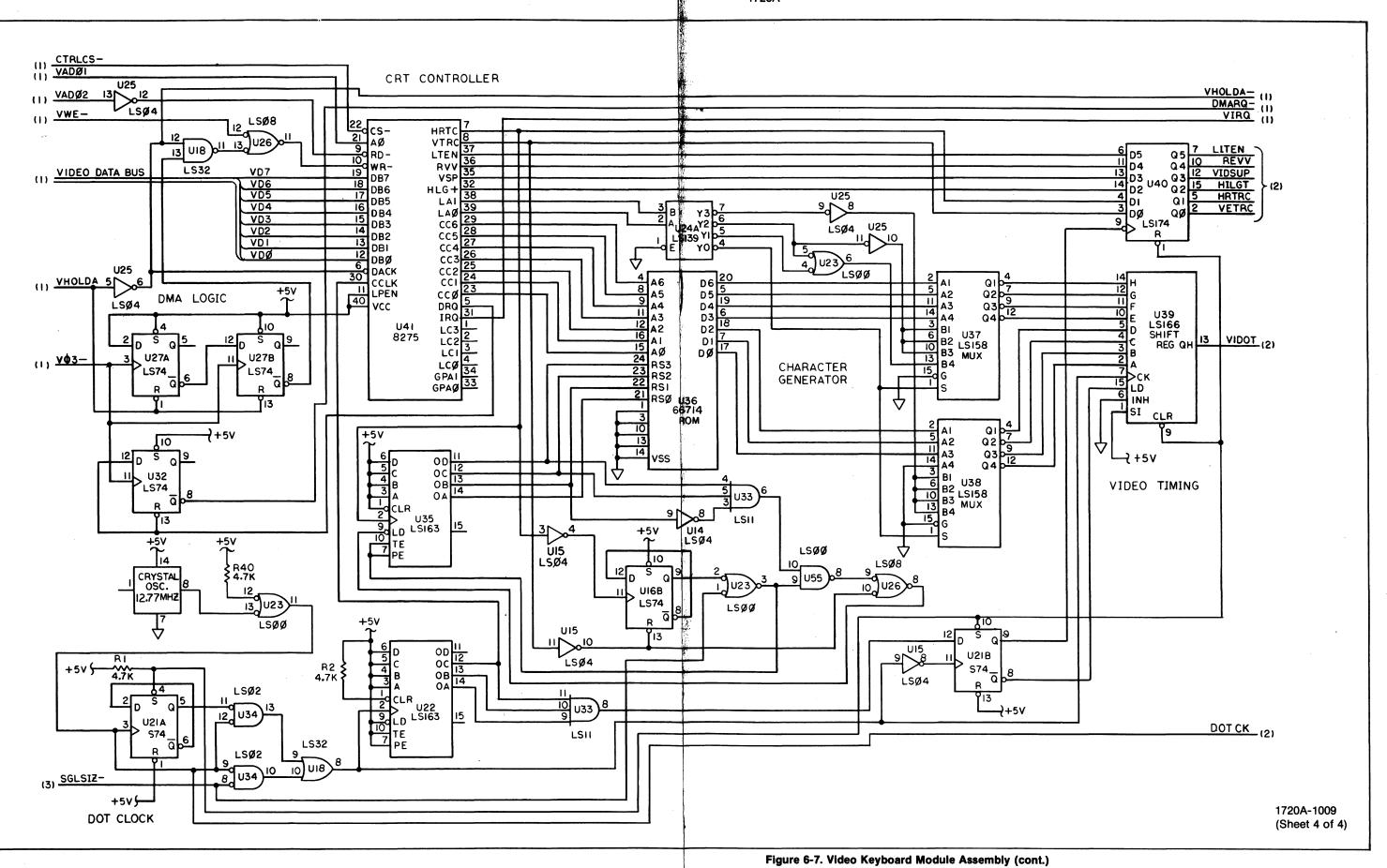

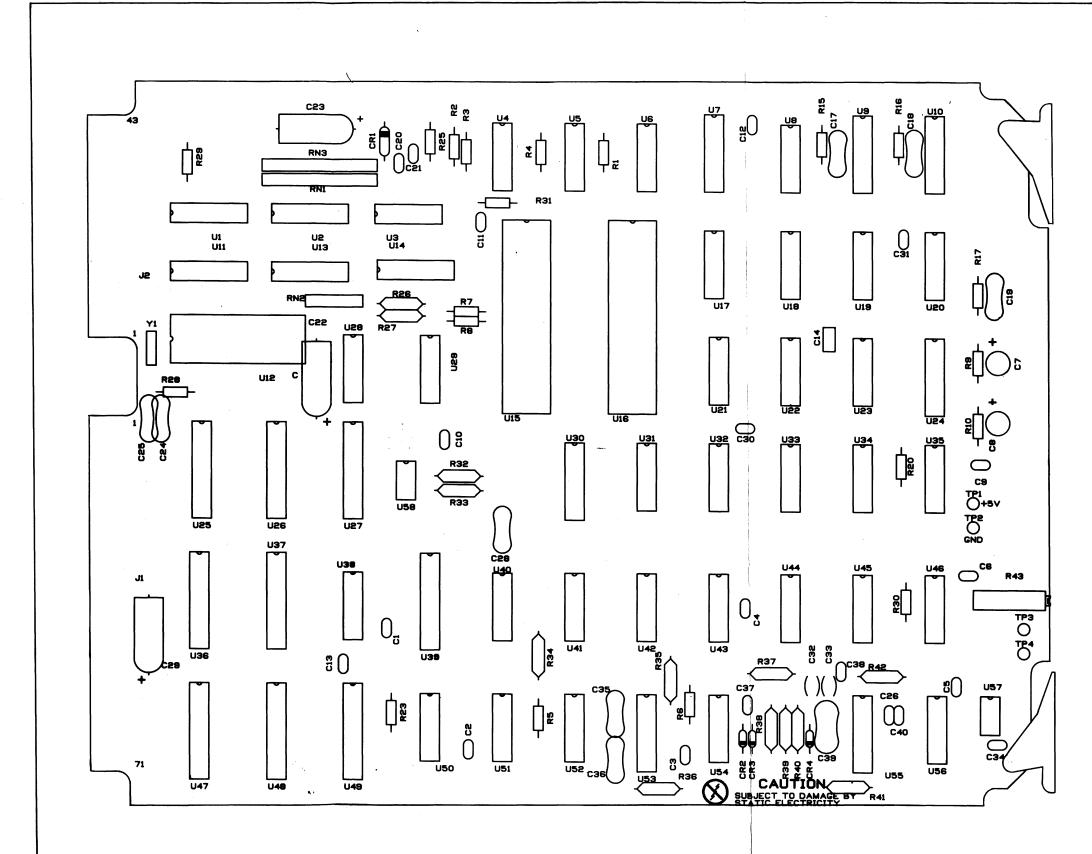

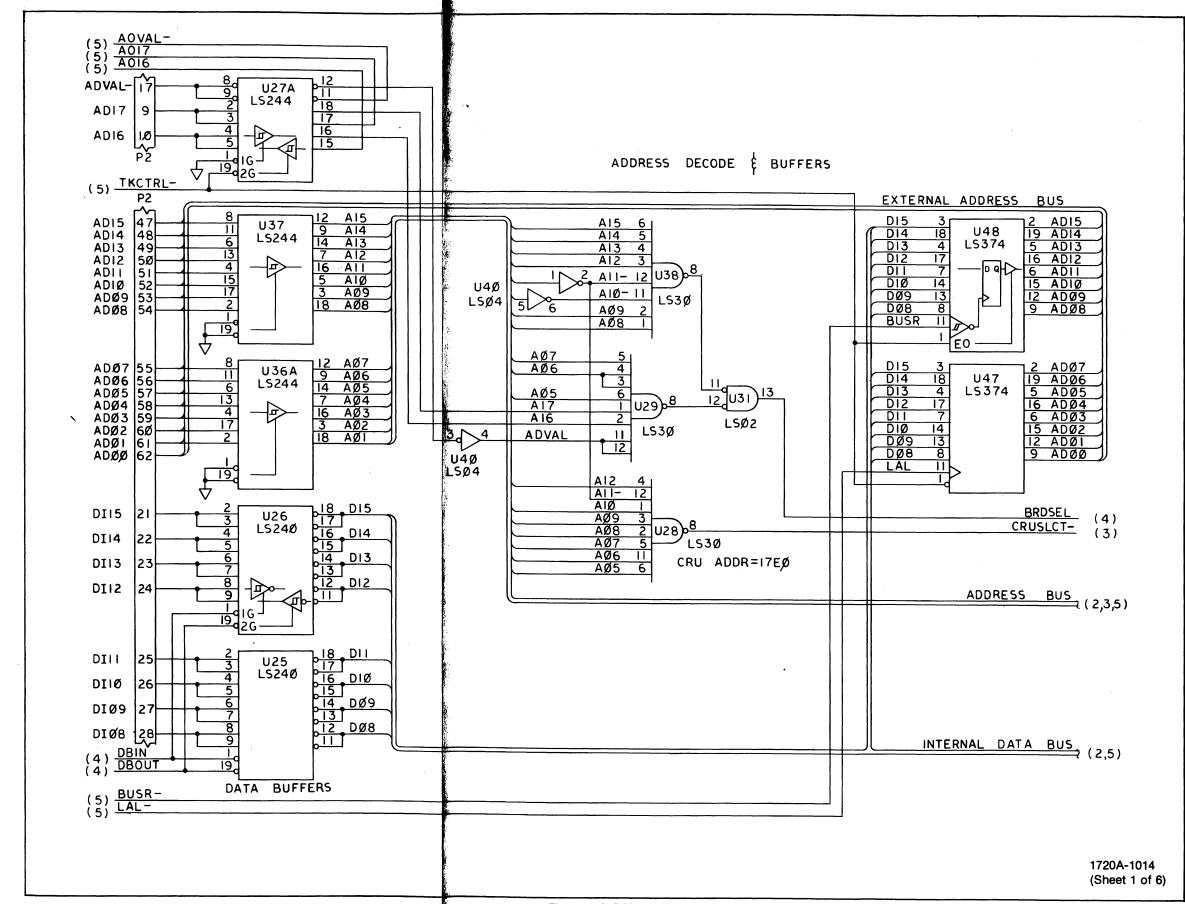

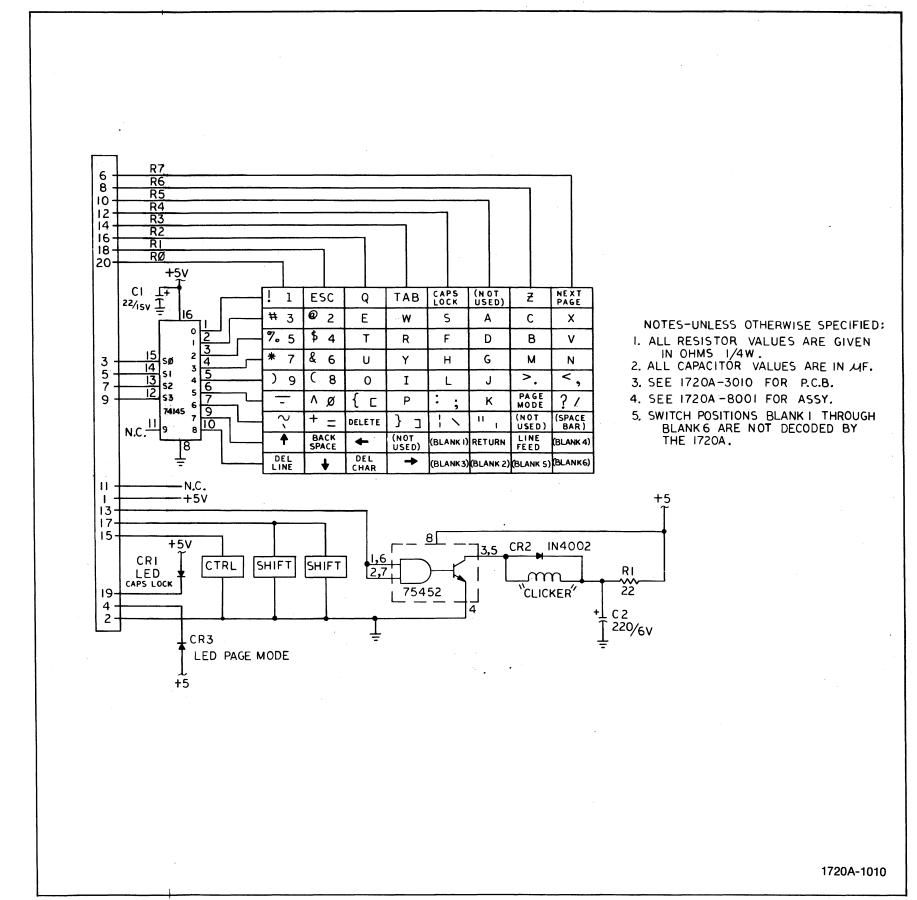

| 2D      | VIDEO            | /KEYBOARD                                     | . 2D-1  |

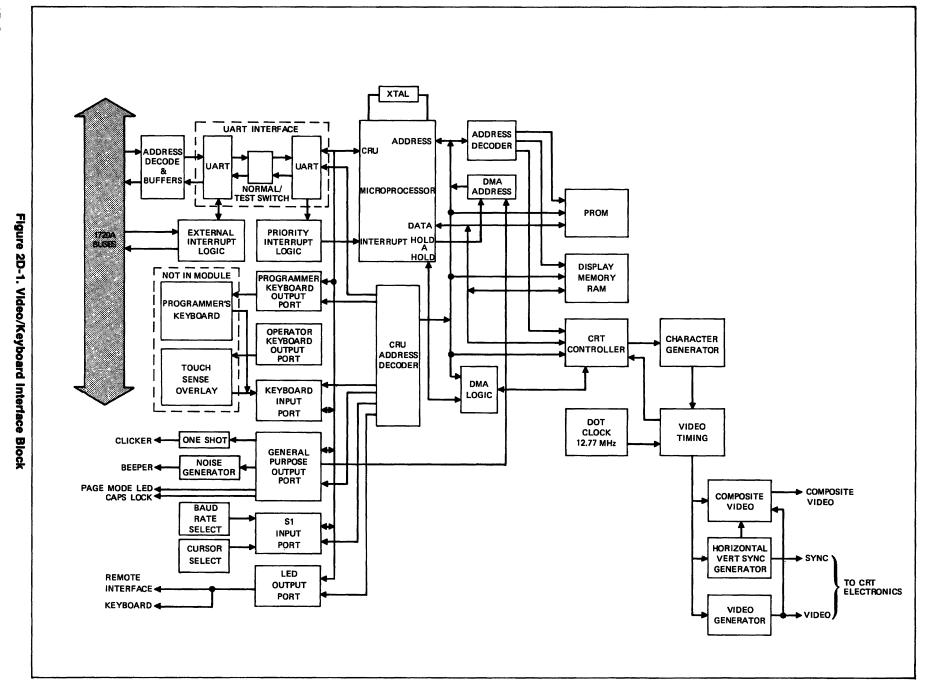

|         | 2D-1.            | INTRODUCTION                                  | 2D-1    |

|         | 2D-1.<br>2D-4.   | FEATURES OF THE VIDEO/KEYBOARD MODULE         |         |

|         | 2D-5.            | THE NORMAL/TEST SWITCH                        |         |

| SECTION |                  | TITLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | PAGE  |

|---------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|         | 2D-7.            | KEYBOARD SCANNING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2D-3  |

|         | 2D-10.           | ASCII CODE GENERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2D-3  |

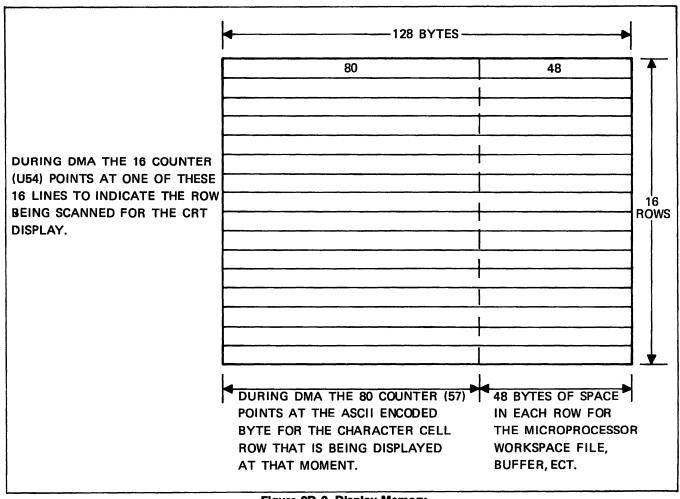

|         | 2D-12.           | DISPLAY MEMORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |

|         | 2D-14.           | CLICKER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2D-4  |

|         | 2D-16.           | INTERRUPTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2D-4  |

|         | 2D-18.           | INTERFACE TO THE 1720A BUSES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2D-4  |

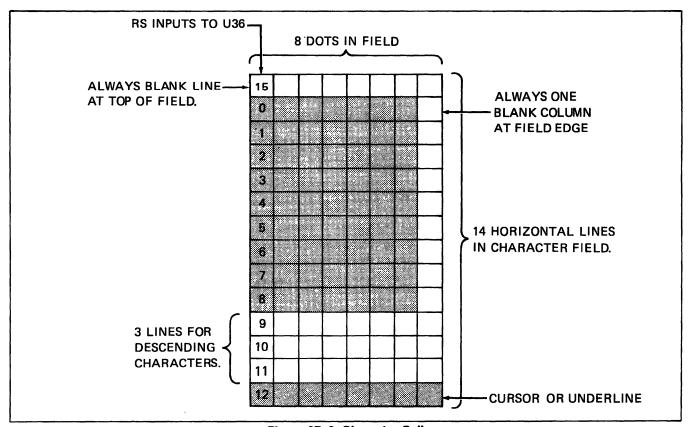

|         | 2D-20.           | DISPLAY FORMAT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2D-5  |

|         | 2D-22.           | CRT CONTROLLER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2D-5  |

|         | 2D-24.           | DMA FOR DISPLAY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

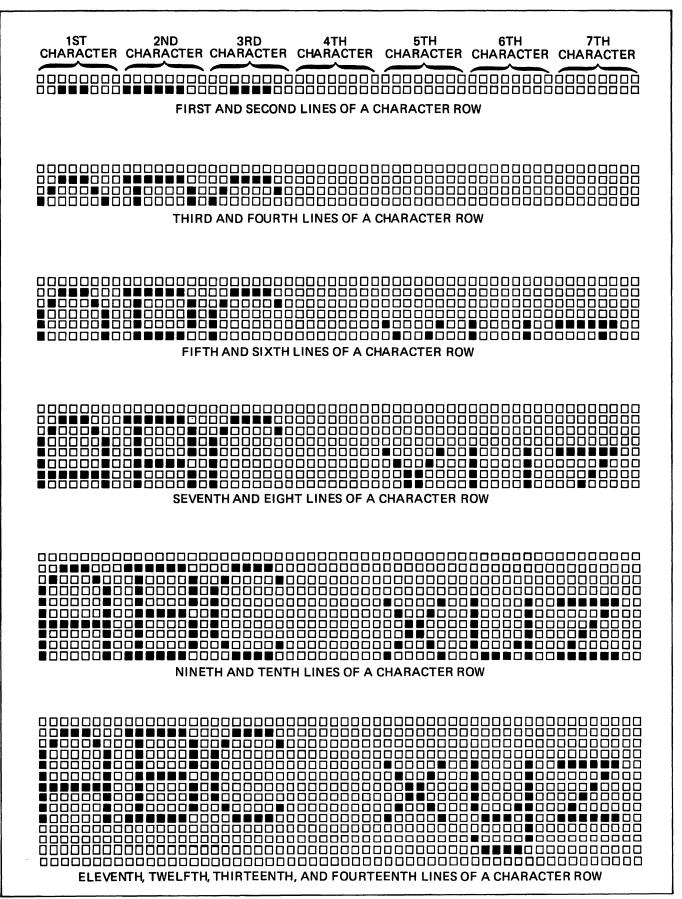

|         | 2D-29.           | CHARACTER GENERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

|         | 2D-34.           | DISPLAY REFRESH AND SCROLLING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

|         | 2D-37.           | CURSOR/BAUD RATE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |

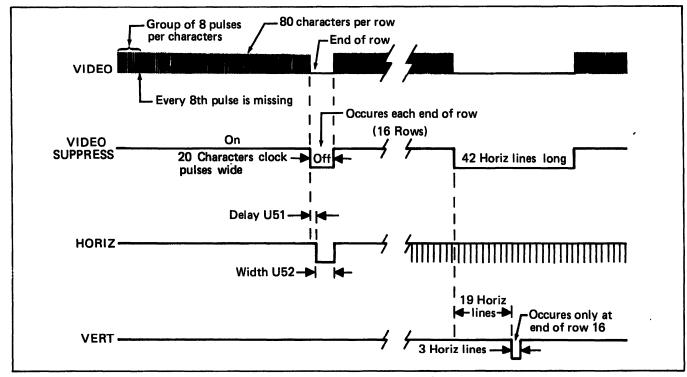

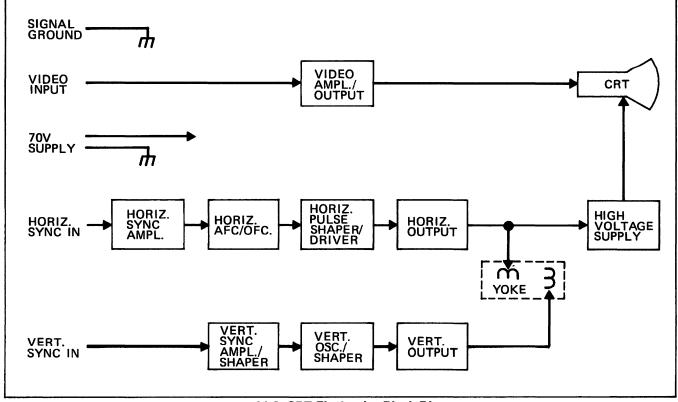

|         | 2D-40.           | VIDEO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |

|         | 2D-48.           | DOUBLE SIZE CHARACTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

|         | 2D-51.           | BEEPER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

|         | 2D-53.           | LEDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

|         | 2D-55.           | CAPS LOCK LED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

|         | 2D-57.           | PAGE MODE LED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

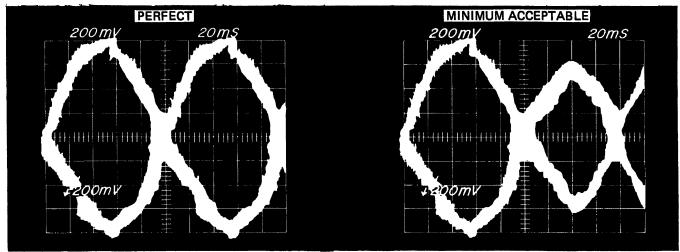

|         | 2D-59.           | COMPOSITE VIDEO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

|         | 2D-61.           | TEST MODE OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2D-10 |

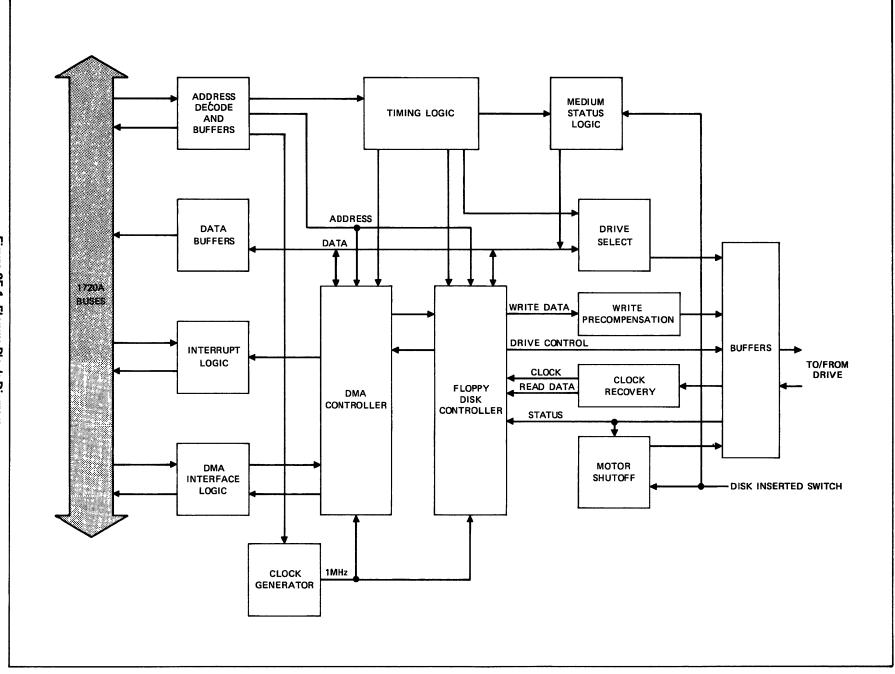

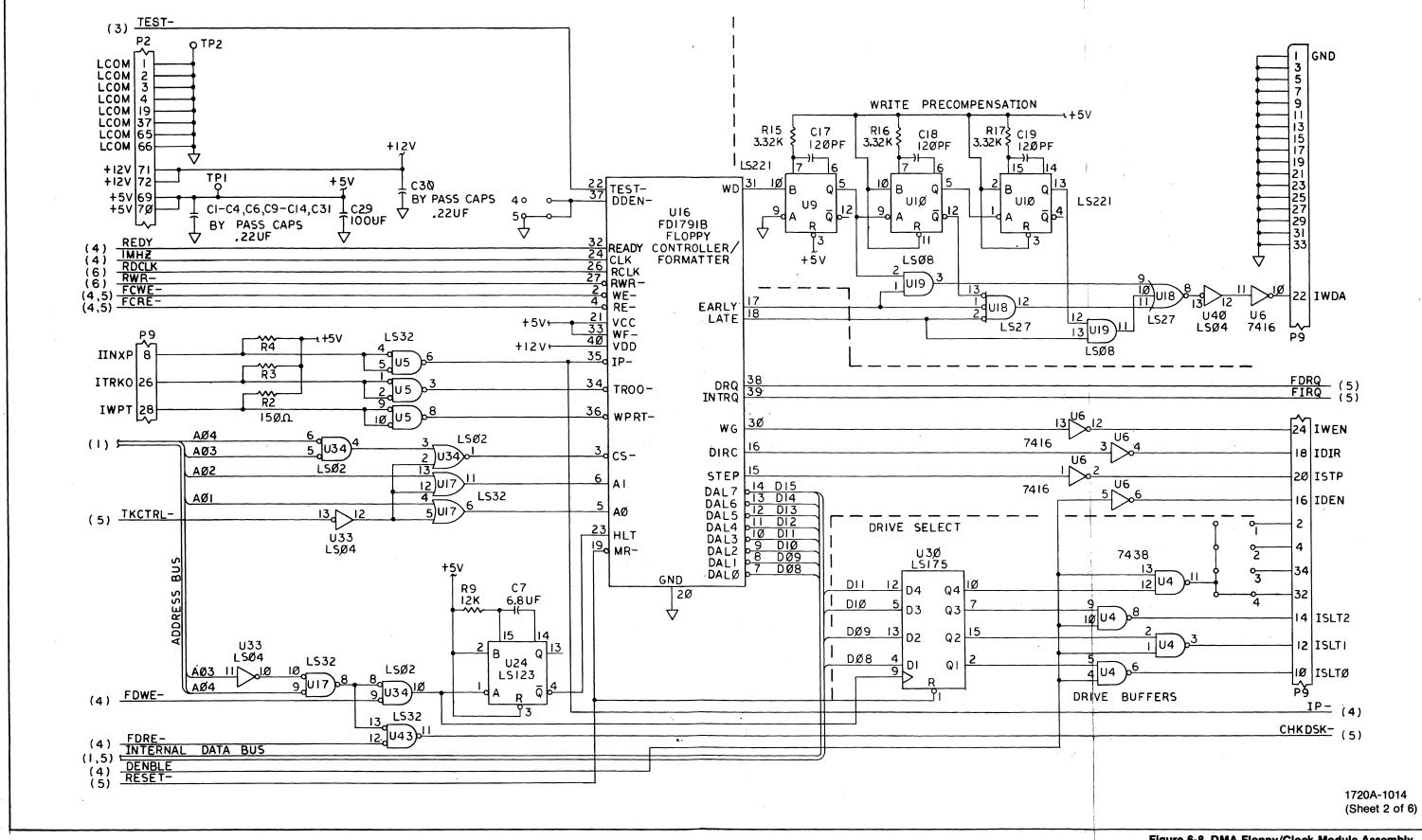

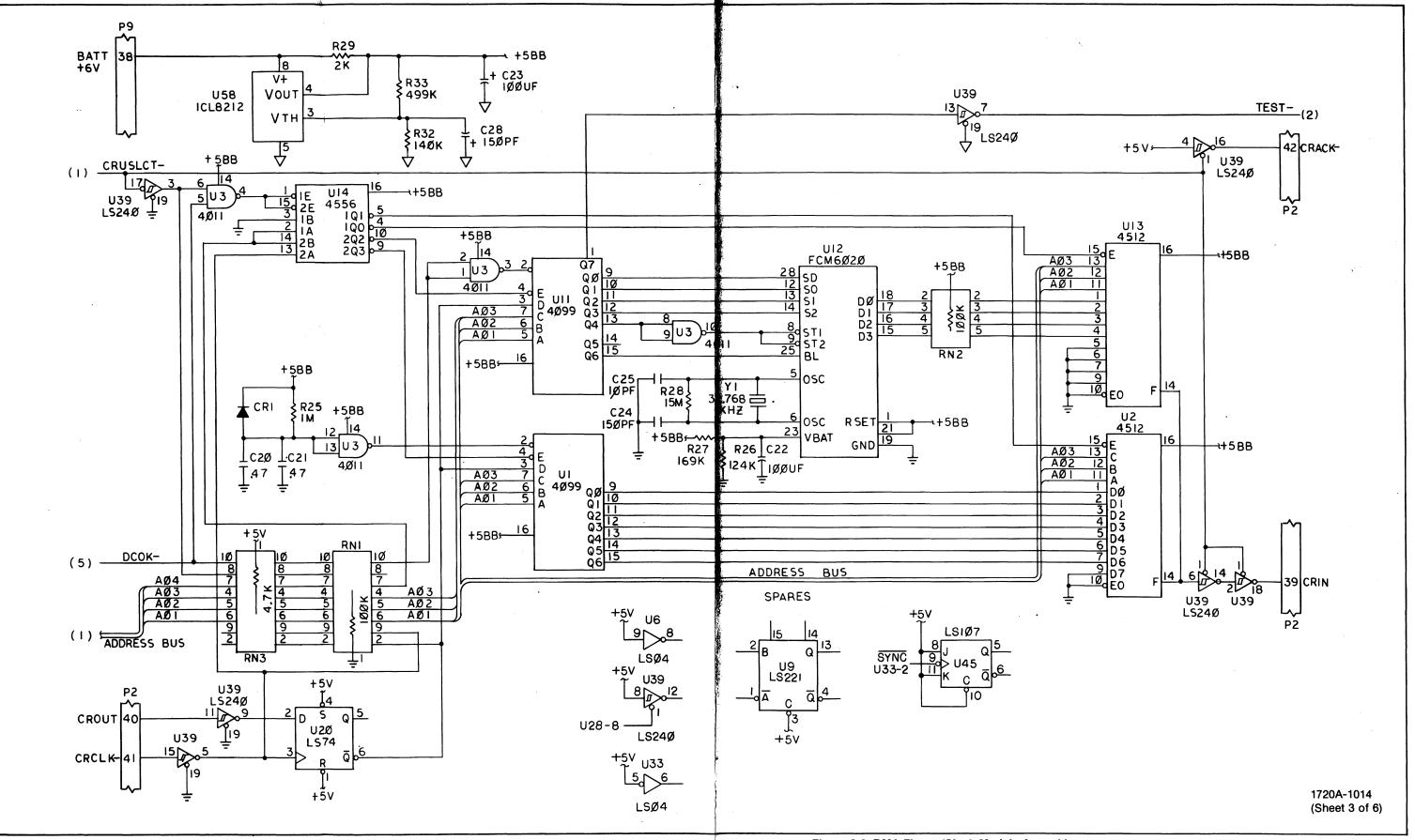

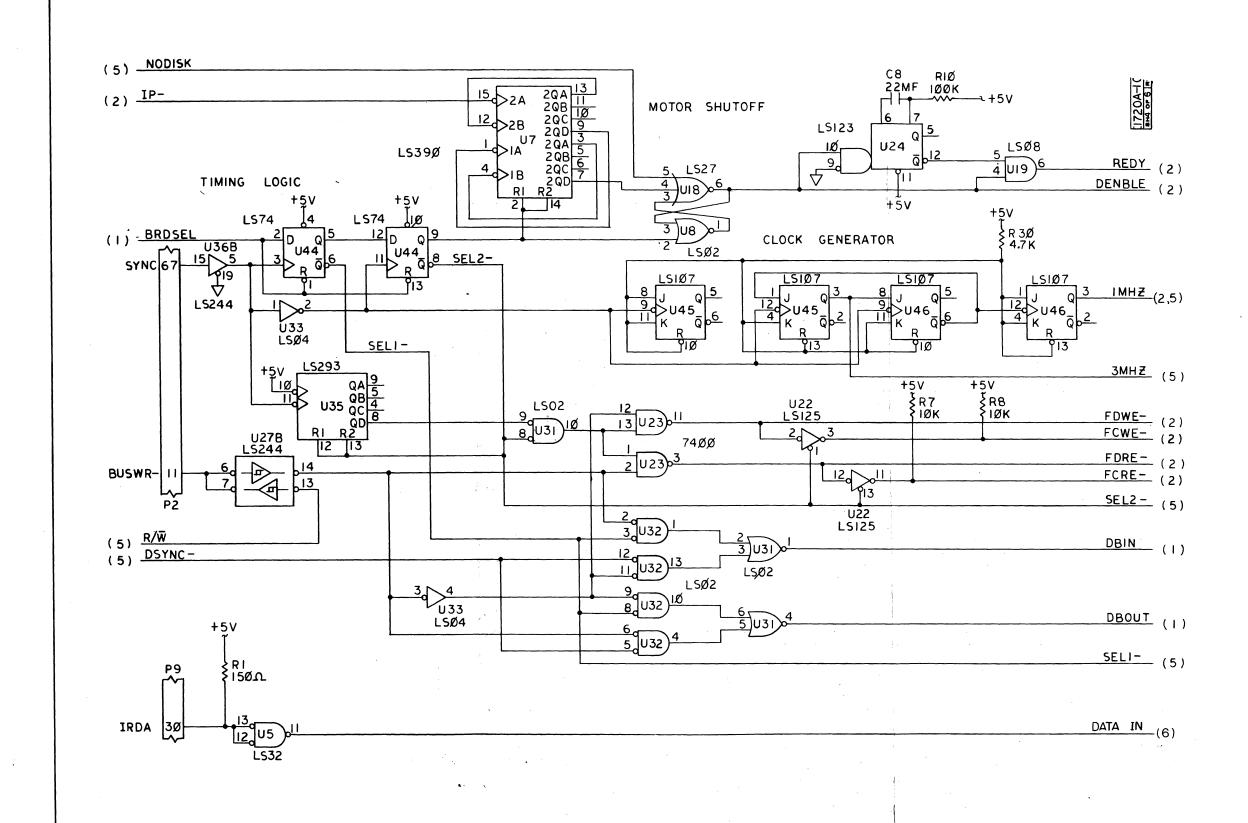

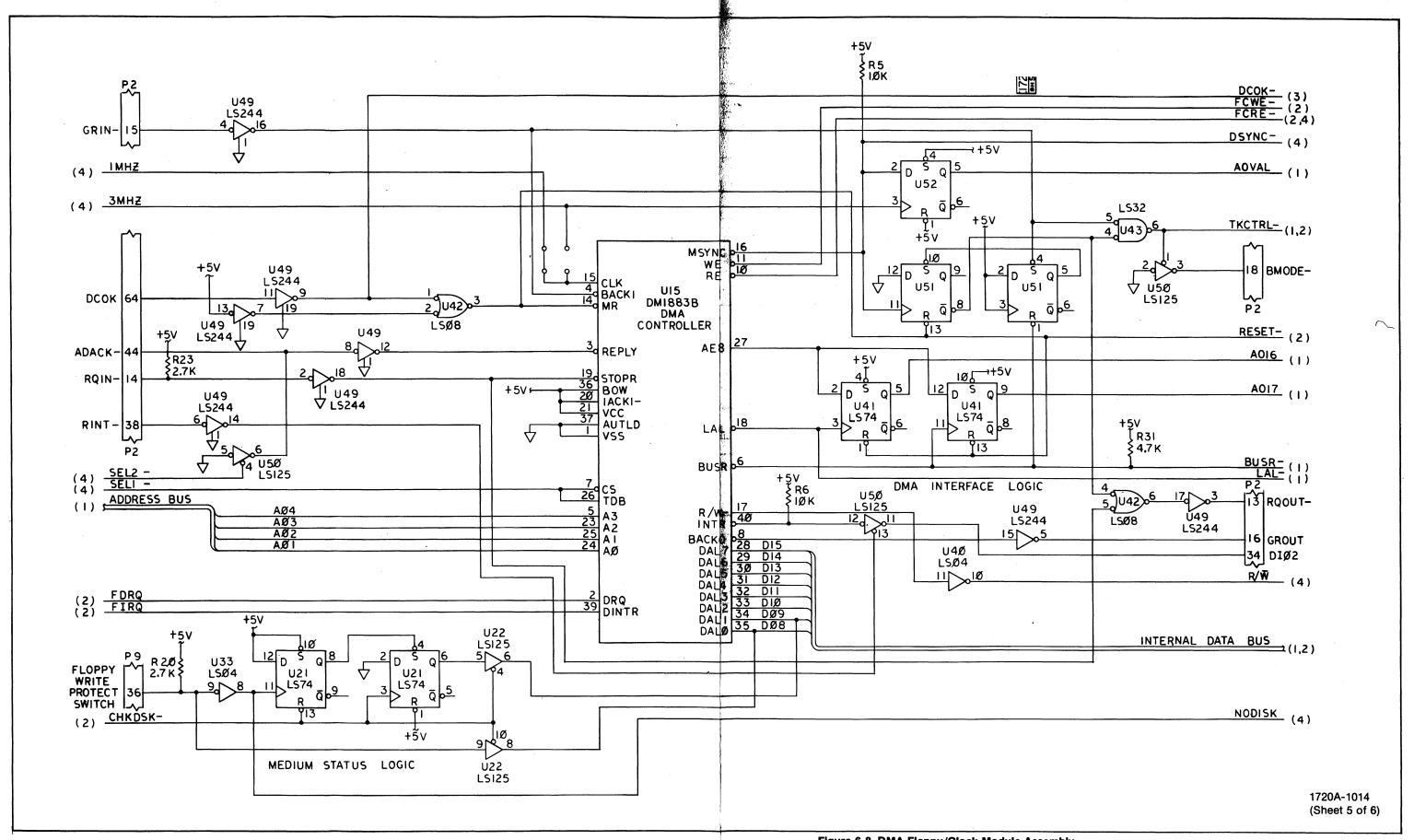

| 2E      | DMA-FI           | LOPPY MODULE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2E-1  |

|         |                  | NAMES OF MOST OF MARKET OF THE PROPERTY OF THE | ٠     |

|         | 2E-1.            | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

|         | 2E-4.            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

|         | 2E-11.           | Module-To-Memory DMA Transfers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |

|         | 2E-25.<br>2E-39. | DMA Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |

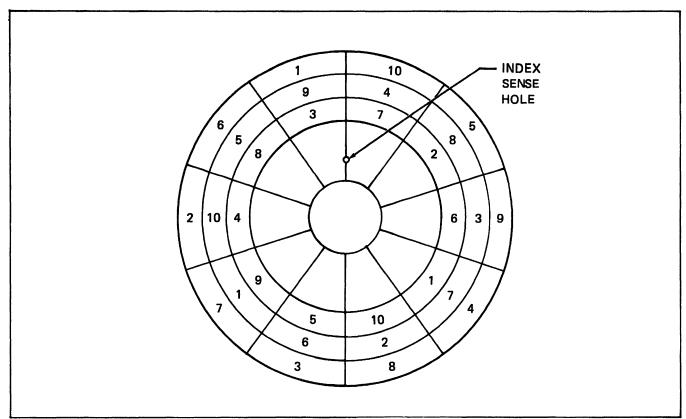

|         | 2E-39.<br>2E-43. | FLOPPY DISK CONTROLLER GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

|         | 2E-45.           | DMA and System Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

|         | 2E-49.           | Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |