# Cigital Service Seminar

#### **RECIRCULATING REMAINDER**

When the John Fluke Manufacturing Company entered the digital field it was decided that any instrument that we did manufacture would have to meet our established reputation for accuracy and reliability. Existing techniques of conversion were explored and rejected, either for their inability to meet the accuracy requirements, or their high cost, and/or their failure probability. The problem was solved in our own engineering department with the invention and development of the Recirculating Remainder technique of conversion.

High on our list of requirements, as always, is accuracy, and Recirculating Remainder gave us the accuracy we required, plus a low parts count and the resultant low power requirement for a highly reliable instrument. The technique also gave us excellent linearity and excellent Normal Mode Noise Rejection.

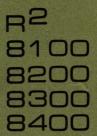

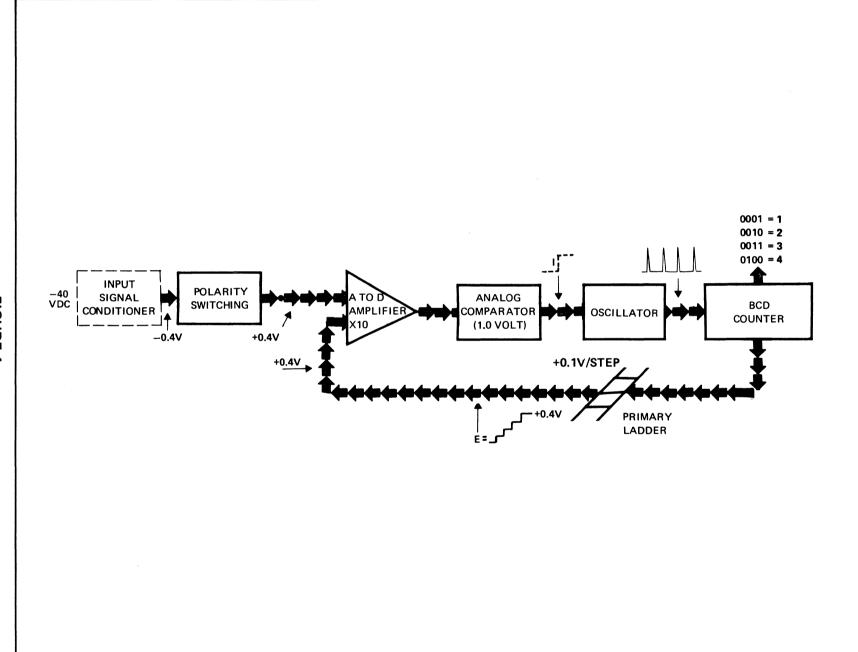

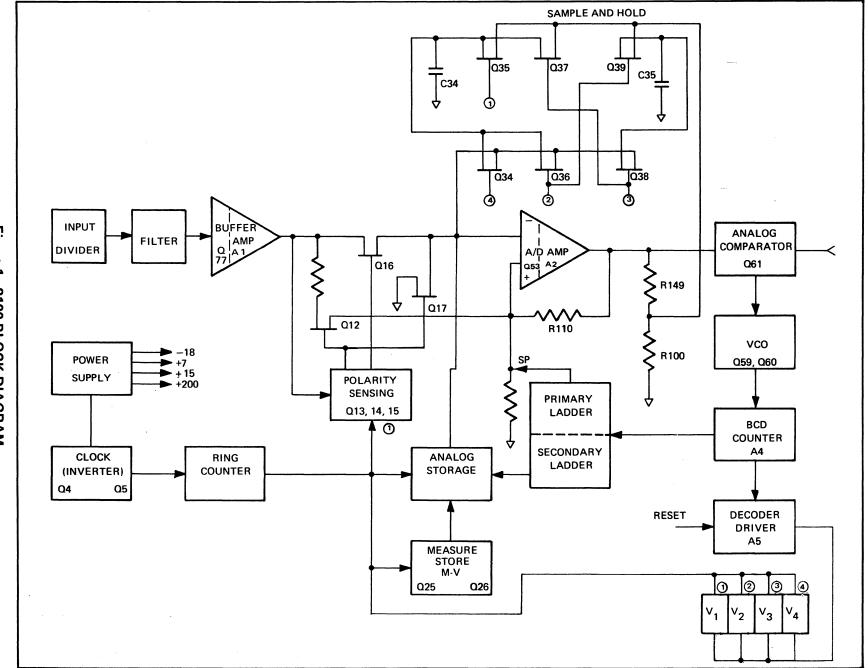

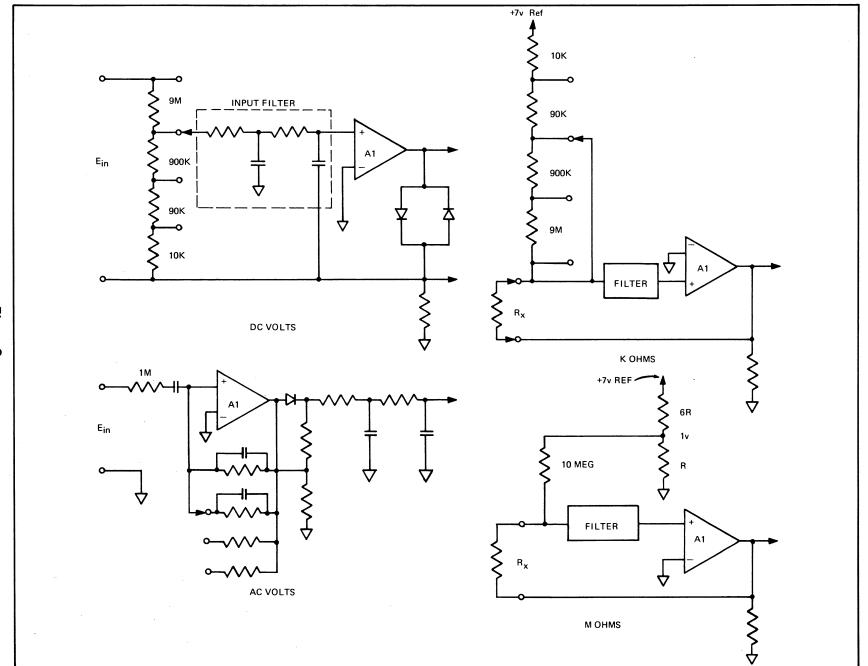

As seen in Figure 1 the first block represents the Input Signal Conditioner. It is the function of this circuitry to convert the input to the instrument to a DC signal within the basic range of the instrument. In the case of DC the usual task is attenuation. For AC it is necessary to convert the AC to DC via rectification and then attenuate the signal. In the case of ohms it is necessary to convert the ohms measurement to voltage within the basic range of the instrument. And with millivolt measurements it is usually necessary to amplify the signal up to the basic input level.

The second block in the system is Polarity Switching. Since we want an automatic instrument, we include Polarity Sensing and Switching as an integral feature. Polarity Sensing and Switching feeds the A - D, or Analog to Digital Amplifier, which is the heart of the instrument. It is an Operational Amplifier with a differential input. In the case of our example circuitry this amplifier has a gain of ten. Through the years the John Fluke Manufacturing Company has made extensive use of the Operational Amplifier to achieve accuracy and stability in our instrumentation. The application in the Recirculating Remainder system is not a particularly difficult one for a good Operational Amplifier. In the example system shown we will consider the basic input to the instrument as zero to 1.2 volts. This would correspond to the 1 volt range with 20% over-ranging. The input to the Polarity Switching circuit would be plus or minus zero to 1.2 volts DC and the output of the polarity switching would always be zero to plus 1.2 volts.

The A to D Amplifier feeds the Analog Comparator. It is the function of the analog comparator to produce current any time the output voltage of the A - D Amplifier is 1 volt or higher. Outputs of less than 1 volt from the Amplifier will result in no current from the Analog Comparator. Current from the Analog Comparator feeds the Oscillator. It is the function of the Oscillator to produce a train of pulses whenever it is fed current from the Analog Comparator.

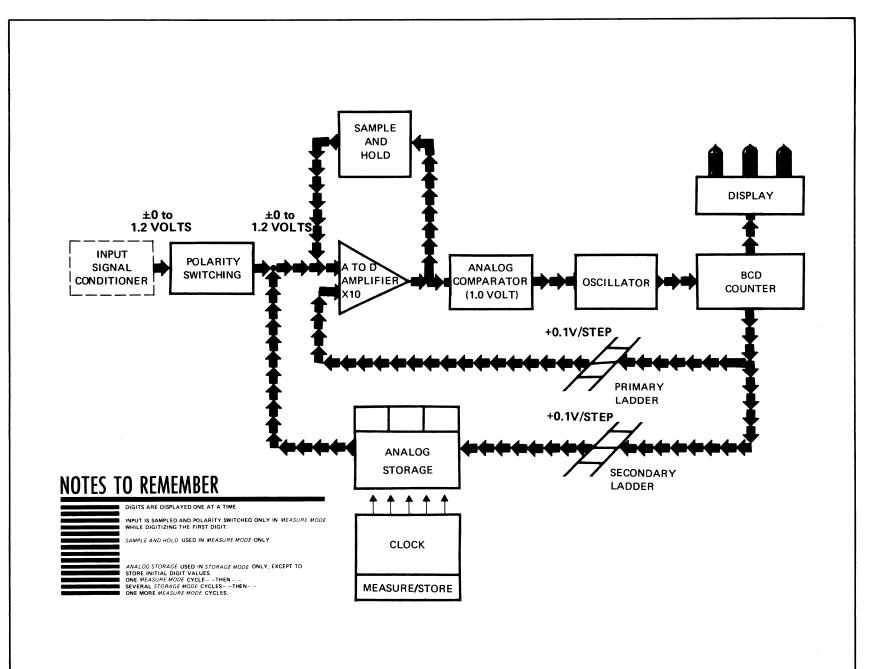

The pulse train generated by the Oscillator is counted by the BCD Counter. The counting is done in BCD, or Binary Coded Decimal format, as shown in Figure 2. This counter is reset to zero after each digitizing period.

One of the circuits that is fed by the BCD Counter is the Primary Ladder. This Ladder generates 0.1 volt output for every pulse that is translated by the Counter. Should the Oscillator produce six pulses the output of the BCD Counter would be a BCD 6 and the output of the Ladder would be 0.6 volts. The output of the Ladder is fed back to the input of the A to D Amplifier.

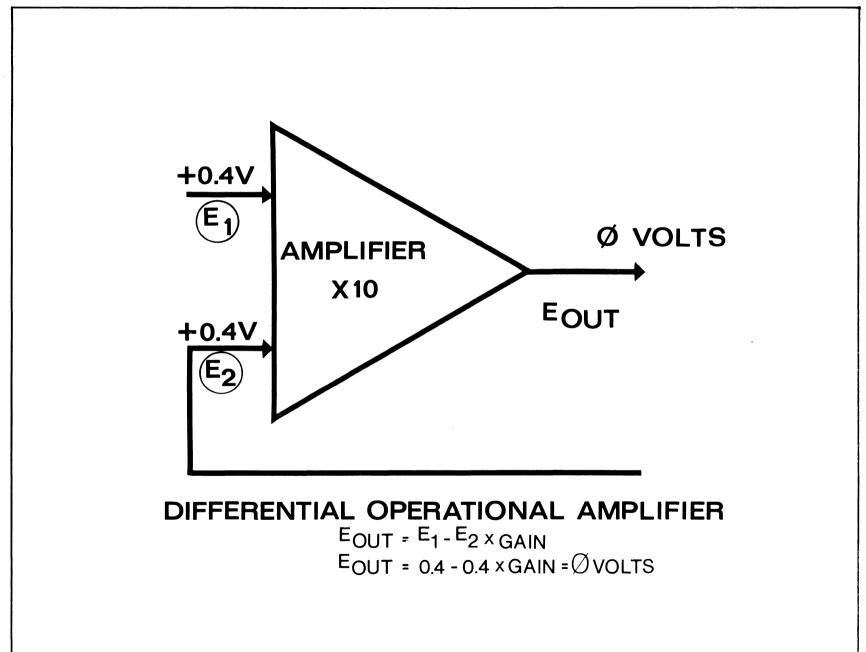

It should be noted that one input of the differential A to D Amplifier is from the Polarity Switching circuit, and the other is from the Primary Ladder. It is characteristic of a differential amplifier that when the inputs to the amplifier are equal, the output will be zero. The output voltage of a Differential Amplifier is equal to the difference voltage input, times the gain of the amplifier. (See Figure 3.)

The BCD Counter also feeds the Display. As numbers are digitized in Recirculating Remainder they are sequentially displayed. In orther words, the numbers blink ON in sequence. The hundreds digit turns ON and

$\mathbb{R}^2$

FIGURE

<u>...</u>

.

.

FIGURE 2.

3

$\mathbb{R}^2$

displays the number that was digitized, then turns OFF. The tens digit turns ON and displays the number that was digitized, then turns OFF. The ones digit turns ON, displays the number that was digitized, turns OFF, etc. Applying -40 volts DC at the input to the Block Diagram shown in Figure 4, the Input Signal Conditioner would attenuate the forty volts down to -0.4 volts by dividing by 100. The -0.4 volts would be fed to the Polarity Switching Circuitry. The Polarity Switching Circuit will sense the negative voltage and cause FET transistor switches to operate in such a manner as to apply the +0.4 volts to the A to D Amplifier.

With +0.4 volts on one input to the Amplifier and the other input being zero volts from the Primary Ladder the resultant voltage out of the Amplifier will be +4.0 volts due to the times ten gain of the Amplifier.

The Analog Comparator sensing more than one volt of output from the Amplifier produces current which is fed to the Oscillator. The Oscillator will commence producing a pulse train. It is interesting to note that the rate of pulsing is a function of current. That is, when more current is fed to the Oscillator the faster it will pulse. As the current is reduced the pulse rate will slow down.

The BCD Counter will count the pulses and translate them into BCD notation as shown. The BCD output is fed to the Primary Ladder which will have an output of +0.4 volts at the end of the fourth pulse. The +0.4 volt from the Primary Ladder being fed to the lower input of the A to D Amplifier, the upper input of the A to D Amplifier is +0.4 volts. At this point in time we have applied +0.4 volts to both inputs of the differential A to D Amplifier.

As shown in Figure 3, the output voltage of a Differential Operational Amplifier is equal to  $E_1$  minus  $E_2$  times the gain of the amplifier. In this case,  $E_1$  equals +0.4 volts and  $E_2$  equals +0.4 volts, the difference being zero volts and the output, times 10, is zero volts.

The Analog Comparator no longer sees a voltage from the A to D Amplifier and, therefore, no longer produces current for the Oscillator; current being cut off from the Oscillator, no more pulses will be produced. The circuitry is in a state of rest, having digitized a four. At this time the BCD four from the Counter is fed to the Display circuitry. The Decoder Driver will decode the BCD four, place a ground on the "4" line to the display tubes. During this initial period of time the most significant digit tube will be ionized, but only for a few milliseconds. As each number is digitized in the Recirculating Remainder system it is displayed for a short time only. The numbers are displayed in sequence, but at a rate so fast that the persistency of the human eye does not see the blinking.

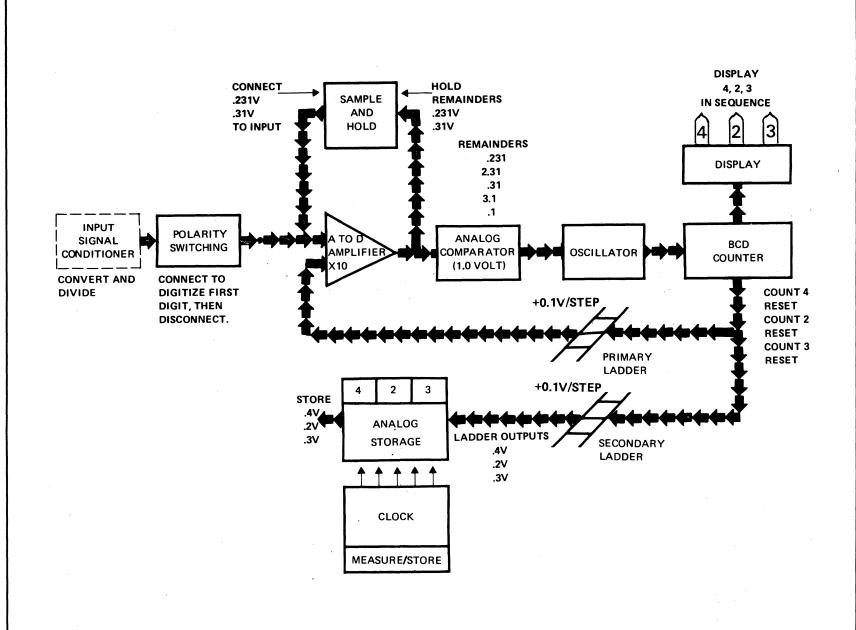

The example of -40 volts works out well, but we were working with an even voltage. Let us take the example of 42.31 volts AC applied to the input. Referring to Figure 5, the first action that must take place is the conversion of the AC to DC, then the attenuation of the result down to a voltage within the basic range of the instrument; the Input Signal Conditioner serves both purposes. The AC is rectified and attenuated so that the resultant output from the Input Signal Conditioner is within the range of zero to 1.2 volts, or, in this case, +.4231 volts, which is fed to the Polarity Sensing and Switching circuit and then on to the input to the A to D Amplifier. In order to digitize the first significant digit the output of the A to D Amplifier will be 4.231 volts until the Analog Comparator has supplied current to the Oscillator long enough for four fulses to be generated, which are counted by the BCD Counter. The output of the Primary Ladder is now 0.4 volts, and the inputs to the A to D Amplifier are +0.4 volts and +0.4231 volts, the difference being +0.231 volts. The output of the amplifier will be +0.231 volts, insufficient to cause the Analog Comparator to supply further current to the Oscillator. The Display Circuit will display a 4 in the first tube. All of the other display tubes will be dark. The output of the A to D Amplifier after the fourth pulse has been counted will be +0.231 volts, which is the remainder voltage. Instrument timing will cause the Sample and Hold circuit to accept the 0.231 volts into a storage capacitor where it will be stored until we need it to digitize the next increment of voltage. The Clock will also reset the BCD Counter to zero. It is the Clock that synchronizes the Display to operate in the proper sequence and at the proper time.

## FIGURE 4.

R2

FIGURE 5.

R2

At the next moment in time the Clock will cause the input line to the Sample and Hold circuit to cut OFF, while turning the output line from the Sample and Hold circuit ON and connecting it to the input to the A to D Amplifier. (See Figure 5.) This action causes the 0.231 volts that was stored in the Sample and Hold circuit to be applied to the Amplifier input. The input from the primary ladder is once again zero volts, having been reset as a result of the counter reset that was applied during the last Clock action in the first digitizing period.

The voltage from the Amplifier will be 2.31 volts. With more than 1 volt output from the Amplifier the Analog Comparator will once again supply current to the Oscillator. The Oscillator Pulses will be counted and translated to BCD output by the BCD Counter. Remember that the Clock had caused the BCD Counter to be reset to zero during the previous time period. When the Counter was reset the Display Tube was extinguished and now all of the display tubes are dark. When the oscillator has pulsed twice the output of the Primary Ladder will be .2 volts, which is fed back to the input of the A to D Amplifier. Figure 5 shows an additional Ladder connection to the output of the Counter. A Secondary Ladder has simultaneous outputs with the Primary Ladder. These output voltages are fed to a circuit called Analog Storage. When the 4 was digitized in the first period the output of the Secondary Ladder was +0.4 volts; the Clock will cause the 0.4 volts to be stored in Analog Storage in a specific location reserved for the first digit.

The circuit has just digitized the 2 and now the Clock will cause the +0.2 volts from the Secondary Ladder to be stored in Analog Storage in a position reserved for the second digit. +0.2 volts being fed back to the input of the A to D Amplifier from the Primary Ladder caused the input voltage difference to the Amplifier to be .031 volts, and the output of the Amplifier to be 0.31 volts, which is less than one volt. Consequently, the Analog Comparator will no longer supply current.

A "2" having been digitized, BCD information is fed to the Display circuit where the "2" is displayed as the second most significant digit. The remainder voltage from the Amplifier, which was .31 volts, will be stored in the Sample and Hold circuit. At this moment in time the Display tube will be extinguished and the BCD Counter will be reset to zero which causes the output voltage of the Ladders to be reduced to zero volts.

The output of the Sample and Hold will cause the .31 volts just stored to be applied to the input of the A to D Amplifier . . . resulting in an output of 3.1 volts. The Analog Comparator will produce current, the Oscillator will start generating a pulse train. The Counter will count that pulse train and the BCD Counter will translate those pulses into BCD format, causing each Ladder to increase its output by 0.1 volt per pulse. At the end of the third pulse the inputs to the A to D Amplifier are +0.3 volts from the Primary Ladder, and .31 volts from the Sample and Hold circuit, where a difference voltage of .01 times 10 will result in an output of 0.1 volt, which is insufficient to cause the Analog Comparator to supply further current. "3" having been digitized, the BCD Counter will now place a ground on the "3" line to all of the display tubes, so that the "3" will be caused to display in the least significant digit display device. The Secondary Ladder's output will be 0.3 volts, which is fed to Analog Storage where it is stored in a capacitor reserved for the third digit storage.

In summary, during the first digitizing timer period, the input to be measured was sampled and the most significant number was digitized and displayed. Its remainder was stored in Sample and Hold, and an analog value representative of the first digit magnitude was stored in Analog Storage. The Polarity Switch then disconnected the input from the instrument. The Counters were reset and the remainder voltage from Sample and Hold was connected to the input of the A to D Amplifier. Once again the instrument digitizes the second digit, displays the second digit, stores a value in Analog Storage that corresponds to the magnitude of the second digit, and stores the remainder in Sample and Hold. The Counter is reset and Sample and Hold is connected to the input of the A to D Amplifier and the last digit is digitized, displayed, and a value representative of the magnitude of the third digit is stored in Analog Storage. Since in the example given we were using a three digit voltmeter, the digitizing process is completed, and through we had a .1 volt remainder there was no place left to store it. This completes the MEASURE MODE of Operation.

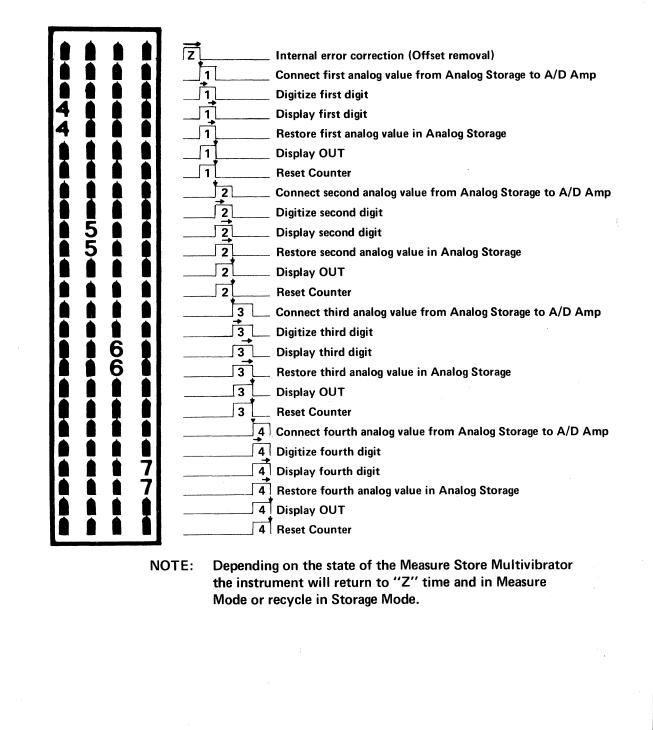

#### **STORAGE MODE**

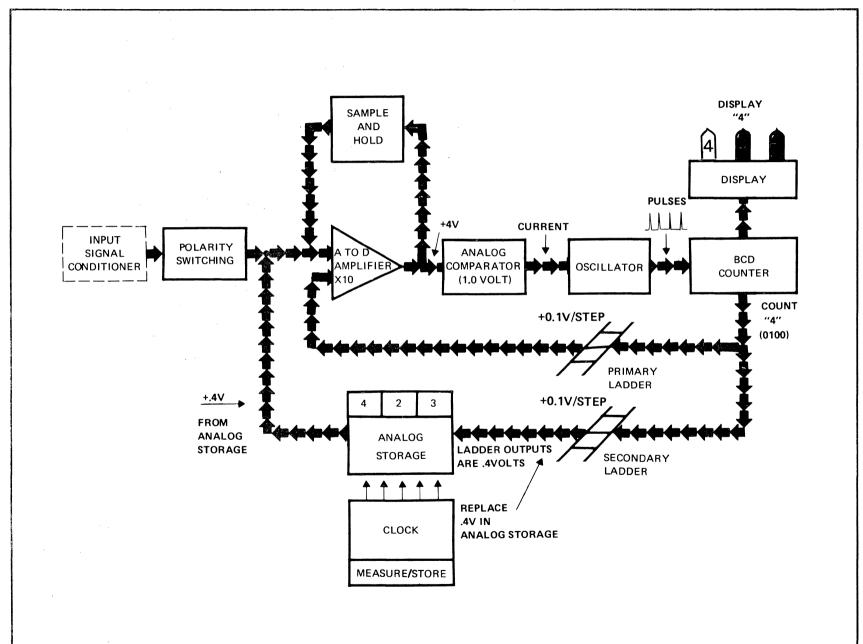

Recirculating Remainder instruments operate in two modes of operation - Measurement Mode and Storage Mode. It is interesting to note that during Measurement Mode, Recirculating Remainder stores analog voltages in Analog Storage, but they are never used in the Measurement Mode.

Taking the instrument into Storage Mode, the Sample and Hold circuit will not be used, and during the first time period the analog value stored in Analog Storage most significant digit position is connected to the input of the A to D Amplifier, and the digit is digitized and displayed and the Secondary Ladder replaces the value in Analog Storage. (See Figure 6.) Each digit is digitized in turn using the values that were stored in Analog Storage. Each time a digit is digitized as one of the final actions in that time period, the output of the Secondary Ladder restores the analog value in Analog Storage.

Depending upon the Sample Rate in Recirculating Remainder, it is customary for an instrument to operate in one measurement mode cycle and then six to eighteen storage mode cycles. In some cases where instruments are made for specific interface into systems such as the 8200, the 8300 and the 8400, instruments can be operated in a continuous measurement mode.

In summary, there are two modes of operation - Measurement Mode and Storage Mode. In the usual application an instrument proceeds through one Measurement Mode of operation and then several cycles of Storage Mode.

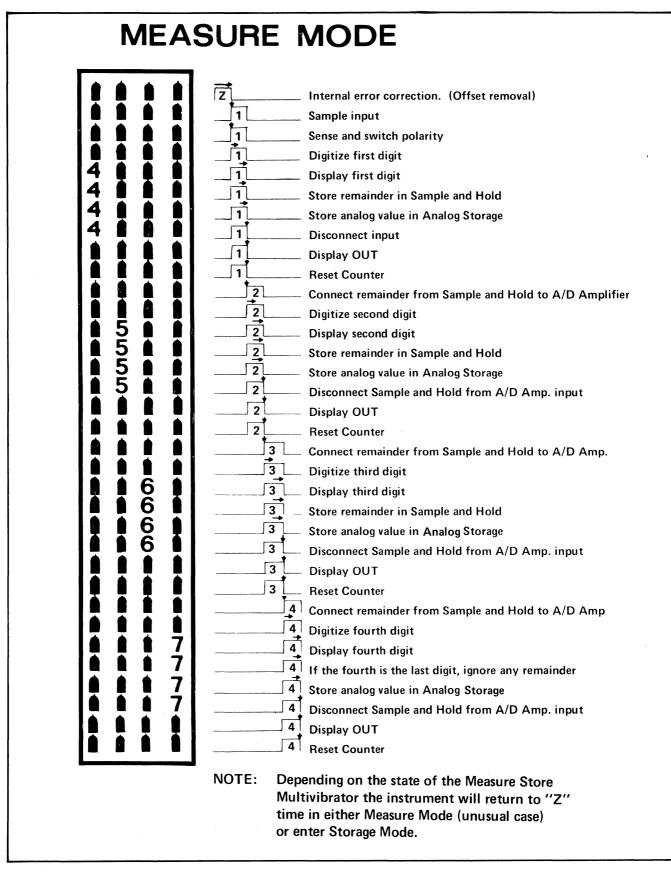

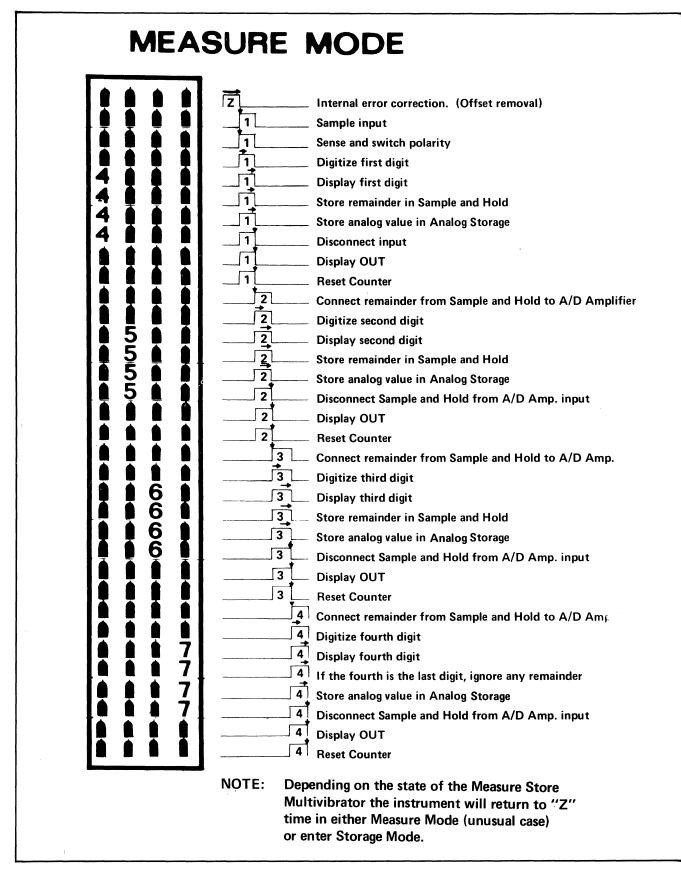

#### **MEASUREMENT MODE (Refer to Figure 7)**

#### Review and Highlight Time

There are several significant points that we must remember in order to understand Recirculating Remainder. There are two modes of operation - Measure Mode and Storage Mode. In the usual application, an instrument proceeds through one Measurement Mode of operation and then several cycles of Storage Mode.

#### A Review of the Actions in Measurement Mode.

#### **MEASURE MODE**

- a. The input is sampled.

- b. The first digit is digitized and displayed.

- c. The input is disconnected by the Polarity Switch.

- d. The remainder of the first digit is stored in Sample and Hold.

- e. An analog value is stored in Analog Storage for later use in the Storage Mode.

- f. The Counter is reset.

- g. The remainder voltage that was stored in Sample and Hold is connected to the input of the A to D Amplifier.

- h. The second digit is digitized and displayed.

- i. The remainder is stored in Sample and Hold.

- j. An analog value is stored in the second digit position in Analog Storage.

FIGURE 6.

FIGURE 7.

$\mathbb{R}^2$

- k. The Counter is reset.

- 1. The remainder from the second digit is connected to the A to D Amplifier and is digitized and displayed. This being the third and last digit the instrument is ready to proceed into Storage Mode.

#### NOTE!

After digitizing the last digit all three digits have been stored in Analog Storage, and at this point in time, the Measure Store portion of the clock causes the instrument to shift to Storage Mode of operation.

#### A Review of Actions in Storage Mode

#### STORAGE MODE (Refer to Figure 8)

- a. The first analog quantity from Analog Storage is applied to the A to D Amplifier and digitized.

- b. The first digit is displayed.

- c. Analog quantity is restored in Analog Storage.

- d. The display is extinguished and the Counter reset.

- e. The second digit is applied to the input of the A to D Amplifier from Analog Storage and digitized.

- f. The second digit is displayed.

- g. The second digit quantity is restored in Analog Storage.

- h. The display goes out and the Counter is reset.

- i. The third digit quantity from Analog Storage is applied to the input of the A to D Amplifier and digitized.

- j. Third digit is displayed.

- k. Third digit quantity is replaced in Analog Storage.

- 1. The display goes out and the Counter is reset, and the instrument is ready to start another cycle of either Storage Mode or Measurement Mode.

#### SCHEMATIC DIAGRAM DESCRIPTION

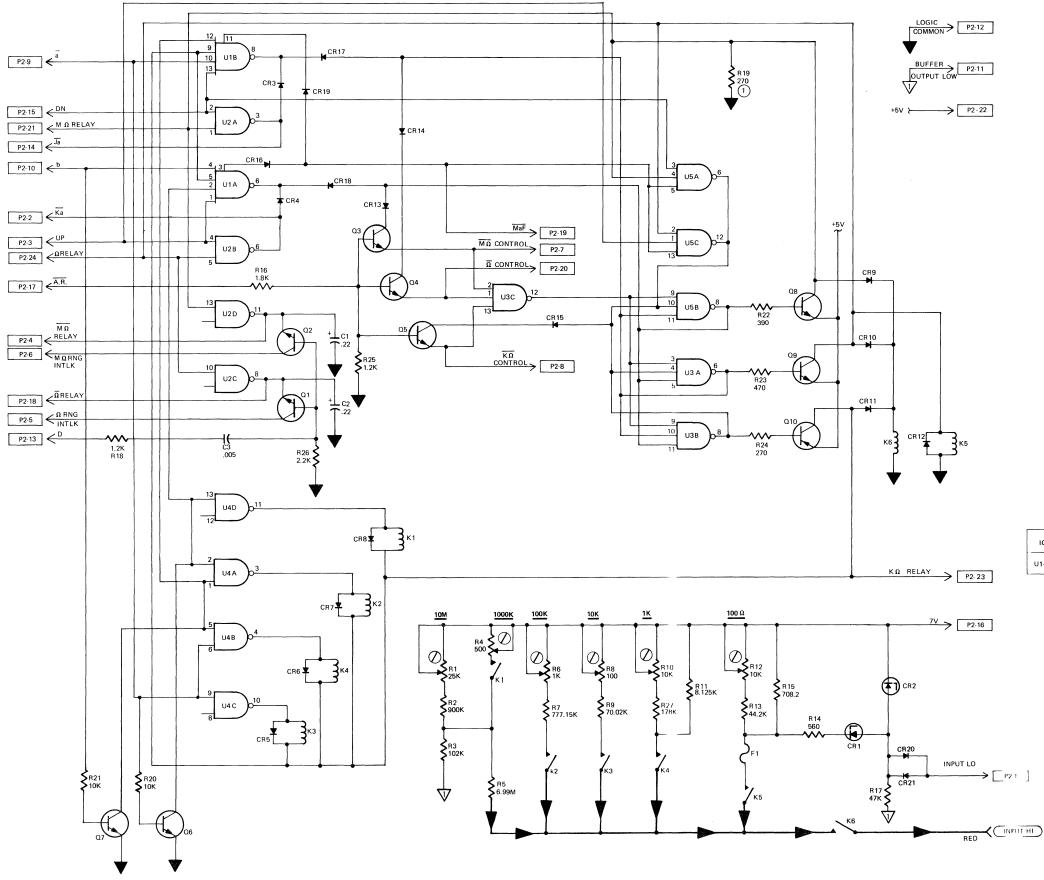

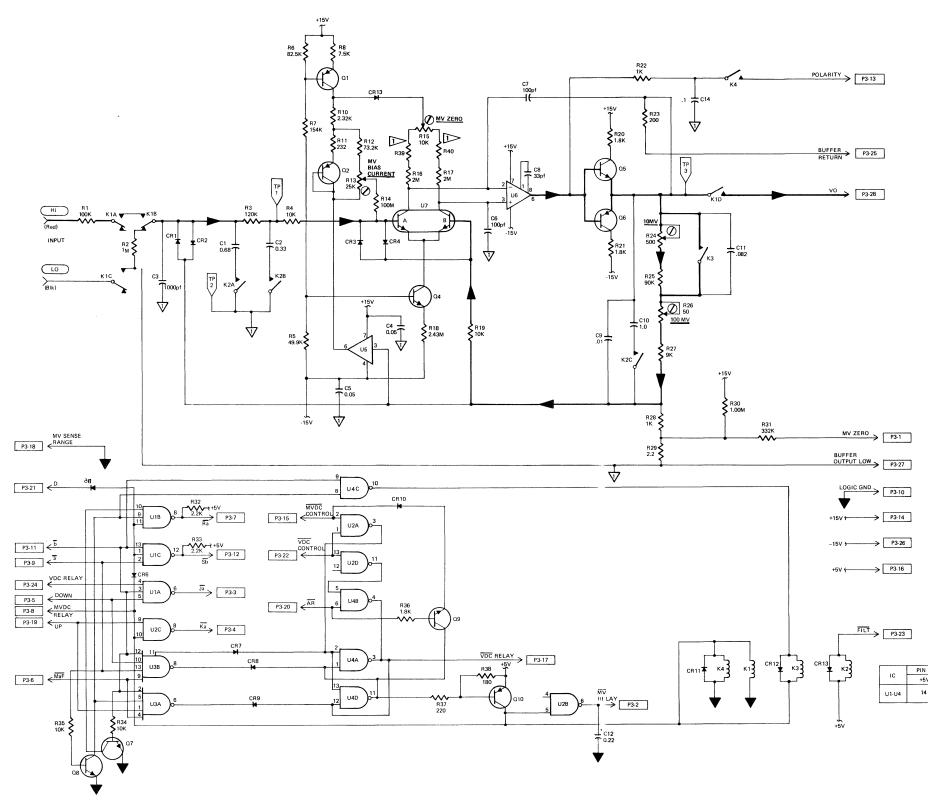

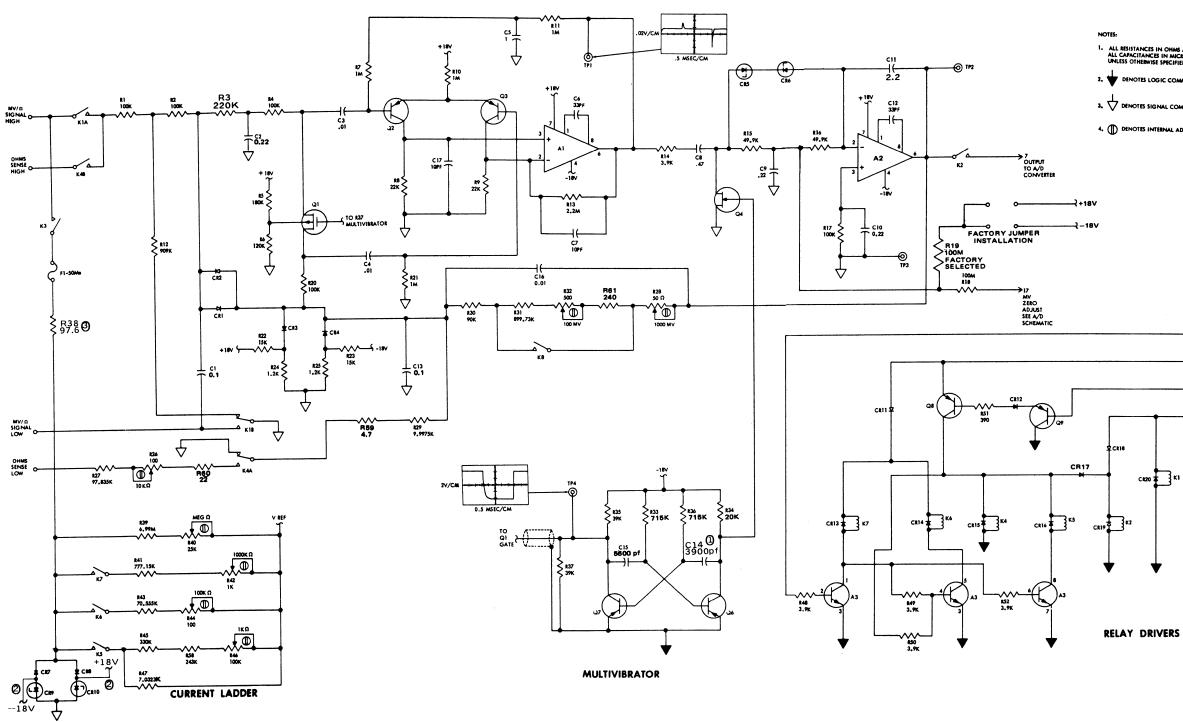

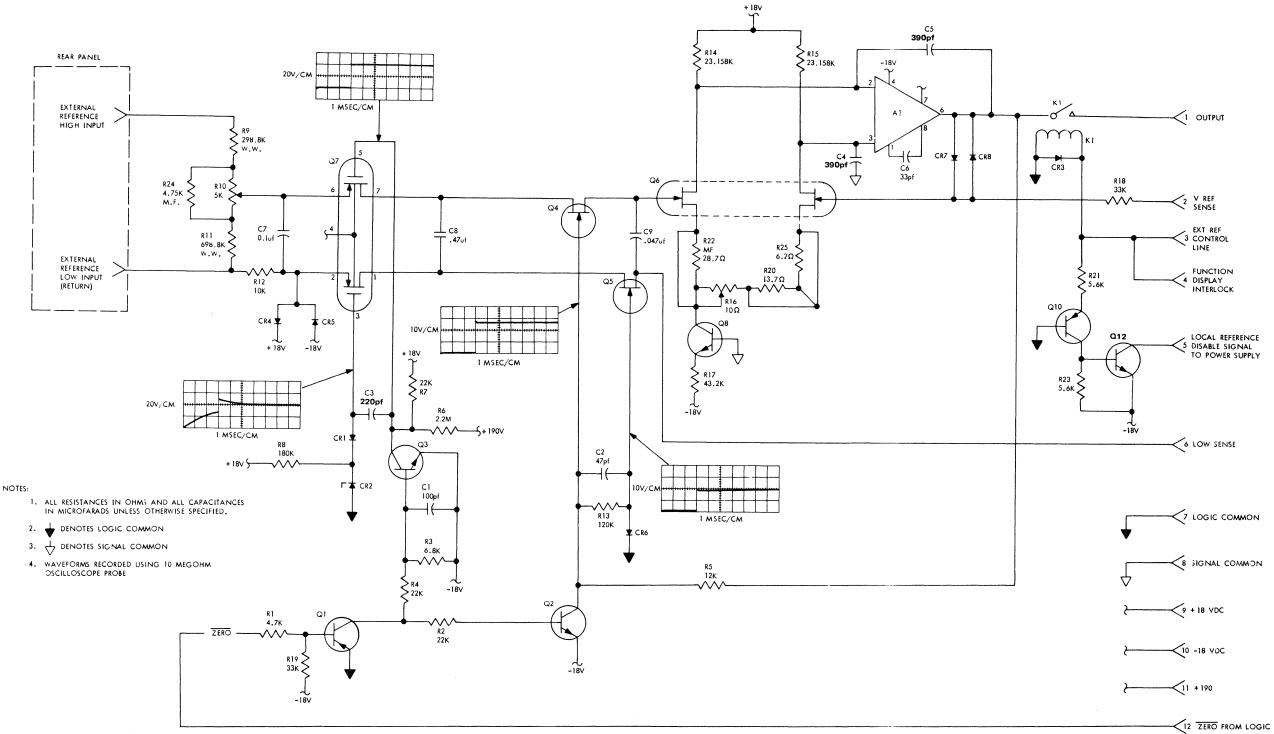

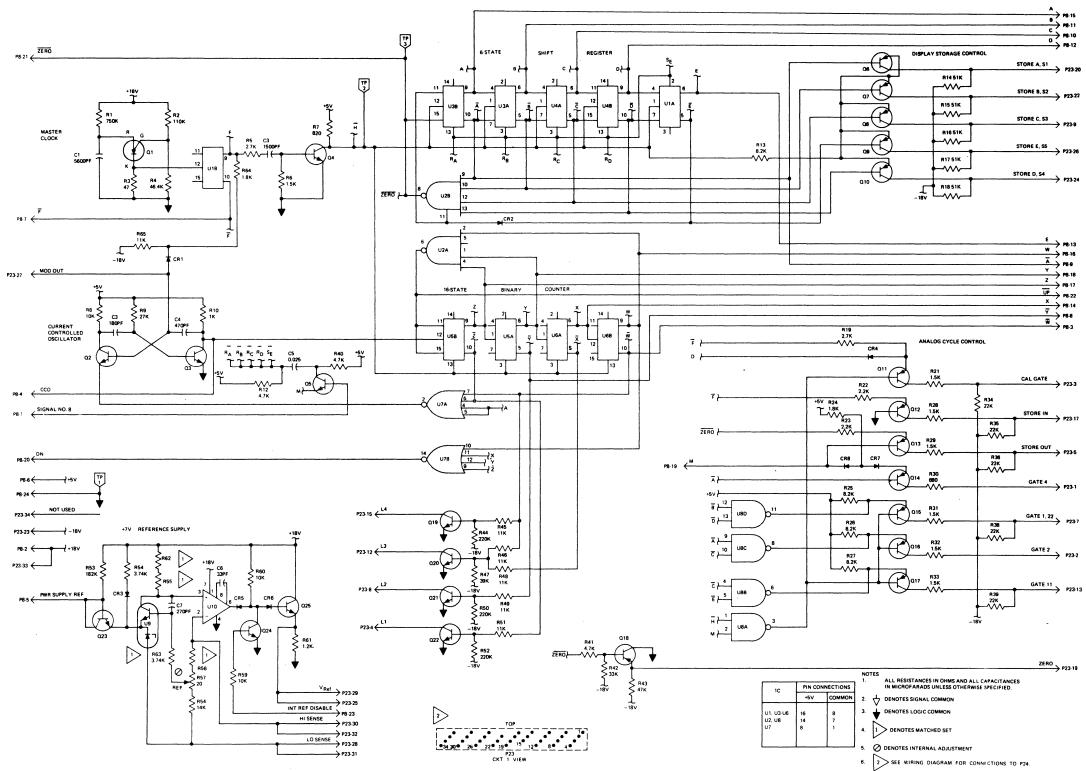

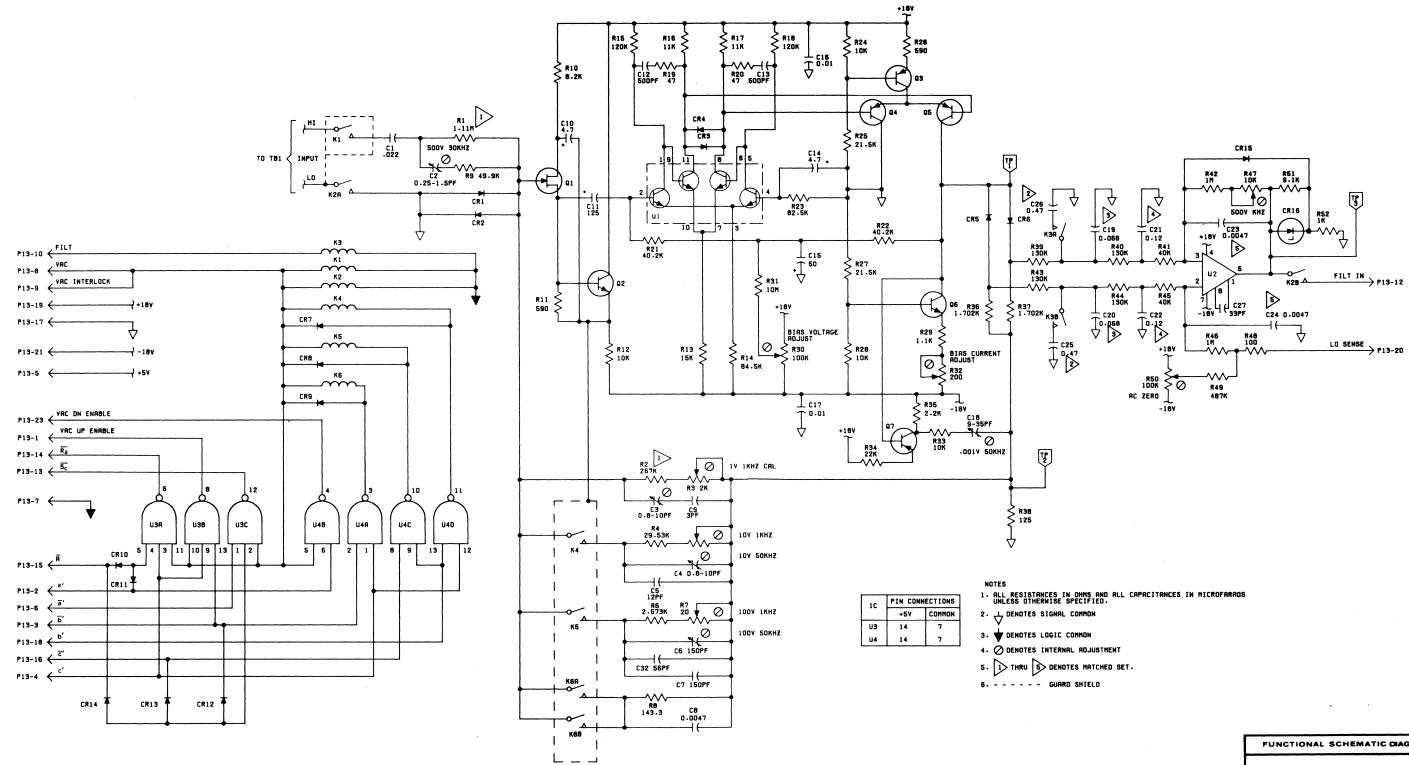

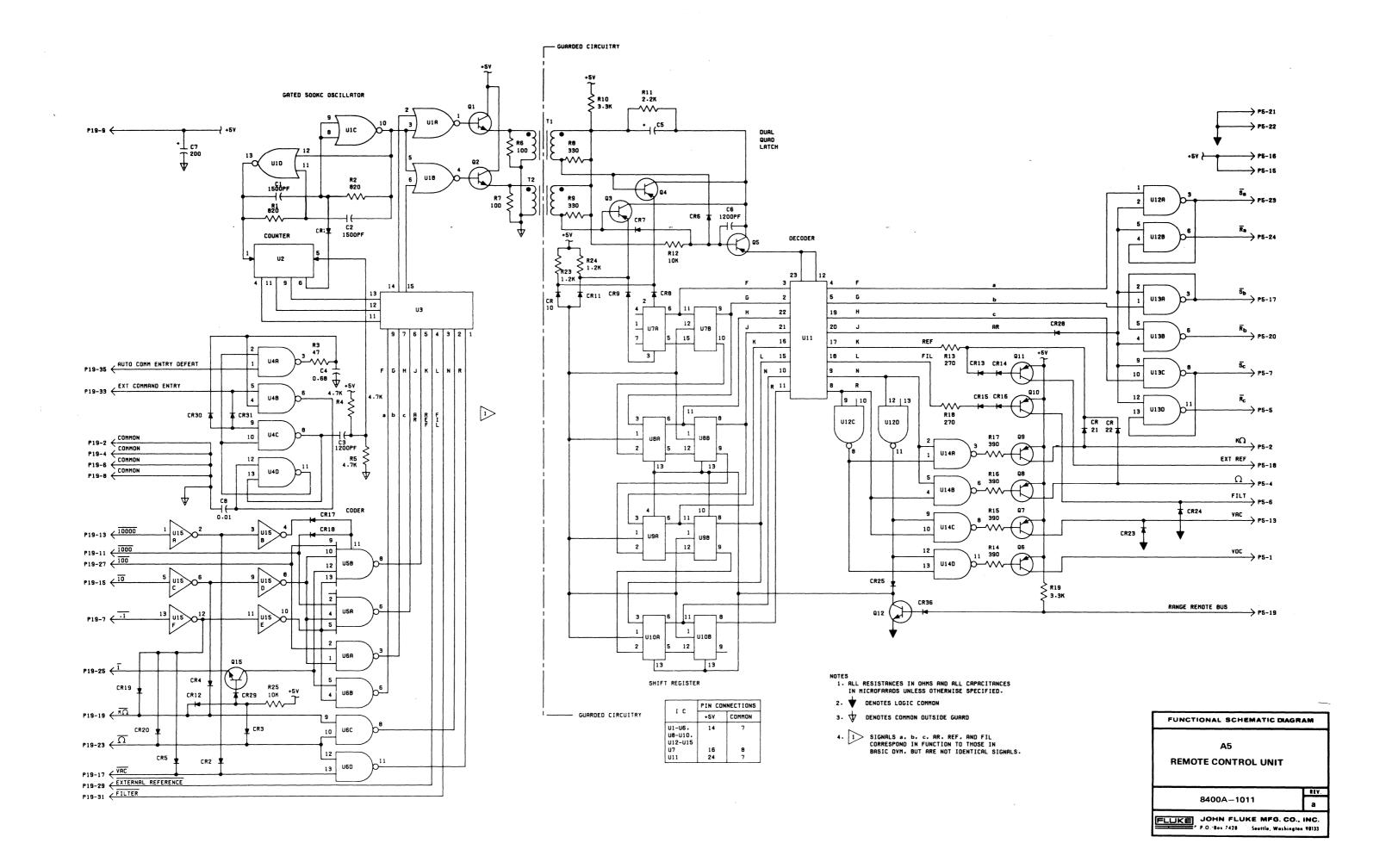

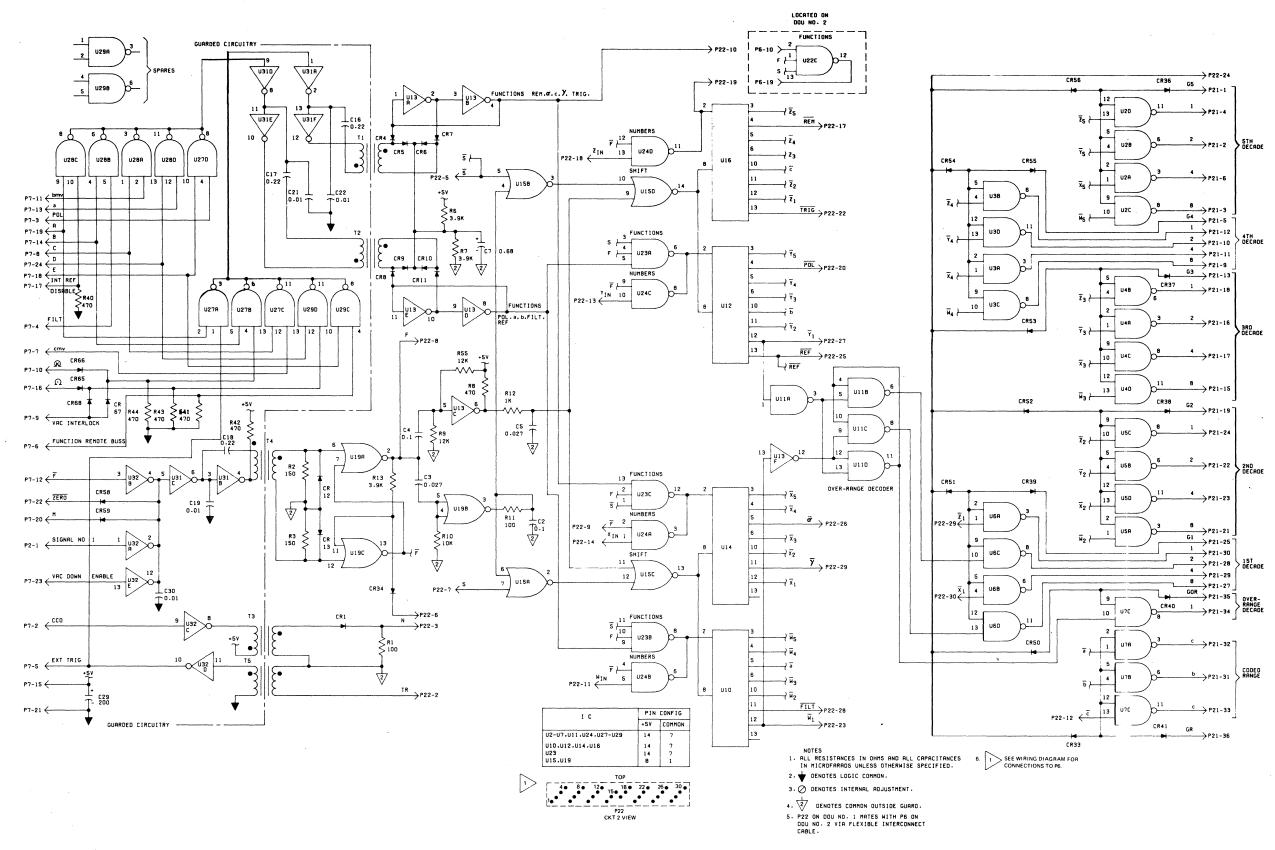

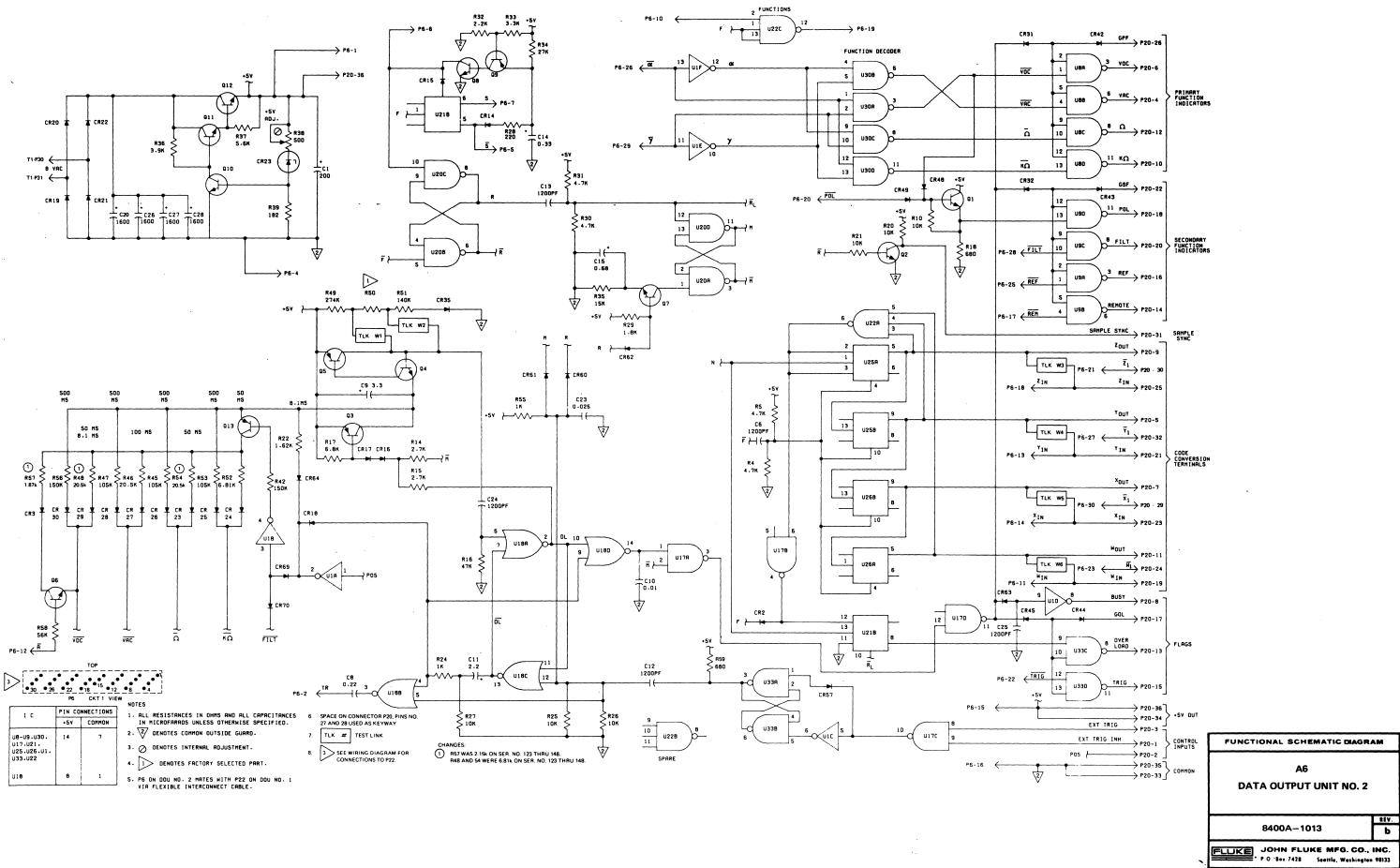

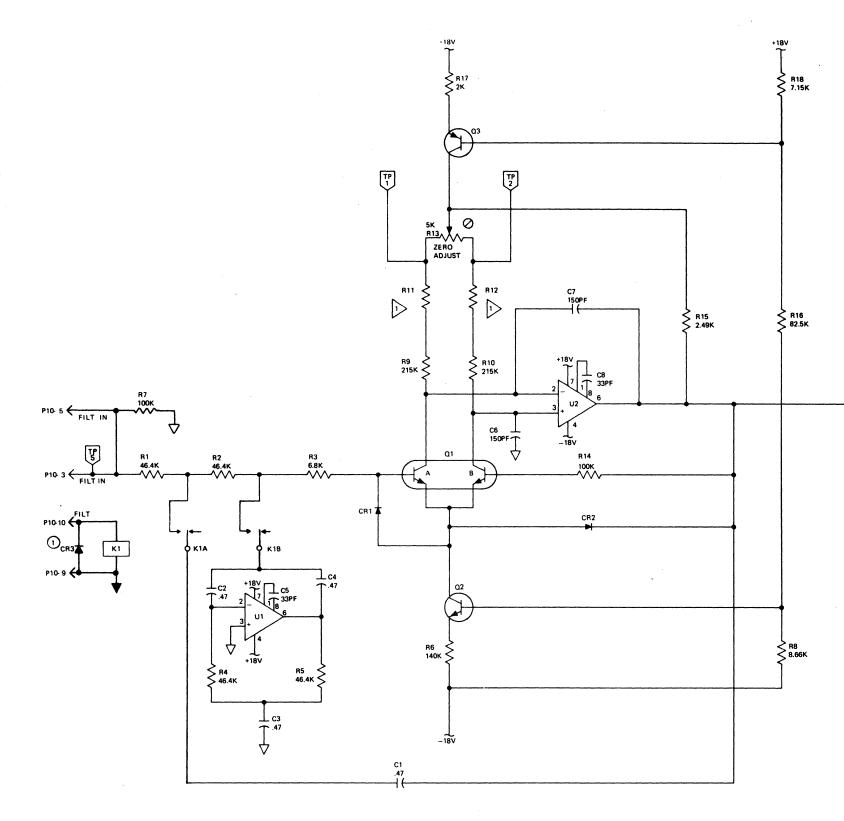

#### A TO D CONVERTER (Refer to Figure 9 and 10)

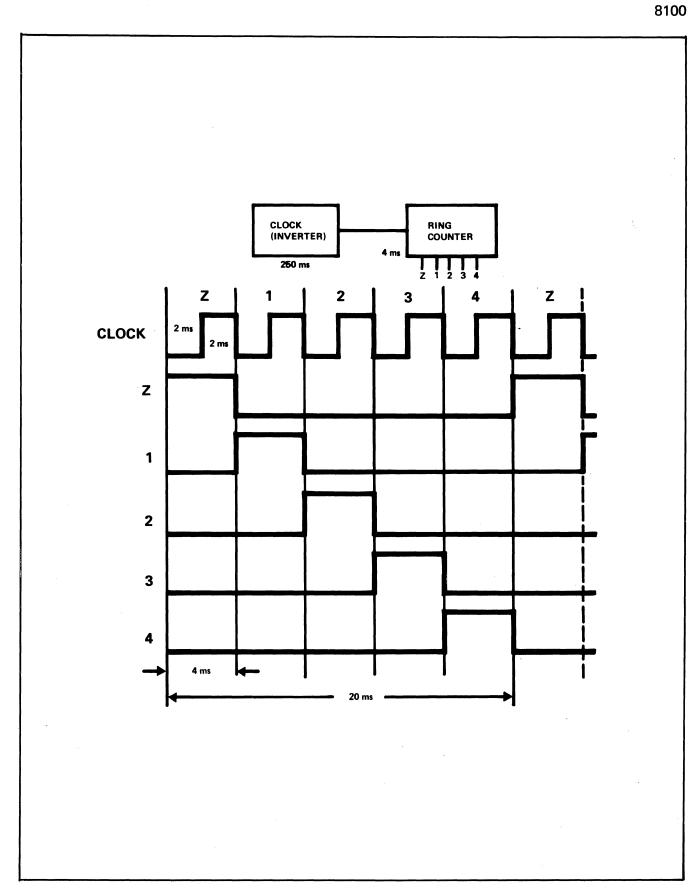

It has been demonstrated in the Block Diagram description that the Recirculating Remainder conversion process is synchronously operated. A Ring Counter fed by an internal Clock develops the time periods required. In our schematic example, the Ring Counter develops five time periods of 4 milliseconds each. The ZERO time period and four remaining periods identified as "1', "2", "3" and "4". Our example schematic has been stripped

of all circuits that are not essential to the description of the conversion process and does not include any of the refinements necessary for an accurate instrument.

## STORAGE MODE

FIGURE 8.

FIGURE 9.

$\mathbb{R}^2$

FIGURE 10.

15

$\mathbb{R}^2$

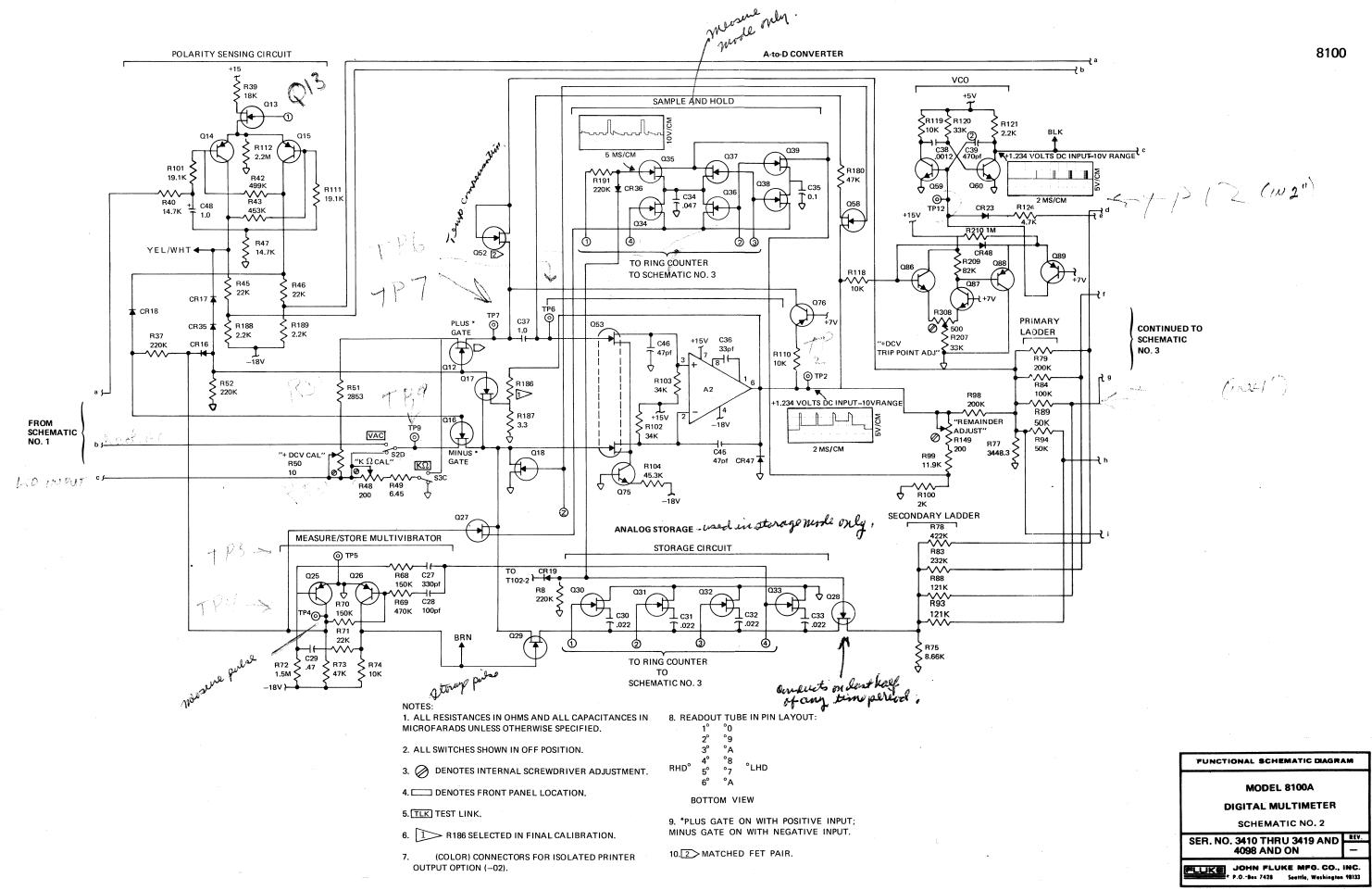

#### POLARITY SENSING CIRCUIT (Figure 9)

The Polarity Sensing Circuit is composed of Q13, Q14 and Q15 and their associated parts. Input from the Input Signal Conditioner arrives at R40. The "1" time period pulse is connected to the Gate of Q13 and enables it only when the instrument is in the "1" time period. The Measure Pulse arriving at the junction of R37 and CR16 enables Q14 and Q15. It is apparent that the Polarity Sensing Circuit is only functional when the instrument is in the "1" time period.

If the voltage arriving at R40 is negative, Q14 will conduct. This will cause Q12 and Q17 to conduct and apply the input from "+ DCV CAL" R50 to be applied to the input to the A - D Amplifier. Q17 is used to correct the polarity reversal error into the A - D Amplifier. The reason that a negative voltage at R40 causes the "PLUS GATE" to operate, rather than the "MINUS GATE" is due to the fact that the Input Signal Conditioner inverts the input voltage. (A plus voltage into the instrument will arrive at the Polarity Sensing Circuit as a minus voltage.)

Should the voltage arriving at R40 be positive, Q15 will conduct and cause the "MINUS GATE" Q16 to conduct.

#### A/D AMPLIFIER

The A/D Amplifier is a monolithic, differential amplifier, in an operational amplifier configuration with a gain of 10. In instrument applications, this amplifier has been refined with circuits to make temperature corrections, fast feedback networks to prevent saturation and a variety of other refinements.

#### ANALOG COMPARATOR

Q61 is connected to the output of the A/D Amplifier, with its Base connected to 1.0 volt reference. When the Emitter voltage exceeds 1.0 volt the transistor will conduct and supply voltage to the Voltage Controlled Oscillator of VCO. The greater the voltage on the Emitter, the greater will be the source power for the VCO.

#### VCO (Voltage Controlled Oscillator)

The VCO is a multivibrator formed by Q59 and Q60. It has no output until supplied voltage by the Analog Comparator. The pulse repetition rate of the VCO is proportional to the voltage magnitude being fed to it. The greater the voltage, the higher the pulse rate. The output of the VCO is fed to the Counter.

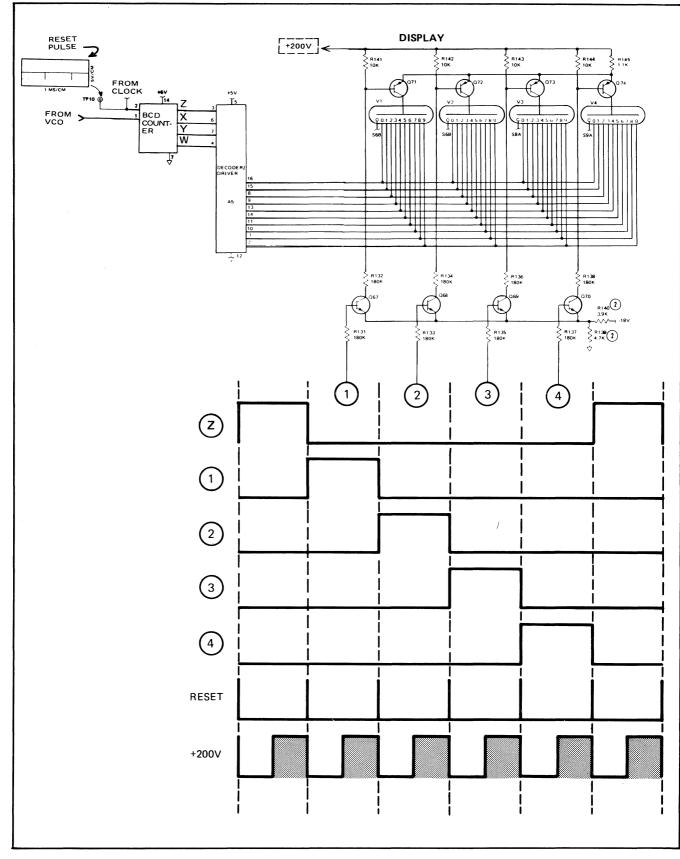

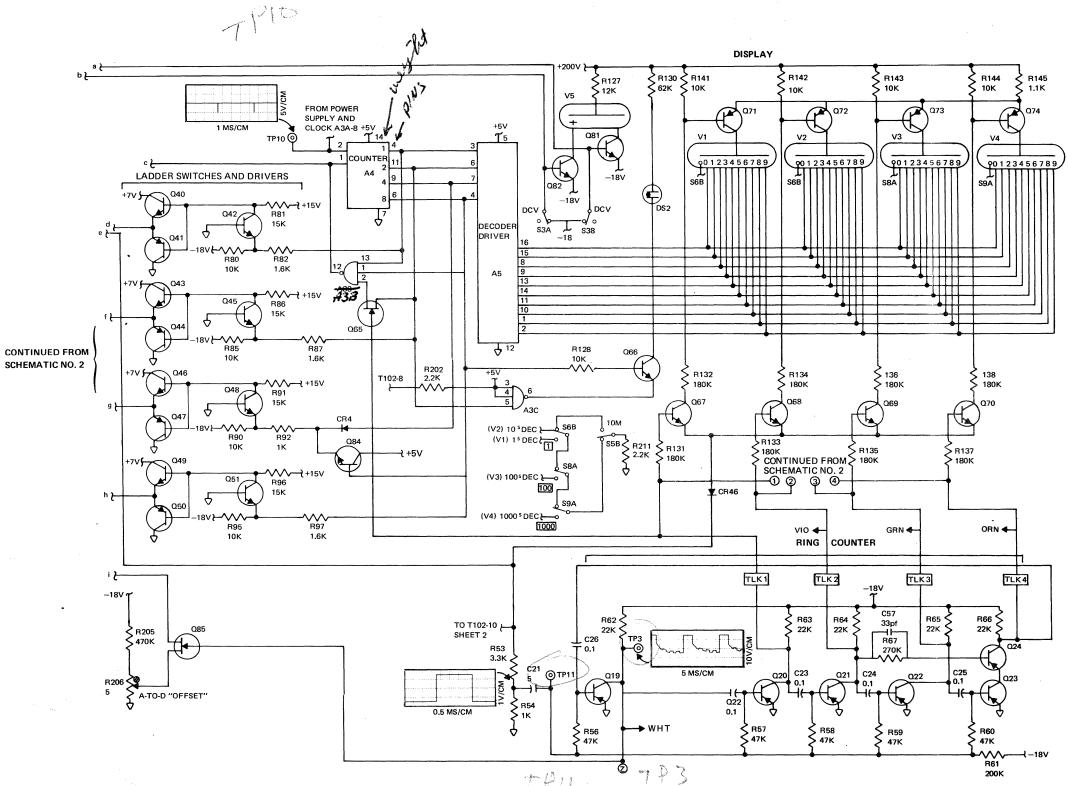

#### **BCD COUNTER**

The BCD Counter is an in-line logic pack counter. It is note-worthy that the BCD Counters used in FLUKE instruments are of a variety that are sixteen state counters. This makes it impossible to replace them with the normal "garden variety" counters with ten states. The counter translates the pulses from the VCO into BCD or Binary Coded Decimal format. Refering to Figure 10, the Reset Pulse, which occurs at the end of each time period can be seen. The BCD output of the Counter is fed to the Ladder Switches and Drivers. The BCD output also feeds the Display circuit.

#### LADDER SWITCHES AND DRIVERS

The output of the 16 state BCD Counter is fed to transistors Q40 through Q51. The output of the ladder switches is applied to both the Primary Ladder and the Secondary Ladder. Each Ladder comprises a

4-bit, weighted-resistor, digital to analog converter. The output of each of the ladders is 0.1 volt per pulse counted, the format of the Ladders is binary 1248. The Primary Ladder feeds the A/D Amplifier input to balance the input to the differential amplifier. The output of the Secondary Ladder feeds analog voltages to the Analog Storage circuit, to be stored for use in the Storage Mode of operation.

#### ANALOG STORAGE

Each capacitor in the Analog Storage circuit stores an analog voltage that represents the digit developed in each particular time period. For example: C31 stores an analog value that will cause the circuitry to digitize the number that was developed in the second digitizing time period of the last Measure Mode. Q28 conducts during the last half of every time period (after digitizing has been accomplished in that time period). Q30 through Q33 conduct during the time period pulse connected to their respective GATES. Q29 conducts during Storage Mode and allows the voltage stored on the individual capacitors to be applied to the input to the A/D Amplifier.

#### **MEASURE/STORE MULTIVIBRATOR**

The one-shot multivibrator, composed of Q25 and Q26 has dual synchronizing inputs. The Measure Pulse (approximately 20 milliseconds) is coincident with the conduction of Q26. The multivibrator is triggered at the end of each cycle by the trailing edge of the "4" time pulse. If C29 is sufficiently discharged, the trailing edge will cause the multivibrator to flop and Q26 to conduct, otherwise Q25 continues to conduct and the instrument remains in Storage Mode (approximately 320 milliseconds).

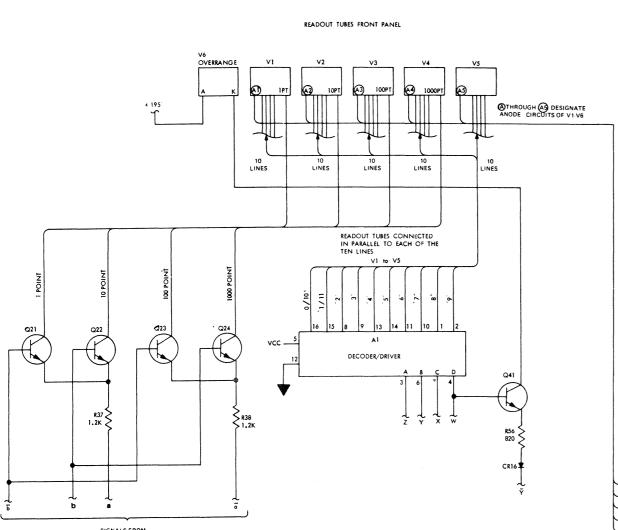

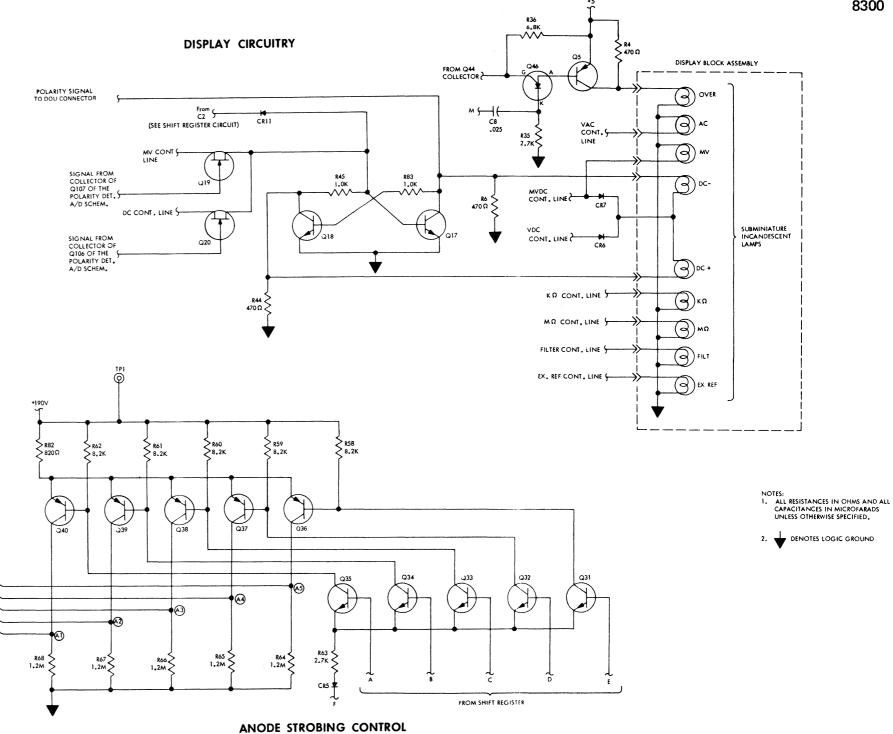

#### DISPLAY

The Display circuit is shown in Figure 10. Note that the +200 volts as shown in the timing diagram is high only during the last half of each digitizing time period.

The Decoder Driver accepts the BCD output from the Counter and translates it to a decimal ground, i.e., if the BCD count were "4-2" or 6, the Decoder Driver would place a ground potential on the "6" line to all of the display tubes. The anode of the appropriate tube would be allowed to receive the +200 volt pulse in the last half of the time period and display the 6. As an example, consider the "3" digitizing period which will place a HI on the base of Q69, causing it to conduct. Q69 conducting will lower the voltage on the base of Q73, which will cause it to conduct and allow the +200 volts to ionize V3 during the last half of the "3" digitizing period.

#### FACTS IN REVIEW:

- a. Two Modes of operation, STORAGE and MEASURE.

- b. Input is sampled only during MEASURE MODE and "1" digitizing time.

- c. Sample and Hold is used only during MEASURE MODE.

$\sim$

d. ANALOG STORAGE receives its initial voltages during MEASURE MODE, but they are not used until the instrument is in STORAGE MODE.

#### 8100A DIGITAL MULTIMETER OPERATIONAL THEORY

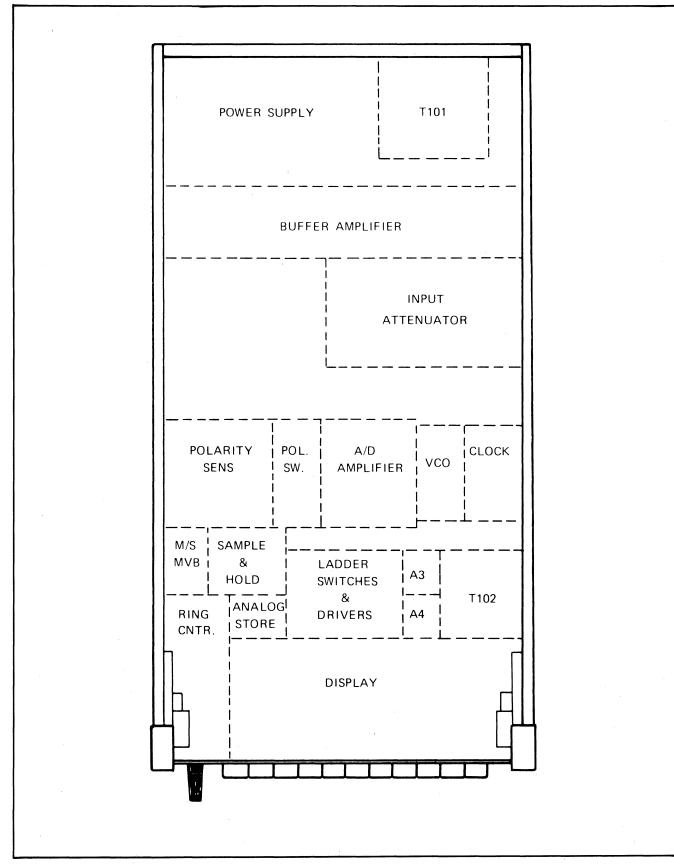

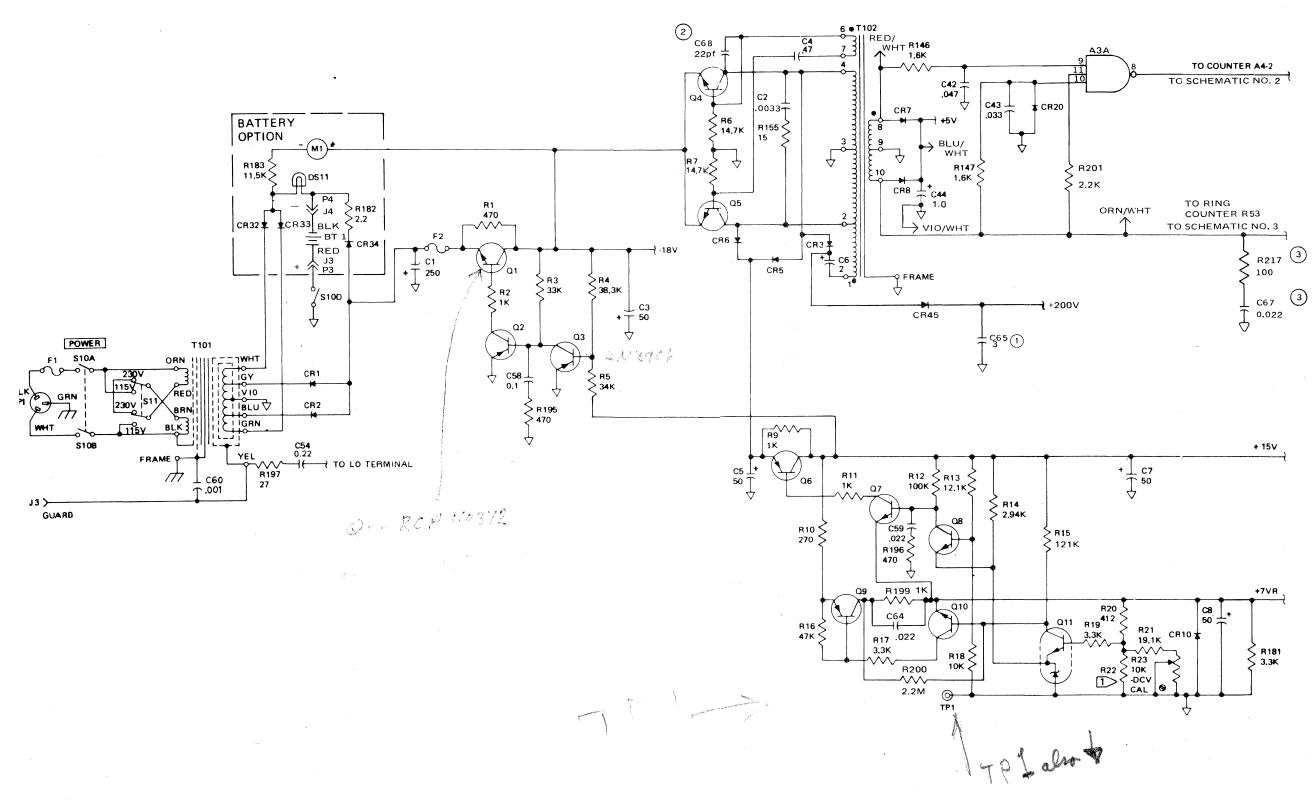

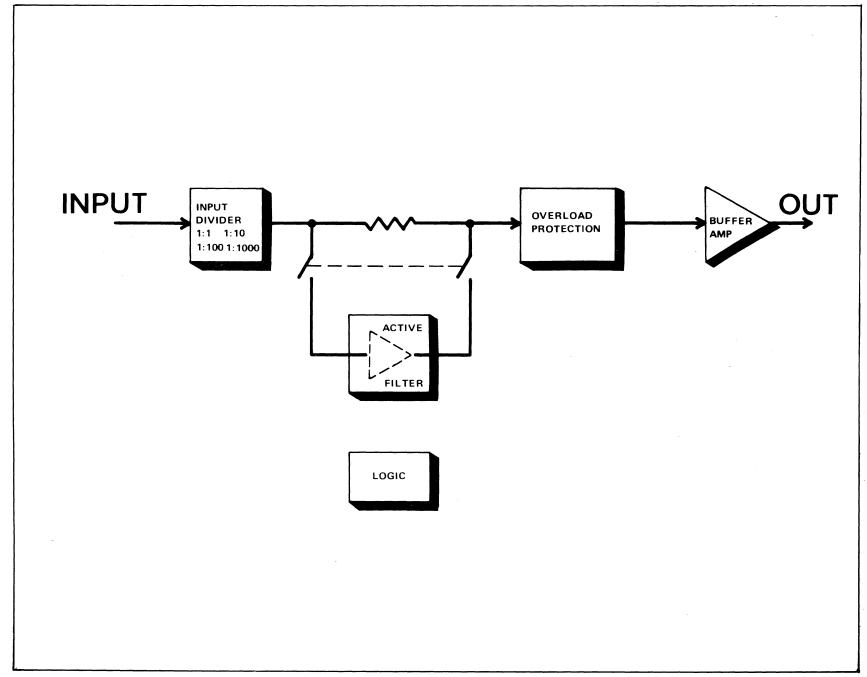

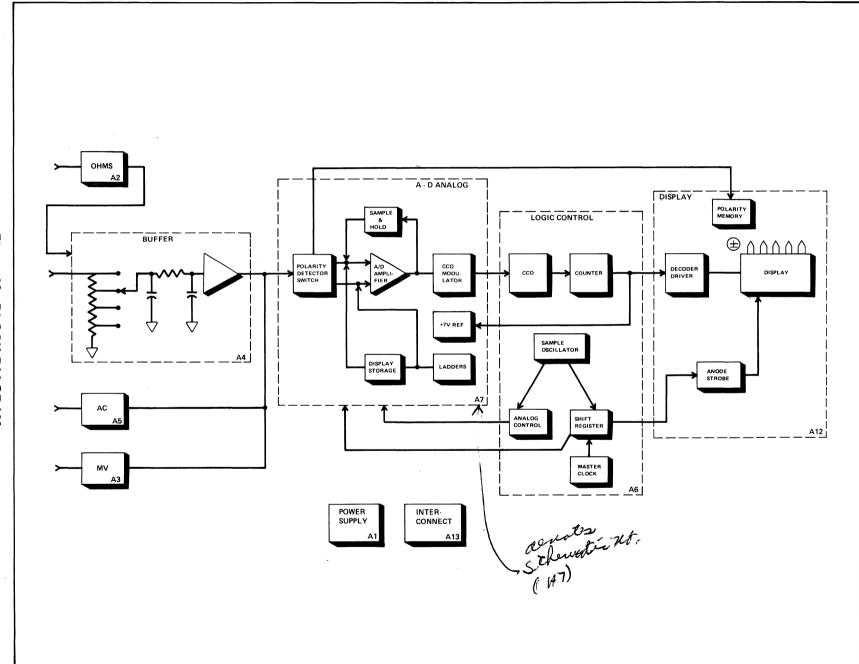

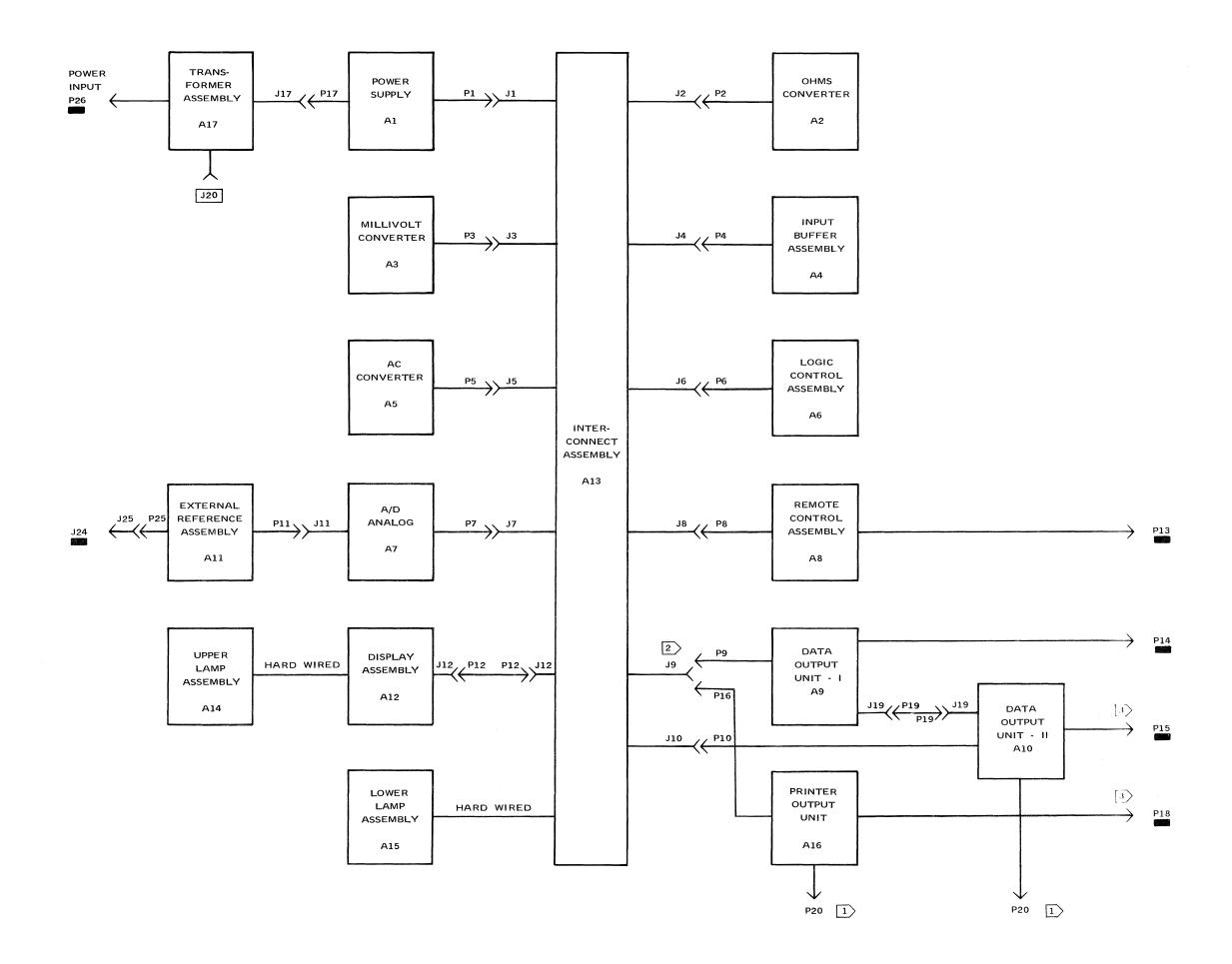

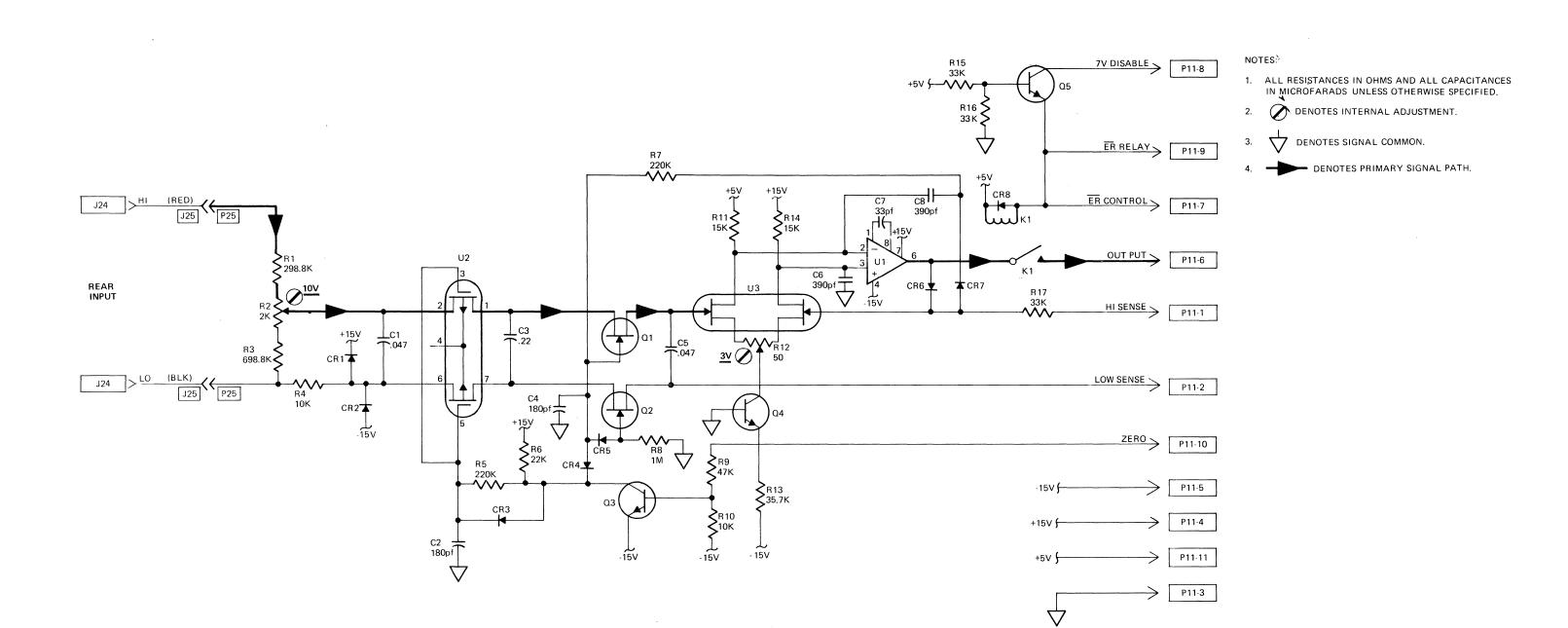

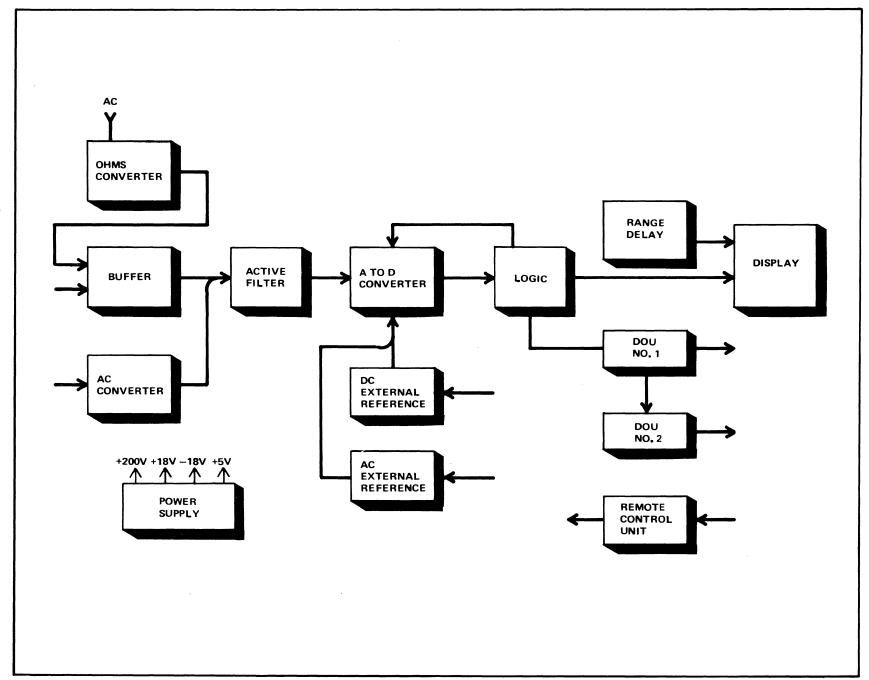

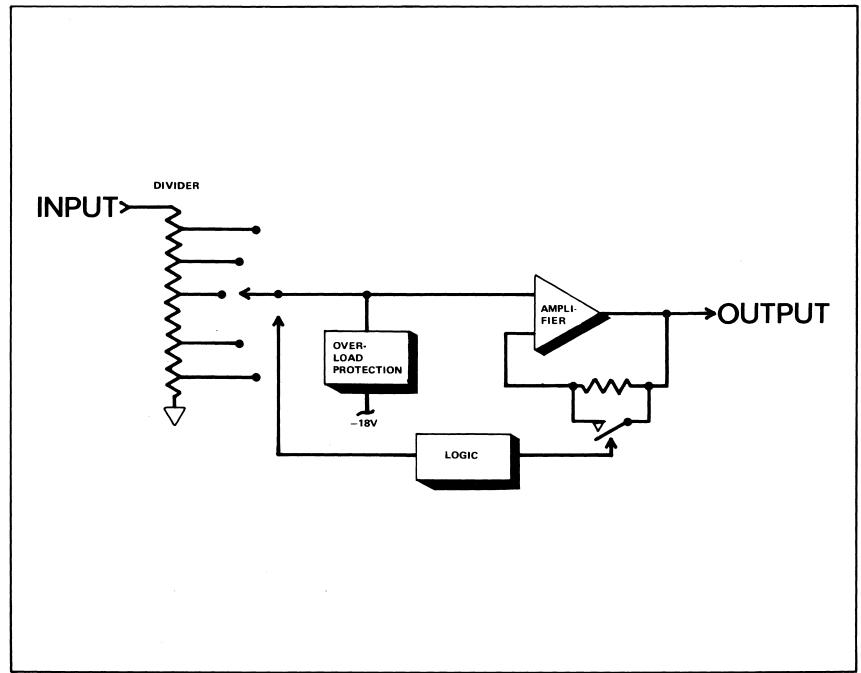

The 8100A consists of three main sections, referring to Figure 1 and the Schematic Drawings.

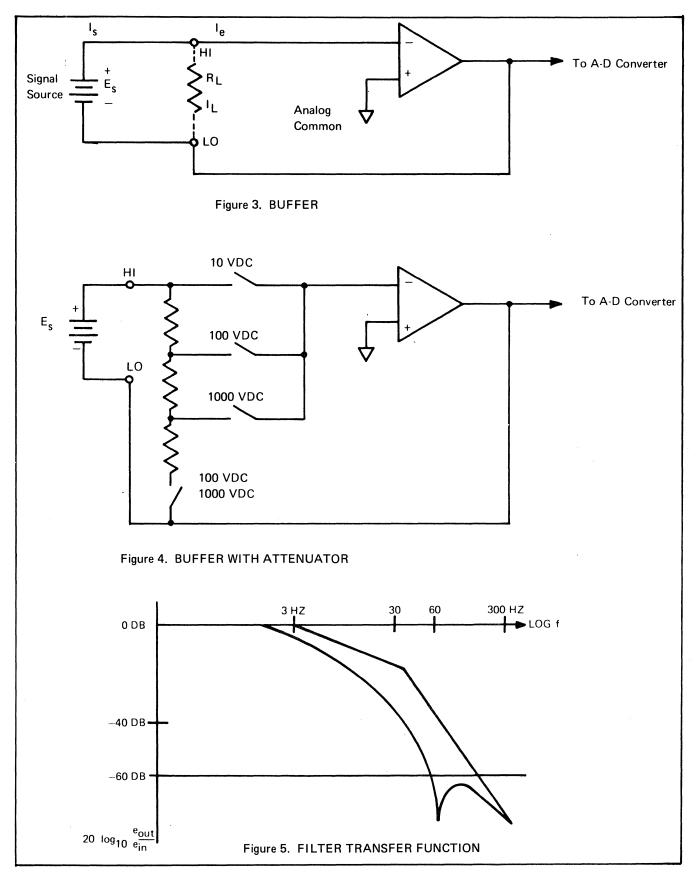

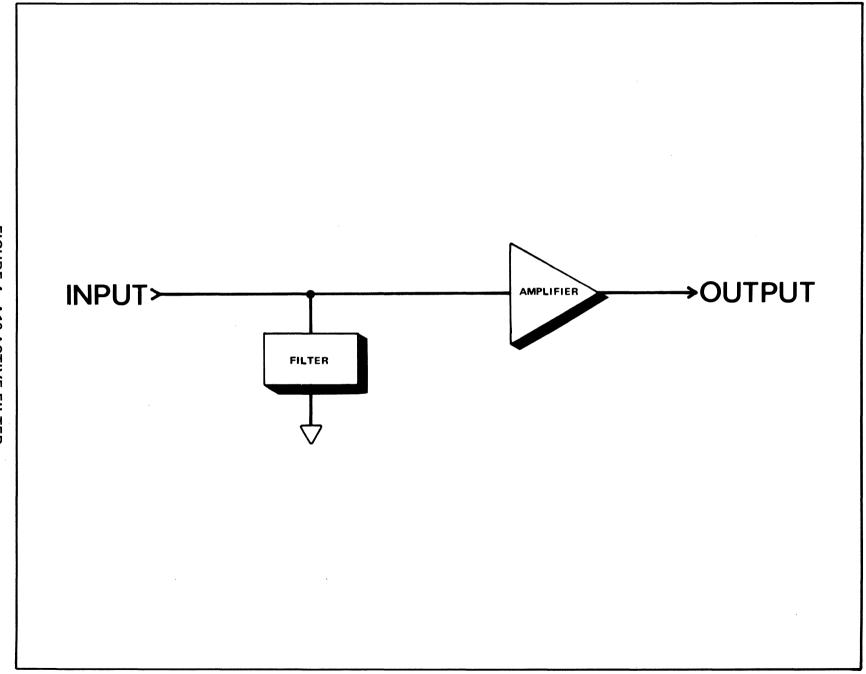

- 1. The Buffer section acts as a signal conditioner, capable of dividing voltage inputs, filtering and impedance conversion. The input divider also functions as a portion of the current source in the resistance ranges. (See Figure 2)

- 2. The Analog/Digital Conversion system, accepts the output from the Buffer and digitizes it using FLUKE'S Recirculating Remainder system of conversion. The unit samples three times a minute and recycles every 20 milliseconds.

- 3. The display section accepts the BCD output of the Analog to Digital Converter and puts it into ten line decimal output and displays the result on NIXIE tubes on a timed pulse basis.

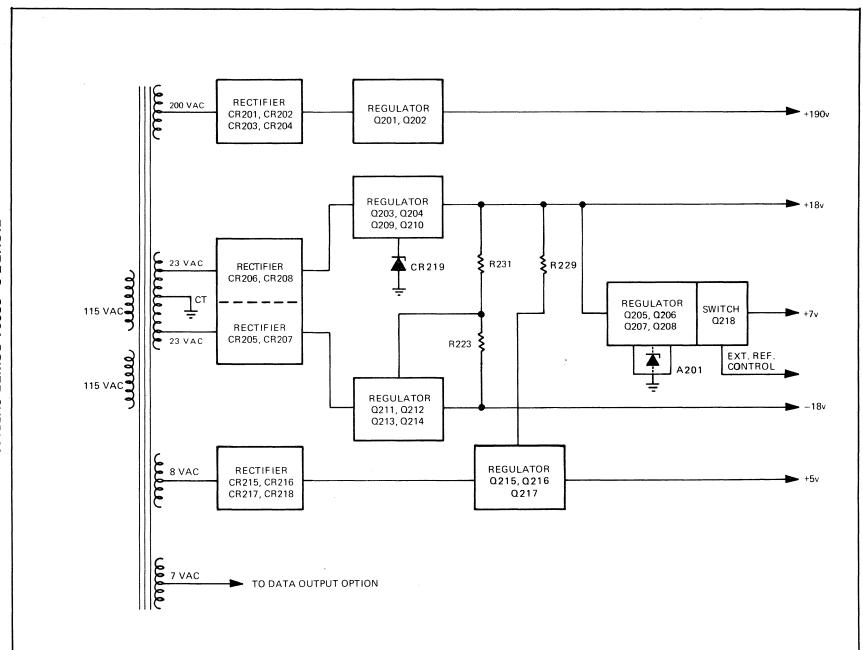

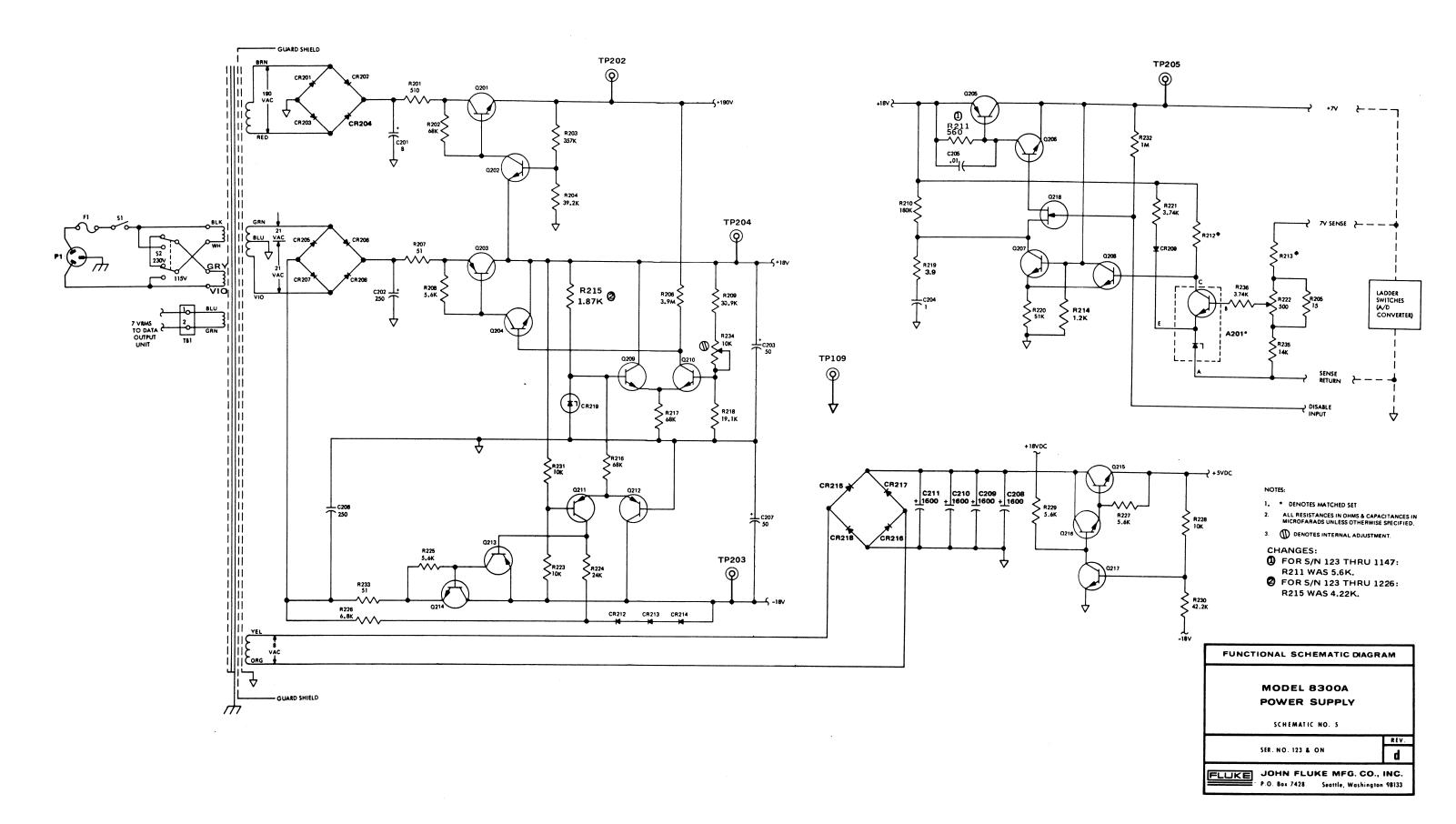

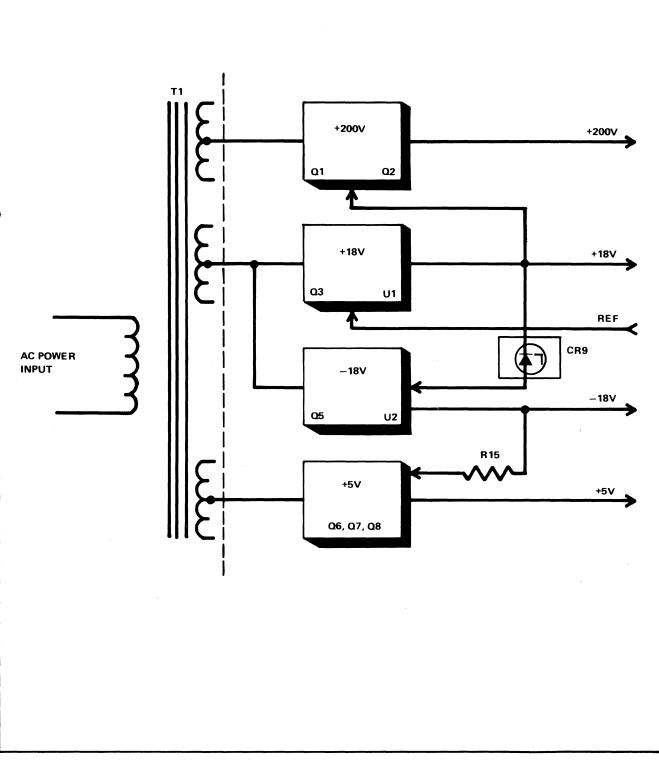

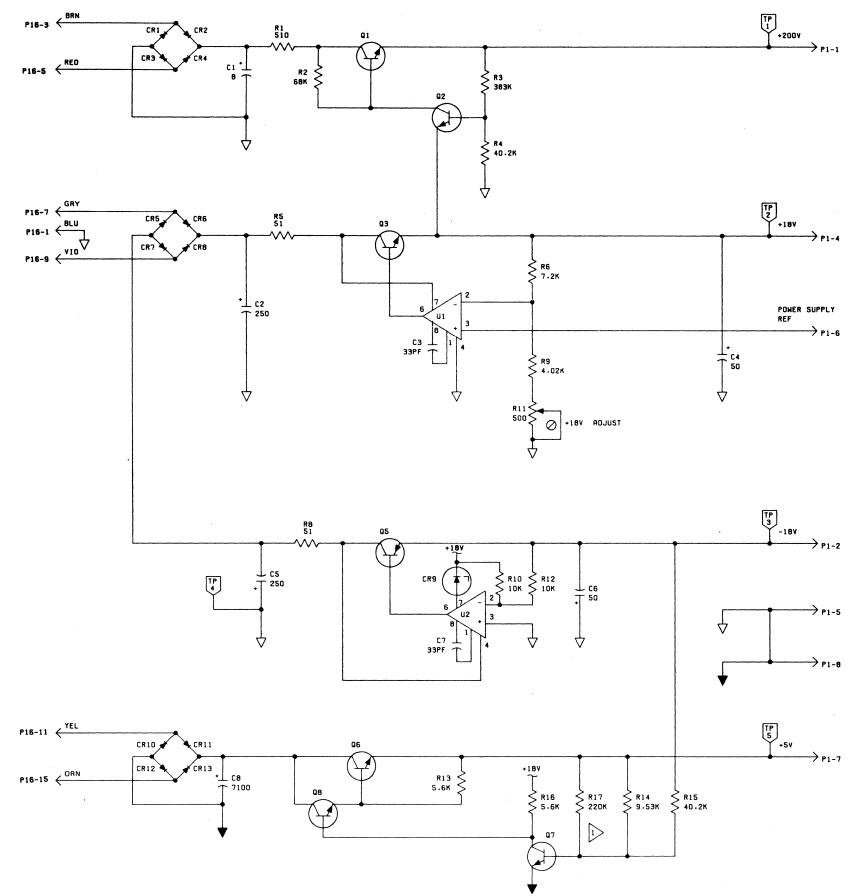

In addition to the three main sections described above, the Power Supply serves dual functions. (See Figure 3 and Schematic No. 4). In addition to supplying the voltages required by the instrument it also contains an inverter that is used to both produce operating voltages for the instrument and supply the clock or synchronization for timing the instrument.

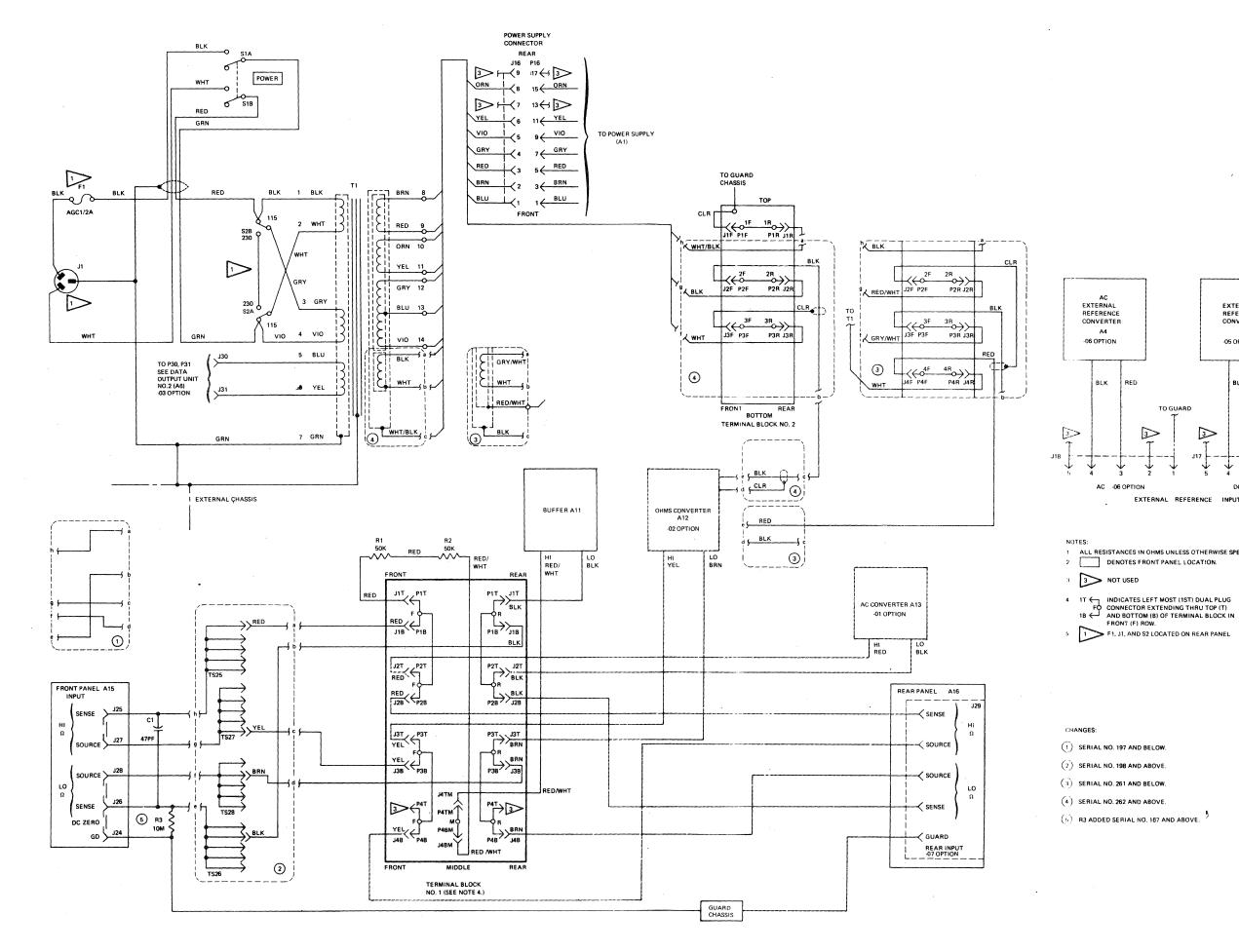

Power for the 8100A is supplied by either the AC power line or via the internal battery pack, as furnished with the -01 option. When operated from line voltage transformer, T101 provides two outputs. One output is rectified and filtered and used for the -18 volt supply in the instrument. The other winding provides a higher voltage which is rectified and used to charge the battery option, through DS11 which acts as a series limiting element.

The voltage supplied by the line voltage conversion is always greater than the voltage from the batteries, back biasing CR34 which prevents draining the batteries. The negative voltage, from either the batteries or the rectifiers CR1 and CR2, is regulated and filtered after passing through the protective fuse, F2, and then on to supply the instrument all of it's negative voltage needs.

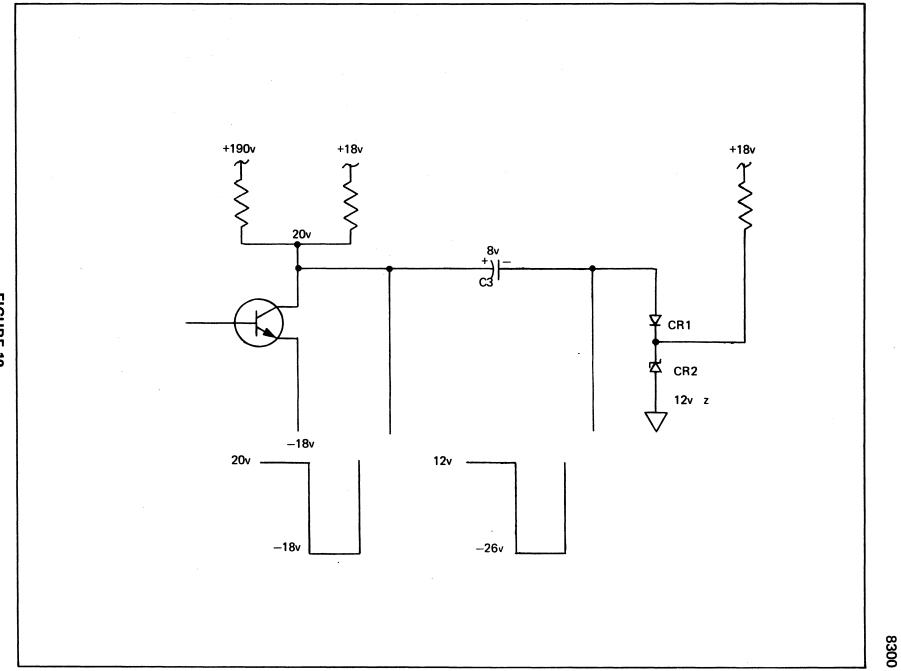

The -18 volts operates a 250 Hz inverter consisting of Q4, Q5 and a driver transformer T102. The output voltages from T102 are then conditioned to supply the remaining potential needs of the 8100A.

A high voltage winding (100V) operates a doubler rectifier circuit which provides 200V dc. This +200V dc is used to pulse the readout tubes.

T102 also provides one output which is rectified and filtered to +5 volts which is used to supply all of the integrated circuit logic. Another winding of T102 provides a voltage which is rectified and regulated to provide the +15 volts needed as a positive supply in the instrument. This +15volts is further dropped by a zener regulated circuit to provide the +7.0 volt reference needed in the 8100A. This +7.0 volt reference supply has a fixed load of 2 ma in R181 and is protected from current reversals when an overload occurs in the ohms configuration by CR10.

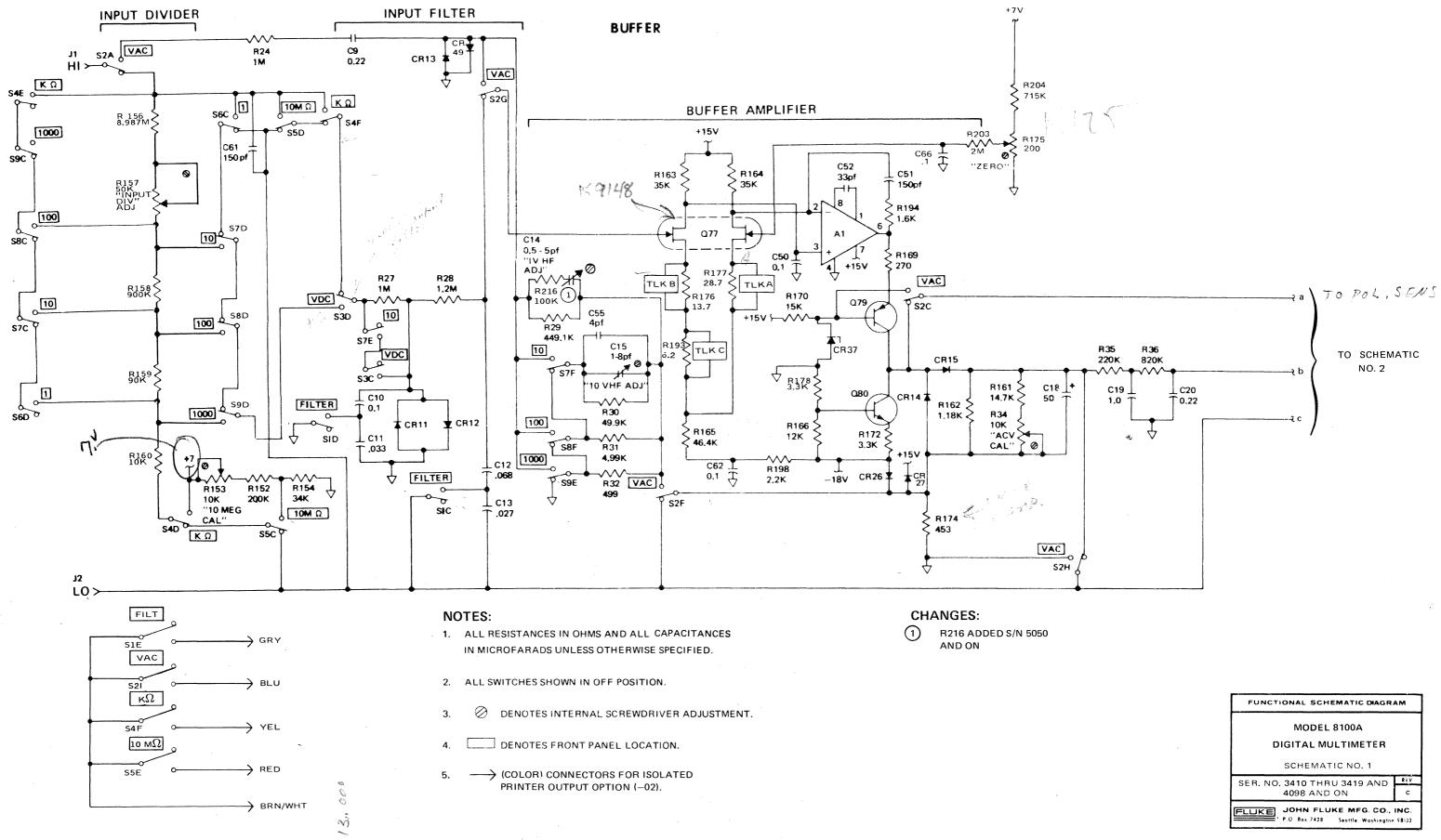

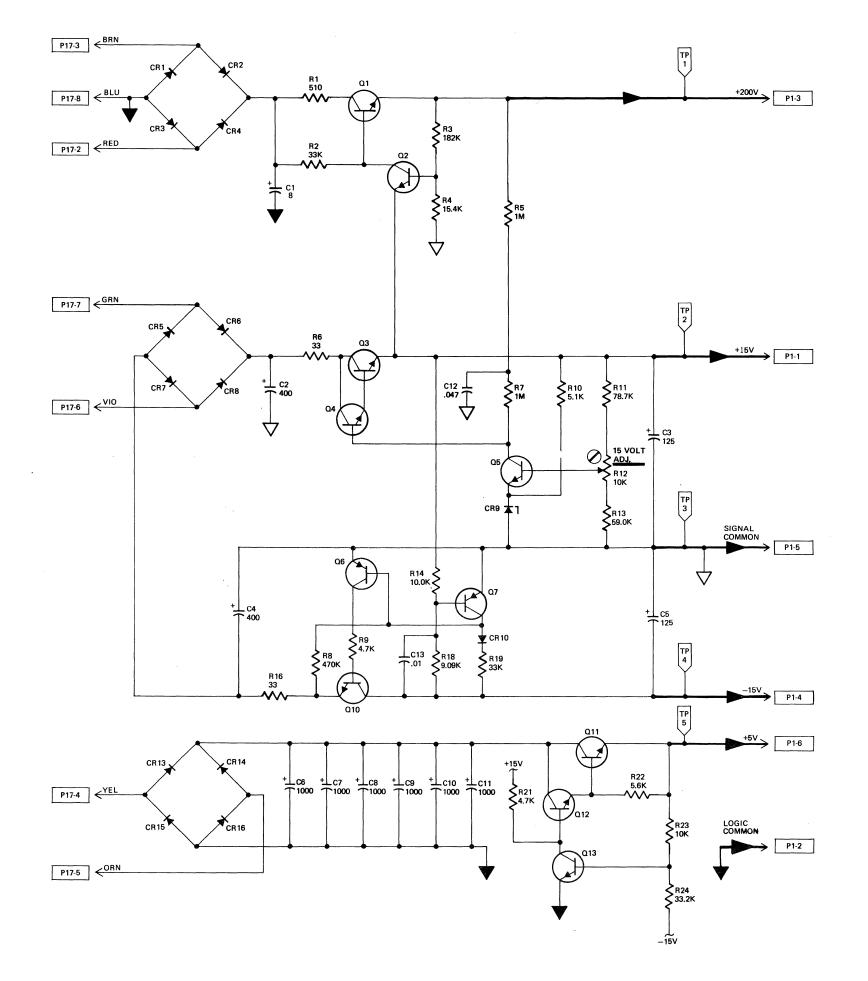

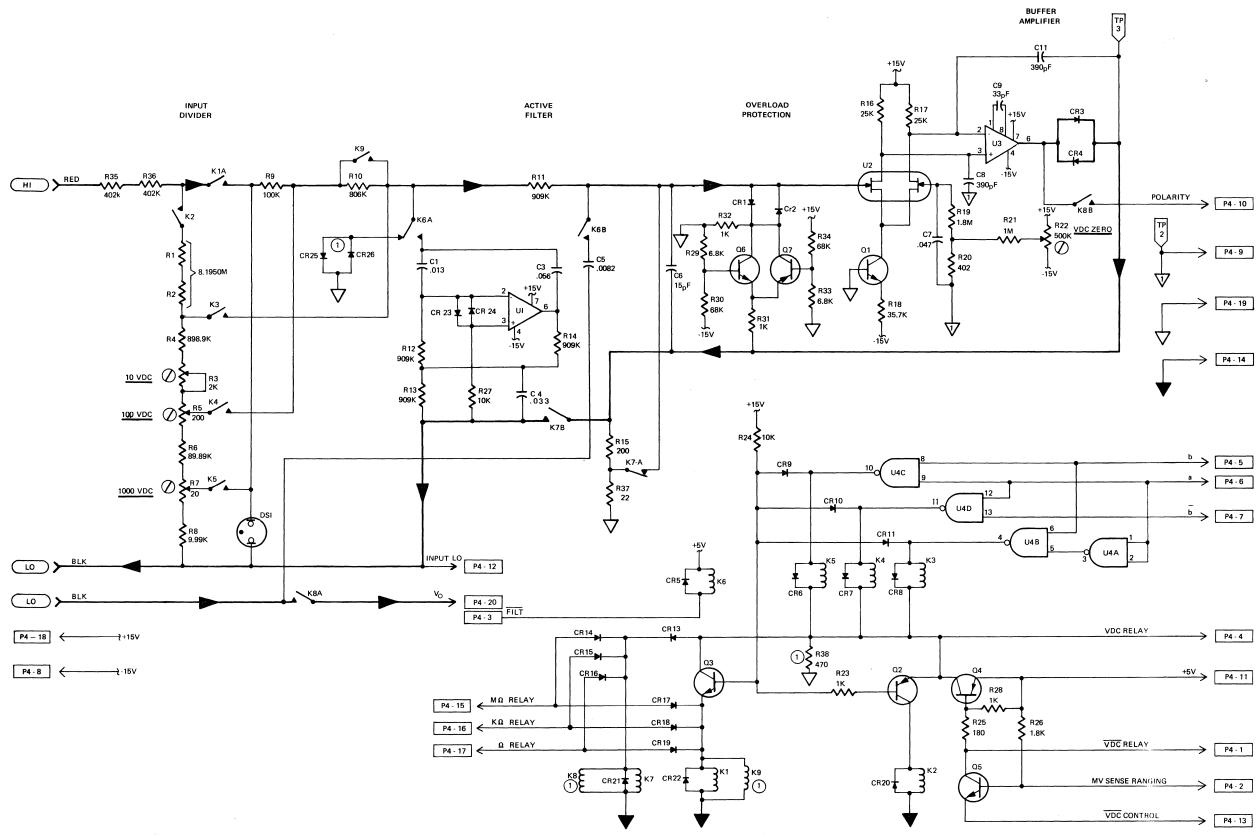

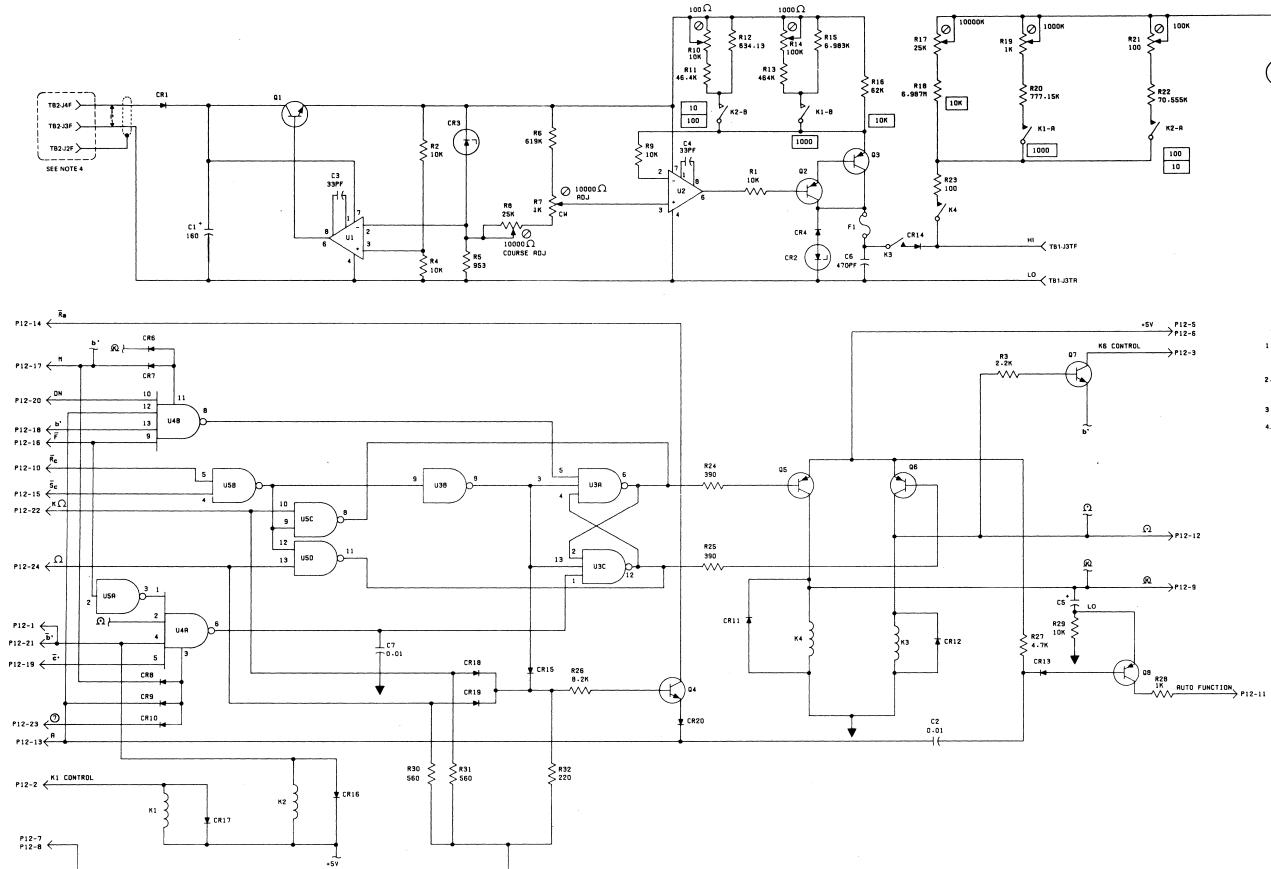

#### INPUT RANGE DIVIDER (Figure 2 and Schematic No. 1)

The function switching on the front panel will provide one of the four basic configurations shown in Figure 2. When the instrument is operated in the DC volts position the divider will provide divisions of 1, 10, 100 and 1000 in order to maintain a 1 volt input into the Buffer. The input divider consists of R156, R158, R159, R160 and R157 is provided for calibration.

Figure 1. 8100 BLOCK DIAGRAM

8100

Ν

8100

Figure 2.

ω

200v RECTIFIER DOUBLER BATTERY CHARGE CIRCUIT COUNTER (A4) RESET T101 100 VAC ז 115/230v 37 VAC 8 VAC 250 Hz —18v INVERTER REGULATOR **M** 26 VAC 3.4 VAC (CLOCK) 20 VAC REFERENCE RING COUNTER NEGATIVE SUPPLY +15 v +15v REGULATOR REF. +7v REFERENCE +7v VOLTAGE

Figure 3. 8100 POWER SUPPLY

8100

In the K Ohms function, the bottom of the input divider (R160) is removed from the common binding post and connected to the +7.0 volt reference supply. The divider now acts as the current supply for resistance measurements.

In the 10M Ohm function the bottom end of the range divider is connected to divider R152 and R154 which can be adjusted by R153 to provide 10M Ohm calibration.

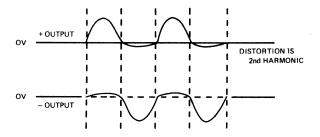

When the AC Volts function is selected the input configuration is changed to an operational rectifier. A pair of rectifier diodes is placed inside a strong feedback loop. A negative feedback signal proportional to the input voltage is developed across R161, R162, R174 and calibration pot R34, which is fed to the A-D Amplifier.

#### **INPUT FILTER**

The output of the Range Divider is fed into a two pole, passive filter consisting of R27, R28, C10, C11, C12 and C13. (Filter switch out). The settling time is .25 sec and 60 Hz is attenuated about 20 db. With the Filter switch depressed, C10 and C13 are removed from the circuit and the settling time becomes 1 second and 60 Hz is now attenuated about 60 db. CR11 and CR12, together with R27 provide protection for both the filter and the Buffer amplifier from excessive voltage inputs. In the 10 volt range, R27 is switched out since the output impedance of the range divider is 1M Ohm and R27 is not needed.

#### **BUFFER AMPLIFIER**

Q77 is a low noise, low drive J-FET pair, operating in a common source configuration and serves as the input stage to the Buffer Amplifier configuration. R175 is the zero adjustment pot, which in conjunction with R176, R177 and R188 forms a network by which the initial offset of Q77 can be reduced to zero. The output of Q77 drives A1, a monolithic operational amplifier, which provides the bulk of the gain. C51 is placed around A1 to provide a smooth roll off through unity gain. Q79 is a common base output stage whose purpose is to raise the output impedance of the amplifier as high as possible. In order to avoid degrading the high output impedance, Q79 operates into a constant load current, Q80. The Buffer amplifier feedback loop is completed through diodes CR14 and CR15, which provide a voltage step around zero to drive the following polarity sensing circuit. R174 provides the load resistance for the amplifier.

When AC Volts function is selected, the buffer amplifier is connected as an operational rectifier with R24 as the input resistor, AC coupled through C9 and R29, R30, and R32 as the negative feedback ranging resistors. Diodes CR14 and CR15 now act as an operational rectifier. The positive half cycles only flow through CR15 and R162 where they develop a half wave rectified DC voltage proportional to the average value of the AC input. The high output impedance of Q79 and Q80 aids appreciably in improving the linearity at low levels where the threshold voltages of CR14 and CR15 tend to lower the amplifier loop gain. The half wave rectifier output is smoothed by two stage RC filter R35, C19, R36 and C20 to provide a 1 volt full-scale output for the A-D Converter. Because the input capacity of Q77, along with additional stray capacities, causes an additional pole in the loop response of the AC converter. Trimmer capacitors C14 and C15 are provided on the two lowest ranges to adjust the frequency response up through 20 kHz. The low resistances of R31 and R32 make this unnecessary on the two upper ranges.

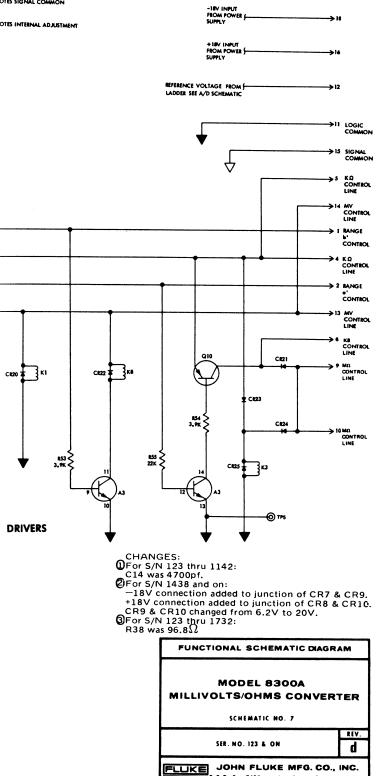

#### A-D CONVERTER (Figure 1 and Schematic No's. 2 and 3)

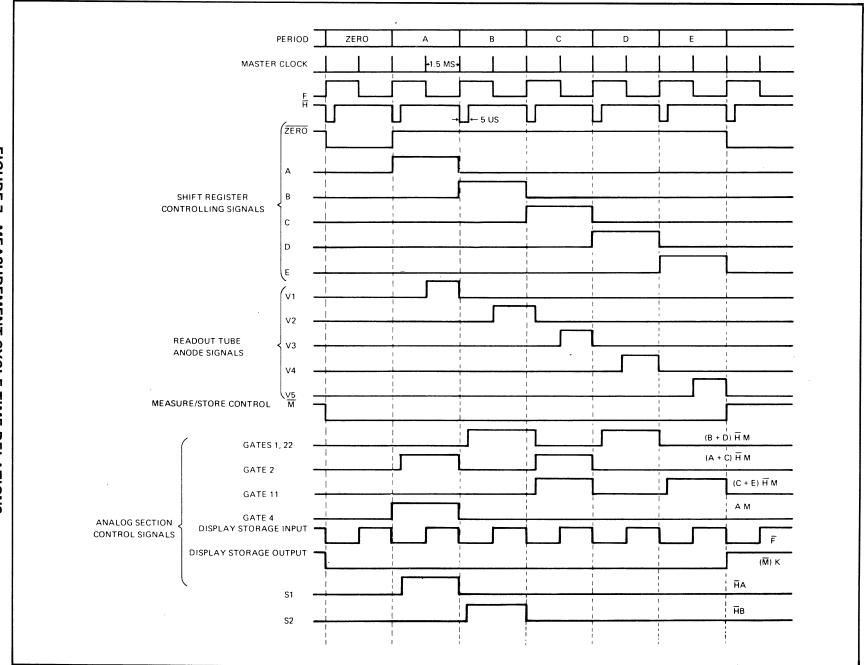

The Recirculating Remainder conversion process is synchronously operated. That is to say; it progresses through it's steps in time with an internal clock, which is the Power Supply Inverter (250 Hz).

acust f

A Ring Counter fed by one of the outputs of T102, divides each cycle into five time periods of 4 milliseconds each as shown in Figure 4. The first time period is the ZERO time, this is the time period when the offset is removed from the A-D Converter amplifier. During the remaining four time periods each of the four digits is digitized and then displayed. At the end of the last period, the Ring Counter supplies a synchronizing pulse through R68 and C27 to the Measure Store Multivibrator Q25. It is the job of the Measure Store circuit to determine whether the A-D Converter will sample (Measurement Mode) the input voltage or continue to display the information held in storage (Storage Mode). See Figure 5 for sequence of operation.

#### POLARITY SENSING

Q13 turns on only when a 1 period time pulse appears at its gate and in Measurement Mode. This activates the Polarity Sensing Circuit. If the voltage at R40 is positive (Negative instrument input) Q15 will conduct and the signal from the Measure Store Multivibrator (Q25) will cause FET switch Q16 to conduct placing input on the A-D Amplifier.

If the voltage sensed by R40 is negative (Positive input to the 8100) Q14 will conduct and the signal at the collector of Q14 and the pulse from the Measure Store Multivibrator Q25 will turn FET switches Q12 and Q17 on. The negative output of the Buffer will be applied through the scaling resistors R50 and R51 and switch Q12 to the positive input of the A-D Amplifier. The Polarity Detector operates only while the instrument is in the Measurement Mode of operation and serves no function in the Storage Mode.

During time period 1, the amplified remainder is applied to C34. Q35 is prevented from conducting during the first half of the time period by the clock signal which is coupled through CR36 to its gate. During the second half of the period Q35 is ON and the amplified remainder is applied to C34.

During the second time period, Q35 is OFF and Q36 is ON which applies the remainder stored in C34 to be applied to the input of the Amplifier. Q39 is switched ON and the remainder is now applied to C35. Q39 is switched OFF during the third time period and Q37 and Q38 are switched ON which allows the remainder stored in C35 to be applied to the amplifier input.

During the third time period the remainder is stored in C34.

During the fourth and last time period Q34 is switched ON and the final remainder stored in C34 is applied to the input of the Amplifier.

#### ANALOG STORAGE

Clock pulses being applied through CR19 and Q28 allow conduction only during the second half of each time period. Q30 through Q33 are enabled only during the time period pulse corresponding to its gate connection.

During the last half of the 1 period the output of the Secondary Ladder is stored in capacitor C30. During the last half of the second period, the output of the Secondary Ladder is stored in C31. Etc.....

Q29 is enabled only when the instrument is in the Storage Mode and allows the output of each of the storage capacitors to appear at the input to the amplifier.

Analog storage is used only when the instrument is in the Storage Mode of operation as determined by the Measure Store Multivibrator.

Figure 4. 8100 TIMING DIAGRAM

Figure 5. 8100 DISPLAY SEQUENCE, MEASURE MODE

#### **MEASURE STORE MULTIVIBRATOR**

The one shot multivibrator formed by Q25 and Q26 has dual synchronizing inputs. The Measurement Cycle (approx. 20 ms) is coincident with the conduction of Q25. The Storage Cycle (approx. 330 ms) is coincident with the conduction of Q26. The multivibrator is triggered at the end of each complete cycle by the negative edge of the 4th time period pulse. If C29 is sufficiently discharged, this negative pulse will cause the multivibrator to pulse, sending a 20 ms measure pulse to the Polarity Sensing circuit which starts a measurement cycle. If the multivibrator does not pulse the 8100 remains in Storage Mode.

#### DISPLAY

It should be noted that each readout tube is on only during the last half of its corresponding time period. (2 ms on and 18 ms off).

The BCD output of the A4 Counter is fed to the Decoder Driver where it is translated into decimal output. If the BCD code was 3 the Decoder Driver will apply ground to the three line to all readout tubes. The 1 time period pulse, in conjunction with the clock **pulse**, which occurs only during the second half of each time period, will enable Q67 and Q71 thus allowing the +200 volts to light the three digit in V1.

#### EXAMPLE OPERATION (Figure 6) (Example voltage is .6532V)

Counter A4 is reset to zero as it is at the beginning of every time period by the pulse from A3A NAND gate.

The Ring Counter produces the ZERO pulse and Q18 and Q58 are turned on. Q58 connects C37, the zero holding capacitor, to the output of amplifier A2. Q18 connects the positive input of the amplifier to ground. This operation removes the offset for the remainder of the measurement cycle.

The Ring Counter produces the 1 time period pulse. It is necessary to assume that Q25 in the Measurement Store Multivibrator is conducting. The 1 pulse will turn transistor Q13 on. Since the .6532 volts into the instrument is positive, the voltage across R40 will be negative. Q14 will conduct which will cause Q12 and Q17 to turn on. These transistors were enabled by the Measure pulse from the Measure Store Multivibrator. The negative voltage from the Buffer will be applied to the A-D Amplifier through scaling resistors R50 and R51. Q17 connects the positive input to the amplifier to ground via resistors R186 and R187 which provide offset correction voltage to the positive input.

With R98, 200 k $\Omega$ , in the feedback loop and R51 and R50 as the input resistance the gain of the amplifier is 70. Q52 is used as temperature compensation only.

With .6532 volts at the input terminal of the amplifier, the output will attempt to go to 40 volts to satisfy the loop gain, but will be prevented from going so high by the limiting action of  $\Omega$ 76 and R110. The output will exceed 7.0 volts and cause the Analog Comparator to conduct.

The Analog Comparator, Q89, will generate current at any time the voltage output of the Amplifier is seven or more volts. The current that it supplies is fed to the Voltage Controlled Oscillator.

| MEASURE MODE                                                                                                                                    | ZERO | I | 2  | 3 | 4 |

|-------------------------------------------------------------------------------------------------------------------------------------------------|------|---|----|---|---|

| Q18 & Q58 conduct and remove offset from A-D amp.                                                                                               |      |   |    |   |   |

| 1 from Ring Counter enables Q13, polarity is determined and input FETs apply .6532 to A-D.                                                      |      |   |    |   |   |

| 6 is digitized, remainder is stored in S & H C34.                                                                                               |      |   |    |   |   |

| 6 is displayed and .6v stored in C30.                                                                                                           |      |   |    |   |   |

| Input is disconnected from A-D amplifier.                                                                                                       |      |   |    |   |   |

| .532v from C34 is applied to A-D input.                                                                                                         |      |   |    |   |   |

| 5 is digitized and remainder .32 is stored in S & H C35.                                                                                        |      |   |    |   |   |

| 5 is displayed and .5v is stored in C31.                                                                                                        |      |   |    |   |   |

| .32 from C35 is applied to A-D amplifier.                                                                                                       |      |   |    |   |   |

| 3 is digitized and remainder .2 is stored in C34.                                                                                               |      |   |    |   |   |

| 3 is displayed and .3v is stored in C32.                                                                                                        |      |   |    |   |   |

| .2v from C34 is applied to A-D input and digitized.                                                                                             |      |   |    |   |   |

| 2 is displayed and .2v is stored in C33.                                                                                                        |      |   |    |   |   |

| STORAGE MODE                                                                                                                                    | ZERO | 1 | 2  | 3 | 4 |

| Q18 & Q58 conduct and remove offset from A-D amp.                                                                                               |      |   |    |   |   |

| Q30 conducts and applies .6v from C30 to A-D amp.                                                                                               |      |   |    |   |   |

| 6 is digitized                                                                                                                                  |      |   |    |   |   |

| 6 is displayed and .6v is restored to C30.                                                                                                      |      |   |    |   |   |

| Q31 conducts and applies .5v from C31 to A-D amp.                                                                                               |      |   |    |   |   |

| 5 is digitized                                                                                                                                  |      |   |    | 4 |   |

| 5 is displayed and .5v is restored to C31.                                                                                                      |      |   |    |   |   |

| Q32 conducts and applies .3v from C32 to A-D amp.                                                                                               |      |   |    | 1 |   |

| 3 is digitized.                                                                                                                                 |      |   |    |   |   |

| 3 is displayed and .3v is restored to C32.                                                                                                      |      |   |    |   |   |

| Q33 conducts and applies .2v from C33 to A-D amp.                                                                                               |      |   |    |   |   |

| 2 is digitized.                                                                                                                                 |      |   | р. |   |   |

| 2 is displayed and .2v is restored to C33.                                                                                                      |      |   |    |   |   |

| NOTE: If C29 is sufficiently discharged, the negative going<br>Multivibrator and a measure pulse will be generated<br>storage cycle will start. |      |   |    |   |   |

The Voltage Controlled Oscillator, Q59 and Q60, will supply a series of pulses when supplied current. The repetition rate will be proportional to the current being supplied.

The pulses from the VCO are applied to the Counter A4, which is reset at the start of each time period. This counter translates the pulses into Binary Coded Decimal output. This BCD output is applied to the Ladder Switches and Drivers. As the BCD numerical value increases, the ladders produce 0.1 volt steps in their output. Thus in this case when the Primary Ladder output reaches .6 volts and is fed back to the input of the A-D Amplifier, the input difference to the amplifier becomes .0532 volts and the output of the amplifier will be less than 7 volts. When this occurs the Analog Comparitor Q89 does not furnish current to the VCO which causes it to stop pulsing.

The Decoder Driver translates this BCD output to decimal and produces a ground potential that is fed to all of the readout tubes 6 line. Only the 1 tube will light since it is the only one enabled by both clock and the 1 pulse via Q67 and Q71.

The Secondary Ladder feeds the Analog Storage circuit. Q28 is enabled only during the second half of each time period and Q30 is enabled by the 1 time period pulse. This causes C30 to be charged to .6 volts being furnished by the Secondary Ladder.

The remainder voltage during time period 1 was 0.532 volts at the input to the A-D Amplifier. This remainder is multiplied by the amplifier to 3.724 volts and appears across remainder resistors R99, R100 and R149. It is apparent that the total resistance is 14  $\Omega$  and that 2 k $\Omega$  represents 1/7 of the total resistance. This means that one seventh of the voltage appearing across the total remainder resistance appears across R100. This means, in the example case, .532 volts. This voltage will be applied across C34 in the Sample and Hold Circuit by the 1 time period pulse enabling transistor Q35. CR36 allows Q35 to be enabled only during the second half of the time period.

#### SUMMARY:

The highlights of the action that has taken place during the first time period are as follows:

1. The .6 volt was digitized.

- 2. .6 volt was placed in Analog Storage.

- 3. The remainder voltage .532 was placed in Sample and Hold.

- 4. The 6 was displayed during the last half of the time period by V1.

Time period 1 ends and transistor Q13 is no longer enabled as the 1 pulse is no longer furnished to it.

At the start of time period pulse 2 enables Q36 which applied the .532 volt remainder stored in C34 to appear at the input to the A-D Amplifier via Q18 which is enabled for the entire duration of The Measure Cycle. The .532 volts are amplified by 70 and once again the output of the amplifier exceeds the 7 volt reference causing Q89 to furnish current to the Voltage Controlled Oscillator. The pulse train produced is translated to BCD output and the Ladders are switched up in 0.1 volt increments until .5 volts is fed from the Primary Ladder to the summing junction of the A-D Amplifier. The input to the amplifier at this time is 0.32 volts which results in an output from the amplifier that is less than 7 volts and Q89 cuts off. The

BDC output from the A4 Counter is applied to the Decoder Driver and translated to decimal output, placing ground potential on all of the "5" lines to the readout tubes. The clock and 2 pulses enable Q68 and Q72 during the last half of the time period. Thus the readout tube V2 will display the "5" only during that last half of the time period.

The Secondary ladder will have an output of .5 volts at this time and it will be stored on capacitor C31 during the last half of the time period when Q28 conducts and Q31 is enabled by the 2 pulse.

The remainder, .032 volts will be amplified and divided by the remainder resistors and will be stored in the Sample and Hold circuit capacitor C35 via the enabled Q39 as .32 volts.

During period "3" Q38 will be enabled and apply the .32 volts, stored there, across the input to the A-D Amplifier through Q27.

The amplified voltage from the output of the amplifier will exceed the 7 volts of reference and Q89 will supply current to the Voltage Controlled Oscillator which will start a pulse chain. The pulses will be translated into BCD output. The BCD output will switch both Ladders and be decimalized by the Decoder Driver. When the output of the Primary Ladder reaches .3 volts the output of the amplifier will be less than 7 volts and Q89 will stop supplying current to the VCO. The decimalized "3" will appear as a ground potential on all of the 3 lines to the readout tubes. During the last half of the time period the +200 volts will be applied to V3 via Q69 and Q73 being enabled by the clock pulse and the 3 pulse thus allowing V3 to display the digit 3.

The .3 volts from the Secondary Ladder will be stored in Analog Storage capacitor C32 during the last half of the time period when Q28 is enabled and the 3 pulse has enabled Q32.

The remainder .02 at the input of the amplifier is amplified and appears across the remainder resistors and will be divided down to .2 volts and Q37 will be enabled causing this remainder to be stored in C34.

During time period 4 Q34 conducts applying the .2 volts stored in C34 to appear on the input to the A-D Amplifier. The output will exceed the reference voltage causing Q89 to supply current to the VCO which will start a pulse train. Counter A4 will count the pulses and translate them to BCD output. This BCD output causes the Ladder switches to operate and the output from the Primary Ladder is fed back to the summing point of the A-D Amplifier. When the output reaches .2 volts, the output of the amplifier is no longer higher than 7 volts and Q89 will stop conducting. The VCO stops pulsing and the Decoder Driver will translate the BCD output to decimal and apply ground potential to the 2 lines of all of the readout tubes. The clock and 4 pulses will enable Q70 and Q74, which will allow the +200 volts to light the tube V4 during the second half of the time period. The Secondary Ladder will have an output of .2 volts which will be stored in Analog Storage capacitor C33, the 4 pulse having enabled Q33 and the second half time period pulse having enabled Q28.

This completes a Measurement Cycle. As the 4 time pulse goes negative returning to zero potential it will cause Q25 (Measure Pulse) to conduct, only if capacitor C29 is sufficiently discharged. In this case it would not be possible for the instrument to start another Measurement Cycle as C29 would be fully charged.

#### SUMMARY:

It will be noted that each increment of voltage has been stored in the Analog Storage capacitor as follows:

C30 .6 volts C31 .5 volts C33 .2 volts

None of these stored voltages were used in the Measurement Cycle. C29 was fully charged and Q26 is conducting, which occurs during the Storage Cycles of the instrument. Q27 will be off and Q29 will be enabled until the Measure Store Multivibrator is operated again. Q26 will conduct for approximately 330 ms or about 16 cycles of the instrument. At that time C29 will be sufficiently discharged to allow Q25 to conduct when it receives a negative going pulse from the 4th time period pulse. Q25 will then conduct for approximately 20 ms or one Measurement cycle.

#### STORAGE CYCLE (Figure 7)

The ZERO pulse will again cause the offset to be removed from the A-D Amplifier by placing C37 across the output of the amplifier and grounding the input, as the result of Q18 and Q58 conducting.

The 1 pulse will cause Q30 to enable and the voltage stored on C30 (0.6 volts) to be applied to the input of the A-D Amplifier through Q29, which has been enabled by the Measure Store Multivibrator.

The A-D Amplifier amplifies the .6 volts by 70 and the output of the A-D Amplifier exceeds the 7 volt reference causing Q89 to conduct and supply current to the VCO. The VCO will start producing a pulse train. These pulses are counted and translated into BCD output by the action of Counter A4. The BCD output causes the Ladders to switch and increase their output by .1 volt per pulse. When the output of the Primary Ladder reaches .6 volts it will cause the A-D Amplifier to be satisfied and it will no longer have an output that is above the 7 volt reference of the instrument. The Secondary Ladder will have produced a .6 volt output which will be stored in C30 during the second half of the time period via Q28.

The Decoder Driver will have translated the BCD output to decimal and applied ground to all of the readout lamps on the 6 line. Q67 and Q71 are enabled, during the second half of the time period, by the clock and 1 pulses thus applying the +200 volts to V1 enabling it to display the 6.

During time period 2, Q31 and Q29 will conduct causing the .5 volts stored in C31 to appear across the input to the A-D Amplifier. The amplifier will have an output of more than 7 volts, which will cause Q89 to conduct and supply current to the VCO, which will produce a pulse train. The Counter A4 will count and translate the output to BCD. The Ladders will produce .1 volt of output for every pulse. The Primary Ladder being fed back to the input of the A-D Amplifier will cause the output of that amplifier to drop below 7 volts when .5 volts level is reached, which will cause Q89 to cut off and the VCO to stop producing pulses.

The Secondary Ladder will have produced .5 volts which will be stored on C31 during the second half of the time period by the conduction of Q28. The Decoder Driver will have placed ground

### STORAGE MODE

Figure 7. 8100 DISPLAY SEQUENCE, STORAGE MODE

potential on the 5 lines to the readout tubes. Q68 and Q72 will be enabled by the 1 pulse and clock pulse during the second half of the time period. This applies the +200 volts to V2 causing it to display the digit 5.

During the 3 time period, Q32 will be enabled placing the .3 volts stored in C32 to be applied to the A-D Amplifier. The output of the amplifier will exceed the 7 volt reference and Q89 will supply current to the VCO which produces a pulse train. The pulses will be counted and translated to BCD output. This BCD output will cause the ladder switches to operate and cause the output of both ladders to increase by .1 volt for every pulse of the VCO. When the output of the Primary Ladder reaches .3 volts the A-D Amplifier will be satisfied and its output will drop below 7 volts causing Q89 to stop conducting, and the VCO will stop pulsing. The output of the Secondary Ladder (.3 volts) will be stored on C32 during the second half of the time period through Q28 which conducts only during the second half of each time period.

The Decoder Driver will have translated the BCD output to decimal and placed ground potential on all of the 3 lines to the readout tubes. Q69 and Q73 will have been enabled, during the second half of the time period, by the 3 time pulse and the clock pulse and the 3 will be displayed by V3.

Time pulse 4 will cause the .2 volts on C33 to be placed on the input to the A-D Amplifier whose output will exceed the 7 volt reference. Q89 will conduct and the VCO will pulse causing the ladder outputs to step .1 volt for every pulse received. When the output of the Primary Ladder, which is fed back to the summing point, reaches .2 volts, the output of the amplifier will no longer be higher than the 7 volt reference and Q89 will stop supplying current to the VCO. The Secondary Ladder will charge C33 to .2 volts and the action of the Decoder Driver will cause ground potential to appear on all of the 2 lines to the readout tubes. Q70 and Q74 will be enabled during the second half of the time period, at which time V4 will display the 2.

#### SUMMARY:

The capacitors in the Analog Storage Circuit will contain all of the increments of the voltage that were digitized during the previous Measurement Cycle. The Sample and Hold Circuit is disabled during all Storage Cycles. Each digit is displayed only during the last half of each time period. During the Storage Cycle the Polarity Sensing Circuit is not enabled.

This completes the Storage Cycle and as previously explained, the instrument will enter another Storage Cycle unless the charge on capacitor C29 has decreased to a value low enough to cause the Measure Store Multivibrator to pulse. If the Multivibrator does pulse a new Measurement Cycle will start and the input will be sampled again.

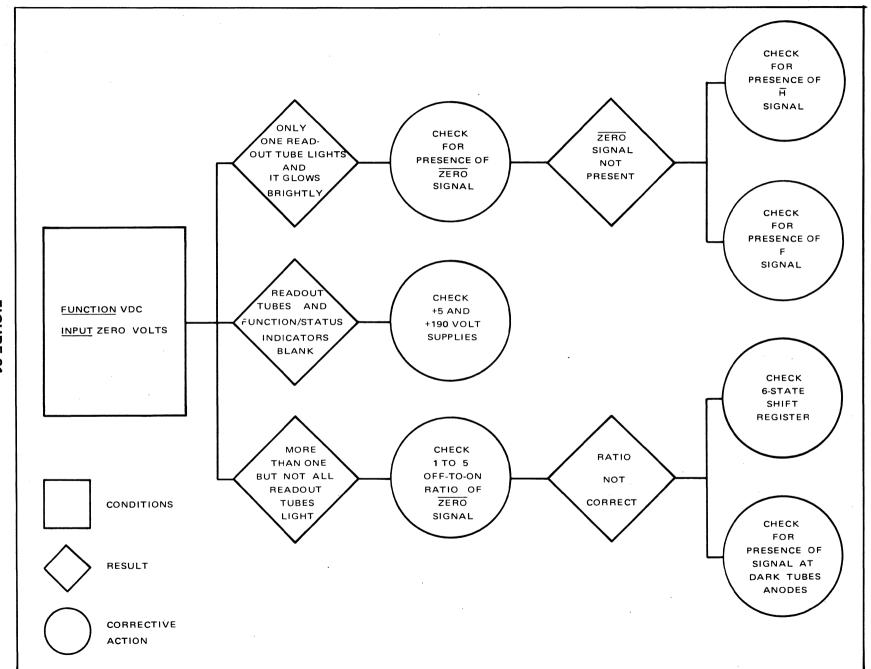

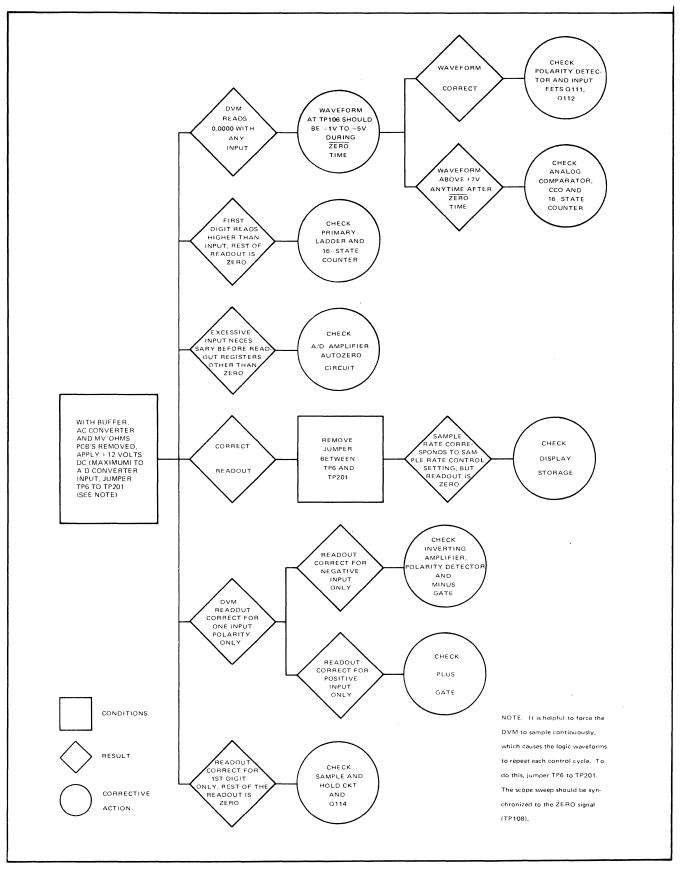

#### **TROUBLESHOOTING: (Figure 8)**

1. There are several ways of isolating the section of the 8100 that is malfunctioning. Observation of the readout and logical deduction based upon the knowledge of the theory of operation may be adequate to sectionalize the trouble.

2. The Power Supplies are interrelated and to isolate troubles in this area it may be necessary to isolate the -18 volt supply. To do this, disconnect the +15 volt end of R5 and connect it to an external source, or disconnect R35 and place a  $1330\Omega \pm 1\%$  resistor from the base of Q3 to ground.

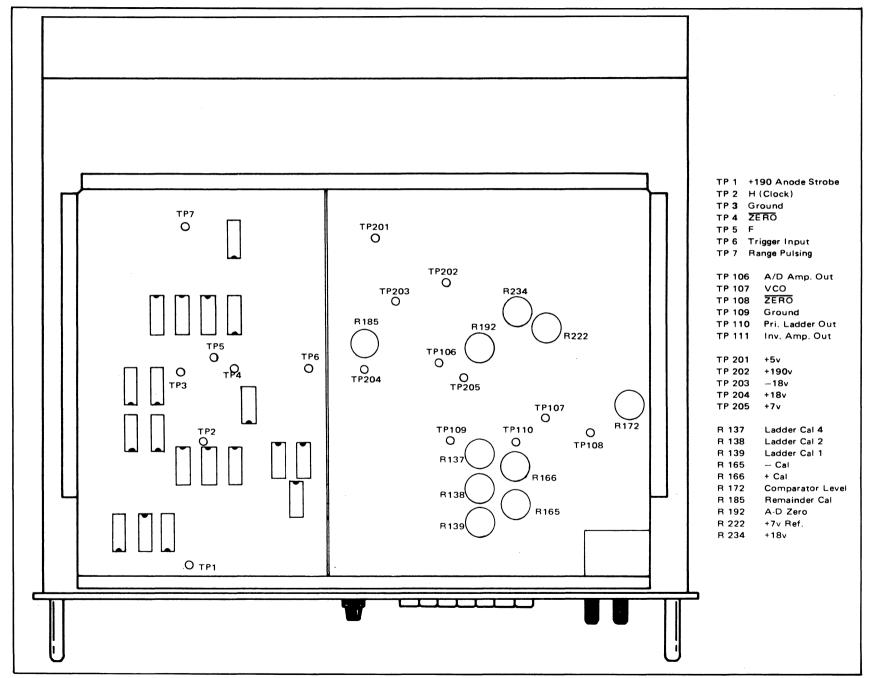

Figure 8. 8100 LAYOUT

3. The Input Buffer can be checked by measuring the voltage between TP9 and TP1 (ground), while measuring a voltage in the 1 Volt DC range. The voltage measured should be the same as the input but in reverse polarity.

4. The Auto Zero circuit will mask many types of trouble, so to disable this circuit it will be necessary to jumper TP6 to TP7 and jumper -18 volts to TP8. The measurement will now have an offset but the Auto Zero will be disabled.

5. Storage Mode can be avoided and the instrument placed in continuous Measurement Mode by placing a jumper between TP4 and TP5.

6. Connect +15 volt supply to the junction of R60 and R61, the Ring Counter will stop and the instrument will no longer display anything in the readout tubes. All of the output lines should measure -18 volts at this time. Remove the jumper and measure the collector voltage with an oscilloscope, each collector should measure about .3 volts when the transistor conducts.

7. An excessive load on any Ring Counter output can cause it to oscillate. Spikes following the time pulse indicate that the Ring Counter is near oscillation.

8. Trailing edge droop on the time pulses is caused by low gain transistors Q20 through Q28.

9. The following procedure will check the operation of the A-D Amplifier:

- a. Disable the Ring Counter by placing a jumper from +15 volts to TP11.

- b. Disable the Measure Store Multivibrator by placing a jumper from TP4 to TP5.

- c. Enable the Polarity Sense by placing a jumper from Q13 source to Q13 drain.

- d. Remove Binary Counter A4.

e. Measure the voltage between TP2 and TP1 (ground).

f. Apply 100 mv increments of input to the 8100. The measured voltage should increase 350 mv for every 100 mv increment of input and will be of the same polarity.

~

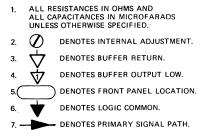

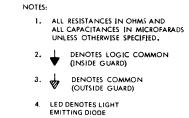

1. ALL RESISTANCES IN OHMS AND ALL CAPACITANCES IN MICROFARADS UNLESS OTHERWISE SPECIFIED.

2. ALL SWITCHES SHOWN IN OFF POSITION.

3. Ø DENOTES INTERNAL SCREWDRIVER ADJUSTMENT.

4. DENOTES FRONT PANEL LOCATION

5. TLK TEST LINK

6. 1 R186 SELECTED IN FINAL CALIBRATION.

7. ---- (COLOR) CONNECTORS FOR ISOLATED PRINTER

8. READOUT TUBE IN PIN LAYOUT:

BOTTOM VIEW

9. \*PLUS GATE ON WITH POSITIVE INPUT; MINUS GATE ON WITH NEGATIVE INPUT.

OUTPUT OPTION (-02).

NOTES :

VALUE SELECTED AT TEST OF Q11 1. 1

clift, Aleila, DAN Madel 8120A Batt-opet 01

CHANGES:

- (1)FOR S/N 3410 THRU 3419, 4098 THRU 4365, & 4429 THRU 4477: C65 WAS 4uf.

- 2 C68 ADDED S/N 5050 AND ON.

- 3 R217 AND C67 ADDED S/N 5018 AND ON.

- 4  $\rightarrow$  (COLOR) CONNECTORS FOR ISOLATED PRINTER OUTPUT OPTION (-02).

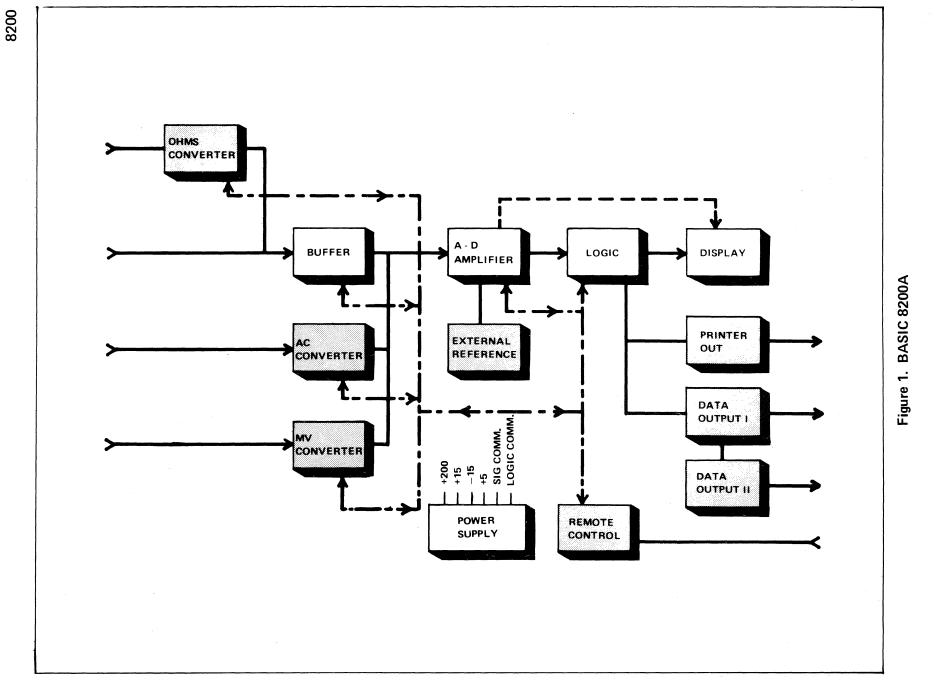

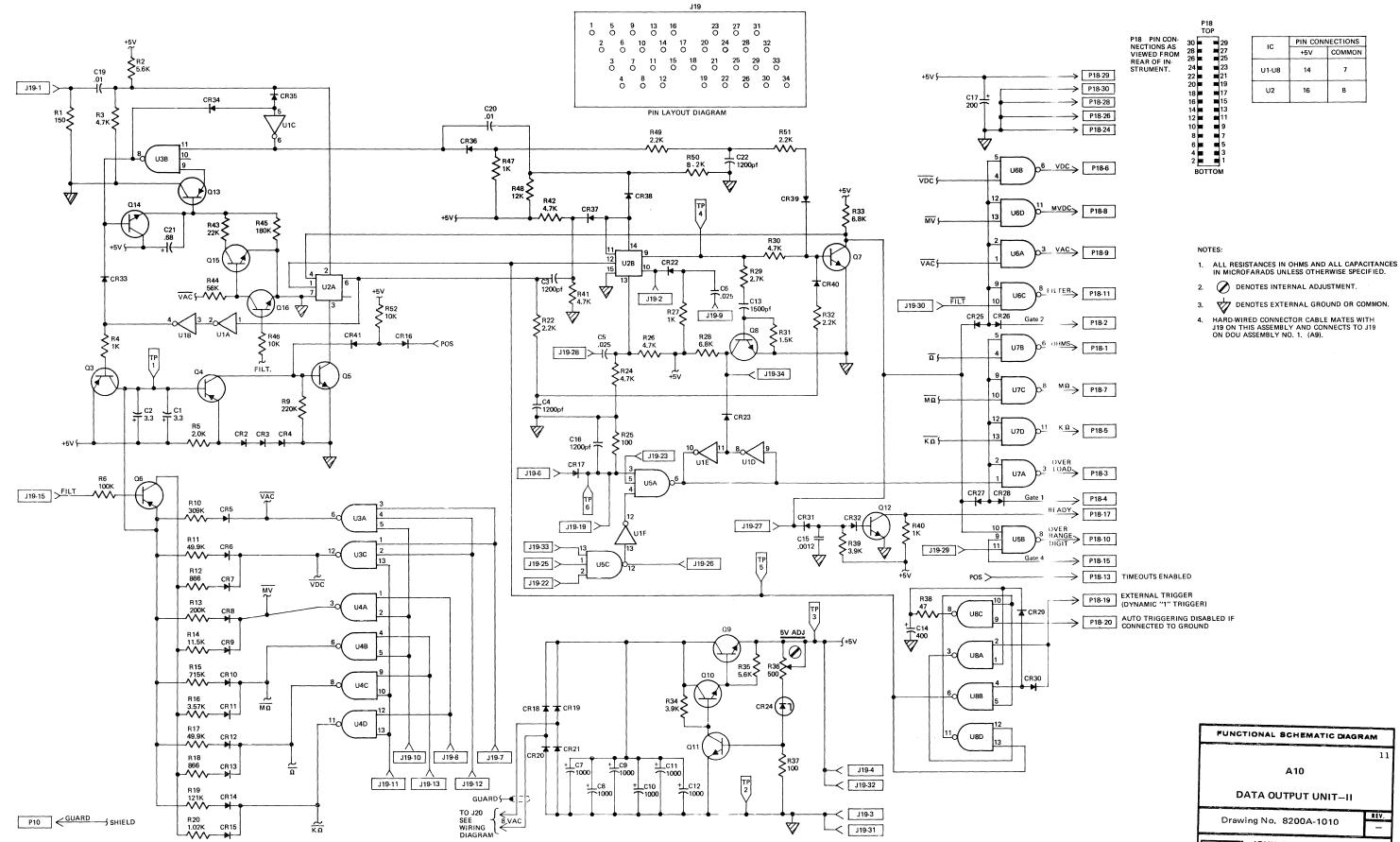

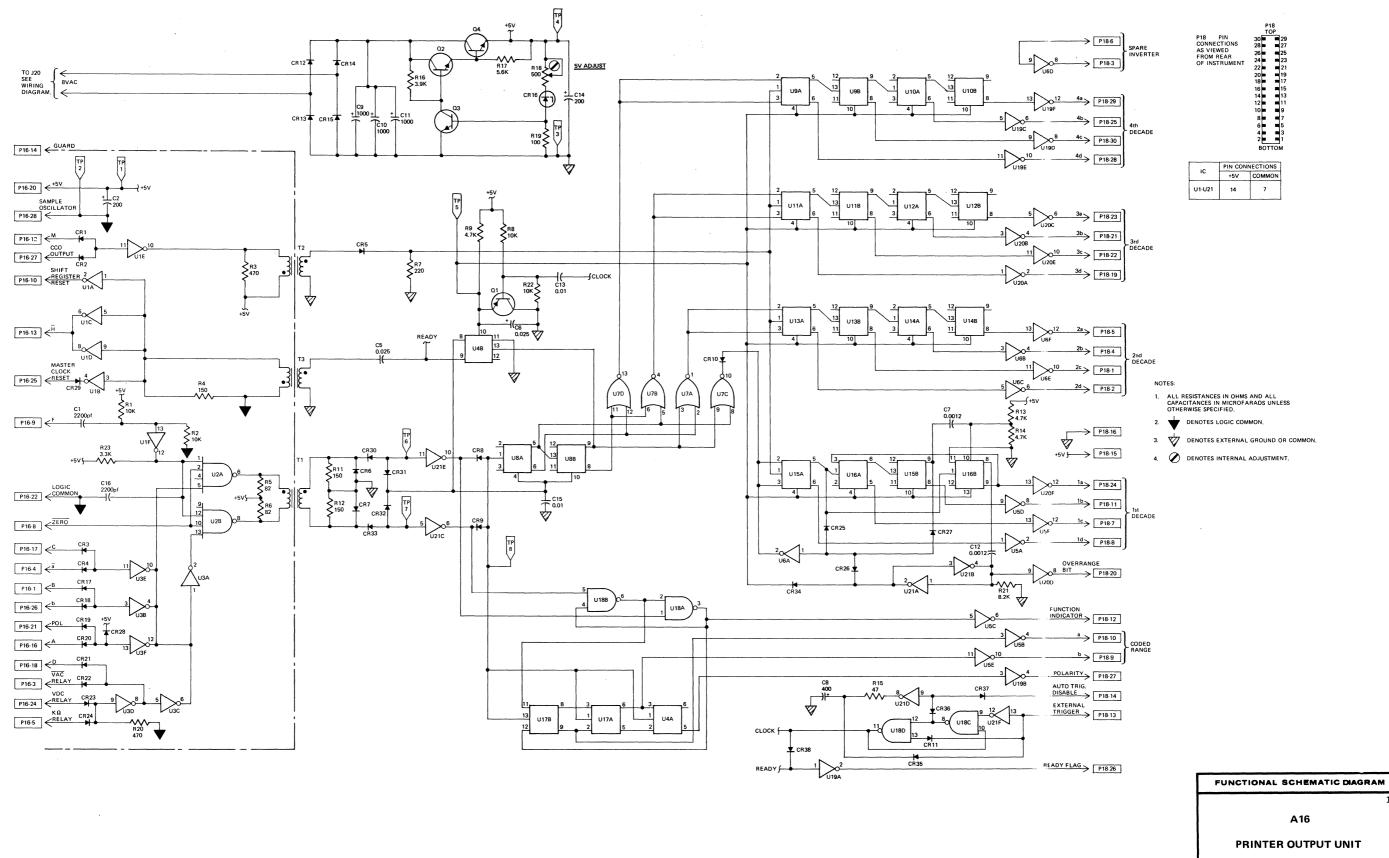

The rapid and efficient repair of any instrument is greatly enhanced by a thorough understanding of the theory of operation. This course is designed to fill that need for experienced technicians who are engaged in the calibration and repair of the Fluke 8200A Digital Voltmeter.

The basic 8200A is a four-digit DC voltmeter providing 1, 10, 100, and 1000 volt ranges complete with automatic polarity, automatic ranging, and 60 percent over-ranging. It comes equipped to accept a variety of options. Each of the options can be installed in the field. The options available include the:

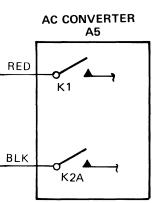

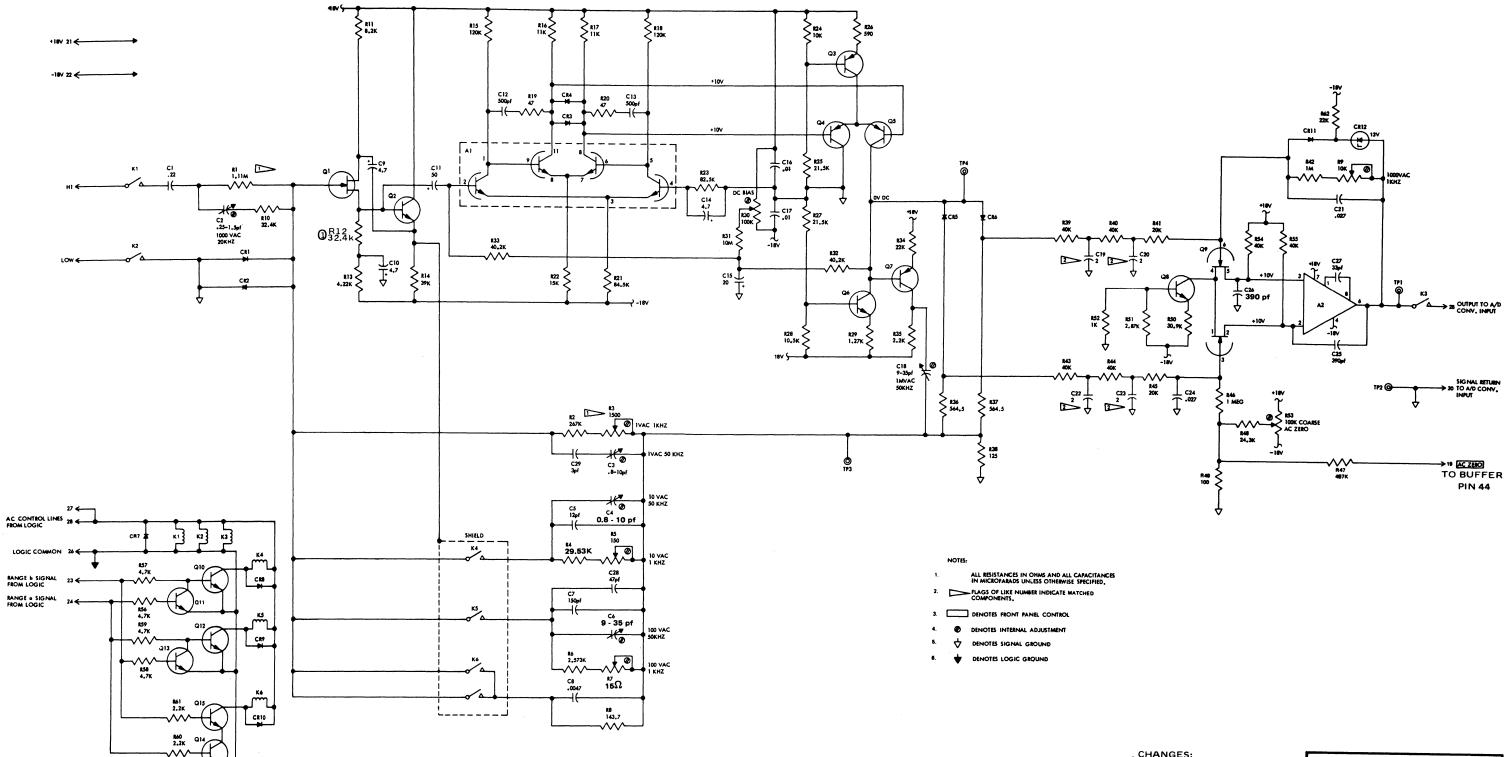

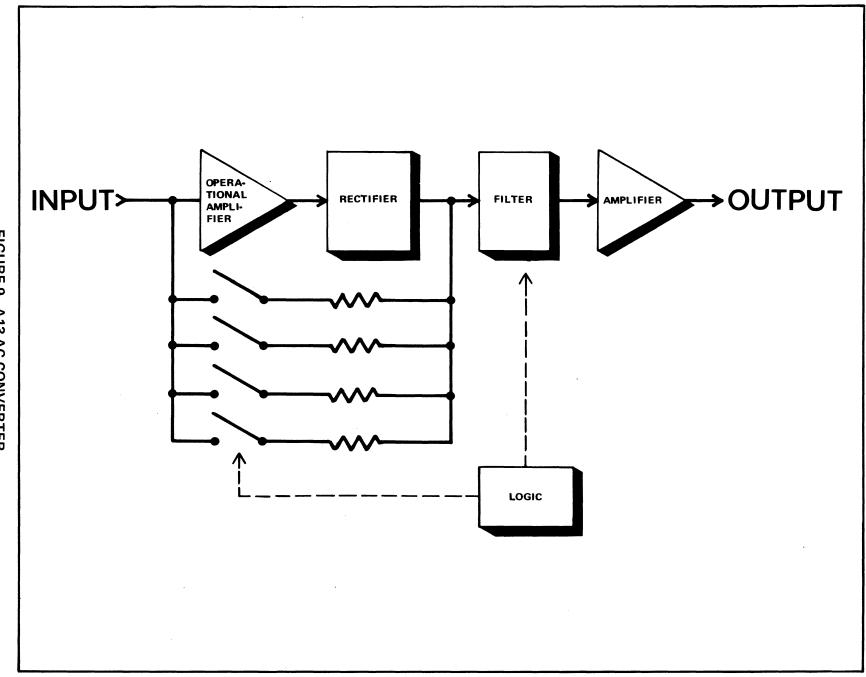

The -01 AC Converter Option provides four AC ranges with 30 Hz to 100 kHz response. Autoranging from the 1 VAC range to the 1000 VAC range is provided.

The -02 Millivolt DC Option provides two ranges of millivolt measurement; a 10 mV range and a 100 mV range. It provides automatic polarity, and the instrument will autorange down into the 100 or 10 mV range, from the VDC ranges. Autorange up from 10 or 100 mV range to VDC ranges is also provided.

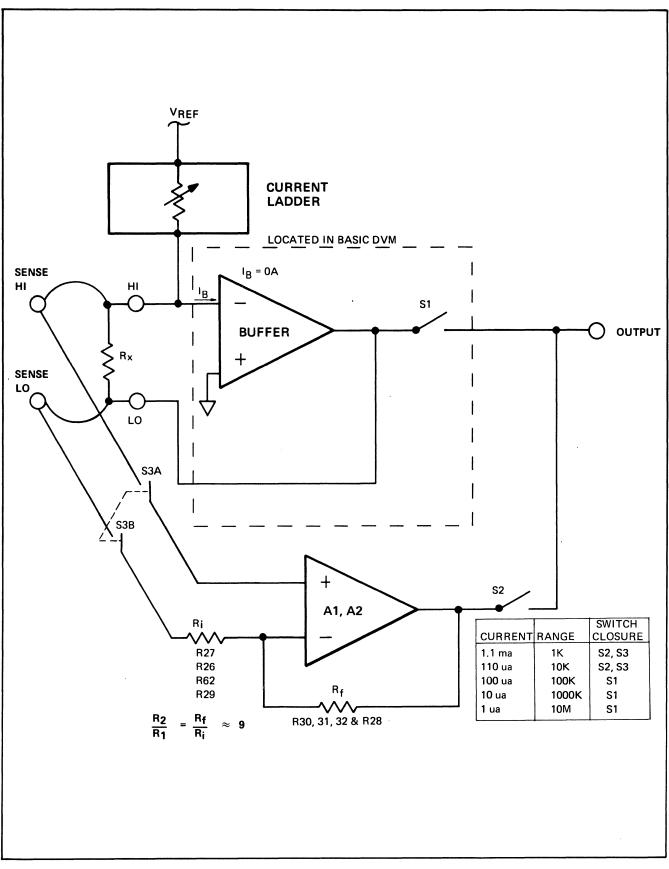

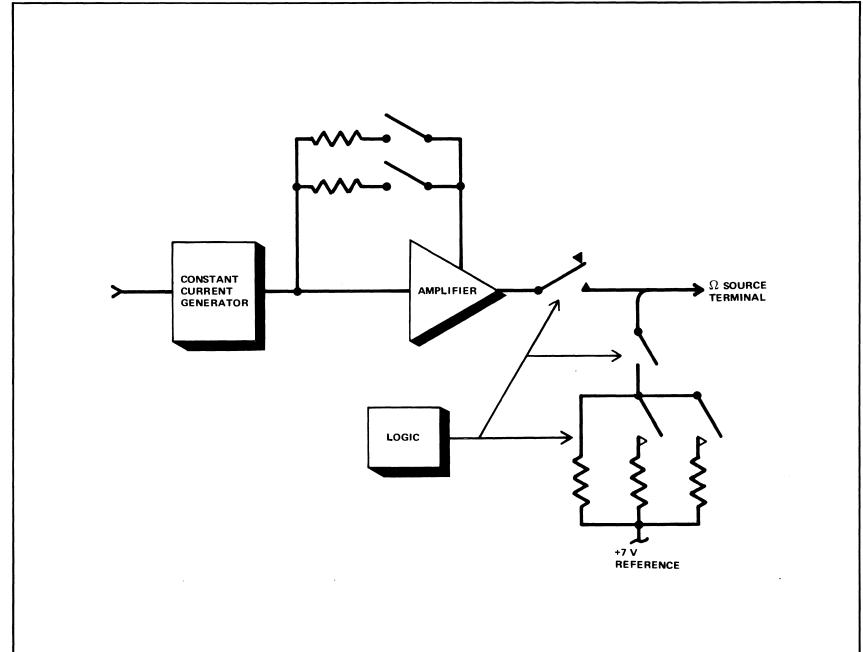

The -03 Resistance Option provides six resistance ranges from 100 ohms to 10M ohms, and it is overload fused at 30V RMS. Autoranging has been included in the Resistance Option.

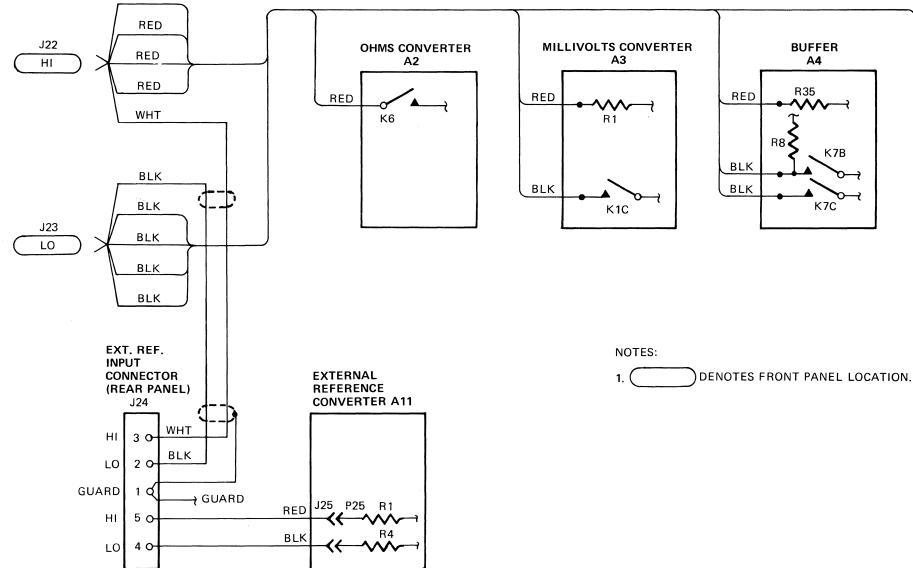

The -04 Isolated External Reference option; it is necessary that the instrument be provided with an -05 Option, which is the Rear Input option, when an Isolated External Reference Option is installed because of the limitation of the three front panel terminals. The Isolated External Reference will provide four terminal measurements: real-time ratio determinations, DC to DC in four ranges in the basic instrument, and AC and millivolt ratios when the options are installed.

The -05 rear input option provides a five-pin connector. Offering Signal HI and LOW, Guard, and External Reference HI and LOW.

The -06 Printer Output Option provides digits, polarity, and range information. Digits information and range information is given in Binary Coded Decimal format and in parallel output. The interface logic levels are +5V and 0V, and it can be used with the Remote Control Unit; -08 Option.

The -07 Data Output Option offers digits, polarity, and range in BCD format for digits and range in 8421 parallel or 4-bit serial format. The logic levels are +5V and 0V. It provides control input for an external trigger, automatic triggering, and time-outs enabled or disabled. It can be used with the 08 Remote Control Unit option. The Isolated Data Output option cannot be installed simultaneously with the 06 Isolated Printer Output option. The instrument can only accept one of the output options.

The -08 Remote Control Unit control, or program control, will interface with DTL or TTL. The Remote Control Unit requires +5V of DC at 105 mA from either the Data Output option or the Printer Output option. If the instrument is not equipped with either of these options, a special supply accessory is available, or it must be supplied from an external power supply. The Remote Control Unit option provides a remote flag, interlock protection, and address controlled by triggers.

In addition to the options provided for the 8200A, several accessories interface with the instrument. The A90 AC-DC Current Shunts, the 80F-5 High Voltage Probe, the 80F-15 High Voltage

Probe, the 80 RF Probes, and the rack-mounting hardware for either offset center or side-by-side installation.

## MAIN BODY OF TEXT

#### **BLOCK DIAGRAM**

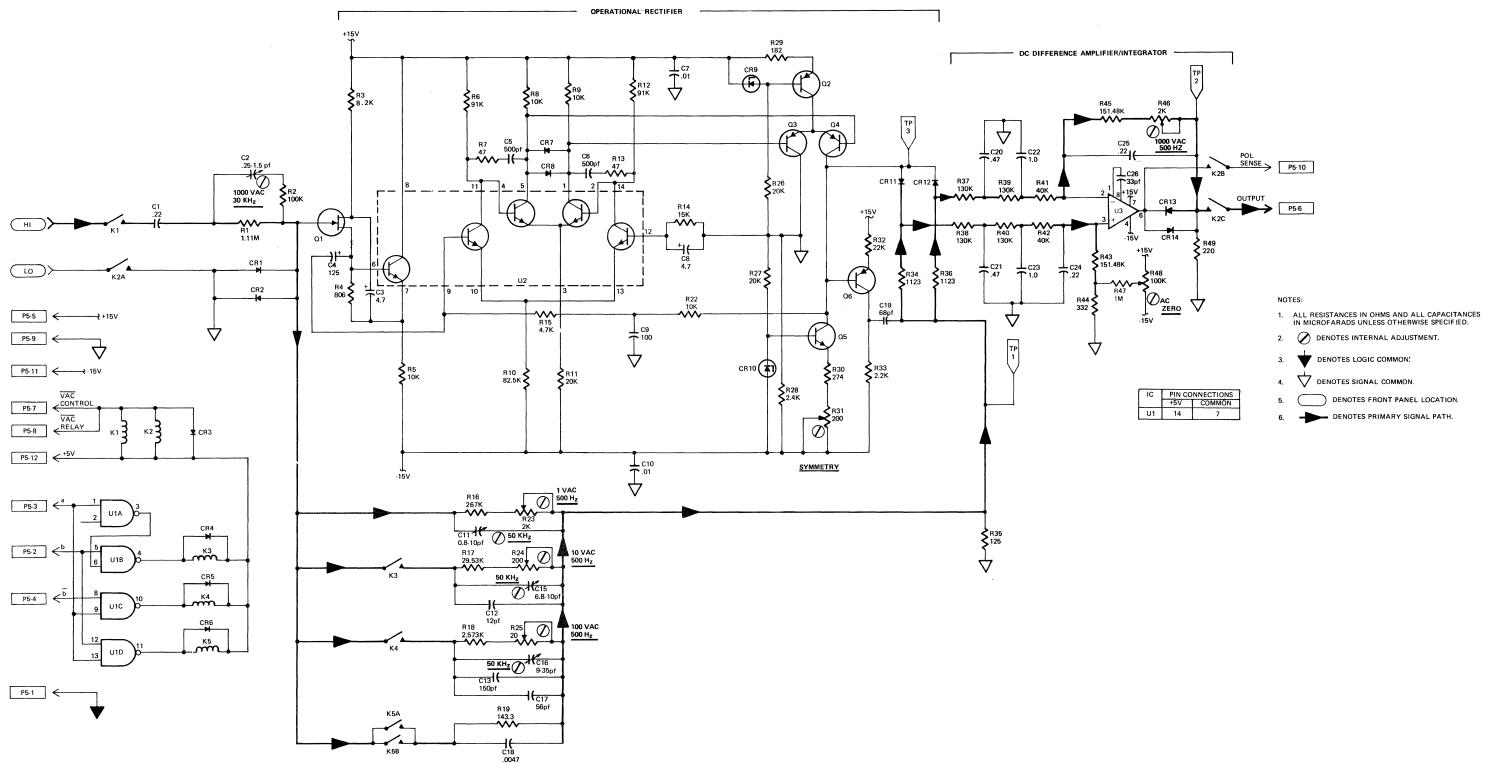

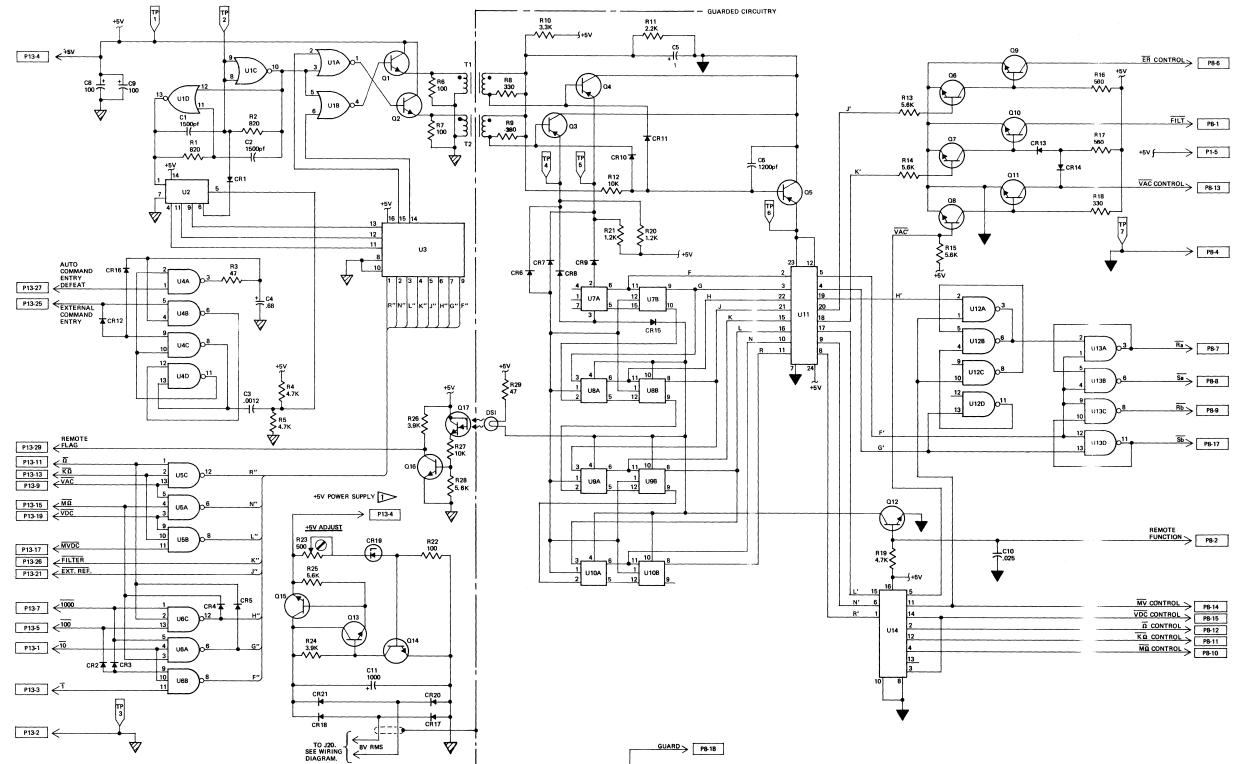

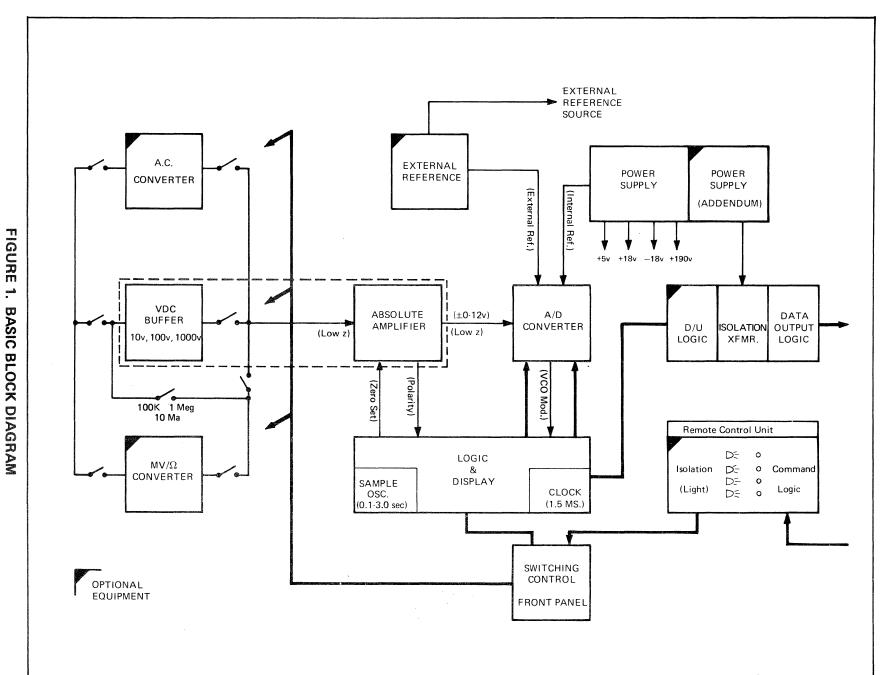

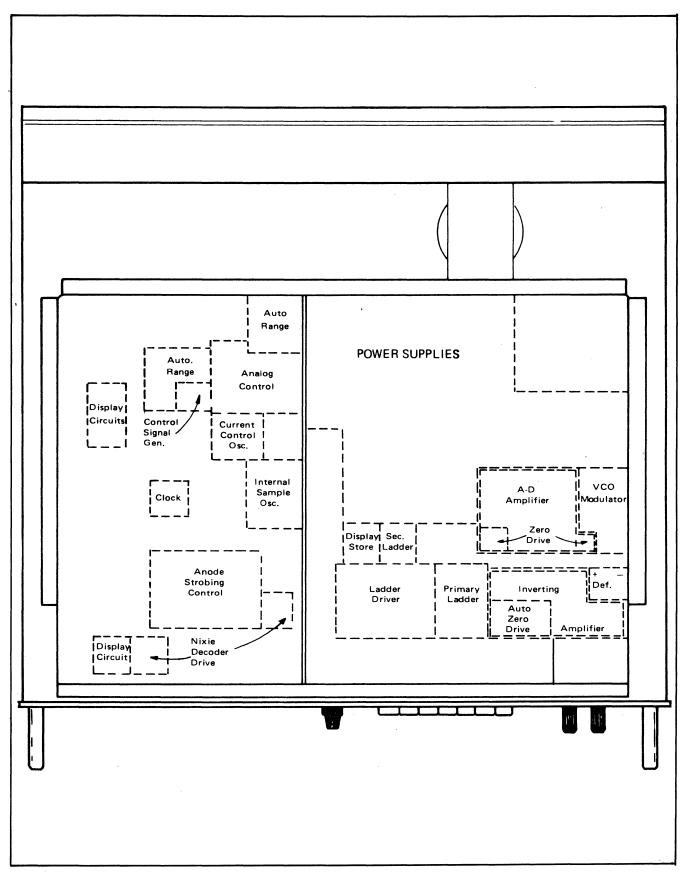

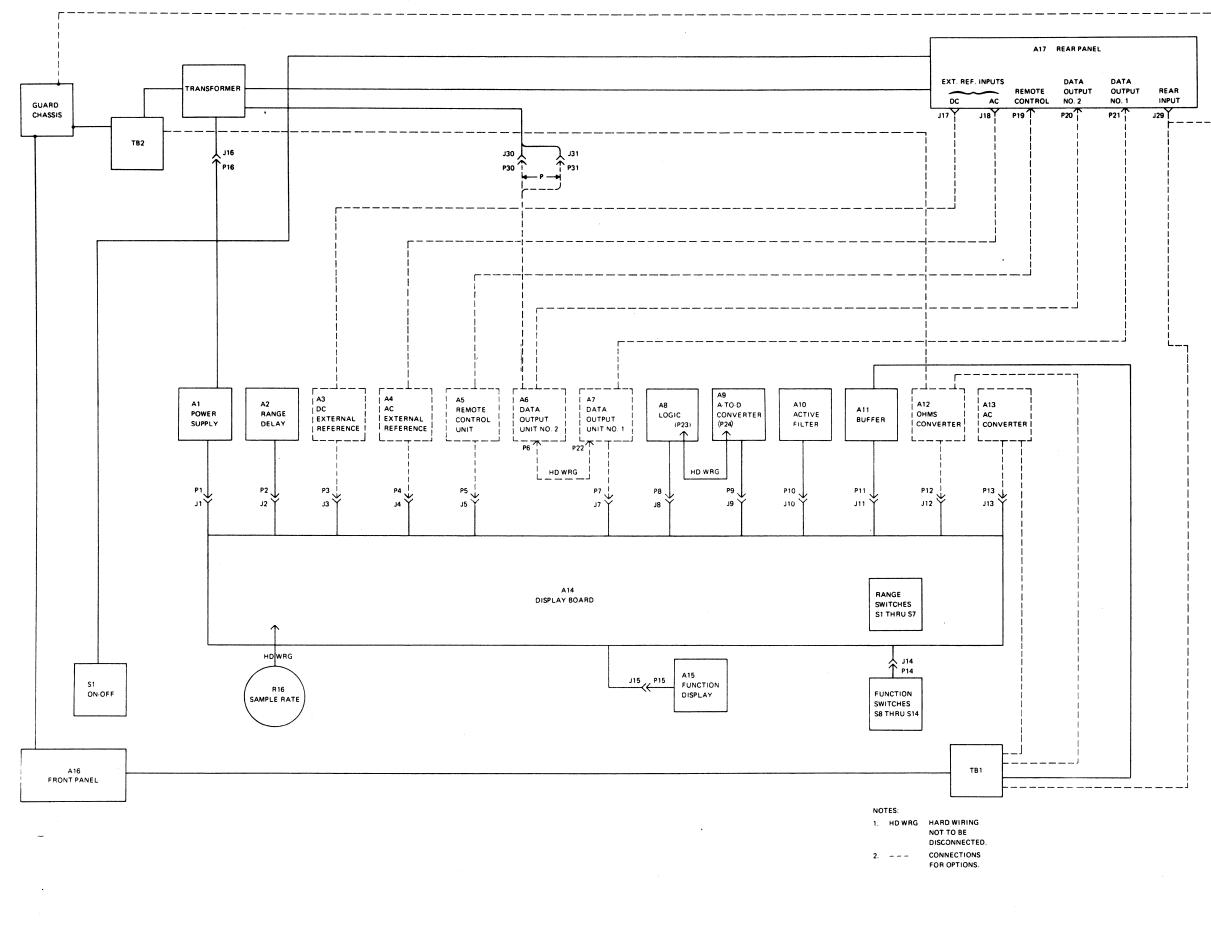

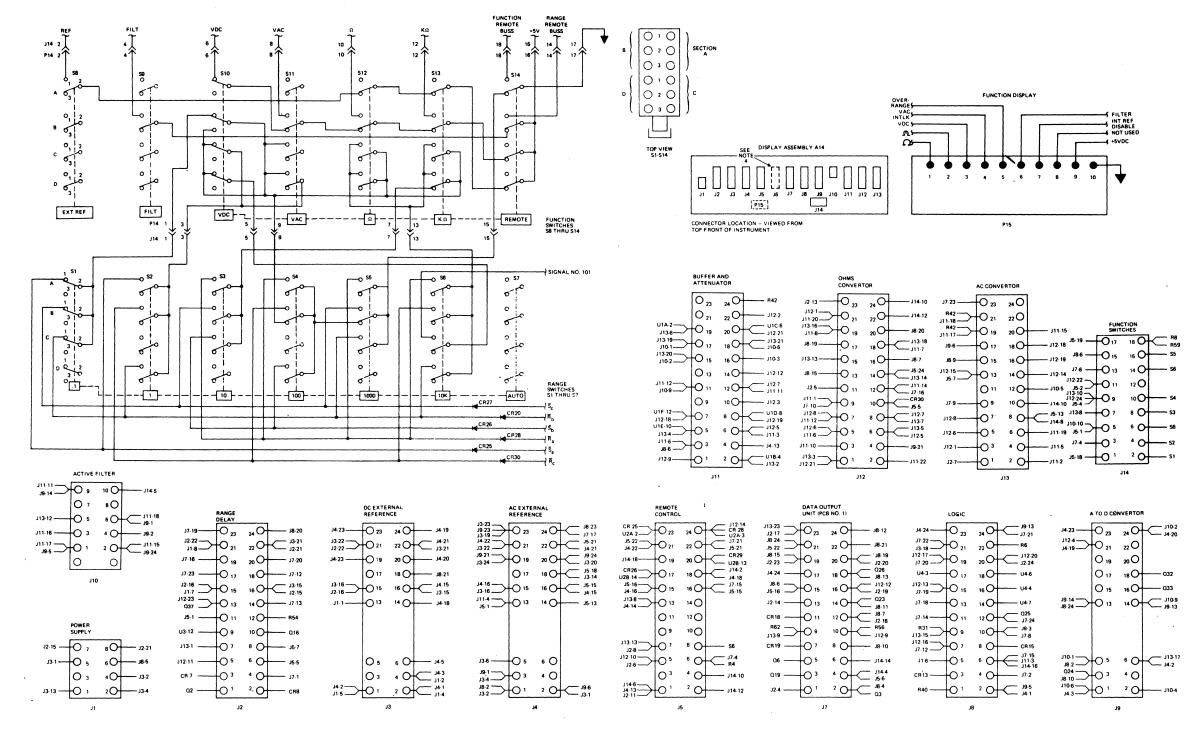

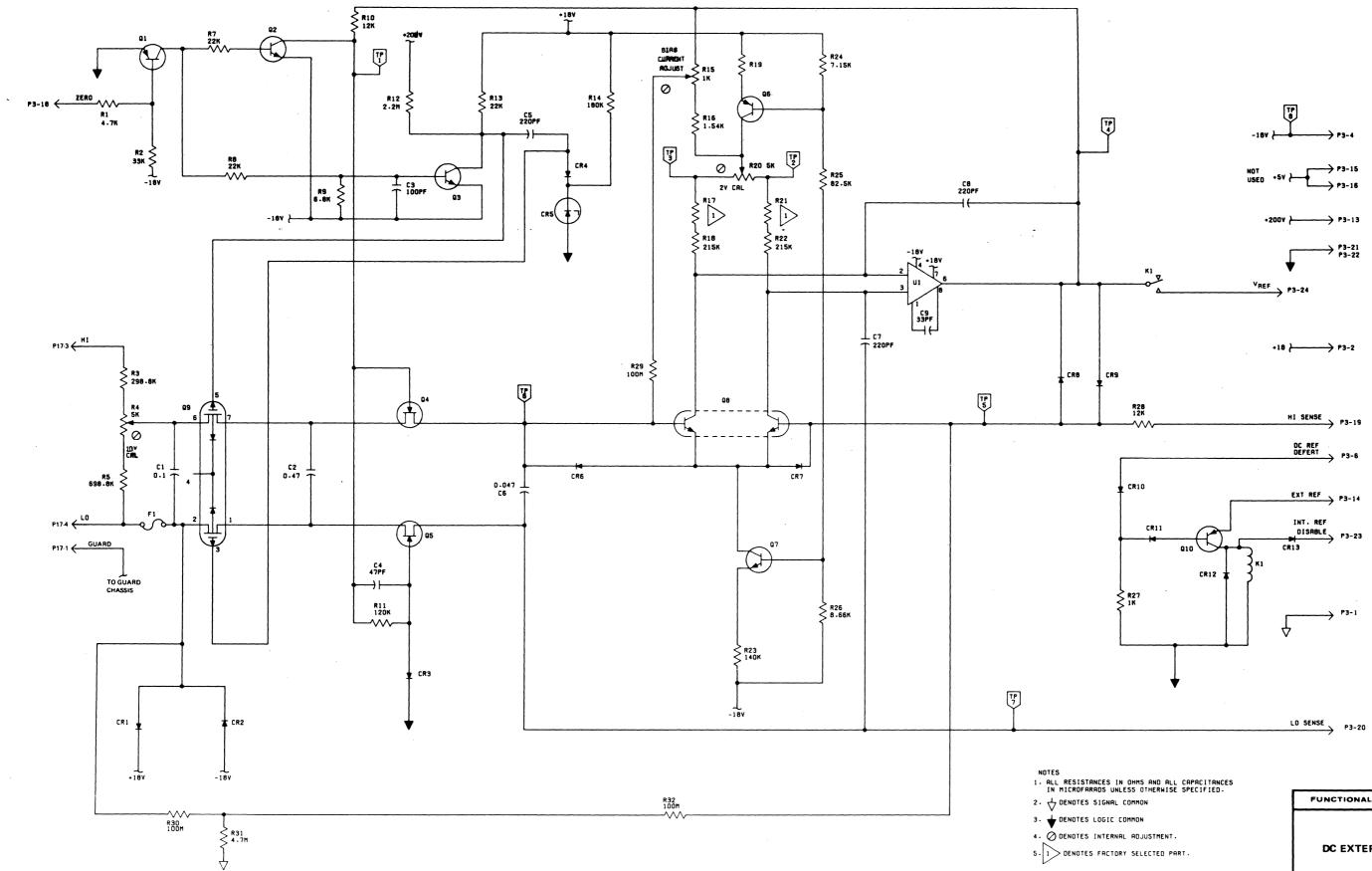

As can be seen in the block diagram (Figure 1), the instrument consists of several basic blocks; the Power Supply, Buffer, A-D Amplifier, Logic Control, Display, and the Inter-Connect assembly. Within the Power Supply four separate voltages are sourced: A +200V DC supply for the display tubes, a +15V DC, and a -15V DC operating supplies, and a +5V DC logic supply.

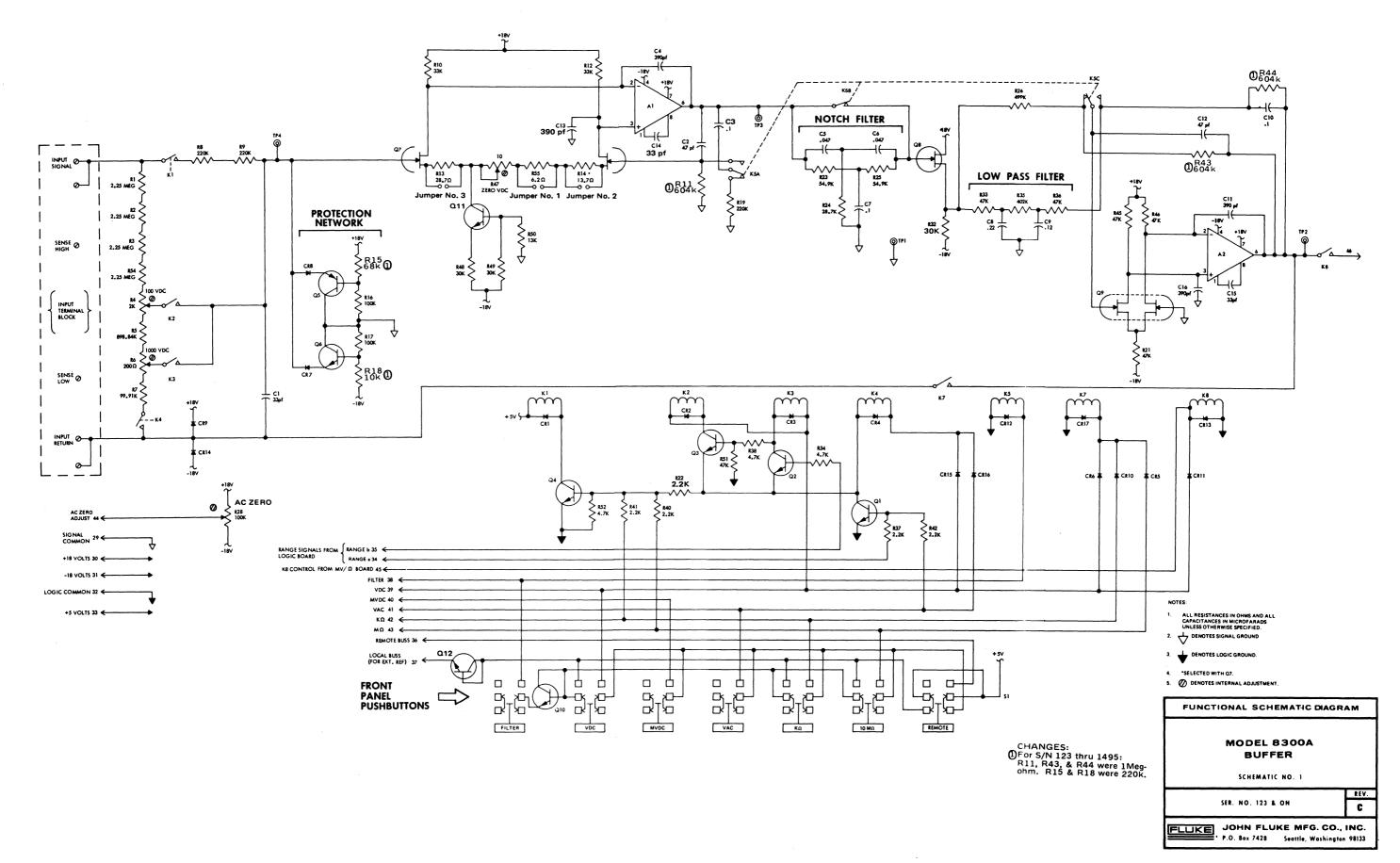

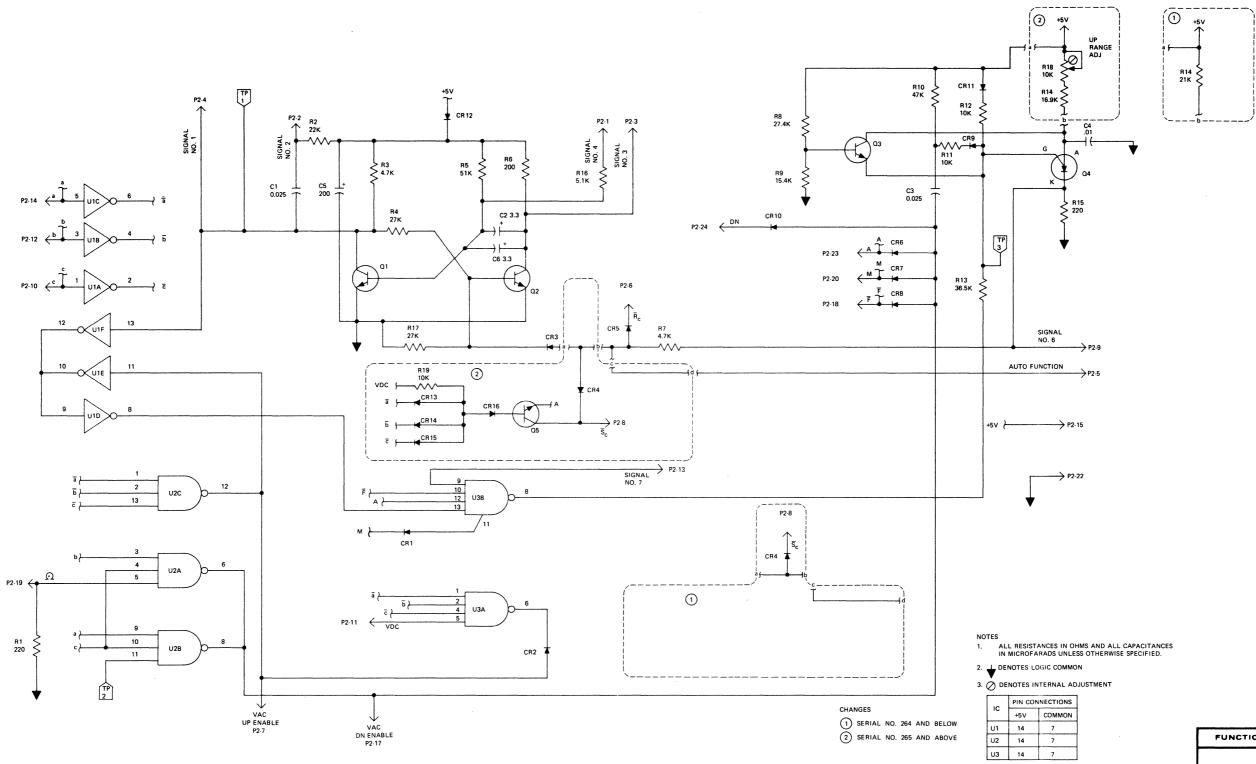

## BUFFER (Figure 2)

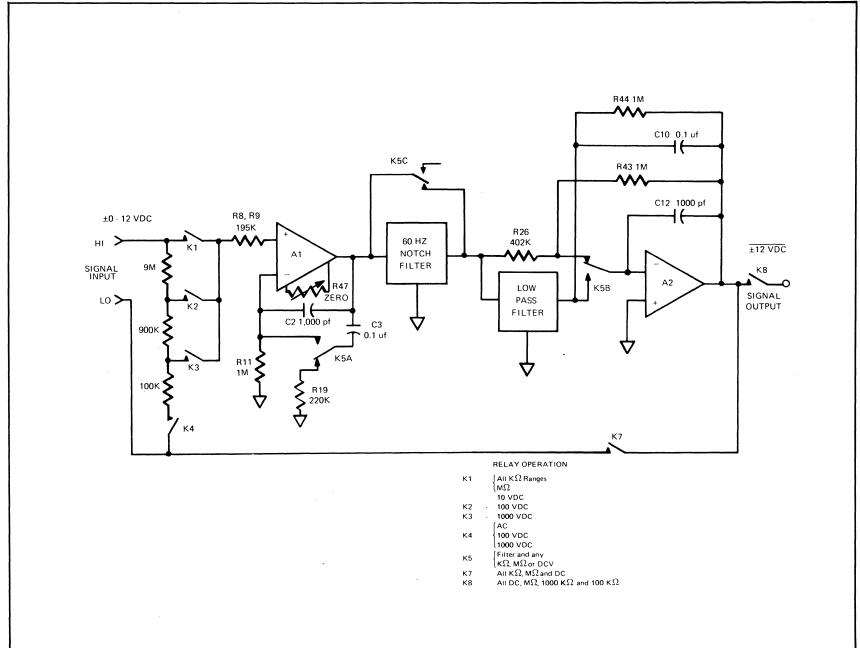

The Buffer is an operational amplifier with a gain of one inverted. If the Buffer sees a +1V at its input terminals, it will produce a -1V at its output terminals. The primary purpose of the Buffer is isolation and impedance matching. The Buffer assembly also contains the Range Divider for DC giving division ratios of 1/1, 10/1, 100/1, and 1000/1. It contains a switchable four-pole active filter which provides losses in excess of 60 DB at 50 Hz cycles, greater than 65 DB at 60 cycles, and 100 DB or more at 200 cycles and above. The Buffer also contains its own Logic circuitry for range and function switches.

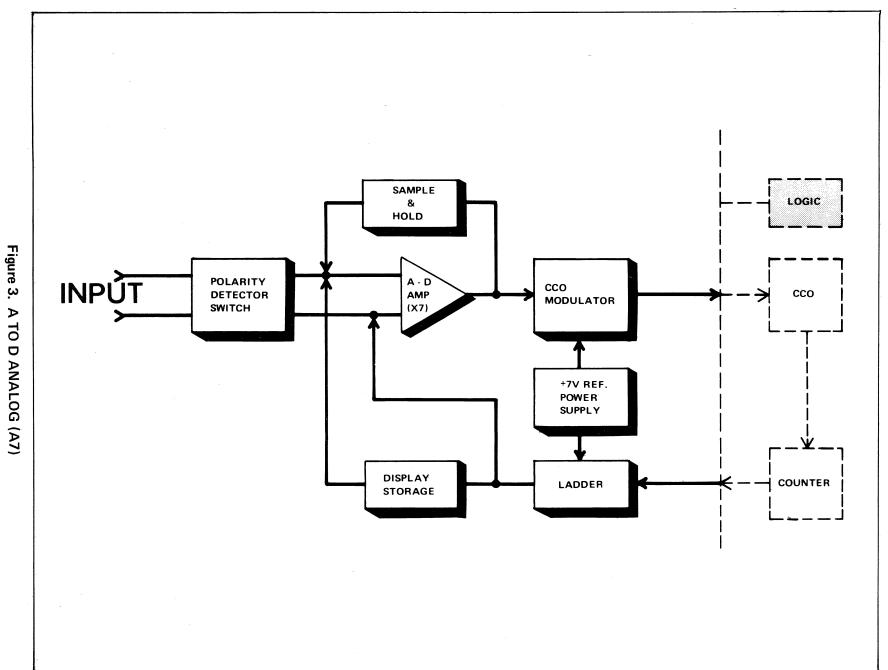

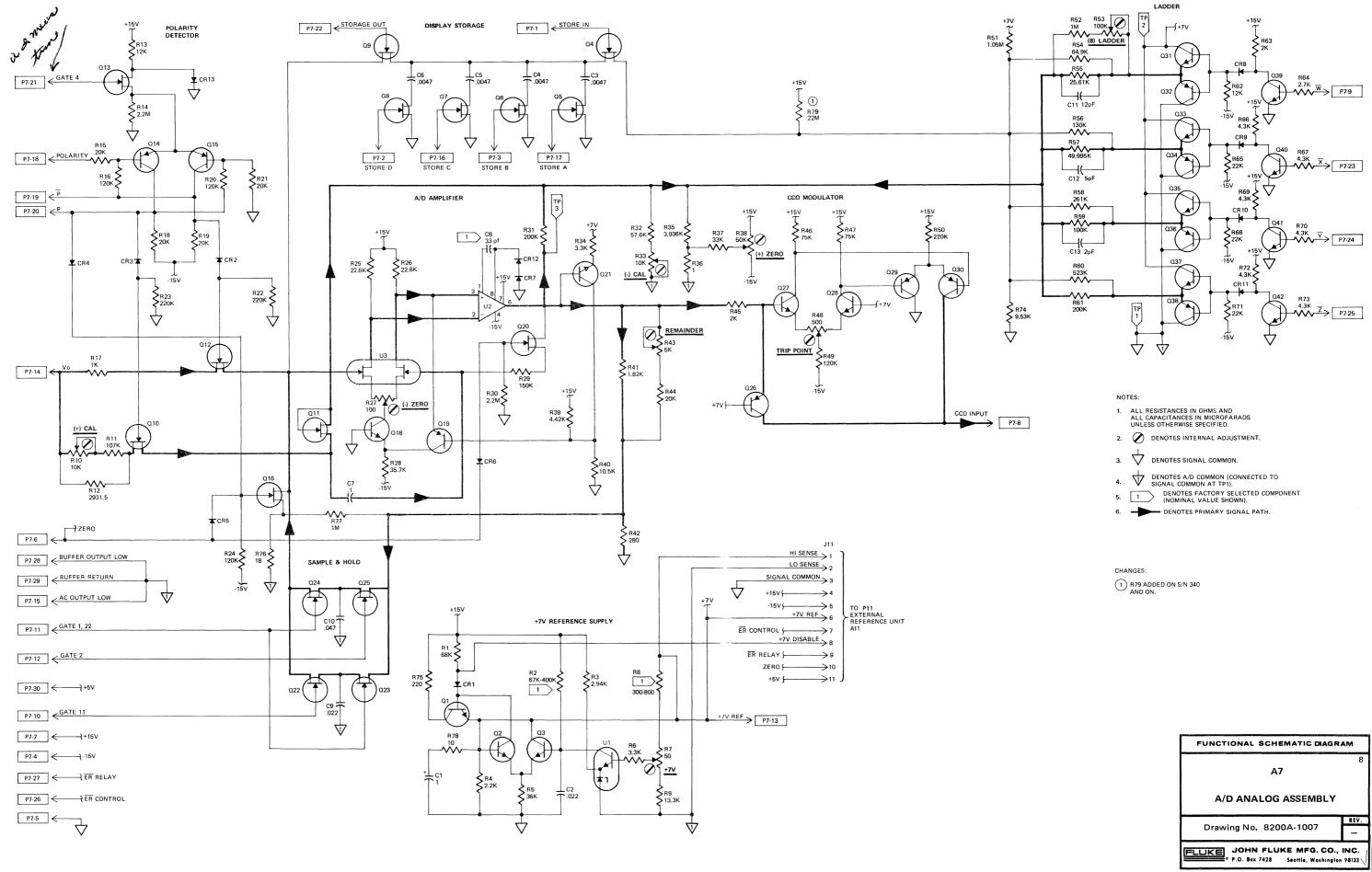

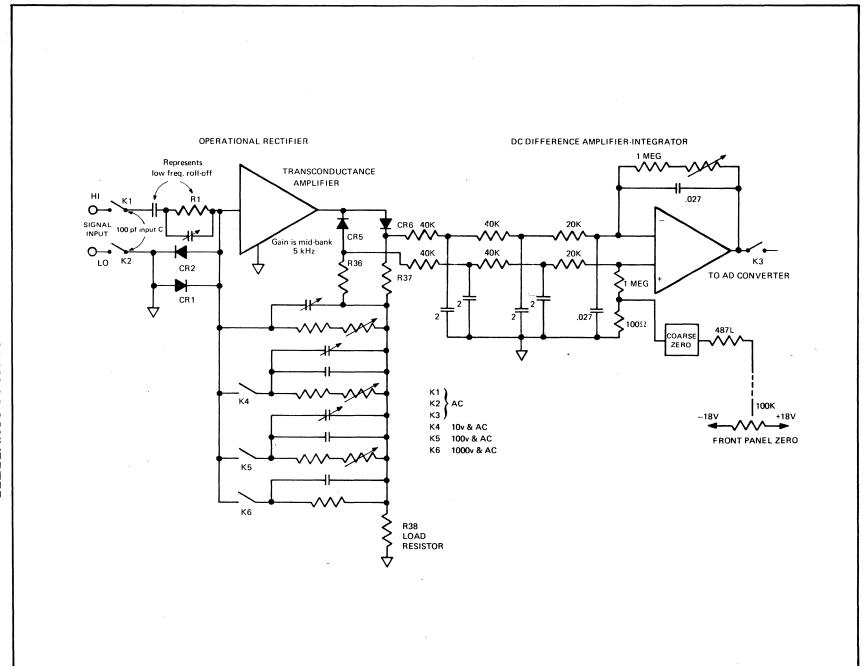

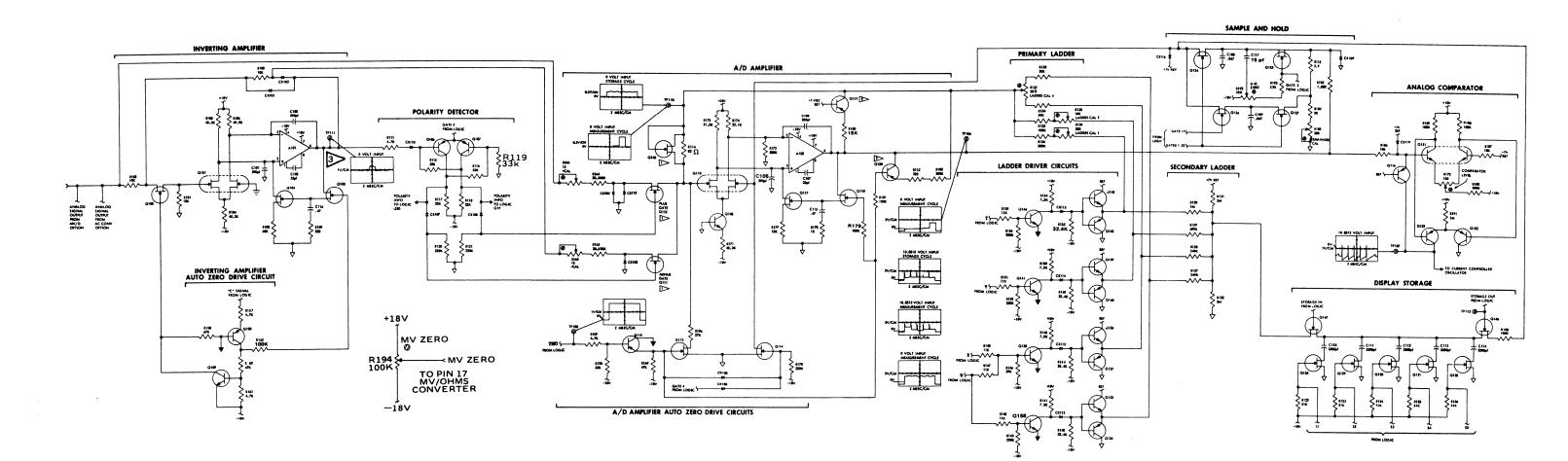

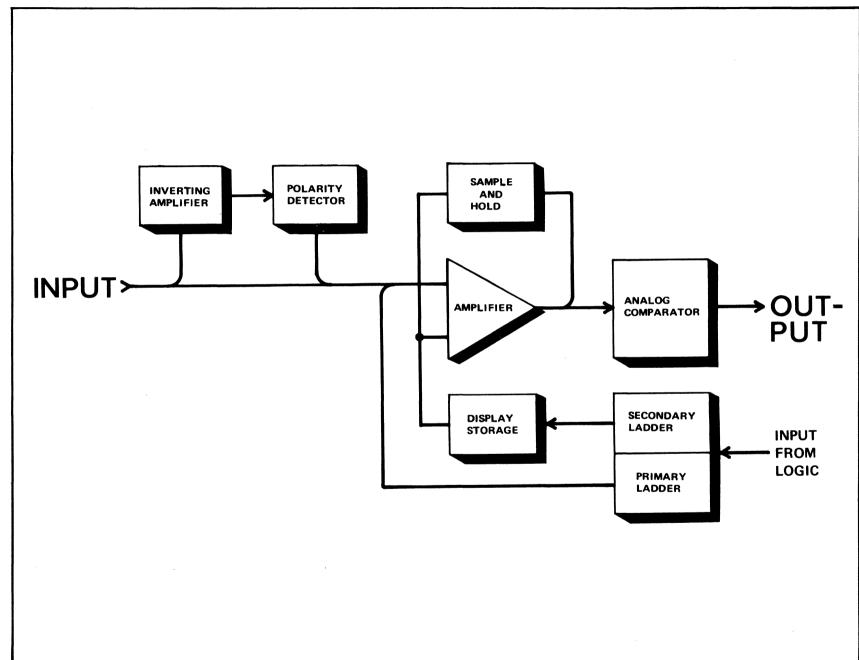

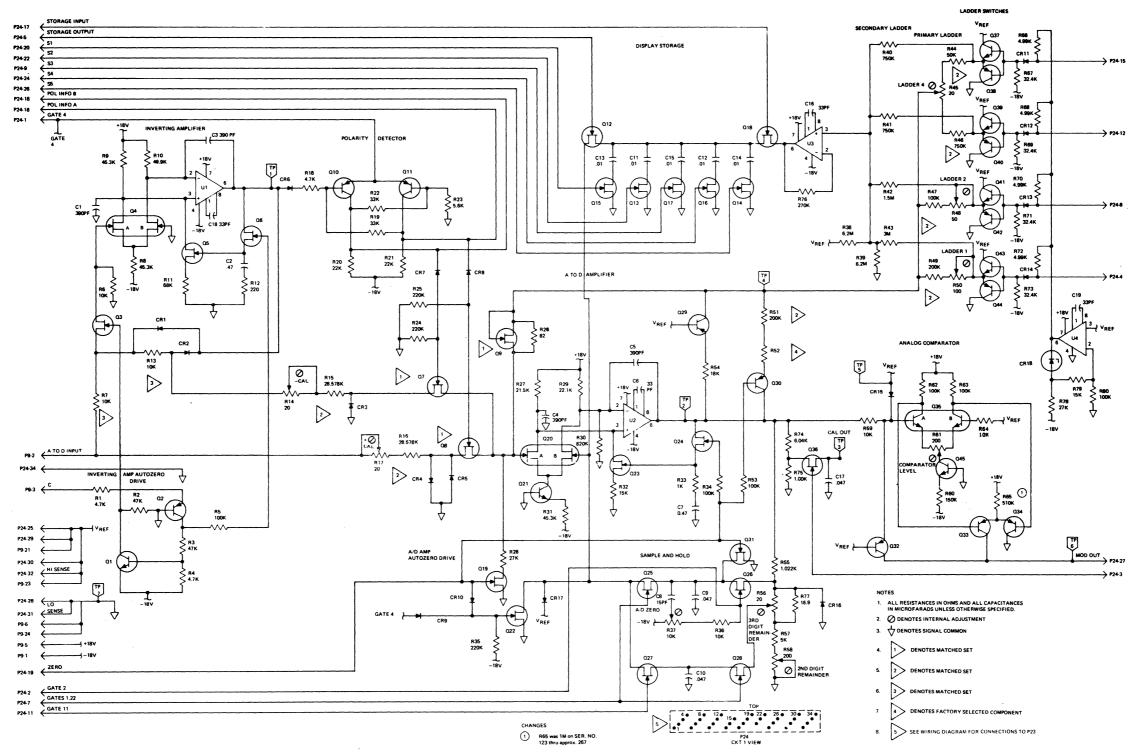

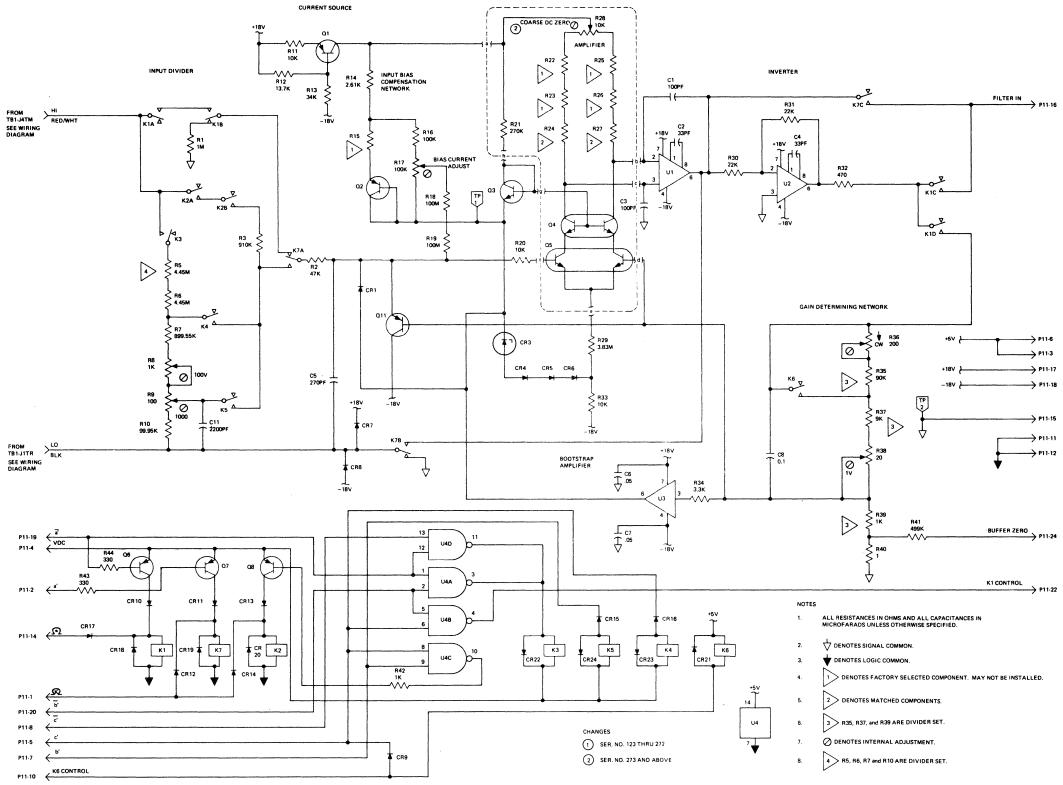

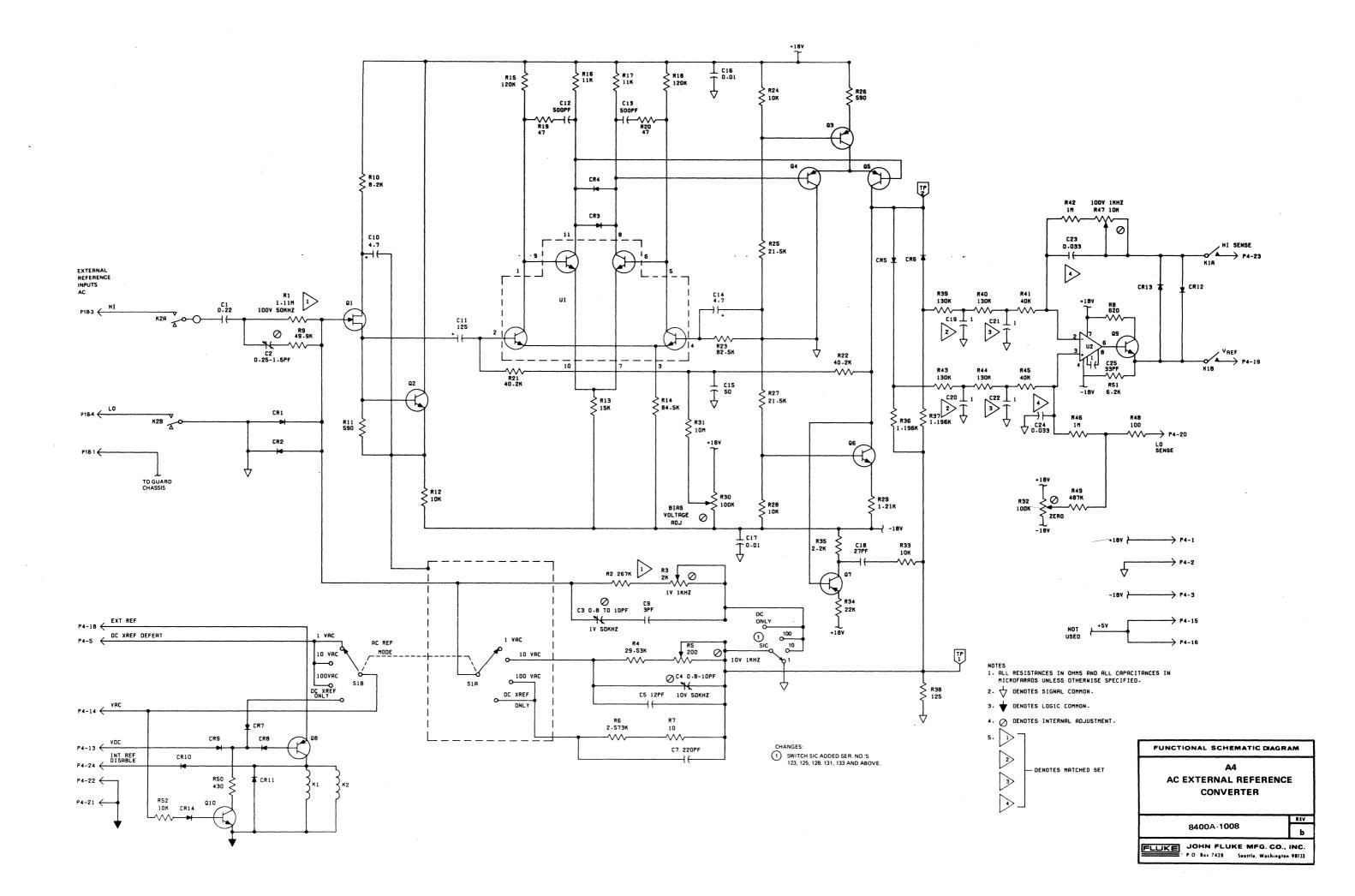

#### A-D ANALOG (Figure 3)

The A-D Analog assembly is made up of several circuits: the Polarity Detector and Switching circuit which provides the instrument with its automatic polarity detection and indication. It contains the Sample and Hold circuitry that is used when the instrument is initially digitizing a measurement. The +7V DC Reference Supply is also contained within the A-D Analog module, as is the Current Oscillator Modulator, the Ladders, and the Display Storage network.

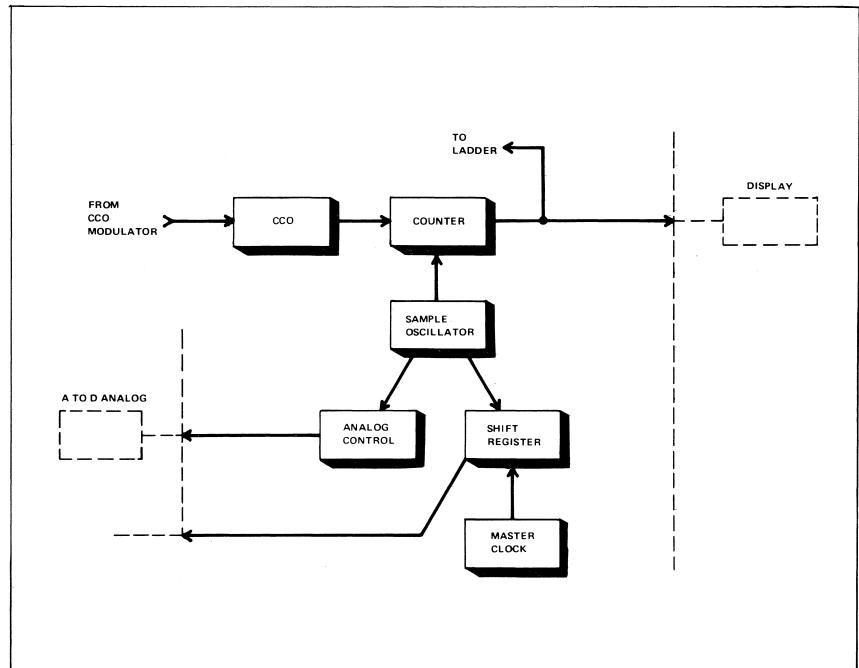

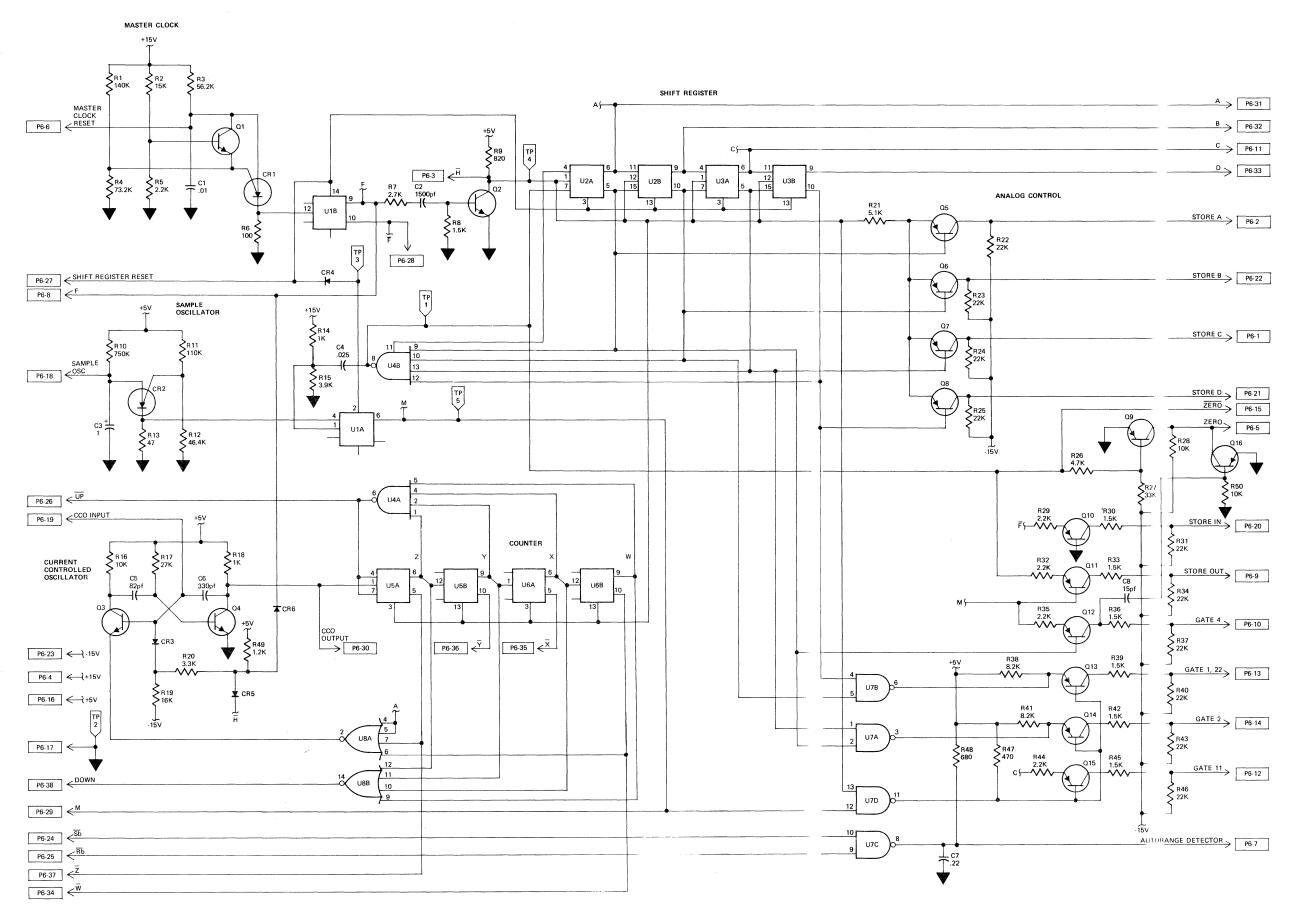

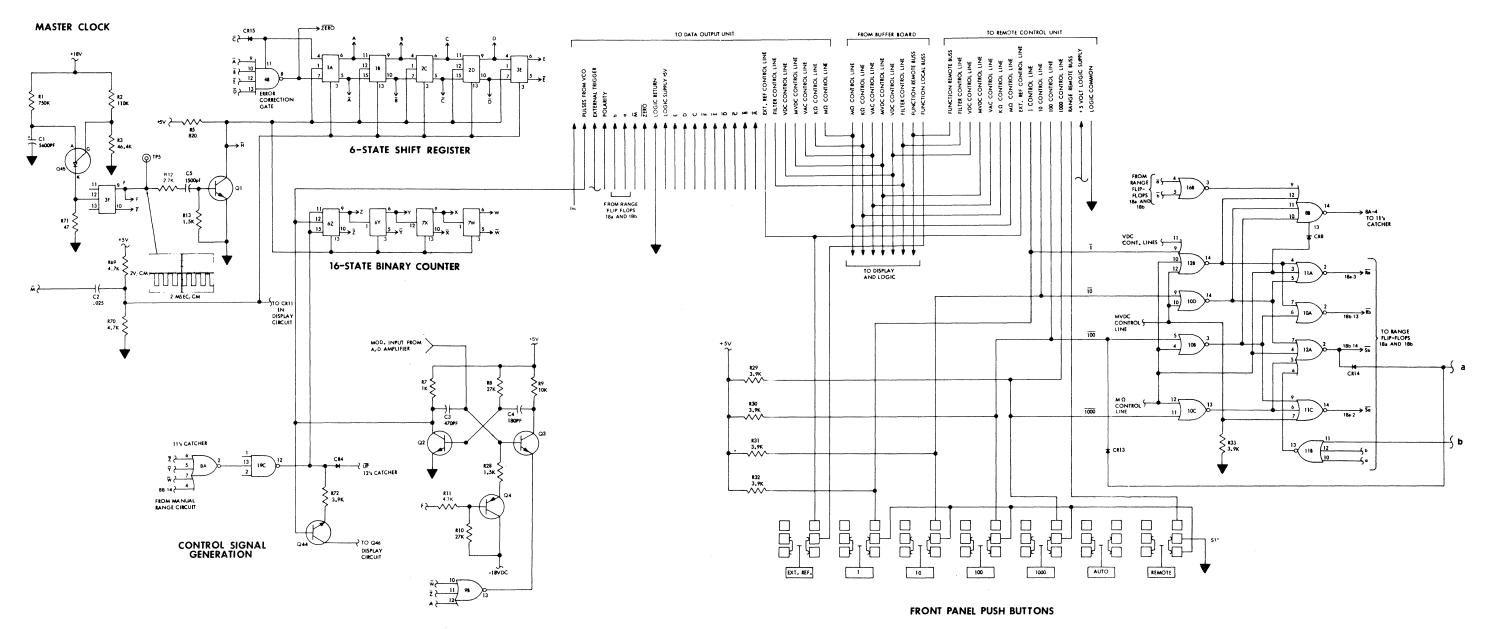

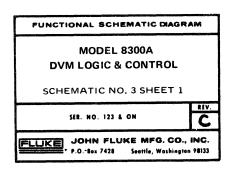

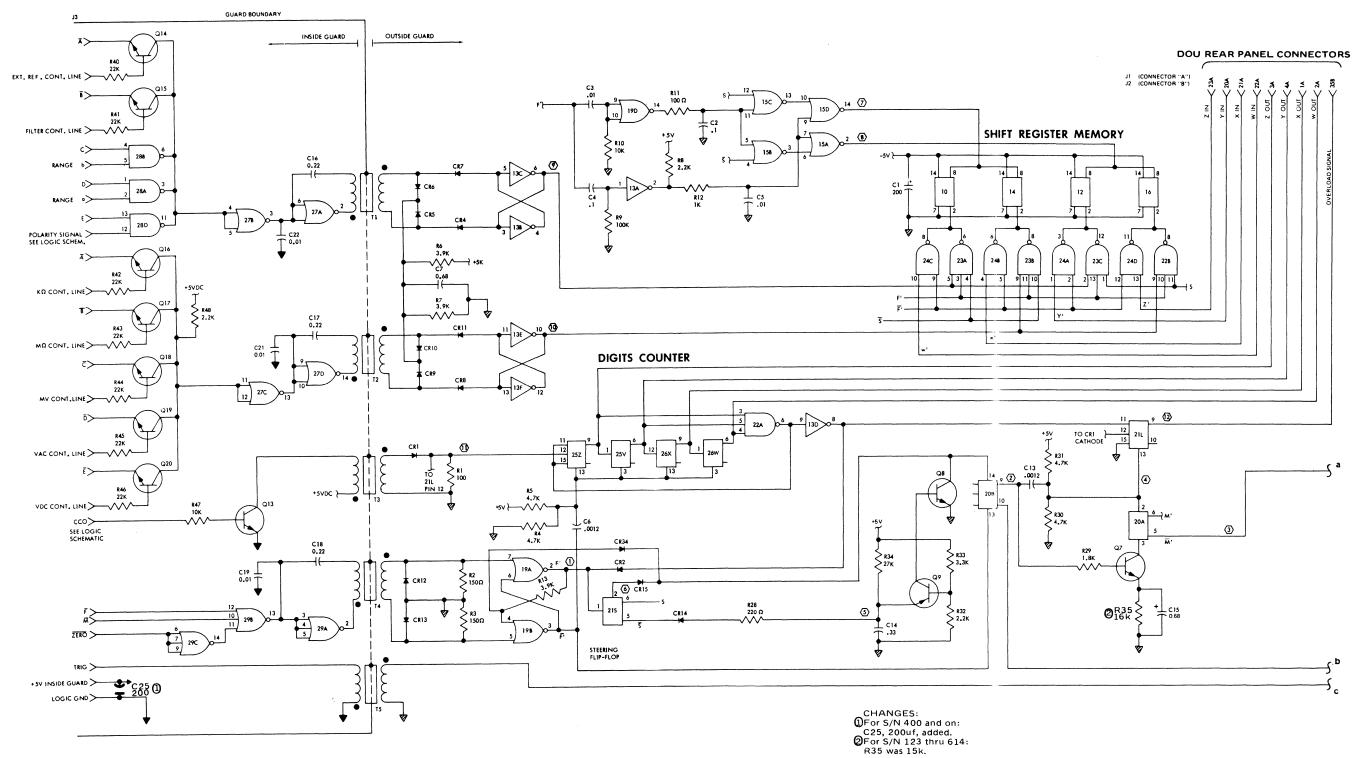

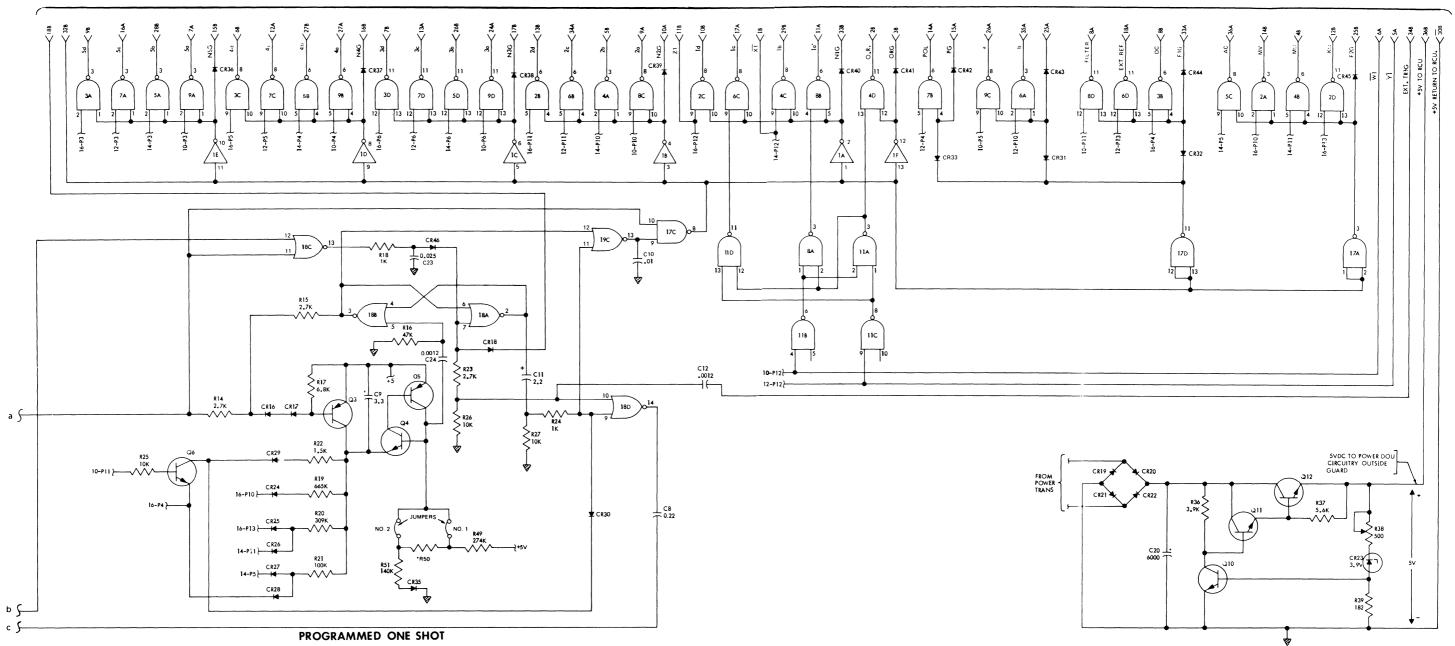

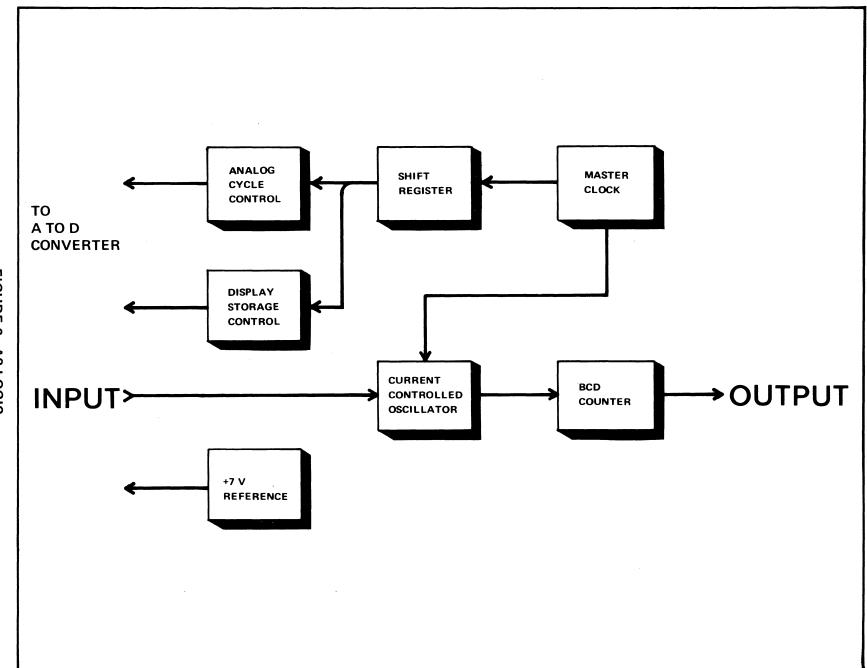

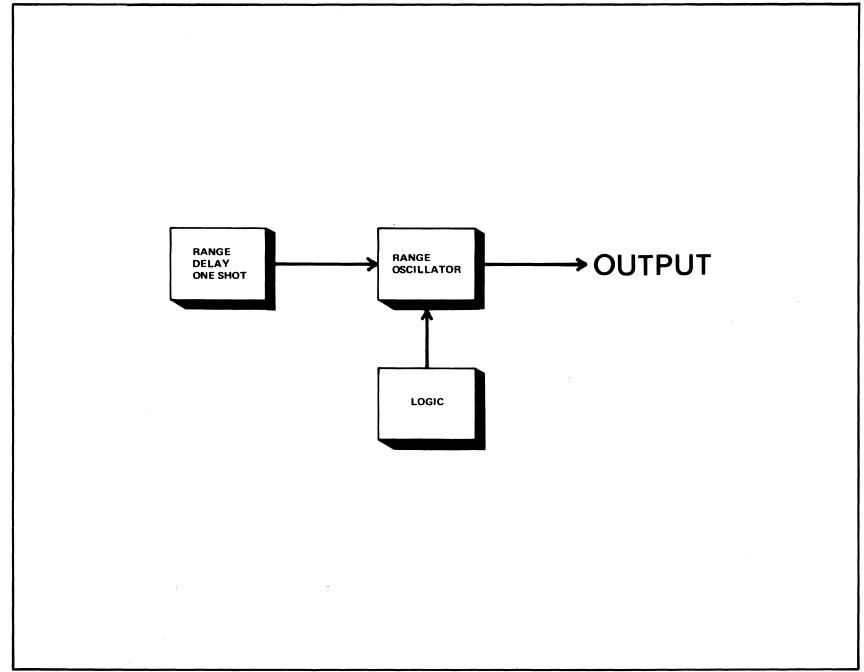

## LOGIC CONTROL (Figure 4)

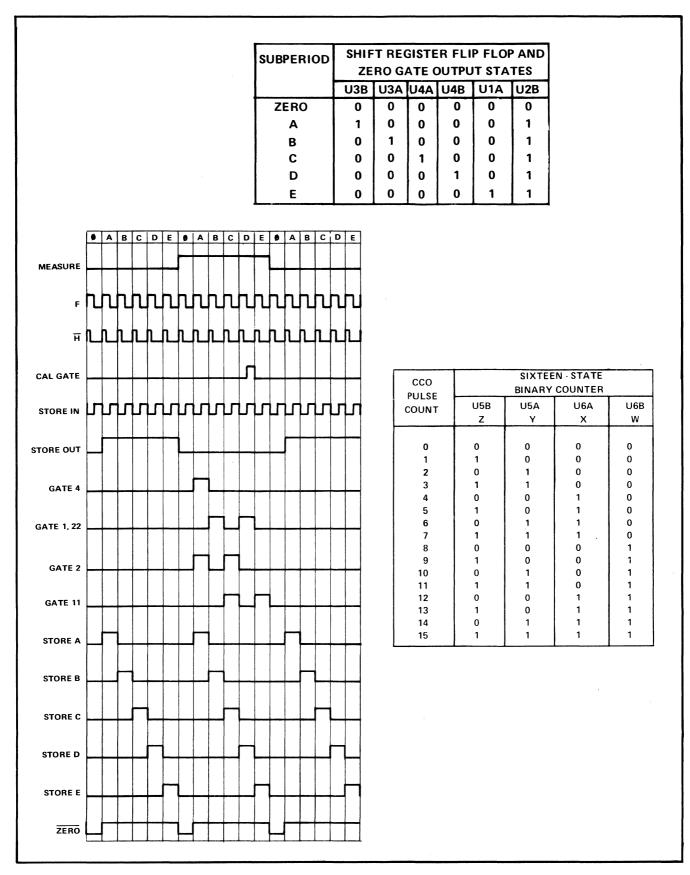

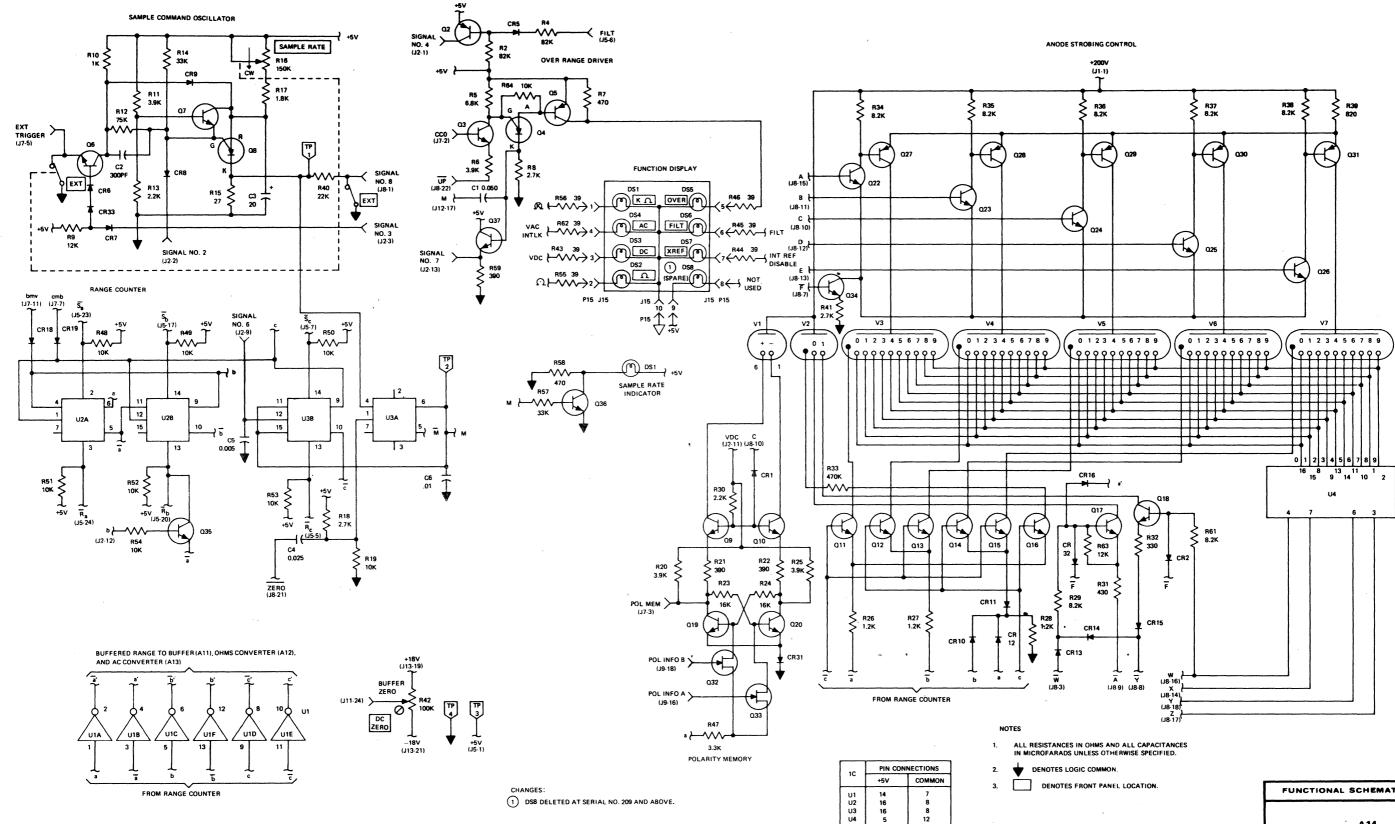

The Logic Control contains the Constant Current Oscillator and the Counter. In addition, it also contains the Master Clock, which generates the basic timing for the instrument. The Master Clock feeds the Shift Register which generates the five timing periods; ZERO and the four digitizing periods. In addition, a Sample Oscillator is provided that feeds both the Shift Register and the Analog Control circuitry. The Sample Oscillator provides the Measure and Storage pulses. In addition, the Analog Control assembly provides gating pulses that are required for the special switching requirements in Recirculating Remainder. The Sample Oscillator also feeds the Shift Register to synchronize the start of Measurement time with the Master Clock and the Shift Register.

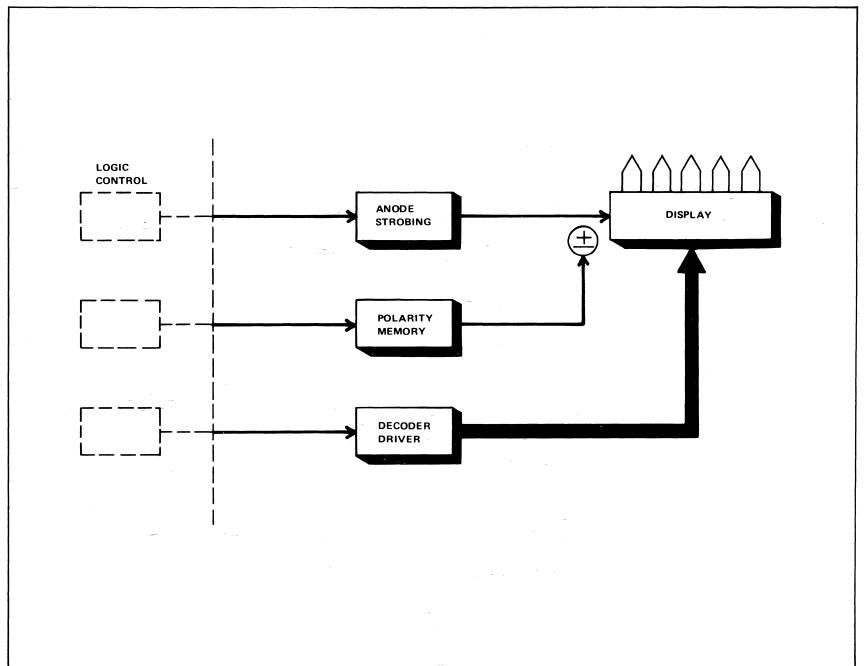

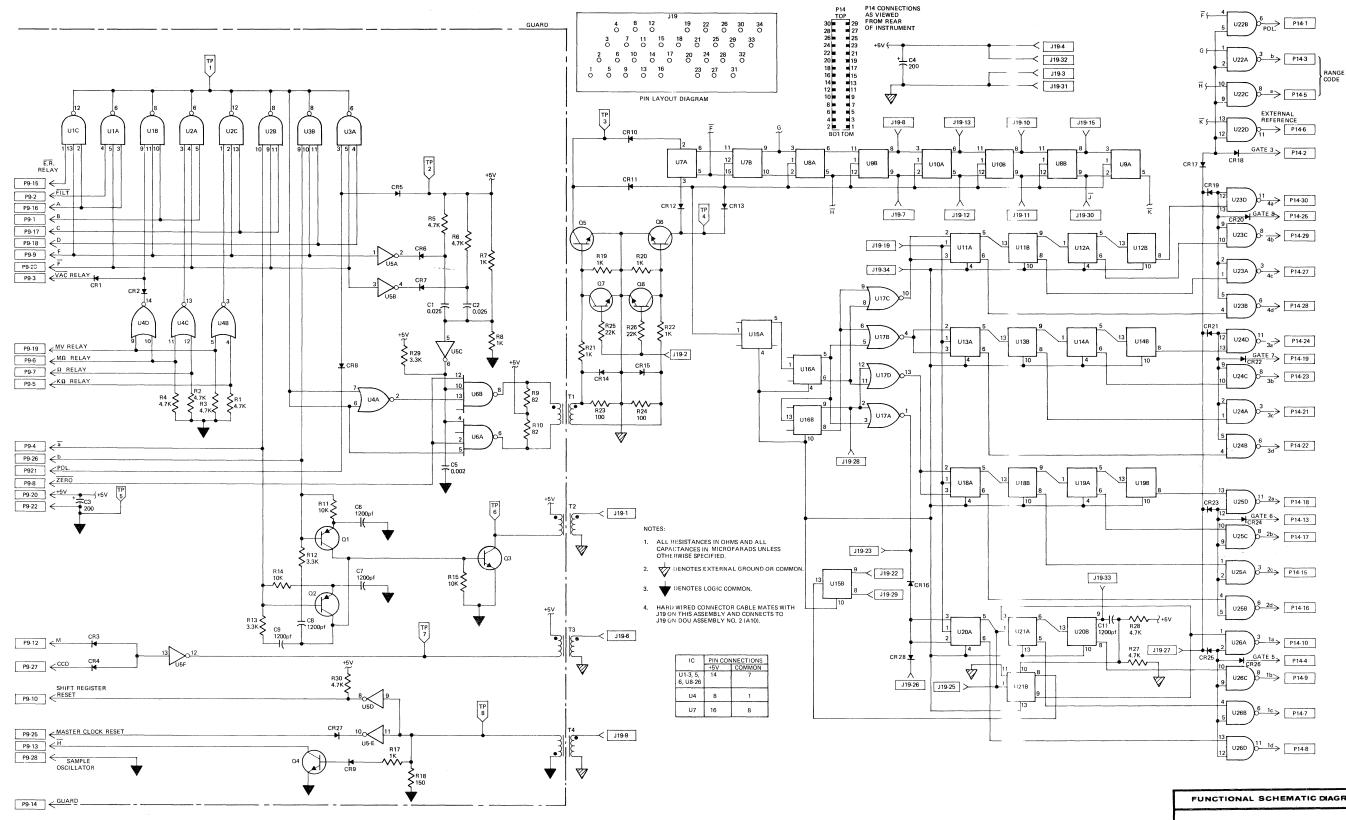

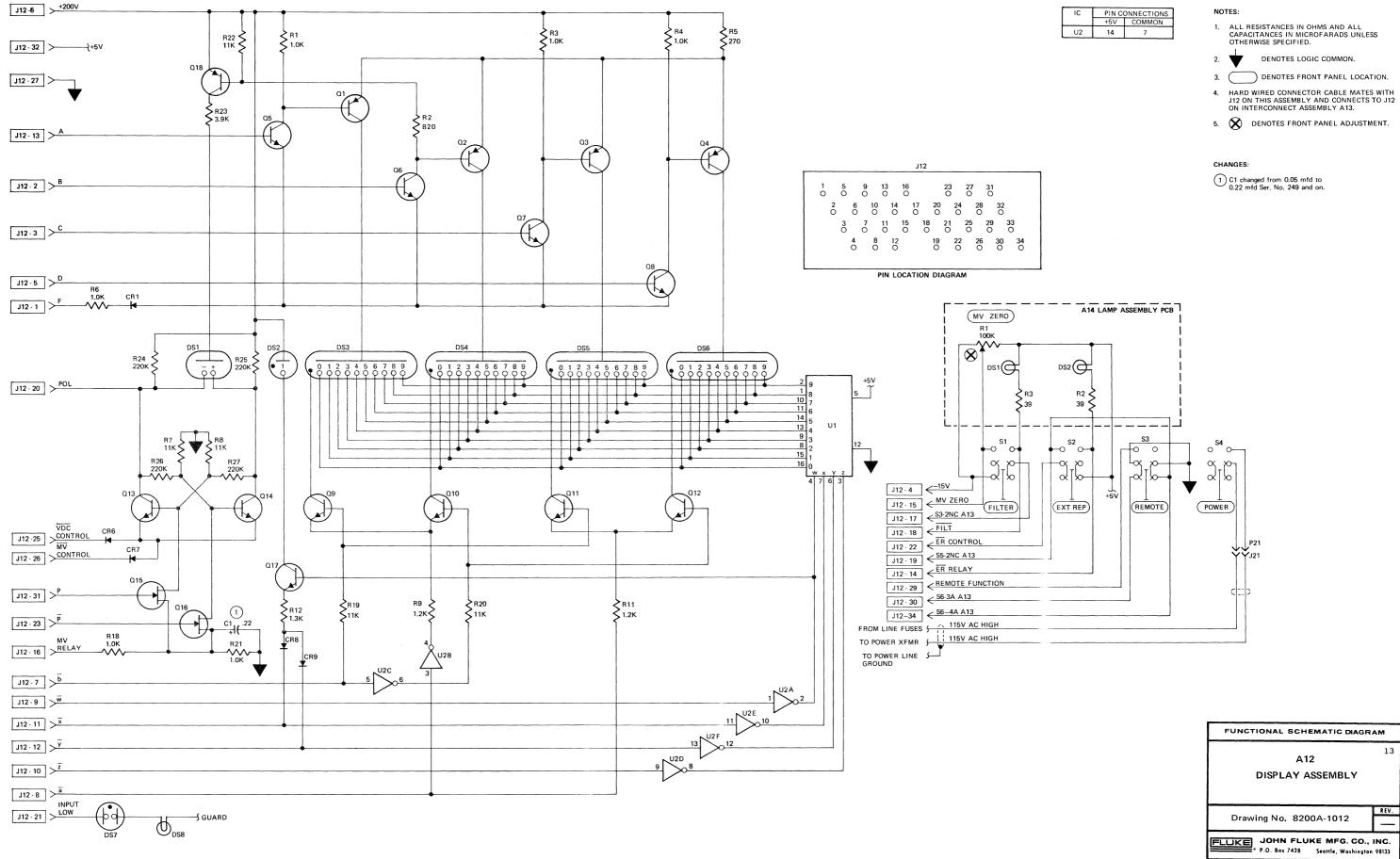

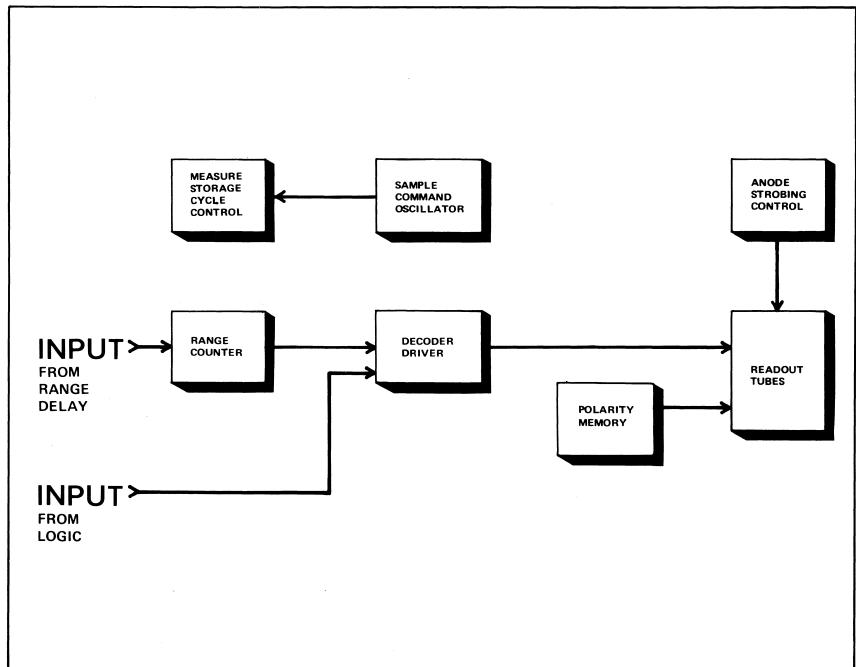

#### DISPLAY (Figure 5)

The Display assembly contains four circuit functions; Anode Strobing, Polarity Memory, Decoder Driver, and the Display. Anode Strobing, using the timing pulses from Logic Control, turns the display tubes ON in the proper sequence. The Polarity Memory circuit is a bi-stable multivibrator that receives information from the Polarity Sensing circuits in the Buffer, and holds that information in "memory" until it is displayed. The Decoder Driver is a sixteen state, monolithic device used to translate the Binary Coded Decimal information from the Counter, into decimal information to be used in order to ionize the proper digit in each display tube. The Display circuitry consists of the various interconnections required for supporting the illuminated display tubes and lights.

З

Figure 2. BUFFER (A4)

ഗ

Figure 4. LOGIC CONTROL (A6)

Figure 5. DISPLAY (A12)

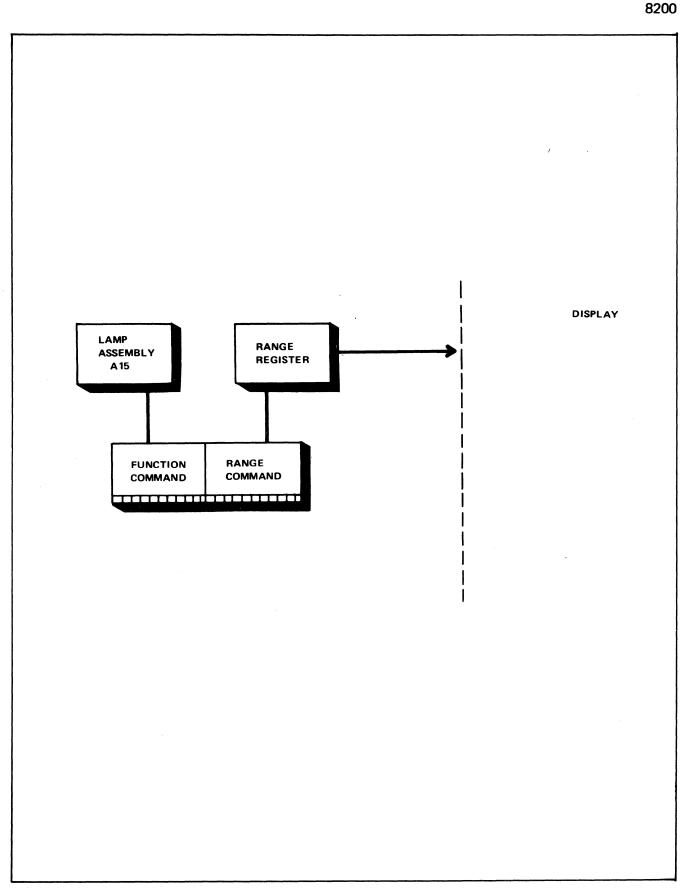

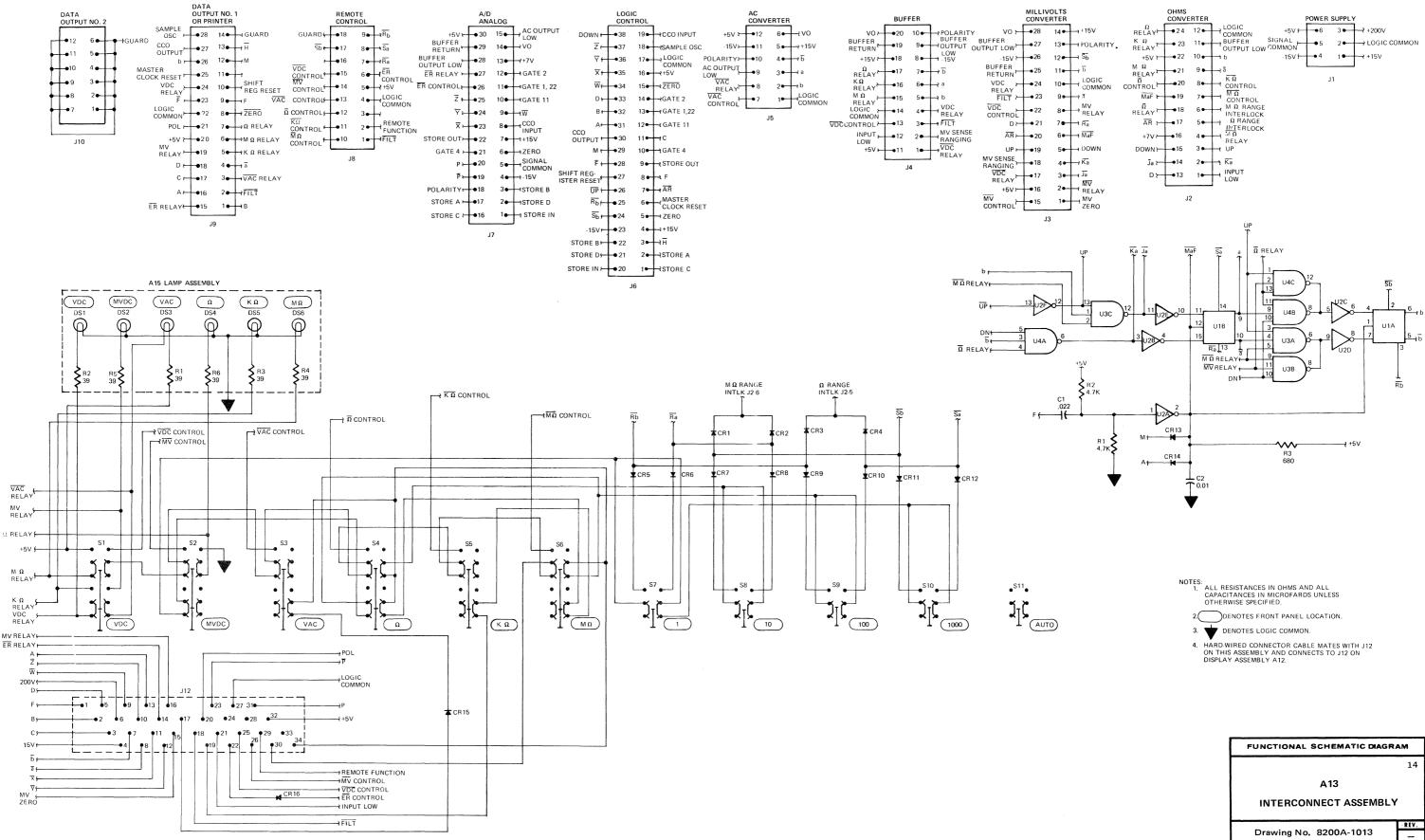

# **INTERCONNECT (Figure 6)**

The Interconnect assembly contains the circuits used for Range Command, Function Command, Range Register, and the Lamp Assembly used to display function selection. The Function and Range Command circuitry consists of the manual push-button switches used for selection. The Range Register contains the circuitry used in the autoranging functions.

# **OPTIONS (Figures 7, 8, and 9)**

Figures 7, 8, and 9 are the block diagrams of the Option assemblies. Each of the options contains its own Logic circuitry, in addition to the circuitry to support its functional purpose.

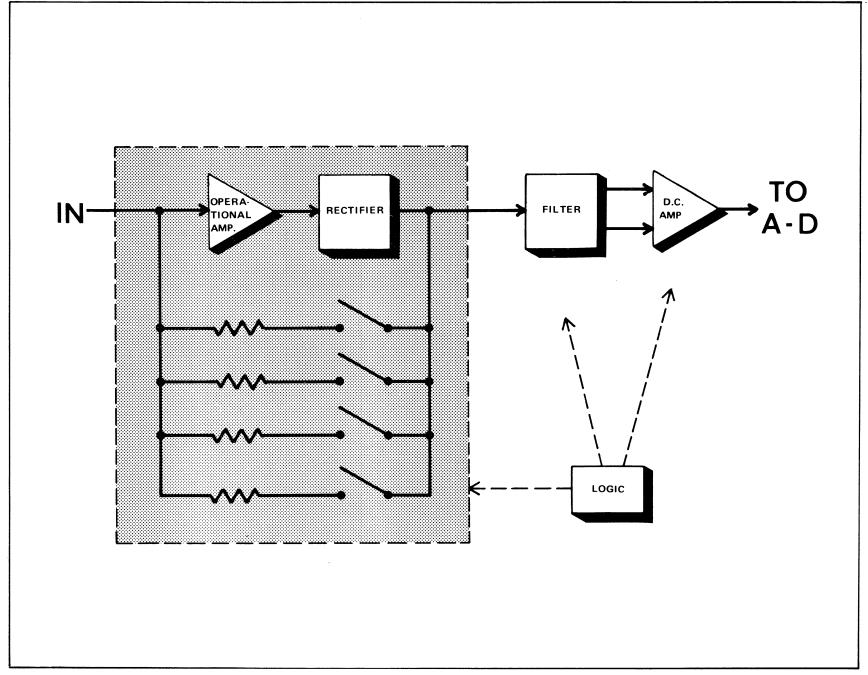

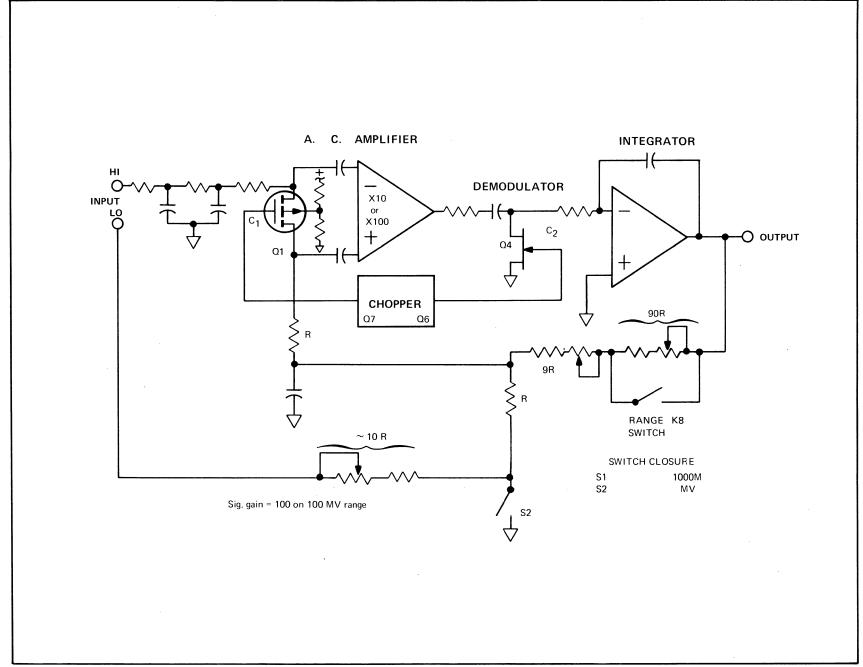

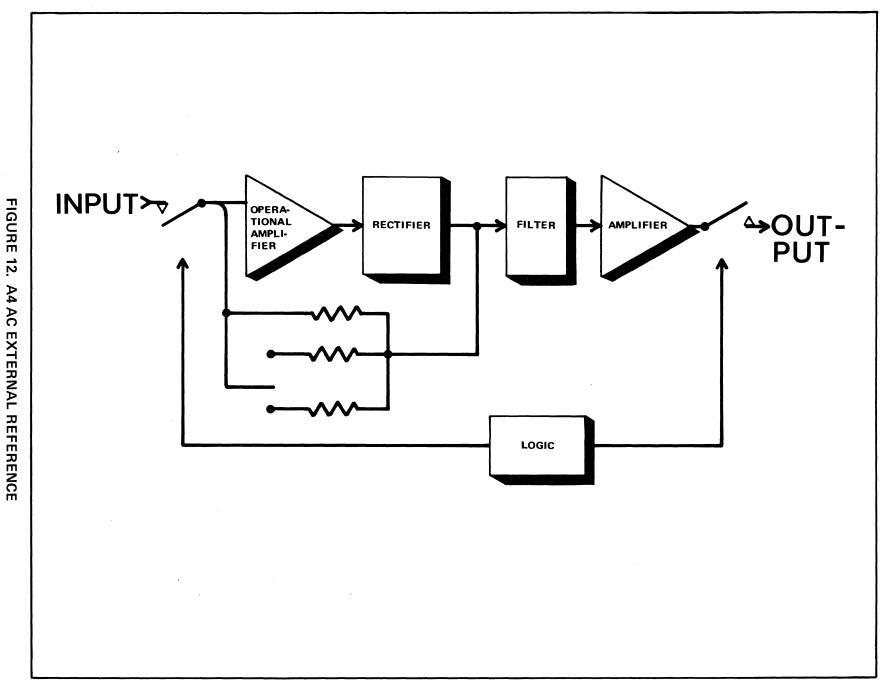

The AC Converter, shown in Figure 7, contains two operational amplifiers; one used in the input to the rectifier, and one which is used to match the output impedance of the Filter to the input to the A/D circuitry. Range switching is accomplished by switching the resistors in the feedback loop of the AC operational amplifier.

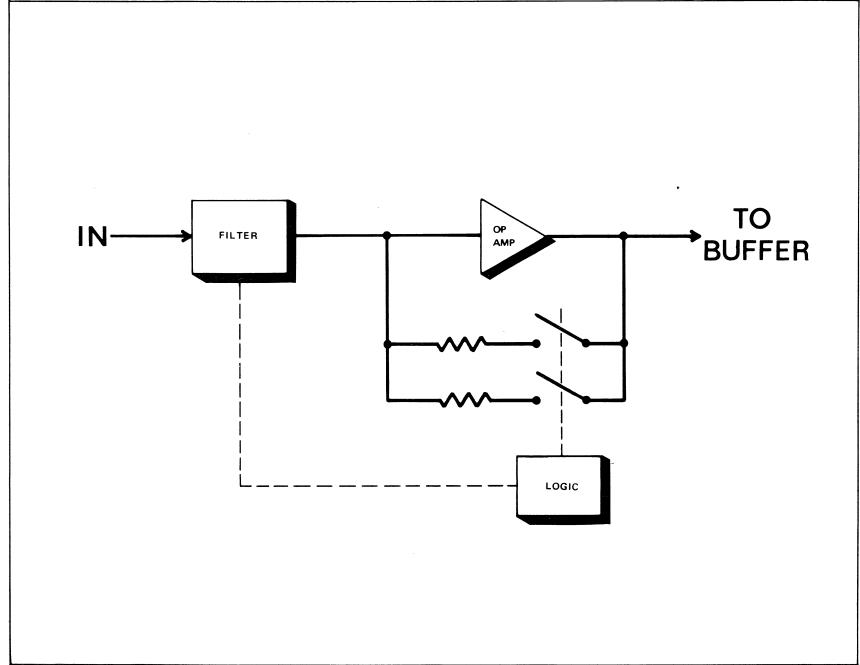

The MV Converter, shown in Figure 8, contains a Filter and an operational amplifier with two feedback loops. These feedback loops control the gain of the amplifier. In the 10 mV range the amplifier has a gain of 100, and in the 100 mV range it has a gain of 10.

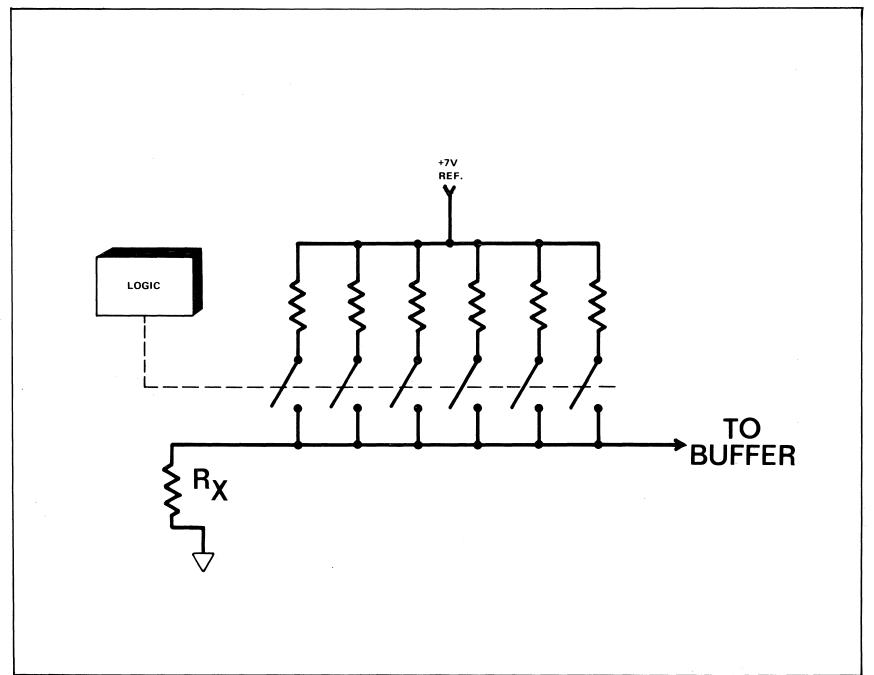

The Ohms option uses the +7 volt reference voltage, as shown in Figure 9, through series resistors to develop a voltage across the Rx or resistance to be measured. The resulting voltage across the unknown resistor is translated into an ohms measurement. This option feeds the Buffer assembly rather than feeding the A/D Analog assembly as do the other Options.

# **BLOCK DIAGRAM EXAMPLE VOLTAGE MEASUREMENT**

Referring to the full block diagram given in Figure 10, the operation can be described as follows:

- 1. The input is applied to the buffer and divided down so that the output of the attenuator will be within the range of ZERO to 1.6 volts. The Filter is selected or not selected and the signal is passed to the Buffer Amplifier which has a gain of one and whose output is inverted. It is the purpose of the Buffer to keep the input impedance as high as possible while matching the impedance of the A-to-D Amplifier circuit which follows it.

- 2. A-to-D Analog Amplifier assembly receives the signal at the Polarity Detector which operates the FET switches applying the proper polarity to the A-to-D Amplifier which has a gain of 70. When the output of the amplifier is greater than the 7 volts, the CCO Modulator will produce current.

- 3. Current from the CCO Modulator is fed to the Logic Control assembly, where it is fed to the Current Control Oscillator. The Current Controlled Oscillator produces a pulse train. This pulse train is fed to the BCD Counter.

- 4. The BCD Counter counts the pulses from the CCO and feeds BCD information to the Decoder Driver which will furnish a ground to the proper numeral line to all of the display tubes.

- 5. The BCD Counter output is also fed to the Ladder Switches and Drivers and each BCD count causes the Ladder outputs to advance by 0.1 a volt. The output of the Primary Ladder is fed back to the input to the A-to-D Amplifier.

Figure 6. INTERCONNECT (A13)

Figure 7. AC CONVERTER --01

Figure 9.  $\Omega$  CONVERTER -03

Figure 10. BLOCK DIAGRAM

- Note: Since the output of the differential operational amplifier is equal to the difference in input voltage times the gain, the output of the Primary Ladder would cause the output voltage of the A-to-D Amplifier to decrease until it is below 7 volts. When the output of the A-to-D Amplifier is less than 7 volts the CCO Modulator will supply no more current to the Oscillator. The remainder voltage is divided by 7 and is moved into storage in Sample and Hold.

- 6. The BCD information from the counter being fed to the Decoder Driver translated into decimal format, and as pointed out previously, will cause a ground to occur on the proper numeral line to all of the display tubes. As the count is finished in each time period, the Anode Strobing circuit will cause the proper display tube to light and display the number that has been grounded. The first display tube displays the number digitized in the A time period. The second display tube displays the number digitized in the second or B time period, etc.

- 7. The output of the A-to-D Amplifier is divided by 7 prior to placing it in Sample and Hold storage. This is the input difference times 10 since the gain of the amplifier is 70, which is divided by 7 before storage. During the second digitizing or B time period, the first remainder is placed on the input of the A-to-D Amplifier, and is digitized and displayed just as was the first digit. Again, the remainder will be stored in another section of Sample and Hold to be used during the third digitizing period. This process is repeated until all four digits have been digitized and displayed.

- 8. Display Storage functions in such a manner as to receive an analog charge on each of a series of a capacitors representing the digit that was developed in each digitizing period. Though the analog values are stored initially in the Measurement Mode, the output of the Display Storage is used only during the Storage Mode of operation.

# THEORY OF OPERATION

# TIME

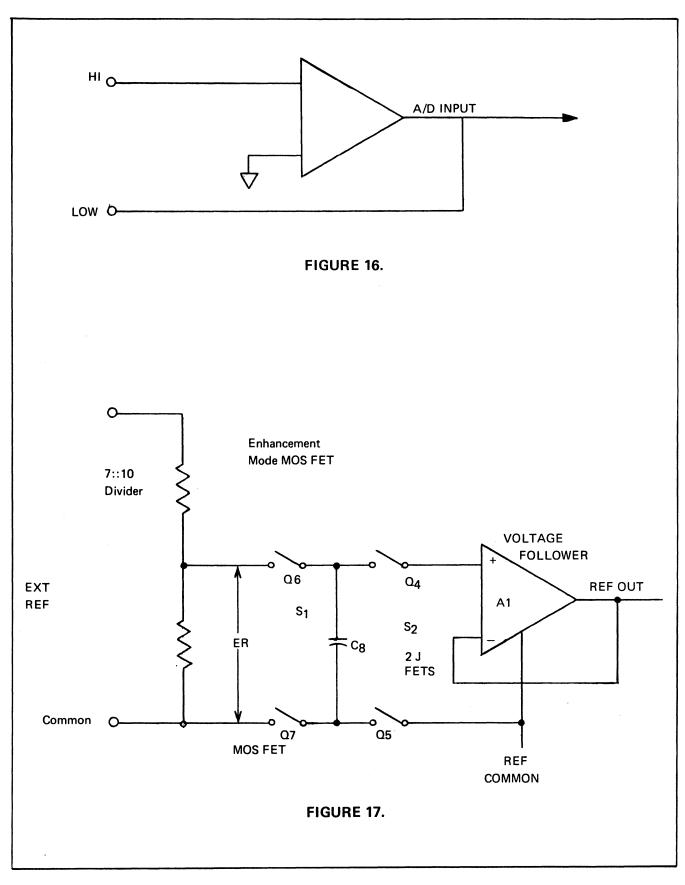

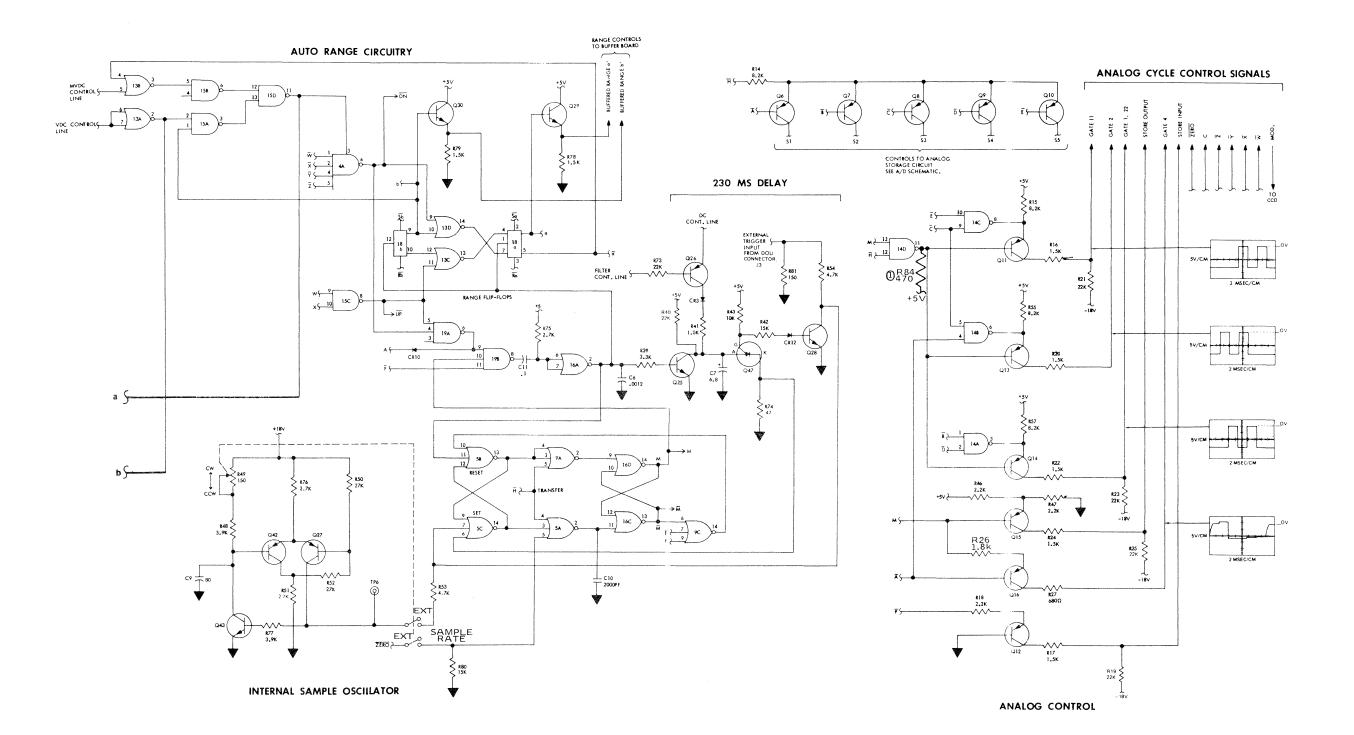

In the Recirculating Remainder system there is an obvious need for time control for Measurement and Storage Modes of operation, in addition to digitizing, display, error removal, and other switching functions that must be carried out in the instrument. Figure 11 is a timing diagram of the time pulses generated in an 8200. The Master Clock output is a 4 kilohertz pulse. This results in one pulse every 250 micro-seconds. Looking at Logic Control schematic (A6), the Master Clock feeds the clock input of the J-K flip-flop U1B, resulting in the F and F outputs; a square wave with a 500 micro-second cycle time.  $\Omega 2$ , accepting the F signal, produces, at its collector, the H signal which is fed to the Shift Register comprising U2A, U2B, U3A, and U3B. Each of the J-K flip-flops in the Switch Register generates one of the digitizing period pulses. The Q output of flip-flop U2A generates the A time output. U2B generates the B time output. U3A generates the C time output. U3B generates the D time output. ZERO is generated by the NAND gate U4B. The inputs to the NAND gate being  $\overline{A}$ ,  $\overline{B}$ ,  $\overline{C}$ , and  $\overline{D}$ ; when all of these outputs are high, the ZERO pulse is generated. Looking to the right of the schematic diagram, ZERO pulse is generated by the inversion that takes place through Q9. The Sample Oscillator element is CR2, a programmable unijunction transistor which is RC timed and locked in operation with the Master Clock. From the J-K flip-flop U1A, the M or Measure pulse is derived, which is used throughout the instrument for the Measure Mode functions. In the Analog Control circuitry the gate pulses are generated for the various storing and timing functions throughout the instrument.

a and b-a and t-a and b-10 100 1000 TEST в С Ø Α С D Ø ø Α D В С D ø Α В POINT 500 μs MASTER A6 CLOCK CR1 A6 F U1B 4 μs A6 Ħ TP4 2.5 ms A6 Α U2A A6 U2B В DIGITIZING PERIODS **A**6 С U3A A6 TP1 D 2.5 ms A6 0 TP5 mean A6 STØRE Storage, MEASURE CR2 SAMPLE A6 RATE Q12 TRIGGER - - eres Tuns A6 (A) GATE 4 Q14 NOTE: GATE PULSES DO . . A6 (C) (A) NOT OCCUR DUR-GATE 2 Q14 ING STORAGE TIME. A6 (B) (D) c.1 Q13 GATE 1 & 22 A6 (C) GATE 11 Q15 С D ø С D ø Α в D ø С В ø Α В Α

RANGE

CODE Ta to

15

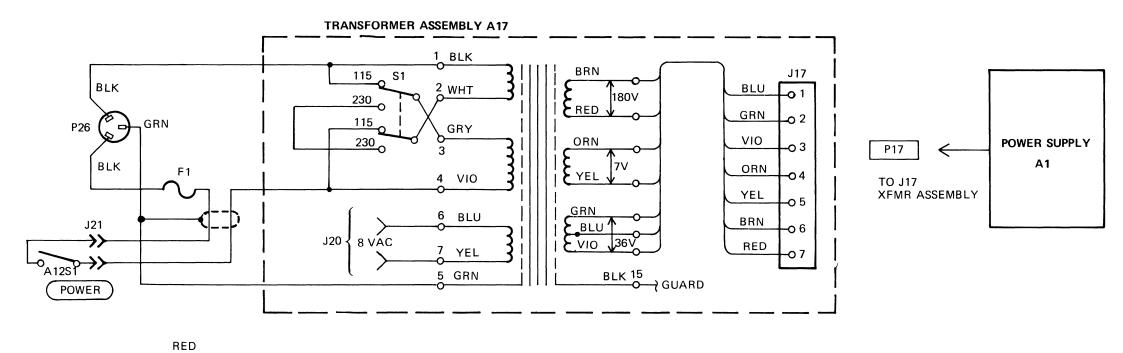

# POWER SUPPLY (A1) Drawing No. 8200A-1001

Voltages from the A17 Transformer assembly are fed to each of three bridge rectifiers. Starting with the regulated +15 volt DC supply, 36 volts AC is applied from the power transformer across the rectifier bridge composed of CR5 through CR8. The positive side of the bridge is fed through R6 and Q3 as the series pass element. It is referenced to the Zener diode CR9. The +15 volt power supply is used as the reference voltage for the other three supplies. Reference for the minus 15 volt supply is developed as a result of the voltage division through R14 and R18 between the plus and minus 15 volt supplies. R21 connects the 5 volt supply back to the 15 volt supply for reference. The 200 volt display supply is connected back from the collector of Q2 to the 15 volt supply; the base of Q2 being connected to the voltage drop between R3 and R4 and is referenced in that manner.

# BUFFER (A4) Drawing No. 8200A-1004

The overall gain of the Buffer is 1 inverted, and the Buffer serves five separate functions: an Input Divider, an Active Filter, Overload Protection, the Buffer Amplifier, and the Logic circuitry.

The Input Divider offers an input impedance of 10,000 meg ohms shunted by less than 130 pf, and in the 10 to 1000 volt ranges offers an input impedance of 10 meg ohms. Monolithis amplifier U1 serves as the active element in the filter. K6 closes to activate the filter, which provides 60 db at 50 hertz and 100 db at 200 hertz and above. CR25 and CR26 serve as protection diodes and rapid overload recovery, while CR23 and CR24 protect the filter amplifier.

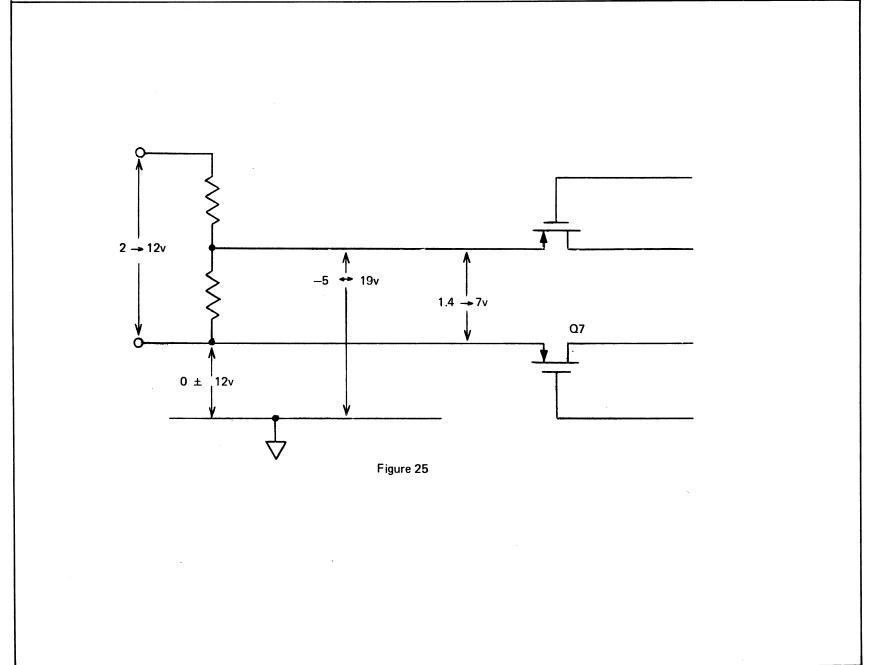

Overload protection has been provided that operates at a 2 volt level as provided by CR1, CR2, Q6, and Q7. They operate with 1.4 volts on the base and .6 volts on the emitter, and serve to keep U2 and the U3, the Buffer Amplifiers, in linear operation. VS1, a neon bulb, holds the input potential below 100 volts and indirectly illuminates the readout portion of the front panel. CR3 and CR4, at the output of the Buffer Amplifier, serve function as a fast feedback for over voltage, preventing saturation in the amplifier. The amplifier itself being a differential input operational amplifier with a total gain of 1 and composed of dual FET U2 and monolithic amplifier U3.

# A-TO-D ANALOG ASSEMBLY (A7) Drawing No. 8200A-1007

Seven separate circuits make up the A-to-D Analog Assembly: the Polarity Detector, A-to-D Amplifier, CCO Modulator, Sample and Hold circuit, Ladder circuit, Display Storage, and +7 volt Reference Supply. The Polarity Circuit consists of three transistors, Q13, Q14, and Q15, which operate the polarity switches consisting of FET's Q10, Q12, and Q16. The Polarity Detector is enabled by the pulse GATE 4 at Q13. GATE 4, consisting of A time, and Measure Mode, is generated in the Logic Control assembly A6. A negative voltage appearing on R15 will cause Q14 to conduct. The line P from the emitter of Q14 will go high, and Q10 and Q16 will conduct. If, in contrast, the voltage on R15 is positive, Q15 will conduct,  $\overline{P}$  from the emitter of Q15 will go high and Q12 will turn ON. The voltage on R15 is opposite in polarity to the input of the instrument due to the inversion in the Buffer. The P and  $\overline{P}$  signals are used in the Display circuit to indicate polarity. If  $\overline{P}$  is high, positive voltage is being fed to the 8200. If P is high, negative voltage is being fed to the 8200.

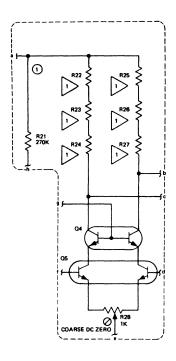

The A-to-D Amplifier consists of a dual FET, U3, and a monolithic amplifier U2. The overall gain of the amplifier is 70, and its normal input is from zero to 1.6 volts. It is connected as a differential input operational amplifier. Offset removal is accomplished with C7 and FET switches Q16 and Q20. During the ZERO time period Q16 and Q20 conduct placing C7 in the output of the A-to-D Amplifier. When the ZERO pulse is completed, Q16 and Q20 open, C7 is effectively placed in series with the amplifier. Q16 functions to short the input of the A-to-D Amplifier, and Q20 functions to connect C7 to a 1 to 69 divider in the A-to-D Amplifier output. In this manner, offset is removed from the A-to-D Amplifier.

ι

Q19 and Q21 provide a fast feedback circuit to prevent the amplifier from saturating. Such precautions are necessary, in that an operational amplifier once saturated generally takes several seconds to recover. Q11, in the input circuit of the Amplifier, is a temperature compensation device.

The CCO modulator, or constant current oscillator modulator, operates to produce current from the emitters of U26 and U30 to operate the constant current oscillator. When the output of the A-to-D Amplifier is above 7 volts, the modulator is caused to supply current. Q26 supplies the high current during large voltage outputs, and the differential pair Q27 and Q28 control Q29 and Q30 to supply current when the output approaches 7 volts. R48 adjusts the activation point of Q27.

Q22, Q23, Q24, and Q25 are connected to gate pulses that appear only during Measure Mode. In the block diagram explanation it was pointed out that Sample and Hold operates only during the Measure Mode. Capacitor C9 stores the remainder in the A time period. No remainder is stored in the D time period.