### **OPERATING MANUAL**

#### **OPERATING MANUAL**

### MODEL 10342B BUS PREPROCESSOR

© COPYRIGHT HEWLETT-PACKARD COMPANY/COLORADO SPRINGS DIVISION 1985 1900 GARDEN OF THE GODS ROAD, COLORADO SPRINGS, COLORADO U.S.A.

ALL RIGHTS RESERVED

Manual Part No. 10342-90901 Microfiche Part No. 10342-90801

**PRINTED: AUGUST 1985**

#### CERTIFICATION

Hewlett-Packard Company certifies that this product met its published specifications at the time of shipment from the factory. Hewlett-Packard further certifies that its calibration measurements are traceable to the United States National Bureau of Standards, to the extent allowed by the Bureau's calibration facility, and to the calibration facilities of other International Standards Organization members.

#### WARRANTY

This Hewlett-Packard product is warranted against defects in material and workmanship for a period of one year from date of shipment. During the warranty period, Hewlett-Packard Company will, at its option, either repair or replace products which prove to be defective.

For warranty service or repair, this product must be returned to a service facility designated by HP. Buyer shall prepay shipping charges to HP and HP shall pay shipping charges to return the product to Buyer. However, Buyer shall pay all shipping charges, duties, and taxes for products returned to HP from another country.

HP warrants that its software and firmware designated by HP for use with an instrument will execute its programming instructions when properly installed on that instrument. HP does not warrant that the operation of the instrument or software, or firmware will be uninterrupted or error free.

#### **LIMITATION OF WARRANTY**

The foregoing warranty shall not apply to defects resulting from improper or inadequate maintenance by Buyer, buyer-supplied software or interfacing, unauthorized modification or misuse, operation outside the environmental specifications for the product, or improper site preparation or maintenance.

NO OTHER WARRANTY IS EXPRESSED OR IMPLIED. HP SPECIFICALLY DISCLAIMS THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

#### **EXCLUSIVE REMEDIES**

THE REMEDIES PROVIDED HEREIN ARE BUYER'S SOLE AND EXCLUSIVE REMEDIES. HP SHALL NOT BE LIABLE FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, WHETHER BASED ON CONTRACT, TORT, OR ANY OTHER LEGAL THEORY.

#### **ASSISTANCE**

Product maintenance agreements and other customer assistance agreements are available for Hewlett-Packard products.

For any assistance, contact your nearest Hewlett-Packard Sales and Service Office. Addresses are provided at the back of this manual.

### 10342B Operating Manual

### **Table of Contents**

|                                    | 4 4   |

|------------------------------------|-------|

| Introduction                       | . !-! |

| Manual Purpose and Organization    | . 1-1 |

| Preprocessor Description           | . 1-1 |

| HP-IB                              | . 1-1 |

| RS-232-C/CCITT V.24                | . 1-2 |

| RS-449                             | . 1-2 |

| Operating Characteristics          | . 1-2 |

| Equipment Supplied                 | 1-4   |

| Minimum Equipment Required         | 1_4   |

| William Equipment required         |       |

| Chapter 2. Hardware Information    |       |

| Introduction                       | . 2-1 |

| Initial Inspection                 | . 2-1 |

| Power Requirements                 | 2-1   |

| Operator Maintenance               | 2-1   |

| Testing and Troubleshooting        | 2-1   |

| Testing and Troubleshooting        | 2 1   |

| Probe Interface Overlay            | 2-1   |

| Replaceable Parts                  | . 2-2 |

| Schematics                         | . 2-2 |

| Serial Input Circuits              | . 2-2 |

| Serial Timing Connections          | . 2-2 |

| Chapter 3. Software Information    |       |

| Introduction                       | . 3-1 |

| Copying Files                      | . 3-1 |

| Copyring Tilles                    |       |

| Chapter 4. HP-IB Bus Preprocessing |       |

| Introduction                       | . 4-1 |

| Preprocessor Function              | . 4-1 |

| System Set-up                      | . 4-1 |

| Logic Analyzer                     | . 4-1 |

| Bus Preprocessor                   | . 4-2 |

| Probe Interface                    | . 4-3 |

| System Operation                   | 4-3   |

| Signal Connections                 | 4-4   |

| Clocks                             | Δ.    |

| Obstace (OTAT) times               |       |

| Status (STAT) Lines                | . +-: |

| Control (CNTRL) Lines              | , 4°. |

| Address (ADDR)                     | . 4-0 |

| Timing Reconfiguration Example     | . 4-6 |

### Chapter 5. RS-232-C/V.24 Bus Preprocessing

| Introduction                             | . 5-1      |

|------------------------------------------|------------|

| Preprocessor Function                    |            |

| System Set-up                            | . 5-1      |

| Logic Analyzer                           |            |

| Bus Preprocessor                         |            |

| Probe Interface                          |            |

| System Operation                         |            |

| Signal Connections                       |            |

| Clock                                    |            |

| Data                                     |            |

| Status Byte                              |            |

| Timing Signals                           |            |

| Address (ADDR)                           |            |

| Mnemonics                                |            |

| Sync Characters                          |            |

| Block Check Characters                   | . 5-6      |

| block Check Characters                   | . 5-9      |

|                                          |            |

| Chapter 6. RS-449 Bus Preprocessing      |            |

| Onapter of 110-149 bus i reprocessing    |            |

| Introduction                             | <b>.</b> . |

| Preprocessor Function                    | . 6-1      |

| System Set-up                            |            |

| Logic Analyzer                           |            |

|                                          |            |

| Bus Preprocessor                         |            |

| Probe Interface                          |            |

| System Operation                         |            |

| Signal Connections                       |            |

| Clock                                    |            |

| Data                                     |            |

| Status Byte                              |            |

| Timing Signals                           |            |

| Address (ADDR)                           |            |

| Sync Characters                          | . 6-7      |

| Block Check Characters                   | 6-8        |

|                                          |            |

|                                          |            |

| Appendix A. HP-IB Overview               |            |

|                                          |            |

| Introduction                             |            |

| The HP-IB                                |            |

| Interface Management Lines               |            |

| Handshake Lines                          | A-2        |

|                                          |            |

|                                          |            |

| Appendix B. Serial Interface Comparisons |            |

|                                          |            |

| Introduction                             | R_1        |

### Appendix C. RS-232-C/CCITT V.24 Overview Appendix D. RS-449 and RS-422 Overview The RS-449/RS-422..... D-1 List of Illustrations **Figure Page** 2-1. Serial Input Circuitry ...... 2-3 4-2. Timing Jumper Reconfiguration..... 4-6 6-1. RS-449 Timing Connector Locations.......6-2 6-3. 7-Bit ASCII Sync Sequence ...... 6-8

### **List of Tables**

| Table            | e I                                                                  | Page       |

|------------------|----------------------------------------------------------------------|------------|

| 1-1.             | Operating Characteristics                                            | 1-2        |

| 2-1.             | Replaceable Parts                                                    | 2-2        |

| 3-1.             | Software File List                                                   | 3-1        |

| 4-1.<br>4-2.     | Logic Analyzer to HP-IB Signal ConnectionsStatus Lines               | 4-4<br>4-5 |

| 5-2.             | Logic Analyzer to RS-232-C Signal Connections                        | 5-7        |

| 6-1.<br>6-2.     | Logic Analyzer to RS-449 Signal Connections Standard Sync Characters | 6-5<br>6-8 |

| B-2.             | Serial Interface Standards Comparison                                | B-1        |

| C-1.<br>C-2.     | Interchange Circuits for RS-232-C and CCITT V.24 Equivalents         | C-2<br>C-3 |

| D <sub>-</sub> 1 | Interchange Circuits for RS-449                                      | D-3        |

## Chapter 1 GENERAL INFORMATION

#### INTRODUCTION

The HP 10342B Bus Preprocessor, with the HP 10269A or HP 10269B General Purpose Probe Interface, provides an easy connection between the HP 1630A/D/G or HP 1631A/D Logic Analyzers and three popular data buses, HP-IB (Hewlett-Packard's implementation of IEEE 488-1978), RS-232-C/CCITT V.24, or RS-449. Software supplied with the HP 10342B provides inverse assembly of activity on the buses and configurations for the logic analyzers.

## MANUAL PURPOSE AND ORGANIZATION

The purpose of this manual is to provide information for using the HP 10342B. The extent to which a bus can be analyzed is generally dependent on the model of logic analyzer used. Any information provided in this manual concerning using the logic analyzers is supplementary to that provided in the analyzer operation and programming manual.

Also, this manual does not contain the complete standards for the three buses covered. The appendices contain abbreviated versions of the standards for the buses. Additional information should be obtained from the appropriate standards organization for each bus.

This manual is organized into several chapters.

CHAPTER 1 covers general information such as product description and accessories.

CHAPTER 2 covers general hardware information, such as inspection, power requirements, maintenance, and troubleshooting.

CHAPTER 3 covers general information about the software supplied.

CHAPTER 4 covers use of the HP 10342B for preprocessing the HP-IB. It includes installation and other information specific to using the HP 10342B on this bus.

CHAPTER 5 covers use of the HP 10342B for preprocessing the RS-232-C/CCITT V.24 bus. It includes installation and other information specific to using the HP 10342B on this bus.

CHAPTER 6 covers use of the HP 10342B for preprocessing the RS-449 bus. It includes installation and other information specific to using the HP 10342B on this bus.

APPENDICES provide some of the basic specifications of the three buses handled by the HP 10342B.

#### PREPROCESSOR DESCRIPTION

The HP 10342B Bus Preprocessor combines the capability for analysis of three popular buses into one instrument. The HP 10342B itself consists of an interface module which plugs into the HP 10269A/B General Purpose Probe Interface. Three connectors on the front panel of the interface module accept cables which connect with the bus being tested. Switches on the front panel are set up to match the parameters of the signals on the bus

The inverse assembler and configuration files loaded into the logic analyzer from disc set up the basic analysis parameters. The operator can further set up the analyzer to make and process the measurements in other ways. The exact measurement capabilities depend on the analyzer being used.

#### • HP-IB

The HP-IB input to the HP 10342B provides one HP-IB defined load to the bus being monitored. The data and handshake

lines of the bus are buffered and run directly to the probe connectors of the HP 10269A/B.

#### RS-232-C/CCITT V.24

The RS-232-C input to the HP 10342B provides one RS-232-C defined load on the bus being monitored. The lines of the bus under test are buffered and applied to circuitry that takes the serial data stream and converts it back into original data and status. It monitors five handshake lines and their status is stored with each character received. Four switches set up the protocol and data rates. A microprocessor controls the functions in the preprocessor.

#### • RS-449

The RS-449 input to the HP 10342B provides one RS-449 defined load on the bus being monitored. The lines of the bus are buffered and ORed with the buffered lines from the RS-232-C connector. From that point all the preprocessing in the HP 10342B is the same. RS-449 inverse assembler and configuration files are provided for the logic analyzer however.

#### **OPERATING CHARACTERISTICS**

Table 1-1 gives operating characteristics of the HP 10342B.

Table 1-2. Operating Characteristics

#### RS-232C (V.24)/449

#### **ASYNCHRONOUS**

Data Transfer Rates: 50, 75, 110, 134.5, 150, 300, 600, 1200, 1800, 2000, 2400, 3600, 4800,

(bits/second) 7200, 9600 or 19 200

Parity: Odd, even, or none

Bits per character: 6-bit transcode

7-bit ASCII 8-bit ASCII 8-bit EBCDIC

Stop bits per character: 1, 1.5, 2

#### **SYNCHRONOUS**

**Data transfer rate:** To 72k bits/second **Format:** Bit-oriented protocols (BOP)

Synchronous data link control (SDLC) High-level data link control (HDLC)

X.25 packet mode

Standard network access protocol (SNAP) Hewlett-Packard data link control (HPDLC)

Burroughs data link control (BDLC)

Advanced data communication control procedure (ADCCP)

Character-oriented protocols (COP)

Binary synchronous communication (BSC)

Digital data communications message protocol (DDCMP)

Selectable: 6, 7, or 8 bits per character

Transmit clock source: Data terminal equipment (DTE) or data circuit-terminating equipment

(DCE). Internally selectable on pc-board.

Table 1-2. Operating Characteristics (cont).

|                     | , a.s.e . 2. • pe. a. | 9                  | - (  |  |

|---------------------|-----------------------|--------------------|------|--|

| DATA/HANDSHAKE      | =                     |                    |      |  |

| RS-232C/(V.24)      |                       |                    |      |  |

|                     |                       | LABELS             | EIA  |  |

| Data Lines:         | Transmit data         | (TX)               | (BA) |  |

|                     | Receive data          | (RX)               | (BB) |  |

| Handshake Lines:    | Request to send       | (RTS) <sup>1</sup> | (CA) |  |

|                     | Clear to send         | (CTS) <sup>1</sup> | (CB) |  |

|                     | Data set ready        | (DSR) <sup>1</sup> | (CC) |  |

|                     | Data terminal ready   | (DTR) <sup>1</sup> | (CD) |  |

|                     | Carrier detect        | (CD) <sup>2</sup>  | (CF) |  |

| RS-449              |                       |                    |      |  |

|                     |                       | LABELS             |      |  |

| Data Lines:         | Send data             | (SD)               |      |  |

|                     | Receive data          | (RD)               |      |  |

| Handshake Lines:    | Request to send       | (RS) <sup>1</sup>  |      |  |

|                     | Clear to send         | (CS) <sup>1</sup>  |      |  |

|                     | Data mode             | (DM) <sup>1</sup>  |      |  |

|                     | Terminal ready        | (TR) <sup>1</sup>  |      |  |

|                     | Receive ready         | (RR) <sup>2</sup>  |      |  |

| HP-IB               |                       |                    |      |  |

| Data: Data in/out ( | 1 through 8)          |                    |      |  |

|                     | ·                     | LABELS             |      |  |

| Management:         | Interface clear       | (IFC)              |      |  |

| • •                 | Attention             | (ATŃ)              |      |  |

|                     | Service request       | (SRQ)              |      |  |

|                     | Remote enable         | (REN)              |      |  |

|                     | End or identify       | (EOI)              |      |  |

| Handshake:          | Data valid            | (DAV) <sup>3</sup> |      |  |

|                     | Not ready for data    | (NRFD)             |      |  |

|                     | Not data accepted     | (NDAC)             |      |  |

|                     | •                     | , ,                |      |  |

NOTES: 1. Synchronous 2. Asynchronous 3. Used as Data Clock

#### GENERAL

Inputs: Three provided: RS-232C/(V.24), RS-449, and HP-IB.

Outputs: Three mini-probe sockets can be connected internally to any of the input lines via

jumper wires.

Signal line loading: RS-232C/V.24 and RS-449, 1 standard load; HP-IB, 1 LS load; load is at

the end of the supplied ribbon cables.

Power requirement: +5 V at 0.65A

#### **ENVIRONMENTAL**

Temperature: Operating, 0° to 55°C (+32° to +131°F);

Non-operating, -40° to +75° C (-40° to +167° F).

Altitude: Operating, up to 4600 m (15 000 ft).

Non-operating, up to 15 300 m (50 000 ft).

Humidity: 90% non-condensing. Avoid sudden, extreme temperature change that could

cause condensation within the instrument.

#### **EQUIPMENT SUPPLIED**

Equipment supplied with the HP 10342B consists of the following:

Preprocessor Module

One .75 meter (2.5 ft) HP-IB ribbon cable

One .75 meter (2.5 ft) RS-232C/V.24 ribbon

cable

One .75 meter (2.5 ft) RS-449 ribbon cable

One 16-pin jumper cable

20 jumper wires

HP 10269B Overlay

Operating Manual

#### **MINIMUM EQUIPMENT REQUIRED**

The following is a list of the minimum equipment required in a system using the HP 10342B Bus preprocessor.

HP 1630A/D/G or HP 1631A/D HP 10269A or HP 10269B HP 9121D/S or HP 9122D/S HP 10342B HP-IB cables for peripherals

## Chapter 2 HARDWARE INFORMATION

#### INTRODUCTION

This chapter contains information about the hardware supplied with the HP 10342B Bus Preprocessor. Inspection, power requirements, maintenance, and set-up of the logic analyzer system are some subjects covered.

#### **INITIAL INSPECTION**

Inspect the shipping container for damage. If the shipping container or cushioning material is damaged, it should be kept until the contents of the shipment have been inspected mechanically and electrically. If the contents are incomplete, if there is mechanical damage or defect, or if the instrument does not operate, notify your nearest Hewlett-Packard Sales and Service Office. If the shipping container is damaged, or the cushioning materials show signs of stress, notify the carrier as well as the Hewlett-Packard office. Keep the shipping materials for inspection by the carrier.

#### **POWER REQUIREMENTS**

The HP 10342B draws power, +5V, from the rear-panel power BNC of the HP 1630/31 Logic Analyzer. It draws approximately .65 amps. A cable is provided in the accessories for the HP 10269A/B.

#### **OPERATOR MAINTENANCE**

The only instrument maintenance an operator needs to perform is to keep the instrument clean. Caution must be used in the selection of cleaning agents. Use a mild soap and water solution. Harsh soaps and solvents could damage the painted finish.

CAUTION

Use care when cleaning the panel of the instrument. Soap and solvents could damage parts or contaminate circuitry below. It is better to apply cleaning solutions to a cloth, then wipe the panel, than to wet the surface directly.

CAUTION

Do not use chemical cleaning agents or abrasive cleaners that could damage plastic parts. Recommended cleaning agents are isopropyl alcohol or a 1% solution of mild detergent in water.

#### **TESTING AND TROUBLESHOOTING**

There are no established field testing procedures for the HP 10342B. The HP 10342B is on the Blue Stripe board exchange program. If your instrument is inoperative contact the nearest Hewlett-Packard Sales and Service office for assistance.

The circuitry is fairly simple. Standard off-theshelf parts are used. If you must effect a repair, standard troubleshooting techniques should be sufficient to isolate and correct a problem.

#### PROBE INTERFACE OVERLAY

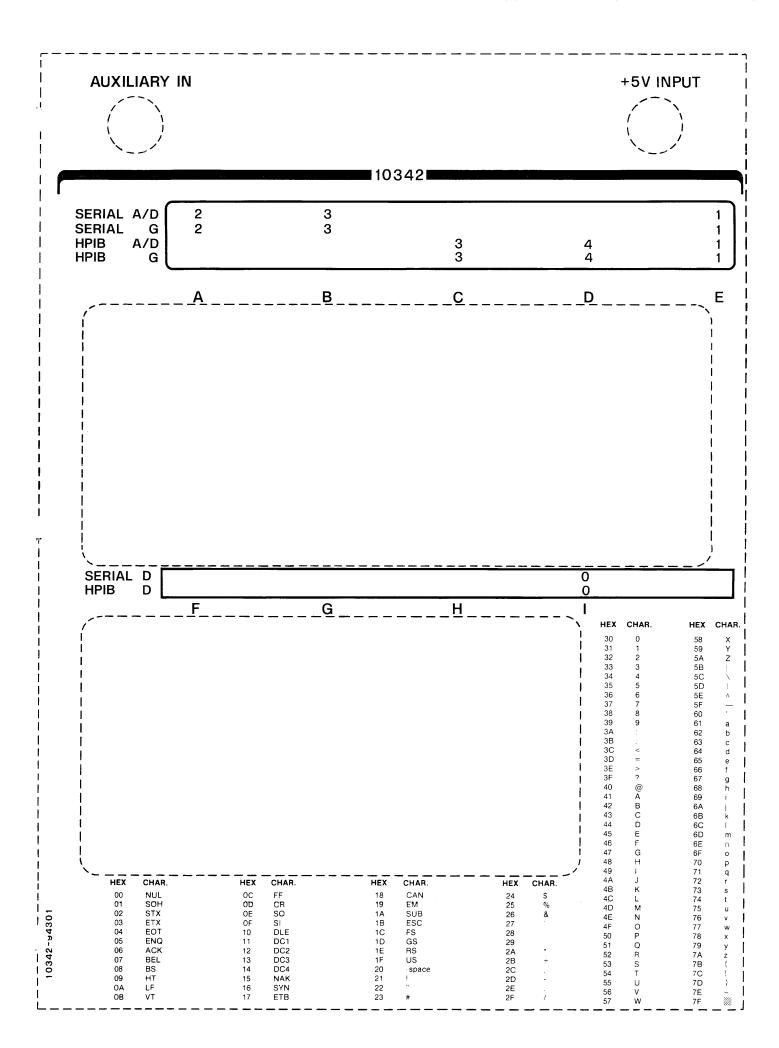

On page 2-5 is a reproduction of the HP 10269B overlay. It is full size so it can be reproduced to make a replacement.

#### REPLACEABLE PARTS

Since the HP 10342B is on the Blue Stripe board exchange program the only replaceable parts are the major parts and cabling.

Table 2-1. Replaceable Parts.

| QTY | DESCRIPTION             | PART NUMBER |

|-----|-------------------------|-------------|

| 1   | Software Disc           | 10342-13012 |

| 1   | HP-IB Cable             | 10342-61603 |

| 1   | RS-232-C Cable          | 10342-61601 |

| 1   | RS-449 Cable            | 10342-61602 |

| 1   | Probe Interface Overlay | 10342-94301 |

| 1   | 16-pin Jumper Cable     | 10342-61604 |

| 20  | Jumper wires            | 8120-4665   |

| 1   | PC Board                | 10342-66501 |

| 1   | Top cover               | 10342-04104 |

| 1   | Bottom plate            | 10342-04102 |

| 12  | 4-40 Flathead screw     | 2200-0512   |

| 2   | Captive screw           | 1390-0393   |

| 2   | Retaining ring          | 0510-0952   |

#### **SCHEMATICS**

The following information is supplied to help the user understand how the HP 10342B impacts timing measurements of serial bus signals and is not intended to be used to troubleshoot an inoperative instrument.

#### **Serial Input Circuits**

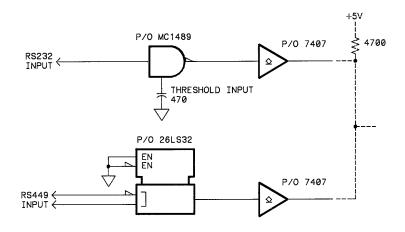

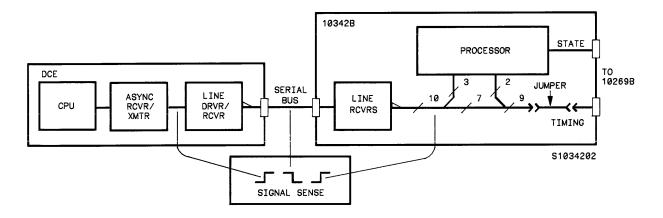

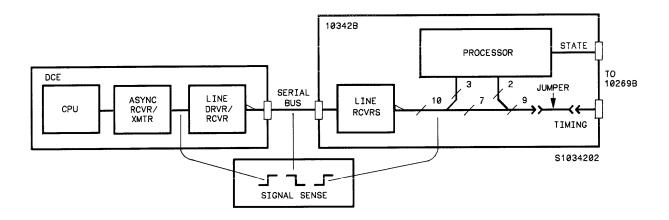

The input circuitry for one signal from each of the RS-232 and RS-449 buses is shown in figure 2-1. The inputs for the other signals are identical. Both inputs are buffered and supplied to open-collector drivers. The output of an RS-232 driver is wire-ored with the output of the corresponding RS-449 driver and the line is pulled up to +5V.

The RS-232 line receiver has a threshold connection which is connected to ground through 470pF. This supplies noise immunity for RS-232 signals.

Inversion in the RS-232 circuit is done by using an inverting line receiver. In the RS-449 circuit, "inversion" is done by reversing the connections of the two lines for each signal.

#### **Serial Timing Connections**

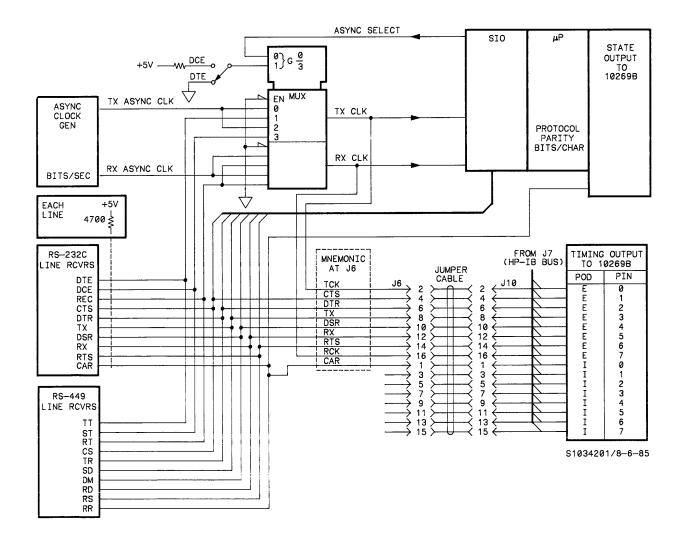

An overall view of the timing connections is shown in figure 2-2. The RS-232 and RS-449 input circuitry (previously covered) is represented by their respective blocks.

The three synchronous clocks from the buses are multiplexed with the two asynchronous clocks generated in the HP 10342B to provide one transmit and one receive clock. Clock selection depends on the internal and front-panel switch settings. The two selected clocks are used by the SIO and also sent to J6 where they join the buffered and inverted serial signals for connection to the logic analyzer timing inputs.

Figure 2-1. Serial Input Circuitry.

Figure 2-2. Serial Timing Circuitry.

## Chapter 3 SOFTWARE INFORMATION

#### INTRODUCTION

This chapter contains information about the software supplied with the HP 10342B Bus Preprocessor. There are three types of files on the flexible disc supplied with the HP 10342B. There is a disc copy program for use in duplicating the disc for archive purposes. There are inverse assembly files for set-up of

the logic analyzer and disassembly of the bus activity. There are also configuration files for setting up timing functions of the logic analyzer.

Table 3-1 is a composite list of the files in the software provided with the HP 10342B.

| Filename | Type*  | Date     | Time  | File Description*          |

|----------|--------|----------|-------|----------------------------|

| COPYFILE | prog   | XX/XX/XX | XX:XX | Disk File Copy Utility     |

| IHPIB    | config |          |       | HPIB CONFIG FOR 163XAD     |

| IHPIB    | invasm |          |       | HPIB INVERSE ASSEM 2519    |

| IHPIBG   | config |          |       | HPIB CONFIG FOR 1630G      |

| IRS232C  | config | SEE NO   | TE**  | RS232C CONFIG FOR 163XAD   |

| IRS232C  | invasm | 1        |       | RS232C INVERSE ASSEM. 2519 |

| IRS232G  | config |          |       | RS232C CONFIG FOR 1630G    |

| IRS449   | config |          |       | RS 449 CONFIG FOR 163XAD   |

| IRS449   | invasm | <b>↓</b> |       | RS 449 INVERSE ASSEM. 2519 |

| IRS449G  | config | XX/XX/XX | XX:XX | RS 449 CONFIG FOR 1630G    |

Table 3-1. Software File List.

#### NOTES:

- \* Configuration files for the instrument not being loaded will show up in the "Type" column as being unknown. For example when loading an HP 1630A/D or HP 1631A/D the HP 1630G files will be unknown and there will be no file description. They cannot be loaded.

- \*\* Date and Time information may vary depending on the version of the software on the disc.

#### **COPYING FILES**

As soon as possible after receiving your instrument you should copy your disc so that you have a back-up copy. Use the copy and keep the original as a back-up.

Copying files is done with the COPYFILE utility program which provides the user with a method of copying HP 1630/31 executable

programs, configuration files, and inverse assemblers from one disc to another.

COPYFILE is an extension of the Storage Operations capabilities of the HP 1630/31 which are limited to copying only non executable programs. An example of a non-executable would be a timing file.

To use COPYFILE, load it using the same loading procedure described in the logic analyzer operating manual.

Once the program starts, the logic analyzer display will ask for: copy FROM file name, file TYPE, bus address and unit number. When these have been specified, press INSERT to load the file to be copied. When the copy FROM file has been loaded, the logic analyzer

will display all the same information in the copy TO fields as a default. The filename, bus address, and unit number can be respecified if desired, however, the filetype must remain the same as the file being copied. Press INSERT to write the file.

To exit the COPYFILE program, move the cursor to the EXIT field and press either the NEXT [] or PREV [] key.

# Chapter 4 HP-IB BUS PREPROCESSING

#### INTRODUCTION

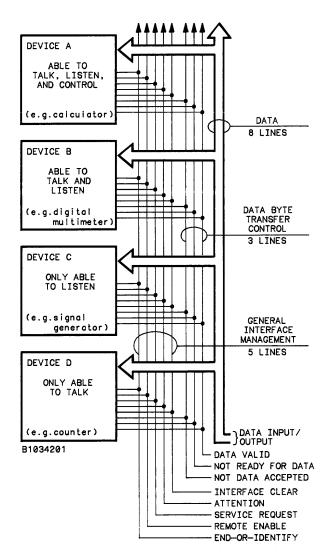

The HP-IB is the Hewlett-Packard implementation of IEEE Standard 488-1978. The HP-IB is a parallel bus with eight data lines, three handshake lines and five control lines. A brief overview of HP-IB is given in appendix A.

#### PREPROCESSOR FUNCTION

The function of the HP 10342B when monitoring the HP-IB is to connect onto the bus, buffer the lines, provide easy connection to the logic analyzer, and provide set-up of logic analyzer menus and inverse assembly of captured data. The HP 10342B can monitor the state of all the signal lines of the HP-IB. Depending on the logic analyzer used, either all 16 lines (using an HP 1630D or HP 1631D) or eight lines (using the HP 1630A, HP 1630G, or HP 1631A) can be monitored for timing information.

The HP 10342B provides a mass-connect feature for connecting the HP-IB lines up to timing channels or individual connections can be made with jumper wires provided. Timing channels are connected directly to the HP-IB without buffering.

Additionally, any HP-IB line can be connected, unbuffered, to one of the three HP 10342B front panel outputs provided. These can be used for connection to an oscilloscope or one of the analog channels or trigger of an HP 1631A/D.

#### SYSTEM SET-UP

The minimum equipment necessary to use the HP 10342B Bus Preprocessor is as follows:

Logic Analyzer: HP 1630A/D/G\* or HP 1631A/D\*

\* with HP 1630/31A or HP 1630G only 8 timing channels are available

Probe Interface: HP 10269A\* or HP 10269B

\* with the HP 10269A only 8 timing channels are available

Disc Drive: HP 9121D/S or HP 9122D/S

HP-IB cables for peripherals HP 10342B Bus Preprocessor

Use the following step-by-step procedure to set up the HP-IB Bus Preprocessing system.

#### Logic Analyzer

SET UP SYSTEM

Set up your logic analyzer system using procedures in your equipment operators manuals. Set-up will depend on the equipment and peripherals you are using.

#### **Bus Preprocessor**

The HP 10342B comes from the factory set up for processing HP-IB, therefore some of the following instructions may be redundant if the HP 10342B is being used for the first time.

### CONNECT TIMING JUMPER

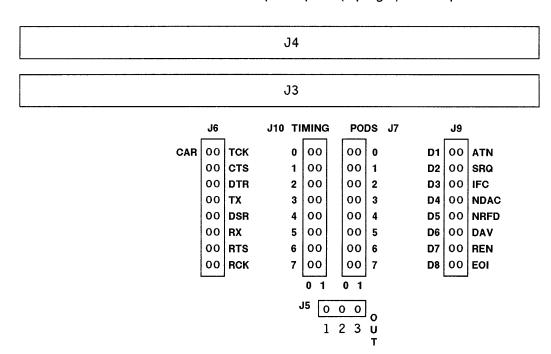

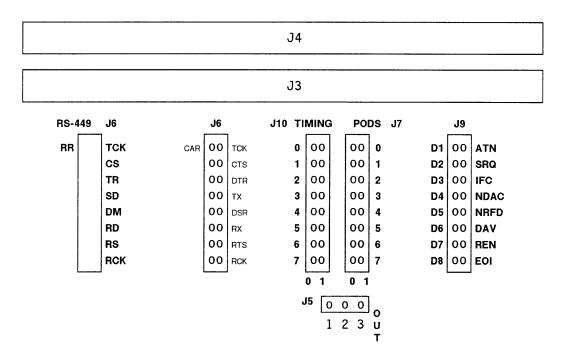

On the HP 10342B, connect the ribbon jumper cable from J7 to J9. All 16 possible timing channels are connected when the jumper cable is used. See figure 4-1.

If you use the single jumper wires to connect the timing signals be sure to connect them to corresponding pins of J7 and J9 or the data captured will not match the HP 163X setup provided on disc. You would then need to change the HP 163X [Timing] Format Specification menu to match your hook-up.

One reason to make changes in the timing connections is to put different bus lines onto timing inputs 0-3 for edge and glitch triggering. The preprocessor is set up to have ATN, SRQ, IFC, and NDAC on these lines. For further information, see TIMING RECONFIGURATION on page 4-6.

### CONNECT FRONT PANEL OUTPUTS

If you want any data or control lines connected to the front panel outputs, use the small jumper wires to connect pins of J10 to pins of J5. See figure 4-1. When using the mass-connect jumper cable the signals at J10 correspond to the mnemonics at J9.

Example: To connect ATN to front panel Output 1, connect a jumper between J10 pod 1 pin 0 (top right) and J5 pin 1.

Figure 4-1. HP-IB Timing Connector Locations.

### INSTALL PREPROCESSOR

Once all the connections are made, place the HP 10342B at the bottom of the HP 10269 and connect the two 60-pin cables to the connectors on the HP 10342B. Fit the HP 10342B into the bottom of the HP 10269 and fasten them together with the two captive screws.

### FRONT PANEL SWITCHES

The front panel switches are used for serial data preprocessing and have no function in preprocessing the HP-IB.

#### **Probe Interface**

Though either an HP 10269B or HP 10269A can be used with the HP 10342B, The HP 10269A does not support the additional 8 timing channels of the HP 1630D.

### POD CONNECTOR OVERLAY

Lay the HP 10269B overlay over the pod connectors. If you are using an HP 10269A the overlay will be too large to fit well. The overlay shows where pods connect for various logic analyzers and bus preprocessing and gives other useful information.

#### **CONNECT PODS**

Connect the logic analyzer pods to the connectors on the HP 10269. If you are using an HP 10269B follow the overlay. For an HP 163XD, POD 3 goes in pod connector C, POD 4 into D, POD 1 into E, and POD 0 into I. For an HP 163XA/G there is no POD 0. If you are using an HP 10269A the connections are the same except there is no pod connector I.

If you are going to be using the HP 10342B on both HP-IB and RS-232-C or RS-449 buses, you can connect logic analyzer POD 2 to pod connector A. You can then switch to serial processing by moving POD 3 to connector B and loading the serial inverse assembler and configuration files.

#### **CONNECT POWER**

Connect the BNC to BNC cable supplied with the HP 10269 between the +5V INPUT (ACCESSORY POWER) of the HP 10269 and the +5V (ACCESSORY POWER) output of the logic analyzer.

### CONNECT HP-IB CABLE

Connect the HP-IB ribbon cable between the HP-IB bus to be monitored and the HP-IB connector on the HP 10342B.

#### **System Operation**

Be sure all the addresses are set on the peripherals before you apply power since most address switch settings are read on power-up.

| APPLY POWER | Turn on power for all equipment involved. The logic analyzer comes |

|-------------|--------------------------------------------------------------------|

|             | up in the [Configuration] menu of the System Specification. Press  |

|             | the PREV[] key to get the [Storage Operations] menu.               |

### CHECK FOR DISC

Press INSERT to check for the disc drive and display the disc file directory.

LOAD INVASM ROLL the list up to point to the desired file to load. The inverse

assembler must be loaded first, so load "IHPIB invasm" by pointing to it selecting [Load] for an Operation and pression (NOSE).

to it, selecting [Load] for an Operation, and pressing INSERT.

LOAD CONFIG Next, load the configuration file "IHPIB config" or "IHPIBG config"

depending on your logic analyzer. The instrument will not load the

wrong one.

RUN Press RUN. As soon as a clock is available on the bus the logic

analyzer will begin to accumulate data.

You may modify the logic analyzer menus to suit the measurement you need to make. Consult your logic analyzer operating manual

for further information.

#### SIGNAL CONNECTIONS

**NRFD**

С

7

The HP 10342B monitors all HP-IB lines for state information. Eight or 16 lines (depending on the logic analyzer or HP 10269) can be monitored for timing information. Following is a list of the HP-IB signals and where they are input to the analyzer.

|                       |                        | OT 1 TE |          |                        |     |         |  |

|-----------------------|------------------------|---------|----------|------------------------|-----|---------|--|

| LID ID                | 115.44                 | STATE   | 110 1001 | TIMING                 |     | 1       |  |

| HP-IB                 | HP 10269B <sup>1</sup> |         | HP 163X  | HP 10269B <sup>1</sup> |     | HP 163X |  |

| LINE                  | CONN                   | PIN     | POD      | CONN                   | PIN | POD     |  |

| DAV                   | D                      | J CLK   | 4        |                        |     |         |  |

|                       |                        |         |          |                        |     |         |  |

| DIO1                  | D                      | 0       |          | i                      | 0   | 0       |  |

| DIO2                  | D                      | 1       |          | I                      | 1   |         |  |

| DIO3                  | D                      | 2       |          | 1                      | 2   |         |  |

| DIO4                  | D                      | 3       |          | ŀ                      | 3   | HP 163X |  |

|                       |                        |         |          | •                      |     | ONLY    |  |

| DIO5                  | D                      | 4       |          | I                      | 4   | 1       |  |

| DIO6                  | D                      | 5       |          | 1                      | 5   |         |  |

| DIO7                  | D                      | 6       | . ↓      | ı                      | 6   | 1       |  |

| DIO8                  | D                      | 7       | 4        | ı                      | 7   | ď       |  |

| PAR POLL <sup>2</sup> | С                      | K CLK   | 3        |                        |     |         |  |

|                       |                        |         |          |                        |     |         |  |

| ATN                   | С                      | 0       |          | Ε                      | 0   | 1       |  |

| EOI                   | С                      | 1       |          | E                      | 7   |         |  |

| REN                   | С                      | 2       |          | Е                      | 6   |         |  |

| IFC                   | С                      | 3       |          | E                      | 2   |         |  |

| SBO                   | 0                      | 4       |          | -                      |     |         |  |

| SRQ                   | С                      | 4       |          | E                      | 1   |         |  |

| NDAC                  | C                      | 5       |          | E                      | 3   |         |  |

| DAV                   | C                      | 6       | ↓        | E                      | 5   | 1       |  |

Table 4-1. Logic Analyzer to HP-IB Signal Connections.

Ε

<sup>1.</sup> HP 10269A connections are the same except there is no pod connector I (POD 0).

<sup>2.</sup> Parallel Poll is available but not activated. See CLOCKS in following text.

#### Clocks

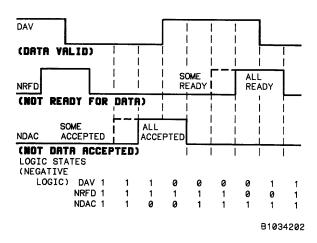

Two clocks are provided to the logic analyzer. These clocks can be ORed to clock data.

DAV

DAV, Data Valid, is brought out at HP 10269 pod connector D. Logic analyzer POD 4 is connected there, which provides DAV as the J Clock. The logic analyzer clocks data on the negative edge of the J Clock.

PARALLEL POLL The Parallel Poll clock is brought out at HP 10269 pod connector C. This is the K Clock at logic analyzer POD 3. The PAR POLL clock is ANDed from the EOI and ATN lines of the HP-IB.

The IEEE Standard 488 defines the Parallel Poll to require the EOI and ATN lines to be true for  $2\mu$ s to be valid. This timing function is not implemented in the HP 10342B.

The configuration file on the disc does not automatically set up the logic analyzer to clock data on parallel polls. To clock data using the ANDed function of EOI and ATN go to the [ State ] Format Specification menu of the logic analyzer and use the CURSOR and NEXT[ ] keys to put a  $\downarrow$  symbol under the K in the ORed Clock field. Remember that only data clocked after the  $2\mu$ s specification is a valid parallel poll.

#### Status (STAT) Lines

The State Listing monitors the HP-IB interface management (ATN, EOI, REN, IFC, and SRQ) and handshake (NDAC, DAV, and NRFD) lines under the Status label. Only the interface management lines are used in the inverse assembler. All of the lines are displayed in the [State] Waveform Diagram. Table 4-2 shows which HP-IB line corresponds to which Status line.

STATUS LINE **HP-IB LINE HP-IB LINE** STATUS LINE STAT 4 SRQ STAT 0 ATN NDAC STAT 1 EOI STAT 5 STAT 6 DAV STAT 2 REN **IFC** STAT 7 NRFD STAT 3

Table 4-2. Status Lines.

#### Control (CNTRL) Lines

The CNTRL lines are the HP-IB ATN and EOI lines and are the same as the first two STAT lines. They are displayed in the [State] Listing in their user base format.

#### ADDRESS (ADDR)

There is an Address (ADDR) label set up in the [State] Format Specification with one bit from an unused pod assigned to the label. This label is necessary for operation of the logic analyzer but not for use with the HP 10342B. If the ADDR label appears on screen you can go to the [State] List menu and move it off the screen using the SHIFT and ROLL keys. This is done by the configuration file when the software is loaded.

#### TIMING RECONFIGURATION EXAMPLE

The HP 10342B is factory configured to put ATN, SRQ, IFC, and NDAC on the edge-sensitive channels (0-3) of the timing pod. This is done with the ribbon jumper cable of the HP 10342B and the [Timing] Format Specification menu of the logic analyzer, as set up by the software supplied. Connection of different lines to the edge sensitive timing inputs requires connecting the timing channels with the single jumper wires provided and reconfiguring the menu.

The following example shows how to put NDAC, NRFD, DAV, and EOI onto the edge/glitch timing lines of a logic analyzer with eight timing channels, an HP 1630A, HP 1630G, or HP 1631A. If an HP 1630D or HP 1631D is being used, 16 timing channels with 8 edge-sensitive inputs are available. The method of set-up is the same. The drawing, part of figure 4-1, shows the HP-IB area for jumper connections on the HP 10342B. The accompanying table gives the individual jumper connections to be made.

| TI | MING        | à | PO  | DS | J7 |    | J9 |      |

|----|-------------|---|-----|----|----|----|----|------|

| 0  | 00          |   | OØ  | 0  |    | D1 | 00 | ATN  |

| 1  | 00          |   | OØ  | 1  |    | D2 | 00 | SRQ  |

| 2  | 00          |   | O₩  | 2  |    | D3 | 00 | IFC  |

| 3  | 00          |   | OØ  | 3  |    | D4 | OØ | NDAC |

| 4  | 00          |   | 00  | 4  |    | D5 | OØ | NRFD |

| 5  | 00          |   | 00  | 5  |    | D6 | OΜ | DAV  |

| 6  | 00          |   | 00  | 6  |    | D7 | 00 | REN  |

| 7  | 00          |   | 00  | 7  |    | D8 | ОØ | EOI  |

|    | 0 1         |   | 0 1 | i  |    | 1  |    | l    |

| ٠  | )5 <u>C</u> |   | 2 3 | 0  |    |    |    |      |

| CONNECT JUMPER      |       |  |  |  |  |

|---------------------|-------|--|--|--|--|

| FROM J7<br>POD1 PIN | TO J9 |  |  |  |  |

| 0                   | NDAC  |  |  |  |  |

| 1                   | NRFD  |  |  |  |  |

| 2                   | DAV   |  |  |  |  |

| 3                   | EOI   |  |  |  |  |

| 4                   | ATN   |  |  |  |  |

| 5                   | SRQ   |  |  |  |  |

| 6                   | IFC   |  |  |  |  |

| 7                   | REN   |  |  |  |  |

₩ = EDGE SENSITIVE CONNECTIONS

Figure 4-2. Timing Jumper Reconfiguration.

Change the logic analyzer [ Timing ] Format Specification channel assignments to those shown below.

[Timing] Format Specification\_\_\_\_\_

| [Assigr | nment] | Pod1                 |

|---------|--------|----------------------|

| _       | _      | [ TTL ]              |

|         |        | = =                  |

|         |        | 70                   |

| Activit | :y>    |                      |

| Label   | Po1    |                      |

| ATN     | [+]    | [*]                  |

| SRQ     | [+]    | [*]                  |

| IFC     | [+]    | [.*]                 |

| NDAC    | [+]    | [*]                  |

| NRFD    | [+]    | [*.]                 |

| DAV     | [+]    | $[\ldots, \star, .]$ |

| REN     | [+]    | [*]                  |

| EOI     | [+]    | $[\ldots *\ldots]$   |

|         |        |                      |

Figure 4-3. [ Timing ] Format Specification Menu Reconfiguration.

# Chapter 5 RS-232-C/V.24 BUS PREPROCESSING

#### INTRODUCTION

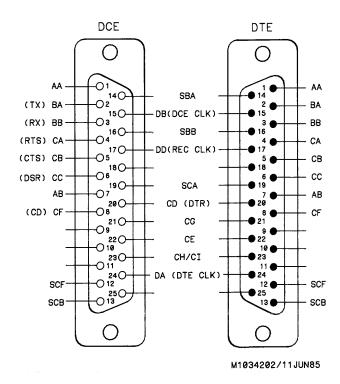

The RS-232-C/V.24 is a serial interface with unbalanced data and control lines. A brief overview of RS-232-C/V.24 is given in Appendix C. A comparison between several of the serial interfaces is provided in Appendix B. Further references to RS-232-C should be assumed to include CCITT V.24.

#### PREPROCESSOR FUNCTION

The primary function of the HP 10342B is to convert the serial data stream into parallel data and status. It monitors five handshake lines and stores their states for each character. Four of the handshake lines are synchronous with the serial controller and one line (carrier detect) is asynchronous but sampled each time a character is output to the logic analyzer.

All lines are buffered at the input to the HP 10342B. The buffers provide one RS-232-C standard load to the bus. Signals are inverted by the buffer circuitry.

The HP 10342B provides a mass-connect feature for connecting the bus lines to timing channels, or individual connections can be made with jumper wires provided. Timing connections are made to the buffered and inverted signals.

Additionally, any buffered line can be connected to one of the three HP 10342B front panel outputs provided. These can be used for connection to an oscilloscope or one of the analog channels or trigger of an HP 1631A/D.

#### SYSTEM SET-UP

The minimum equipment necessary to use the HP 10342B Bus Preprocessor is as follows:

Logic Analyzer: HP 1630A/D/G\* or HP 1631A/D\*

\* with HP 1630/31A or HP 1630G only 8 timing channels are available

Probe Interface: HP 10269A\* or HP 10269B

\* with the HP 10269A only 8 timing channels are available

Disc Drive: HP 9121D/S or HP 9122D/S

HP-IB cables for peripherals HP 10342B Bus Preprocessor

Use the following step-by-step procedure to set up the system for RS-232-C preprocessing.

#### Logic Analyzer

**SET UP SYSTEM**

Set up your logic analyzer system using procedures in your equipment operators manuals. Set-up will depend on the equipment and peripherals you are using.

#### **Bus Preprocessor**

The HP 10342B comes from the factory set up for processing HP-IB.

### CONNECT TIMING JUMPER

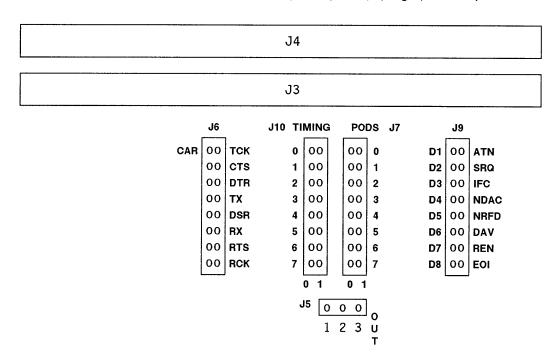

On the HP 10342B, connect the ribbon jumper cable to the appropriate pins. All 16 possible timing channels are connected when the jumper cable is connected from J6 to J10. Only nine channels are used with RS-232-C processing. See figure 5-1.

If you use the single jumper wires to connect the timing signals be sure to connect them to corresponding pins of J6 and J10 or the data captured will not match the HP 163X setup provided on disc. You would then need to change the HP 163X [Timing] Format Specification menu to match your hook-up.

### CONNECT FRONT PANEL OUTPUTS

If you want any data or control lines connected to the front panel outputs, use the single jumper wires to connect pins of J7 to pins of J5. See figure 5-1. When using the mass-connect jumper cable the signals at J7 correspond to the mnemonics at J6.

For example: To connect TCK to front panel Output 1, connect a jumper between J7 pod 1 pin 0 (top right) and J5 pin 1.

Figure 5-1. RS-232-C Timing Connector Locations.

SET DTE/DCE SWITCH Set the DTE/DCE switch (left side of PC board) to the position corresponding to the desired sync transmit clock. If the transmit clock from the terminal (computer) is desired use DTE and if the transmit clock from the modem is desired use DCE.

#### **INSTALL PREPROCESSOR**

Once all the connections are made, place the HP 10342B at the bottom of the HP 10269B and connect the two 60-pin cables to the connectors on the HP 10342B. Fit the HP 10342B into the bottom of the HP 10269B and fasten them together with the two captive screws.

#### FRONT PANEL **SWITCHES**

Set the front panel switches depending on the protocol, parity, etc. of the bus you are working with. The HP 10342B needs the proper protocol settings to disassemble the data on the bus.

BIT

In BIT PROTOCOL (BOP, bit oriented synchronous protocol), the only other switch setting that must be made is 8 ASCII or 8 EBCDIC in BITS/CHAR. No other switch selections are relevant because the rest of the protocol is predefined. Clock comes from the external source, either terminal (DTE) or modem (DCE).

CHAR

In CHAR PROTOCOL (BCP, byte control synchronous protocol), the PARITY and BITS/CHAR switch settings must be set so that the HP 10342B knows which characters to svnc on. These svnc characters are not displayed due to internal processing in the HP 10342B. Clock comes from the external source, either terminal (DTE) or modem (DCE).

#### ASYNC

When ASYNChronous is selected, the settings of all other front panel switches are relevant. The clock source is from the internal source. ASYNC BITS/SEC.

The PARITY must be set.

The BITS/CHAR must be set.

ASYNC BITS/SEC must be set.

When transmit or receive data is present a state will be stored. Lack of data, or improper sync characters, results in a slow clock indication from the logic analyzer.

#### **Probe Interface**

Either an HP 10269B or HP 10269A can be used with the HP 10342B. The HP 10269A does not support the additional 8 timing channels of the HP 1630D. Since the HP 10342B provides nine timing channels, the CAR (Carrier Detect) line is dropped for eight-channel timing.

### POD CONNECTOR OVERLAY

Lay the HP 10269B overlay over the pod connectors. If you are using an HP 10269A the overlay will be too large to fit well. The overlay shows where pods connect for various logic analyzers and bus preprocessing. It also gives other useful information.

#### **CONNECT PODS**

Connect the logic analyzer pods to the connectors on the HP 10269. If you are using an HP 10269B follow the overlay. For an HP 163XD, POD 2 connects to connector A, POD 3 to B, POD 1 to E, and POD 0 to connector I. If you are using an HP 163XA/G there is no POD 0. If you are using an HP 10269A the connections are the same except there is no POD connector I.

If you are using the HP 10342B on both RS-232-C and HP-IB, you can connect logic analyzer POD 4 to pod connector D. You can then switch to HP-IB processing by moving POD 3 to connector C and loading the HP-IB inverse assembler and configuration files.

#### **CONNECT POWER**

Connect the BNC cable supplied with the HP 10269B between the +5V input of the HP 10269B and the +5V output of the logic analyzer.

#### CONNECT RS-232-C CABLE

Connect the RS-232 ribbon cable between the bus to be monitored and the RS-232C/V.24 connector on the HP 10342B.

#### System Operation

Be sure all the addresses are set on the peripherals before you apply power, since most address switch settings are read on power-up.

| APPLY POWER | Turn on power for all equipment involved. The logic analyzer comes |

|-------------|--------------------------------------------------------------------|

|             | up in the [Configuration] menu of the System Specification. Press  |

the PREV[] key to get the [Storage Operations] menu.

CHECK FOR DISC Press INSERT to check for the disc drive and display the disc file

directory.

LOAD INVASM ROLL the list up to point to the desired file to load. The inverse

assembler must be loaded first, so load "IRS232C invasm" by pointing to it, selecting [Load] for an Operation, and pressing

INSERT.

LOAD CONFIG Next, load the configuration file "IRS232C config" or "IRS232G

config" depending on your logic analyzer. The instrument will not

load the wrong one.

RUN Press RUN. As soon as data is available on the bus the logic

analyzer will begin to accumulate data.

You may modify the logic analyzer menus to suit the measurement you need to make. Consult your logic analyzer Operating Manual for further information.

#### SIGNAL CONNECTIONS

The HP 10342B provides processed data and status to the logic analyzer state inputs. The timing inputs are buffered from the RS-232-C bus except for TX CLK and RX CLK which are selected in the HP 10342B.

Table 5-1. Logic Analyzer to RS-232-C Signal Connections.

|                     | STATE <sup>1</sup> |             |              |  |  |  |  |  |  |

|---------------------|--------------------|-------------|--------------|--|--|--|--|--|--|

|                     | HP 10              | HP 163X     |              |  |  |  |  |  |  |

| SIGNAL              | CONN               | PIN         | POD          |  |  |  |  |  |  |

| Clock               | Α                  | L CLK       | 2            |  |  |  |  |  |  |

|                     |                    |             |              |  |  |  |  |  |  |

|                     | Α                  | 0           |              |  |  |  |  |  |  |

|                     | Α                  | 1<br>2<br>3 |              |  |  |  |  |  |  |

| Serial              | A                  | 2           |              |  |  |  |  |  |  |

| Data                | Α                  | 3           |              |  |  |  |  |  |  |

| Converted<br>to     | Α                  | 4           |              |  |  |  |  |  |  |

| Parallel            | A                  | 5           |              |  |  |  |  |  |  |

| raialici            | Ā                  | 6           |              |  |  |  |  |  |  |

|                     | Â                  | 7           | 2            |  |  |  |  |  |  |

| TX/RX               | В                  | 0           | 3            |  |  |  |  |  |  |

| CC LSB              | В                  | 1           |              |  |  |  |  |  |  |

| CC MSB              | В                  | 2<br>3      |              |  |  |  |  |  |  |

| CTS                 | В                  | 3           |              |  |  |  |  |  |  |

| DCD                 | Б                  | 4           |              |  |  |  |  |  |  |

| DSR<br>RTS          | B<br>B             | 5           |              |  |  |  |  |  |  |

| DTR                 | В                  | 6           |              |  |  |  |  |  |  |

| CD                  | В                  | 3           |              |  |  |  |  |  |  |

|                     |                    | 7<br>TIMING | <del>.</del> |  |  |  |  |  |  |

| TX CLK <sup>3</sup> | E                  | 0           | 1            |  |  |  |  |  |  |

| CTS⁴                | E                  | 1           |              |  |  |  |  |  |  |

| DTR <sup>4</sup>    |                    | 2           |              |  |  |  |  |  |  |

| TX <sup>4</sup>     | E                  | 3           |              |  |  |  |  |  |  |

| DSR <sup>4</sup>    | Е                  | 4           |              |  |  |  |  |  |  |

| RX <sup>4</sup>     | E                  | 5           |              |  |  |  |  |  |  |

| RTS <sup>4</sup>    | E                  | 6           |              |  |  |  |  |  |  |

| RX CLK <sup>3</sup> | Ē                  | 7           | 1            |  |  |  |  |  |  |

| CAR <sup>4,5</sup>  | I                  | 0           | 0            |  |  |  |  |  |  |

- 1. Processed through SIO in HP 10342B

- 2. Same for HP 10269A except no pod connector I (POD 0).

- 3. Clock selected in HP 10342B

- 4. Signal from buffered RS-232-C lines.

- 5. HP 163XD only and HP 10269B only.

#### Clock

One clock is supplied to the logic analyzer from the processor in the HP 10342B. This clock is provided to POD 2 and is the L Clock. The logic analyzer clocks data on the negative edge of the L Clock.

#### Data

The Data, at HP 10269 connector A (logic analyzer POD 2), is the parallel format of the serial data byte. It has been processed in the SIO (Serial IN/OUT Interface) and processor of the HP 10342B.

#### **Status Byte**

The Status Byte, at Connector B of the HP 10269, is provided by the processor in the HP 10342B.

Bit 0 represents whether the data is transmitted (1) or received (0) and is used by the inverse assembler.

Bits 1 and 2, CC LSB and CC MSB, represent front panel settings for BITS/CHAR and are used by the inverse assembler to interpret data.

00 = Normal Character

01 = EBCDIC Character Set

10 = 6-bit Transcode Character Set

11 = Not Used

Bits 3-7 are the handshake signals. They have been processed in the SIO in the HP 10342B and represent the status of the handshake lines for each serial data byte.

#### **Timing Signals**

For further information about the timing signals see text and partial schematics following SCHEMATICS in Chapter 2.

Most timing signals are buffered directly from the RS-232-C bus. The TXCLK and RXCLK are clocks selected in the HP 10342B by the DTE/DCE switch and front panel set-up.

The Carrier Detect (CAR) is also buffered directly from the RS-232-C bus. The CAR timing signal is not available when using a factory configured HP 10342B with the HP 163XA, HP 1630G, or the HP 10269A.

The timing signals supplied to the logic analyzer are of the opposite sense compared to the mark/space definition in the RS-232-C standard (see figure 5-2). The line receivers buffer, invert, and convert the RS-232 signals to TTL. The logic analyzer timing inputs are not designed to handle the ±25V signals specified by RS-232-C, so they are connected to the buffered signals.

Though the timing signals are of the opposite sense to that defined by the RS-232-C specification, they are of the same sense as the signals supplied to the RS-232 line drivers in the DCE. This makes it easier to compare the output (TTL) of the asynchronous receiver/transmitter in the DCE to the TTL signal applied to the SIO in the DTE.

Figure 5-2. Signal Sense Diagram.

#### ADDRESS (ADDR)

There is an Address (ADDR) label set up in the [State] Format Specification with one bit from a pod assigned to the label. There is no RS-232-C information in this label. The label is necessary for operation of the logic analyzer but not for use with the HP 10342B. If the ADDR label appears on screen you can go to the [State] List menu and move it off the screen using the SHIFT and ROLL keys. This is done by the configuration file when the software is loaded.

#### **MNEMONICS**

The HP 10342B inverse assembler for RS-232-C uses the common mnemonics rather than the mnemonics specified in the EIA Standard. Table 5-2 provides a cross reference.

Table 5-2. RS-232-C Mnemonic Cross Reference.

| PIN | MNEMONIC |

|-----|----------|

| PIN | MNEMONIC |          |  |  |  |  |  |  |  |

|-----|----------|----------|--|--|--|--|--|--|--|

|     | COMMON   | RS-232-C |  |  |  |  |  |  |  |

| 2   | TX       | BA       |  |  |  |  |  |  |  |

| 3   | RX       | BB       |  |  |  |  |  |  |  |

| 4   | RTS      | CA       |  |  |  |  |  |  |  |

| 5   | CTS      | СВ       |  |  |  |  |  |  |  |

| 6   | DSR      | CC       |  |  |  |  |  |  |  |

| 8   | CD       | CF       |  |  |  |  |  |  |  |

| 15  | DCE CLK  | DB       |  |  |  |  |  |  |  |

| 17  | REC CLK  | DD       |  |  |  |  |  |  |  |

| 20  | DTR      | CD       |  |  |  |  |  |  |  |

| 24  | DTE CLK  | DA       |  |  |  |  |  |  |  |

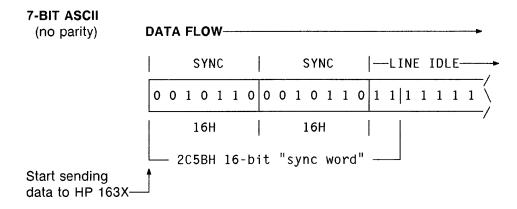

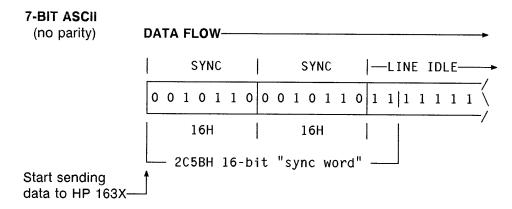

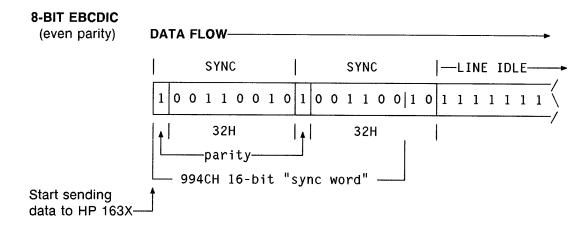

#### SYNC CHARACTERS

The HP 10342B must receive the proper sync characters in order to process data. The SIO is programmed to recognize the standard sync characters for the selected character code. If some other sync characters are being sent the logic analyzer will display "Slow Clock".

The only place the transmitted sync character can be seen is in the timing display. The HP 10342B does not provide the sync characters to the state display. Table 5-3 shows the expected sync characters for given character codes.

| CHAR CODE    | SYNC CHAR |

|--------------|-----------|

| 6 BIT TRANS  | 3A3A HEX  |

| 7 BIT ASCII  | 1616 HEX  |

| 8 BIT ASCII  | 1616 HEX  |

| 8 BIT EBCDIC | 3232 HEX  |

Table 5-3. Standard Sync Characters.

The SIO recognizes a 16-bit "character word". When observing the sync character data string, the relationship of this word to the idle characteristics of the data line and the parity of the transmitted data must be taken into account. This is shown further in the following two examples.

When observing bit strings on the timing channels of the logic analyzer note that data is clocked on the rising edge of TX CLK or RX CLK.

Figure 5-3. 7-Bit ASCII Sync Sequence.

As can be seen, the SIO uses two "bits" from the idle bus to fill out the two "missing" bits of the character. It then uses 2C5BH as a comparison to recognize the sync characters. If the bus does not idle high (idle high is standard) the sync characters will not be recognized.

Figure 5-4. 8-Bit EBCDIC Sync Sequence.

Here the sync characters with parity have a longer bit string than the "sync word". The two least significant bits are dropped and the SIO uses 994CH as a comparison to recognize the sync characters.

#### **BLOCK CHECK CHARACTERS**

Tha last two characters of the data stream are Block Check Characters (BCC). These characters are actually CRCs and are passed on to the logic analyzer as data. However, they have been altered by the SIO and their value is no longer significant.

## Chapter 6 RS-449 BUS PREPROCESSING

#### INTRODUCTION

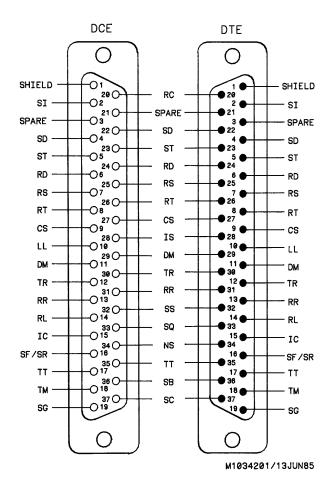

The RS-449 is a serial interface with balanced data and control lines. A brief overview of RS-449 is given in Appendix D. A comparison between several of the serial interfaces is provided in Appendix B.

#### PREPROCESSOR FUNCTION

The RS-449 has two categories of interchange circuits, Category I and Category II. Category I circuits are the high-speed circuits and are balanced. Category II circuits are low-speed, unbalanced and used for secondary functions. The HP 10342B processes only the Category I circuits.

The primary function of the HP 10342B is to convert the serial data stream into parallel data and status. It monitors five handshake lines and stores their states for each character. Four of the handshake lines are synchronous with the serial controller and one line (carrier detect) is asynchronous but sampled each time a character is output to the logic analyzer.

All lines are buffered at the input to the HP 10342B. The buffers provide one RS-449 standard load to the bus. Signals are inverted by the buffer circuitry.

The HP 10342B provides a mass-connect feature for connecting the bus lines to timing channels, or individual connections can be made with jumper wires provided. Timing connections are made to the buffered and inverted signals.

Additionally, any buffered line can be connected to one of the three HP 10342B front panel outputs provided. These can be used for connection to an oscilloscope or one of the analog channels or trigger of an HP 1631A/D.

#### SYSTEM SET-UP

The minimum equipment necessary to use the HP 10342B Bus Preprocessor is as follows:

Logic Analyzer: HP 1630A/D/G\* or HP 1631A/D\*

\* with HP 1630/31A or HP 1630G only 8 timing channels are available

Probe Interface: HP 10269A\* or HP 10269B

\* with the HP 10269A only 8 timing channels are available

Disc Drive: HP 9121D/S or HP 9122D/S

HP-IB cables for peripherals HP 10342B Bus Preprocessor

Use the following step-by-step procedure to set up the system for RS-449 preprocessing.

#### Logic Analyzer

**SET UP SYSTEM**

Set up your logic analyzer system using procedures in your equipment operators manuals. Set-up will depend on the equipment and peripherals you are using.

#### **Bus Preprocessor**

The HP 10342B comes from the factory set up for processing HP-IB.

### CONNECT TIMING JUMPER

On the HP 10342B, connect the ribbon jumper cable to the appropriate pins. All 16 possible timing channels are connected when the jumper cable is connected from J6 to J10. Only nine channels are used with RS-449 processing. See figure 6-1.

If you use the single jumper wires to connect the timing signals be sure to connect them to corresponding pins of J6 and J10 or the data captured will not match the HP 163X setup provided on disc. You would then need to change the HP 163X [Timing] Format Specification menu to match your hook-up.

### CONNECT FRONT PANEL OUTPUTS

If you want any data or control lines connected to the front panel outputs, use the single jumper wires to connect pins of J7 to pins of J5. See figure 6-1. When using the mass-connect jumper cable the signals at J7 correspond to the mnemonics at J6.

For example: To connect TCK to front panel Output 1, connect a jumper between J7 pod 1 pin 0 (top right) and J5 pin 1.

Figure 6-1. Timing Connector Locations.

SET DTE/DCE SWITCH Set the DTE/DCE switch (left side of PC board) to the position corresponding to the desired sync transmit clock. If the transmit clock from the terminal (computer) is desired use DTE and if the transmit clock from the modem is desired use DCE.

#### **INSTALL PREPROCESSOR**

Once all the connections are made, place the HP 10342B at the bottom of the HP 10269B and connect the two 60-pin cables to the connectors on the HP 10342B. Fit the HP 10342B into the bottom of the HP 10269B and fasten them together with the two captive screws.

#### **FRONT PANEL SWITCHES**

Set the front panel switches depending on the protocol, parity, etc. of the bus you are working with. The HP 10342B needs the proper protocol settings to disassemble the data on the bus.

**BIT**

In BIT PROTOCOL (BOP, bit oriented synchronous protocol), the only other switch setting that must be made is 8 ASCII or 8 EBCDIC in BITS/CHAR. No other switch selections are relevant because the rest of the protocol is predefined. Clock comes from the external source, either terminal (DTE) or modem (DCE).

#### **CHAR**

In CHAR PROTOCOL (BCP, byte control synchronous protocol), the PARITY and BITS/CHAR switch settings must be set so that the HP 10342B knows which characters to svnc on. These characters are not displayed due to internal processing in the HP 10342B. Clock comes from the external source, either terminal (DTE) or modem (DCE). Parity must be specified as shown in the following table.

#### **ASYNC**

When ASYNChronous is selected, the settings of all other front panel switches are relevant. The clock source is from the internal source, ASYNC BITS/SEC.

The PARITY must be set.

The BITS/CHAR must be set.

ASYNC BITS/SEC must be set.

When transmit or receive data is present a state will be stored. Lack of data results in a slow clock indication from the logic analyzer.

#### **Probe Interface**

Either an HP 10269B or HP 10269A can be used with the HP 10342B. The HP 10269A does not support the additional 8 timing channels of the HP 1630D. Since the RS-449 only uses nine timing channels, the RR (Receiver Ready) line is dropped for eight-channel timing.

### POD CONNECTOR OVERLAY

Lay the HP 10269B overlay over the pod connectors. If you are using an HP 10269A the overlay will be too large to fit well. The overlay shows where pods connect for various logic analyzers and bus preprocessing. It also gives other useful information.

#### **CONNECT PODS**

Connect the logic analyzer pods to the connectors on the HP 10269. If you are using an HP 10269B follow the overlay. For an HP 163XD, POD 2 connects to connector A, POD 3 to B, POD 1 to E, and POD 0 to connector I. If you are using an HP 1630A/G or HP 1631A there is no POD 0. I you are using an HP 10269A the connections are the same except there is no POD connector I.

If you are going to be using the HP 10342B on both RS-449 and HP-IB, you can connect logic analyzer POD 4 to pod connector D. This will allow you to switch to HP-IB processing by moving POD 3 to connector C and loading the HP-IB inverse assembler and configuration file.

#### **CONNECT POWER**

Connect the BNC to BNC cable supplied with the HP 10269B between the +5V input of the HP 10269 and the +5V output of the logic analyzer.

#### CONNECT RS-449 CABLE

Connect the RS-449 ribbon cable between the bus to be monitored and the RS-449 connector on the HP 10342B.

#### **System Operation**

Be sure all the addresses are set on the peripherals before you apply power, since most address switch settings are read on power-up.

| APPLY POWER | Turn on power for all equipment involved. The logic analyzer comes |

|-------------|--------------------------------------------------------------------|

|             | up in the [Configuration] menu of the System Specification. Press  |

|             | the PREV[] key to get the [Storage Operations] menu.               |

|             |                                                                    |

## CHECK FOR DISC Press INSERT to check for the disc drive and display the disc file directory.

| LOAD INVASM | ROLL the list up to point to the desired file to load. The inverse                                                                 |

|-------------|------------------------------------------------------------------------------------------------------------------------------------|

|             | assembler must be loaded first, so load "IRS449 invasm" by pointing to it, selecting [Load] for an Operation, and pressing INSERT. |

| LOAD CONFIG | Next, load the configuration file "IRS449 config" or "IRS449G     |

|-------------|-------------------------------------------------------------------|

|             | config" depending on your logic analyzer. The instrument will not |

|             | load the wrong one.                                               |

| RUN | Press                                   | RUN. | As | soon | as | data | is | available | on | the | bus | the | logic |

|-----|-----------------------------------------|------|----|------|----|------|----|-----------|----|-----|-----|-----|-------|

|     | analyzer will begin to accumulate data. |      |    |      |    |      |    |           |    |     |     |     |       |

You may modify the logic analyzer menus to suit the measurement you need to make. Consult your logic analyzer Operating Manual for further information.

# SIGNAL CONNECTIONS

The HP 10342B provides processed data and status to the logic analyzer state inputs.

Table 6-1. Logic Analyzer to RS-449 Signal Connections.

|                                          | STATE <sup>1</sup> |         |          |  |  |

|------------------------------------------|--------------------|---------|----------|--|--|

|                                          | HP 10              | HP 163X |          |  |  |

| SIGNAL                                   | CONN               | PIN     | POD      |  |  |

| Clock                                    | Α                  | L CLK   | 2        |  |  |

|                                          |                    |         |          |  |  |

|                                          | Α                  | 0       |          |  |  |

|                                          | Α                  | 1       |          |  |  |

| Serial                                   | Α                  | 2       |          |  |  |

| Data                                     | Α                  | 3       |          |  |  |

| Converted                                |                    |         |          |  |  |

| to                                       | Α                  | 4       |          |  |  |

| Parallel                                 | A                  | 5       |          |  |  |

|                                          | A                  | 6<br>7  | <b>†</b> |  |  |

| TY/DY                                    | <u>А</u><br>В      |         | 2 3      |  |  |

| TX/RX<br>CC LSB                          | В                  | 1       | ]        |  |  |

| CC LSB                                   | В                  | 2       |          |  |  |

| CS                                       | В                  | 3       |          |  |  |

|                                          | ال                 | U       |          |  |  |

| DM                                       | В                  | 4       |          |  |  |

| RS                                       | В                  | 5       |          |  |  |

| TR                                       | В                  | 6       | ↓        |  |  |

| RR                                       | В                  | 7       | š        |  |  |

|                                          |                    | TIMING  |          |  |  |

| TX CLK <sup>3</sup>                      | Ε                  | 0       | 1        |  |  |

| CS <sup>4</sup>                          | E                  | 1       |          |  |  |

| TR <sup>4</sup>                          | Ε                  | 2       |          |  |  |

| SD <sup>4</sup>                          | Ε                  | 3       |          |  |  |

|                                          | _                  |         |          |  |  |

| DM <sup>4</sup>                          | E                  | 4       |          |  |  |

| RD <sup>4</sup>                          | E                  | 5       |          |  |  |

| RS <sup>4</sup>                          | E                  | 6       |          |  |  |

| RX CLK <sup>3</sup><br>RR <sup>4,5</sup> | E                  | 7       | 0        |  |  |

| KKT,2                                    | 1                  | U       | U        |  |  |

- 1. Processed through SIO in HP 10342B

- 2. Same for HP 10269A except no pod connector I (POD 0).

- 3. Clock selected in HP 10342B

- 4. Signal from buffered RS-449 lines.

- 5. HP 1630D only.

#### Clock

One clock is supplied to the logic analyzer from the processor in the HP 10342B. This clock is provided to POD 2 and is the L Clock. The logic analyzer clocks data on the negative edge of the L Clock.

### Data

The Data, at HP 10269 connector A (logic analyzer POD 2), is the parallel format of the serial data byte. It has been processed in the SIO (Serial IN/OUT interface) and processor of the HP 10342B.

## Status Byte

The Status Byte, at connector B of the HP 10269, is provided by the processor in the HP 10342B.

Bit 0 represents whether the data is transmitted (1) or received (0) and is used by the inverse assembler.

Bits 1 and 2, CC LSB and CC MSB, represent front panel settings for BITS/CHAR and are used by the inverse assembler to interpret data.

00 = Normal Character

01 = EBCDIC Character Set

10 = 6-bit Transcode Character Set

11 = Not Used

Bits 3-7 are the handshake signals. They have been processed in the SIO in the HP 10342B and represent the status of the handshake lines for each serial data byte.

### **Timing Signals**

For further information about the timing signals see text and partial schematics following SCHEMATICS in Chapter 2.

Most timing signals are buffered directly from the RS-449 bus. The TXCLK and RXCLK are clocks selected in the HP 10342B by the DTE/DCE switch and front panel set-up.

The Receiver Ready (RR) is also buffered directly from the RS-449 bus. The RR timing signal is not available when using a factory configured HP 10342B with the HP 163XA, HP 1630G, or the HP 10269A.

The timing signals supplied to the logic analyzer are of the opposite sense compared to the mark/space definition in the RS-449 standard (see figure 6-2). The line receivers buffer, invert, and convert the RS-449 signals to TTL.

Though the timing signals are of the opposite sense to that defined by the RS-449 specification, they are of the same sense as the signals supplied to the RS-449 line drivers in the DCE. This makes it easier to compare the output (TTL) of the asynchronous receiver/transmitter in the DCE to the TTL signal applied to the SIO in the DTE.

Figure 6-2. Signal Sense Diagram.

# ADDRESS (ADDR)

There is an Address (ADDR) label set up in the [State] Format Specification with one bit from a pod assigned to the label. There is no RS-449 information in this label. The label is necessary for operation of the logic analyzer but not for use with the HP 10342B. If the ADDR label appears on screen you can go to the [State] List menu and move it off the screen using the SHIFT and ROLL keys. This is done by the configuration file when the software is loaded.

### SYNC CHARACTERS

The HP 10342B must receive the proper sync characters in order to process data. The SIO is programmed to recognize the standard sync characters for the selected character code. If some other sync characters are being sent the logic analyzer will display "Slow Clock".

The only place the transmitted sync character can be seen is in the timing display. The HP 10342B does not provide the sync characters to the state display. Table 6-2 shows the expected sync characters for given character codes.

| CHAR CODE    | SYNC CHAR |

|--------------|-----------|

| 6 BIT TRANS  | 3A3A HEX  |

| 7 BIT ASCII  | 1616 HEX  |

| 8 BIT ASCII  | 1616 HEX  |

| 8 BIT EBCDIC | 3232 HEX  |

Table 6-2. Standard Sync Characters.

The SIO recognizes a 16-bit "character word". When observing the sync character data string, the relationship of this word to the idle characteristics of the data line and the parity of the transmitted data must be taken into account. This is shown further in the following two examples.

When observing bit strings on the timing channels of the logic analyzer note that data is clocked on the rising edge of TX CLK or RX CLK.

Figure 6-3. 7-Bit ASCII Sync Sequence.

As can be seen, the SIO uses two "bits" from the idle bus to fill out the two "missing" bits of the character. It then uses 2C5BH as a comparison to recognize the sync characters. If the bus does not idle high (idle high is standard) the sync characters will not be recognized.

Figure 6-4. 8-Bit EBCDIC Sync Sequence.

Here the sync characters with parity have a longer bit string than the "sync word". The two least significant bits are dropped and the SIO uses 994CH as a comparison to recognize the sync characters.

### **BLOCK CHECK CHARACTERS**